Analog Devices AD7937 Datasheet

LC2MOS

a

FEATURES

Two 12-Bit DACs in One Package

DAC Ladder Resistance Matching: 0.5%

Surface-Mount Package

4-Quadrant Multiplication

Low Gain Error (3 LSB max Over Temperature)

Byte Loading Structure

Fast Interface Timing

APPLICATIONS

Automatic Test Equipment

Programmable Filters

Audio Applications

Synchro Applications

Process Control

GENERAL DESCRIPTION

The AD7937 contains two 12-bit current output DACs on one

monolithic chip. A separate reference input is provided for each

DAC. The dual DAC saves valuable board space, and the monolithic construction ensures excellent thermal tracking. Both DACs

are guaranteed 12-bit monotonic over the full temperature range.

The AD7937 has a 2-byte (eight LSBs, four MSBs) loading

structure. It is designed for right-justified data format. The control

signals for register loading are A0, A1, CS, WR, and UPD. Data

is loaded to the input registers when CS and WR are low. To

transfer this data to the DAC registers, UPD must be taken

low with WR.

Added features on the AD7937 include an asynchronous CLR

line which is very useful in calibration routines. When this is

taken low, all registers are cleared. The double buffering of the

data inputs allows simultaneous update of both DACs. Also,

each DAC has a separate AGND line. This increases the device

versatility; for instance, one DAC may be operated with AGND

biased while the other is connected in the standard configuration.

The AD7937 is manufactured using the Linear Compatible

CMOS (LC

microprocessors and accepts TTL, 74HC, and 5 V CMOS logic

level inputs.

2

MOS) process. It is speed compatible with most

(8+4) Loading Dual 12-Bit DAC

AD7937

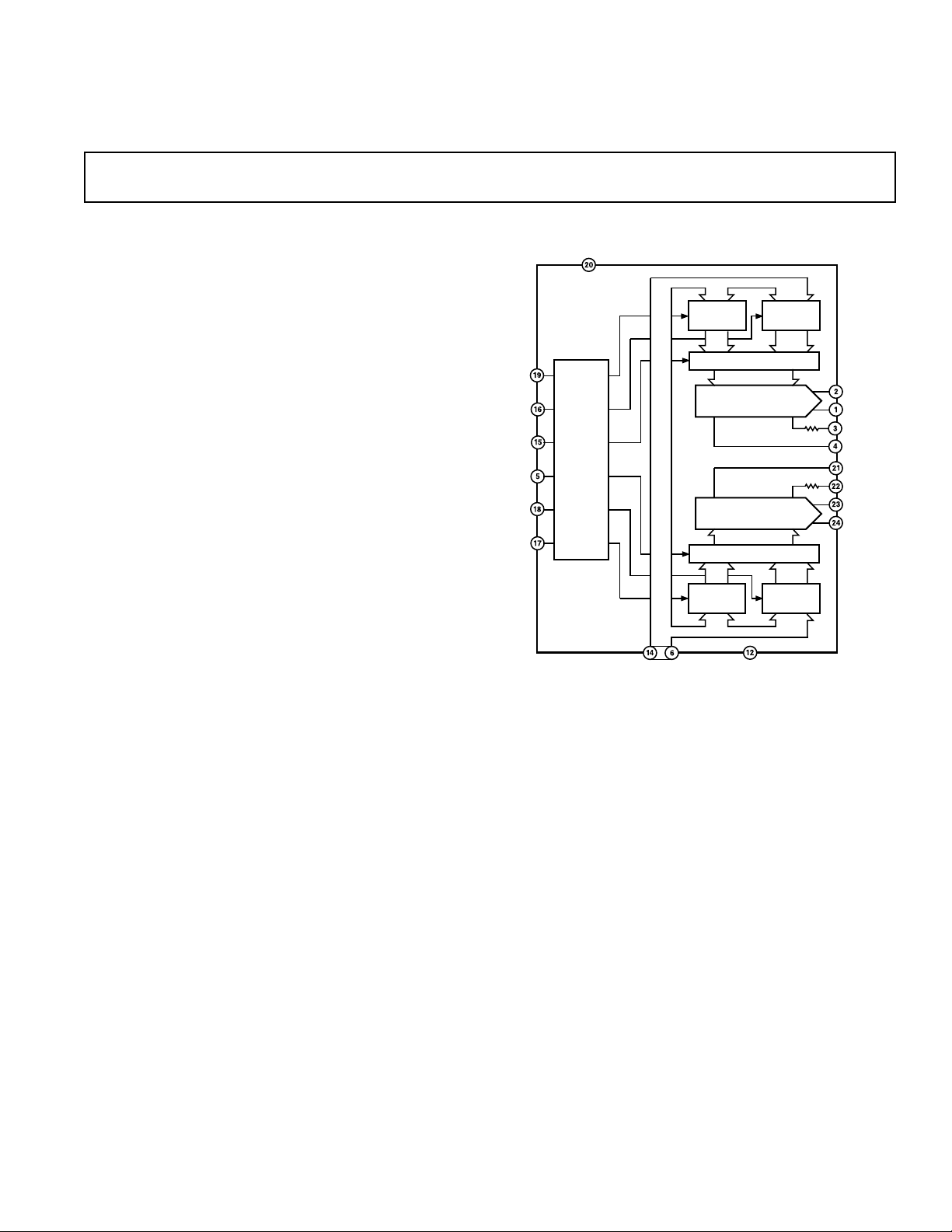

FUNCTIONAL BLOCK DIAGRAM

V

DD

AD7937

UPD

A1

A0

CONTROL

CS

WR

CLR

LOGIC

DB7–DB0 DGND

PRODUCT HIGHLIGHTS

1. DAC-to-DAC Matching

Since both DACs are fabricated on the same chip, precise

matching and tracking is inherent. Many applications that are

not practical using two discrete DACs are now possible.

Typical matching: 0.5%.

2. Small Package Size

The AD7937 is packaged in a small 24-lead SOIC.

3. Wide Power Supply Tolerance

The device operates on a 5 V V

this nominal figure. All specifications are guaranteed over

this range.

DAC A MS

INPUT REG

48

DAC A REGISTER

DAC B REGISTER

48

DAC B MS

INPUT REG

DD

DAC A LS

INPUT REG

12

DAC A

DAC B

12

DAC B LS

INPUT REG

, with ±10% tolerance on

I

OUTA

AGNDA

R

FBA

V

REFA

V

REFB

R

FBB

I

OUTB

AGNDB

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

AD7937–SPECIFICATIONS

(VDD = 5 V 10%, V

specifications T

MIN

= V

REFA

to T

MAX

= 10 V; I

REFB

unless otherwise noted.)

= AGNDA = 0 V, I

OUTA

= AGNDB = 0 V. All

OUTB

Parameter A Version B Version Unit Test Conditions/Comments

ACCURACY

Resolution 12 12 Bits

Relative Accuracy ±1 ±1/2 LSB max

Differential Nonlinearity ±1 ±1 LSB max All grades guaranteed monotonic over temperature.

, R

Gain Error ±6 ±3 LSB max Measured using R

Gain Temperature Coefficient

2

;

. Both DAC registers loaded with all 1s.

FBA

FBB

∆Gain/∆Temperature ±5 ±5 ppm/°C max Typical value is 1 ppm/°C.

Output Leakage Current

I

OUTA

I

OUTB

5 5 nA max DAC A Register loaded with all 0s.

10 10 nA max

5 5 nA max DAC B Register loaded with all 0s.

10 10 nA max

REFERENCE INPUT

Input Resistance 9 9 kΩ min Typical Input Resistance = 14 kΩ.

20 20 kΩ max

, V

V

REFA

REFB

Input Resistance Match ±3 ±3 % max Typically ±0.5%.

DIGITAL INPUTS

(Input High Voltage) 2.4 2.4 V min

V

IH

(Input Low Voltage) 0.8 0.8 V max

V

IL

(Input Current)

I

IN

+25°C ±1 ±1 µA max V

to T

T

MIN

CIN (Input Capacitance)

MAX

2

±10 ± 10 µA max

10 10 pF max

= VDD.

IN

POWER SUPPLY

V

DD

I

DD

4.5/5.5 4.5/5.5 V min/V max

2 2 mA max

0.1 0.1 mA typ

AC PERFORMANCE CHARACTERISTICS

These characteristics are included for Design Guidance only and are not subject to test.

(VDD = 5 V; V

Parameter TA = 25C Unit Test Conditions/Comments

Output Current Settling Time 1 µs max To 0.01% of full-scale range. I

Digital-to-Analog Glitch lmpulse 2.5 nV-s typ Measured with V

AC Feedthrough

V

REFA

V

REFB

Power Supply Rejection

∆Gain/∆V

Output Capacitance

C

OUTA

C

OUTB

C

OUTA

C

OUTB

Channel-to-Channel Isolation

V

REFA

V

REFB

Digital Crosstalk 2.5 nV-s typ Measured for a Code Transition of all 0s to all 1s. I

Output Noise Voltage Density 25 nV/√Hz typ Measured between R

(10 Hz–100 kHz) is 10 Hz–100 kHz.

Total Harmonic Distortion –82 dB typ VIN = 6 V rms, 1 kHz. Both DACs loaded with all 1s.

NOTES

1

Temperature range as follows: A, B Versions: –40°C to +85°C.

2

Sample tested at 25°C to ensure compliance.

Specifications subject to change without notice.

to I

to I

to I

to I

REFA

OUTA

OUTB

DD

OUTB

OUTA

= V

= 10 V; I

REFB

= AGNDA = 0 V, I

OUTA

–70 dB max V

–70 dB max DAC registers loaded with all 0s.

= AGNDB = 0 V. Output Amplifiers are AD644 except where noted.)

OUTB

load = 100 Ω, C

REFB

OUT

= 0 V. I

measured from falling edge of WR. Typical Value of Settling Time is 0.6 µs.

= V

registers alternately loaded with all 0s and all 1s.

, V

REFA

REFA

= 20 V p-p 10 kHz sine wave.

REFB

±0.01 % per % max ∆VDD = VDD max – VDD min.

70 pF max DAC A, DAC B loaded with all 0s.

70 pF max

140 pF max DAC A, DAC B loaded with all 1s.

140 pF max

–84 dB typ V

–84 dB typ V

= 20 V p-p 10 kHz sine wave, V

REFA

= 20 V p-p 10 kHz sine wave, V

REFB

C

= 13 pF.

EXT

and I

FBA

OUTA

EXT

, I

load = 100 Ω, C

OUTB

= 0 V. Both DACs loaded with all 1s.

= 0 V. Both DACs loaded with all 1s.

OUTA

and I

. Frequency of measurement

OUTB

or R

OUTA

REFB

REFA

FBB

= 13 pF. DAC output

= 13 pF. DAC

EXT

, I

load = 100 Ω,

OUTB

–2–

REV. 0

AD7937

WARNING!

ESD SENSITIVE DEVICE

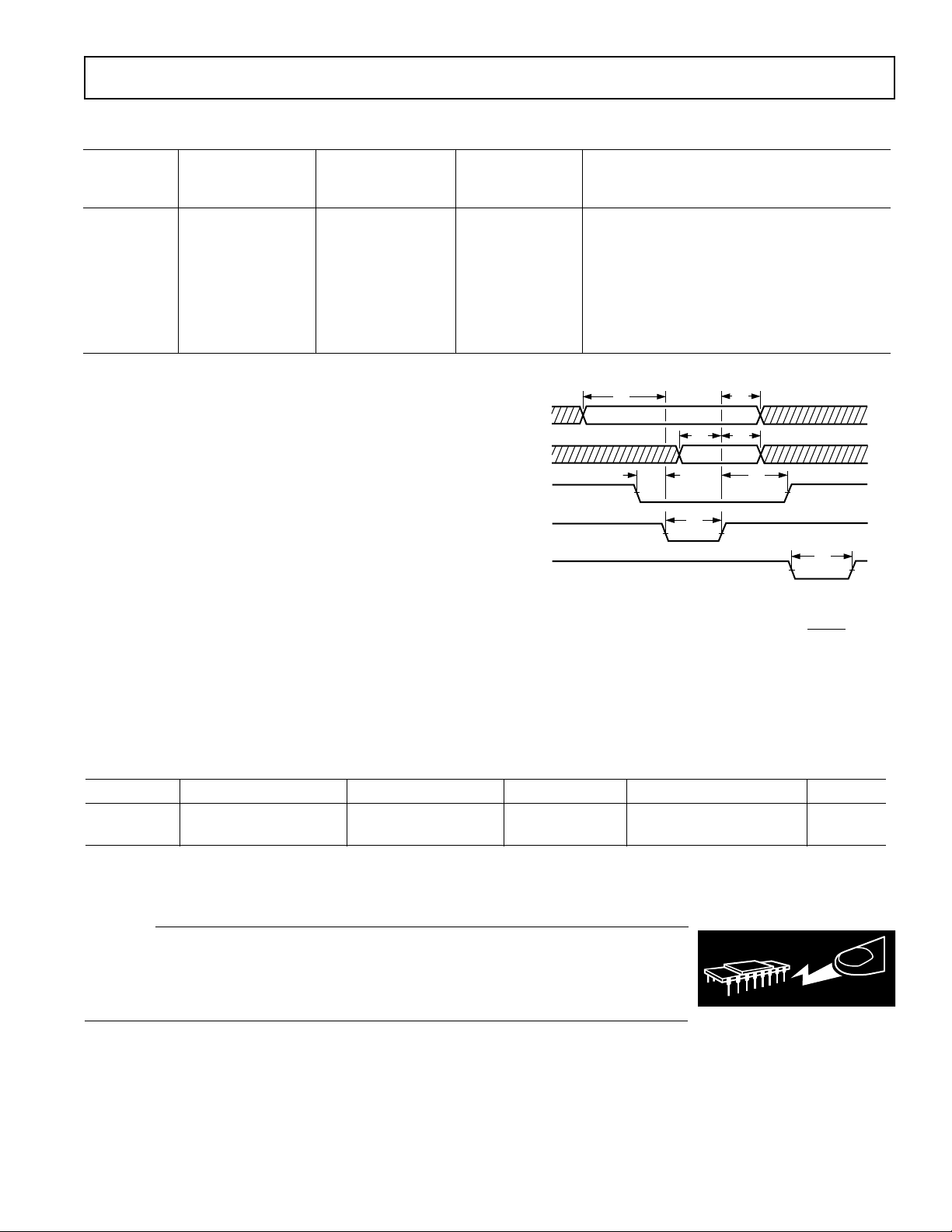

TIMING CHARACTERISTICS

(VDD = 5 V 10%, V

REFA

= V

= 10 V; I

REFB

= AGNDA = 0 V, I

OUTA

= AGNDB = 0 V.)

OUTB

Limit at

Limit at T

= –40C

A

Parameter TA = 25C to +85C Unit Test Conditions/Comments

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C unless otherwise noted)

VDD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +17 V

, V

V

V

REFA

RFBA

to AGNDA, AGNDB . . . . . . . . . . . . . . . . ±25 V

REFB

, V

to AGNDA, AGNDB . . . . . . . . . . . . . . . . ±25 V

RFBB

Digital Input Voltage to DGND . . . . . . . –0.3 V, V

, I

I

OUTA

to DGND . . . . . . . . . . . . . . –0.3 V, VDD +0.3 V

OUTB

AGNDA, AGNDB to DGND . . . . . . . . . –0.3 V, V

SOIC Package

, Thermal Impedance . . . . . . . . . . . . . . . . . . . . 72°C/W

θ

JA

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . 300°C

IR Ref Low Peak Temperature . . . . . . . . . . . . . . . . . . 220°C

Operating Temperature Range

Industrial (A, B Versions) . . . . . . . . . . . . . –40°C to +85°C

10 10 ns min Address Valid to Write Setup Time

10 10 ns min Address Valid to Write Hold Time

20 40 ns min Data Setup Time

30 30 ns min Data Hold Time

0 0 ns min Chip Select or Update to Write Setup Time

0 0 ns min Chip Select or Update to Write Hold Time

115 125 ns min Write Pulsewidth

90 100 ns min Clear Pulsewidth

t

3

t

7

t

2

t

4

= tf = 20ns.

r

t

6

+0.3 V

DD

+0.3 V

DD

A0–A1

DATA

CS, UPD

WR

CLR

t

1

t

5

NOTES

1. ALL INPUT SIGNAL RISE AND FALL TIMES MEASURED

FROM 10% TO 90% OF +5V. t

2. TIMING MEASUREMENT REFERENCE LEVELS IS

Storage Temperature . . . . . . . . . . . . . . . . –65°C to +150°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

Figure 1. Timing Diagram

5V

0V

5V

0V

5V

0V

5V

0V

t

8

+ V

V

IH

5V

0V

IL

2

ORDERING GUIDE

Model Temperature Range Relative Accuracy Gain Error Package Description Option

AD7937AR –40°C to +85°C ±1 LSB ±6 LSB Small Outline R-24

AD7937BR –40°C to +85°C ± 1/2 LSB ±3 LSB Small Outline R-24

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD7937 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. 0

–3–

Loading...

Loading...