Analog Devices AD7751EB, AD7751ABRS, AD7751AARS, AD7751AAN-REF Datasheet

Energy Metering IC

a

FEATURES

High Accuracy, Supports 50 Hz/60 Hz IEC 687/1036

Less than 0.1% Error Over a Dynamic Range of 500 to 1

Supplies

Average Real Power

Outputs F1 and F2

High-Frequency Output CF Is Intended for Calibration

and Supplies

Instantaneous Real Power

Continuous Monitoring of the Phase and Neutral

Current Allows Fault Detection in Two-Wire

Distribution Systems

AD7751 Uses the Larger of the Two Currents (Phase

or Neutral) to Bill—Even During a Fault Condition

Two Logic Outputs (FAULT and REVP) Can be Used to

Indicate a Potential Miswiring or Fault Condition

Direct Drive for Electromechanical Counters and

Two-Phase Stepper Motors (F1 and F2)

A PGA in the Current Channel Allows the Use of Small

Shunt

Values of

and

Proprietary ADCs and DSP Provide High Accuracy Over

Large Variations in Environmental Conditions and Time

On-Chip Power Supply Monitoring

On-Chip Creep Protection (No Load Threshold)

On-Chip Reference 2.5 V ⴞ 8% (30 ppm/ⴗC Typical)

with External Overdrive Capability

Single 5 V Supply, Low Power (15 mW Typical)

Low-Cost CMOS Process

GENERAL DESCRIPTION

The AD7751 is a high-accuracy fault-tolerant electrical energy

measurement IC that is intended for use with 2-wire distribution

systems. The part specifications surpass the accuracy requirements as quoted in the IEC1036 standard.

on the Frequency

Burden Resistance

With On-Chip Fault Detection

AD7751*

The only analog circuitry used in the AD7751 is in the ADCs

and reference circuit. All other signal processing (e.g., multiplication and filtering) is carried out in the digital domain. This

approach provides superior stability and accuracy over extremes

in environmental conditions and over time.

The AD7751 incorporates a novel fault detection scheme that

warns of fault conditions and allows the AD7751 to continue

accurate billing during a fault event. The AD7751 does this

by continuously monitoring both the phase and neutral (return) currents. A fault is indicated when these currents differ by

more than 12.5%. Billing is continued using the larger of the

two currents.

The AD7751 supplies average real power information on the

low-frequency outputs F1 and F2. These logic outputs may be

used to directly drive an electromechanical counter or interface

to an MCU. The CF logic output gives instantaneous real power

information. This output is intended to be used for calibration

purposes.

The AD7751 includes a power supply monitoring circuit on the

AV

supply pin. The AD7751 will remain in a reset condition

DD

until the supply voltage on AV

below 4 V, the AD7751 will also be reset and no pulses will be

issued on F1, F2, and CF.

Internal phase matching circuitry ensures that the voltage and

current channels are matched whether the HPF in Channel 1 is

on or off. The AD7751 also has anticreep protection.

The AD7751 is available in 24-lead DIP and SSOP packages.

reaches 4 V. If the supply falls

DD

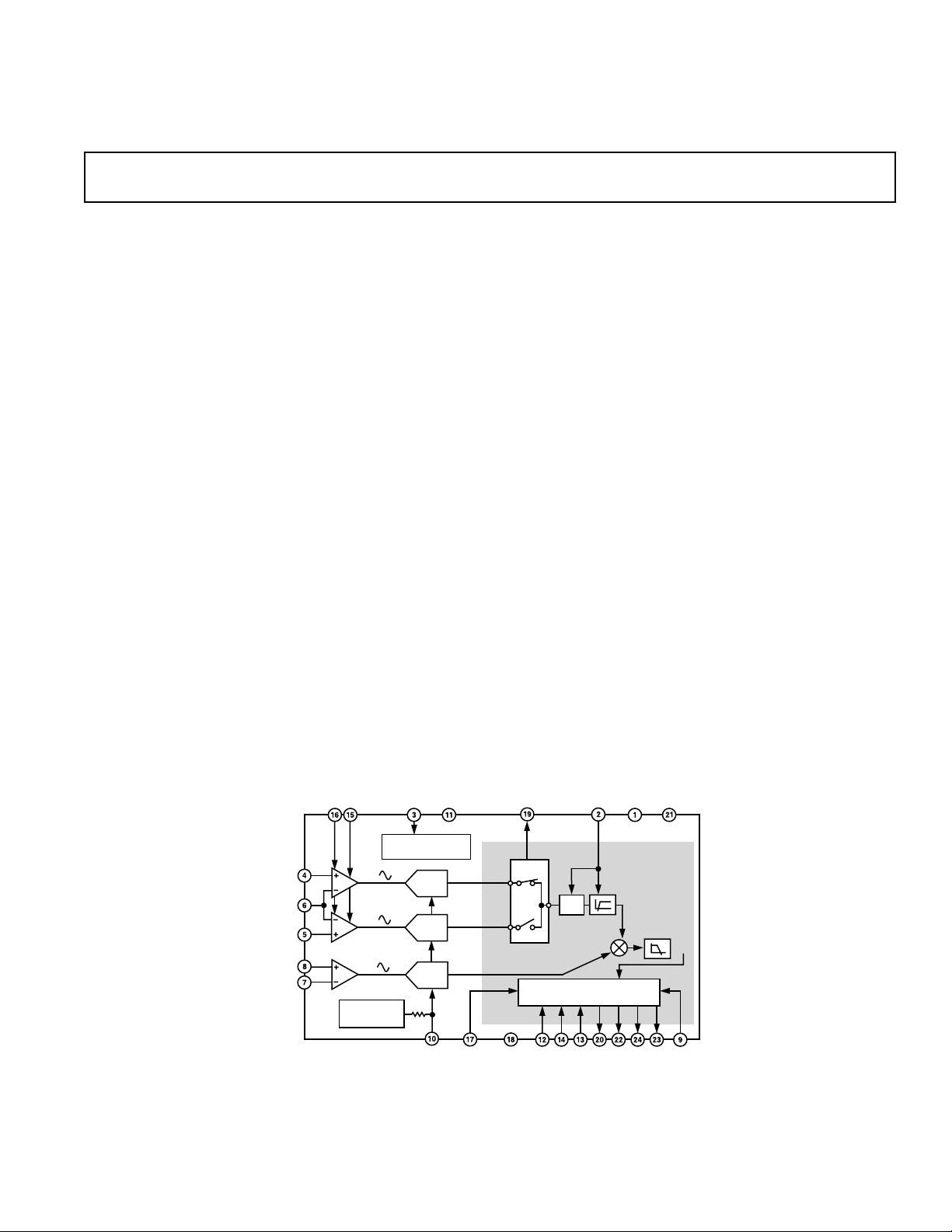

FUNCTIONAL BLOCK DIAGRAM

AV

G0 G1

V1A

V1N

V1B

V2P

V2N

*US Patent 5,745,323; 5,760,617; 5,862,069; 5,872,469.

ⴛ1, ⴛ2, ⴛ8, ⴛ16

ⴛ1, ⴛ2, ⴛ8, ⴛ16

2.5V

REFERENCE

SUPPLY MONITOR

PGA

PGA

DD

POWER

ADC

ADC

ADC

4k⍀

IN/OUT

AGND

...

110101

...

110101

...

11011001

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

AC/DC

FAULT

AD7751

A<>B

A

...

A>B

...

B

B>A

...

CLKOUTCLKINREF

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

⌽

PHASE

CORRECTION

DIGITAL-TO-FREQUENCY

CONVERTER

DV

DGND

DD

SIGNAL

PROCESSING

BLOCK

HPF

MULTIPLIER

F1

F2CFREVPSCF S0 S1

LPF

RESET

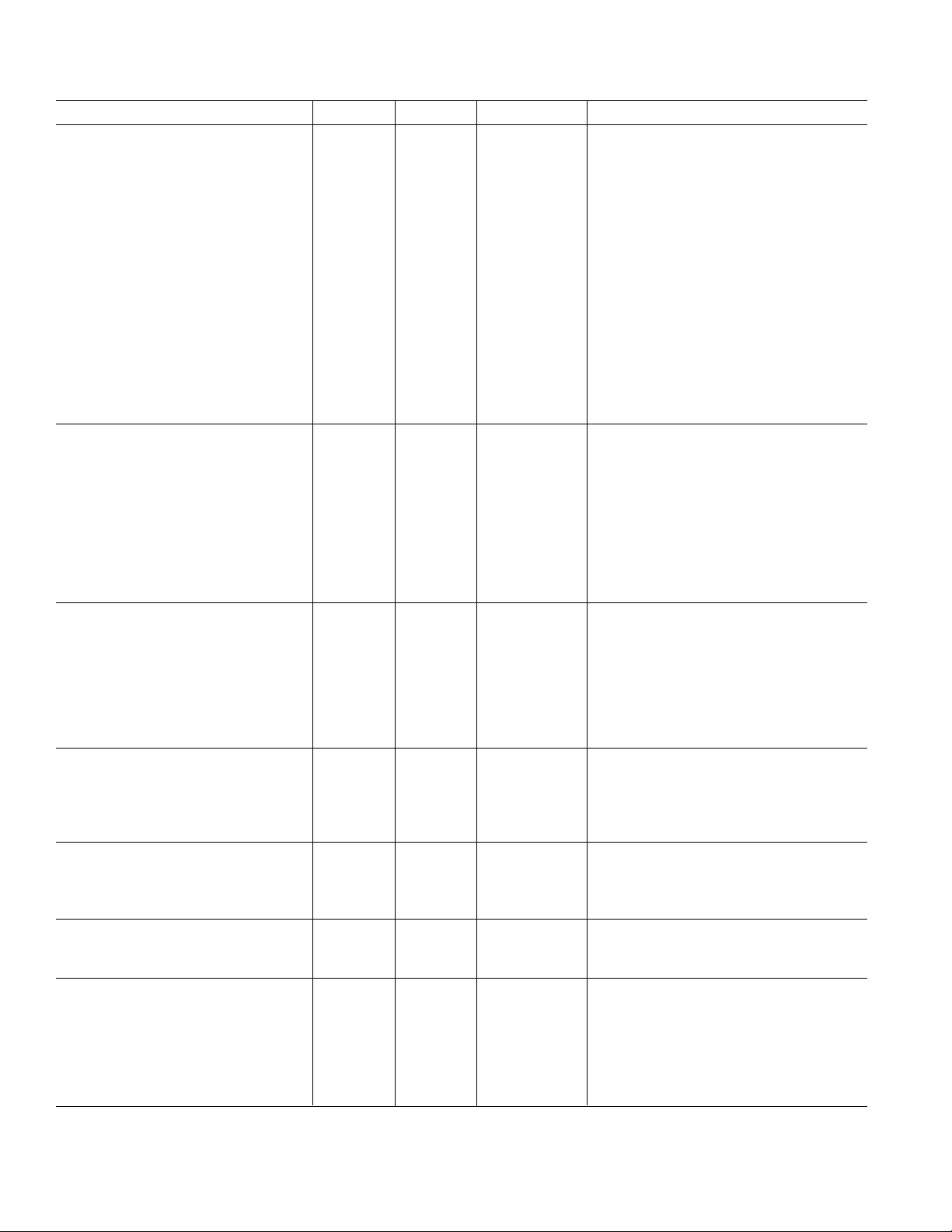

(AVDD = DVDD = 5 V ⴞ 5%, AGND = DGND = 0 V, On-Chip Reference, CLKIN =

1, 2

AD7751–SPECIFICATIONS

3.58 MHz, T

MIN

to T

= –40ⴗC to +85ⴗC)

MAX

Parameter A Version B Version Unit Test Conditions/Comments

ACCURACY

3

Measurement Error1 on Channels 1 and 2 One Channel with Full-Scale Signal (±660 mV)

Gain = 1 0.1 0.1 % Reading typ Over a Dynamic Range 500 to 1

Gain = 2 0.1 0.1 % Reading typ Over a Dynamic Range 500 to 1

Gain = 8 0.1 0.1 % Reading typ Over a Dynamic Range 500 to 1

Gain = 16 0.1 0.1 % Reading typ Over a Dynamic Range 500 to 1

Phase Error

1

Between Channels Line Frequency = 45 Hz to 55 Hz

V1 Phase Lead 37°

(PF = 0.8 Capacitive) ±0.1 ±0.1 Degrees(°) max AC/DC = 0 and AC/DC = 1

V1 Phase Lag 60°

(PF = 0.5 Inductive) ±0.1 ±0.1 Degrees(°) max AC/DC = 0 and AC/DC = 1

AC Power Supply Rejection

1

AC/DC = 1, S0 = S1 = 1, G0 = G1 = 0

Output Frequency Variation (CF) 0.2 0.2 % Reading typ V1 = 100 mV rms, V2 = 100 mV rms @ 50 Hz

of 200 mV rms @ 100 Hz

DD

DC Power Supply Rejection

1

Ripple on AV

AC/DC = 1, S0 = S1 = 1, G0 = G1 = 0

Output Frequency Variation (CF) ±0.3 ±0.3 % Reading typ V1 = 100 mV rms, V2 = 100 mV rms,

AVDD = DVDD = 5 V ± 250 mV

FAULT DETECTION

1, 4

See Fault Detection Section

Fault Detection Threshold

Inactive i/p <> Active i/p 12.5 12.5 % typ (V1A or V1B Active)

Input Swap Threshold

Inactive i/p > Active i/p 14 14 % of Active typ (V1A or V1B Active)

Accuracy Fault Mode Operation

V1A Active, V1B = AGND 0.1 0.1 % Reading typ Over a Dynamic Range 500 to 1

V1B Active, V1A = AGND 0.1 0.1 % Reading typ Over a Dynamic Range 500 to 1

Fault Detection Delay 3 3 Second typ

Swap Delay 3 3 Second typ

ANALOG INPUTS See Analog Inputs Section

Maximum Signal Levels ±1 ±1 V max V1A, V1B, V1N, V2N and V2P to AGND

Input Impedance (DC) 390 390 kΩ min CLKIN = 3.58 MHz

Bandwidth 14 14 kHz typ CLKIN/256, CLKIN = 3.58 MHz

ADC Offset Error

Gain Error

Gain Error Match

1

1

1

±20 ±20 mV max See Terminology and Performance Graphs

±4 ±4 % Ideal typ External 2.5 V Reference, Gain = 1,

V1 = V2 = 660 mV dc

±0.2 ±0.2 % Ideal typ External 2.5 V Reference

REFERENCE INPUT

REF

Input Voltage Range 2.7 2.7 V max 2.5 V + 8%

IN/OUT

2.3 2.3 V min 2.5 V – 8%

Input Impedance 3.2 3.2 kΩ min

Input Capacitance 10 10 pF max

ON-CHIP REFERENCE Nominal 2.5 V

Reference Error ±200 ±200 mV max

Temperature Coefficient ±30 ±30 ppm/°C typ

±60 ppm/°C max

CLKIN Note All Specifications for CLKIN of 3.58 MHz

Input Clock Frequency 4 4 MHz max

1 1 MHz min

LOGIC INPUTS

5

SCF, S0, S1, AC/DC,

RESET, G0 and G1

Input High Voltage, V

Input Low Voltage, V

Input Current, I

INL

IN

Input Capacitance, C

INH

IN

2.4 2.4 V min DVDD = 5 V ± 5%

0.8 0.8 V max DVDD = 5 V ± 5%

±3 ±3 µA max Typically 10 nA, VIN = 0 V to DV

10 10 pF max

DD

–2–

REV. A

Parameter A Version B Version Unit Test Conditions/Comments

LOGIC OUTPUTS

4

F1 and F2

Output High Voltage, V

Output Low Voltage, V

OL

OH

4.5 4.5 V min DV

0.5 0.5 V max DV

I

SOURCE

DD

I

SINK

DD

= 10 mA

= 5 V

= 10 mA

= 5 V

CF, FAULT, and REVP

I

Output High Voltage, V

Output Low Voltage, V

OL

OH

4 4 V min DV

SOURCE

DD

I

SINK

= 5 mA

= 5 V

= 5 mA

0.5 0.5 V max DVDD = 5 V

POWER SUPPLY For Specified Performance

AV

DD

4.75 4.75 V min 5 V – 5%

5.25 5.25 V max 5 V + 5%

DV

DD

4.75 4.75 V min 5 V – 5%

5.25 5.25 V max 5 V + 5%

AI

DD

DI

DD

NOTES

1

See Terminology section for explanation of specifications.

2

See plots in Typical Performance Characteristics graphs.

3

See Fault Detection section of data sheet for explanation of fault detection functionality.

4

Sample tested during initial release and after any redesign or process change that may affect this parameter.

Specifications subject to change without notice.

3 3 mA max Typically 2 mA

2.5 2.5 mA max Typically 1.5 mA

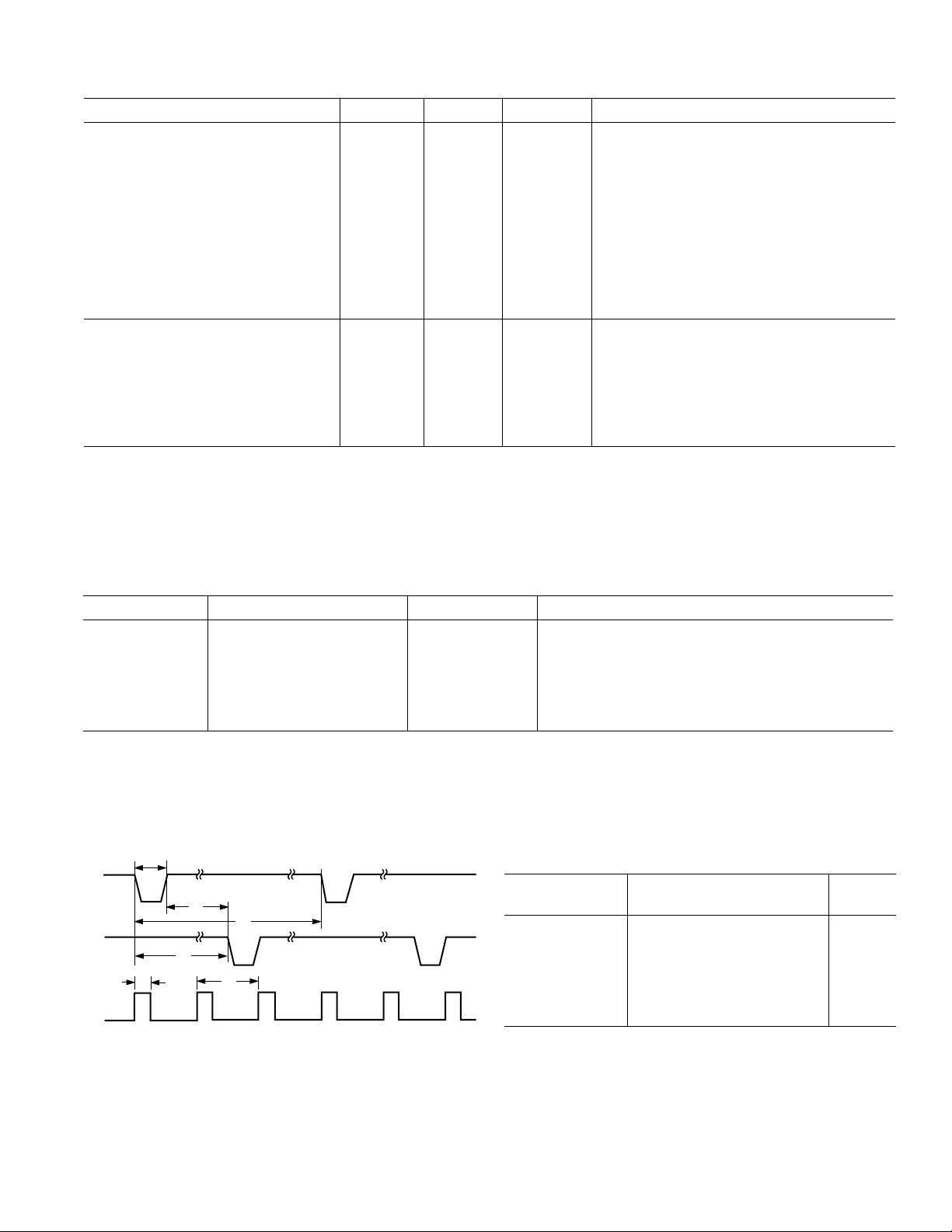

AD7751

(AVDD = DVDD = 5 V ⴞ 5%, AGND = DGND = 0 V, On-Chip Reference, CLKIN = 3.58 MHz,

TIMING CHARACTERISTICS

1, 2

T

to T

MIN

= –40ⴗC to +85ⴗC)

MAX

Parameter A, B Versions Unit Test Conditions/Comments

3

t

1

t

2

t

3

3

t

4

t

5

t

6

NOTES

1

Sample tested during initial release and after any redesign or process change that may affect this parameter.

2

See Figure 1.

3

The pulsewidths of F1, F2 and CF are not fixed for higher output frequencies. See Frequency Outputs section.

Specifications subject to change without notice.

t

1

F1

F2

t

CF

.t

6

.t

3

4

275 ms F1 and F2 Pulsewidth (Logic Low)

See Table III sec Output Pulse Period. See Transfer Function Section

1/2 t

2

sec Time Between F1 Falling Edge and F2 Falling Edge

90 ms CF Pulsewidth (Logic High)

See Table IV sec CF Pulse Period. See Transfer Function Section

CLKIN/4 sec Minimum Time Between F1 and F2 Pulse

ORDERING GUIDE

Model Package Description Option

.

t

2

AD7751AAN Plastic DIP N-24

AD7751AARS Shrink Small Outline Package RS-24

AD7751ABRS Shrink Small Outline Package RS-24

.t

5

EVAL-AD7751EB AD7751 Evaluation Board

AD7751AAN-REF AD7751 Reference Design

PCB (See AN-563)

Package

Figure 1. Timing Diagram for Frequency Outputs

REV. A

–3–

AD7751

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C unless otherwise noted)

AVDD to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DV

to DGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

DD

to AVDD . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

DV

DD

Analog Input Voltage to AGND

V1A, V1B, V1N, V2P, and V2N . . . . . . . . . . –6 V to +6 V

Reference Input Voltage to AGND . . –0.3 V to AV

Digital Input Voltage to DGND . . . . –0.3 V to DV

Digital Output Voltage to DGND . . . –0.3 V to DV

+ 0.3 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

Operating Temperature Range

Industrial (A, B Versions) . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

24-Lead Plastic DIP, Power Dissipation . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 105°C/W

θ

JA

Lead Temperature, (Soldering 10 sec) . . . . . . . . . . . 260°C

24-Lead SSOP, Power Dissipation . . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 112°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . 215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . 220°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD7751 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

TERMINOLOGY

MEASUREMENT ERROR

The error associated with the energy measurement made by the

AD7751 is defined by the following formula:

Percentage Error =

For the ac PSR measurement a reading at nominal supplies

(5 V) is taken. A 200 mV rms/100 Hz signal is then introduced

onto the supplies and a second reading obtained under the same

input signal levels. Any error introduced is expressed as a percentage of reading—see Measurement Error definition.

For the dc PSR measurement a reading at nominal supplies

Energy Registered by the AD7751 – True Energy

PHASE ERROR BETWEEN CHANNELS

True Energy

× 100%

The HPF (High-Pass Filter) in Channel 1 has a phase lead

response. To offset this phase response and equalize the phase

response between channels a phase correction network is also

placed in Channel 1. The phase correction network matches the

phase to within ±0.1° over a range of 45 Hz to 65 Hz and ±0.2°

over a range 40 Hz to 1 kHz (see Figures 10 and 11).

(5 V) is taken. The supplies are then varied ±5% and a second

reading is obtained with the same input signal levels. Any error

introduced is again expressed as a percentage of reading.

GAIN ERROR

The gain error of the AD7751 is defined as the difference between

the measured output frequency (minus the offset) and the ideal

output frequency. It is measured with a gain of 1 in Channel

V1A. The difference is expressed as a percentage of the ideal

frequency. The ideal frequency is obtained from the transfer

function—see Transfer Function section.

ADC OFFSET ERROR

This refers to the dc offset associated with the analog inputs to

the ADCs. It means that with the analog inputs connected to

AGND the ADCs still see an analog input signal of 1 mV to

10 mV. However, when the HPF is switched on the offset is

removed from the current channel and the power calculation is

not affected by this offset.

GAIN ERROR MATCH

The gain error match is defined as the gain error (minus the

offset) obtained when switching between a gain of 1 and a gain

of 2, 8, or 16. It is expressed as a percentage of the output

frequency obtained under a gain of 1. This gives the gain

error observed when the gain selection is changed from

1 to 2, 8, or 16.

POWER SUPPLY REJECTION

This quantifies the AD7751 measurement error as a percentage

of reading when the power supplies are varied.

–4–

REV. A

AD7751

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Description

1DV

DD

2 AC/DC High-Pass Filter Select. This logic input is used to enable the HPF in Channel 1 (the current

3AV

DD

4, 5 V1A, V1B Analog Inputs for Channel 1 (Current Channel). These inputs are fully differential voltage inputs

6 V1N Negative Input Pin for Differential Voltage Inputs V1A and V1B. The maximum signal level at this

7, 8 V2N, V2P Negative and Positive Inputs for Channel 2 (Voltage Channel). These inputs provide a fully differ-

9 RESET Reset Pin for the AD7751. A logic low on this pin will hold the ADCs and digital circuitry in a reset

10 REF

IN/OUT

11 AGND Provides the Ground Reference for the Analog Circuitry in the AD7751, i.e., ADCs and Reference.

12 SCF Select Calibration Frequency. This logic input is used to select the frequency on the calibration

13, 14 S1, S0 These logic inputs are used to select one of four possible frequencies for the digital-to-frequency

15, 16 G1, G0 These logic inputs are used to select one of four possible gains for the analog inputs V1A and V1B.

17 CLKIN An external clock can be provided at this logic input. Alternatively, a parallel resonant AT crystal can

18 CLKOUT A crystal can be connected across this pin and CLKIN as described above to provide a clock source

19 FAULT This logic output will go active high when a fault condition occurs. A fault is defined as a condition

Digital Power Supply. This pin provides the supply voltage for the digital circuitry in the AD7751.

The supply voltage should be maintained at 5 V ± 5% for specified operation. This pin should be

decoupled with a 10 µF capacitor in parallel with a ceramic 100 nF capacitor.

channel). A Logic 1 on this pin enables the HPF. The associated phase response of this filter has

been internally compensated over a frequency range of 45 Hz to 1 kHz. The HPF filter should be

enabled in energy metering applications.

Analog Power Supply. This pin provides the supply voltage for the analog circuitry in the AD7751.

The supply should be maintained at 5 V ± 5% for specified operation. Every effort should be made

to minimize power supply ripple and noise at this pin by the use of proper decoupling. This pin

should be decoupled to AGND with a 10 µF capacitor in parallel with a ceramic 100 nF capacitor.

with a maximum signal level of ±660 mV with respect to Pin V1N for specified operation. The

maximum signal level at these pins is ±1 V with respect to AGND. Both inputs have internal ESD

protection circuitry and an overvoltage of ±6 V can also be sustained on these inputs without risk of

permanent damage.

pin is ±1 V with respect to AGND. The input has internal ESD protection circuitry and in addition,

an overvoltage of ±6 V can be sustained without risk of permanent damage. This input should be

directly connected to the burden resistor and held at a fixed potential, i.e., AGND. See Analog

Input section.

ential input pair. The maximum differential input voltage is ±660 mV for specified operation. The

maximum signal level at these pins is ±1 V with respect to AGND. Both inputs have internal ESD

protection circuitry and an overvoltage of ±6 V can also be sustained on these inputs without risk of

permanent damage.

condition. Bringing this pin logic low will clear the AD7751 internal registers.

Provides Access to the On-Chip Voltage Reference. The on-chip reference has a nominal value of

2.5 V ± 8% and a typical temperature coefficient of 30 ppm/°C. An external reference source may also

be connected at this pin. In either case, this pin should be decoupled to AGND with a 1 µF ceramic

capacitor and 100 nF ceramic capacitor.

This pin should be tied to the analog ground plane of the PCB. The analog ground plane is the

ground reference for all analog circuitry, e.g., antialiasing filters, current and voltage transducers, etc. For good noise suppression the analog ground plane should only be connected to the digital

ground plane at one point. A star ground configuration will help to keep noisy digital return currents

away from the analog circuits.

output CF. Table IV shows how the calibration frequencies are selected.

conversion. This offers the designer greater flexibility when designing the energy meter. See Selecting a Frequency for an Energy Meter Application section.

The possible gains are 1, 2, 8 and 16. See Analog Input section.

be connected across CLKIN and CLKOUT to provide a clock source for the AD7751. The clock

frequency for specified operation is 3.579545 MHz. Crystal load capacitors of between 22 pF

and 33 pF (ceramic) should be used with the gate oscillator circuit.

for the AD7751. The CLKOUT pin can drive one CMOS load when an external clock is supplied

at CLKIN or by gate oscillator circuit.

under which the signals on V1A and V1B differ by more than 12.5%. The logic output will be reset

to zero when a fault condition is no longer detected. See Fault Detection section.

REV. A

–5–

Loading...

Loading...