Analog Devices AD7390, AD7391 Datasheet

+3 Volt Serial-Input

a

Micropower 10-Bit & 12-Bit DACs

FEATURES

Micropower—100 mA

Single-Supply—12.7 to 15.5 V Operation

Compact 1.75 mm Height SO-8 Package

& 1.1 mm Height TSSOP-8

AD7390—12-Bit Resolution

AD7391—10-Bit Resolution

SPI & QSPI Serial Interface Compatible with Schmitt

Trigger Inputs

APPLICATIONS

Automotive 0.5 V to 4.5 V Output Span Voltage

Portable Communications

Digitally Controlled Calibration

GENERAL DESCRIPTION

The AD7390/AD7391 family of 10-bit & 12-bit voltage-output

digital-to-analog converters is designed to operate from a single

13 V supply. Built using a CBCMOS process, these monolithic

DACs offer the user low cost, and ease-of-use in single-supply

13 V systems. Operation is guaranteed over the supply voltage

range of 12.7 V to 15.5 V consuming less than 100 µA making

this device ideal for battery operated applications.

The full-scale voltage output is determined by the external reference input voltage applied. The rail-to-rail REF

to DAC

IN

OUT

allows for a full-scale voltage set equal to the positive supply

or any value in between.

V

DD

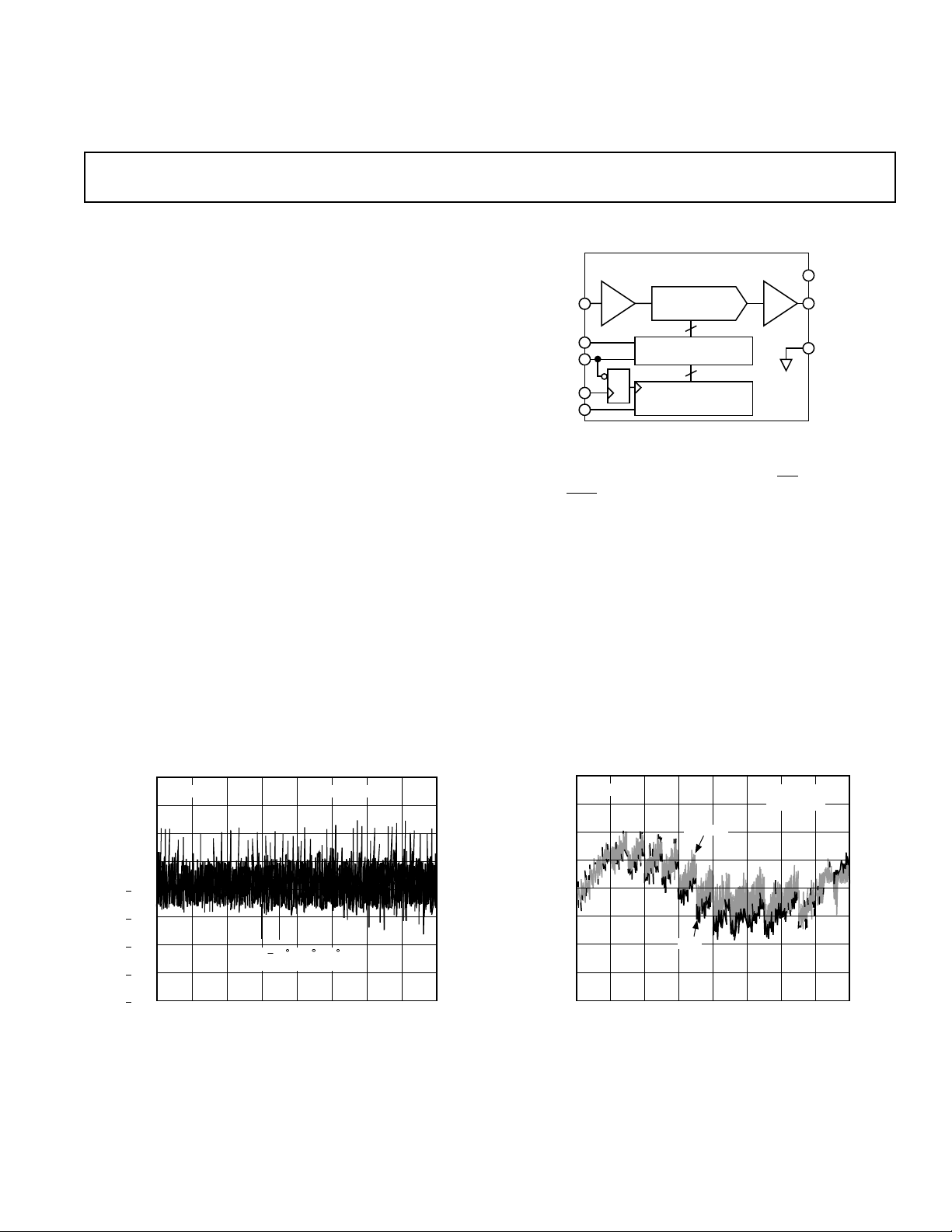

AD7390/AD7391

FUNCTIONAL DIAGRAM

AD7390

REF

CLR

LD

EN

CLK

SDI

12-BIT DAC

12

DAC REGISTER

12

SERIAL REGISTER

A doubled-buffered serial-data interface offers high speed,

three-wire, SPI and microcontroller compatible inputs using

data in (SDI), clock (CLK) and load strobe (

tionally, a

CLR input sets the output to zero scale at power on

or upon user demand.

Both parts are offered in the same pinout to allow users to select

the amount of resolution appropriate for their application without circuit card redesign.

The AD7390/AD7391 are specified over the extended industrial

(240°C to 185°C) temperature range. The AD7391AR is

specified for the 240°C to 1125°C automotive temperature

range. The AD7390/AD7391s are available in plastic DIP, and

low profile 1.75 mm height SO-8 surface mount packages. The

AD7391ARU is available for ultracompact applications in a thin

1.1 mm TSSOP-8 package.

V

DD

V

OUT

GND

LD) pins. Addi-

1.00

0.75

0.50

0.25

0.00

DNL – LSB

0.25

0.50

0.75

1.00

0 4096512

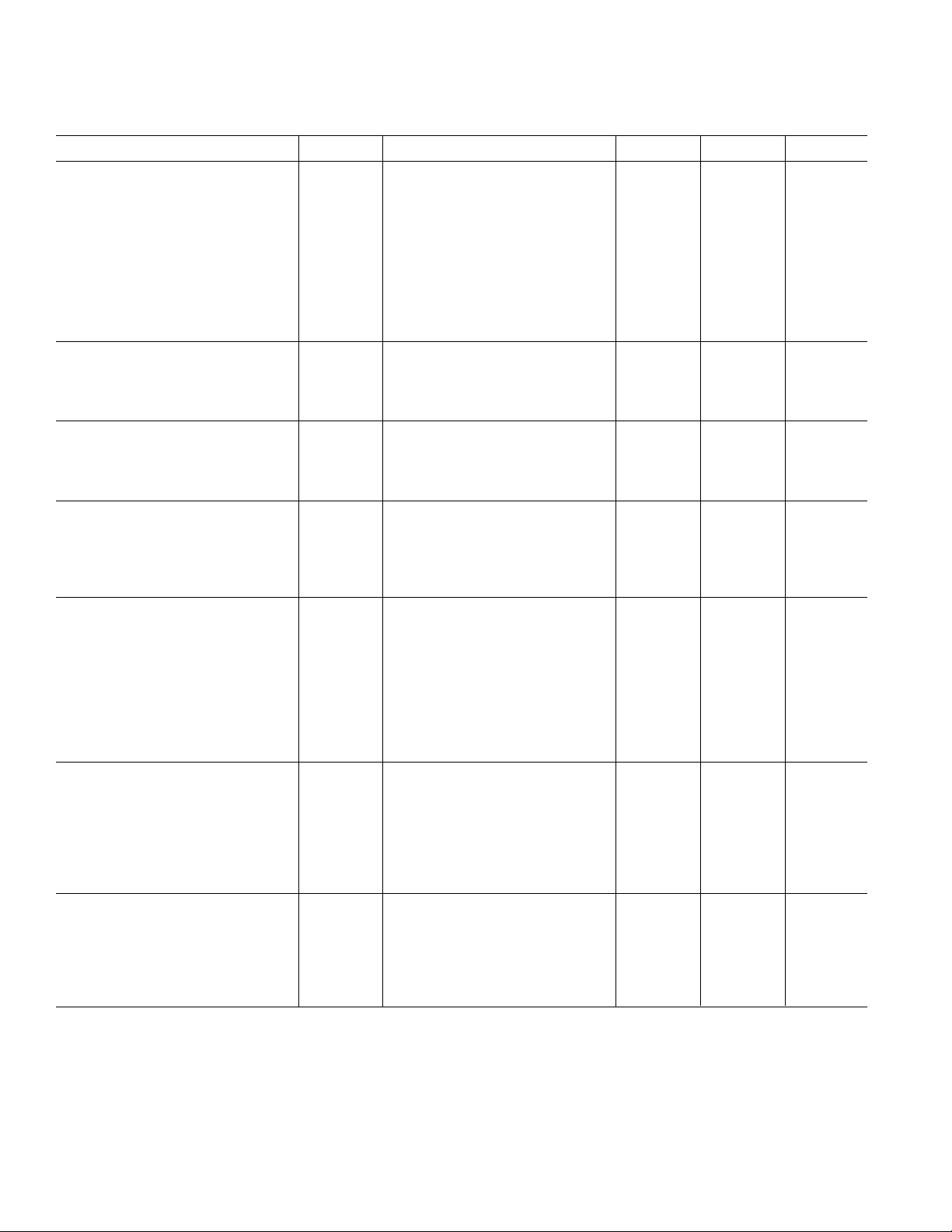

AD7390

TA = 55 C, 25 C, 85 C

SUPERIMPOSED

1024 1536 2048 2560 3072 3584

CODE – Decimal

VDD = +3.0V

Figure 1. Differential Nonlinearity Error vs. Code

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

2.0

AD7390

1.5

1.0

0.5

0.0

INL – LSB

20.5

21.0

21.5

22.0

0 4096512 1024 1536 2048 2560 3072 2584

258, 858C

2558

CODE – Decimal

VDD = +3.0V

= +2.5V

V

REF

Figure 2. INL Error vs. Code & Temperature

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD7390/AD7391–SPECIFICATIONS

AD7390 ELECTRICAL CHARACTERISTICS

(@ V

= 2.5 V, 2408C < TA < 1858C, unless otherwise noted)

REF IN

Parameter Symbol Conditions 3 V 6 10% 5 V 6 10% Units

STATIC PERFORMANCE

Resolution

Relative Accuracy

Relative Accuracy

Differential Nonlinearity

Differential Nonlinearity

Zero-Scale Error V

Full-Scale Voltage Error V

Full-Scale Voltage Error V

Full-Scale Tempco

1

2

2

2

2

3

N 12 12 Bits

INL T

INL T

DNL T

= 125°C 61.6 61.6 LSB max

A

= 240°C, 185°C 62.0 62 LSB max

A

= 125°C, Monotonic 60.9 60.9 LSB max

A

DNL Monotonic 61 61 LSB max

ZSE

FSE

FSE

TCV

FS

Data = 000

T

= 125°C, 185°C, Data = FFF

A

T

= 240°C, Data = FFF

A

H

H

4.0 4.0 mV max

68 68 mV max

H

620 620 mV max

16 16 ppm/°C typ

REFERENCE INPUT

V

Range V

REF IN

Input Resistance R

Input Capacitance

3

REF

REF

C

REF

0/V

DD

0/V

DD

V min/max

2.5 2.5 MΩ typ

5 5 pF typ

ANALOG OUTPUT

Output Current (Source) I

Output Current (Sink) I

Capacitive Load

3

OUT

OUT

C

Data = 800

Data = 800

L

No Oscillation 100 100 pF typ

H

H

, ∆V

, ∆V

= 5 LSB 1 1 mA typ

OUT

= 5 LSB 3 3 mA typ

OUT

LOGIC INPUTS

Logic Input Low Voltage V

Logic Input High Voltage V

Input Leakage Current I

Input Capacitance

INTERFACE TIMING

3

3, 5

Clock Width High t

Clock Width Low t

Load Pulse Width t

Data Setup t

Data Hold t

Clear Pulse Width t

Load Setup t

Load Hold t

AC CHARACTERISTICS

6

IL

IH

IL

C

IL

CH

CL

LDW

DS

DH

CLRW

LD1

LD2

Output Slew Rate SR Data = 000H to FFFH to 000

Settling Time t

S

DAC Glitch Q Code 7FF

To 60.1% of Full Scale 70 60 µs typ

to 800H to 7FF

H

H

H

0.5 0.8 V max

VDD20.6 VDD20.6 V min

10 10 µA max

10 10 pF max

50 30 ns min

50 30 ns min

30 20 ns min

10 10 ns min

30 15 ns min

15 15 ns min

30 15 ns min

40 20 ns min

0.05 0.05 V/µs typ

65 65 nVs typ

Digital Feedthrough Q 15 15 nVs typ

Feedthrough V

OUT/VREFVREF

= 1.5 VDC 11 V p-p

,

263 263 dB typ

Data = 000H, f = 100 kHz

4

SUPPLY CHARACTERISTICS

Power Supply Range V

Positive Supply Current I

Positive Supply Current I

Power Dissipation P

DD RANGE

DD

DD

DISS

Power Supply Sensitivity PSS ∆V

NOTES

1

One LSB = V

2

The first two codes (000H, 001H) are excluded from the linearity error measurement.

3

These parameters are guaranteed by design and not subject to production testing.

4

Typicals represent average readings measured at 25°C.

5

All input control signals are specified with

6

The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

Specifications subject to change without notice.

/4096 V for the 12-bit AD7390.

REF

t

=

t

= 2 ns (10% to 90% of 13 V) and timed from a voltage level of 1.6 V.

R

F

DNL < 61 LSB 2.7/5.5 2.7/5.5 V min/max

VIL = 0 V, No Load, T

V

= 0 V, No Load 100 100 µA max

IL

V

= 0 V, No Load 300 500 µW max

IL

= 65% 0.003 0.006 %/% max

DD

= 125°C55 55 µA typ

A

REV. 0–2–

SPECIFICATIONS

AD7390/AD7391

AD7391 ELECTRICAL CHARACTERISTICS

(@ V

= 2.5 V, 2408C < TA < 1858C, unless otherwise noted)

REF IN

Parameter Symbol Conditions 3 V 6 10% 5 V 6 10% Units

STATIC PERFORMANCE

Resolution

Relative Accuracy

Relative Accuracy

Differential Nonlinearity

Zero-Scale Error V

Full-Scale Voltage Error V

Full-Scale Voltage Error V

Full-Scale Tempco

1

2

2

2

3

N 10 10 Bits

INL T

INL T

= 125°C 61.75 61.75 LSB max

A

= 240°C, 185°C, 1125°C 62.0 62.0 LSB max

A

DNL Monotonic 60.9 60.9 LSB max

ZSE

FSE

FSE

TCV

FS

Data = 000

T

= 125°C, 185°C, 1125°C, 632 632 mV max

A

Data = 3FF

T

= 240°C, Data = 3FF

A

H

H

H

9.0 9.0 mV max

635 635 mV max

16 16 ppm/°C typ

REFERENCE INPUT

Range V

V

REF IN

Input Resistance R

Input Capacitance

3

REF

REF

C

REF

0/V

DD

0/V

DD

V min/max

2.5 2.5 MΩ typ

5 5 pF typ

ANALOG OUTPUT

Output Current (Source) I

Output Current (Sink) I

Capacitive Load

3

OUT

OUT

C

Data = 800

Data = 800

L

No Oscillation 100 100 pF typ

H

H

, ∆V

, ∆V

= 5 LSB 1 1 mA typ

OUT

= 5 LSB 3 3 mA typ

OUT

LOGIC INPUTS

Logic Input Low Voltage V

Logic Input High Voltage V

Input Leakage Current I

Input Capacitance

INTERFACE TIMING

3

3, 5

Clock Width High t

Clock Width Low t

Load Pulse Width t

Data Setup t

Data Hold t

Clear Pulse Width t

Load Setup t

Load Hold t

AC CHARACTERISTICS

6

IL

IH

IL

C

IL

CH

CL

LDW

DS

DH

CLRW

LD1

LD2

Output Slew Rate SR Data = 000H to 3FFH to 000

Settling Time t

S

DAC Glitch Q Code 7FF

To 60.1% of Full Scale 70 60 µs typ

to 800H to 7FF

H

H

H

0.5 0.8 V min

VDD20.6 VDD20.6 V max

10 10 µA max

10 10 pF max

50 30 ns

50 30 ns

30 20 ns

10 10 ns

30 15 ns

15 15 ns

30 15 ns

40 20 ns

0.05 0.05 V/µs typ

65 65 nVs typ

Digital Feedthrough Q 15 15 nVs typ

Feedthrough V

OUT/VREFVREF

= 1.5 VDC 11 V p-p, 263 263 dB typ

Data = 000H, f = 100 kHz

4

SUPPLY CHARACTERISTICS

Power Supply Range V

Positive Supply Current I

Positive Supply Current I

Power Dissipation P

DD RANGE

DD

DD

DISS

Power Supply Sensitivity PSS ∆V

NOTES

1

One LSB = V

2

The first two codes (000H, 001H) are excluded from the linearity error measurement.

3

These parameters are guaranteed by design and not subject to production testing.

4

Typicals represent average readings measured at 25°C.

5

All input control signals are specified with tR = tF = 2 ns (10% to 90% of 13 V) and timed from a voltage level of 1.6 V.

6

The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

Specifications subject to change without notice.

/1024 V for the 10-bit AD7391.

REF

DNL < 61 LSB 2.7/5.5 2.7/5.5 V min/max

VIL = 0 V, No Load, T

V

= 0 V, No Load 100 100 µA max

IL

V

= 0 V, No Load 300 500 µW max

IL

= 65% 0.003 0.006 %/% max

DD

= 125°C55 55 µA typ

A

REV. 0 –3–

AD7390/AD7391

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . 20.3 V, 18 V

to GND . . . . . . . . . . . . . . . . . . . . . . . 0.3 V, V

V

REF

1 0.3 V

DD

Logic Inputs to GND . . . . . . . . . . . . . . . . . . . . .20.3 V, 18 V

to GND . . . . . . . . . . . . . . . . . . . . . 20.3 V, V

V

OUT

Short Circuit to GND . . . . . . . . . . . . . . . . . . . . . . 50 mA

I

OUT

Package Power Dissipation . . . . . . . . . . . . . . (T

Thermal Resistance θ

JA

J MAX

1 0.3 V

DD

2 T

)/θ

A

JA

8-Pin Plastic DIP Package (N-8) . . . . . . . . . . . . . . 103°C/W

8-Lead SOIC Package (SO-8) . . . . . . . . . . . . . . . . 158°C/W

TSSOP-8 Package (RU-8) . . . . . . . . . . . . . . . . . . . 240°C/W

Maximum Junction Temperature (T

) . . . . . . . . . . 150°C

J MAX

Operating Temperature Range . . . . . . . . . . . 240°C to 1 85°C

Storage Temperature Range . . . . . . . . . . . . 265°C to 1150°C

Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . . 1300°C

NOTES

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational specification is not implied. Exposure to the above maximum rating

conditions for extended periods may affect device reliability.

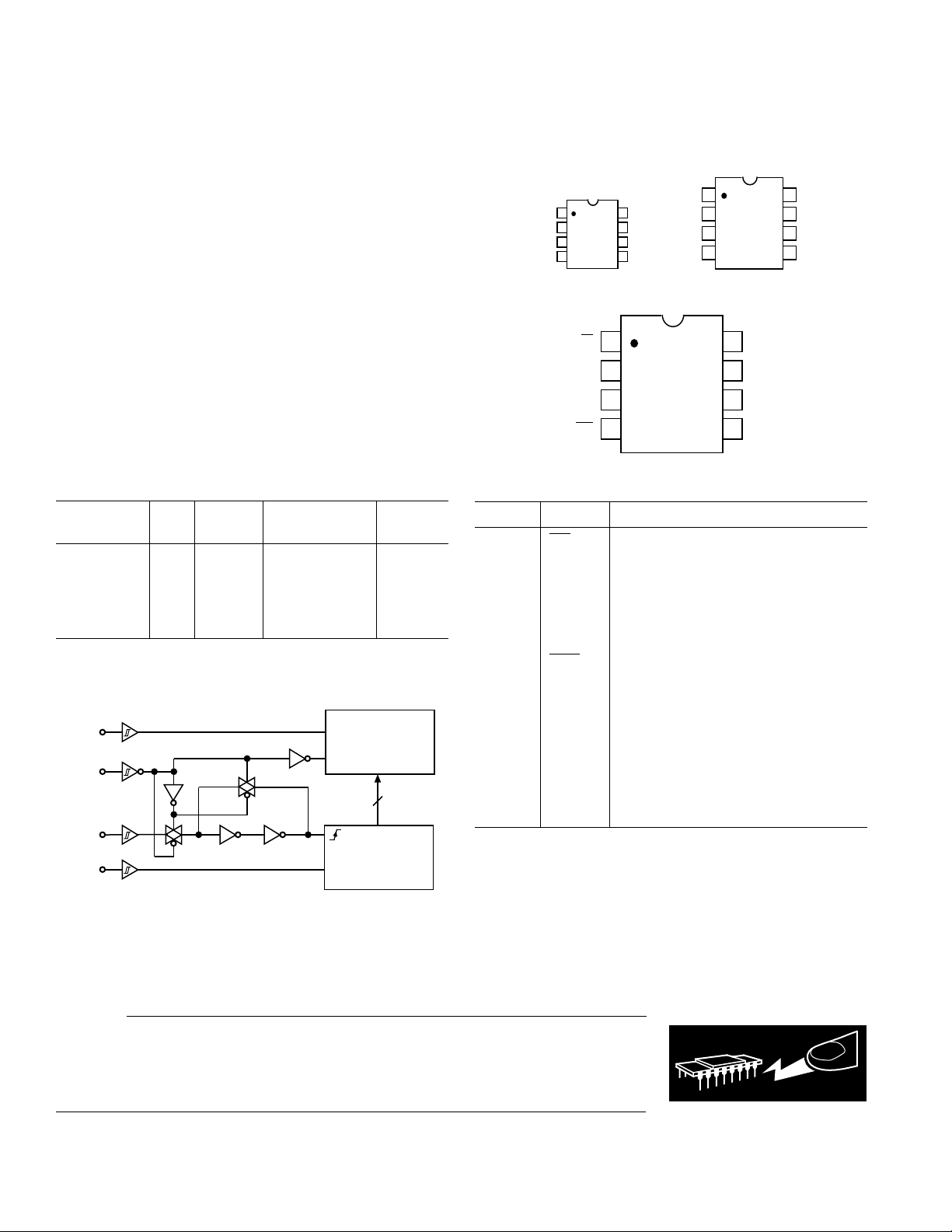

ORDERING GUIDE

Package Package

Model Res Temp Description Option

AD7390AN 12 XIND 8-Pin P-DIP N-8

AD7390AR 12 XIND 8-Lead SOIC SO-8

AD7391AN 10 XIND 8-Pin P-DIP N-8

AD7391AR 10 AUTO 8-Lead SOIC SO-8

AD7391ARU 10 XIND TSSOP-8 RU-8

NOTES

XIND = 240°C to 185°C; AUTO = 240°C to 1125°C

The AD7390 contains 558 transistors. The die size measures 70 mil X 68 mil.

CLR

LD

CLK

SDI

RESET

REGISTER

LOAD

CLK

12-BIT AD7390*

SHIFT REGISTER

D

DAC

12

PIN CONFIGURATIONS

SO-8

TSSOP-8

1

TOP

2

VIEW

3

(Not to

Scale)

4

1

8

7

6

5

2

TOP VIEW

(Not to Scale)

3

4

8

7

6

5

P-DIP-8

LD

CLK

SDI

CLR

1

2

3

4

TOP VIEW

(Not to Scale)

V

8

REF

V

7

DD

6

V

OUT

5

GND

PIN DESCRIPTIONS

Pin No. Name Function

1

LD Load Strobe. Transfers shift register

data to DAC register while active low.

See truth table for operation.

2 CLK Clock Input. Positive edge clocks data

into shift register.

3 SDI Serial Data Input. Data loads directly

into the shift register.

4

CLR Resets DAC register to zero condition.

Active low input.

5 GND Analog & Digital Ground.

6V

OUT

DAC Voltage Output. Full-scale output

1 LSB less than reference input voltage

REF.

7V

DD

Positive Power Supply Input. Specified

range of operation 12.7 V to 15.5 V.

8V

REF

DAC Reference Input Pin. Establishes

DAC full-scale voltage.

* NOTE: AD7391 HAS A 10-BIT SHIFT REGISTER

Figure 3. Digital Control Logic

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7390/AD7391 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. 0–4–

Loading...

Loading...