120 mA, Current Sinking,

V

FEATURES

Current sink: 120 mA

Available in 3 × 3 array WLCSP package

2-wire, (I

10-bit resolution

Integrated current sense resistor

Power supply range: 2.7 V to 5.5 V

Guaranteed monotonic over all codes

Power down to 0.5 μA typical

Internal reference

Ultralow noise preamplifier

Power-down function

Power-on reset

APPLICATIONS

Consumer

2

C-compatible) 1.8 V serial interface

Lens autofocus

Image stabilization

Optical zoom

Shutters

Iris/exposure

Neutral density (ND) filters

Lens covers

Camera phones

Digital still cameras

Camera modules

Digital video cameras/camcorders

Camera-enabled devices

Security cameras

Web/PC cameras

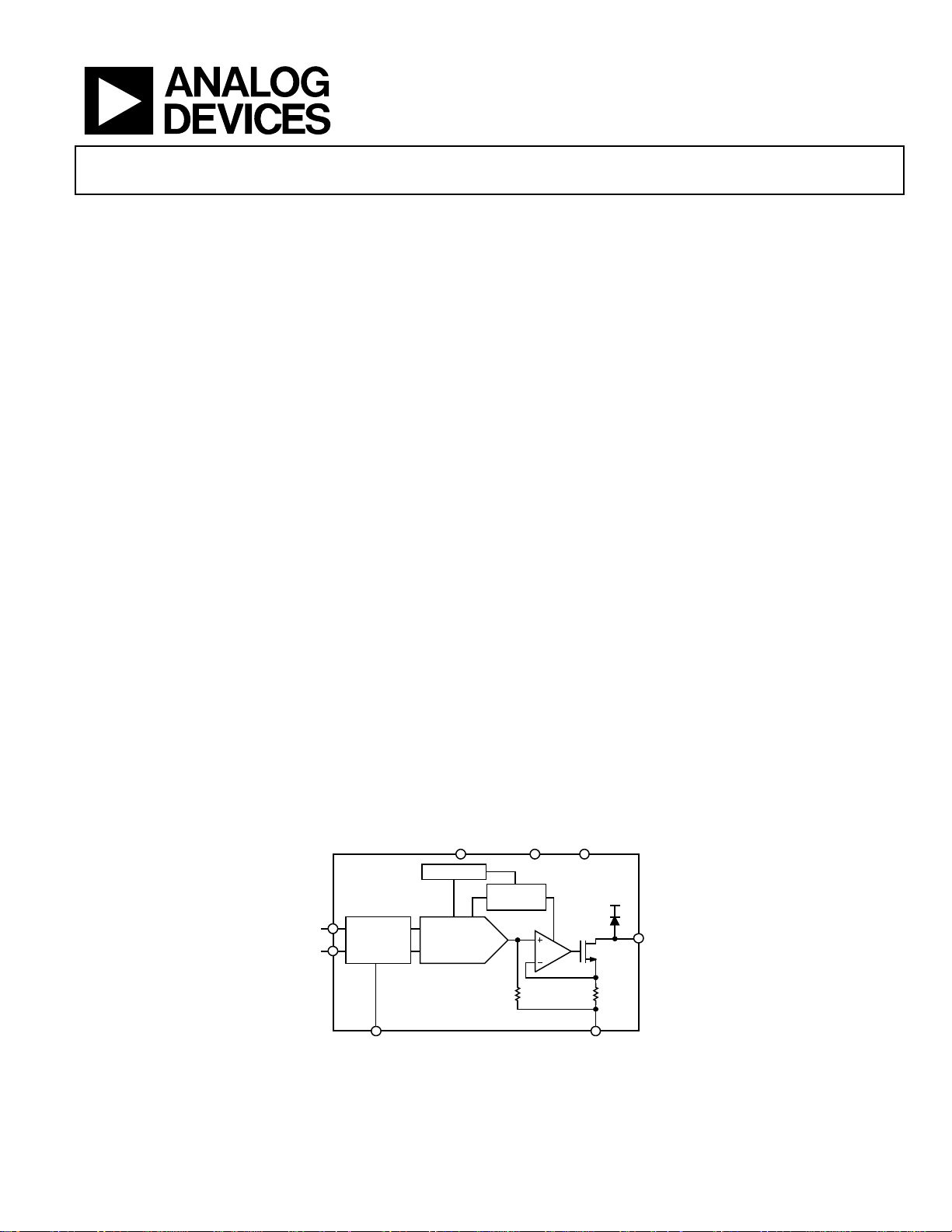

FUNCTIONAL BLOCK DIAGRAM

XSHUTDOWN

10-Bit, I2C DAC

AD5821A

Industrial

Heater controls

Fan controls

Cooler (Peltier) controls

Solenoid controls

Valve controls

Linear actuator controls

Light controls

Current loop controls

GENERAL DESCRIPTION

The AD5821A is a single, 10-bit digital-to-analog converter

(DAC) with output current sinking capability of 120 mA. It

features an internal reference and operates from a single 2.7 V

to 5.5 V supply. The DAC is controlled via a 2-wire, I

compatible serial interface that operates at clock rates up to

400 kHz.

The AD5821A incorporates a power-on reset circuit that

ensures the DAC output powers up to 0 V and remains there until

a valid write takes place. It has a power-down feature that reduces

the current consumption of the device to 1 µA maximum.

The AD5821A is designed for autofocus, image stabilization,

and optical zoom applications in camera phones, digital still

cameras, and camcorders.

The AD5821A is also suitable for many industrial applications,

such as controlling temperature, light, and movement without

derating over temperatures ranging from −30°C to +85°C.

2

The I

C 7-bit address for the AD5821A is 0xC.

DGND

DD

2

C®-

REFERENCE

POWER-ON

RESET

SDA

SCL

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

I2C SERIAL

INTERFACE

DGND

10-BIT

CURRENT

OUTPUT DAC

AD5821A

R

Figure 1.

R

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

SENSE

3.3Ω

D1

AGND

V

DD

I

SINK

07796-001

AD5821A

TABLE OF CONTENTS

Features .............................................................................................. 1

Consumer Applications ................................................................... 1

Industrial Applications .................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

AC Specifications .......................................................................... 4

Timing Specifications .................................................................. 4

Absolute Maximum Ratings ............................................................ 5

Pin Configuration and Function Descriptions ............................. 6

REVISION HISTORY

10/08—Revision 0: Initial Version

Typical Performance Characteristics ..............................................7

Terminology .................................................................................... 10

Theory of Operation ...................................................................... 11

Serial Interface ............................................................................ 11

I2C Bus Operation ...................................................................... 11

Data Format ................................................................................ 11

Power Supply Bypassing and Grounding ................................ 12

Applications Information .............................................................. 14

Outline Dimensions ....................................................................... 15

Ordering Guide .......................................................................... 15

Rev. 0 | Page 2 of 16

AD5821A

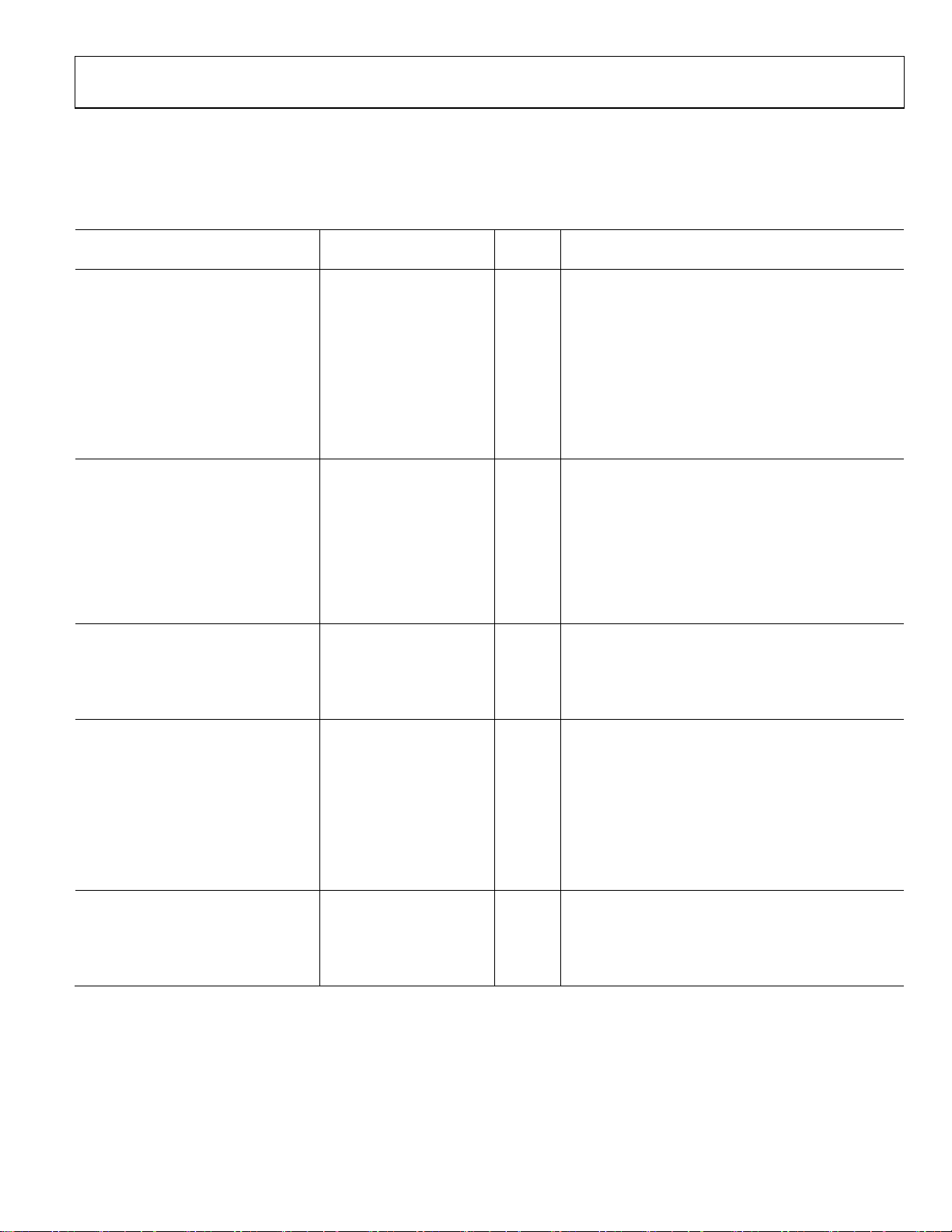

SPECIFICATIONS

VDD = 2.7 V to 5.5 V, AGND = DGND = 0 V, load resistance (RL) = 25 Ω connected to VDD. All specifications T

otherwise noted.

MIN

to T

MAX

, unless

Table 1.

B Version

1

Parameter Min Typ Max Unit Test Conditions/Comments

DC PERFORMANCE

= 3.6 V to 4.5 V; device operates over 2.7 V to 5.5 V

V

DD

with reduced performance

Resolution 10 Bits 117 μA/LSB

Relative Accuracy

Differential Nonlinearity

Zero-Code Error

Offset Error @ Code 16

Gain Error

Offset Error Drift

Gain Error Drift

2

2, 3

2, 4

2

±0.6 % of FSR at 25°C

4, 5

2, 5

±0.2 ±0.5 LSB/°C

±1 LSB Guaranteed monotonic over all codes

0 0.5 1 mA All 0s loaded to DAC

2

0.5 mA

10 μA/°C

±1.5 ±4 LSB

OUTPUT CHARACTERISTICS

Minimum Sink Current

4

3 mA

Maximum Sink Current 120 mA

Output Current During XSHUTDOWN

Output Compliance

5

0.6 V

5

80 nA XSHUTDOWN = 0

V

DD

Output voltage range over which maximum 120 mA

sink current is available

Output Compliance

5

0.48 V

V

DD

Output voltage range over which 90 mA sink current

is available

Power-Up Time

LOGIC INPUTS (XSHUTDOWN)

5

20 μs To 10% of FS, coming out of power-down mode; V

5

DD

= 5 V

Input Current ±1 μA

Input Low Voltage, V

Input High Voltage, V

0.54 V VDD = 2.7 V to 5.5 V

INL

1.26 V VDD = 2.7 V to 5.5 V

INH

Pin Capacitance 3 pF

LOGIC INPUTS (SCL, SDA)

Input Low Voltage, V

Input High Voltage, V

Input Low Voltage, V

Input High Voltage, V

5

−0.3 +0.54 V VDD = 2.7 V to 3.6 V

INL

1.26 VDD + 0.3 V VDD = 2.7 V to 3.6 V

INH

−0.3 +0.54 V VDD = 3.6 V to 5.5 V

INL

1.4 VDD + 0.3 V VDD = 3.6 V to 5.5 V

INH

Input Leakage Current, IIN ±1 μA VIN = 0 V to VDD

Input Hysteresis, V

0.05 VDD V

HYST

Digital Input Capacitance, CIN 6 pF

Glitch Rejection

6

50 ns Pulse width of spike suppressed

POWER REQUIREMENTS

VDD 2.7 5.5 V

IDD (Normal Mode) 0.5 1 mA IDD specification is valid for all DAC codes;

V

IDD (Power-Down Mode)

1

Temperature range for the B version is −30°C to +85°C.

2

See the Terminology section.

3

Linearity is tested using a reduced code range: Code 32 to Code 1023.

4

To achieve near zero output current, use the power-down feature.

5

Guaranteed by design and characterization; not production tested. XSHUTDOWN is active low. SDA and SCL pull-up resistors are tied to 1.8 V.

6

Input filtering on both the SCL and the SDA inputs suppress noise spikes that are less than 50 ns.

7

XSHUTDOWN is active low.

7

0.5 μA V

= 1.8 V, V

INH

= 1.8 V, V

INH

= GND, VDD = 2.7 V to 3.6 V

INL

= GND, VDD = 3 V

INL

Rev. 0 | Page 3 of 16

AD5821A

S

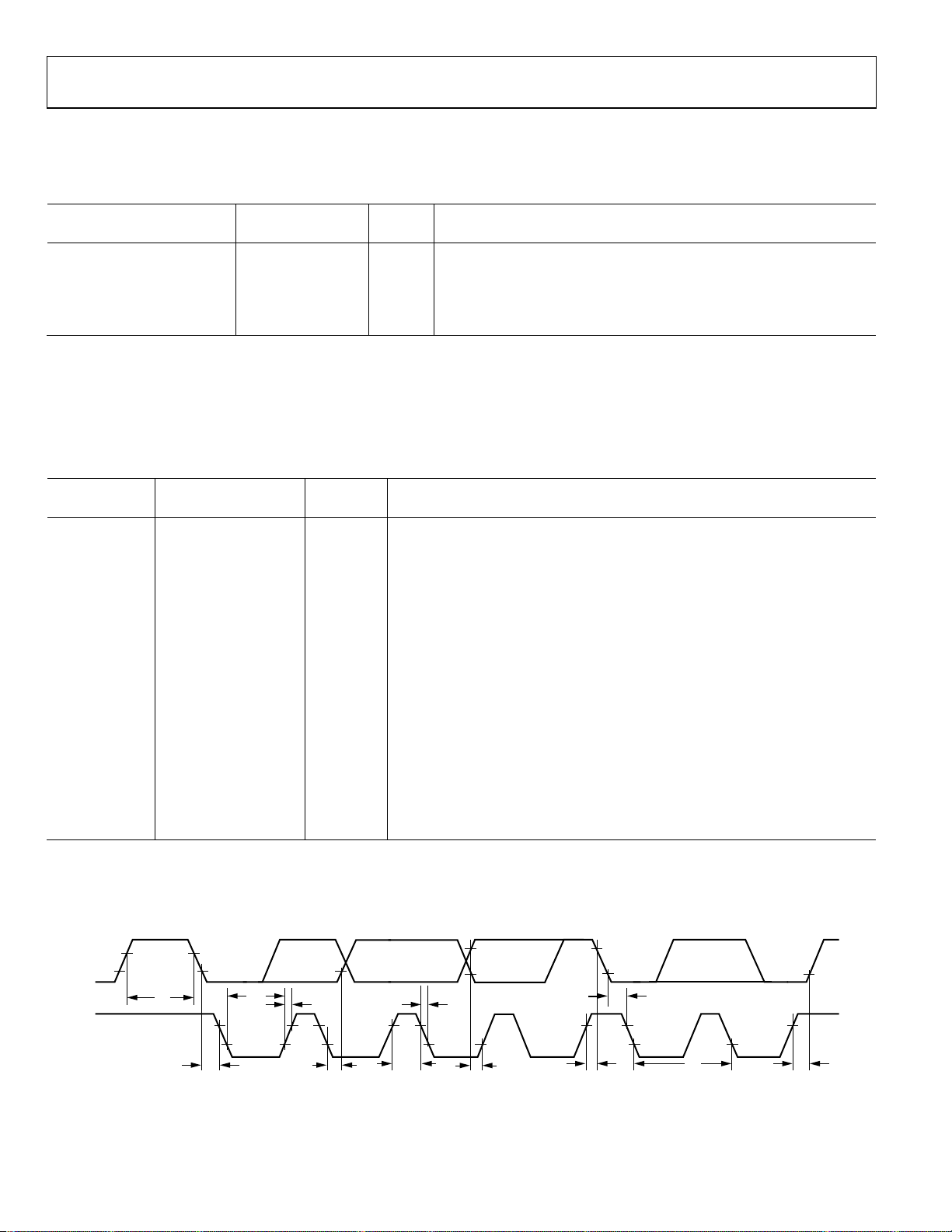

AC SPECIFICATIONS

VDD = 2.7 V to 5.5 V, AGND = DGND = 0 V, RL = 25 Ω connected to VDD, unless otherwise noted.

Table 2.

1, 2

B Version

Parameter Min Typ Max Unit Test Conditions/Comments

Output Current Settling Time 250 μs VDD = 3.6 V, RL = 25 Ω, LL = 680 μH, ¼ scale to ¾ scale change (0x100 to 0x300)

Slew Rate 0.3 mA/μs

Major Code Change Glitch

0.15 nA-sec 1 LSB change around major carry

Impulse

Digital Feedthrough

1

Temperature range for the B version is −40°C to +85°C.

2

Guaranteed by design and characterization; not production tested.

3

See the Terminology section.

3

0.06 nA-sec

TIMING SPECIFICATIONS

VDD = 2.7 V to 3.6 V. All specifications T

Table 3.

B Version

Parameter

f

400 kHz max SCL clock frequency

SCL

1

Limit at T

MIN

, T

MAX

t1 2.5 μs min SCL cycle time

t2 0.6 μs min t

t3 1.3 μs min t

t4 0.6 μs min t

t5 100 ns min t

2

t

6

0.9 μs max t

0 μs min

t7 0.6 μs min t

t8 0.6 μs min t

t9 1.3 μs min t

t10 300 ns max tR, rise time of both SCL and SDA when receiving

0 ns min Can be CMOS driven

t11 250 ns max tF, fall time of SDA when receiving

300 ns max tF, fall time of both SCL and SDA when transmitting

20 + 0.1 C

CB 400 pF max Capacitive load for each bus line

1

Guaranteed by design and characterization; not production tested.

2

A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the VINH MIN of the SCL signal) to bridge the undefined region of the SCL falling edge.

3

C

is the total capacitance of one bus line in pF. t

B

3

B

Timing Diagram

MIN

to T

, unless otherwise noted.

MAX

Unit Description

, SCL high time

HIGH

, SCL low time

LOW

, start/repeated start condition hold time

HD, STA

, data setup time

SU, DAT

, data hold time

HD, DAT

, setup time for repeated start

SU, STA

, stop condition setup time

SU, STO

, bus free time between a stop condition and a start condition

BUF

ns min

and tF are measured between 0.3 VDD and 0.7 VDD.

R

DA

SCL

t

9

t

4

START

CONDITIO N

t

3

t

10

t

6

t

t

11

2

t

5

REPEATED

CONDITION

t

7

START

t

4

t

1

t

8

STOP

CONDITIO N

07796-002

Figure 2. 2-Wire Serial Interface Timing Diagram

Rev. 0 | Page 4 of 16

AD5821A

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 4.

Parameter Rating

VDD to AGND −0.3 V to +5.5 V

VDD to DGND −0.3 V to VDD + 0.3 V

AGND to DGND −0.3 V to +0.3 V

SCL, SDA to DGND −0.3 V to VDD + 0.3 V

XSHUTDOWN to DGND −0.3 V to VDD + 0.3 V

I

to AGND −0.3 V to VDD + 0.3 V

SINK

Operating Temperature Range

Industrial (B Version) −30°C to +85°C

Storage Temperature Range −65°C to +150°C

Junction Temperature (TJ

WLCSP Power Dissipation (TJ

θJA Thermal Impedance

) 150°C

MAX

1

− TA)/θJA

MAX

Mounted on 4-Layer Board 95°C/W

Lead Temperature, Soldering

Maximum Peak Reflow Temperature2260°C (±5°C)

1

To achieve the optimum θJA, it is recommended that the AD5821A be

soldered on a 4-layer board.

2

As per JEDEC J-STD-020C.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 16

Loading...

Loading...