ANALOG DEVICES AD1836 Service Manual

PRELIMINARY TECHNICAL DATA

a

Multichannel 96 kHz Codec

Preliminary Technical Data AD1836

FEATURES

5 V Multichannel Audio System

Accepts 16-/18-/20-/24-Bit Data

Supports 24 Bits and 96 kHz Sample Rate

Multibit Sigma-Delta Modulators with Data Directed

Scrambling

Data-Directed Scrambling ADCs and DACs—Least

Sensitive to Jitter

Differential Output for Optimum Performance

ADCs: –92 dB THD + N, 105 dB SNR and Dynamic Range

DACs: –95 dB THD + N, 108 dB SNR and Dynamic Range

On-Chip Volume Control with “Autoramp” Function

Programmable Gain Amplifier for ADC Input

Hardware and Software Controllable Clickless Mute

Digital De-Emphasis Processing

Supports 256 f

, 512 fS, or 768 fS Master Clock

S

Power-Down Mode Plus Soft Power-Down Mode

Flexible Serial Data Port with Right-Justified, Left-

Justified, I

2

S-Compatible and DSP Serial Port Modes

TDM Interface Mode Supports 8 In/8 Out Using a

Single SHARC® SPORT

52-Lead MQFP (PQFP) Plastic Package

APPLICATIONS

Home Theatre Systems

Automotive Audio Systems

DVD

Set-Top Boxes

Digital Audio Effects Processors

GENERAL DESCRIPTION

The AD1836 is a high-performance, single-chip codec providing three stereo DACs and two stereo ADCs using ADI’s

patented multibit sigma-delta architecture. An SPI port is

included, allowing a microcontroller to adjust volume and

many other parameters. The AD1836 operates from a 5 V

supply, with provision for a separate output supply to interface

with low-voltage external circuitry. The AD1836 is available

in a 52-lead MQFP (PQFP) package.

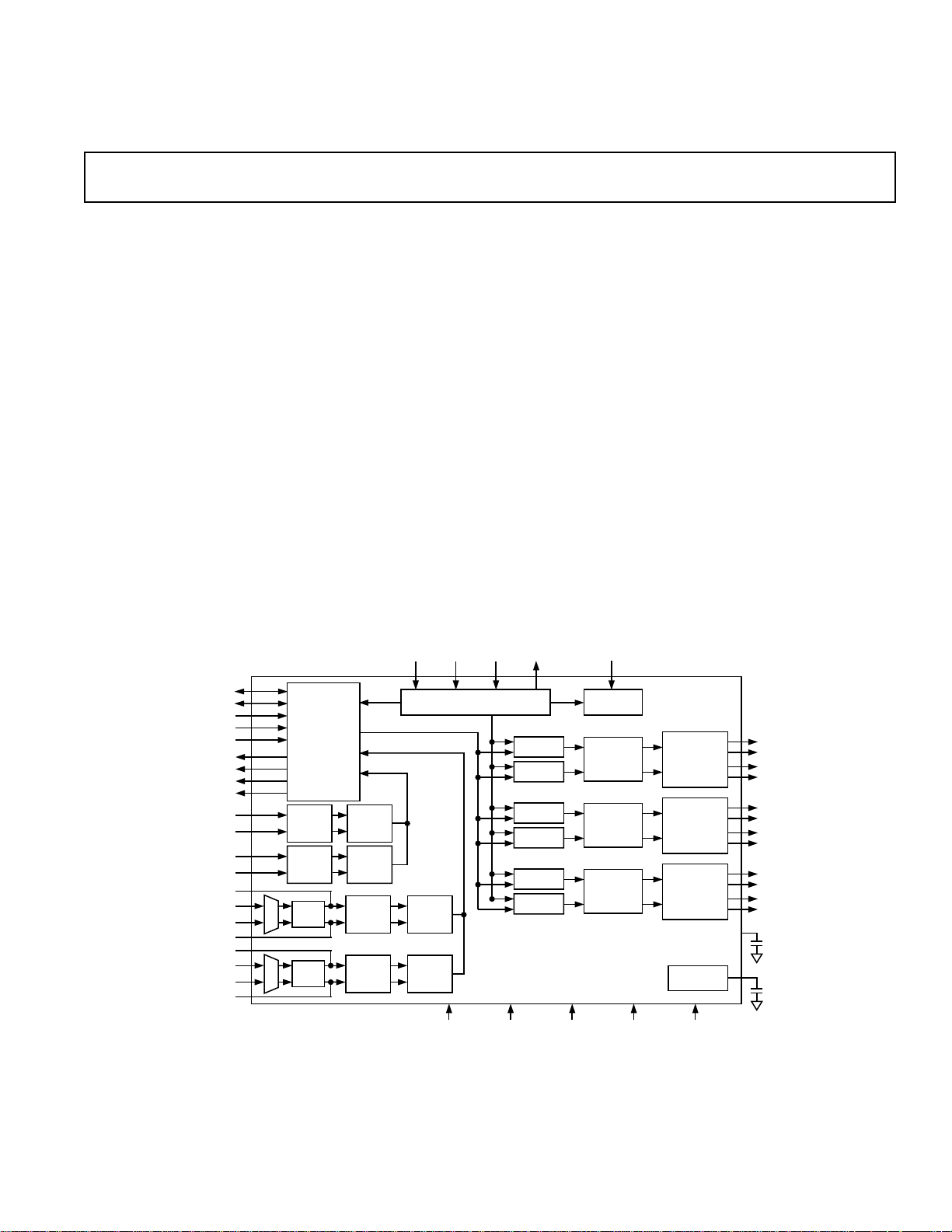

DLRCLK

DBCLK

DSDATA1

DSDATA2

DSDATA3

ALRCLK

ABCLK

ASDATA1

ASDATA2

AIN1L

AIN1R

CAPL1

AIN2L1

AIN2L2

CAPL2

CAPR1

AIN2R1

AIN2R2

CAPR2

MUX

MUX

SERIAL

DATA

PORT

ADC1L

48/96kHz

ADC1R

48/96kHz

PGA

PGA

I/O

FUNCTIONAL BLOCK DIAGRAM

DIGITAL

FILTER

48/96kHz

DIGITAL

FILTER

48/96kHz

ADC2L

48kHz

ADC2R

48kHz

CCLK CDATA CLATCH

CONTROL PORT

DIGITAL

FILTER

48kHz

DIGITAL

FILTER

48kHz

PWRDWN/RESET AVDD AGND DVDD DGND

COUT

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

2432

MCLK

CLOCK

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DAC

DAC

DAC

V

REF

A

OUT

A

OUT

A

OUT

A

OUT

A

OUT

A

OUT

FILTD

FILTR

1

2

3

4

5

6

SHARC is a registered trademark of Analog Device, Inc.

REV.PrC

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

PRELIMINARY TECHNICAL DATA

AD1836–SPECIFICATIONS

TEST CONDITIONS UNLESS OTHERWISE NOTED

Supply Voltages (AVDD, DVDD) 5.0 V

Ambient Temperature 25°C

Master Clock 12.288 MHz, (48 kHz f

Input Signal 1.000 kHz, 0 dBFS (Full Scale)

Input Sample Rate 48 kHz

Measurement Bandwidth 20 Hz to 20 kHz

Word Width 20 Bits

Load Capacitance 100 pF

Load Impedance 47 kΩ

Input Voltage HI 2.4 V

Input Voltage LO 0.8 V

NOTE

Performance of all channels are identical (exclusive of the Interchannel Gain Mismatch and Interchannel Phase Deviation specifications).

ANALOG PERFORMANCE

ANALOG-TO-DIGITAL CONVERTERS

ADC Resolution (all ADCs) 24 Bits

Dynamic Range (20 Hz to 20 kHz, –60 dB Input)

No Filter 102 dB

With A-Weighted Filter 105 dB

Total Harmonic Distortion + Noise –92 dB

Interchannel Isolation 100 dB

Interchannel Gain Mismatch 0.01 dB

Programmable Input Gain 12 dB

Gain Step Size 3 dB

Offset Error LSB

Full-Scale Input Voltage At Each Pin (Single-Ended) 1.0 (2.8) V rms (V p-p)

Gain Drift 100 ppm/°C

Input Resistance 10 kΩ

Input Capacitance 15 pF

Common-Mode Input Volts 2.25 V

DIGITAL-TO-ANALOG CONVERTERS

Dynamic Range (20 Hz to 20 kHz, –60 dB Input)

No Filter 105 dB

With A-Weighted Filter 108 dB

Total Harmonic Distortion + Noise –95 dB

Interchannel Isolation 100 dB

Interchannel Gain Mismatch 0.01(0.12) dB (%)

DC Accuracy %

Gain Error ± 3.0 %

Interchannel Gain Mismatch 0.01 dB

Gain Drift 150 ppm/°C

Interchannel Crosstalk (EIAJ Method) –120 dB

Interchannel Phase Deviation ± 0.1 Degrees

Volume Control Step Size (1023 Linear Steps) 0.098 %

Volume Control Range (Max Attenuation) 60 dB

Mute Attenuation –100 dB

De-Emphasis Gain Error ± 0.1 dB

Full-Scale Output Voltage At Each Pin (Single-Ended) 1.0 (2.8) V rms (V p-p)

Output Resistance At Each Pin 115 Ω

Common-Mode Output 2.25 V

, 256 × fS Mode)

S

Min Typ Max Unit

–2–

REV. PrC

PRELIMINARY TECHNICAL DATA

DIGITAL FILTERS at 44.1 kHz

Min Typ Max Unit

ADC DECIMATION FILTER

Pass Band 20 kHz

Pass Band Ripple ± 0.0001 dB

Transition Band 22 kHz

Stop Band 24 kHz

Stop Band Attenuation 120 dB

Group Delay TBD µs

DAC INTERPOLATION FILTER

Pass Band 20 kHz

Pass Band Ripple ± 0.01 dB

Transition Band 22 kHz

Stop Band 24 kHz

Stop Band Attenuation 70 dB

Group Delay TBD µs

TIMING

Parameter Min Max Unit Comments

MASTER CLOCK AND RESET

t

MH

t

ML

t

MCLK

f

MCLK

t

PDR

SPI PORT

t

CCH

t

CCL

t

CCP

t

CDS

t

CDH

t

CLS

t

CLH

t

CODE

t

COD

t

COH

t

COTS

DAC SERIAL PORT

Normal Modes

t

DBH

t

DBL

t

DBP

f

DB

t

DLS

t

DLH

t

DDS

t

DDH

Packed 128, 256 Modes

t

DBH

t

DBL

t

DBP

f

DB

t

DLS

t

DLH

t

DDS

t

DDH

MCLK High min max ns 256 × f

512 × f

768 × f

S

S

S

MCLK Low min max ns

MCLK Period min max ns

MCLK Freq min max ns

PD/RST Low 4500 MCLK Periods Reset to SPI Register Write

CCLK High min ns

CCLK Low min ns

CCLK Period min ns

CDATA Setup min ns To CCLK Rising

CDATA Hold min ns From CCLK Rising

CLATCH Setup min ns To CCLK Rising

CLATCH Hold min ns From CCLK Falling

COUT Enable max ns From CCLK Falling

COUT Delay max ns From CCLK Falling

COUT Hold min ns From CCLK Falling

COUT Three-State max ns From CCLK Falling

DBCLK High min ns

DBCLK Low min ns

DBCLK Period min ns

DBCLK Freq max ns

DLRCLK Setup min ns To DBCLK Rising

DLRCLK Hold min ns From DBCLK Rising

DSDATA Setup min ns To DBCLK Rising

DSDATA Hold min ns From DBCLK Rising

DBCLK High min ns

DBCLK Low min ns

DBCLK Period min ns

DBCLK Freq max ns

DLRCLK Setup min ns To DBCLK Rising

DLRCLK Hold min ns From DBCLK Rising

DSDATA Setup min ns To DBCLK Rising

DSDATA Hold min ns From DBCLK Rising

AD1836

REV. PrC–3–

PRELIMINARY TECHNICAL DATA

AD1836–SPECIFICATIONS

TIMING (continued)

Parameter Min Max Unit Comments

ADC Serial Port

Normal Modes

t

ABH

t

ABL

t

ALS

t

ABDD

t

ALRDD

Packed 128, 256 Modes

t

ABH

t

ABL

t

ALS

t

ABDD

t

ALRDD

TDM PACKED AUX, MASTER MODE

t

ABH

t

ABL

t

XBH

t

XBL

t

ALS

t

XLS

t

ABDD

t

ALRDD

t

DDS

t

DDH

t

DDS

t

DDH

t

DXDD

t

DXDD

ABCLK Delay High max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

ABCLK Delay Low max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

LRCLK Delay max ns From ABCLK Falling

ASDATA Delay max ns From ABCLK Falling

ASDATA Delay max ns From ALRCLK Changing

(Left-Justified)

ABCLK Delay High max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

ABCLK Delay Low max ns From MCLK Rising

256× f

S

512 × f

S

768 × f

S

LRCLK Delay max ns From ABCLK Falling

ASDATA Delay max ns From ABCLK Falling

ASDATA Delay max ns From ALRCLK Changing

(Left-Justified)

ABCLK Delay High max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

ABCLK Delay Low max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

AUXBCLK Delay High max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

AUXBCLK Delay Low max ns From MCLK Rising

256 × f

S

512 × f

S

768 × f

S

LRCLK Delay max ns From ABCLK Falling

AUXLRCLK Delay max ns From ABCLK Falling

ASDATA Delay max ns From ABCLK Falling

ASDATA Delay max ns From ALRCLK Changing

(Left-Justified)

AAUXDATA Setup min ns To AUXBCLK Rising

AAUXDATA Hold min ns From AUXBCLK Rising

DSDATA Setup min ns To DBCLK Rising

DSDATA Hold min ns From DBCLK Rising

DAUXDATA Delay max ns From AUXBCLK Falling

DAUXDATA Delay max ns From AUXLRCLK Changing

(Left-Justified)

–4–

REV. PrC

PRELIMINARY TECHNICAL DATA

TIMING (continued)

Parameter Min Max Unit Comments

TDM, PACKED AUX, SLAVE MODE

t

ABH

t

ABL

t

ABP

f

AB

t

ALS

t

ALH

t

ABDD

t

ALRDD

t

AXDS

t

AXDH

t

DDS

t

DDH

t

DXDD

t

DXDD

POWER SUPPLIES

Parameter Min Typ Max Unit

Supplies

Voltage, Analog and Digital 4.5 5 5.5 V

Analog Current 108 mA

Analog Current, Power-Down 47 mA

Digital Current 78 mA

Digital Current, Power-Down 1.5 mA

Dissipation

Operation, Both Supplies 930 mW

Operation, Analog Supply 540 mW

Operation, Digital Supply 390 mW

Power-Down, Both Supplies 243 mW

Power Supply Rejection Ratio

1 kHz 300 mV p-p Signal at Analog Supply Pins –60 dB

20 kHz 300 mV p-p Signal at Analog Supply Pins –50 dB

ABCLK High min ns

ABCLK Low min ns

ABCLK Period min ns

ABCLK Freq max ns

LRCLK Setup min ns To ABCLK Rising

LRCLK Hold min ns To ABCLK Rising

ASDATA Delay max ns From ABCLK Falling

ASDATA Delay max ns From ALRCLK Changing

(Left-Justified)

AAUXDATA Setup min ns To AUXBCLK Rising

AAUXDATA Hold min ns From AUXBCLK Rising

DSDATA Setup min ns To DBCLK Rising

DSDATA Hold min ns From DBCLK Rising

DAUXDATA Delay max ns From AUXBCLK Falling

DAUXDATA Delay max ns From AUXLRCLK Changing

(Left-Justified)

AD1836

TEMPERATURE RANGE

Parameter Min Typ Max Unit

Specifications Guaranteed 25 °C

Functionality Guaranteed –40 +85 °C

Storage –65 +150 °C

Specifications subject to change without notice.

REV. PrC–5–

AD1836

WARNING!

ESD SENSITIVE DEVICE

PRELIMINARY TECHNICAL DATA

ABSOLUTE MAXIMUM RATINGS*

Parameter Min Max Unit

Power Supplies

Analog (AVDD) –0.3 6.0 V

Digital (DVDD) –0.3 6.0 V

Input Current ± 20 mA

(Except Supply Pins)

Analog Input Voltage –0.3 AVDD + 0.3 V

(Signal Pins)

Digital Input Voltage –0.3 DVDD + 0.3 V

(Signal Pins)

Ambient Temperature –40 +85 °C

(Operating)

ESD Tolerance 1 kV

(Human Body Model, Method 3015.2, MIL-STD-883B)

*Stresses greater than those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

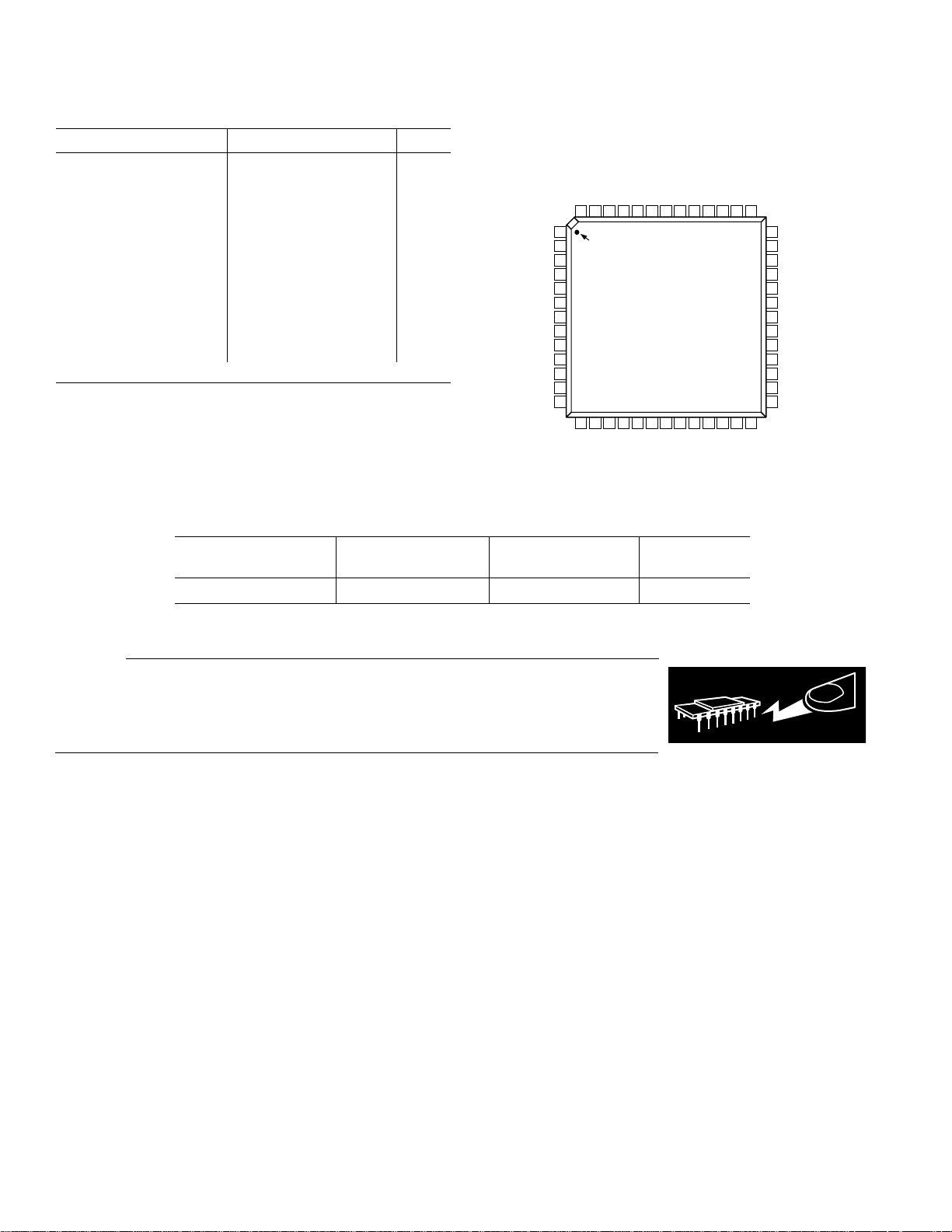

ORDERING INFORMATION

Model Temperature Package Package

Range Description Option

AD1836AS –40 to +85°C 52-Lead MQFP S-52

DVDD

CDATA

PD/RST

OUTLP3

OUTLN3

OUTLP2

OUTLN2

OUTLP1

OUTLN1

AVDD

AGND

FILTD

FILTR

PIN CONFIGURATION

52-Lead MQFP

DGND

CCLK

CLATCH

COUT

ASDATA2

ASDATA1

ODVDD

MCLK

CAPL2

CAPL1

ADC1INRN

ALRCLK

ADC2INL1

52 51 50 49 48 43 42 41 4047 46 45 44

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

AVDD

AGND

AD1836

TOP VIEW

(Not to Scale)

ADC1INLP

ADC1INLN

ADC1INRP

ABCLK

DSDATA3

DSDATA2

ADC2INL2

ADC2INR2

ADC2INR1

DVDD

39

38

37

36

35

34

33

32

31

30

29

28

27

CAPR1

DGND

DSDATA1

DBCLK

DLRCLK

OUTRP3

OUTRN3

OUTRP2

OUTRN2

OUTRP1

OUTRN1

AGND

AGND

CAPR2

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD1836 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–6–

REV. PrC

Loading...

Loading...