Page 1

AMD SR5650 Databook

Technical Reference Manual

Rev 2.10

© 2011 Advanced Micro Devices, Inc.

P/N: 47062_sr5650_ds_pub

Page 2

Trademarks

AMD, the AMD Arrow logo, AMD PowerNow!, AMD Virtualization, AMD-V, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Microsoft, Windows, and Windows Server are registered trademarks of Microsoft Corporation.

PCI Express and PCIe are registered trademarks of PCI-SIG.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with

respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time

without notice. AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to this document including, but not limited to, the implied

warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right. AMD shall not be liable for any damage, loss, expense,

or claim of loss of any kind or character (including without limitation direct, indirect, consequential, exemplary, punitive, special, incidental or reliance damages) arising

from use of or reliance on this document. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this

publication. Except for AMD product purchased pursuant to AMD's Standard Terms and Conditions of Sale, and then only as express ly set forth therein, AMD's products

are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to

support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or

environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

© 2011 Advanced Micro Devices, Inc. All rights reserved.

Page 3

Table of Contents

Chapter 1: Overview

1.1 Introducing the SR5650 ......................................................................................................................................................1-1

1.2 SR5650 Features .................................................................................................................................................................1-1

1.2.1 CPU Interface .......................................................................................................................................................1-1

1.2.2 PCI Express® Interface ........................................................................................................................................1-1

1.2.3 A-Link Express II Interface..................................................................................................................................1-1

1.2.4 Multiple Processor Support ..................................................................................................................................1-2

1.2.5 Multiple Northbridge Support ..............................................................................................................................1-2

1.2.6 Power Management Features ...............................................................................................................................1-2

1.2.7 PC Design Guide Compliance..............................................................................................................................1-2

1.2.8 Test Capability Features .......................................................................................................................................1-2

1.2.9 Packaging .............................................................................................................................................................1-2

1.3 Software Features................................................................................................................................................................1-2

1.4 Device ID ............................................................................................................................................................................1-3

1.5 Branding Diagrams .............................................................................................................................................................1-3

1.6 Conventions and Notations .................................................................................................................................................1-4

1.6.1 Pin Names.............................................................................................................................................................1-4

1.6.2 Pin Types ..............................................................................................................................................................1-4

1.6.3 Numeric Representation .......................................................................................................................................1-4

1.6.4 Hyperlinks ............................................................................................................................................................1-5

1.6.5 Acronyms and Abbreviations ...............................................................................................................................1-5

Chapter 2: Functional Descriptions

2.1 HyperTransport™ Interface ................................................................................................................................................2-1

2.1.1 Overview ..............................................................................................................................................................2-1

2.1.2 HyperTransport™ Flow Control Buffers .............................................................................................................2-3

2.2 IOMMU ..............................................................................................................................................................................2-4

2.3 Multiple Northbridge Support.............................................................................................................................................2-4

2.4 Interrupt Handling...............................................................................................................................................................2-4

2.4.1 Legacy INTx Handling.........................................................................................................................................2-4

2.4.2 Non-SB IOAPIC Support .....................................................................................................................................2-4

2.4.3 Integrated IOAPIC Support..................................................................................................................................2-5

2.4.4 MSI Interrupt Handling and MSI to HT Interrupt Conversion ............................................................................2-5

2.4.5 Internally Generated Interrupts.............................................................................................................................2-5

2.4.6 IOMMU Interrupt Remapping .............................................................................................................................2-5

2.4.7 Interrupt Routing Architecture .............................................................................................................................2-5

2.5 RAS Features ......................................................................................................................................................................2-7

2.5.1 Parity Protection ...................................................................................................................................................2-7

2.5.2 SERR_FATAL# and NON_FATAL_CORR# Pins .............................................................................................2-7

2.5.3 NMI# and SYNCFLOODIN# ..............................................................................................................................2-8

2.5.4 Suggested Platform Level RAS Sideband Signal Connections............................................................................2-8

2.5.5 Error Reporting and Logging ...............................................................................................................................2-9

2.5.6 Interrupt Generation on Errors ........................................................................................................................... 2-11

2.5.7 Poisoned Data Support ....................................................................................................................................... 2-11

2.5.8 PCIe® Link Disable State ..................................................................................................................................2-11

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary Table of Contents-1

Page 4

2.5.9 HT Syncflood Based on PCIe® Error ............................................................................................................... 2-12

2.6 PCI Express® .................................................................................................................................................................. 2-12

2.6.1 PCIe® Ports ....................................................................................................................................................... 2-12

2.6.2 PCIe® Reset Signals.......................................................................................................................................... 2-12

2.7 External Clock Chip ......................................................................................................................................................... 2-12

Chapter 3: Pin Descriptions and Strap Options

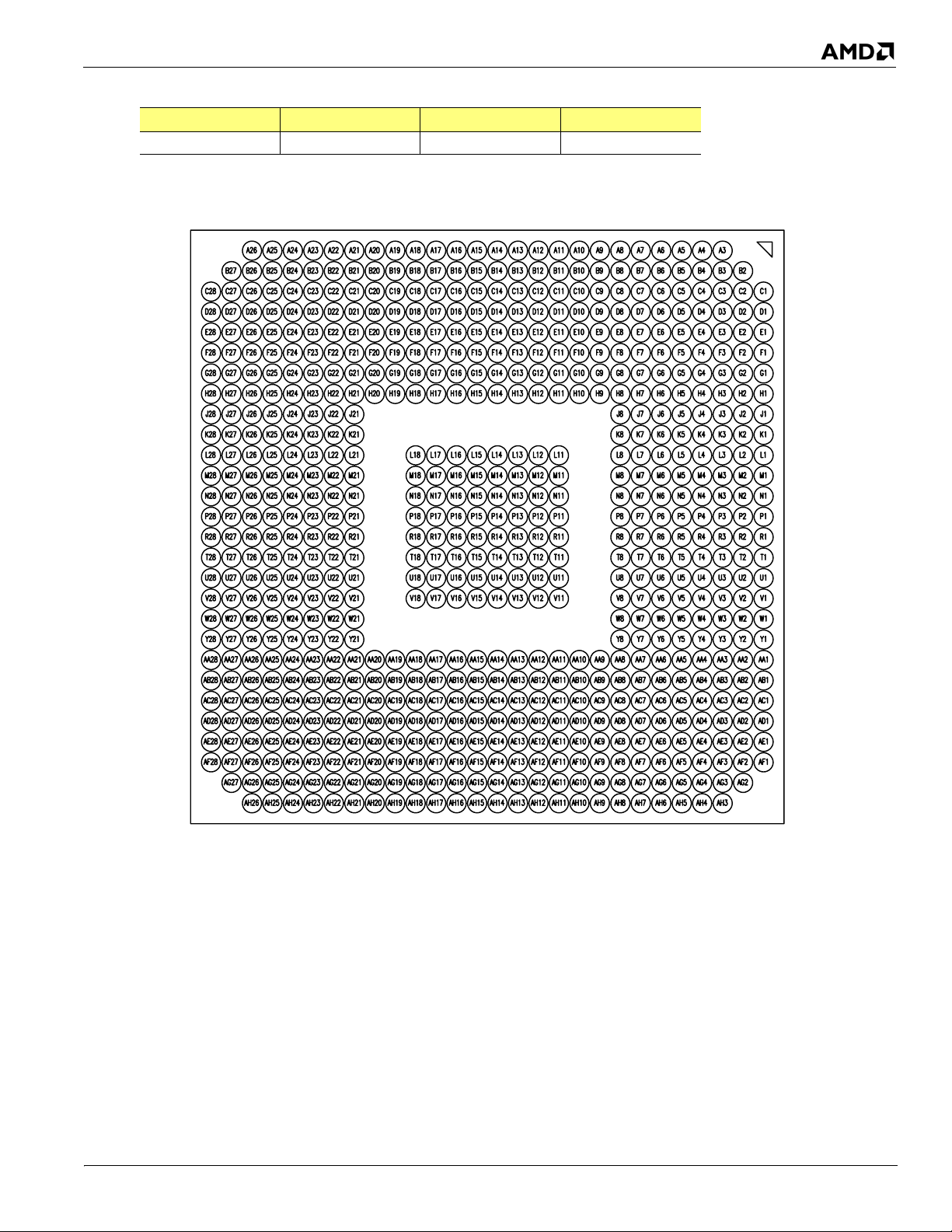

3.1 Pin Assignment Top View ................................................................................................................................................. 3-2

3.2 SR5650 Interface Block Diagram ...................................................................................................................................... 3-4

3.3 CPU HyperTransport™ Interface ...................................................................................................................................... 3-4

3.4 PCI Express® Interfaces .................................................................................................................................................... 3-5

3.4.1 PCI Express® Interface for General Purpose External Devices ......................................................................... 3-5

3.4.2 A-Link Express II Interface to Southbridge ........................................................................................................ 3-5

3.4.3 Miscellaneous PCI Express® Signals ................................................................................................................. 3-6

3.5 Clock Interface ................................................................................................................................................................... 3-6

3.6 Power Management Pins.................................................................................................................................................... 3-6

3.7 Miscellaneous Pins ............................................................................................................................................................. 3-7

3.8 Power Pins.......................................................................................................................................................................... 3-7

3.9 Ground Pins........................................................................................................................................................................ 3-9

3.10 Strapping Options........................................................................................................................................................... 3-10

Chapter 4: Timing Specifications

4.1 HyperTransport™ Bus Timing .......................................................................................................................................... 4-1

4.2 PCI Express® Differential Clock AC Specifications......................................................................................................... 4-1

4.3 HyperTransport™ Reference Clock Timing Parameters ................................................................................................... 4-1

4.4 OSCIN Reference Clock Timing Parameters..................................................................................................................... 4-2

4.5 Power Rail Sequence.......................................................................................................................................................... 4-2

4.5.1 Power Up ............................................................................................................................................................. 4-3

4.5.2 Power Down ........................................................................................................................................................ 4-4

Chapter 5: Electrical Characteristics and Physical Data

5.1 Electrical Characteristics.................................................................................................................................................... 5-1

5.1.1 Maximum and Minimum Ratings........................................................................................................................ 5-1

5.1.2 DC Characteristics............................................................................................................................................... 5-1

5.2 SR5650 Thermal Characteristics........................................................................................................................................ 5-2

5.2.1 SR5650 Thermal Limits ...................................................................................................................................... 5-2

5.2.2 Thermal Diode Characteristics ............................................................................................................................ 5-3

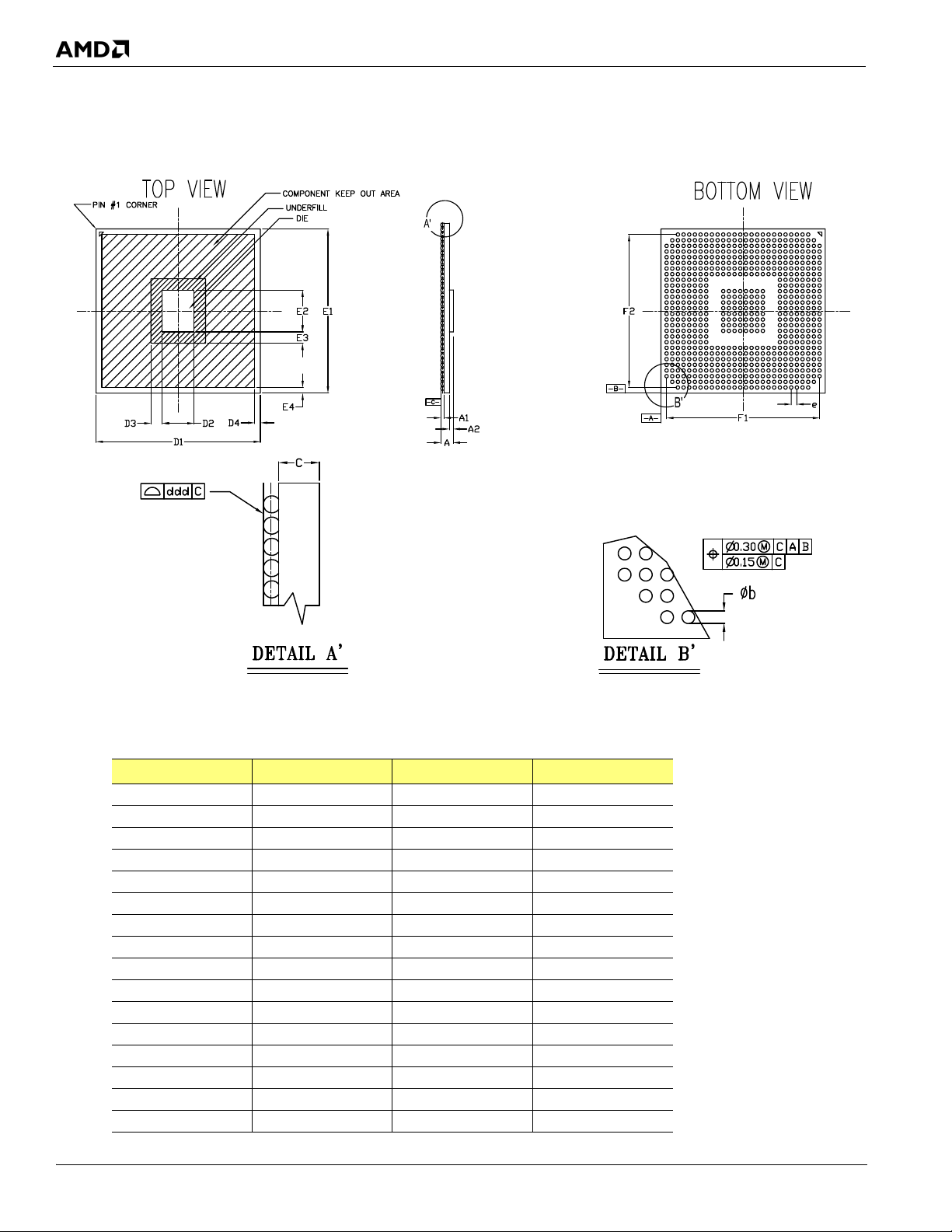

5.3 Package Information .......................................................................................................................................................... 5-4

5.3.1 Pressure Specification.......................................................................................................................................... 5-5

5.3.2 Board Solder Reflow Process Recommendations ............................................................................................... 5-6

Chapter 6: Power Management and ACPI

6.1 ACPI Power Management Implementation ....................................................................................................................... 6-1

Chapter 7: Testability

7.1 Test Capability Features..................................................................................................................................................... 7-1

7.2 Test Interface...................................................................................................................................................................... 7-1

7.3 XOR Tree ........................................................................................................................................................................... 7-1

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

Table of Contents-2 Proprietary

Page 5

7.3.1 Brief Description of an XOR Tree .......................................................................................................................7-1

7.3.2 Description of the XOR Tree for the SR5650 ......................................................................................................7-2

7.3.3 XOR Tree Activation ...........................................................................................................................................7-2

7.3.4 XOR Tree for the SR5650....................................................................................................................................7-3

7.4 VOH/VOL Test...................................................................................................................................................................7-4

7.4.1 Brief Description of a VOH/VOL Tree................................................................................................................7-4

7.4.2 VOH/VOL Tree Activation..................................................................................................................................7-5

7.4.3 VOH/VOL pin list ................................................................................................................................................7-6

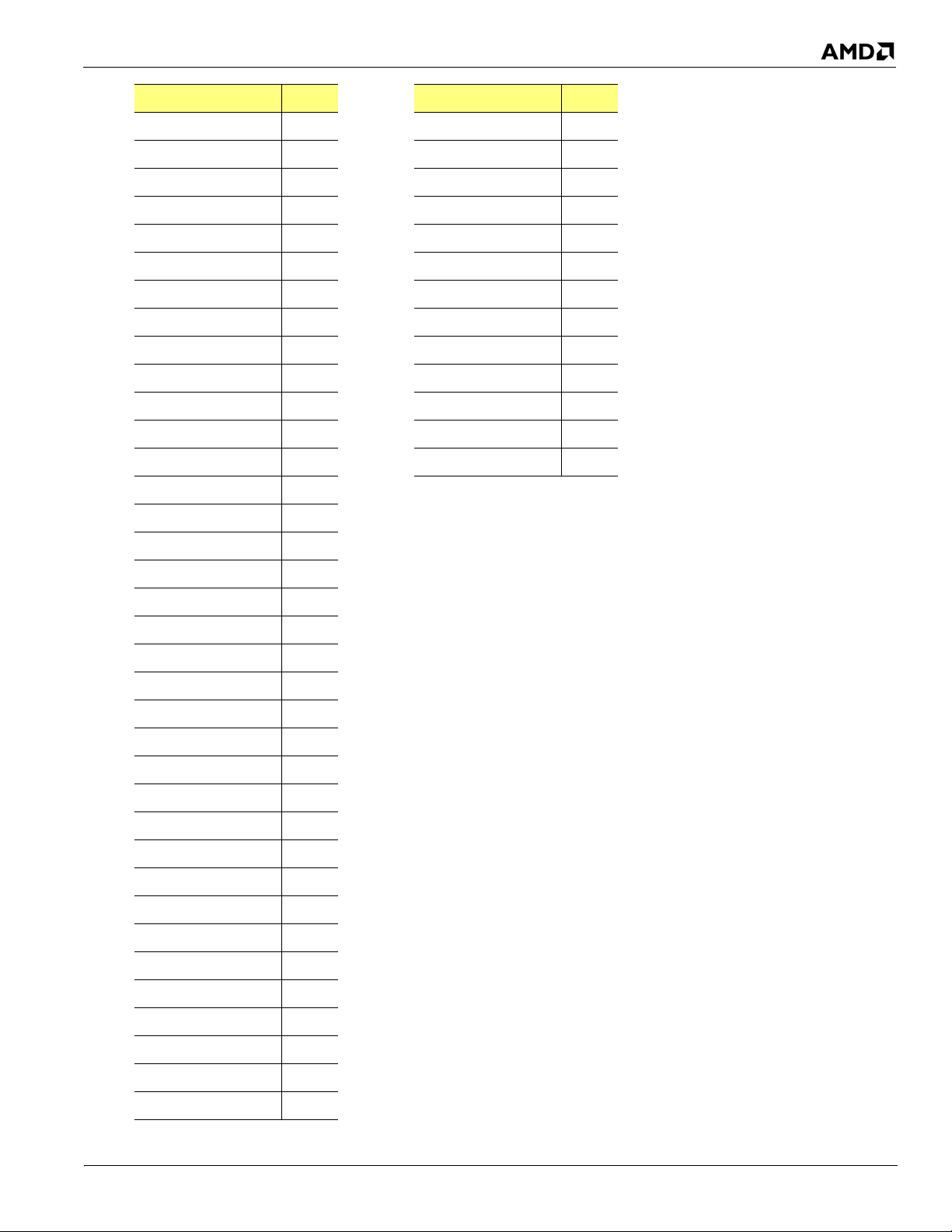

Appendix A: Pin Listings

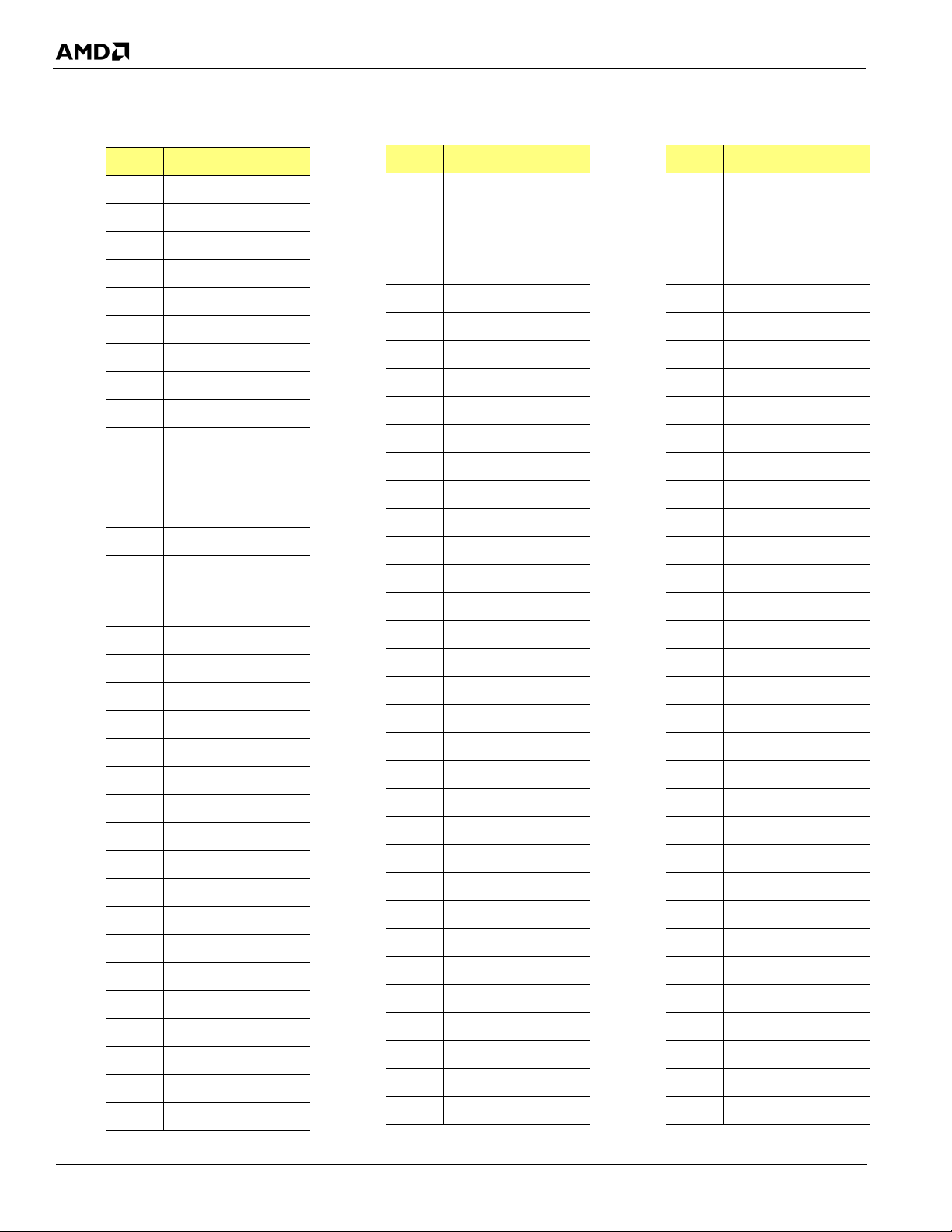

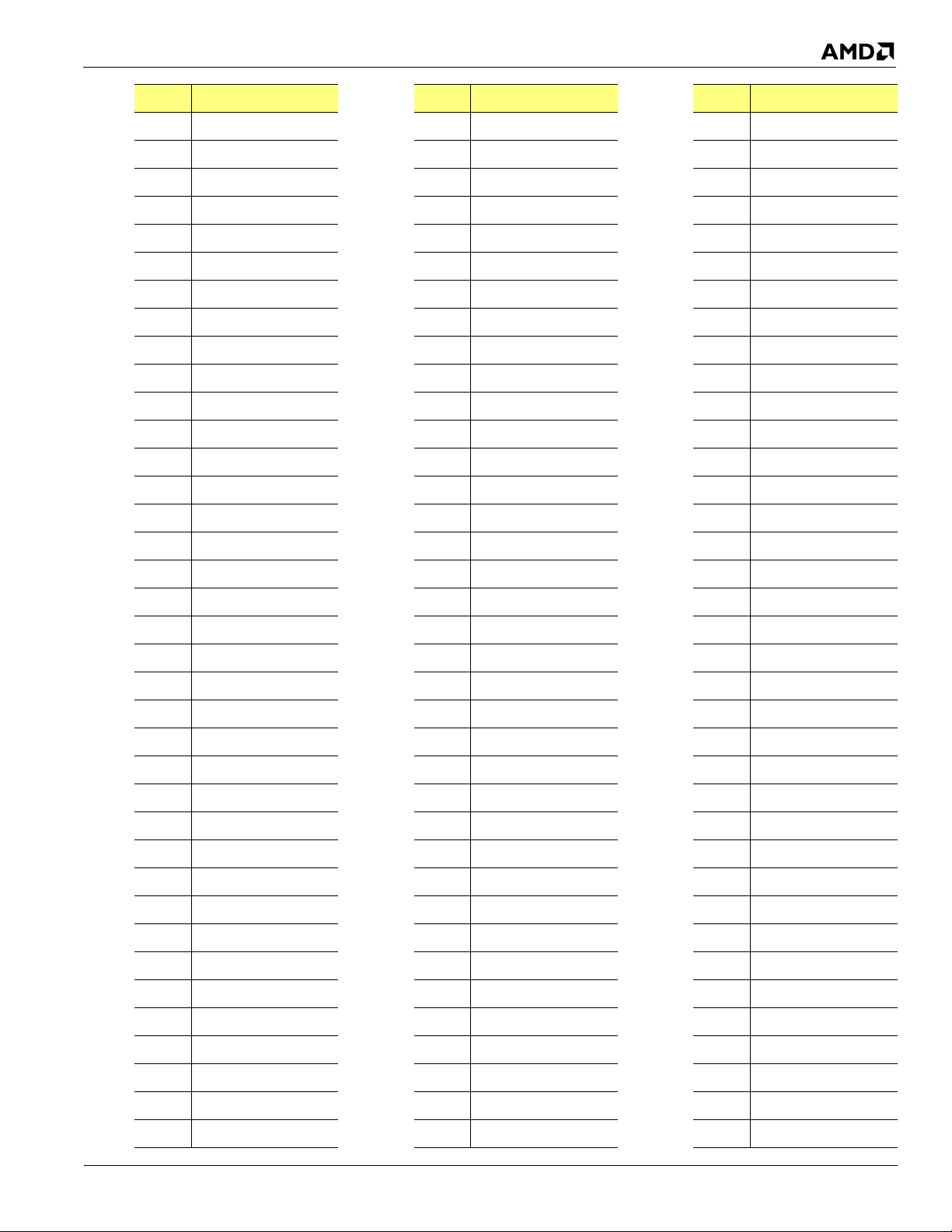

7.5 SR5650 Pin Listing Sorted by Ball Reference................................................................................................................... A-2

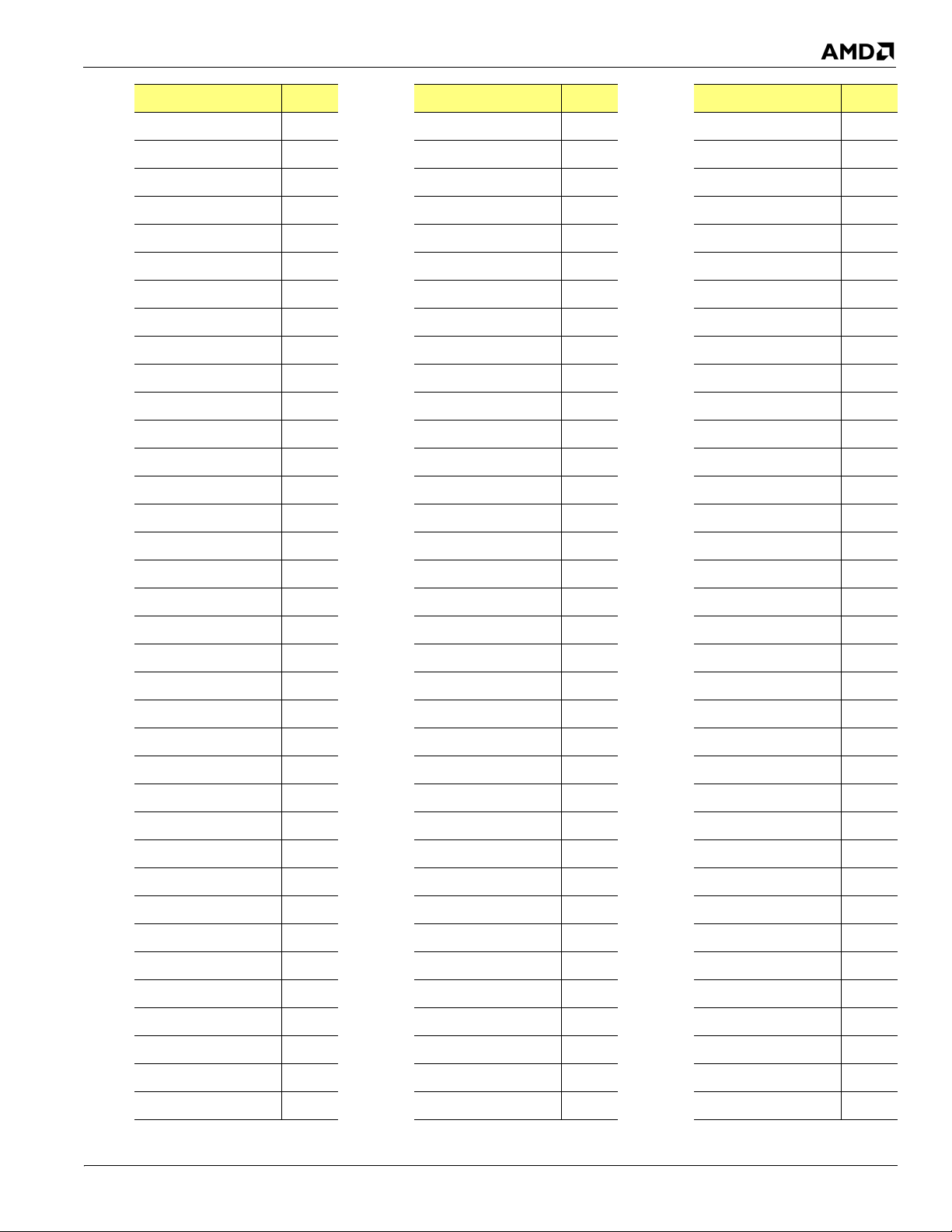

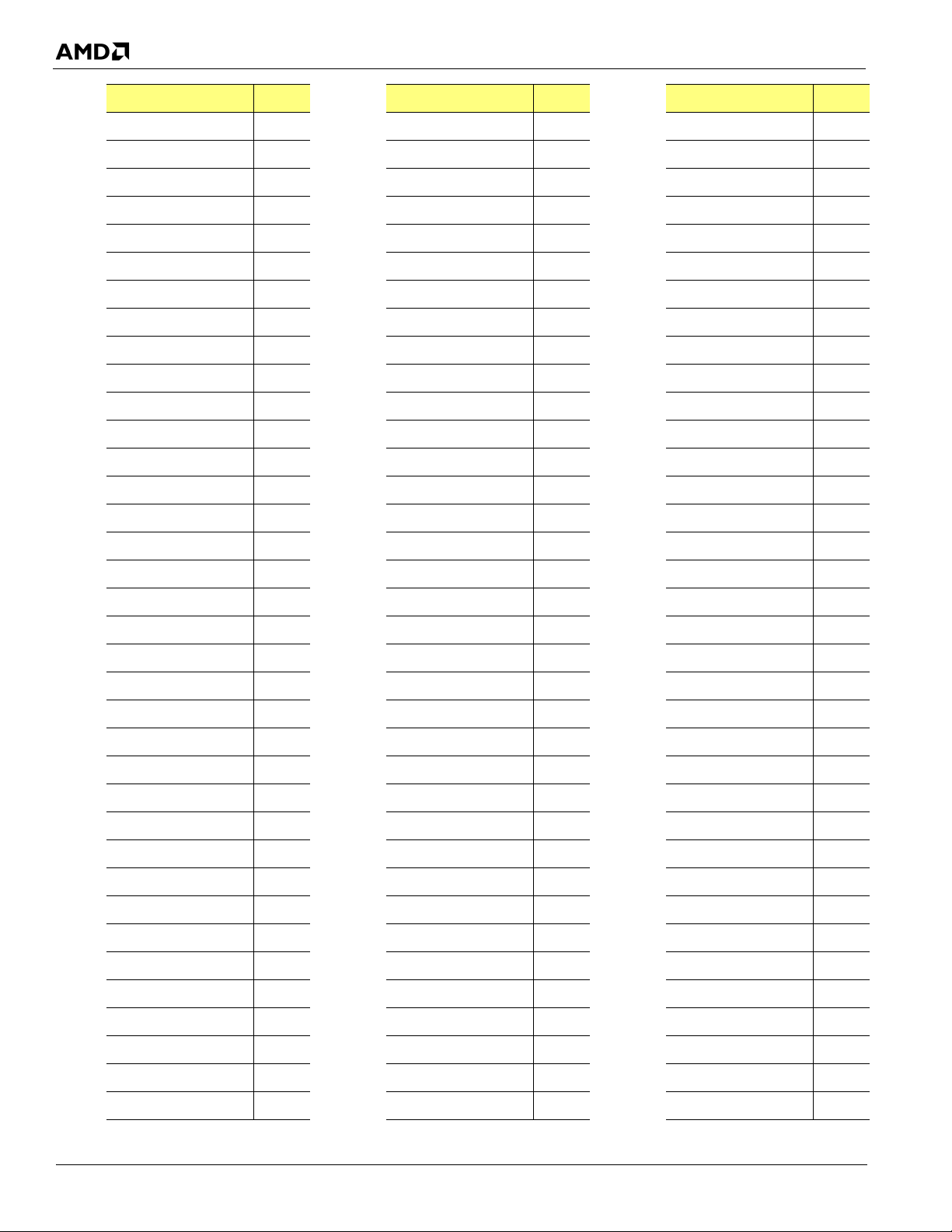

A.1 SR5650 Pin Listing Sorted by Pin Name .......................................................................................................................... A-9

Appendix B: Revision History

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary Table of Contents-3

Page 6

This page is left blank intentionally.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

Table of Contents-4 Proprietary

Page 7

List of Figures

Figure 1-1: SR5650 Branding Diagram for A21 Production ASIC (Eutectic Part) ....................................................................... 1-3

Figure 1-2: SR5650 Branding Diagram for A21 Production ASIC (Lead Free Part) .................................................................... 1-3

Figure 1-3: SR5650 Alternate Branding for A21 Production ASIC (Lead Free Part) ................................................................... 1-4

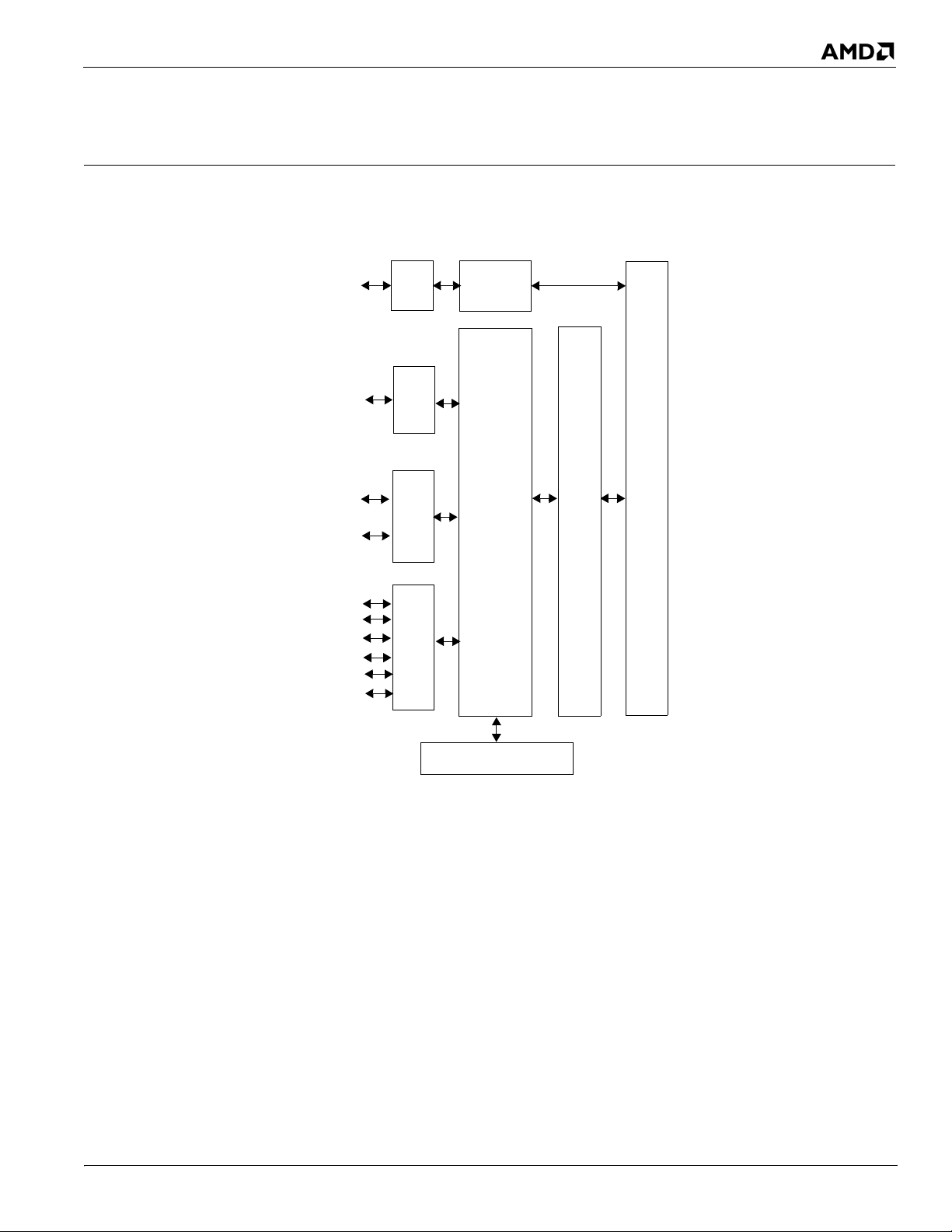

Figure 2-1: SR5650 Internal Blocks and Interfaces ....................................................................................................................... 2-1

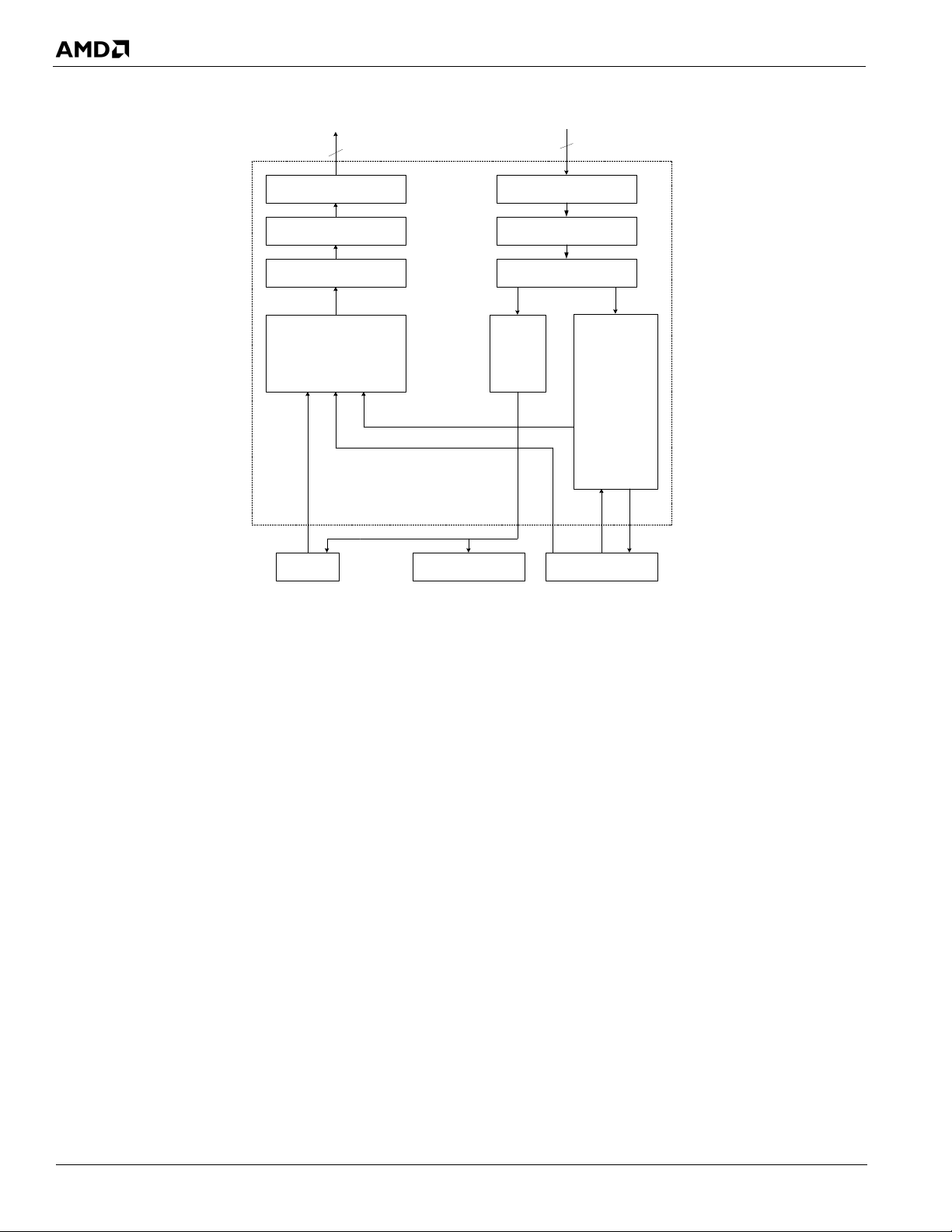

Figure 2-2: HyperTransport™ Interface Block Diagram ............................................................................................................... 2-2

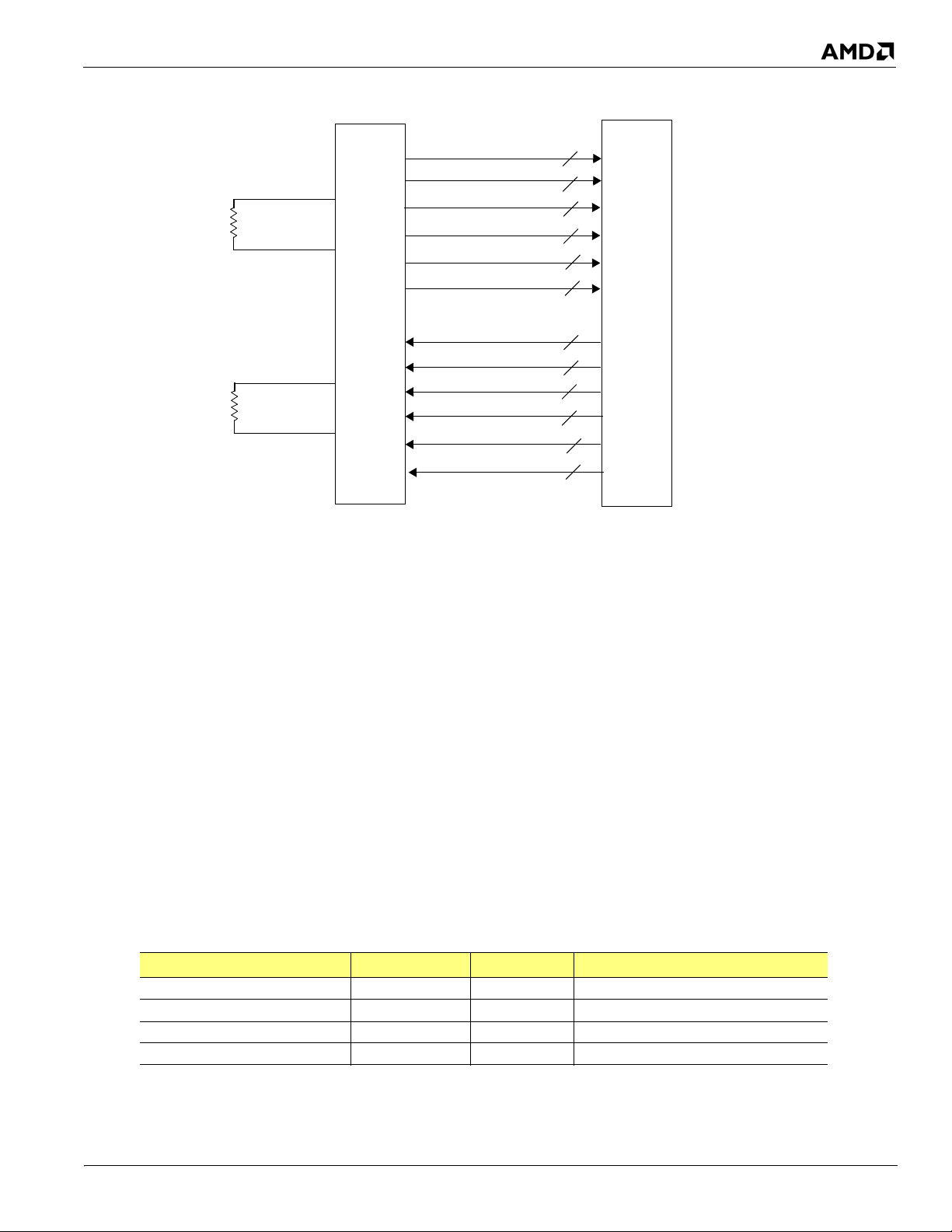

Figure 2-3: SR5650 HyperTransport™ Interface Signals .............................................................................................................. 2-3

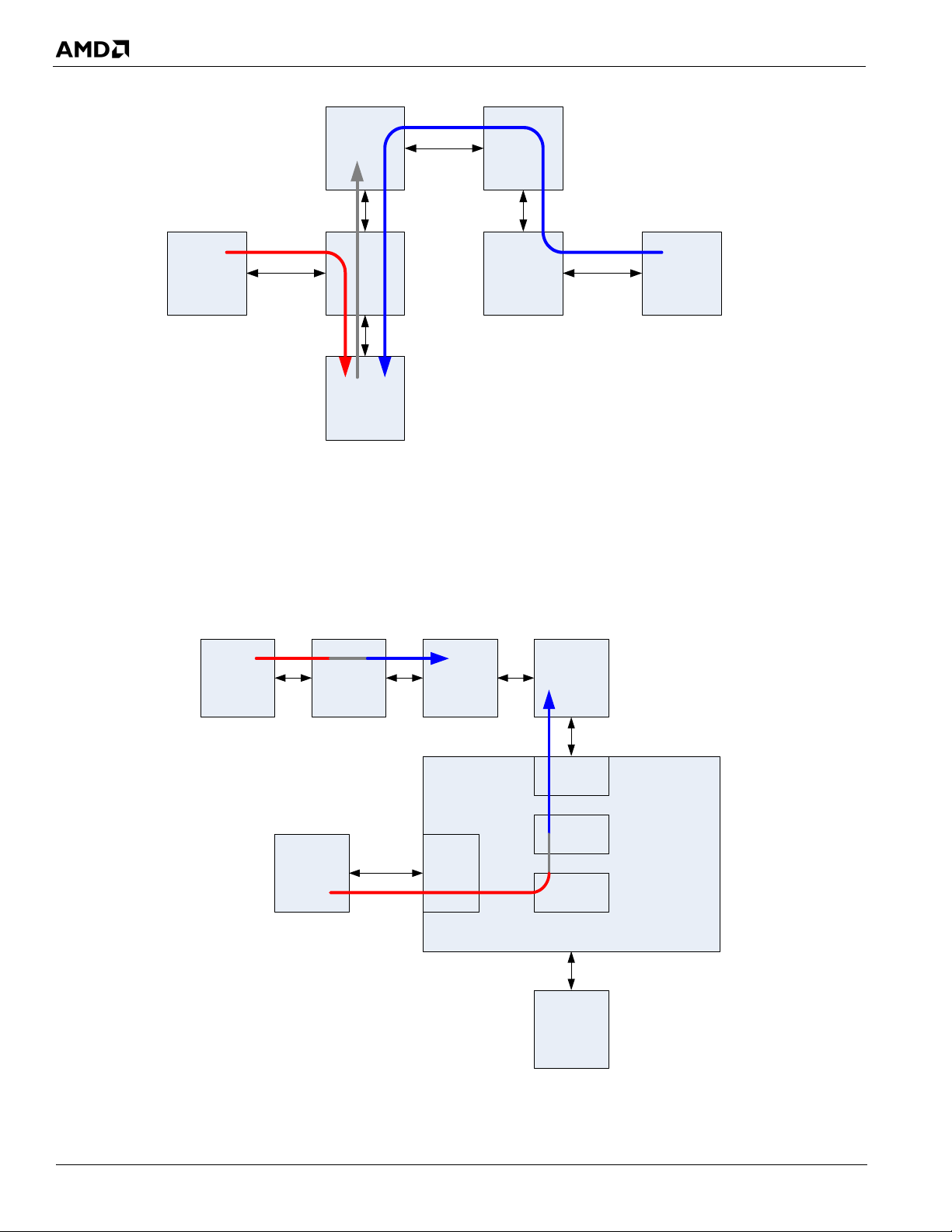

Figure 2-4: Interrupt Routing Paths in Legacy Mode .................................................................................................................... 2-6

Figure 2-5: Interrupt Routing Paths in Legacy Mode with Integrated IOAPIC ............................................................................. 2-6

Figure 2-6: Interrupt Routing Path in MSI Mode .......................................................................................................................... 2-7

Figure 2-7: Suggested Platform Level RAS Sideband Signal Connections ................................................................................... 2-9

Figure 3-1: SR5650 Interface Block Diagram ............................................................................................................................... 3-4

Figure 4-1: SR5650 Power Rail Power Up Sequence .................................................................................................................... 4-3

Figure 5-2: SR5650 692-Pin FCBGA Package Outline ................................................................................................................. 5-4

Figure 5-3: SR5650 Ball Arrangement (Bottom View) ................................................................................................................. 5-5

Figure 5-4: RoHS/Lead-Free Solder (SAC305/405 Tin-Silver-Copper) Reflow Profile .............................................................. 5-7

Figure 7-1: XOR Tree .................................................................................................................................................................... 7-2

Figure 7-2: Sample of a Generic VOH/VOL Tree ......................................................................................................................... 7-5

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary List of Figures-1

Page 8

This page is left blank intentionally.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

List of Figures-2 Proprietary

Page 9

List of Tables

Table 1-1: Device IDs for the SR5690/5670/5650 Chipset Family ................................................................................................1-3

Table 1-2: Pin Type Codes ..............................................................................................................................................................1-4

Table 1-3: Acronyms and Abbreviations ........................................................................................................................................1-5

Table 2-1: SR5650 HyperTransport™ Flow Control Buffers .........................................................................................................2-3

Table 2-2: Types of Errors Detectable by the SR5650 AER Implementation ..............................................................................2-10

Table 2-3: Types of HyperTransport™ Errors Supported by the SR5650 ....................................................................................2-11

Table 2-4: Possible Configurations for the PCI Express® General Purpose Links ......................................................................2-12

Table 3-1: HyperTransport™ Interface ...........................................................................................................................................3-4

Table 3-2: PCI Express® Interface for General Purpose External Devices ....................................................................................3-5

Table 3-3: 1 x 4 Lane A-Link Express II Interface for Southbridge ...............................................................................................3-5

Table 3-4: Miscellaneous PCI Express® Signals ............................................................................................................................3-6

Table 3-5: Clock Interface ...............................................................................................................................................................3-6

Table 3-6: Power Management Pins ...............................................................................................................................................3-6

Table 3-7: Miscellaneous Pins ........................................................................................................................................................3-7

Table 3-8: Power Pins .....................................................................................................................................................................3-7

Table 3-9: Ground Pins ...................................................................................................................................................................3-9

Table 3-10: Strap Definitions for the SR5650 ..............................................................................................................................3-10

Table 3-11: Strap Definition for STRAP_PCIE_GPP_CFG .........................................................................................................3-10

Table 4-1: Timing Requirements for PCIe® Differential Clocks (GPP1_REFCLK and GPP3_REFCLK at 100MHz) ...............4-1

Table 4-2: Timing Requirements for HyperTransport™ Reference Clock (100MHz) ...................................................................4-1

Table 4-3: Timing Requirements for OSCIN Reference Clock (14.3181818MHz) .......................................................................4-2

Table 4-4: Power Rail Groupings for the SR5650 ..........................................................................................................................4-2

Table 4-5: SR5650 Power Rail Power-up Sequence .......................................................................................................................4-3

Table 5-1: Power Rail Maximum and Minimum Voltage Ratings .................................................................................................5-1

Table 5-2: Power Rail Current Ratings ...........................................................................................................................................5-1

Table 5-1: DC Characteristics for PCIe® Differential Clocks (GPP1_REFCLK and GPP3_REFCLK at 100MHz) ....................5-1

Table 5-3: DC Characteristics for 1.8V GPIO Pads ........................................................................................................................5-2

Table 5-4: DC Characteristics for the HyperTransport™ 100MHz Differential Clock (HT_REFCLK) .......................................5-2

Table 5-5: SR5650 Thermal Limits ................................................................................................................................................5-2

Table 5-6: SR5650 692-Pin FCBGA Package Physical Dimensions .............................................................................................5-4

Table 5-7: Recommended Board Solder Reflow Profile - RoHS/Lead-Free Solder ......................................................................5-6

Table 6-1: ACPI States Supported by the SR5650 .........................................................................................................................6-1

Table 7-1: Pins on the Test Interface ..............................................................................................................................................7-1

Table 7-2: Example of an XOR Tree ..............................................................................................................................................7-2

Table 7-3: SR5650 XOR Tree .........................................................................................................................................................7-3

Table 7-4: Truth Table for the VOH/VOL Tree Outputs ................................................................................................................7-5

Table 7-5: SR5650 VOH/VOL Tree

...............................................................................................................................................7-6

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary List of Tables-1

Page 10

This page intentionally left blank.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

List of Tables-2 Proprietary

Page 11

1.1 Introducing the SR5650

Chapter 1

Overview

The SR5650 is the system logic of the latest server/workstation platform from AMD that enables its next generation

CPUs. The SR5650 has a total of 26 PCI Express

are dedicated for the A-Link Express II interface to AMD’s Southbridges such as the SP5100 (formerly SB700S). The

SR5650 also comes equipped with the new HyperTransport™ 3 and PCIe Gen 2 technologies. All of these are achieved

by a highly integrated, thermally efficient design in a 29mm x 29mm package.

The SR5650 introduces a variety of Reliability, Availability and Serviceability (RAS) capabilities. These include parity

protection for on-chip memories, PCI Express Advanced Error Reporting (AER), and advanced error handling

capabilities for HyperTransport.

The SR5650 also supports a revision 1.26 compliant IOMMU (Input/Output Memory Management Unit) implementation

for address translation and protection services. This feature allows virtual addresses from PCI Express endpoint devices to

be translated to physical memory addresses. On-chip caching of address translations is provided to improve I/O

performance. The device is also compliant with revision 1.0 of the PCI Express Address Translation Services (ATS)

specification to enable ATS-compliant endpoint devices to cache address translation. These features enhance memory

protection and support hardware-based I/O virtualization when combined with appropriate operating system or hypervisor

software. Combined with AMD Virtualization™ (AMD-V™) technology, these features are designed to provide

comprehensive platform level virtualization support.

1.2 SR5650 Features

1.2.1 CPU Interface

•

Supports 16-bit up/down HyperTransport™ (HT) 3.0 interface up to 5.2 GT/s.

• Supports 200, 400, 600, 800, and 1000 MHz HT1 frequencies.

• Supports 1200, 1400, 1600, 1800, 2000, 2200, 2400, and 2600 MHz HT3 frequencies (up to 2400 MHz only for the

RX980) .

• Supports “Shanghai” and subsequent series of AMD server/workstation and desktop processors through sockets F,

AM3, G34, and C32.

• Supports LDTSTOP interface and CPU throttling.

®

(PCIe®) lanes: 22 lanes are dedicated for external PCIe devices, and 4

1.2.2 PCI Express® Interface

•

Supports PCIe Gen 2 (version 2.0).

• Optimized peer-to-peer and general purpose link performance.

• Supports 22 PCIe Gen 2 general purpose lanes, and up to 8 devices on specific ports (possible configurations are

described in Section 2.6, “PCI Express®”).

• Supports a revision 1.26 compliant IOMMU (Input/Output Memory Management Unit) implementation for address

translation and protection services. Please refer to the AMD I/O Virtualization Technology (IOMMU) Specification

for more details.

1.2.3 A-Link Express II Interface

•

One x4 A-Link Express II interface for connection to an AMD Southbridge. The A-Link Express II is a proprietary

interface developed by AMD based on the PCI Express technology, with additional Northbridge-Southbridge

messaging functionalities.

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 1-1

Page 12

1.2.4 Multiple Processor Support

•

Supports multiple-socket configurations for up to 8 processors on the same system.

1.2.5 Multiple Northbridge Support

Supports multiple-SR5690/5670/5650 configurations on the same system. See Section 2.3, “Multiple Northbridge

•

Support,” for details.

1.2.6 Power Management Features

•

Fully supports ACPI states S1, S3, S4, and S5.

• The Chip Power Management Support logic supports four device power states defined for the OnNow Architecture—

On, Standby, Suspend, and Off. Each power state can be achieved by software control bits.

• Support for AMD PowerNow!™ technology.

• Clocks are controlled dynamically using a mechanism that is transparent to the software. The ASIC hardware detects

idle blocks and turns off the clocks to those blocks in order to reduce power consumption.

• Supports dynamic lane reduction for the PCIe interfaces, adjusting to the task the number of lanes employed.

1.2.7 PC Design Guide Compliance

The SR5650 complies with all relevant Windows Logo Program (WLP) requirements from Microsoft® for WHQL

certification.

Software Features

1.2.8 Test Capability Features

The SR5650 has a variety of test modes and capabilities that provide a very high fault coverage and low DPM (Defect Per

Million) ratio:

• Full scan implementation on the digital core logic which provides about 97% fault coverage through ATPG

(Automatic Test Pattern Generation Vectors).

• Dedicated test logic for the on-chip custom memory macros to provide complete coverage on these modules.

• A JTAG test mode in order to allow board level testing of neighboring devices.

• An XOR tree test mode on all the digital I/O's to allow for proper soldering verification at the board level.

• Access to the analog modules and PLLs in the SR5650 in order to allow full evaluation and characterization of these

modules.

• IDDQ mode support to allow chip evaluation through current leakage measurements.

• Highly advanced signal observability through the debug port.

These test modes can be accessed through the settings of the instruction register of the JTAG circuitry.

1.2.9 Packaging

•

Single chip solution in 65nm, 1.1V CMOS technology.

• Flip chip design in a 29mm x 29mm 692-FCBGA package.

1.3 Software Features

• Supports Windows Server

• Supports corporate manageability requirements such as DMI.

• ACPI support.

• Full write combining support for maximum performance.

• Comprehensive OS and API support.

• Extensive Power Management support.

®

2003, Windows Server® 2008, Red Hat Enterprise Linux, SUSE Linux, and Solaris.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

1-2 Proprietary

Page 13

Device ID

Northbridge

YYWW

MADE IN TAIWAN

WXXXXX

215-0716032

* YY - Assembly Start Year

WW - Assembly Start Week

Part Number

Date Code*

AMD Product Type

AMD Logo

Wafer Lot Number

Country of Origin

Note: Branding can be in laser, ink, or

mixed laser-and-ink marking.

Northbridge

YYWW

MADE IN TAIWAN

WXXXXX

215-0716042

* YY - Assembly Start Year

WW - Assembly Start Week

Part Number

Date Code*

AMD Product Type

AMD Logo

Wafer Lot Number

Country of Origin

Note: Branding can be in laser, ink, or

mixed laser-and-ink marking.

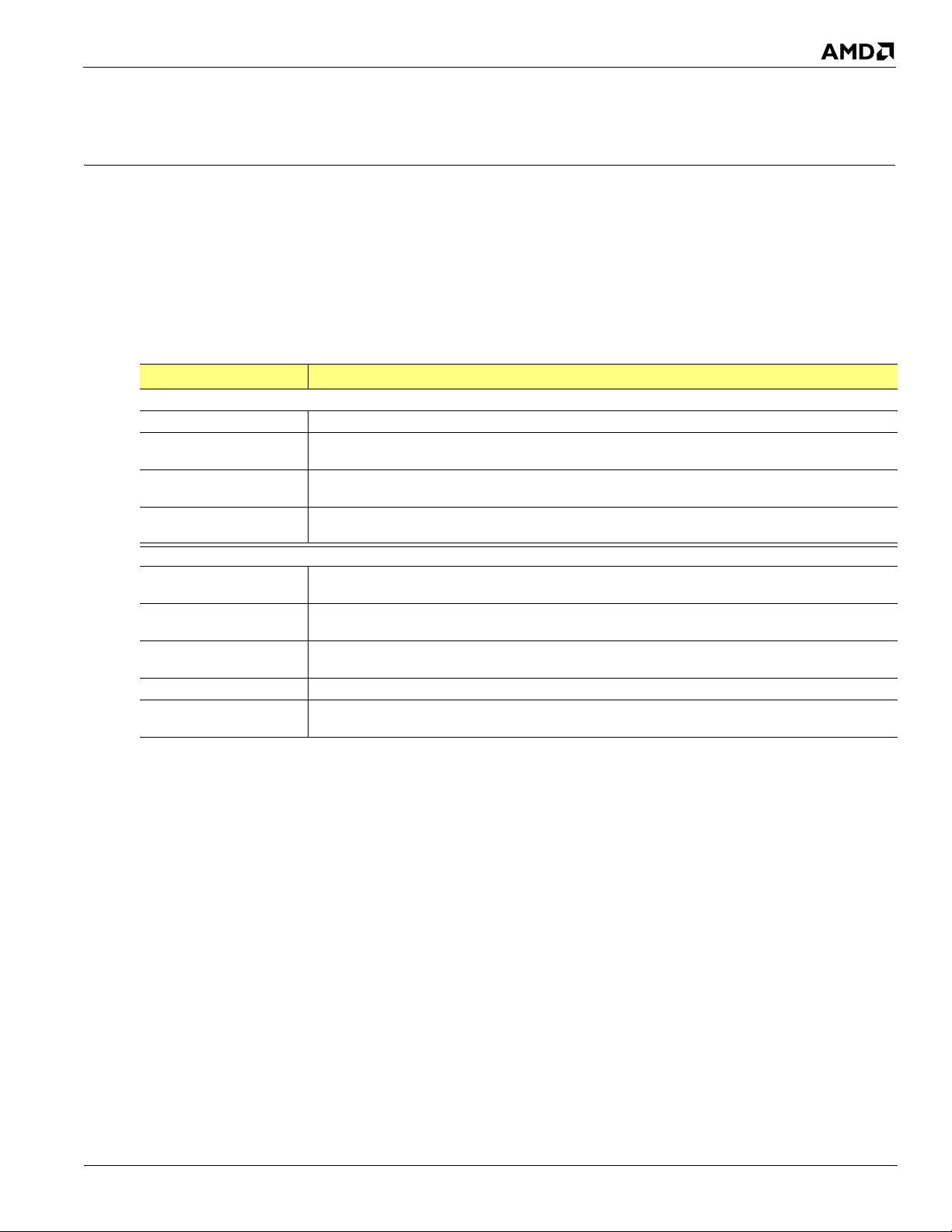

1.4 Device ID

The SR5650 is a member of the AMD chipset family, which consists of different devices designed to support different

platforms. Each device is identified by a device ID, which is stored in the NB_DEVICE_ID register. The device IDs for

the SR5650/5690/5670 chipset family are as follows:

Table 1-1 Device IDs for the SR5690/5670/5650 Chipset Family

Device Device ID

SR5690 5A10h

SR5670 5A12h

SR5650 5A13h

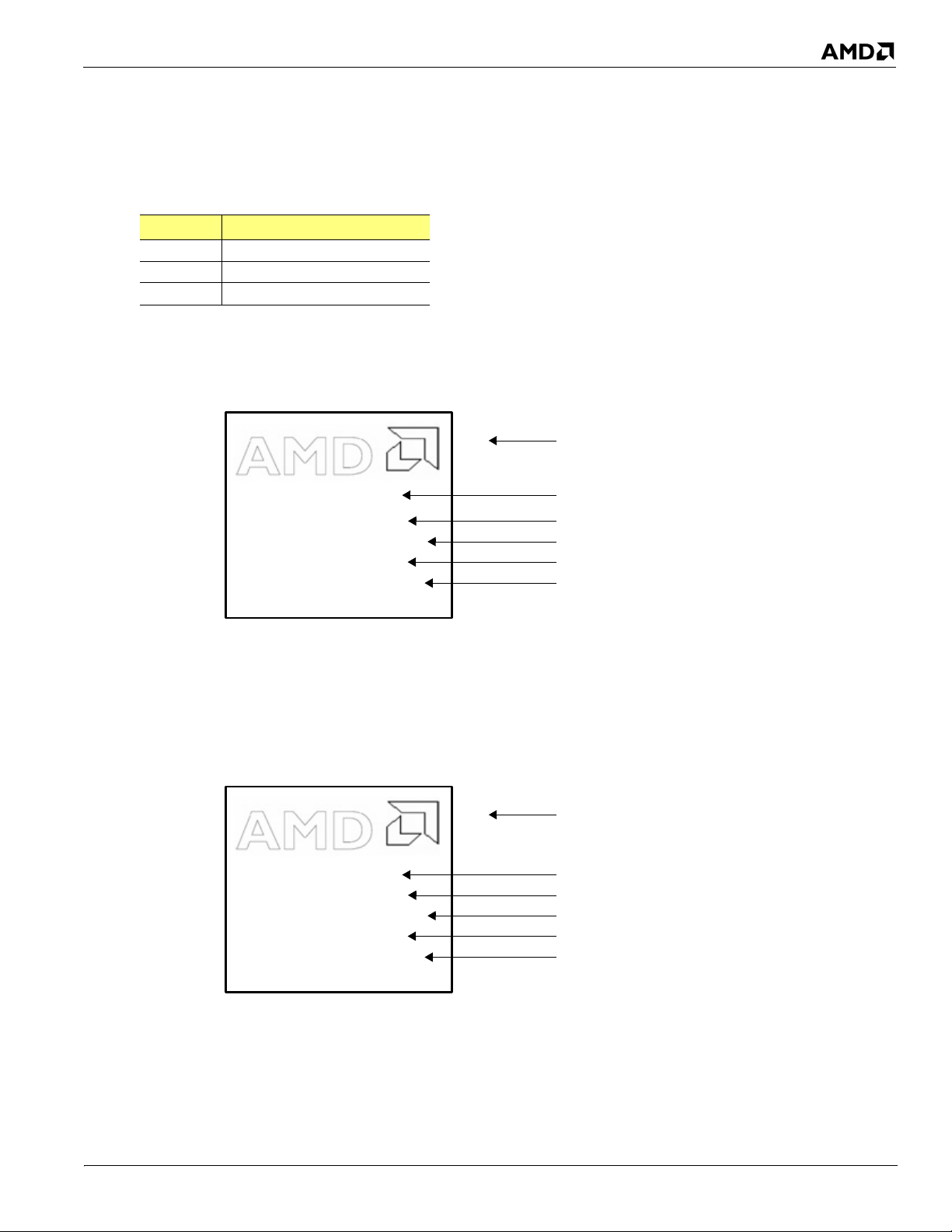

1.5 Branding Diagrams

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 1-3

Figure 1-1 SR5650 Branding Diagram for A21 Production ASIC (Eutectic Part)

Figure 1-2 SR5650 Branding Diagram for A21 Production ASIC (Lead Free Part)

Page 14

Northbridge

YYWW

MADE IN TAIWAN

WXXXXX

215-0716054

* YY - Assembly Start Year

WW - Assembly Start Week

Part Number

Date Code*

AMD Product Type

AMD Logo

Wafer Lot Number

Country of Origin

Note: Branding can be in laser, ink, or

mixed laser-and-ink marking.

Figure 1-3 SR5650 Alternate Branding for A21 Production ASIC (Lead Free Part)

1.6 Conventions and Notations

Conventions and Notations

The following sections explain the conventions used throughout this manual.

1.6.1 Pin Names

Pins are identified by their pin names or ball references. All active-low signals are identified by the suffix ‘#’ in their

names (e.g., SYSRESET#).

1.6.2 Pin Types

The pins are assigned different codes according to their operational characteristics. These codes are listed in Table 1-2.

Table 1-2 Pin Type Codes

Code Pin Type

I Digital Input

O Digital Output

I/O Bi-Directional Digital Input or Output

M Multifunctional

Pwr Power

Gnd Ground

A-O Analog Output

A-I Analog Input

A-I/O Analog Bi-Directional Input/Output

A-Pwr Analog Power

A-Gnd Analog Ground

Other Pin types not included in any of the categories above

1.6.3 Numeric Representation

Hexadecimal numbers are appended with “h” whenever there is a risk of ambiguity. Other numbers are in decimal.

Pins of identical functions but different trailing digits (e.g., DFT_GPIO0, DFT_GPIO1, ...DFT_GPIO5) are referred to

collectively by specifying their digits in square brackets and with colons (i.e., “DFT_GPIO[5:0]”). A similar short-hand

notation is used to indicate bit occupation in a register. For example, NB_COMMAND[15:10] refers to the bit positions

10 through 15 of the NB_COMMAND register.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

1-4 Proprietary

Page 15

Conventions and Notations

1.6.4 Hyperlinks

Phrases or sentences in blue italic font are hyperlinks to other parts of the manual. Users of the PDF version of this manual

can click on the links to go directly to the referenced sections, tables, or figures.

1.6.5 Acronyms and Abbreviations

The following is a list of the acronyms and abbreviations used in this manual.

Table 1-3 Acronyms and Abbreviations

Acronym Full Expression

ACPI Advanced Configuration and Power Interface

ASPM Active State Power Management

A-Link-E A-Link Express interface between the Northbridge and Southbridge.

BGA Ball Grid Array

BIOS

BIST Built In Self Test.

DBI Dynamic Bus Inversion

DPM Defects per Million

EPROM Erasable Programmable Read Only Memory

FCBGA Flip Chip Ball Grid Array

FIFO First In, First Out

VSS Ground

GPIO General Purpose Input/Output

HT HyperTransport™ interface

IDDQ Direct Drain Quiescent Current

IOMMU Input/Output Memory Management Unit

JTAG Joint Test Access Group. An IEEE standard.

MB Mega Byte

NB Northbridge

PCI Peripheral Component Interface

®

PCIe

PLL Phase Locked Loop

POST Power On Self Test

PD Pull-down Resistor

PU Pull-up Resistor

RAS Reliability, Availability and Serviceability

SB Southbridge

TBA To Be Added

VRM Voltage Regulation Module

Basic Input Output System. Initialization code stored in a ROM or Flash RAM used to start up a

system or expansion card.

PCI Express

®

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 1-5

Page 16

This page is left blank intentionally.

Conventions and Notations

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

1-6 Proprietary

Page 17

Chapter 2

HyperTransport™ 3

Unit

CPU

Interface

Root

CPU

Southbridge

Complex

A-Link-E

Interface

GPP3 Interface

PCIe

(6 Lanes for 6 ports)

Expansion

Slots

(1 x 4 Lanes)

IO Controller

GPP1 Interface

PCIe

®

Register Interface

(1 x 16 or 2 x 8 Lanes)

IOMMU

Expansion

Slots

Functional Descriptions

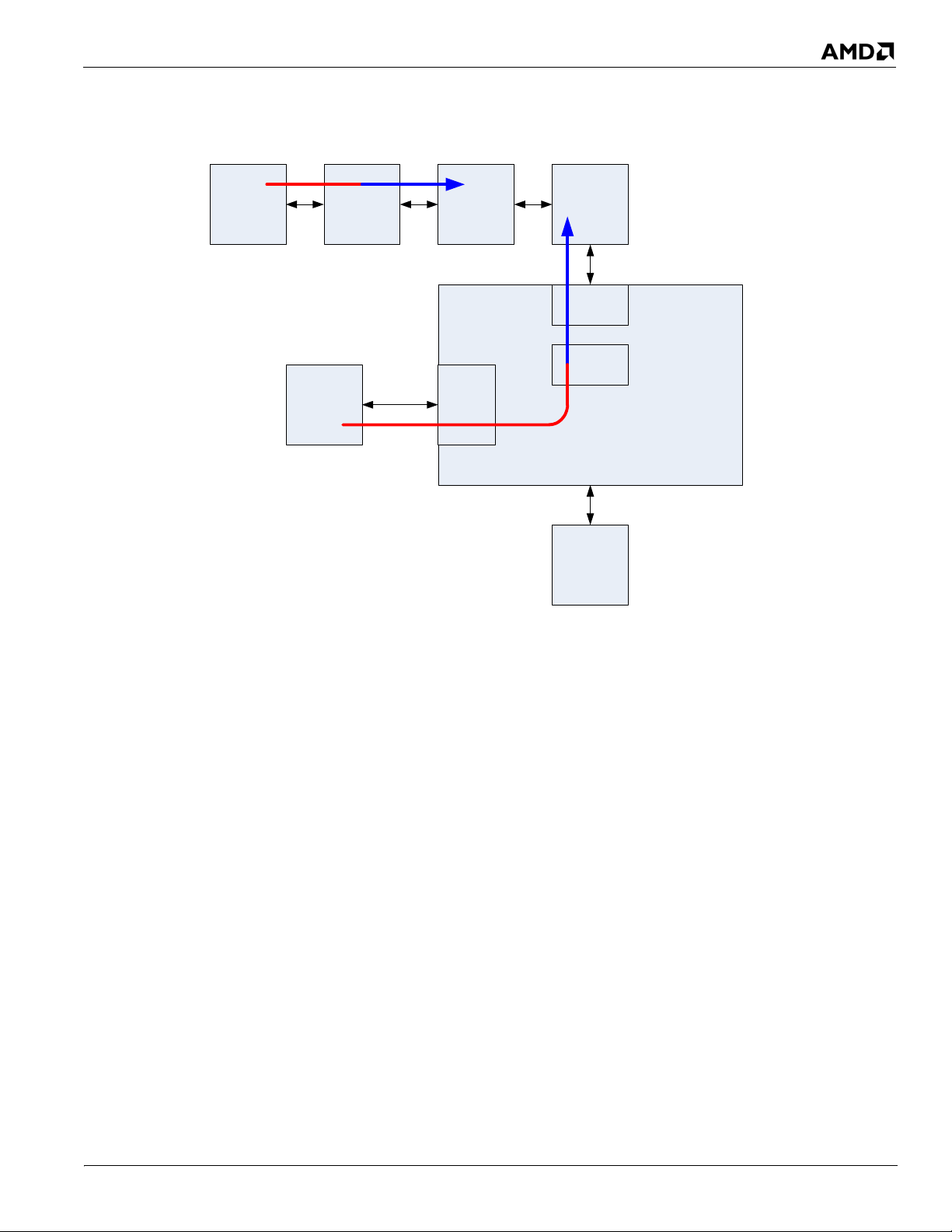

This chapter describes the functional operation of the major interfaces of the SR5650 system logic chip. Figure 2-1

illustrates the SR5650 internal blocks and interfaces.

Figure 2-1 SR5650 Internal Blocks and Interfaces

2.1 HyperTransport™ Interface

2.1.1 Overview

The SR5650 is optimized to interface with “Shanghai” and subsequent series of AMD server/workstation and desktop

processors through sockets F, AM3, G34, and C32. The SR5650 supports HyperTransport

HyperTransport 1 (HT1) for backward compatibility and for initial boot-up. For a detailed description of the interface,

please refer to the HyperTransport I/O Link Specification from the HyperTransport Consortium. Figure 2-2,

“HyperTransport™ Interface Block Diagram,” illustrates the basic blocks of the host bus interface of the SR5650.

™

3 (HT3), as well as

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 2-1

Page 18

I/O Controller

Upstream Arbitration

IOMMU L2

10.4 GB/s to

CPU

Response

Interface

Host Interface

Host

requests

Host read

responses

Host read

responses

DMA requests

DMA

read

response

data

IOMMU

requests

10.4 GB/s from

CPU

Rx PHYTx PHY

Rx PHY InterfaceTx PHY Interface

Protocol ReceiverProtocol Transmitter

PCIe® Cores

HyperTransport™ Interface

Figure 2-2 HyperTransport™ Interface Block Diagram

The SR5650 HyperTransport bus interface consists of 16 unidirectional differential Command/Address/Data pins, and 2

differential Control pins and 2 differential Clock pins in both the upstream and downstream directions. On power up, the

link is 8-bit wide and runs at a default speed of 400MT/s in HyperTransport 1 mode. After negotiation, carried out by the

HW and SW together, the link width can be brought up to the full 16-bit width and the interface can run up to 5.2GT/s in

HyperTransport 3 mode. In HyperTransport 1 mode, the interface operates by clock-forwarding while in HyperTransport

3 mode, the interface operates by dynamic phase recovery, with frequency information propagated over the clock pins.

The interface is illustrated below in Figure 2-3, “SR5650 HyperTransport™ Interface Signals.” The signal name and

direction for each signal is shown with respect to the SR5650. Detailed descriptions of the signals are given in Section 3.3,

“CPU HyperTransport™ Interface‚’ on page 3-4.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

2-2 Proprietary

Page 19

HyperTransport™ Interface

HT_TXCALP

HT_RXCALN

HT_RXCALP

HT_TXCALN

HT_RXCADN

2

2

SR5650

CPU

HT_RXCADP

HT_RXCTLN

HT_RXCTLP

HT_RXCLKN

HT_RXCLKP

16

16

HT_TXCADN

2

2

HT_TXCADP

HT_TXCTLN

HT_TXCTLP

HT_TXCLKN

HT_TXCLKP

16

16

2

2

2

2

2.1.2 HyperTransport™ Flow Control Buffers

Figure 2-3 SR5650 HyperTransport™ Interface Signals

The SR5650 HyperTransport interface has the following features:

• HyperTransport 3.0 compliant

• 16-bit and 8-bit link widths supported. Width for each direction of the link is independently controlled.

• 400MT/s to 5.2GT/s link speeds in increments of 400MT/s (up to 2GT/s only for HyperTransport 1 mode)

• DC-coupled HyperTransport mode only

• UnitID clumping for x16 PCI Express

®

ports

• Isochronous flow-control mode for Southbridge audio and IOMMU traffic

• 64-bit address extension support (52-bit physical addressing)

• Link disconnection with tristate, LS1, and LS2 low-power modes

• Error retry in HyperTransport 3 mode

• Full HyperTransport-defined BIST support for both internal and external loopback modes

The SR5650 HTIU implements the following flow control buffers in its receiver:

Table 2-1 SR5650 HyperTransport™ Flow Control Buffers

Flow Control Buffer Type Posted Non-Posted Response

Cmd 16 16 Advertise 63 credits.

Data 16 1 Advertise 63 credits.

ISOC Cmd 0 0 Advertise 63 credits.

ISOC Data 0 0 Advertise 63 credits.

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 2-3

Page 20

2.2 IOMMU

The SR5650’s IOMMU (Input/Output Memory Management Unit) block provides address translation and protection

services as described in version 1.26 of the AMD I/O Virtualization Technology (IOMMU) Specification. The SR5650

also supports the PCI Express Address Translation Services 1.0 Specification, which allows the supporting of endpoint

devices to request and cache address translations.

When DMA requests containing virtual addresses are received, the IOMMU looks up the page translation tables located

in the system memory in order to convert the virtual addresses into physical addresses and to verify access privileges.

On-chip caching is provided in order to speed up translation and reduce or eliminate the number of system memory

accesses required. Every PCIe core contains a local translation cache, and the SR5650 also contains a shared global

translation cache.

The SR5650 supports up to 2

52-bit physical address space.

16

domains, each of which can utilize a separate 64-bit virtual address space. It supports a

2.3 Multiple Northbridge Support

Multiple SR5690/5670/5650 (referred to as “SR56x0”below) Northbridges may be implemented in the same system given

enough free HyperTransport links from the processor complex. However, only a single Southbridge may be used. The

SR56x0 attached to the Southbridge is called the primary SR56x0, and any other instance of SR56x0 is called a secondary

SR56x0. The A-Link Express interface on any secondary SR56x0 must be left unconnected, and it cannot be used to

support any PCI Express endpoint devices.

IOMMU

The PWM_GPIO5 pin-strap is used to indicate whether an SR56x0 is a primary or a secondary Northbridge. If no

pull-down resistor is attached on the pin, the internal pull-up resistor on it will set the strap value to “1,” indicating the

device to be a primary Northbridge. On any secondary SR56x0, the PWM_GPIO5 pin-strap must be pulled low.

In the multi-NB mode, special PCI Express messages for functions such as PME may be passed from a secondary SR56x0

to the primary SR56x0 or the Southbridge over the HyperTransport bus. If the SR56x0’s internal IOAPIC is not used,

INTx messages may also be forwarded over the HyperTransport bus to the Southbridge IOAPIC. Peer-to-peer writes

between PCI Express endpoints are also allowed between any SR56x0 and another by routing peer-to-peer requests over

the HyperTransport bus.

Note: As it is possible to mix-and-match SR5650, SR5670, and SR5690 on the same system, whenever a

multiple-SR5650 configuration is being referred to in this document, it actually represents any combination of SR5650,

SR5670, and SR5690 possible under that situation. Some constrains may apply.

2.4 Interrupt Handling

2.4.1 Legacy INTx Handling

In legacy interrupt mode, all INTx messages must be routed to the Southbridge IOAPIC. The primary NB directs all INTx

messages directly down to the Southbridge IOAPIC. Secondary NBs direct INTx messages up to the processor complex,

where they are broadcast down to all HT devices. See Section 2.3, “Multiple Northbridge Support‚’ on page 2-4 for

details.

The 4 legacy interrupts sent by endpoint devices (INT A/B/C/D) may undergo a 2-stage programmable swizzling process

that maps them onto the 8 possible internal INTx messages (INT A/B/C/D/E/F/G/H). The first swizzling stage is

performed by rotating the interrupt message number based upon the bridge device number. The second stage is register

controllable on a per-bridge basis and maps the rotated INT A/B/C/D onto INT E/F/G/H. INT A to H messages sent to the

Southbridge are mapped onto the SB IOAPIC interrupt redirection table entries 16 to 23.

2.4.2 Non-SB IOAPIC Support

The SR5650 supports routing legacy IOAPIC memory-mapped I/O addresses (0xFECx_xxxx) to any PCI Express port to

support endpoint devices with integrated IOAPIC.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

2-4 Proprietary

Page 21

Interrupt Handling

2.4.3 Integrated IOAPIC Support

The SR5650 supports routing local INTx messages to its integrated IOAPIC. The integrated IOAPIC contains a 32-entry

redirection table. INTx messages from endpoint devices, bridges, HTIU, and IOMMU can be mapped onto different

redirection entries under register control.

2.4.4 MSI Interrupt Handling and MSI to HT Interrupt Conversion

In MSI interrupt mode, all interrupts are sent directly from the endpoint devices through the SR5650 up to the processor

complex. All MSI interrupts are converted into HT-formatted interrupts. For MSIs from PCI Express endpoint devices

and internally generated PCI Express interrupts, the conversion occurs in the associated IOMMU L1 block. For IOMMU

interrupts and, optionally, HT error interrupts and internal parity error interrupts, the conversion occurs in the HTIU

block. HT error interrupts and internal parity error interrupts may be optionally redirected to an MSI generation block

underneath the SB VC1 IOMMU L1 so that they can be remapped by IOMMU. IOMMU internal MSI interrupts are never

remapped.

The PCI configuration spaces of each on-board device contains a fixed HT MSI mapping capability (except for Device 1,

which is unused). This implies that all MSI interrupts with address 0xFEEx_xxxx have to be converted to HT interrupts.

Because of this, software is required to program all MSI address registers with an 0xFEEx_xxxx address.

2.4.5 Internally Generated Interrupts

The SR5650 may internally generate interrupts for the following purposes:

• PCI Express error

• PCI Express PME

• HT error

• Internal parity error

• IOMMU command handler

• IOMMU event logger

Internally generated interrupts may be in either legacy INTx or MSI format. Internal MSI interrupt sources do not support

per-vector masking.

2.4.6 IOMMU Interrupt Remapping

When the IOMMU is enabled, interrupts generated downstream of the IOMMU are remapped based upon the IOMMU

tables. The following classes of interrupts are not remapped by the IOMMU because they are generated upstream of the

IOMMU:

• HT error (optional)

• Internal parity error (optional)

• IOMMU command handler and event logger

2.4.7 Interrupt Routing Architecture

2.4.7.1 Legacy Mode

Primary SR5650: Legacy INTx messages are routed directly to the SB IOAPIC. The SB IOAPIC generates upstream

interrupt requests, which are translated by the IOMMU before they are delivered up to the processor complex.

Secondary SR5650: Legacy INTx messages are routed over HyperTransport through the processor complex to the

primary SR5650, which forwards them to the SB IOAPIC. The SB IOAPIC generates upstream interrupt requests, which

are translated by the IOMMU before being delivered up to the processor complex.

The routing paths are illustrated in Figure 2-4 below.

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 2-5

Page 22

Interrupt Handling

CPU

SR5650

CPU

SR5650

SB

PCI-E

Endpoint

Device

PCI-E

Endpoint

Device

INTx Message from device attached to primary SR5650

INTx Message from device attached to secondary SR5650

Interrupts from SB IOAPIC

CPU

SB

PCI-E

Endpoint

Device

IOMMU

HT

PCI-

Express

IOAPIC

SR5650

INTx Message from PCI-Express device attached to SR5650

Internal interrupt

Remapped HT Interrupt

SR5650

PCI-E

Endpoint

Device

CPU

Figure 2-4 Interrupt Routing Paths in Legacy Mode

2.4.7.2 Legacy Mode with Integrated IOAPIC

For both the primary and secondary SR5650s, legacy INTx messages are routed to the integrated IOAPICs of the

SR5650s, which generates interrupt requests. These requests are remapped by the IOMMU before being delivered up to

the processor complex. If an INTx message gets directed to an IOAPIC table entry that is not enabled, the IOAPIC sends

the INTx message back to the IOC to go to the SB PIC/IOAPIC.

The routing paths are illustrated in Figure 2-5 below.

Figure 2-5 Interrupt Routing Paths in Legacy Mode with Integrated IOAPIC

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

2-6 Proprietary

Page 23

RAS Features

CPU

SB

PCI-E

Endpoint

Device

IOMMU

HT

PCI-

Express

SR5650

MSI Interrupt from PCI-Express device attached to SR5650

Remapped HT Interrupt

SR5650

PCI-E

Endpoint

Device

CPU

2.4.7.3 MSI Mode

For both the primary and secondary SR5650s: MSI interrupt requests are remapped by the IOMMU and sent up to the

processor complex. The routing path is illustrated in Figure 2-6 below.

2.5 RAS Features

2.5.1 Parity Protection

All memories in SR5650 are parity protected to reduce the possibility of silent data corruption. Multiple parity words are

interleaved to convert burst errors (multiple physically adjacent bits corrupted) into multiple single-bit detectable errors to

increase robustness. The minimum number of interleaved parity words in any on-board memory is 4. All macros contain

2.5.1.1 Parity Protection for IOMMU Cache Memories

2.5.1.2 Parity Protection for Normal Memories

2.5.2 SERR_FATAL# and NON_FATAL_CORR# Pins

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 2-7

test circuitry for software to generate false errors on either the read or write side of the memory for verification of error

handling routines. Error injection circuitry only corrupts parity bits rather than real data bits to avoid data corruption.

All IOMMU cache memories are parity protected. When a parity error is detected, the access from the associated bank is

marked as an automatic miss. The cache line is marked as invalid and may later be overwritten with data from system

memory (which is ECC protected). The error is logged in a status bit and an optional interrupt is generated (either fatal,

non-fatal, or correctable parity error).

All normal memories are also parity protected. When a parity error is detected, the failure is likely to be fatal as there is no

automatic recovery mechanism and no way for hardware to tag a specific request or operation with the error. The error is

logged in a status bit for later diagnosis and an optional interrupt is generated (either fatal or non-fatal parity error).

The SR5650 implements a dedicated pin, DBG_GPIO0/SERR_FATAL#, to signal either a system or a fatal error, which

can be used to signal a BMC for further actions. SERR_FATAL# may be asserted on various error conditions like HT

Figure 2-6 Interrupt Routing Path in MSI Mode

Page 24

syncflood, as well as internal parity errors or fatal errors for which signalling by SERR_FATAL# is enabled. Fatal errors

are identified via the fatal error status bits.

Non-fatal or correctable errors may be likewise signalled via DBG_GPIO3/NON_FATAL_CORR#.

The SERR_FATAL# and NON_FATAL_CORR# pin functionalities are disabled on warm reset.

2.5.3 NMI# and SYNCFLOODIN#

The SR5650 may configure the DFT_GPIO0/NMI# pin as an input pin for triggering an upstream NMI packet to the

processor complex. The pin should be driven by a BMC. An internal sticky status bit records the use of the NMI# pin.

Also, the SR5650 may configure the DFT_GPIO5/SYNCFLOODIN# pin as an input pin for triggering a HyperTransport

syncflood event. The pin should driven by a BMC. An internal sticky status bit records the use of the SYNCFLOODIN#

pin.

2.5.4 Suggested Platform Level RAS Sideband Signal Connections

Figure 2-7 is a logical diagram showing suggestions for RAS sideband signal connections at the platform level .

RAS Features

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

2-8 Proprietary

Page 25

RAS Features

SR5650

BMC, SuperIO or other GPIO

source

SP5100

DBG_GPIO0/

SERR_FATAL#

DBG_GPIO3/

NON_FATAL_CORR#

Attach to a pin that can

generate SMI# like

USB_OC5#/IR_TX0/

GPM5#

DFT_GPIO0/NMI#

DFT_GPIO5/

SYNCFLOODIN#

Enable only after

reset. This is a pin-

strap sampled

shortly after

powergood

Enable signals

should default to

logic 0 on reset/

powergood

Add option to drive

SYNCFLOODIN#

pins on all SR5650s

in the system

SERR_FATAL# and

NON_FATAL_CORR#

from other SR5650s.

These are buffered to help

isolate the failing device.

S/W path to

trigger NMI#

pin

Enable only after

reset. This is a pin-

strap sampled

shortly after

powergood

PCIe

®

From NMI button and

MCARD_NMIBTN_L

OPMA pin

To

SYS_NMIBTN_L

OPMA pin

GPIO Expander

attached to OPMA

SMBus (either private

0 or private 1 SMBus

segments).

Alternately, this can

connect directly to a

BMC

SCL/SDA

Interrupt l ine to

Sys_SMBUS_IO_EXP_INTR_L

OPMA pin

Separate connections to

debug pins and GPIO

expander for each SR5650

in the system

NMI# only needs to

be connected on

the primary SR5650

Figure 2-7 Suggested Platform Level RAS Sideband Signal Connections

2.5.5 Error Reporting and Logging

2.5.5.1 PCI Error Logging

The SR5650 implements all PCI standard error logging bits for all on-board devices and functions including the host

bridge device, IOMMU, and PCI Express bridges.

2.5.5.2 PCIe

The SR5650 PCIe

®

Advanced Error Reporting

®

cores implement the optional Advanced Error Reporting (AER) feature mechanism in the PCI

Express 2.0 Base Specification. Errors are logged for received packet errors such as poisoned data, malformed TLP, and

etc. within the PCIe core and are accessible via the bridge configuration spaces.

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 2-9

Page 26

RAS Features

The ACS violations for ACS Source Validation and ACS Translation Blocking are recorded in the AER error log. Errors

due to IOMMU translation failures are not logged as ACS violations, but are logged as UR or CA depending on the error

type.

IOC may abort a non-posted request with UR status if it determines that the request will not hit system memory. Such

errors are pushed back into the PCIe core for logging. The IOC must abort potential peer-to-peer non-posted requests to

avoid a deadlock condition. For posted requests, the IOC can be configured to forward all non-decoded (non system

memory and non-peer-to-peer) posted requests up to the processor, which may abort the request and generate an MCA

error log.

For downstream completions with abort status coming back from the processor, error status is propagated to the endpoint

but no AER header information is logged in the chipset.

For upstream completions, error status is propagated up to the processor and AER information may be logged.

Table 2-2 lists the types of errors that are detectable by the SR5650 AER implementation. For details, see the PCI Express

2.0 Base Specification.

Table 2-2 Types of Errors Detectable by the SR5650 AER Implementation

Error Type Error Class

ACS Violation Uncorrectable – Fatal or Non-fatal

Unsupported Request Uncorrectable – Fatal or Non-fatal

Malformed TLP Uncorrectable – Fatal or Non-fatal

Unexpected Completion Uncorrectable – Fatal or Non-fatal

Completer Abort Uncorrectable – Fatal or Non-fatal

Completion Timeout Uncorrectable – Fatal or Non-fatal

Poisoned TLP Received Uncorrectable – Fatal or Non-fatal

Data Link Layer Protocol Error Uncorrectable – Fatal or Non-fatal

ECRC Error Uncorrectable – Fatal or Non-fatal

Replay Timeout Correctable

REPLAY_NUM Rollover Correctable

Bad DLLP Correctable

Bad TLP Correctable

The following error classes are NOT supported:

• Receiver Overflow Error

• Flow Control Error

• Surprise Down Error

• Receiver Error

2.5.5.3 IOMMU Error Reporting

The IOMMU specification defines a standard error logging facility that logs error events in system memory with register

status bits or interrupt notification to system software. The SR5650 fully supports the generation of logging events

following this standard.

2.5.5.4 HyperTransport™ Error Reporting

The HyperTransport specification defines various levels of error handling for link-related errors. The SR5650 supports

the detection of most error classes including protocol error, overflow error, and response error. The SR5650 also supports

notification of error conditions via fatal interrupts, non-fatal interrupts, or syncflood.

Table 2-3 lists the types of errors supported by the error handling capabilities of the SR5650 for HyperTransport.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

2-10 Proprietary

Page 27

RAS Features

Table 2-3 Types of HyperTransport™ Errors Supported by the SR5650

Error Type Description

Response Error Received incorrect response type such as tgtdone for read request, read response for flush, or size of

Overflow Error Flow-control buffer overflow in the receiver. This is only mapped to a fatal or non-fatal error in HT1

CRC Error Periodic CRC error

Retry Error Per-packet CRC error received

Retry Count Rollover Per-packet CRC error counter overflowed. Non-fatal interrupt only.

Protocol Error Protocol conditions detected in HT1 mode:

received data did not match size of requested data.

mode. In HT3 mode, this maps onto a retry in the hope that when the packet is subsequently received,

there is space in the FCB. No interrupt will be generated in HT3 mode.

• Data count not matching header

• Invalid command encoding

• Invalid CTL encoding

• Incomplete header

• Unexpected data

Protocol conditions detected in HT3 mode

• Data count not matching header

• Invalid command encoding

• Invalid CTL encoding

• Incomplete header

• Unexpected data

• Unexpected CRC

• Missing CRC

• Non-NOP inserted command

• Inserted command without inserted command CTL encoding

End of chain error is not supported, since the end of the chain is on PCI Express instead HyperTransport.

2.5.5.5 Internal Parity Error Reporting

One register bit per memory macro is used to log parity errors. Values for those bits are persistent across a warm reset for

diagnostic purposes.

2.5.6 Interrupt Generation on Errors

Internal interrupts may be generated on the following error conditions:

• PCI Express errors (fatal, non-fatal, or correctable)

• HT errors (fatal or non-fatal)

• IOMMU events

• Internal parity error (fatal or non-fatal)

• Internal parity error in the IOMMU cache (fatal, non-fatal, or correctable)

2.5.7 Poisoned Data Support

The SR5650 supports the propagation of poisoned data attributes (EP in PCIe and Data Error in HT) between PCI Express

endpoints and the processor for both host and DMA requests or responses. The SR5650 cannot actively mark a transaction

with a poisoned data attribute even if the transaction encounters an internal parity error. Received packets containing

ECRC errors are not marked as poisoned.

2.5.8 PCIe® Link Disable State

The SR5650 has the ability to put PCIe links into the disabled state as an error response in order to help stop data

movement within the system. Links which received fatal errors may be disabled. Also, a HyperTransport syncflood event

may be used to trigger all links to enter the disabled state.

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 2-11

Page 28

2.5.9 HT Syncflood Based on PCIe® Error

The SR5650 has the ability to put the HyperTransport link into the syncflood state when a fatal or non-fatal error is

received on the PCIe interface. This is done in order to help stop data movement within the system.

PCI

Express®

2.6 PCI Express

2.6.1 PCIe® Ports

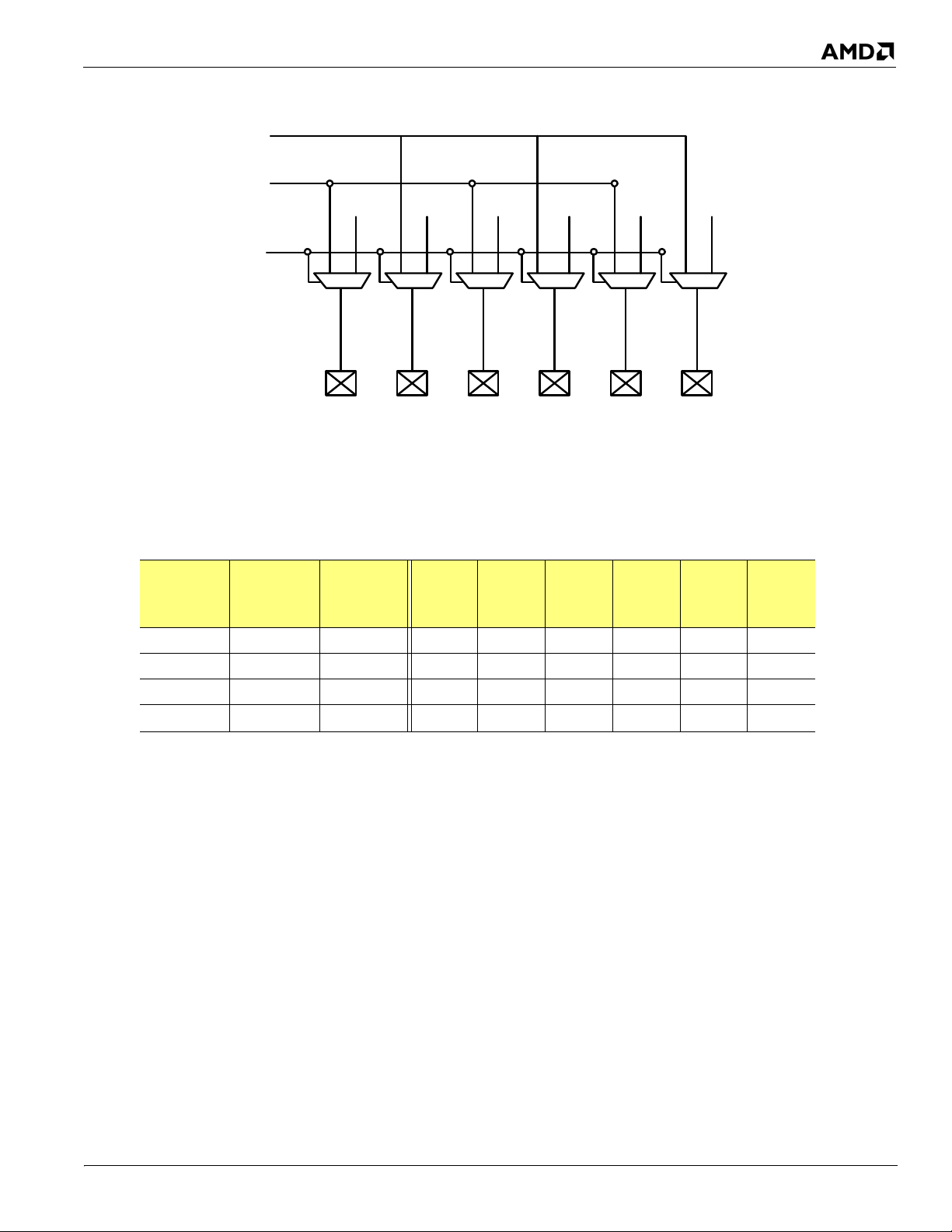

In total, there are 9 PCIe® ports on the SR5650, divided into 3 groups and implemented in hardware as 3 separate cores:

• PCIE-GPP1: 2 general purpose ports, 16 lanes in total. Width of each port is x8. In the default configuration, the 2

ports are combined to provide a 1 x16 port.

• PCIE-GPP3: 6 general purpose ports, with 6 lanes in total. They support 6 different configurations with respect to

link widths: 4:2, 4:1:1, 2:2:2, 2:2:1:1, 2:1:1:1:1, and 1:1:1:1:1:1 (default configuration). For details on the possible

configurations for the GPP3 lanes, see Table 2-4 below and .

Table 2-4 Possible Configurations for the PCI Express® General Purpose Links

PCIe Core Physical Lane Config. B Config. C Config. C2 Config. E Config. K Config. L

GPP3

• PCIE-SB: The Southbridge port provides a dedicated x4 link to the Southbridge (also referred to as the “A-Link

Express II interface”).

Each port supports the following PCIe functions:

®

GPP3 lane 0

GPP3 lane 1 x1

GPP3 lane 2

GPP3 lane 3 x1 x1

GPP3 lane 4

GPP3 lane 5 x1 x1 x1 x1

x4 x4

x2

x1

x2 x2 x2

x2

x2

x1

x1 x1 x1

x2

x1

x1

• PCIe Gen 1 link speeds

• ASPM L0s and L1 states

• ACPI power management

• Endpoint and root complex initiated dynamic link degradation

• Lane reversal

• Alternative Routing-ID Interpretation (ARI)

• Access Control Services (ACS)

• Advanced Error Reporting (AER)

• Address Translation Services (ATS)

2.6.2 PCIe® Reset Signals

Reset signals to PCIe slots, as well as embedded PCIe devices, must be controlled through one or more

software-controllable GPIO pins instead of the global system reset. It is recommended that unique GPIO pins be used for

each slot or device. The SR5650 has four GPIO pins that may be used for the purpose of driving reset signals

(PCIE_GPIO_RESET[5:4] and PCIE_GPIO_RESET[2:1]). Additional reset GPIO pins may be driven by

platform-specific means such as a super I/O or an I/O expander.

2.7 External Clock Chip

On the SR5650 platform, an external clock chip provides the CPU, PCI Express, and A-Link Express II reference clocks.

For requirements on the clock chip, please refer to the 800-Series IGP Express AMD Platform External Clock Generator

Requirements Specification for Server Platforms.

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

2-12 Proprietary

Page 29

Chapter 3

Pin Descriptions and Strap Options

This chapter gives the pin descriptions and the strap options for the SR5650. To jump to a topic of interest, use the

following list of hyperlinked cross references:

“Pin Assignment Top View” on page 3-2

“SR5650 Interface Block Diagram” on page 3-4

“CPU HyperTransport™ Interface” on page 3-4

“PCI Express® Interfaces” on page 3-5:

“PCI Express® Interface for General Purpose External Devices” on page 3-5

“A-Link Express II Interface to Southbridge” on page 3-5

“Miscellaneous PCI Express® Signals” on page 3-6

“Clock Interface” on page 3-6

“Power Management Pins” on page 3-6

“Miscellaneous Pins” on page 3-7

“Power Pins” on page 3-7

“Ground Pins” on page 3-9

“Strapping Options” on page 3-10

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 3-1

Page 30

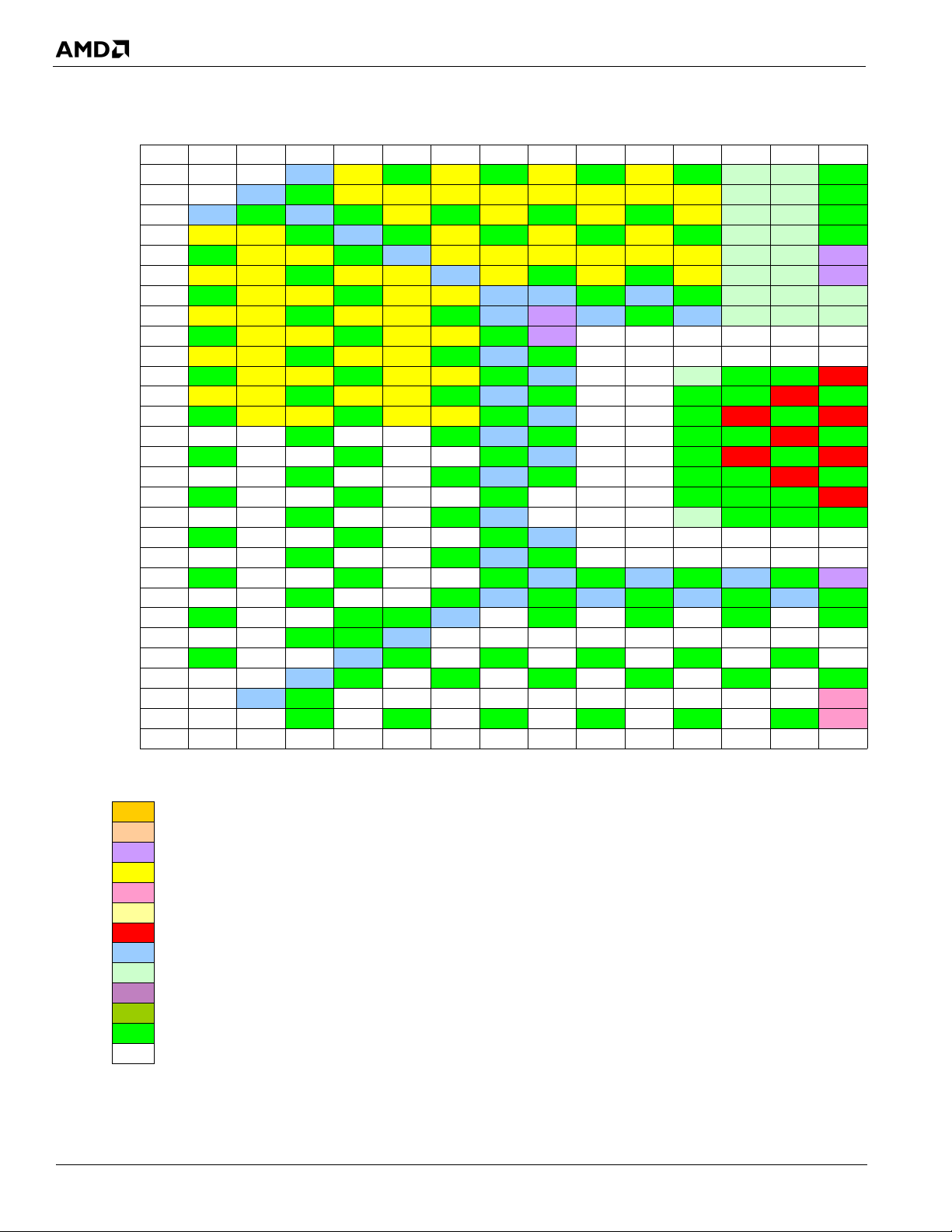

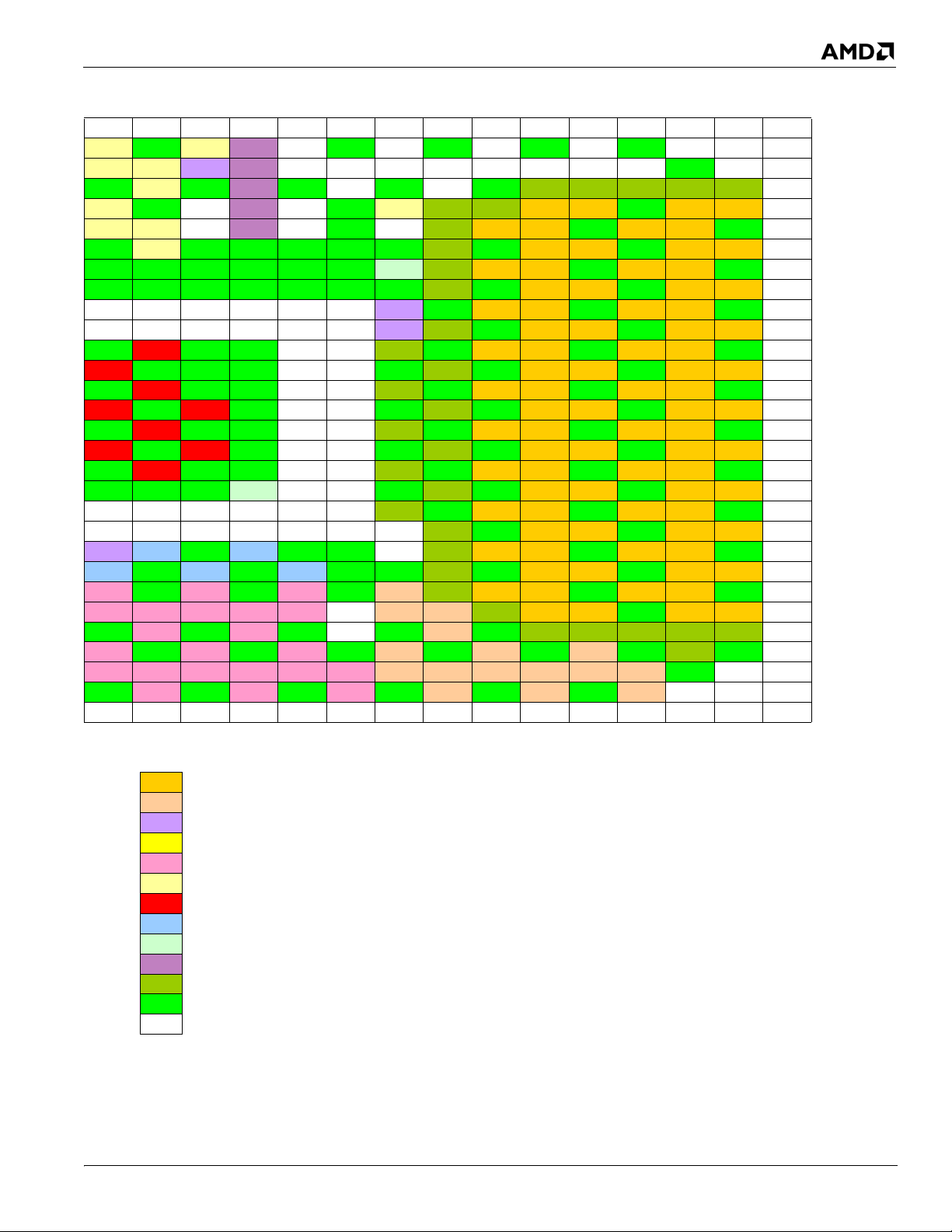

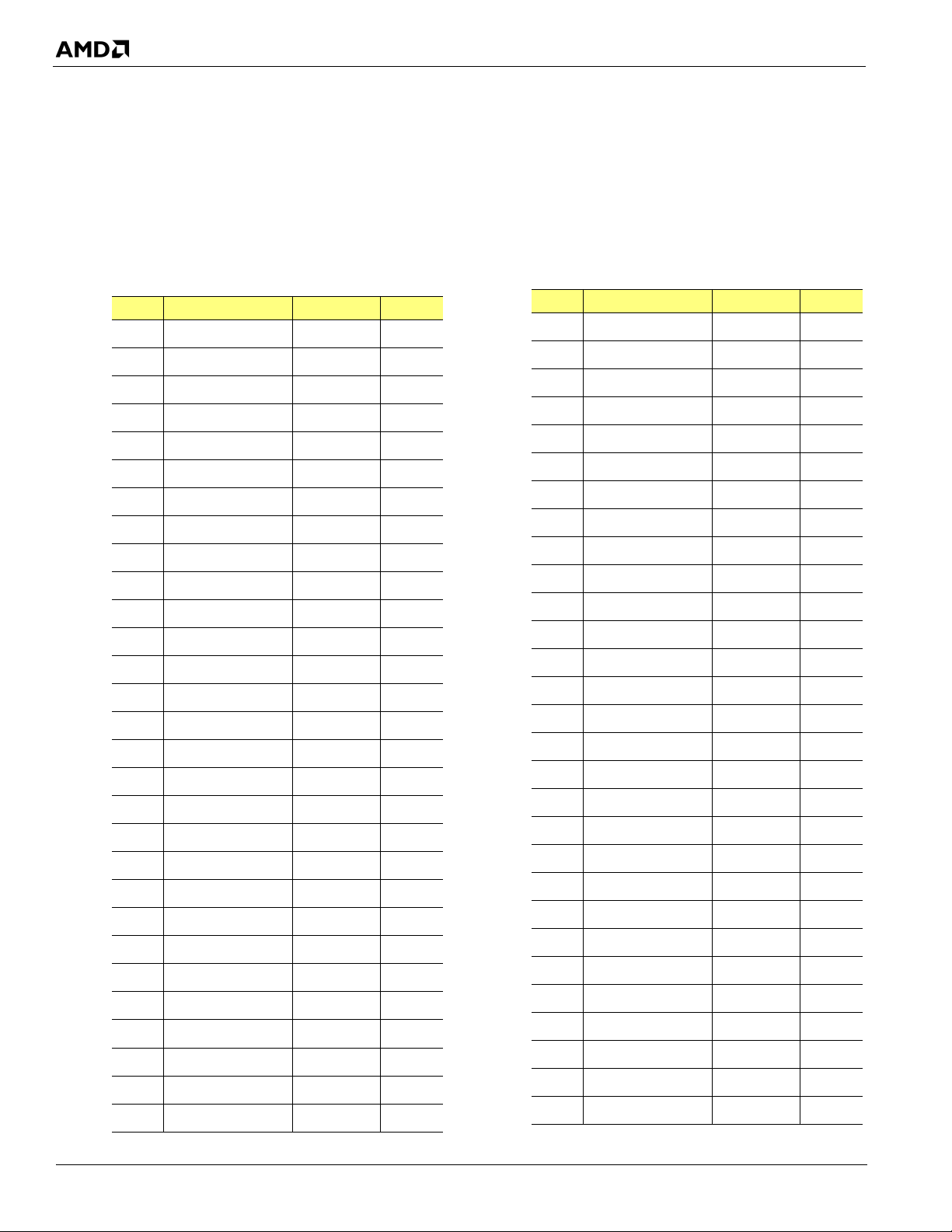

3.1 Pin Assignment Top View

1234567891011121314

A

B

C

VDDPCIE VSS VDDPCIE VSS GPP1_RX6N VSS GPP1_TX4N VSS GPP1_TX2N VSS GPP1_TX0N VDDA18PCIE VDDA18PCIE VSS

D

GPP1_RX7N GPP1_RX 7P VSS VDDPCIE VSS GPP1_RX5P VSS GP P1_RX3P VSS G PP1_RX1P VSS VDDA18PCIE VDDA18P CIE VSS

E

F

GPP1_TX8N GPP1_TX8P VSS GPP1_RX8N GPP1_RX8P VDDPCIE GPP1_RX4N VSS GPP1_RX2N VSS GPP1_RX0N VDDA18PCIE VDDA18PCIE PCE_TCALRP

G

H

GPP1_TX10N GPP1_TX10P VSS GPP1_RX10N GPP1_RX10P VSS VDDPCIE

J

GPP1_TX12N GPP1_TX12P VSS GPP1_RX12N GPP1_RX12P VSS VDDPCIE VSS

K

L

M

GPP1_TX14N GPP1_TX14P VSS GPP1_RX14N GPP1_RX14P VSS VDDPCIE VSS VSS VSS VDDC VS S

N

PNCNC

R

TNCNC

U

VNCNC

W

YNCNC

AA

AB NC NC

AC

AD NC NC

AE

AF NC NC

AG

AH

VDDPCIE VSS GPP1_TX6N GPP1_RX6P GPP1_TX5N GPP1_TX4P GPP1_TX3N GPP1_TX2P GPP1_TX1N GPP1_TX0P VDDA18PCIE VDD A18PCIE VSS

VSS GPP1_TX7N GPP1_TX7P VSS VDDPCIE GPP1_RX5N GPP1_R X4P GPP1_RX3N GP P1_RX2P GPP1_RX1N GPP1_RX0P VDDA18PCIE VDDA18PCIE PCE_TCALRN

VSS GPP1_TX9N GPP1_TX9P VSS GPP1_RX9N GP P1_RX9P VDDPCIE VDDPCIE VSS VDDPCIE VSS VD DA18PCIE VDDA18PCIE V DDA18PCIE

VSS GPP1_TX11N G PP1_TX11P VSS GPP1_RX11N GPP1_RX11P VSS

VSS GPP1_TX13N GPP1_TX13P VSS GPP1_RX13N GPP1_RX13P VSS VDDPCIE VDDA18PCIE VSS VSS VDDC

VSS GPP1_TX15N GPP1_TX15P VSS GPP1_RX15N GPP1_RX15P VSS VDDPCIE VSS VDDC VSS VDDC

VSS NC NC VSS NC NC VSS VDDPCIE VSS VDD C VSS VDDC

VSS NC NC VSS NC NC VSS NC VSS VSS VSS VDDC

VSS NC NC VSS NC NC VSS VDDPCIE

VSS NC NC VSS NC NC VSS VDDPCIE VSS VDDPCIE VSS VDDPCIE VSS

VSS NC NC VSS VSS VDDPCIE NC VSS NC VSS NC VSS NC VSS

VSS NC NC VDDPCIE VSS NC VSS NC VSS PCE_RCALRP VSS NC VSS NC

VDDPCIE VSSNCNCNCNCNCNCNCNCNCNCGPP3_TX5N

1234567891011121314

VDDPCIE GPP1_TX6P VSS GPP1_TX5P VSS GPP1_TX3P VSS GPP1_TX1P VSS VDDA18P CIE VDDA18PCIE VSS

VDDPCIE VSS NC VSS NC VSS NC VSS NC VSS NC VSS

Pin Assignment Top View

GPP1_REFCL

GPP1_REFCL

VSS NC NC VSS VDDPCIE VSS VSS VSS VDDC VSS

VSS NC NC VSS VDDPCIE VSS VSS VSS VDDC VSS

VSS NC NC VSS VDDPCIE NC VDDA18PCIE VSS VSS VSS

VSS NC NC VSS VDDPCIE VSS

VSS NC NC VSS VDDPCIE VSS VDDPCIE VSS VDDPCIE VSS VDDPCIE VSS

VSS VSS VDDPCIE NC NC NC NC PCE_RCALRN NC NC NC NC

VSS NC VSS NC VSS NC VSS NC VSS NC VSS GPP3_TX5P

VDDPCIE VSS VDDPCIE VDDA18PCIE VDDA18PCIE VDDA18PCIE

KN

KP

GPP3_REFCL

KN

CPU Interface

A-Link Express II Interface

Clock Interface

PCIe® GPP1 General Purpose Interface

PCIe GPP3 General Purpose Interface

Power Management Interface

Core Power

PCIe Main I/O Power

PCIe 1.8V I/O Power and PLL Power

GPIO 1.8V I/O Power

HyperTransport™ Interface Power

Grounds

Other

47062 SR5650 Databook 2.10 © 2011 Advanced Micro Devices, Inc.

3-2 Proprietary

Page 31

Pin Assignment Top View

15 16 17 18 19 20 21 22 23 24 25 26 27 28

PWM_GPIO4 VSS

PWM_GPIO2

SYSRESET# VSS

GPP3_REFCL

GPP3_RX5N VSS GPP3_RX3N VSS GPP3_R X1N VSS SB_RX3P VDDHT HT_RXCAD9N HT_RXCAD9P VSS HT_RXCAD1N HT_RXCAD1P VSS AC

GPP3_RX5P GPP3_RX4N GPP3_RX3P GPP3_RX2N GPP3_RX1P PCE_BCALRN SB_RX3N SB_RX2P VDDHT HT_RXCAD8N HT_RXCAD8P VSS HT_RXCAD0N HT_RXCAD0P AD

GPP3_TX4N VSS GPP3_TX2N VSS GPP3_TX0N VSS SB_ TX2P VSS SB_TX1P VSS SB_RX1P VSS VDDHT VSS AF

GPP3_TX4P GPP3_TX3N GPP3_TX2P GPP3_TX1N GPP 3_TX0P GPP3_RX0N SB_TX2N SB_TX3P SB_TX1N SB_TX0P SB_RX1N SB_RX0P VSS AG

PWM_GPIO6 OSCIN VDD18

VSS PWM_GPIO5 VSS VDD18 VSS I2C_DATA VSS

LDTSTOP# PWM_GPIO1

VSS PWM_GPIO3 VSS VSS VSS VSS VSS VDDHTTX VSS HT_TXCAD9P HT_TXCAD9N VSS HT_TXCAD1P HT_TXCAD1N F

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS VSS VDDHTTX VSS

VSS VDDC VSS VSS VDDHT VSS

VDDC VSS VSS VSS VSS VDDHT VSS

VSS VDDC VSS VSS VDDHT VSS

VDDC VSS VDDC VSS VSS VDDHT VSS HT_TXCTL1P HT_TXCTL1N VSS HT_TXCTL0P HT_TXCTL0N P

VSS VDDC VSS VSS VDDHT VSS HT_RXCTL1N HT_RXCTL1P VSS HT_RXCTL0N HT_RXCTL0P VSS R

VDDC VSS VDDC VSS VSS VDDHT VSS

VSS VDDC VSS VSS VDDHT VSS

VSS VSS VSS VDDA18PCIE VSS VDDHT VSS

KP

VDDPCIE VSS VDDPCIE VSS VDDPCIE VSS VSS VDDHT VSS

VSS GPP3_RX4P VSS GPP3_RX2P VSS PCE_BCALRP VSS SB_RX2N VSS VDDHT VDDHT VDDHT VDDHT VDDHT AE

VSS GPP 3_TX3P VSS GPP3_TX1P VSS GPP3_RX0P VSS SB_TX3N VSS SB_TX0N VSS SB_RX0N AH

15 16 17 18 19 20 21 22 23 24 25 26 27 28

POWERGOO

PCIE_RESET_

GPIO2

PCIE_RESET_

GPIO5

VDDPCIE VSS VDDPCIE VSS VSS

VDD18 TESTMODE VSS

D

VDD18

VDD18

PCIE_RESET_

GPIO1

PCIE_RESET_

GPIO3

PCIE_RESET_

GPIO4

DBG_GPIO3/

NON_FATAL_CO

I2C_CLK DBG_GPIO2 DBG_GPIO1 DFT_GPIO4 DFT_GPIO2 DFT_GPIO3

VSS

VSS STRP_DATA VDDHTTX HT_TXCAD8P HT_TXCAD8N VSS HT_TXCAD0P HT_TXCAD0N VSS E

RR#

DBG_GPIO0/S

ALLOW_LDTS

VDDA18HTPL

HT_REFCLKN VSS HT_TXCLK1 P HT_TXCLK1N VSS HT_TXCLK0P HT_TXCLK 0N VSS J

HT_REFCLKP VDDHT VSS

THERMALDIO

THERMALDIO

ERR_FATAL#

VDDHTTX VDDHTTX HT_RXCALN HT_RXCALP VSS HT_TXCALN HT_TXCALP D

TOP

VDDHTTX

L

VDDHT VSS

DE_P

DE_N

DFT_GPIO5/

SYNCFLOODIN

VSS

VSS VDDHTTX VDDHTTX VDDHTTX VDDHTTX VDDHTTX C

HT_TXCAD10PHT_TXCAD10

HT_TXCAD13PHT_TXCAD13

HT_TXCAD15PHT_TXCAD15

HT_RXCAD14NHT_RXCAD14

HT_RXCAD12NHT_RXCAD12

VDDHT VSS HT_RX CLK1N HT_RXCLK1P VSS HT_RXCLK0N HT_RXCLK0P Y

HT_RXCAD11NHT_RXCAD11

VDDHT

VSS DFT_GPIO1 VSS A

#

HT_TXCAD11PHT_TXCAD11

HT_TXCAD12PHT_TXCAD12

HT_TXCAD14PHT_TXCAD14

HT_RXCAD15NHT_RXCAD15

HT_RXCAD13NHT_RXCAD13

HT_RXCAD10NHT_RXCAD10

N

N

N

P

P

P

DFT_GPIO0/

NMI#

VSS HT_TXCAD2P HT_TXCAD2N VSS G

VSS HT_TXCAD3P HT_TXCAD3N H

N

VSS HT_TXCAD4P HT_TXCAD4N K

N

VSS HT_TXCAD5P HT_TXCAD5N VSS L

VSS HT_TXCAD6P HT_TXCAD6N M

N

VSS HT_TXCAD7P HT_TXCAD7N VSS N

VSS HT_RXCAD7N HT_RXCAD7P T

P

VSS HT_RXCAD6N HT_RXCAD6P VSS U

VSS HT_RXCAD5N HT_RXCAD5P V

P

VSS HT_RXCAD4N HT_RXCAD4P VSS W

VSS HT_RXCAD3N HT_RXCAD3P VSS AA

VSS HT_RXCAD2N HT_RXCAD2P AB

P

VSS B

CPU Interface

A-Link Express II Interface

Clock Interface

PCIe GPP1 General Purpose Interface

PCIe GPP3 General Purpose Interface

Power Management Interface

Core Power

PCIe Main I/O Power

PCIe 1.8V I/O Power and PLL Power

GPIO 1.8V I/O Power

HyperTransport Interface Power

Grounds

Other

© 2011 Advanced Micro Devices, Inc. 47062 SR5650 Databook 2.10

Proprietary 3-3

Page 32

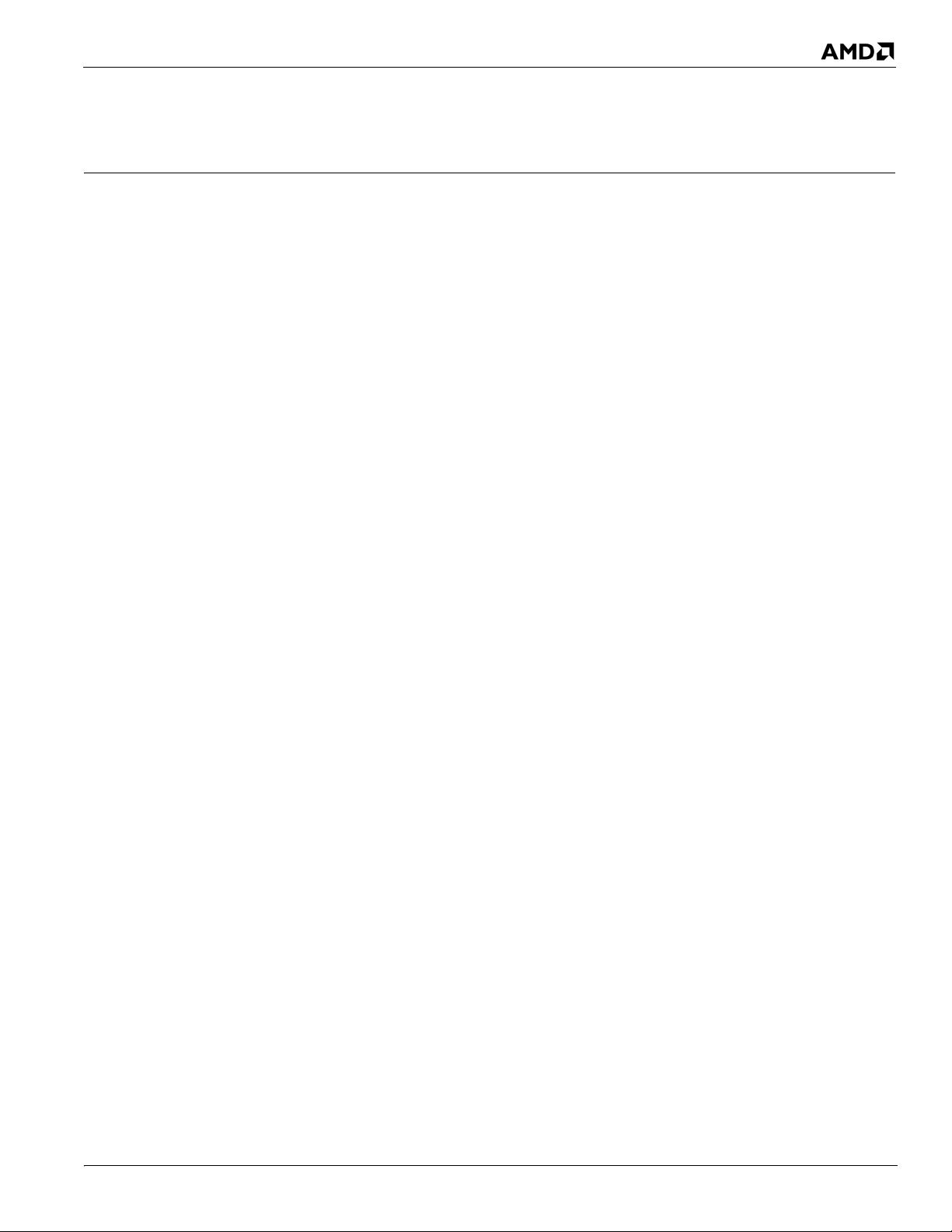

3.2 SR5650 Interface Block Diagram

HT_RXCAD[15:0]P, HT_RXCAD[15:0]N

HT_RXCLK[1:0]P, HT_RXCLK[1:0]N

HT_RXCTL[1:0]P, HT_RXCTL[1:0]N

HT_TXCTL[1:0]P, HT_TXCTL[1:0]N

HT_RXCALP, HT_RXCALN

HT_TXCALP, HT_TXCALN

HT_TXCLK[1:0]P, HT_TXCLK[1:0]N

HT_TXCAD[15:0]P, HT_TXCAD[15:0]N

SB_TX[3:0]P, SB_TX[3:0]N

SB_RX[3:0]P, SB_RX[3:0]N

OSCIN

SYSRESET#

POWERGOOD

VDDPCIE

VDD18

VDDC

HyperTransport™

Interface

A-Link Express

II Interface

Power

Management

Interface

Clock Interface

VDDHT

VDDA18HTPLL

PCIe® Interface

for General

Purpose

External

Devices

GPP3_TX[5:0]P, GPP3_TX[5:0]N

GPP3_RX[5:0]P, GPP3_RX[5:0]N

PCE_BCALRP, PCE_BCALRN

Misc. PCIe

Signals

HT_REFCLKP, HT_REFCLKN

LDTSTOP#

ALLOW_LDTSTOP

VSS

GPP1_TX[15:0]P, GPP1_TX[15:0]N

GPP1_RX[15:0]P, GPP1_RX[15:0]N

PCIE_RESET_GPIO[5:1]

VDDA18PCIE

GPP3_REFCLKP, GPP3_REFCLKN

GPP1_REFCLKP, GPP1_REFCLKN

PCE_RCALRP, PCE_RCALRN

PCE_TCALRP, PCE_TCALRN

VDDHTTX

TESTMODE

Misc. Signals

I2C_CLK

I2C_DATA

STRP_DATA

DFT_GPIO5/SYNCFLOODIN#

DBG_GPIO0/SERR_FATAL#

THERMALDIODE_P

THERMALDIODE_N

DFT_GPIO[4:1]

DFT_GPIO0/NMI#

DBG_GPIO[2:1]

DBG_GPIO3/NON_FATAL_CORR#

Power

Grounds

PWM_GPIO[6:1]

Figure 3-1 shows the different interfaces on the SR5650. Interface names in blue are hyperlinks to the corresponding

sections in this chapter.

SR5650 Interface Block Diagram

Figure 3-1 SR5650 Interface Block Diagram

3.3 CPU HyperTransport™ Interface

Table 3-1 HyperTransport™ Interface

Pin Name Type

HT_RXCAD[15:0]P,

HT_RXCAD[15:0]N

HT_RXCLK[1:0]P,

HT_RXCLK[1:0]N

HT_RXCTL[1:0]P,