AMD SP5100

BIOS Developer’s Gui de

Technical Reference M anu al

Rev. 3.01

PN: 44415_SP5100_bdg_pub_3.01

2011 Advanced Micro Devices, Inc.

Trademarks

AMD, the AMD Arrow logo, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

PCI Express and PCIe are registered trademarks of PCI-SIG.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their

respective companies.

Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD

makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication

and reserves the right to make changes to specifications and product descriptions at any time without notice. No license,

whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this

publication. Except for AMD products purchased directly from AMD pursuant to AMD's terms and conditions of sale and

then only as expressly set forth therin, AMD assumes no liability whatsoever, and disclaims any express or implied

warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a

particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for

surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in

which the failure of AMD's product could create a situation where personal injury, death, or severe property or

environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time

without notice.

.

©2011 Advanced Micro Devices, Inc.

Table of Contents

Table of Contents

1 Introduction ............................................................................................................. 7

1.1 About this Manual ........................................................................................................................... 7

1.2 Overview ........................................................................................................................................ 7

1.3 Block Diagram ................................................................................................................................ 7

1.4 Internal PCI Devices....................................................................................................................... 8

2 SP5100 Programming Ar chi t ectu re ....................................................................... 9

2.1 PCI Devices and Functions ............................................................................................................ 9

2.2 I/O Map ......................................................................................................................................... 11

2.2.1 Fixed I/O Address Ranges ................................................................................................................... 11

2.2.1.1 Fixed I/O Address Ranges – SP5100 Proprietary Ports ..................................................................................... 11

2.2.2 Variable I/O Decode Ranges................................................................................................................ 11

2.3 Memory Map ................................................................................................................................ 12

3 SP5100 Early-POST Initialization ......................................................................... 13

3.1 512K/1M ROM Enable ................................................................................................................. 13

3.1.1 PCI ROM .............................................................................................................................................. 13

3.1.2 LPC ROM ............................................................................................................................................. 13

3.1.3 LPC ROM Read/Write Protect .............................................................................................................. 13

3.1.4 SPI ROM Controller ............................................................................................................................. 14

3.2 Real Time Clock (RTC) ................................................................................................................ 15

3.2.1 RTC Access ......................................................................................................................................... 15

3.2.1.1 Special Locked Area in CMOS .......................................................................................................................... 15

3.2.1.2 Century Byte ..................................................................................................................................................... 15

3.2.1.3 Date Alarm ........................................................................................................................................................ 15

3.3 BIOS RAM .................................................................................................................................... 16

3.4 Serial IRQ ..................................................................................................................................... 16

3.5 SubSystem ID and SubSystem Vendor ID................................................................................... 17

3.6 AMD K8 Registers ........................................................................................................................ 17

3.7 System Restart after Power Fail .................................................................................................. 18

3.7.1 Power Fail and Alarm Setup................................................................................................................. 18

4 PCI IRQ Routing .................................................................................................... 19

4.1 PCI IRQ Routing Registers .......................................................................................................... 19

4.2 PCI IRQ BIOS Programming ........................................................................................................ 19

4.3 Integrated PCI Devices IRQ Routing ........................................................................................... 20

4.3.1 IRQ Routing for HD Audio .................................................................................................................... 20

4.4 PCI IRQ Routing for APIC Mode .................................................................................................. 21

5 SMBus Programming ............................................................................................ 22

5.1 SMBus I/O Base Address ............................................................................................................ 22

5.2 SMBus Timing .............................................................................................................................. 22

5.3 SMBus Host Controller Programming .......................................................................................... 23

6 IDE Controller ........................................................................................................ 25

6.1 PIO Modes ................................................................................................................................... 25

AMD SP5100 BIOS Developer ’s Guide Page 3

©2011 Advanced Micro Devices, Inc.

Table of Contents

6.1.1 PIO Mode ............................................................................................................................................. 25

6.1.2 PIO Timing ........................................................................................................................................... 25

6.2 DMA Modes .................................................................................................................................. 25

6.2.1 Legacy (Multi-Words) DMA mode ........................................................................................................ 25

6.2.2 Ultra-DMA Mo d e .................................................................................................................................. 26

7 USB Controllers ..................................................................................................... 27

7.1 Interrupt Routing for USB Controllers .......................................................................................... 27

8 Serial ATA (SATA) ................................................................................................. 28

8.1 SATA New Features..................................................................................................................... 29

8.2 Device ID ...................................................................................................................................... 31

8.3 SATA Controller Operating Modes ............................................................................................... 31

8.4 SATA Hot Plug ............................................................................................................................. 32

8.4.1 Sample Code ....................................................................................................................................... 32

9 Power Management ............................................................................................... 33

9.1 SMI Handling – EOS (PM IO Reg10h[Bit0]) ................................................................................ 33

9.2 Programmable I/Os ...................................................................................................................... 33

9.3 Power Management Timers ......................................................................................................... 34

9.3.1 PM Timer 1 (Inactivity Timer) ............................................................................................................... 34

9.3.2 PM Timer 2 (Activity Timer) .................................................................................................................. 34

9.4 SMI Events ................................................................................................................................... 35

9.4.1 Power Button ........................................................................................................................................ 36

9.5 C-State Break Events ................................................................................................................... 36

9.5.1 Break Events for C2 State .................................................................................................................... 36

9.5.2 Break Events for C3 and C4 States ..................................................................................................... 36

9.6 Save/Restore Sequence for S3 State .......................................................................................... 36

9.6.1 Register Save Sequence for S3 State .................................................................................................. 36

9.7 Wake on PCIe® ............................................................................................................................ 37

9.7.1 Legacy PCIe ......................................................................................................................................... 37

9.7.2 Native PCIe .......................................................................................................................................... 37

9.8 Sleep SMI Events ......................................................................................................................... 37

9.8.1 Sleep SMI Control Register .................................................................................................................. 37

9.8.2 Sleep SMI Programming Sequence ..................................................................................................... 38

9.8.2.1 Set Sleep SMI Control Register ......................................................................................................................... 38

9.8.2.2 Enter Sleep SMI# Routine ................................................................................................................................. 38

10 APIC Programming................................................................................................ 39

10.1 Northbridge APIC Enable ............................................................................................................. 39

10.2 Southbridge APIC En abl e ............................................................................................................ 39

10.3 IOAPIC Base Address .................................................................................................................. 39

10.4 APIC IRQ Assignment .................................................................................................................. 39

10.5 APIC IRQ Routing ........................................................................................................................ 40

11 Watchdog Timer .................................................................................................... 41

12 A-Link Bridge ......................................................................................................... 43

AMD SP5100 BIOS Developer ’s Guide Page 4

©2011 Advanced Micro Devices, Inc.

Table of Contents

12.1

Programming Procedure .............................................................................................................. 44

12.2 A-Link Express Configuration DMA Access ................................................................................. 45

12.3 Enable Non-Posted Memory Write for K8 Platform. .................................................................... 46

13 High Precision Event Timer (HPET) ..................................................................... 47

13.1 Initialization ................................................................................................................................... 47

13.1.1 Sample Initialization Code .................................................................................................................... 47

13.2 ACPI HPET Description Table ..................................................................................................... 48

13.3 HPET Support for Vista ................................................................................................................ 48

14 Workarounds ......................................................................................................... 49

14.1 Workaround for SMI Command Port Status Byte ........................................................................ 49

15 Sample Programs .................................................................................................. 51

15.1 IXP700 Register Initialization on Power-Up ................................................................................. 51

15.1.1 Initialization of PCI IRQ Routing before Resource Allocation ............................................................... 51

15.2 Setup Options ............................................................................................................................... 52

15.2.1 64 Bytes DMA ...................................................................................................................................... 52

15.2.2 USB Overcurrent Detection Disable ..................................................................................................... 52

15.2.3 C3 Support ........................................................................................................................................... 52

15.2.4 Subtractive Decoding for P2P Bridge ................................................................................................... 53

15.2.5 Enable/Disable On-Chip SATA ............................................................................................................ 54

15.2.6 Change Class ID for SATA................................................................................................................... 54

15.2.7 Disable AC97 Audio or MC97 Modem ................................................................................................. 56

15.2.8 Enable EHCI Controller ........................................................................................................................ 57

15.2.9 Enable OHCI Controller ....................................................................................................................... 59

15.3 IDE Settings ................................................................................................................................. 59

15.3.1 PIO Mode Settings ............................................................................................................................... 59

15.3.2 Multiword DMA Settings ....................................................................................................................... 61

15.3.3 UDMA Mode Settings ........................................................................................................................... 61

15.3.4 IDE Channel Disable ............................................................................................................................ 62

15.3.5 IDE Channel Enable ............................................................................................................................. 64

15.4 USB Controller Reset at Hard Reset ............................................................................................ 65

15.5 Clock Throttling ............................................................................................................................ 65

15.6 Lid Switch ..................................................................................................................................... 67

15.6.1 Lid Switch Hardware Connection ......................................................................................................... 67

15.6.2 Associated Registers ........................................................................................................................... 67

15.6.3 BIOS Initialization ................................................................................................................................. 67

15.6.4 ACPI Programming .............................................................................................................................. 68

15.7 SATA Hot Plug Sample Program ................................................................................................. 70

15.8 Temperature Limit Shutdown through SMI# ................................................................................ 75

15.8.1 Setting Up ITE 8712 Super I/O Registers ............................................................................................ 76

15.8.2 Initialize Southbridge Registers for SMI# ............................................................................................. 81

15.8.3 SMI Programming to Shut Down the System ....................................................................................... 82

15.9 Sleep Trap through SMI# ............................................................................................................. 83

15.9.1 Enable Sleep SMI# in ACPI ASL code ................................................................................................. 83

15.9.2 Sleep Trap SMI Routine ....................................................................................................................... 84

AMD SP5100 BIOS Developer ’s Guide Page 5

©2011 Advanced Micro Devices, Inc.

Table of Contents

15.10

HD Audio – Detection and Configuration ..................................................................................... 85

16 Chipset Integration Module Extensive (SB7xx CIMx) ......................................... 94

16.1 Introduction ................................................................................................................................... 94

16.2 Distribution Model ......................................................................................................................... 94

16.3 CIMx Architecture ......................................................................................................................... 94

16.4 Binary File .................................................................................................................................... 96

16.4.1 Overview .............................................................................................................................................. 96

16.4.2 Binary Header ...................................................................................................................................... 97

16.5 CIMx Interface Calls Environment ................................................................................................ 97

16.6 Interface Definition ....................................................................................................................... 97

16.6.1 Southbridge Power-On/R eset I nitia liz ation ........................................................................................... 97

16.6.2 SouthBridge BIOS Post Initialization .................................................................................................. 101

16.6.3 S3 Resume Initialization ..................................................................................................................... 110

16.7 Callback Interface Definition ...................................................................................................... 110

16.7.1 SATA OEM Call Back “SATA_PHY_PROGRAMMING” ..................................................................... 110

16.7.2 Integrated Pull-up and Pull-down Settings “PULL_UP_PULL_DOWN_SETTINGS” ............................. 111

16.8 SMM Functions Support ............................................................................................................. 111

16.9 Reference Code ......................................................................................................................... 112

Appendix: Revision History ...................................................................................... 113

AMD SP5100 BIOS Developer ’s Guide Page 6

©

1 Introduction

1.1 About this Manual

This manual provides guidelines for BIOS developers working with the AMD SP5100 (previously called

SB700S) Southbridge. It describes the BIOS and software modifications required to fully support the device.

Other documents on the SP5100 are available at AMD’s NDA website or from your AMD FAE representative.

Note: To help the reader to readily identify changes/updates in this document, changes/updates over the

previous revision are highlighted in red. Refer to Appendix: Revision History at the end of this document for a

detailed revision history.

1.2 Overview

AMD’s SP5100 Southbridge integrates the key I/O, communications, and audio features required in a stateof-the-art server into a single device. These products are specifically designed to operate with AMD’s

RADEON IGP Xpress family of integrated graphics processor products in server products.

1.3 Bl ock Diagram

This section contains a diagram for the SP5100. Figure 1 below shows the SP5100 intern al PCI de vices

and the major function blocks.

2011 Advanced Micro Devices, Inc.

AMD SP5100 BIOS Developers Guide Page 7

©2011 Advanced Micro Devices, Inc.

GPP_P/N (3:0)

LPC

LPC /FWH/SPI Rom interface

PCI Bridge

SMBUS /ACPI

AB

HD Audio

PORT 1 PORT 0

USB:OHCI(x5)

USB:EHCI(x2)

8250 TIMER

GPIO

RTC

ACPI / HW

Monitor

SMBUS

BUS Controler

APIC/ PIC

INTERRUPT

controller

SMI

SIRQ

PM

SPEAKER

GEVENT[7:0],SLPBUTTON

GPM [9:0]TEMPDEAD,

TEMPCAUT,

SHUTDOWN,DC_STOP#

SCIOUT,

SOFF#

INT# H:A

LDTRST#

RESET#

PWRGOOD

A-LINK

B-LINK

PICD[0]

RTC_IRQ#,

PIDE_INTRQ,

USB_IRQ#,

SATA_IRQ#,

AZ_IRQ#

X1/X2

12 USB2.0 + 2

USB1.1 PORTS

SERIRQ#

6 PCI SLOTS

LPC bus

SPI bus

Debug port

B-LINK A-LINK

Alink Express II

IMC

8051

IMC_INT

Clock Gen

CPU_NB_HT

NB Disp Clock

USB Clock

SIO Clock

SATA Clock

USB clock

Flash Cont Clock

CPU_HT_HT

PCIE_GFX_Clock

25MHz X1 / X2

Flash

Controller

SATA

Controller

6 PORTS(

GEN-II)

IDE

1 CHANNEL

FC interface

IDE interface

HD Link

ASF

SMBUS

Figure 1: SP5100 PCI Internal Devices and Major Function Blocks

1.4 Internal PCI Devices

Note: The SP5100 internal PCI devices are listed in Figur e 2 below. The sub-sections that f ollow provide

descriptions of the PCI configuration space, the I/O space, and the memory space registers for each device. PCI

configuration space registers are only accessible with configuration Read or configuration Write cycles and with

the target device selected by settling its corresponding IDSEL bit in the configuration cycle address field.

AMD SP5100 BIOS Developers Guide Page 8

©2011 Advanced Micro Devices, Inc.

LPC

PCI Bridge

Bus 0 DEV 20 Function 4

Device ID 4384h

SMBUS /ACPI

Bus 0 DEV 20 Function 0

AB

HD Audio

PORT 1

PORT 0

USB:OHCI(x5)

Bus 0 DEV 19 Function 0:4

Device ID 4387h : 4388h :

4389h : 438Ah : 438Bh

USB:EHCI(x2)

A-LINK

B-LINK

12 USB2.0 + 2

USB1.1 PORTS

6 PCI SLOTS

LPC bus

SPI bus

Debug port

B-LINK A-LINK

Alink Express II

IMC

8051

IMC_INT

Flash Controller

SATA Controller

IDE

HD Link

Bus 0 DEV 20 Function 1

Bus 0 DEV 20 Function 2

Bus 0 DEV 19 Function 0

Device ID 438Ch

Device ID 438Dh

Bus 0 DEV 20 Function 3

Device ID 4383h

Device ID 4385h

Device ID 4390h

Device ID 4391h

Device ID 4392h

Device ID 4393h

Device ID 4394h

Bus:Device:Function

Function Description

Dev ID

Enable/Disable

Figure 2: SP5100 PCI Internal Devices

2 SP5100 Programmi ng Archit ectur e

2.1 PCI De vic e s and Func t ions

AMD SP5100 BIOS Developers Guide Page 9

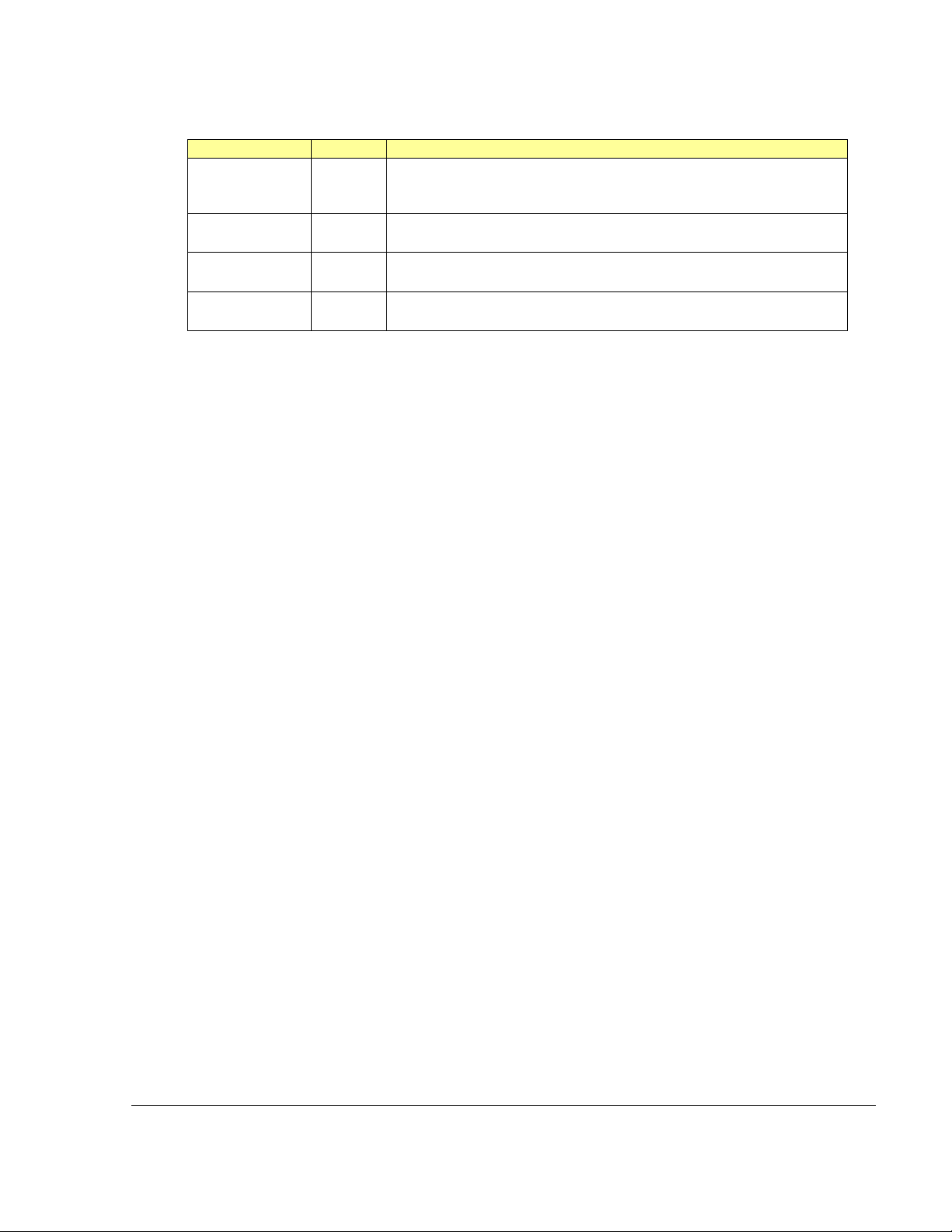

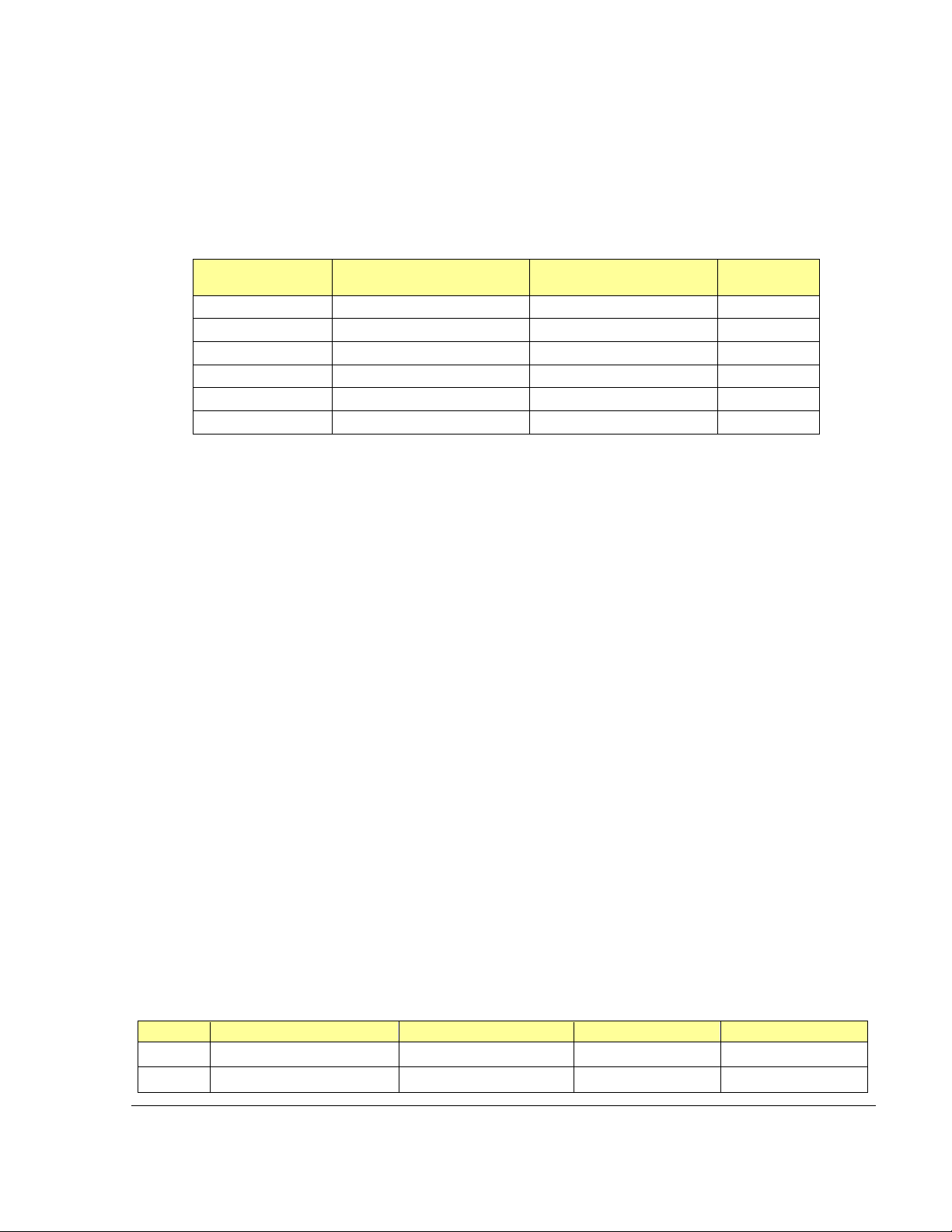

Bus 0:Device 14h:Function 0 SMBus Controller 4385h Always enabled

Bus 0:Device 14h:Function 1 IDE Controller 438Ch PM IO Reg59h[Bit3]

Bus 0:Device 14h:Function 2 Azalia Controller 4383h PM IO Reg59h[Bit3]

0: Disables flash controller and

enables ide controller

1: Enables flash controller and

disables ide controller

0: Disables Azalia

1: Enables Azailia

©2011 Advanced Micro Devices, Inc.

Bus 0:Device 14h:Function 3 LPC Controller 438Dh SMBus PCI Reg64h[Bit20]

0: Disables LPC controller

1: Enables LPC controller

Bus 0:Device 14h:Function 4 PCI to PCI Bridge 4384h Always enabled

Bus 0:Device 12h:Function 2

Bus 0:Device 13h:Function 2

Bus 0:Device 12h:Function 0

Bus 0:Device 12h:Function 1

Bus 0:Device 13h:Function 0

Bus 0:Device 13h:Function 1

Bus 0:Device 14h:Function 5

Bus 0:Device 11h:Function 0 Native/Legacy IDE Mode

USB #1EHCI Controller

USB #2EHCI Controller

USB #1 OHCI Controller #0

USB #1 OHCI Controller #1

USB #1 OHCI Controller #0

USB #1 OHCI Controller #1

USB #3 OHCI Controller

AHCI mode

Non-Raid-5 Mode

Raid5 Mode

AMD AHCI mode (uses AMD

AHCI drivers instead of MS

drivers)

4396h

4396h

4397h

4398h

4397h

4398h

438Bh

4390h

4391h

4392h

4393h

4394h

SMBus PCI Reg68h[Bit0]

SMBus PCI Reg68h[Bit4]

0: Enables EHCI controller

1: Disables EHCI controller

SMBus PCI Reg68h[Bit1]

SMBus PCI Reg68h[Bit2]

SMBus PCI Reg68h[Bit5]

SMBus PCI Reg68h[Bit6]

SMBus PCI Reg68h[Bit7]

0: Disables OHCI controller

1: Enables OHCI controller

SMBus PCI Reg ADh[bit 0]

0: Disables SATA controller

1: Enables SATA controller

AMD SP5100 BIOS Developers Guide Page 10

©2011 Advanced Micro Devices, Inc.

2.2 I/O Map

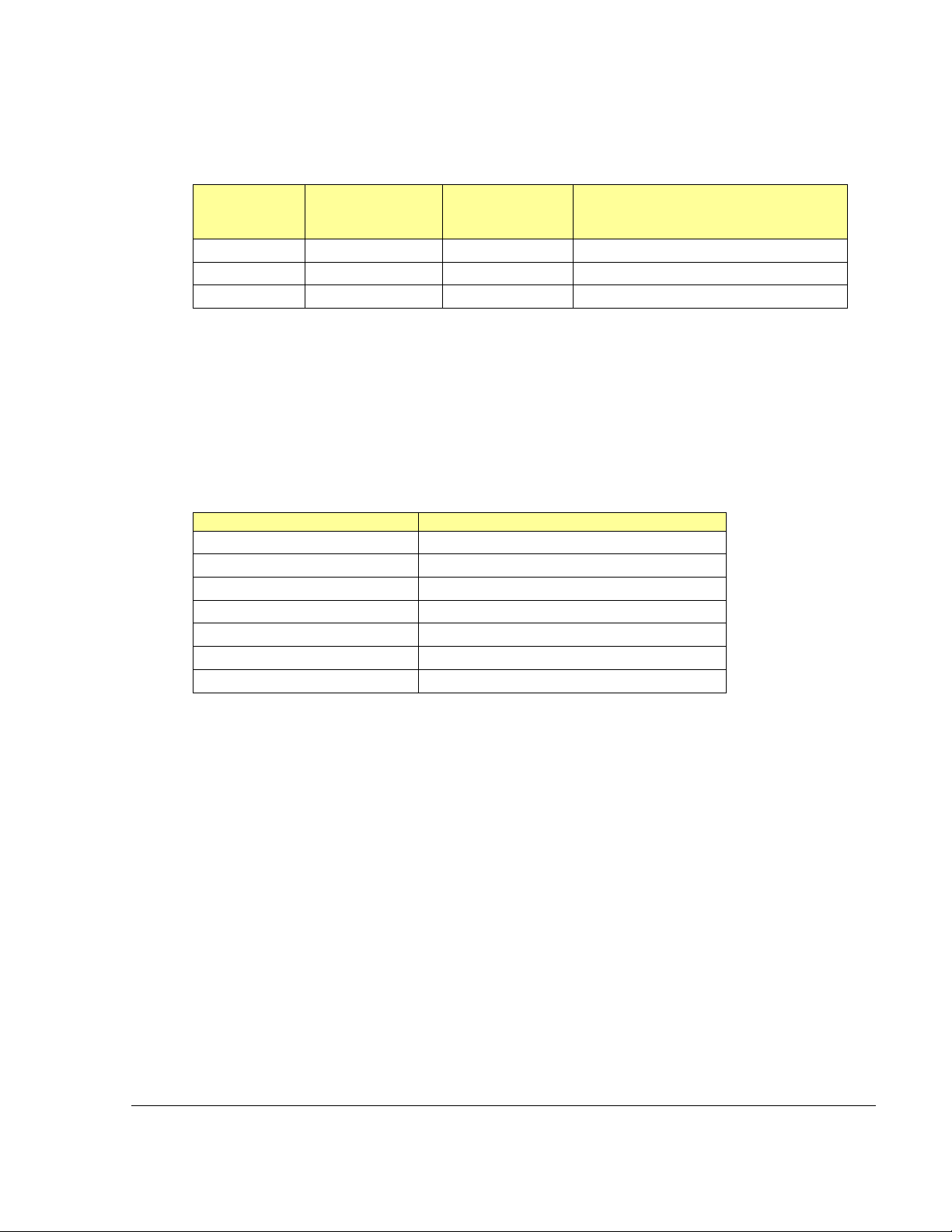

I/O Address

Description

Enable Bit

I/O Name

Description

Configure Register

Range Size

(Bytes)

The I/O map is divided into Fixed and Variable address ranges. Fixed ranges cannot be moved, but

can be disabled in some cases. Variable ranges are configurable.

2.2.1 Fixed I/O Address Ranges

2.2.1.1 Fixed I/O Address Ranges – SP5100 Proprietary Ports

C00h-C01h IRQ Routing Index/Data register SMBus PCI Reg64h[Bit0]

C14h PCI Error Control register SMBus PCI Reg78h[Bit4]

C50h-C51h Client Management Index /Data

registers

C52h Gpm Port SMBus PCI Reg78h[Bit6]

C6Fh Flash Rom Program Enable SMBus PCI Reg78h[Bit8]

CD0h-CD1h PM2 Index/Data

CD4h-CD5h BIOS RAM Index/Data

CD6h-CD7h Power Management I/O register SMBus PCI Reg64h[Bit2] & Reg78h[Bit9]

SMBus PCI Reg 79h[Bit3]

2.2.2 Variable I/O Decode Ranges

PIO0 Programmable I/O Range 0 PM IO Reg14h & Reg15h <=16

PIO1 Programmable I/O Range 1 PM IO Reg16H & Reg17H <=16

PIO2 Programmable I/O Range 2 PM IO Reg18h & Reg19h <=16

PIO3 Programmable I/O Range 3 PM IO Reg1Ah & Reg1Bh <=16

PIO4 Programmable I/O Range 4 PM IO Reg A0h & Reg A1h <=16

PIO5 Programmable I/O Range 5 PM IO Reg A2h & Reg A3h <=16

PIO6 Programmable I/O Range 6 PM IO Reg A4h & Reg A5h <=16

PIO7 Programmable I/O Range 7 PM IO Reg A6h & Reg A7h <=16

PM1_EVT ACPI PM1a_EVT_BLK PM IO Reg20h & Reg21h 4

PM1_CNT ACPI PM1a_CNT_BLK PM IO Reg22h & Reg23h 2

PM_TMR ACPI PM_TMR_BLK PM IO Reg24h & Reg25h 4

P_BLK ACPI P_BL K PM IO Reg26h & Reg27h 6

GPE0_EVT ACPI GPE0_EVT_BLK PM IO Reg28h & Reg29h 8

SMI CMD Block * SMI Command Block PM IO Reg2Ah & Reg2Bh 2

Pma Cnt Block PMa Control Block PM IO Reg2Ch & Reg2Dh 1

SMBus SMBus IO Space S MBus PCI Reg90h &

16

RegD2h[Bit0]

AMD SP5100 BIOS Developers Guide Page 11

©2011 Advanced Micro Devices, Inc.

Note:

Memory Range

Description

Enable Bit

• The SMI CMD Block must be word aligned, i.e., the least significant bit of the address

must be zero (address[0] must be 0). For example, B0h, B2h, B4h, B6h, B8h etc.

• The SMI CMD Block consists of two ports – the SMI Command Port at base address, and

the SMI Status Port at base address+1.

• The writes to SMI Status Port will not generate an SMI. The writes to the SMI Command

Port will generate an SMI.

• The SMI Command and SMI Status ports may be written individually as 8 bit ports, or

together as a 16-bit port.

2.3 Memory Map

0000 0000h-000D FFFFh

0010 0000h- TOM

000E 0000h-000F FFFFh Either PCI ROM or LPC

FFC0 0000h-FFC7 FFFFh

FF80 0000h-FF87 FFFFh

FFC8 0000h-FFCF FFFFh

FF88 0000h-FF8F FFFFh

FFD0 0000h-FFD7 FFFFh

FF90 0000h-FF97 FFFFh

FFD8 0000h-FFDF FFFFh

FF98 0000h-FF9F FFFFh

FFE0 0000h-FFE7 FFFFh

FFA0 0000h-FFA7 FFFFh

FFE8 0000h-FFEF FFFFh

FFA8 0000h-FFAF FFFFh

FFF0 0000h-FFF7 FFFFh

FFB0 0000h-FFB7 FFFFh

FFF8 0000h-FFFF FFFFh

FFB8 0000h-FFBF FFFFh

Main System Memory

ROM

FWH LPC Reg70h[3:0]

FWH LPC Reg70h[7:4]

FWH LPC Reg70h[11:8]

FWH LPC Reg70h[15:12]

FWH LPC Reg70h[19:16]

FWH LPC Reg70H[23:20]

FWH LPC Reg70h[27:24]

FWH LPC Reg70h[31:28]

PCI ROM : SMBus PCI Reg41h[Bit4]

LPC ROM : LPC Reg68h & LPC_Rom strap

AMD SP5100 BIOS Developers Guide Page 12

©2011 Advanced Micro Devices, Inc.

3 SP5100 Early-POST Initialization

256K ROM

(Default)

512K ROM

Setting

512K ROM

Setting

1 M ROM

Setting

The system BIOS needs to configure the SP5100 at the very beginning of POST. Some of the

settings will change depending on the OEM design, or on the newer revision chipset.

3.1 512K/1M ROM Enable

With the SP5100 design, there can be two possible ROM sources: PCI ROM and LPC ROM. Two pin

straps (UseLpcRom, FWHDisable) decide where the ROM is (see the SP5100 Databook). Upon

system power on, the SP5100 enables 256K ROM by default. The BIOS needs to enable 512K ROM

or up to 1M for LPC ROM, if required.

3.1.1 PCI ROM

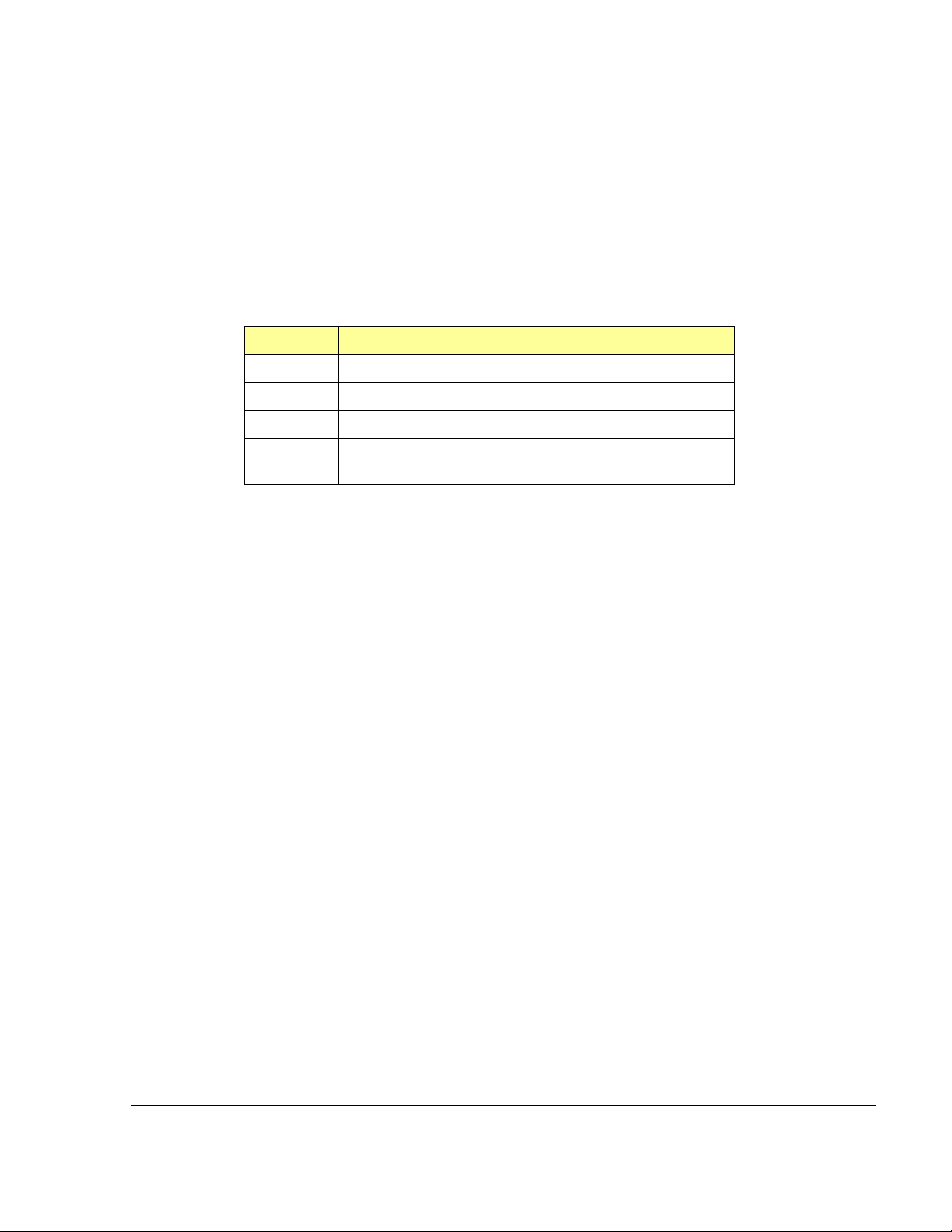

Control Bit Description

SMBus PCI Reg41h[Bit1] When set to 1, the address between FFF80000h

to FFFDFFFFh will be directed to the PCI ROM

interface.

SMBus PCI Reg41h[Bit4] When set to 1, the address between 0E0000h to

0EFFFFh will be directed to the PCI ROM

interface.

0 1

0 1

3.1.2 LPC ROM

To use the LPC ROM, the pin straps UseLpcRom, FWHDisable must be set accordingly.

Control Bit(s) Description Default

LPC PCI

Reg68h

LPC PCI Reg6Ch 16-bit starting & end address of the

LPC PCI

Reg48Hh[Bits4:3]

16-bit starting & end address of the

LPC ROM memory address range 1.

LPC ROM memory address range 2.

Enable bits for LPC ROM memory

address range 1 & 2.

Note: with pins straps set to LPC ROM,

these two bits have no effect on Reg68

& Reg6C.

000E0000h 000E0000h 000E0000h

FFFE0000h FFF80000h FFF00000h

00b 11b 11b

3.1.3 LPC ROM Read/Write Protect

The SP5100 allows all or a portion of the LPC ROM addressed by the firmware hub to be read

protected, write protected, or both read and write protected. Four dword registers are provided to

select up to 4 LPC ROM ranges for read or write protection. The ROM protection range is defined by

the base address and the length. The base address is aligned at a 2K boundary. The address length

can be from 1K to 256K in increments of 1K.

AMD SP5100 BIOS Developers Guide Page 13

©2011 Advanced Micro Devices, Inc.

Register 50h, 54h, 58h, 5ch of Device 14h, Function 3

Field Name

Bits

Description

Base Address 31:11 ROM Base address. The most significant 21 bits of the base address

are defined in this field. Bits 10:0 of the base address are assumed to

be zero. Base address, therefore, is aligned at a 2K boundary.

Length 10:2 These 9 bits (0-511) define the length from 1K to 512K in increments of

1K.

Read Protect 1 When set, the memory range defined by this register is read protected.

Reading any location in the range returns FFh.

Write Pr otect 0 When set, the memory range defined by this register is write protected.

Writing to the range has no effect.

Example:

Protect 32K LPC ROM starting with base address FFF80000.

Base address bits 31:11 1111 1111 1111 1000 0000 0 b

Length 32K bit 10:2 = 31h = 000 0111 11 b

Read protect bit 1 = 1

Write protect bit 0 = 1

Register 50h = 1111 1111 1111 1000 0000 0000 0111 1111 b = FFF8007F h

Note:

1. Registers 50h ~ 5Fh can be written once after the hardware reset. Subsequent writes to

them have no effect.

2. Setting sections of the LPC ROM to either read or write protect will not allow the ROM to

be updated by a flash programming utility. Most flash utilities write and verify ROM

sectors, and will terminate programming if verification fails due to read protect.

3.1.4 SPI ROM Controller

The SPI ROM interface is a new feature added to the SP5100. Refer to the AMD SP5100 Register

Reference Manual for more information on this feature.

Note: The LPC ROM Read/Write Protect mentioned in the previous paragraph also applies to SPI.

Two strap pins, PCICLK0 and PCICLK1, determine the SP5100 boot up from LPC ROM or SPI ROM.

There is no register status to reflect whether the current ROM interface is LPC or SPI.

AMD SP5100 BIOS Developers Guide Page 14

©2011 Advanced Micro Devices, Inc.

3.2 Real Time Clock (RTC)

RTCProtect- RW - 8 bits - [PCI_Reg: 6Ah]

Field Name

Bits

Default

Description

RTCProtect

0

0h

When set, RTC RAM index 38h:3Fh will be locked from

read/write. This bit can only be written once.

read/write. This bit can only be written once.

read/write. This bit can only be written once.

RTCProtect

3

0h

When set, RTC RAM index D0h:DFh will be locked from

read/write. This bit can only be written once.

RTCProtect

4

0h

When set, RTC RAM index C0h:CFh will be locked from

read/write. This bit can only be written once.

Reserved

7:5

0h

3.2.1 RTC Access

The internal RTC is div ided into two sections: the c lock and alarm function (registers 0 to 0Dh) , and

CMOS memory (registers 0Eh to FFh). T he clock and alarm func tions must be acces sed through I/O

ports 70h/71h. The CMOS memory (registers 0Eh to FFh) should be accessed through I/O ports

72h/73h.

3.2.1.1 Special Locked Area in CMOS

Some CMOS memory locations may be disabled for read/write. Register 6Ah of SMBus (Bus 0,

Device 14h, Function 0) ha s bits to d isab le these C M OS m emor y locations. T hes e bits can be wr itten

only once after each power up reset or PCI reset.

RTCProtect 1 0h When set, RTC RAM index F0h:FFh will be locked from

RTCProtect 2 0h When set, RTC RAM index E0h:EFh will be locked from

3.2.1.2 Century Byte

The RTC has a century byte at CMOS location 32h. Century is stored in a single byte and the BCD

format is used for the century (for example, 20h for the year 20xx). This byte is accessed using I/O

ports 70h and 71h. (The BIOS must set PMIO register 7Ch bit 4 to 1 to use this century byte at

CMOS location 32h

3.2.1.3 Date Alarm

The RTC has a date alarm byte. This byte is accessed as follows:

1. Set to 1 the RTC register 0Ah , bit 4, using I/O ports 70h and 71h.

2. Write Date Alarm in BCD to register 0Dh using I/O ports 70h and 71h.

3. Clear to 0 the RTC register 0Ah bit 4 using I/O ports 70h and 71h.

Note: It is important to clear RTC register 0Ah bit 4 to zero; otherwise, the CMOS memory may not be

accessed correctly from this point onward.

AMD SP5100 BIOS Developers Guide Page 15

©2011 Advanced Micro Devices, Inc.

3.3 BIOS RAM

Bits in SMBus

PCI Reg69

Power-on

Default

Recommended

Value

The SP5100 has 256 bytes of BIOS RAM. Data in this RAM is preserved until RSMRST# or S5 is

asserted, or until power is lost.

This RAM is accessed using index and data registers at CD4h/CD5h.

3.4 Serial IRQ

The SP5100 s upports seria l IRQ, which all ows one single si gnal to report m ultiple interru pt requests.

The SP5100 supports a m essage f or 21 serial interru pts , which inc lude 15 I RQs, SMI#, IOC HK#, a nd

4 PCI interrupts.

SMBus PCI Reg69h is used for setting serial IRQ.

Description

7 1 – Enables the serial IRQ function

0 – Disables the serial IRQ function

6 1 – Active (quiet) mode

0 – Continuous mode

5:2 Total number of serial IRQs = 17 +

NumSerIrqBits

0 – 17 serial IRQs (15 IRQs, SMI#,

IOCHK#)

1 – 18 serial IRQs (15 IRQs, SMI#,

IOCHK#, INTA#)

...

15 - 32 serial IRQ's

The SP5100 serial IRQ can support

15 IRQs, SMI#, IOCHK#, INTA#,

INTB#, INTC#, and INTD#.

1:0 Number of clocks in the start frame 0 00b

0 1

0 0

0 0100b

Note: T he BIOS s hou ld e nt er t he conti nuo us mode first when enabling the seri al I RQ pr otocol, s o th at

the SP5100 can generate the start frame.

AMD SP5100 BIOS Developers Guide Page 16

©2011 Advanced Micro Devices, Inc.

3.5 SubSystem ID and SubSystem Vendor ID

Register

Name

Default

Description

SubSytem ID and SubSystem Vendor ID can be programmed in various functions of SP5100 register

2Ch. These registers are write-once registers. For example, to program a SubSytem vendor ID of

1002h and SubSystem ID of 4341h in AC97 device 14h, function 5, use the following assembly

language sample code:

mov eax,8000A52Ch

mov dx,0CF8h

out dx,eax

mov dx,0CFCh

mov eax,43411002h

out dx,eax

3.6 AMD K8 Registers

The SP5100 is set for the AMD K8 processor by hardware strap. The following registers in the PM IO

space (accessed through index/data registers at CD6h/CD7h) are specific for the AMD K8 processor.

For the early post initialization these registers may be left at default values.

TM

SMAFx in the table below are sent with STPCLK messages down the HyperTransport

link.

PM IO 80h SMAF0 06h System Management Action for C2 and S4/S5

PM IO 81h SMAF1 21h System Management Action for VFID and C3

PM IO 82h SMAF2 43h System Management Action for S3 and S1

PM IO 83h SMAF3 55h System Management Action for thermal and normal

throttling.

PM IO 85h CF9Rst 00h Full reset/INIT

PM IO 86h Thermal Throttle

Control

PM IO 87h LdtStpCmd 00h Write bit[0] = 1 to generate C3

PM IO 88h LdtStartTime 00h LDTSTP# assertion delay in microseconds

PM IO 8Ah LdtAgpTimeCntl 00h LDTSTP# de-assertion delay select

PM IO 8Bh StutterTime 00h Stutter LDTSTP# duration in microse co nds

PM IO 8Ch StpClkDlyTime 00h STPCLK# assertion in microseconds

PM IO 8Dh AbPmeCntl 0Eh Fake A-link bridge PME

00h Enables time control for thermal throttling.

AMD SP5100 BIOS Developers Guide Page 17

©2011 Advanced Micro Devices, Inc.

3.7 System Restart after Power Fail

The system will remain off until the power button is pressed.

The way the system restarts following a power-fail/ power-restore cycle depends on the setting of

PMIO register 74h [bits 1:0].

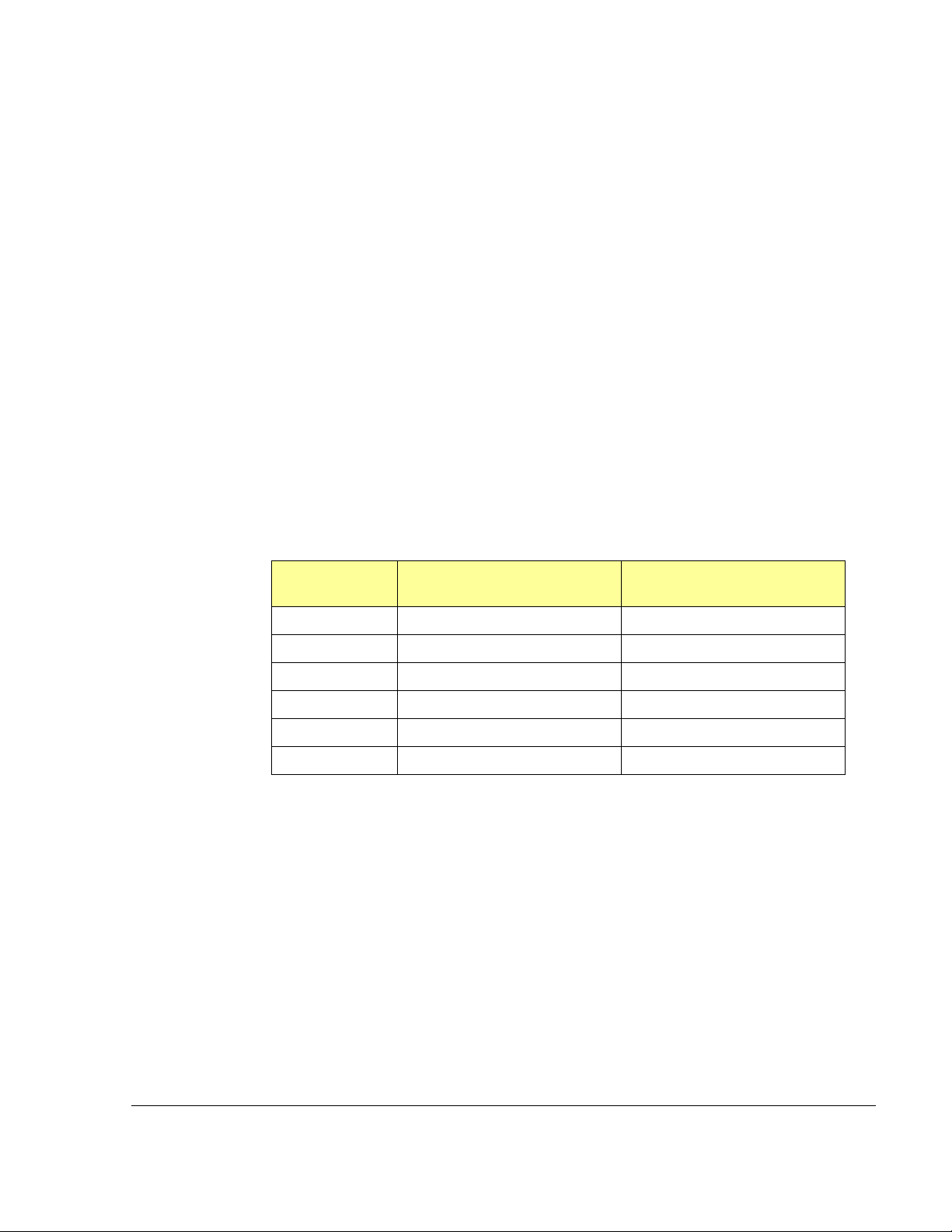

PMIO Register 74h bits[1:0] Description

00b or 10b

01b The system will always restart after the power is restored.

11b At power-up the system will either restart or remain off

depending on the state of the system at power failure. If the

system was on when the power failed, the system will restart

at power-up. If the system was off when the power failed, the

system will remain off after the power is restored. Pressing

the power button is required to restart the system.

Notes on programming the PMIO register 74h:

1. Bits[3:0] should be used for programming. Bits[7:4] are read-only bits and reflect the

same values as bits[3:0].

2. Bit 2 is used by the hardware to save the power on/off status. This bit should not be

modified during software/BIOS programming, however, its value should be restored

(effectively setting a value of ‘1’ as will be the case after every power up) upon every

access into this register. The BIOS programmer should always read PMIO register

74h, modify bit3 and bits[1:0] as required, and write back the PMIO register 74h.

3. PM_Reg:74h is initialized on every cold boot (G3->S5->S0 transition); however, it is

also required to restore the settings in bits [7, 5:4] to bits [3, 1:0] following any

SYS_RST# or RSMRST# assertion.

3.7.1 Power Fail and Alarm Setup

The state of the machine after the power-fail/power-restore cycle is controlled by PMIO register 74h

bits[1:0] as described above. This programming can be over-ridden for the special case when the

alarm is set. When both the alarm and the PMIO register 74h bit3 are set, the system will restart after

the power is restored, regardless of how register 74h bits [1:0] are defined.

AMD SP5100 BIOS Developers Guide Page 18

©2011 Advanced Micro Devices, Inc.

4 PCI IRQ Routing

Address

Register Name

Description

4.1 PCI IRQ Routing Registers

The SP5100 uses one pair of I/O ports to do the PCI IRQ routing. The ports are at C00h/C01h.

C00h PCI_Intr_Index PCI IRQ Routing Index

0 – INTA#

1 – INTB#

2 – INTC#

3 – INTD#

4 – SCI

5 – SMBus interrupt

9 – INTE#

0Ah – INTF#

0Bh – INTG#

0Ch – INTH#

C01h PCI_Intr_Data 0 ~ 1 5 : IRQ0 to IRQ15

IRQ0, 2, 8, 13 are reserved

4.2 PCI IRQ BIOS Programming

PCI IRQs are assigned to interrupt lines using I/O ports at C00h and C01h in index/data format. The

register C00h is used for index as written with index number 0 through 0Ch as described in section

4.1 above. Register C01h is written with the interrupt number as data.

The following assembly language example assigns INTB# line to interrupt 10 (0Ah).

mov dx,0C00h ; To write to IO port C00h

mov al,02h ; Index for PCI IRQ INTB# as defined in section 4.1

out dx,al ; Index is now set for INTB#

mov dx,0C01h ; To write interrupt number 10 (0Ah)

mov al,0Ah ; Data is interrupt number 10 (0Ah )

out dx,al ; Assign IRQB# to interrupt 10

AMD SP5100 BIOS Developers Guide Page 19

©2011 Advanced Micro Devices, Inc.

4.3 Int e grated PCI Devices IRQ Routing

Device

Reg3Dh of

PCI Device

PCI INT#

Description

In the SP5100, the AC’97 and USB need PCI IRQ. Internally, they are routed to different PCI INT#s.

Bus 0:Device 14h:Function 1 01 INTA# IDE Controller*

Bus 0:Device 14h: Function 2 01 Programmable** High Definition Audio

Bus 0:Device 14h: Function 5 03 Programmable*** USB #3 OHCI Controller

Bus 0:Device 12h:Function 0 01 Programmable*** USB #1 OHCI Controller #0

Bus 0:Device 12h:Function 1 01 Programmable*** USB #1 OHCI Controller #1

Bus 0:Device 12h:Function 2 02 Programmable*** USB #1 EHCI Controller

Bus 0:Device 13h: Function 0 01 Programmable*** USB #2 OHCI Controller #0

Bus 0:Device 13h: Function 1 01 Programmable*** USB #2 OHCI Controller #1

Bus 0:Device 13h: Function 2 02 Programmable*** USB #2 EHCI Controller

Bus 0:Device 11h:Function 0 01 Programmable**** SATA Controller #2

Notes:

* IDE controller needs PCI IRQ only if it is set to the native mode.

** Refer to section 4.3.1 for details.

***Refer to section 7.1 for details.

**** Smbus_pci_config 0xAF [4:2] for SATA Controller

4.3.1 IRQ Routing for HD Audio

Interrupt routing for device 14h, function 2 HD Audio is done through PCI SMBUS (device 14h,

function 0) register 63h. Values from INTA# to INTH# can be set in this register.

Sample Code: Set High Definition Audio interrupt routing to INTA#:

mov eax,8000A060h ; Device 14h, function 0, registers 60h-63h

mov dx,0CF8h ; PCI configuration Index register

out dx,eax ; Set to read/write registers 60h-63h

mov dx,0CFFh ; PCI configuration Data register for 63h

mov al,0 ; Set to INTA#

out dx,al ; Write to PCI register 63h

Note: The SP5100 has provisions to modify the interrupt pin register (PCI register 3Dh) for special

conditions. This pin is modified through device 14h, function 2, register 44h. Under normal

circumstances do not modify this register. The default is Pin 1.

AMD SP5100 BIOS Developers Guide Page 20

©2011 Advanced Micro Devices, Inc.

4.4 PCI IRQ Routing for APIC Mode

PCI IRQ

APIC Assignment

INTA# 16

INTB# 17

INTC# 18

INTD# 19

INTE# 20

INTF# 21

INTG# 22

INTH# 23

AMD SP5100 BIOS Developers Guide Page 21

©2011 Advanced Micro Devices, Inc.

5 SMBus Programming

The SP5100 SMBus (System Management Bus) complies with SMBus Specification Version 2.0.

5.1 SMBus I/O Base Address

The BIOS needs to set a valid SMBus I/O base address before enabling the SMBus Controller. The

SMBus I/0 base address should be set at PCI Reg90h in the SMBus Controller (Bus 0, Device 14h,

Function 0).

The SMBus controller enable bit is bit 0, register D2h, of the SMBus device (Bus 0, Device 14h,

Function 0).

The following is a sample code to enable the SMBus with a temporary I/O base address:

SMB_IO EQU 8040h

; Set SMBus I/O base address

mov dx, 0CF8h ; PCI Index Register

mov eax, 8000A090h ; Reg90h on SMBus PCI Control ler

out dx, eax

mov dx, 0CFCh ; PCI Data Register

mov eax, SMB_IO ; Temp SMBus I/O base address

out dx, eax

; Enable the SMBus controller

mov dx, 0CF8h ; PCI Index Register

mov eax, 8000A0D0h ; RegD0 on SMBus PCI Controller

out dx, eax

mov dx, 0CFEh ; PCI Data Register

in al, dx ; Read back from RegD2h

or al, 01 ; Bit [0] for enabling SMBus Controller interface

out dx, al

5.2 SM Bus Timing

The SMBus frequency can be adjusted using different values in an 8-bit I/O register at the SMBus

base + 0Eh location.

The SMBus frequency is set as follows:

SMBus Frequency = (Primary Alink Clock )/(Count in index 0Eh * 4)

The power-up default value in register 0Eh is A0h, therefore the default frequency is (66MHz)/(160 *

4), or approximately 103 KHz.

The minimum SMBus frequency can be set with the value FFh in the register at index 0Eh, which

yields the following: (66MHz)/(255*4) = 64.7 KH z.

AMD SP5100 BIOS Developers Guide Page 22

©2011 Advanced Micro Devices, Inc.

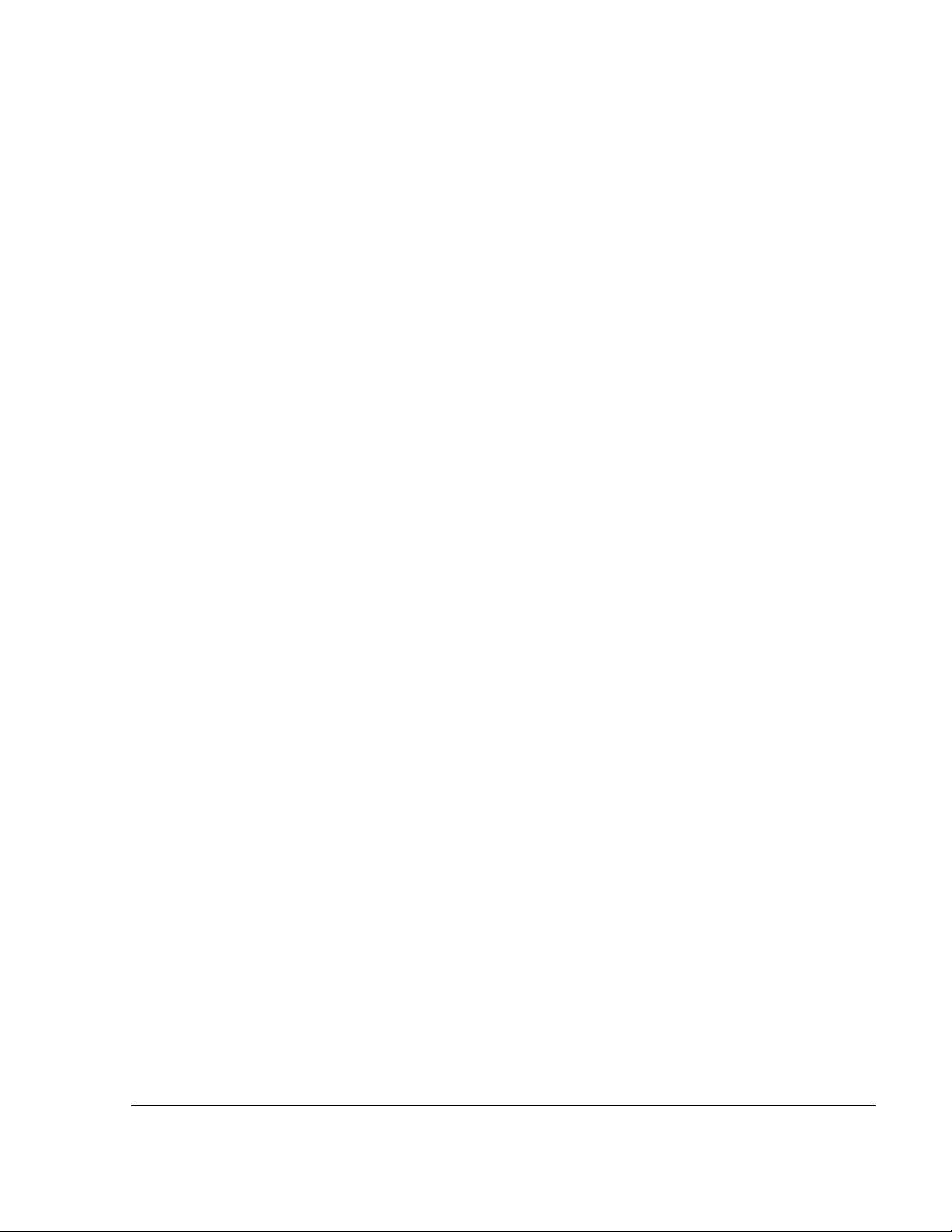

5.3 SM Bus Host Contr oller Programming

Step

Descriptions

Register in

Space

Comments

SMBus I/O

1 Wait until SMBus is idle. Reg00h[Bit0] 0 – Idle

1 – Busy

2 Clear SMBus status. Reg00h[Bit4:1] Write all 1’s to clear

3 Set SMBus command. Reg03h The command will go to SMBus device.

4 Set SMBus device address with

read/write protocol

5 Select SMBus protocol Reg02h[Bit4:2]

6 Do a read from Reg02 to reset

the counter if it’s going to be a

block read/write operation

7 Set low byte when write

command

8 Set high byte when write

command

9 Write the data when block write Reg07h Block write – write data one by one to it

10 Start SMBus command execution Reg02h[Bit6] Write 1 to start the command

11 Wait for host not busy Reg00h[Bit0]

12 Check status to see if there is any

error

13 Read data Reg05h Byte command – It is the read data

14 Read data Reg06h Word command – It is the high byte data

15 Read the data when block write Reg07h Block read – r ead data one by one.

The following flow chart illustrates the steps to program the SMBus host controller.

Reg04h Bit7:1 – address

Bit0 – 1 for read, 0 for write

Reg02h

Reg05h Byte command – It is the written data

Word command – It is the low byte data

Block command – It is block count

Others – Don’t care

Reg06h Word command – It is the high byte data

Others – Don’t care

Others – Don’t care

Reg00h[Bit4:2] With 1 in the bit, there is error

Word command – It is the low byte data

Block command – It is block count

Others – Don’t care

Others – Don’t care

Others – Don’t care

AMD SP5100 BIOS Developers Guide Page 23

©2011 Advanced Micro Devices, Inc.

AMD SP5100 BIOS Developers Guide Page 24

Figure 3: SMBus Host Controller Programming

©2011 Advanced Micro Devices, Inc.

6 IDE Controller

PIO

Command

(In Reg40h)

Recovery Width

The SP5100 IDE controller supports Ultra ATA 33/66/100/133 modes. The IDE controller can be

configured into either the compatible mode or the native mode. Under the compatible mode, the IDE

controller will use the legacy resourc es.

The SP5100 allows programming of the IDE timing and mode for each drive independently on each

channel.

6.1 PIO Modes

The SP5100 supports IDE PIO mode 0, 1, 2, 3, and 4. For PIO mode selection, the BIOS needs to

program not only the PIO mode register, but also the PIO timing register.

6.1.1 PIO Mode

The BIOS can simply give the PIO mode number through Reg4Ah on the IDE controller.

6.1.2 PIO Timing

Two parameters determine the PIO bus-cycle timing: the command width and the recovery width.

CT (bus-cycle timing) = 30ns * ((command width + 1) + (recovery width + 1))

For each PIO mode, the command width and the recovery width must be set by the BIOS

accordingly:

Mode

0 9 9 600ns = 30 * ((9+1) + (9+1))

1 4 7 390ns = 30 * ((4+1) + (7+1))

2 3 4 270ns = 30 * ((3+1) + (4+1))

3 2 2 180ns = 30 * ((2+1) + (2+1))

4 2 0 120ns = 30 * ((2+1) + (0+1))

Width

(In Reg40h) CT

6.2 DMA Modes

The SP5100 IDE controller can run at either the legacy (Multi-Words) DMA mode, or the Ultra-DMA

mode.

6.2.1 Legacy (Multi-Words) DMA mode

The SP5100 IDE controller will run at the legacy DMA mode only when the Ultra-DMA mode is

disabled.

Two parameters determine the DMA bus-cycle timing: the command width and the recovery width.

CT (bus-cycle timing) = 30ns * ((command width + 1) + (recovery width + 1))

AMD SP5100 BIOS Developers Guide Page 25

©2011 Advanced Micro Devices, Inc.

For each legacy DMA mode, the command width and recovery width must be set by the BIOS

Legacy DMA

Command

(In Reg44h)

Recovery

(In Reg44h)

UDMA Mode

Bus-Cycle Timing (ns)

accordingly:

Mode

0 7 7 480ns = 30 * ((7+1) + (7+1))

1 2 1 150ns = 30 * ((2+1) + (1+1))

2 2 0 120ns = 30 * ((2+1) + (0+1))

Width

Width

CT

6.2.2 Ultra-DMA Mod e

The SP5100 IDE controller supports UDMA mode 0, 1, 2, 3, 4, 5, and 6.

It only takes two simple steps to program the SP5100 IDE controller into the UDMA mode:

1. Set the mode number in UDMA mode register (Reg56h).

2. Enable the UDMA mode through the UDMA control register (Reg54h). The UDMA

bus-cycle timing is fixed after the UDMA mode is selected.

0 120

1 90

2 60

3 45

4 30

5 20

6 15

AMD SP5100 BIOS Developers Guide Page 26

©2011 Advanced Micro Devices, Inc.

7 USB Controllers

UsbIntMap - RW - 16 bits - [PCI_Reg: BEh]

Field Name

Bits

Default

Description

UsbInt1Map

2:0

000b

UsbInt1 interrupt mapping to PCI interrupt

UsbInt2Map

5:3

001b

UsbInt2 interrupt mapping to PCI interrupt

Reserved

7:6

UsbInt3Map

10:8

010b

UsbInt3 interrupt mapping to PCI interrupt

UsbInt4Map

13:11

011b

UsbInt4 interrupt mapping to PCI interrupt

Reserved

15:14

UsbIntMap register

Encoding:

EHCI (fun-2) – UsbInt4

Usb3AzIntMap- RW - 8 bits - [PCI_Reg: 63h]

Field Name

Bits

Default

Description

AzIntMap

2:0

110b

Interrupt routing table for HD Audio. Setting this register

circumstance

EcIRQ12En

3

Set to 1 to enable the IRQ12 coming from IMC

Usb3IntMap

6:4

010b

Interrupt routing table for USB3 (stand alone OHCI controller)

EcIRQ1En

7

Set to 1 to make IRQ1 comes from IMC

000 - INTA#, 001 - INTB#, 010 – INTC#, 011 - INTD#, 100 - INTE#, 101 - INTF#, 110 - INTG#, 111 - INTH#

7.1 Int e rrupt Routing for USB Controller s

Bus 0 Dev 14h Func 0 Reg 0BEh is used to program the interrupt routing for the usb controllers 1 &

2.

000 - INTA#, 001 - INTB#, 010 - INTC#, 011 - INTD#, 100 - INTE#, 101 - INTF#, 110 - INTG#, 111 - INTH#

The Interrupt mapping from USB controllers to Interrupt controller is as following,

USB1(device-18) : OHCI0(fun-0)/OHCI1(fun-1) – UsbInt1

EHCI (fun-2) – UsbInt2

USB2(device-19) : OHCI0(fun-0)/OHCI1(fun-1) – UsbInt3

Bus 0 Dev 14h Func 0 Reg 063h is used to program the interrupt routing for the standalone OHCI

controller (Bus 0 Dev 14h Func 5).

routes the HD audio’s interrupt to the specific PCI interrupt

before it is routed to the interrupt controller. In general

software should not need to reroute HDaudio interrupt. SW

only needs to do so for debugging purpose or special

AzIntMap register

Encoding:

AMD SP5100 BIOS Developers Guide Page 27

©2011 Advanced Micro Devices, Inc.

8 Serial ATA (SATA)

MiscSata - RW - 8 bits - [PCI_Reg: ADh]

Field Name

Bits

Default

Description

SATA Enable

0

1

SATA enable

SataSmbusEn

1

0

SATA SMBus enable

SataSmbusMode

2

0

SATA SMBus mode, set to 1 to put SATA I2C on GPIO pins

Enable

MiscSata register

The SP5100 has one SATA controller. The SATA devices are enabled/disabled through register ADh

in the SMBus controller (Device 14h, function 0).

SataPsvEn

5 1 SATA power saving enable

The SATA option ROM initial load size is 64KB, and the run time size is 50KB.

A SATA controller enable/disable sample code is found in section 14.2.5.

A SATA class ID change sample code is found in section 14.2.6.

AMD SP5100 BIOS Developers Guide Page 28

©2011 Advanced Micro Devices, Inc.

8.1 SATA New Features

Port Number

Primary , Secondary ,

SATA Drive Controlled by

Port 0

Primary master

SATA controller

Port 1

Secondary master

SATA controller

Port 2

Primary slave

SATA controller

Port 3

Secondary slave

SATA controller

Port 4

Primary (Secondary) master

PATA controller

Port 5

Primary (Secondary) slave

PATA controller

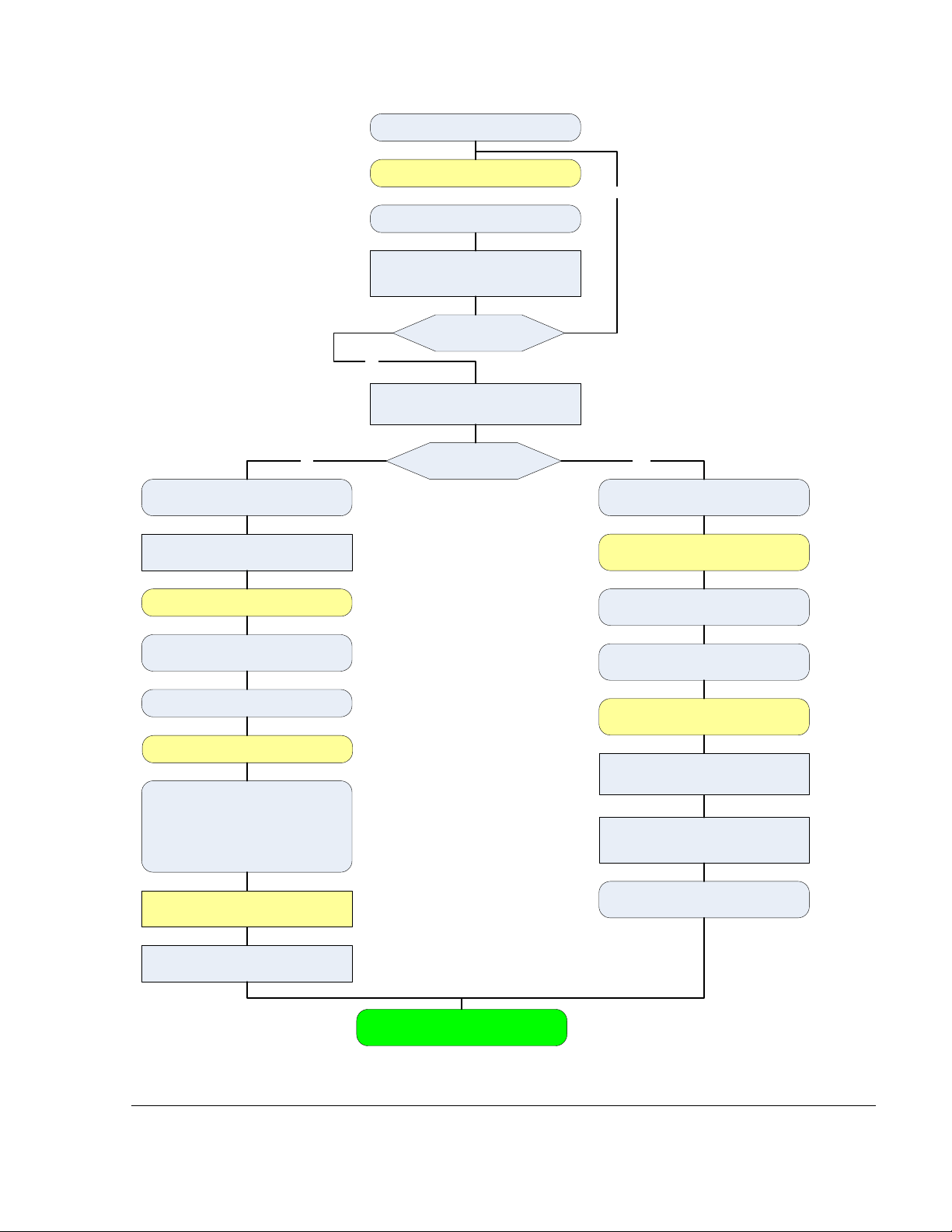

The SP5100 SATA controller compared to the previous generation southbridges

differs in two areas:

1. SATA Controller supports two additional ports providing a total of six SATA ports.

2. SATA controller supports a unique architecture that allo ws the user to configure

the SATA controller to work in-conjunction with the PATA controller to provide

configurations that cann ot be supported with SATA c ontroller alone. T his feature

is referred as “Combined Mode” in this document.

In the combined m ode, the SATA Contro ller can be c onfigured as either AHCI mode

or RAID mode and su pport up to f our (4) SAT A ports. Ports 0:3 are ass igned for this

configuration. The other two (2) SATA ports will be configured as PATA ports and

function in IDE mode. Two SATA ports (port 4 and port5) share one IDE channel

(could be either Primary or Secondary channel) from IDE (PATA) controller.

Alternatively, the SATA controller can be configured as IDE mode supporting up to six

IDE channels. In this conf iguration the SATA ports w ill be assigned to the Primar y /

Secondary channels as d efined in Table 1 below. The conf iguration for six IDE por ts

can also be achiev ed in two m odes sim ultaneous l y by usin g the com bined m ode. I.E.

Two IDE ports can be co nfigured to work in Legac y mode while the other f our ports

can be configured to work in Native or compatibility mode.

Table 1 SATA Port Assignment in Combined IDE Mode

Master / Slave Assignment

The following figures show the combined mode configurations:

AMD SP5100 BIOS Developers Guide Page 29

©2011 Advanced Micro Devices, Inc.

Note: In this mode the MS inbox driver will control all PATA drives showing all devices under

two physical IDE controllers.

AMD SP5100 BIOS Developers Guide Page 30

Fig 4: Combined Mode Configurations

©2011 Advanced Micro Devices, Inc.

8.2 Device ID

Device ID

Device

4390

SATA in IDE mode

4391

SATA in AHCI mode with Microsoft® driver

4392

SATA in RAID 0, 1, 10 mode

4394

AMD inbox AHCI support for Windows® 7 and Server

The SP5100 SATA will have different device IDs for different drivers, because they are totally

different devices from driver point of view. It’s not sufficient for OS to know whether to load

IDE, AHCI, or RAID driver. In non fresh installed condition, Windows

(vendor ID, device ID, sub-system ID, sub-vendor ID) first, and if they are matched, it will load

the driver. Window will not check sub-class code if 4-IDs are matched. This will cause blue

screen Windows XP when SATA RAID driver loaded, and SATA controller is in IDE mode, if

device ID is shared.

2008 R2

®

will match 4 IDs

8.3 SATA Controller Operating Modes

Whenever SATA is set to any IDE mode (native ide, legacy ide, ide->ahci, ide->hfs) and combined

mode is set to OFF, only 4 ports (0-3) can be supported by the SATA controller and other 2 ports (4-

5) cannot be used (it may work under OS but will not work under BIOS). IDE->Hyperflash mode is

intended only for driver testing and debugging. In IDE->Hyperflash mode, ports 1/3 will not work

under BIOS post and this is a limitation of hardware.

When combined mode is on, ports 4/5 will always be connected through PATA controller, meaning

any device connected to this port will be shown as PATA IDE device. For trevally reference board,

SATA port 4 is the one which is closest to CPU and port 5 is the one which has mobile sata

connector. For Shiner reference board, ports 4/5 are the two e-SATA ports.

Standalone mode was intended for debugging and bringup purposes only. Behind SATA mode will be

the official driver supported mode and all qualifications should be done in this mode.

AMD SP5100 BIOS Developers Guide Page 31

©2011 Advanced Micro Devices, Inc.

8.4 SATA Hot Plug

The SATA hot plug feature is implemented through the following registers:

1. ACPI GPE0 Block status register bit 31 for SCI status.

2. ACPI GPE0 Block enable register bit 31 for SCI enable.

3. PMIO register 37h bit 2 to trigger SATA hot plug SCI.

1 = Rising edge.

0 = Falling edge trigger.

4. The SATA internal status is set whenever a SATA hard drive is plugged in,

unplugged, powered up, or powered down. The status registers are:

Register BAR 5 + 10Ah, bit 0, for primary channel.

Register BAR 5 + 18Ah, bit 0, for secondary channel.

8.4.1 Sample Code

See section 14.7 for the SATA Hot Plug sample code.

AMD SP5100 BIOS Developers Guide Page 32

©2011 Advanced Micro Devices, Inc.

9 Power Management

I/O Name

Description

Configure Register

Range Size

(Bytes)

I/O Name

Description

Configure Register

Enable

Status

On the SP5100, PM registers can be accessed through I/O ports CD6h/CD7h. Before initiating any

power management functions in the SP5100, the BIOS needs to set the I/O base addresses for the

ACPI I/O register, the SMI Command Port, and the SpeedStep Control register (etc):

PM1_EVT ACPI PM1a_EVT_BLK PM IO Reg20h & Reg21h 4

PM1_CNT ACPI PM1a_CNT_BLK PM IO Reg22h & Reg23h 2

PM_TMR ACPI PM_TMR_BLK PM IO Reg24h & Reg25h 4

P_BLK ACPI P_BLK PM IO Reg26h & Reg27h 6

GPE0_EVT ACPI GPE0_EVT_BLK PM IO Reg28h & Reg29h 8

SMI CMD Bl ock * SMI Command Block PM IO Reg2Ah & Reg2Bh 2

Notes:

• The SMI CMD Block must be word aligned, i.e., the least significant bit of the address

must be zero (address[0] must be 0). For example, B0h, B2h, B4h, B6h, B8h etc.

• The SMI CMD Block consists of two ports – the SMI Command Port at base address, and

the SMI Status Port at base address+1. Note: For an IMC-enabled platform that uses

SMI Status Port at base address=1, word access should be used instead of byte access.

Refer to Section 14.1 ”Workaround for SMI Command Port Status Byte” on how to

program for byte access.

• The writes to the SMI Status Port will not generate an SMI. The writes to the SMI

Command Port will generate an SMI.

• The SMI Command and SMI Status ports may be written individually as 8 bit ports, or

together as a 16 bit port.

9.1 SMI Ha ndli ng – EOS (PM IO Reg10h[Bit0])

Upon each SMI generation, the SP5100 will clear the EOS bit automatically. At the end of the SMI

service, the BIOS needs to clear the status bit of the SMI event and re-enable the EO S; oth erw ise,

the SP5100 will not be able to generate SMI, even if SMI events arrive.

9.2 Pr ogrammable I/Os

There are eight sets of programmable I/Os available on the SP5100. The BIOS can use them for I/O

trapping, which means that an SMI will be generated if any access falls into the PIO range.

The PIO address range can be set to 2, 4, 8, and 16.

PIO0 Programmable I/O Range 0 PM IO Reg14h & Reg15h PM IO Reg1Ch[Bit7] PM IO Reg1Dh[Bit7]

PIO1 Programmable I/O Range 1 PM IO Reg16h & Reg17h PM IO Reg1Ch[Bit6] P M IO Reg1Dh[Bit6]

AMD SP5100 BIOS Developers Guide Page 33

©2011 Advanced Micro Devices, Inc.

I/O Name

Description

Configure Register

Enable

Status

PIO2 Programmable I/O Range 2 PM IO Reg18h & Reg19h PM IO Reg1Ch[Bit5] PM IO Reg1Dh[Bit5]

PM Timer1 Reloading On

Description

Enable

PIO3 Programmable I/O Range 3 PM IO Reg1Ah & Reg1Bh PM IO Reg1Ch[Bit4] PM IO Reg1Dh[Bit4]

PIO4 Programmable I/O Range 4 PM IO RegA0 & RegA1h PM IO Reg A8h[Bit0] PM IO RegA9h[Bit0]

PIO5 Programmable I/O Range 5 PM IO RegA2 & RegA3h PM IO Reg A8h[Bit1] PM IO RegA9h[Bit1]

PIO6 Programmable I/O Range 6 PM IO RegA4 & RegA5h PM IO Reg A8h[Bit2] PM IO RegA9h[Bit2]

PIO7 Programmable I/O Range 7 PM IO RegA6 & RegA7h PM IO Reg A8h[Bit3] PM IO RegA9h[Bit3]

Note: PM IO Reg04h[Bit7] is the overall control bit for enabling all the PIOs. The BIOS must set it before using any

PIO.

9.3 Power Management Timers

There are two PM timers available on the SP5100 – PM Timer 1 and PM Timer 2. The PM Timer 1

(Inactivity Timer) can be programmed to reload on some activities, but not the PM Timer 2 (Activity

Timer).

9.3.1 PM Timer 1 (Inactivity Timer)

The PM Timer 1 is a 6-bit timer with a granularity of 1 minute. The BIOS can set the initial value of the

PM Timer 1 through PM IO Reg0Bh. PM IO Reg0Ch will return the current value of the decrementing

counter.

The PM Timer 1 is typically used as a stand-by timer under the APM mode.

IRQ[15:8] IRQ[15:8] activity. PM IO Reg08h[Bit7:0]

IRQ[7:3], NMI, and IRQ[1:0] IRQ[7:3], NMI, and IRQ[1:0] activity PM IO Reg09h[Bit7:0]

Programmable IO Any access to PIO ports. PM IO Reg0Ah[Bit7]

Parallel Port Parallel ports activity PM IO Reg0Ah[Bit6]

Serial Port Serial Ports activity PM IO Reg0Ah[Bit5]

IDE Port IDE port activity PM IO Reg0Ah[Bit4]

Floppy Port Floppy port activity PM IO Reg0Ah[Bit3]

Game Port Game port (201H) activity PM IO Reg0Ah[Bit2]

ExtEvent1 Assert ExtEvent1 pin PM IO Reg0Ah[Bit1]

ExtEvent0 Assert ExtEvent0 pin PM IO Reg0Ah[Bit0]

9.3.2 PM Timer 2 (Activity Timer)

The PM Timer 2 is an 8-bit timer with a granularity of 500 μs. The BIOS can set the initial value of the

PM Timer 2 through PM IO Reg12h. PM IO Reg13h will return the current value of the decrementing

counter.

Note: The PM Timer 2 cannot be configured to reload on any system activities.

AMD SP5100 BIOS Developers Guide Page 34

©2011 Advanced Micro Devices, Inc.

9.4 SM I Events

SMI Source

Description

Enable

Status

The following is a list of all the SMI events available on the SP5100. The events can only generate

SMI, not SCI or wakeup events.

The global SMI disable bit is PM IO register 53h, bit [3].

PM IO register 53h bit [3] = 0 SMI# enabled (default)

PM IO register 53h bit [3] = 1 SMI# disabled (all events disabled)

Software SMI

(obsolete way)

Software SMI Any writing to SMI Command

PM Timer 1 Timeout on PM Timer 1.

PM Timer 2 Timeout on PM Timer 2.

IRQ[15:8] IRQ[15:8] activity. PM IO Reg02h[Bit7:0] PM IO Reg05h[Bit7:0]

IRQ[7:3], NMI, and

IRQ[1:0]

Programmable I/O Any access to PIO ports PM IO Reg04h[Bit7]

Parallel Port Parallel ports activity PM IO Reg04h[Bit6] PM IO Reg07h[Bit6]

Serial Port Serial Ports activity PM IO Reg04h[Bit5] PM IO Reg07h[Bit5]

IDE Port IDE port activity PM IO Reg04h[Bit4] PM IO Reg07h[Bit4]

Floppy Port Floppy port activity PM IO Reg04h[Bit3] PM IO Reg07h[Bit3]

Game Port Game port (201h) activity PM IO Reg04h[Bit2] PM IO Reg07h[Bit2]

ExtEvent1 Assert ExtEvent1 pin PM IO Reg04h[Bit1] PM IO Reg07h[Bit1]

ExtEvent0 Assert ExtEvent0 pin PM IO Reg04h[Bit0] PM IO Reg07h[Bit0]

Mouse/Keyboard Mouse/Keyboard port activity PM IO Reg1Ch[Bit3] PM I O Reg1Dh[Bit3]

Audio/MSS Audio/MSS port activity PM IO Reg1Ch[Bit2] PM IO Reg1Dh[Bit2]

MIDI MINI port activity PM IO Reg1Ch[Bit1] PM IO Reg1Dh[Bit1]

AD_LIB AD_LIB port activity PM IO Reg1Ch[Bit0] PM IO Reg1Dh[Bit0]

SERR# port System error to report parity

Global Release

Write

Temperature

Warning

Set SmiReq (PM IO

Reg00h[Bit4]) to generate SMI.

port.

Activity on PM IO register 08h,

09h, 0Ah will retrigger timer

(See section 9.3.2)

IRQ[7:3], NMI, and IRQ[1:0]

activity

errors or special cycle command

or other catastrophic system

errors.

OS write to PM1 Control register PM IO 0Eh[Bit 0] PM IO 0Fh[Bit0]

C50/C51, index 03,

Always PM IO Reg01h[Bit4]

PM IO Reg0Eh[Bit2] PM IO Reg0Fh[Bit2]

PM IO Reg00h[Bit1] PM IO Reg01h[Bit1]

PM IO Reg00h[Bit2] PM IO Reg01h[Bit2]

PM IO Reg03h[Bit7:0] P M IO Reg06h[Bit7:0]

PM IO Reg1Dh[Bit7:4]

AND

PM IO Reg1Ch[Bit7:4]

PCI SMBus Reg 66h,

bit[0]

[bit1]

PCI SMBus reg 04h, bit

[30].

PM IO reg 0Fh[Bit 1]

C50/C51, index 02,

[bit1]

AMD SP5100 BIOS Developers Guide Page 35

©2011 Advanced Micro Devices, Inc.

9.4.1 Power Button

Power button is always a wake-up event and can be programmed as an SCI wake-up event. The

power button status register is AcpiPmEvtBlk, bit[8]. The BIOS must make sure this bit is cleared prior

to the entry into any C or S states.

In addition, when the power button is pressed for 4 seconds, the SP5100 will shut do wn the entir e

system (by going to S5). No programming is required for this function.

9.5 C-State Break Events

9.5.1 Break Events for C2 State

Under C2 the break events are as follows:

• PBE#

• Special_message from CPU (K8 mode)

• I/O write to special register (K8 mode)

• SMI#

• NMI

• INIT

• Interrupts (in PIC mode only)

9.5.2 Break Events for C3 and C4 States

All of the events listed (above) as break events in C2 state are also break events in C3 and C4 states.

In addition, the Bus Master Status is also a break event in C3 and C4 states.

9.6 Save/Restore Sequence for S3 State

9.6.1 Register Save Sequence for S3 State

Prior to initiating S3 states, the BIOS must save the registers on the machine. The BIOS reserves a

section of the memory and a section of the CMOS to save the registers. Depending on the BIOS

architecture, these registers may be saved either one time just prior to handing of the control over to

the OS, or every time just before going into the S3 states.

The following registers must be saved:

• Some Northbridge registers in CMOS

• Some Northbridge and Memory Controller registers

• Southbridge PCI registers on the SP5100

• Southbridge non-PCI registers

• PCI registers not on the SP5100

• Super I/O and other I/O registers.

The BIOS typically sets aside an area in the memory to save the registers prior to the S3 state. The

Southbridge registers may be saved in any order as long as those registers are visible to the BIO S .

AMD SP5100 BIOS Developers Guide Page 36

©2011 Advanced Micro Devices, Inc.

Some of the registers, such as SubSystem ID and SubSystem Vendor ID, may be saved, but written

only once as dword. They are handled separately during restore.

9.7 Wake on PCIe®

9.7.1 Legacy PCIe

On SP5100, GPE event 18 will be used to track the PCIe wake up event (refer to SP5100 RRG

section 2.4.3.3 ACPI Registers, AcpiGpe0Blk:00[18] – PCIePmeStatus). Platform BIOS should follow

ACPI specification to implement the corresponding event handler (GPE._L12).

9.7.2 Native PCIe

Platform BIOS informs OSPM of its capability of supporting native PCIe by defining the control

method OSC (Operating System Capabilities). In the control field passed via Capabilities Buffer,

when PCIe Native Power Management Events Control bit (bit 2) is set by OS, OSC should enable

PCIe native mode on SP5100 by setting the following registers:

• PMIO:0x55[3] = 1 // PcieNative – This enables PCIe native PME mode support (sending

PCIePme and Ack message)

• PMIO:0x55[4] = 1 // Pcie_Wak_Mask – This masks out wake event from PCIe devices

• PMIO:0x10[6] = 1 // PciExpWakeDisEn – When set to 1, PciExpWakeDis

(AcpiPmevtBlk:0x02[14] becomes visible

As a reference, SP5100 CIMx also provides a sample OSC implementation as ASL reference code

(ASL\PCI0_OSC.ASL).

9.8 Sleep SMI Events

These events provide an SMI# before the system transits to an SX state (e.g. ACPI S1 , S2, S3,

S4, and S5). This feature helps t he S ystem BIOS to develop software workarounds or

debugging routines before the system goes to sleep state.

9.8.1 Sleep SMI Control Register

There is a Sleep SMI control register in the SP5100. Its base I/O address is defined at PMIO Reg

0x04.

SLP_SMI_EN is a R/W register bit for controlling a Sleep SMI when the system transits to an ACPI

SX state. The register definition is as follows:

• SLP_SMI_EN [Bit7] = 0, Disables Sleep SMI event.

• SLP_SMI_EN [Bit7] = 1, Enables Sleep SMI event.

There is a Sleep SMI Statu s register in the SP5100. Its base I/O address is defined at PMIO Reg

0x07.

SLP_SMI_Status [Bit7] is asserted when the system goes to an ACPI SX state, and when

SLP_SMI_EN is set to enable.

AMD SP5100 BIOS Developers Guide Page 37

©2011 Advanced Micro Devices, Inc.

9.8.2 Sleep SMI Programming Sequence

9.8.2.1 Set Sleep SMI Control Register

The Sleep SMI Control Register does not necessary have to be enabled before the system goes to

the ACPI SX state. One may enable the control the bit in the ACPI ASL code. Please refer to section

14.9 “Sleep Trap Through SMI#” for the sample code.

9.8.2.2 Enter Sleep SMI# Routine

The system does not go into the sleep state (set by ACPI PM1_CNT) when SMI# is asserted. The

System BIOS has to follow the sequence below:

1. Disable Sleep SMI Control register (SLP _S MI_ EN) .

2. Software workaround or system BIOS debugging routing implementation.

3. Write SLP_SMI_Status 1 to clear this event.

4. Rewrite sleep command to ACPI register (ACPI PM1_CNT).

5. RSM if necessary.

AMD SP5100 BIOS Developers Guide Page 38

©2011 Advanced Micro Devices, Inc.

10 APIC Programming

With the AMD integrated chipset solution, the BIOS needs to program both the Northbridge and the

Southbridge in order to support APIC.

10.1 Northbridge APIC Enable

There are three bits in the Northbridge that the BIOS should set before enabling APIC support.

For RS480/RS690:

• Enable Local APIC in K8. (Set bit11 in APIC_BASE MSR(001B) register.)

• Reg4C[bit1] - This bit should be set to enable. It forces the CPU request with address

0xFECx_xxxx to the Southbridge.

• Reg4C[bit18] - This bit should be set to enable. It sets the Northbridge to accept MSI

with address 0xFEEx_xxxx from the Southbridge.

10.2 Southbridge APIC Enable