Page 1

Élan™SC520 Microcontroller

User’s Manual

Order #22004B

Page 2

© 2001 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro De vices, Inc. ("AMD") products. AMD makes no repr esentations

or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD’s Standard Terms and Conditions of Sale, AMD assumes no

liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of

merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD’s products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the

body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD’s product could create a

situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make

changes to its products at any time without notice.

Trademarks

AMD, the AMD logo and combinations thereof, Am186, AMDebug, AMD Athlon, E86, K86, and Élan are trademarks; Am486 and Am5x86 are

registered trademarks; and FusionE86 is a service mark of Advanced Micro Devices, Inc.

Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corp.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Page 3

IF YOU HAVE QUESTIONS, WE’RE HERE TO HELP YOU.

The AMD customer service network includes U.S. offices, international offices, and a

customer training center . Expert technical assistance is av ailab le from the AMD worldwide

staff of field application engineers and fac tory support staff to answer E86™ f amily hardware

and software de ve lopment questions .

Frequently accessed numbers are listed below . Additional contact inf o rmation is listed on

the back of this manual. AMD’s WWW site lists the latest phone numbers.

Technical Support

Answers to tech nical questions are availa ble online, through e-mail, and b y telephone.

Go to AMD’s home p age at www.amd.com and follow t he Support link for the l atest AMD

technical support phone numbers, software, and Frequently Asked Questions.

For technical support questions on all E86 products, send e-mail to

epd.support@amd.com (in the US and Canada) or euro.tech@amd.com (in Euro pe and

the UK).

You can also call the AMD Corporate Applications Hotline at:

(800) 222-9323 Toll-free for U.S. and Canada

44-(0) 1276-803-299 U.K. and Europe hotline

WWW Support

For specifi c information on E86 products, acces s the AMD home page at www.amd.com

and follo w the Embedded Proces sors link. Th ese pages pro vide inf o rmation on upcoming

product releases, overviews of e xisting products , information on prod uct support and tools,

and a list of technical doc umentation. Support tools include online benchmarking tools and

CodeKit software—tested source code example applications. Many of the technical

documents are available online in PDF form.

Questions, requests, and input concerning AMD’s WWW pages can be sent via e-mail to

webfeedback@amd.com.

Documentation and Literature Support

Data books, user’ s manuals, data sheets , application notes , and product CDs are free with

a simple phone call. Internationally , contact y our local AMD sales office for produc t literature.

T o order literature, go to www.amd.com/support/literature.html or, in the US and Canada,

call (800) 222-9323.

Third-Party Support

AMD FusionE86SM program partners pro vide an arra y of products designed t o meet critical timeto-market needs . Product s and sol utions a v ailable include emulators, hardw ar e and sof tw are

debugge r s , b o a r d - leve l p r o d ucts, an d software devel opment t o o l s, amon g o t h e r s. The WWW

site and the

solutions. In addition, mature development tools and applicat ions for the x86 platform are

widely available in the general marketplace.

E86™ Family Products De v elopment Tools CD

, order #21058, describe these

Élan™SC520 Microcontroller User’s Manual iii

Page 4

iv Élan™SC520 Microcontroller User’s Manual

Page 5

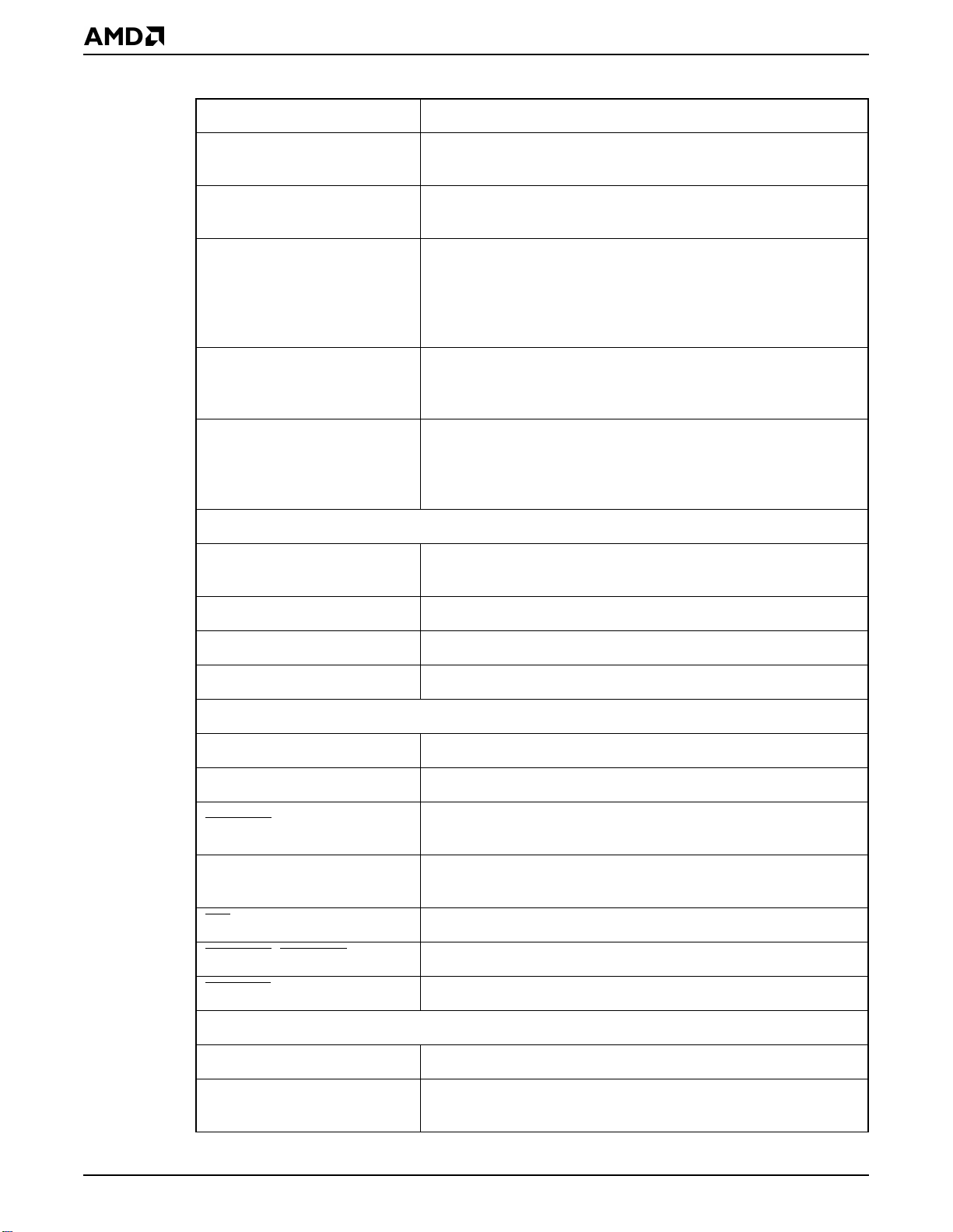

TABLE OF CONTENTS

PREFACE INTRODUCTION XXIII

Élan™SC520 Microcontroller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiii

Purpose of this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiii

Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiii

Overview of this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiii

Related Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

AMD Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

Additional Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xxv

Documentation Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xxv

CHAPTER 1 ARCHITECTURAL OVERVIEW 1-1

1.1 Élan™SC520 Microcontroller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.1 Distinctive Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.3 Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.3.1 Industry-Standard x86 Architecture. . . . . . . . . . . . . . . . . . . . . . . .1-4

1.3.2 AMDebug™ Technology for Advanced Debugging . . . . . . . . . . . .1-4

1.3.3 Industry-Standard PCI Bus Interface . . . . . . . . . . . . . . . . . . . . . .1-5

1.3.4 High-Performance SDRAM Controller. . . . . . . . . . . . . . . . . . . . . . 1-5

1.3.5 ROM/Flash Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.3.6 Flexible Address-Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.3.7 General-Purpose (GP) Bus Interface . . . . . . . . . . . . . . . . . . . . . .1-6

1.3.8 Clock Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3.9 Integrated Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.3.10 JTAG Boundary Scan Test Interface . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.3.11 System Testing and Debugging Features . . . . . . . . . . . . . . . . . . .1-8

1.4 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.4.1 Smart Residential Gateway. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

1.4.2 Thin Client . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

1.4.3 Digital Set Top Box . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-9

1.4.4 Telephone Line Concentrator . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

CHAPTER 2 PIN INFORMATION 2-1

2.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 Logic Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.3 Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

CHAPTER 3 SYSTEM INITIALIZATION 3-1

3.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Native Embedded Initialization Sequence . . . . . . . . . . . . . . . . . .3-1

3.1.2 BIOS Initialization Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

3.1.3 Memory-Mapped Configuration Region (MMCR) . . . . . . . . . . . . . 3-3

3.1.4 Reset Event . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.5 Reset V ector and Reset Segment . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.2 Configuring the SDRAM Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.3 Identifying the CPU Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.4 Setting the CPU Speed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3.5 Configuring External GP Bus Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.6 Configuring the Pin Multiplexing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.7 Configuring the Programmable Address Region (PAR) Registers . . . . . . .3-8

3.7.1 Specifying Pages and Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Élan™SC520 Microcontroller User’s Manual v

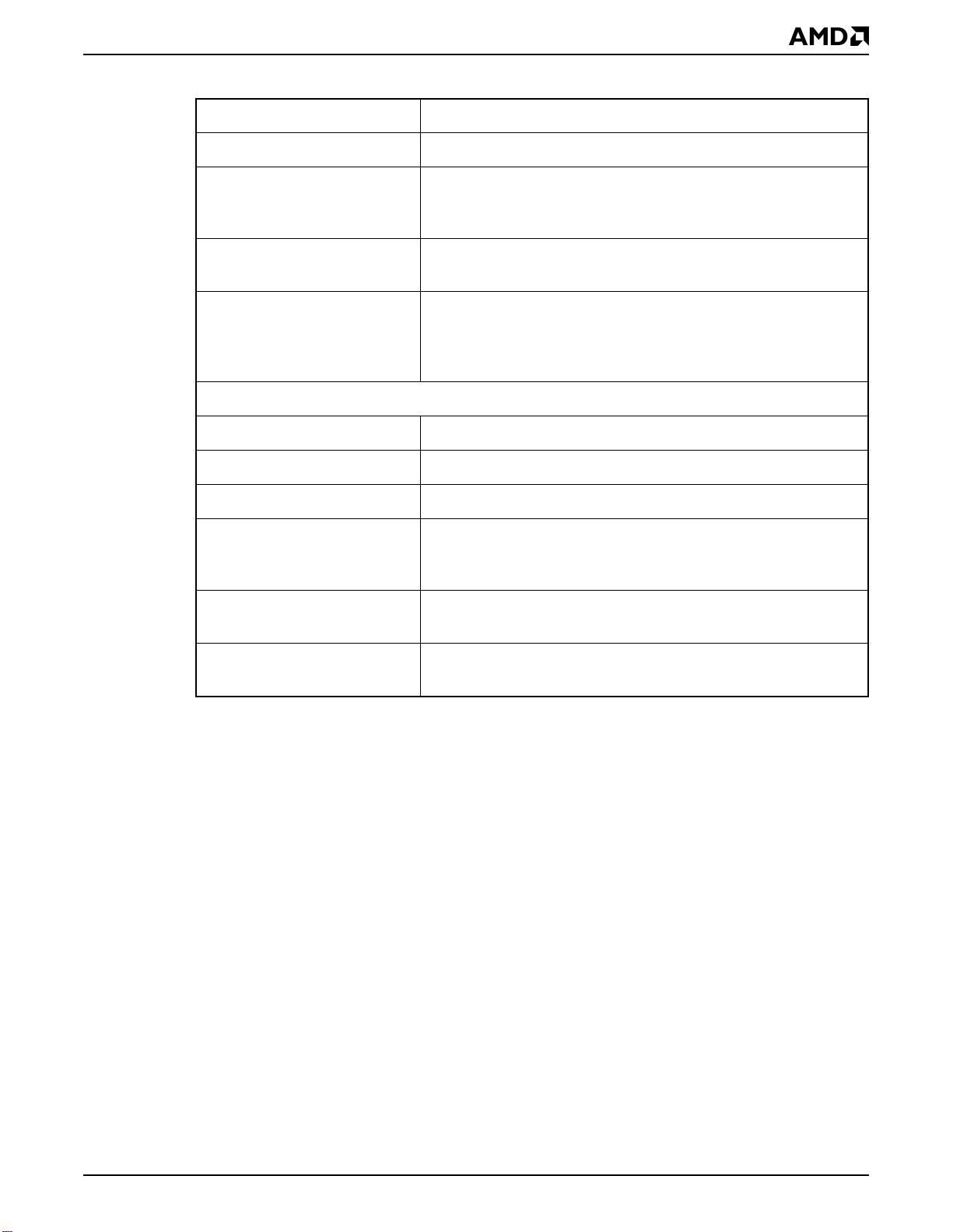

Page 6

Table of Contents

3.7.2 Address Region Attributes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.7.2.1 Write-Protect Attribute . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.7.2.2 Cacheability Control Attribute . . . . . . . . . . . . . . . . . . .3-12

3.7.2.3 Code Execution Attribute . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.7.2.4 Performance Considerations . . . . . . . . . . . . . . . . . . . .3-12

3.7.3 PAR Register Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.7.4 External GP Bus Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.7.4.1 Single Device (an A/D Converter) Using

One Chip Select. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14

3.7.4.2 Single Device That Performs Its Own Decode. . . . . . .3-14

3.7.4.3 Multiple Devices On One Chip Select . . . . . . . . . . . . .3-14

3.7.5 PCI Bus Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3.7.5.1 VGA Controller on the PCI Bus . . . . . . . . . . . . . . . . . .3-15

3.7.5.2 Network Adapter for Remote Program Loading. . . . . .3-16

3.7.6 External ROM Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

3.7.6.1 Boot ROM Device Mapping for BIOS Shadowing . . . .3-17

3.7.6.2 Two Banks of Flash for an Execute-In-Place (XIP)

Operating System . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

3.7.7 SDRAM Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

3.7.7.1 Setting Up DMA Buffers. . . . . . . . . . . . . . . . . . . . . . . .3-18

3.7.7.2 Write-Protected Code Segments. . . . . . . . . . . . . . . . . 3-18

3.8 Configuring the Interrupt Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

3.8.1 Edge-Sensitive or Level-Triggered Interrupts . . . . . . . . . . . . . . . 3-19

3.8.2 Interrupt Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

3.8.3 Interrupt Polarity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-20

3.9 Configuring the Programmable I/O Pins. . . . . . . . . . . . . . . . . . . . . . . . . .3-20

3.10 Configuring the PCI Host Bridge and Arbitration . . . . . . . . . . . . . . . . . . .3-20

3.11 Disabling Internal Peripherals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

CHAPTER 4 SYSTEM ADDRESS MAPPING 4-1

4.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4.3 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.3.1 Programming External Memory, Buses, and Chip Selects . . . . . .4-4

4.3.2 Programmable Address Region (PAR) Registers . . . . . . . . . . . . .4-5

4.3.3 Memory Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

4.3.3.1 SDRAM Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

4.3.3.2 ROM/Flash Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

4.3.3.3 GP Bus Memory Space . . . . . . . . . . . . . . . . . . . . . . . . .4-9

4.3.3.4 PCI Bus Memory Space . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.3.3.5 Memory-Ma pped Config uration Regi on (M MCR)

Registers Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

4.3.4 I/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

4.3.4.1 Configuration Base Address (CBAR) Register . . . . . .4-11

4.3.4.2 PCI Configuration Space . . . . . . . . . . . . . . . . . . . . . . . 4-12

4.3.4.3 PCI I/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

4.3.4.4 PC/AT-Compatible I/O Peripherals Region. . . . . . . . . . 4-13

4.3.4.5 GP Bus I/O Region . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.3.5 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-15

4.3.5.1 Configuring ROM/Flash Space . . . . . . . . . . . . . . . . . .4-15

4.3.5.2 Configuring SDRAM Address Space . . . . . . . . . . . . . .4-15

4.3.5.3 Configuring GP Bus Peripheral Space. . . . . . . . . . . . .4-16

4.3.5.4 Configuring the Élan™SC520 Microcontroller

for Windows® Compatibility. . . . . . . . . . . . . . . . . . . . .4-17

4.3.5.5 Configuring PCI Bus Devices. . . . . . . . . . . . . . . . . . . .4-18

4.3.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

4.3.7 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

4.4 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

vi Élan™SC520 Microcontroller User’s Manual

Page 7

Table of Contents

CHAPTER 5 CLOCK GENERATION AND CONTROL 5-1

5.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

5.3.1 Clock Pin Loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.3.2 Selecting a Crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.3.2.1 Running the Élan™SC520 Microcontroller

at 33.333 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.3.3 Bypassing Internal Oscillators . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-6

5.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.1 Internal Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.1.1 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.1.2 PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

5.5.1.3 SDRAM Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.1.4 ROM/Flash Interface . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

5.5.1.5 GP Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.5.1.6 GP-DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.5.1.7 Programmable Interval Timer. . . . . . . . . . . . . . . . . . . . . 5-8

5.5.1.8 General-Purpose Timers . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.5.1.9 Software Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.5.1.10 Watchdog Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.5.1.11 Real-Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.5.1.12 UART Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

5.5.1.13 Synchronous Serial Interface. . . . . . . . . . . . . . . . . . . . .5-8

5.5.2 Using the CLKTIMER[CLKTEST] Pin . . . . . . . . . . . . . . . . . . . . . .5-9

5.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

CHAPTER 6 RESET GENERATION 6-1

6.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

6.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.5.1 System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.5.2 System Reset with SDRAM Retention . . . . . . . . . . . . . . . . . . . . . 6-6

6.5.3 Soft CPU Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.5.4 GP Bus Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.5.5 PCI Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.5.6 RTC Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-7

6.5.7 Determining Reset Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.5.8 CPU A20 Gate Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.5.9 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.5.10 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.5.11 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

6.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

Élan™SC520 Microcontroller User’s Manual vii

Page 8

Table of Contents

CHAPTER 7 Am5X86® CPU 7-1

7.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7.4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.4.1 Floating Point Unit (FPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.4.2 Cache Memory Management . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

7.4.3 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.4.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.4.5 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.5 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.5.1 Hard CPU Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

7.5.2 Soft CPU Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

CHAPTER 8 SYSTEM ARBITRATION 8-1

8.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.4.1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.4.1.1 Nonconcurrent Arbitration Mode . . . . . . . . . . . . . . . . . . 8-3

8.4.1.2 Concurrent Arbitration Mode . . . . . . . . . . . . . . . . . . . . .8-4

8.4.2 CPU Bus Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.4.2.1 CPU Arbitration Protocol . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.4.2.2 CPU Cache Snooping . . . . . . . . . . . . . . . . . . . . . . . . . .8-6

8.4.2.3 Accessing the PCI Host Bridge Target. . . . . . . . . . . . . . 8-6

8.4.2.4 GP Bus DMA Arbitration . . . . . . . . . . . . . . . . . . . . . . . .8-7

8.4.2.5 Arbitration During Clock Speed Changes . . . . . . . . . . .8-7

8.4.3 PCI Bus Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.4.3.1 PCI Bus Arbitration Protocol . . . . . . . . . . . . . . . . . . . . .8-8

8.4.3.2 Bus Parking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-10

8.4.3.3 Rearbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.4.4 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.4.4.1 CPU Bus Arbitration. . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.4.4.2 CPU Bus Cache Write-Back . . . . . . . . . . . . . . . . . . . . 8-12

8.4.4.3 CPU-to-PCI Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-14

8.4.4.4 PCI Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-15

8.4.4.5 PCI Bus Arbitration Parking . . . . . . . . . . . . . . . . . . . . . 8-16

8.4.4.6 Nonconcurrent Mode Arbitration . . . . . . . . . . . . . . . . .8-18

8.4.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-19

8.4.6 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-19

8.4.7 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-20

8.4.7.1 Simple Rotating Priority Latency . . . . . . . . . . . . . . . . .8-20

8.4.7.2 High-Priority Queue Latency . . . . . . . . . . . . . . . . . . . .8-21

8.4.7.3 Low-Priority Queue Latency. . . . . . . . . . . . . . . . . . . . .8-21

8.4.7.4 CPU Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-21

8.4.7.5 Nonconcurrent Arbitration Mode Latency . . . . . . . . . . 8-21

8.4.7.6 Concurrent Arbitration Mode Latency . . . . . . . . . . . . . 8-22

8.4.7.7 Concurrent Arbitration Mode Bus Parking Latency . . .8-22

8.5 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-22

CHAPTER 9 PCI BUS HOST BRIDGE 9-1

9.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-2

9.3.1 PCI Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.3.1.1 Running the Élan™SC520 Microcontroller

at 33.333 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

viii Élan™SC520 Microcontroller User’s Manual

Page 9

Table of Contents

9.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-7

9.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9.5.1 Unsupported PCI Bus Functions . . . . . . . . . . . . . . . . . . . . . . . . .9-8

9.5.1.1 Unsupported PCI Bus Configuration Registers . . . . . . . 9-9

9.5.2 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.5.2.1 Generating PCI Bus Configuration Cycles. . . . . . . . . .9-10

9.5.3 Élan™SC520 Mic roco nt ro lle r ’s Host Bridge as PCI Bus Master . 9-11

9.5.3.1 Write Posting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-11

9.5.3.2 Read Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-12

9.5.3.3 Delayed Transaction Support. . . . . . . . . . . . . . . . . . . . 9-12

9.5.3.4 Host Bridge Master Bus Cycles. . . . . . . . . . . . . . . . . .9-12

9.5.4 Élan™SC520 Microcontroller’s Host Bridge as PCI Bus Target . .9-18

9.5.4.1 PCI Host Bridge Target Address Space. . . . . . . . . . . . 9-18

9.5.4.2 PCI Bus Command Support . . . . . . . . . . . . . . . . . . . . 9-19

9.5.4.3 DEVSEL

Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-19

9.5.4.4 Delayed Transaction Support. . . . . . . . . . . . . . . . . . . . 9-19

9.5.4.5 Address FIFO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-20

9.5.4.6 PCI Host Bridge FIFOs and Prefetching . . . . . . . . . . .9-20

9.5.4.7 Burst Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-21

9.5.4.8 Maintaining Data Coherency . . . . . . . . . . . . . . . . . . . .9-21

9.5.4.9 PCI Host Bridge Target Bus Cycles. . . . . . . . . . . . . . . 9-22

9.5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-27

9.5.6 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-28

9.5.6.1 Master Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-28

9.5.6.2 Target Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-28

9.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-29

CHAPTER 10 SDRAM CONTROLLER 10-1

10.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

10.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.3.1 SDRAM Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-5

10.3.2 SDRAM Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6

10.3.3 SDRAM Loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-8

10.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

10.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-11

10.5.1 SDRAM Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-11

10.5.2 SDRAM Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

10.5.2.1 Supported SDRAM Devices. . . . . . . . . . . . . . . . . . . .10-13

10.5.2.2 Page Size. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-16

10.5.3 Error Correction Code (ECC) . . . . . . . . . . . . . . . . . . . . . . . . . .10-16

10.5.4 Buffering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-17

10.5.5 SDRAM Control Configuration . . . . . . . . . . . . . . . . . . . . . . . . . 10-18

10.5.5.1 Refresh Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-18

10.5.5.2 Drive-Strength Selection . . . . . . . . . . . . . . . . . . . . . . 10-19

10.5.5.3 Write Buffer Test Mode . . . . . . . . . . . . . . . . . . . . . . .10-19

10.5.5.4 Operation Mode Select . . . . . . . . . . . . . . . . . . . . . . . 10-20

10.5.6 SDRAM Timing Configuration . . . . . . . . . . . . . . . . . . . . . . . . . 10-20

10.5.6.1 CAS

10.5.6.2 RAS

10.5.6.3 RAS

10.5.6.4 RAS

10.5.6.5 Minimum RAS

Latency (CL) . . . . . . . . . . . . . . . . . . . . . . . . . . .10-20

Precharge (TRP) . . . . . . . . . . . . . . . . . . . . . . . .10-21

-to-CAS Delay (T

). . . . . . . . . . . . . . . . . . . . . 10-21

RCD

-to-RAS or Auto-Refresh-to-RAS (TRC) . . . . . . .10-21

(T

). . . . . . . . . . . . . . . . . . . . . . . . .10-22

RAS

10.5.7 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-22

10.5.7.1 SDRAM Burst Read Cycle. . . . . . . . . . . . . . . . . . . . .10-22

10.5.7.2 SDRAM Write Cycle. . . . . . . . . . . . . . . . . . . . . . . . . .10-23

10.5.7.3 ECC SDRAM Cycles . . . . . . . . . . . . . . . . . . . . . . . . .10-24

10.5.7.4 SDRAM Auto Refresh Cycle . . . . . . . . . . . . . . . . . . .10-26

Élan™SC520 Microcontroller User’s Manual ix

Page 10

Table of Contents

10.5.7.5 SDRAM Mode Register Access Cycles . . . . . . . . . . .10-27

10.5.8 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-27

10.5.9 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-28

10.5.9.1 ECC Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-28

10.5.9.2 Buffer Disabling During SDRAM Configuration . . . . .10-28

10.5.9.3 Write Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-28

10.5.10 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-28

10.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-29

10.6.1 Programmable Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-29

10.6.2 SDRAM Device Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-30

10.6.2.1 Operation Mode Select . . . . . . . . . . . . . . . . . . . . . . . 10-30

10.6.2.2 NOP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-31

10.6.2.3 Precharge Command. . . . . . . . . . . . . . . . . . . . . . . . . 10-31

10.6.2.4 Auto Refresh Command . . . . . . . . . . . . . . . . . . . . . .10-31

10.6.2.5 Mode Register Programming. . . . . . . . . . . . . . . . . . .10-31

10.6.3 Boot Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-32

10.6.4 SDRAM Sizing Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-32

10.6.4.1 Determining the Number of Columns

for an External Bank . . . . . . . . . . . . . . . . . . . . . . . . .10-33

10.6.4.2 Determining the Number of Internal Banks . . . . . . . . 10-34

10.6.4.3 Determining the True External Bank Ending Address 10-35

CHAPTER 11 WRITE BUFFER AND READ BUFFER 11-1

11.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

11.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-2

11.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

11.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

11.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-4

11.5.1 Write Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.5.1.1 Write Buffer Disabled. . . . . . . . . . . . . . . . . . . . . . . . . .11-5

11.5.1.2 Write Buffer Enabled . . . . . . . . . . . . . . . . . . . . . . . . . .11-5

11.5.1.3 Write Buffer Watermark . . . . . . . . . . . . . . . . . . . . . . . .11-9

11.5.2 Read Buffer and the Read-Ahead Feature . . . . . . . . . . . . . . . .11-10

11.5.2.1 Read-Ahead Feature Disabled. . . . . . . . . . . . . . . . . .11-10

11.5.2.2 Read-Ahead Feature Enabled . . . . . . . . . . . . . . . . . . 11-10

11.5.3 DMA Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-11

11.5.4 PCI Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-12

11.5.4.1 Write Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-12

11.5.4.2 Read Cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-12

11.5.5 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-13

11.5.6 SDRAM Bandwidth Improvements . . . . . . . . . . . . . . . . . . . . . .11-13

11.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-15

CHAPTER 12 ROM/FLASH CONTROLLER 12-1

12.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

12.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

12.3.1 Voltage Isolation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-3

12.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-5

12.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-5

12.5.1 ROM Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-5

12.5.1.1 Supported Device Types . . . . . . . . . . . . . . . . . . . . . . .12-6

12.5.2 ROM Control and Timing Configuration . . . . . . . . . . . . . . . . . . . 12-7

12.5.2.1 ROM Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.5.2.2 ROM Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.5.2.3 Operating Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.5.2.4 Access Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-8

x Élan™SC520 Microcontroller User’s Manual

Page 11

Table of Contents

12.5.3 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-9

12.5.3.1 Single CPU Read Access . . . . . . . . . . . . . . . . . . . . . . 12-9

12.5.3.2 Page-Mode Read Access . . . . . . . . . . . . . . . . . . . . . 12-10

12.5.3.3 Cache-Line Fill. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-11

12.5.3.4 Writing to Flash Devices . . . . . . . . . . . . . . . . . . . . . . 12-11

12.5.4 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-12

12.5.4.1 Address Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . .12-12

12.5.4.2 Programming Flash Memory . . . . . . . . . . . . . . . . . . .12-12

12.5.5 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-13

12.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-14

CHAPTER 13 GENERAL-PURPOSE BUS CONTROLLER 13-1

13.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

13.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

13.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

13.3.1 GP Bus Loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-4

13.3.2 Voltage Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-4

13.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-5

13.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-6

13.5.1 Programmable Bus Interface Timing . . . . . . . . . . . . . . . . . . . . .13-7

13.5.1.1 Timing Requirements. . . . . . . . . . . . . . . . . . . . . . . . . .13-7

13.5.1.2 Using GPRDY with Programmable Timing. . . . . . . . . . 13-8

13.5.1.3 Using GP Bus Echo Mode with Program ma ble Timing 13-8

13.5.2 I/O-Mapped and Memory-Mapped Device Support . . . . . . . . . .13-9

13.5.3 Chip Select Qualification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-9

13.5.4 Data Sizing and Unaligned Accesses . . . . . . . . . . . . . . . . . . . . .13-9

13.5.5 Sharing the Address and Data Bus

13.5.6 GP Bus Echo Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-10

13.5.7 DMA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-11

13.5.8 Usage Scenarios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-11

13.5.9 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-16

13.5.10 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-21

13.5.11 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-21

13.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-22

with the ROM/Flash Controller . . . . . . . . . . . . . . . . . . . . . . . . . 13-10

13.5.8.1 Compatibility with Common ISA Devices. . . . . . . . . .13-11

13.5.8.2 Interfacing with a Super I/O Controller. . . . . . . . . . . .13-13

13.5.8.3 Interfacing with an AMD Enhanced

Serial Communications Controller (8 MHz) . . . . . . . . 13-14

13.5.9.1 8-Bit Data Access of an 8-Bit I/O Device . . . . . . . . . .13-16

13.5.9.2 16-Bit Data Access of a 16-Bit I/O Device . . . . . . . . . 13-17

13.5.9.3 16-Bit Data Access of an 8-Bit I/O Device . . . . . . . . .13-17

13.5.9.4 32-Bit Data Access of an 8-Bit I/O Device . . . . . . . . .13-18

13.5.9.5 32-Bit Data Access of a 16-Bit I/O Device . . . . . . . . . 13-18

13.5.9.6 8-Bit Data Access of a 16-Bit I/O Device . . . . . . . . . .13-19

13.5.9.7 GPIOCS16

13.5.9.8 Wait States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-20

13.5.11.18/16-Bit GP Bus Width. . . . . . . . . . . . . . . . . . . . . . . .13-21

13.5.11.2Slow GP Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . .13-21

13.5.11.3Noncacheable GP Bus. . . . . . . . . . . . . . . . . . . . . . . .13-21

and GPMEMCS16 Timing. . . . . . . . . . . . 13-19

Élan™SC520 Microcontroller User’s Manual xi

Page 12

Table of Contents

CHAPTER 14 GP BUS DMA CONTROLLER 14-1

14.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

14.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

14.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-3

14.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-4

14.4.1 Memory-Mapped Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-4

14.4.2 Direct-Mapped Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-6

14.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-8

14.5.1 GP-DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-8

14.5.1.1 GP-DMA Initiators . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-9

14.5.1.2 GP-DMA Channel Mapping . . . . . . . . . . . . . . . . . . . .14-10

14.5.2 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-10

14.5.2.1 Normal GP-DMA Mode . . . . . . . . . . . . . . . . . . . . . . .14-10

14.5.2.2 Enhanced GP-DMA Mode . . . . . . . . . . . . . . . . . . . . .14-11

14.5.3 Addressing GP-DMA Channels . . . . . . . . . . . . . . . . . . . . . . . .14-11

14.5.3.1 Addressing In Normal GP-DMA Mode. . . . . . . . . . . .14-11

14.5.3.2 Addressing In Enhanced GP-DMA Mode . . . . . . . . . 14-12

14.5.4 GP-DMA Transfer Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-12

14.5.4.1 Single Transfer Mode . . . . . . . . . . . . . . . . . . . . . . . . . 14-12

14.5.4.2 Demand Transfer Mode . . . . . . . . . . . . . . . . . . . . . . . 14-12

14.5.4.3 Block Transfer Mode . . . . . . . . . . . . . . . . . . . . . . . . .14-13

14.5.4.4 Transfer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-13

14.5.4.5 Automatic Initialization Control. . . . . . . . . . . . . . . . . . 14-14

14.5.4.6 Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-15

14.5.4.7 Buffer Chaining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-15

14.5.5 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-16

14.5.5.1 GP Bus I/O to SDRAM. . . . . . . . . . . . . . . . . . . . . . . .14-16

14.5.5.2 GP-DMA Read with Cache Hit. . . . . . . . . . . . . . . . . .14-17

14.5.6 GP Bus Echo Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-17

14.5.7 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-18

14.5.8 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-18

14.5.9 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-18

14.5.10 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-18

14.5.10.1Nonpreemptive Latency. . . . . . . . . . . . . . . . . . . . . . .14-18

14.5.10.2Preemptive Latency . . . . . . . . . . . . . . . . . . . . . . . . . .14-19

14.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-19

14.6.1 Example Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-19

14.6.1.1 Configuring an 8-Bit Channel

in Normal GP-DMA Mode . . . . . . . . . . . . . . . . . . . . .14-19

14.6.1.2 Configuring a 16-Bit Channel

in Normal GP-DMA Mode . . . . . . . . . . . . . . . . . . . . .14-20

14.6.1.3 Configuring an 8-Bit Channel

in Enhanced GP-DMA Mode . . . . . . . . . . . . . . . . . . . 14-20

14.6.1.4 Configuring a 16-Bit Channel

in Enhanced GP-DMA Mode . . . . . . . . . . . . . . . . . . . 14-21

CHAPTER 15 PROGRAMMABLE INTERRUPT CONTROLLER 15-1

15.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-1

15.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-2

15.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-2

15.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

15.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-7

15.5.1 Interrupt Flow Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-7

15.5.2 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-8

15.5.2.1 Hardware-Generated Interrupts. . . . . . . . . . . . . . . . . . 15-8

15.5.3 Interrupt Source Routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-10

15.5.3.1 Polarity Inversion of Interrupt Requests. . . . . . . . . . .15-10

xii Élan™SC520 Microcontroller User’s Manual

Page 13

Table of Contents

15.5.3.2 PC/AT Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . 15-12

15.5.3.3 Floating Point Errors . . . . . . . . . . . . . . . . . . . . . . . . . 15-12

15.5.3.4 Disabling the Slave Controllers . . . . . . . . . . . . . . . . .15-13

15.5.4 Edge-Triggered or Level-Sensitive Interrupts . . . . . . . . . . . . . .15-13

15.5.5 Interrupt Sharing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-13

15.5.6 Non-Maskable Interrupts and Routing . . . . . . . . . . . . . . . . . . .15-14

15.5.6.1 Sharing NMIs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-14

15.5.7 Priority Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-16

15.5.8 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-16

15.5.8.1 Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-16

15.5.8.2 PC/AT Configuration . . . . . . . . . . . . . . . . . . . . . . . . .15-18

15.5.9 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-18

15.5.9.1 Interrupt Sharing . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-18

15.5.9.2 Disabling the Slave Controllers . . . . . . . . . . . . . . . . .15-19

15.5.9.3 Detecting Invalid Interrupt Requests . . . . . . . . . . . . .15-19

15.5.9.4 Floating Point Unit Error Handling . . . . . . . . . . . . . . . 15-19

15.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-20

CHAPTER 16 PROGRAMMABLE INTERVAL TIMER 16-1

16.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

16.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

16.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-1

16.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-3

16.5.1 PIT Channel 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-3

16.5.2 PIT Channel 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-3

16.5.3 PIT Channel 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-4

16.5.4 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-4

16.5.4.1 Mode 0: Interrupt on Te rminal Count . . . . . . . . . . . . . .16-4

16.5.4.2 Mode 1: Hardware-Retriggerable One-Shot . . . . . . . .16-4

16.5.4.3 Mode 2: Rate Generator . . . . . . . . . . . . . . . . . . . . . . . 16-5

16.5.4.4 Mode 3: Square Wave Mode . . . . . . . . . . . . . . . . . . . . 16-5

16.5.4.5 Mode 4: Software-Triggered Strobe. . . . . . . . . . . . . . . 16-5

16.5.4.6 Mode 5: Hardware-Triggered Strobe . . . . . . . . . . . . . . 16-5

16.5.5 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-6

16.5.5.1 Internal Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-6

16.5.5.2 External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-6

16.5.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-6

16.5.7 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-6

16.5.7.1 Using the PIT Clock Source in PC/AT-Compatible

Systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-6

16.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-7

CHAPTER 17 GENERAL-PURPOSE TIMERS 17-1

17.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-1

17.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-1

17.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

17.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-2

17.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-3

17.5.1 GP Timer 0 and GP Timer 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-3

17.5.2 GP Timer 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-4

17.5.3 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-4

17.5.3.1 Interrupt on Terminal Count Mode . . . . . . . . . . . . . . . .17-4

17.5.3.2 Hardware Retrigger Mode . . . . . . . . . . . . . . . . . . . . . .17-4

17.5.3.3 Alternate Compare Mode. . . . . . . . . . . . . . . . . . . . . . . 17-4

17.5.3.4 Square Wave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-4

17.5.3.5 Continuous Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-4

17.5.3.6 Prescaler Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-4

Élan™SC520 Microcontroller User’s Manual xiii

Page 14

Table of Contents

17.5.4 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-5

17.5.5 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-5

17.5.5.1 Internal Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-5

17.5.5.2 External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-6

17.5.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-6

17.5.7 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-6

17.5.7.1 Combining GP Timer Count Elements. . . . . . . . . . . . . 17-6

17.5.7.2 Reading the Cascaded 32-Bit Timer . . . . . . . . . . . . . . 17-6

17.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-8

CHAPTER 18 SOFTWARE TIMER 18-1

18.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-1

18.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-1

18.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-2

18.4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-2

18.4.1 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-3

18.5 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-3

CHAPTER 19 WATCHDOG TIMER 19-1

19.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-1

19.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-1

19.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-2

19.4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-3

19.4.1 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-3

19.4.1.1 Keyed Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-3

19.4.1.2 Interrupt Request Generation . . . . . . . . . . . . . . . . . . . 19-4

19.4.1.3 System Reset Generation . . . . . . . . . . . . . . . . . . . . . . 19-4

19.4.1.4 Time-Out Duration . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-4

19.4.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-5

19.4.3 AMDebug™ Technology Interface . . . . . . . . . . . . . . . . . . . . . . . 19-5

19.4.4 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-5

19.5 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-6

CHAPTER 20 REAL-TIME CLOCK 20-1

20.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-1

20.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-1

20.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-3

20.3.1 Backup Battery Considerations . . . . . . . . . . . . . . . . . . . . . . . . .20-3

20.3.1.1 System with an External Backup Battery. . . . . . . . . . .20-3

20.3.1.2 System without an External Backup Battery . . . . . . . .20-4

20.3.2 Selecting and Interfacing a 32.768-kHz Crystal . . . . . . . . . . . . .20-5

20.3.3 Using an External RTC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-5

20.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-6

20.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.5.1 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-7

20.5.1.1 Configuring the Hour Format . . . . . . . . . . . . . . . . . . . . 20-7

20.5.1.2 Programming the Date and Time. . . . . . . . . . . . . . . . .20-8

20.5.1.3 Generating Periodic Interrupts. . . . . . . . . . . . . . . . . . .20-8

20.5.1.4 Using the Alarm Function . . . . . . . . . . . . . . . . . . . . . .20-9

20.5.1.5 Handling Year 2000 Issues . . . . . . . . . . . . . . . . . . . . . 20-9

20.5.2 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-9

20.5.3 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-9

20.5.4 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-10

20.5.4.1 Initializing the RTC Divider Chain . . . . . . . . . . . . . . . 20-10

20.5.4.2 Accessing the CMOS Memory. . . . . . . . . . . . . . . . . . 20-10

20.5.4.3 Legacy NMI Enable Bit Moved. . . . . . . . . . . . . . . . . .20-10

20.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20-10

20.6.1 RTC Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-11

xiv Élan™SC520 Microcontroller User’s Manual

Page 15

Table of Contents

CHAPTER 21 UART SERIAL PORTS 21-1

21.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-1

21.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-1

21.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-2

21.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-3

21.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-5

21.5.1 Data Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-6

21.5.1.1 16450-Compatible UART Mode. . . . . . . . . . . . . . . . . .21-6

21.5.1.2 16550-Compatible UART Mode. . . . . . . . . . . . . . . . . .21-7

21.5.2 Data Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-7

21.5.2.1 16450-Compatible UART Mode. . . . . . . . . . . . . . . . . .21-7

21.5.2.2 16550-Compatible UART Mode. . . . . . . . . . . . . . . . . .21-7

21.5.3 Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-8

21.5.3.1 Parity Error. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

21.5.3.2 Framing Error. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

21.5.3.3 Break Indication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

21.5.3.4 Error Reporting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-8

21.5.4 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-9

21.5.4.1 Baud Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-9

21.5.4.2 Hardware Flow Control . . . . . . . . . . . . . . . . . . . . . . . . 21-9

21.5.4.3 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-9

21.5.5 DMA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-10

21.5.5.1 Transmit DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-10

21.5.5.2 Receive DMA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-10

21.5.6 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-10

21.5.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-10

21.5.7.1 Serial Port Interrupts . . . . . . . . . . . . . . . . . . . . . . . . .21-12

21.5.7.2 DMA Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-12

21.5.7.3 Interrupt Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-13

21.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21-13

CHAPTER 22 SYNCHRONOUS SERIAL INTERFACE 22-1

22.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-1

22.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-1

22.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-1

22.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-2

22.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-3

22.5.1 Usage Scenarios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-3

22.5.1.1 Four-Pin Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-3

22.5.1.2 Three-Pin Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-3

22.5.2 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-5

22.5.2.1 Bit Order. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-5

22.5.2.2 Clock Idle State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-5

22.5.2.3 Clock Phase. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-5

22.5.3 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-5

22.5.3.1 4-Bit Read Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-6

22.5.3.2 Burst, 16-Bit, and 32-Bit Cycles. . . . . . . . . . . . . . . . . .22-7

22.5.4 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-7

22.5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-7

22.5.6 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22-8

22.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22-8

Élan™SC520 Microcontroller User’s Manual xv

Page 16

Table of Contents

CHAPTER 23 PROGRAMMABLE INPUT/OUTPUT 23-1

23.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-1

23.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-1

23.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-2

23.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-4

23.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-4

23.5.1 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-5

23.5.1.1 PIO Pins and Simple Input. . . . . . . . . . . . . . . . . . . . . .23-5

23.5.1.2 PIO Pins and Simple Output . . . . . . . . . . . . . . . . . . . .23-5

23.5.2 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23-5

23.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23-6

CHAPTER 24 SYSTEM TEST AND DEBUGGING 24-1

24.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-1

24.2 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-1

24.2.1 Loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-2

24.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-2

24.4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-3

24.4.1 System Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-3

24.4.1.1 Pin Functions in System Test Mode. . . . . . . . . . . . . . .24-3

24.4.1.2 Using the System Test Mode Interface . . . . . . . . . . . .24-4

24.4.1.3 SDRAM Write Cycle in System Test Mode . . . . . . . . .24-4

24.4.1.4 SDRAM Read Cycle in System Test Mode . . . . . . . . .24-5

24.4.1.5 Tracing Transactions on the ROM Interface. . . . . . . . . 24-5

24.4.1.6 Tracing Transactions on the GP Bus Interface. . . . . . .24-6

24.4.2 Write Buffer Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-7

24.4.2.1 Using the Write Buffer Test Mode Interface . . . . . . . . .24-7

24.4.2.2 SDRAM Write Cycle in Write Buffer Test Mode . . . . . .24-8

24.4.2.3 SDRAM Read Cycle in Write Buffer Test Mode. . . . . .24-8

24.4.3 Other Debugging Features . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-10

24.4.3.1 Nonconcurrent Arbitration Mode . . . . . . . . . . . . . . . . 24-10

24.4.3.2 Echoing Integrated Peripheral Accesses

on the GP Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-10

24.4.3.3 Summary of Additional System Debugg in g Features. 24-10

24.4.4 Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24-11

24.4.5 Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-11

24.5 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24-12

CHAPTER 25 BOUNDARY SCAN TEST INTERFACE 25-1

25.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-1

25.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-1

25.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-2

25.3.1 JTAG Pin Strapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-2

25.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-2

25.5 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-2

25.5.1 Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-3

25.5.1.1 Implemented Instructions. . . . . . . . . . . . . . . . . . . . . . .25-3

25.5.2 Configuration Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-5

25.5.2.1 Instruction Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-5

25.5.2.2 Bypass Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25-5

25.5.2.3 Main Data Scan Path. . . . . . . . . . . . . . . . . . . . . . . . . .25-5

25.5.2.4 Serial Debug Port Data Register . . . . . . . . . . . . . . . .25-14

25.5.2.5 Device Identification Register . . . . . . . . . . . . . . . . . . 25-14

25.5.3 Test Access Port (TAP) Controller . . . . . . . . . . . . . . . . . . . . . .25-15

25.5.3.1 TAP Controller States. . . . . . . . . . . . . . . . . . . . . . . . . 25-15

25.5.4 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-19

25.5.5 Clocking Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-20

25.6 Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25-20

xvi Élan™SC520 Microcontroller User’s Manual

Page 17

Table of Contents

CHAPTER 26 AMDebug™ TECHNOLOGY 26-1

26.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26-1

26.2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26-2

26.3 System Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26-2

26.3.1 Connecting the AMDebug™ Port . . . . . . . . . . . . . . . . . . . . . . . . 26-3

26.3.2 Mechanical Specifications for the Target Connector . . . . . . . . . .26-5

26.3.3 Locating the Connector on the Target System . . . . . . . . . . . . . .26-5

26.4 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26-6

26.4.1 On-Chip Trace Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26-7

26.4.2 Software Performance Profiling . . . . . . . . . . . . . . . . . . . . . . . . . 26-7

INDEX Index-1

Élan™SC520 Microcontroller User’s Manual xvii

Page 18

Table of Contents

LIST OF FIGURES

Figure 1-1 Élan™SC520 Microcontroller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 1-2 Élan™SC520 Microcontroller-Based Smart Residential Gateway

Reference Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

Figure 1-3 Élan™SC520 Microcontroller-Based Thin Client Reference Design. . . . . . . . . . . . .1-11

Figure 1-4 Élan™SC520 Microcontroller-Based Digital Set Top Box Reference Design . . . . . .1-12

Figure 1-5 Élan™SC520 Microcontroller-Based Telephone Line Concentrator

Reference Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-13

Figure 2-1 Logic Diagram by Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2 Logic Diagram by Default Pin Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Figure 3-1 Initial Near Jump Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-2 Programmable Address Region (PAR) Register Format . . . . . . . . . . . . . . . . . . . . . . 3-10

Figure 3-3 Programmable Address Region (PAR) Register Worksheet . . . . . . . . . . . . . . . . . . . 3-11

Figure 4-1 Programmable Address Region (PAR) Register Format . . . . . . . . . . . . . . . . . . . . . . .4-6

Figure 4-2 System Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Figure 4-3 System I/O Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-11

Figure 5-1 Clock Source Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Figure 5-2 System Clock Distribution Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Figure 5-3 Bypassing the 32.768-kHz Oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

Figure 5-4 Bypassing the 33-MHz Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Figure 5-5 Clock Routing for the CLKTEST Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Figure 6-1 Reset Controller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

Figure 6-2 PRGRESET Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

Figure 6-3 Power-On Reset Sequence of Events. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-9

Figure 7-1 Am5

86® CPU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-2

x

Figure 8-1 System Arbitration Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Figure 8-2 Skipped Master Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-5

Figure 8-3 CPU Bus Rotating Priority Queue . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-6

Figure 8-4 External PCI Master Arbitration Queues . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

Figure 8-5 Host Bridge Master Arbitration Queue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-9

Figure 8-6 CPU Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11

Figure 8-7 CPU Bus Cache Write-Back . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-13

Figure 8-8 CPU-to-PCI Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-14

Figure 8-9 PCI Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-15

Figure 8-10 PCI Bus Concurrent Mode Arbitration Parking . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-16

Figure 8-11 Nonconcurrent Mode Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-18

Figure 8-12 Simple Rotating Priority Queue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-20

Figure 9-1 PCI Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

Figure 9-2 Élan™SC520 Microcontroller Connection to an External PCI Bus Target. . . . . . . . . . 9-3

Figure 9-3 Élan™SC520 Microcontroller Connection to an External PCI Bus Master . . . . . . . . .9-4

Figure 9-4 Élan™SC520 Microcontroller SERR

and PERR Connection . . . . . . . . . . . . . . . . . . . 9-5

Figure 9-5 PCI Bus Clocking Example 1: Lightly Loaded System . . . . . . . . . . . . . . . . . . . . . . . . 9-6

Figure 9-6 PCI Bus Clocking Example 2: Heavily Loaded System. . . . . . . . . . . . . . . . . . . . . . . . 9-6

Figure 9-7 PCI Configuration Address (PCICFGADR) Register . . . . . . . . . . . . . . . . . . . . . . . .9-10

Figure 9-8 CPU Read Cycle to the PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-13

Figure 9-9 CPU Read Cycle to the PCI Bus with External Target Retry. . . . . . . . . . . . . . . . . . . 9-14

Figure 9-10 CPU Posted Write Cycle to the PCI Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-15

Figure 9-11 Am5

86 CPU Non-Posted Write Cycle to the PCI Bus . . . . . . . . . . . . . . . . . . . . . . .9-16

x

Figure 9-12 CPU Write Cycles to Internal PCI Bus Configuration Registers . . . . . . . . . . . . . . . .9-17

Figure 9-13 CPU Read Cycles from Internal PCI Bus Configuration Registers . . . . . . . . . . . . . .9-18

Figure 9-14 External PCI Bus Master Posted Write to SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . .9-23

Figure 9-15 External PCI Master SDRAM Read (Delayed Transaction). . . . . . . . . . . . . . . . . . . . 9-24

Figure 9-16 PCI Host Bridge Target Disconnect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-26

Figure 10-1 SDRAM Controller Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

Figure 10-2 Detailed Block Diagram of SDRAM Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

Figure 10-3 SDRAM Bank Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

Figure 10-4 Example Configuration of a 168-Pin SDRAM DIMM . . . . . . . . . . . . . . . . . . . . . . . . . 10-5

xviii Élan™SC520 Microcontroller User’s Manual

Page 19

Table of Contents

Figure 10-5 SDRAM Clock Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-7

Figure 10-6 Alternate SDRAM Clock Generation with External Clock Driver. . . . . . . . . . . . . . . .10-7

Figure 10-7 SDRAM Burst Read Cyc l e (R ea d- Ahe ad Feature Disabled) (Pa ge Mis s / Page Hit). . 10-22

Figure 10-8 SDRAM Write Cycle (Write Buffer and ECC Disabled) (Page Miss/page Hit) . . . . . .10-23

Figure 10-9 SDRAM CPU Burst Write (Write Buf fer and ECC Disabled) (Page Miss/P ag e H it ). .10-24

Figure 10-10 SDRAM Burst Read Cycle with ECC Enabled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-25

Figure 10-11 SDRAM Read-Modify-Write Cycl e (for Data Write) with ECC Enabled (Page Hit). . . 10-26

Figure 10-12 SDRAM Auto Refresh Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-27

Figure 10-13 SDRAM Mode Register Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-27

Figure 11-1 Write Buffer and Read Buffer Block Diagram (SDRAM Subsystem) . . . . . . . . . . . . .11-2

Figure 11-2 Write Buffer and Read Buffer Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-3

Figure 11-3 Write Buffer Merging Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-7

Figure 11-4 Write Buffer Collapsing Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8

Figure 11-5 Write Buffer Read-Merging Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-9

Figure 11-6 Bus Thrashing with Write Buffer Disabled and Enabled . . . . . . . . . . . . . . . . . . . . .11-14

Figure 12-1 ROM Controller Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-2

Figure 12-2 Voltage Isolation Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-4

Figure 12-3 Page-Mode ROM: Fetching Four Words from a 16-Bit ROM. . . . . . . . . . . . . . . . . . . 12-6

Figure 12-4 Non-Page-Mode ROM: Fetching Four Words from a 16-Bit ROM. . . . . . . . . . . . . . .12-8

Figure 12-5 Page-Mode ROM: Fetching Four Doublewords (Aligned) from a 32-Bit ROM. . . . . . 12-8

Figure 12-6 Page-Mode ROM: Fetching Four Doublewords (Unaligned) from an 8-Bit ROM. . . . 12-8

Figure 12-7 Multiple Accesses: Data Amounts Smaller than One Doubleword (2 Bytes)

Figure 12-8 Page Access for Fetching Four Doublewords from a 32-Bit ROM

Figure 12-9 Page Access for Fetching Two Doublewords from a 16-Bit ROM . . . . . . . . . . . . . . 12-11

Figure 12-10 Cache-Line Fill (Fetching Four Doublewords from a 32-Bit ROM). . . . . . . . . . . . . .12-11

Figure 12-11 Word Write Cycle to Flash Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-12

Figure 13-1 GP Bus Controller System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-2

Figure 13-2 Example: Using an External Data Buffer to Address Excess Loading . . . . . . . . . . .13-4

Figure 13-3 Example: Using a Voltage Translator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-5

Figure 13-4 GP Bus Timing Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-8