Page 1

AMD RS785E Databook

Technical Reference Manual

Rev 1.30

P/N: 47991_rs785e_ds_pub_1.30

© 2010 Advanced Micro Devices Inc

Page 2

Please note that in this databook, references to "DVI" and "HDMI" refer to the capability of the TMDS interface, multiplexed on the PCIe external graphics interface, to

enable DVI or HDMI through passive enabling circuitries. Any statement in this databook on any DVI or HDMI-related functionality must be understood in that context.

USE OF THIS PRODUCT IN ANY MANNER THAT COMPLIES WITH THE MPEG-2 STANDARD IS EXPRESSLY PROHIBITED WITHOUT A LICENSE

UNDER APPLICABLE PATENTS IN THE MPEG-2 PATENT PORTFOLIO, WHICH LICENSE IS AVAILABLE FROM MPEG LA, L.L.C., 6312 S. FIDDLERS

GREEN CIRCLE, SUITE 400E, GREENWOOD VILLAGE, COLORADO 80111.

Trademarks

AMD, the AMD Arrow, ATI, the ATI logo, 3Dc+, AMD Athlon, AMD Phenom, AMD OverDrive, AMD PowerNow!, Avivo, Cool’n’Quiet, HyperMemory, PowerPlay,

PowerShift, AMD PowerXpress, AMD Radeon, SurroundView, Vari-Bright, CrossFire, and combinati ons thereof are trademarks of Advanced Micro Devices, Inc.

DisplayPort and eDP are trademarks of the Video Electronics Standards Association.

HyperTransport is a trademark of the HyperTransport Technology Consortium.

Microsoft, Windows, Windows Vista, Windows 7, DirectDraw, and DirectX are registered trademarks of Microsoft Corporation.

OpenGL is a registered trademark of Silicon Graphics Internal.

PCI Express and PCIe are registered trademarks of PCI-SIG.

WinBench is a registered trademark of Ziff Davis, Inc.

Linux is a registered trademark of Linus Torvalds in the U.S. and other countries.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Disclaimer

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with

respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time

without notice. No license, whether express, implied, arising by estoppel, or otherwise, to any intellectual property rights are granted by this publication. Except as set

forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products

including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications

intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe

property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

© 2010 Advanced Micro Devices, Inc. All rights reserved.

Page 3

Table of Contents

Chapter 1: Overview

1.1 Introducing the RS785E......................................................................................................................................................1-1

1.2 RS785E Features.................................................................................................................................................................1-2

1.2.1 CPU HyperTransport™ Interface.........................................................................................................................1-2

1.2.2 Memory Interface.................................................................................................................................................1-2

1.2.3 AMD HyperMemory™........................................................................................................................................1-2

1.2.4 PCI Express® Interface........................................................................................................................................1-2

1.2.5 A-Link Express II Interface..................................................................................................................................1-4

1.2.6 2D Acceleration Features.....................................................................................................................................1-4

1.2.7 3D Acceleration Features.....................................................................................................................................1-4

1.2.8 Motion Video Acceleration Features....................................................................................................................1-5

1.2.9 Multiple Display Features ....................................................................................................................................1-5

1.2.10 Integrated LVDS Interface...................................................................................................................................1-7

1.2.11 DVI/HDMI™ .......................................................................................................................................................1-7

1.2.12 DisplayPort™ Interface........................................................................................................................................1-7

1.2.13 Integrated HD Audio Controller and Codec.........................................................................................................1-8

1.2.14 System Clocks ......................................................................................................................................................1-8

1.2.15 Power Management Features ...............................................................................................................................1-8

1.2.16 PC Design Guide Compliance..............................................................................................................................1-8

1.2.17 Test Capability Features.......................................................................................................................................1-8

1.2.18 Additional Features ..............................................................................................................................................1-9

1.2.19 Packaging .............................................................................................................................................................1-9

1.3 Software Features................................................................................................................................................................1-9

1.4 Branding Diagram.............................................................................................................................................................1-10

1.5 Graphics Device ID and Graphics Engine Clock Speed...................................................................................................1-10

1.6 Conventions and Notations ...............................................................................................................................................1-10

1.6.1 Pin Names...........................................................................................................................................................1-10

1.6.2 Pin Types............................................................................................................................................................1-10

1.6.3 Numeric Representation.....................................................................................................................................1-11

1.6.4 Register Field......................................................................................................................................................1-11

1.6.5 Hyperlinks ..........................................................................................................................................................1-11

1.6.6 Acronyms and Abbreviations.............................................................................................................................1-11

Chapter 2: Functional Descriptions

2.1 Host Interface......................................................................................................................................................................2-2

2.2 Side-Port Memory Interface................................................................................................................................................2-3

2.2.1 DDR2 Memory Interface......................................................................................................................................2-3

2.2.2 DDR3 Memory Interface......................................................................................................................................2-5

2.3 LVDS Interface...................................................................................................................................................................2-6

2.3.1 LVDS Data Mapping............................................................................................................................................2-6

2.3.2 LVDS Spread Spectrum .......................................................................................................................................2-8

2.4 DVI/HDMI™......................................................................................................................................................................2-9

2.4.1 DVI/HDMI™ Data Transmission Order and Signal Mapping ............................................................................2-9

2.4.2 Support for HDMI™ Packet Types....................................................................................................................2-12

2.5 VGA DAC Characteristics................................................................................................................................................2-13

2.6 Clock Generation ..............................................................................................................................................................2-13

© 2010 Advanced Micro Devices, Inc. AMD RS785E Databook 1.30

Proprietary Table of Contents-1

Page 4

Table of Contents

Chapter 3: Pin Descriptions and Strap Options

3.1 Pin Assignment Top View ................................................................................................................................................. 3-2

3.1.1 RS785E Pin Assignment Top View .................................................................................................................... 3-2

3.2 Interface Block Diagram.................................................................................................................................................... 3-4

3.3 CPU HyperTransport™ Interface ...................................................................................................................................... 3-5

3.4 Side-port Memory Interface............................................................................................................................................... 3-5

3.5 PCI Express® Interfaces ....................................................................................................................................................3-6

3.5.1 1 x 16 or 2 x 8 Lane Interface for External Graphics.......................................................................................... 3-6

3.5.2 A-Link Express II Interface for Southbridge....................................................................................................... 3-6

3.5.3 6 x 1 Lane Interface for General Purpose External Devices .............................................................................. 3-6

3.5.4 Miscellaneous PCI Express® Signals ................................................................................................................. 3-6

3.6 Clock Interface................................................................................................................................................................... 3-7

3.7 CRT Interface..................................................................................................................................................................... 3-7

3.8 LVDS Interface (24 Bits)................................................................................................................................................... 3-8

3.9 TMDS Interface Multiplexed on the PCI Express® Graphics Lanes................................................................................ 3-9

3.10 DisplayPort™/Embedded DisplayPort Interface ............................................................................................................3-11

3.11 Power Management Pins............................................................................................................................................... 3-12

3.12 Miscellaneous Pins......................................................................................................................................................... 3-12

3.13 Power Pins...................................................................................................................................................................... 3-13

3.14 Ground Pins.................................................................................................................................................................... 3-14

3.15 Strapping Options ........................................................................................................................................................... 3-14

Chapter 4: Timing Specifications

4.1 HyperTransport™ Bus Timing .......................................................................................................................................... 4-1

4.2 HyperTransport™ Reference Clock Timing Parameters ................................................................................................... 4-1

4.3 PCI Express® Differential Clock AC Specifications......................................................................................................... 4-2

4.4 Timing Requirements for REFCLK_P Used as OSCIN (14.3181818MHz)..................................................................... 4-2

4.5 Side-port Memory Timing for DDR2 Mode...................................................................................................................... 4-2

4.5.1 Read Cycle DQ/DQS Delay ................................................................................................................................4-2

4.5.2 Write Cycle DQ/DQS Delay ............................................................................................................................... 4-3

4.6 LVDS Timing..................................................................................................................................................................... 4-3

4.7 Power Rail Power-up Sequence.........................................................................................................................................4-4

4.8 VDDC Ramp Time Requirement for Variable Voltage..................................................................................................... 4-4

4.9 LCD Panel Power Up/Down Timing ................................................................................................................................. 4-5

Chapter 5: Electrical Characteristics and Physical Data

5.1 Electrical Characteristics.................................................................................................................................................... 5-1

5.1.1 Maximum and Minimum Ratings........................................................................................................................ 5-1

5.1.2 DC Characteristics............................................................................................................................................... 5-2

5.2 RS785E Thermal Characteristics ....................................................................................................................................... 5-7

5.2.1 RS785E Thermal Limits...................................................................................................................................... 5-7

5.2.2 Thermal Diode Characteristics............................................................................................................................ 5-8

5.3 Package Information .......................................................................................................................................................... 5-9

5.3.1 Physical Dimensions............................................................................................................................................ 5-9

5.3.2 Pressure Specification........................................................................................................................................ 5-10

5.3.3 Board Solder Reflow Process Recommendations ..............................................................................................5-11

AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

Table of Contents-2 Proprietary

Page 5

Table of Contents

Chapter 6: Power Management and ACPI

6.1 ACPI Power Management Implementation ........................................................................................................................6-1

6.2 Power Management for the Graphics Controller................................................................................................................6-2

6.2.1 PCI Function Power States...................................................................................................................................6-2

6.2.2 PCI Power Management Interface........................................................................................................................6-2

6.2.3 Capabilities List Data Structure in PCI Configuration Space ..............................................................................6-2

6.2.4 Register Block Definition.....................................................................................................................................6-3

6.2.5 Capability Identifier: CAP_ID (Offset = 0) .........................................................................................................6-4

6.2.6 Next Item Pointer (Offset = 1) .............................................................................................................................6-5

6.2.7 PMC - Power Management Capabilities (Offset = 2) ..........................................................................................6-6

Chapter 7: Testability

7.1 Test Capability Features......................................................................................................................................................7-1

7.2 Test Interface.......................................................................................................................................................................7-1

7.3 XOR Test ............................................................................................................................................................................7-1

7.3.1 Description of a Generic XOR Tree.....................................................................................................................7-1

7.3.2 Description of the RS785E XOR Tree .................................................................................................................7-2

7.3.3 XOR Tree Activation ...........................................................................................................................................7-2

7.3.4 XOR Tree for the RS785E ...................................................................................................................................7-2

7.4 VOH/VOL Test...................................................................................................................................................................7-4

7.4.1 Description of a Generic VOH/VOL Tree ...........................................................................................................7-4

7.4.2 VOH/VOL Tree Activation..................................................................................................................................7-5

7.4.3 VOH/VOL Pin List...............................................................................................................................................7-6

Appendix A: Pin Listings

A.1 RS785E Pin List Sorted by Ball Reference........................................................................................................................1-2

A.2 RS785E Pin List Sorted by Pin Name................................................................................................................................1-7

Appendix B: Revision History

© 2010 Advanced Micro Devices, Inc. AMD RS785E Databook 1.30

Proprietary Table of Contents-3

Page 6

Table of Contents

This page is left blank intentionally.

AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

Table of Contents-4 Proprietary

Page 7

List of Figures

Figure 1-1: Possible Configurations for the x16 PCIe® Graphics Interface ................................................................................. 1-3

Figure 1-2: RS785E Multiple Display Options .............................................................................................................................. 1-6

Figure 1-3: RS785E ASIC A11 Production Branding ................................................................................................................. 1-10

Figure 2-1: RS785E Internal Block Diagram ................................................................................................................................. 2-1

Figure 2-2: Host Interface Block Diagram ..................................................................................................................................... 2-2

Figure 2-3: RS785E Host Bus Interface Signals ............................................................................................................................ 2-3

Figure 2-4: RS785E Side-Port Memory Interface .......................................................................................................................... 2-4

Figure 2-5: Single/Dual Channel 24-bit LVDS Data Transmission Ordering ............................................................................... 2-6

Figure 2-6: Data Transmission Ordering for the TMDS Interfaces ...............................................................................................2-9

Figure 3-1: RS785E Pin Assignment Top View (Left) .................................................................................................................. 3-2

Figure 3-2: RS785E Pin Assignment Top View (Right) ................................................................................................................ 3-3

Figure 3-3: RS785E Interface Block Diagram ...............................................................................................................................3-4

Figure 4-1: RS785E Power Rail Power-up Sequence ....................................................................................................................4-4

Figure 4-2.: LCD Panel Power Up/Down Timing .........................................................................................................................4-5

Figure 5-1: DC Characteristics of the TMDS Interface ................................................................................................................. 5-4

Figure 5-2: DC Characteristics of the LVDS Interface .................................................................................................................. 5-5

Figure 5-3: RS785E 528-Pin FCBGA Package Outline ................................................................................................................ 5-9

Figure 5-4: RS785E Ball Arrangement (Bottom View) ............................................................................................................... 5-10

Figure 5-5: Recommended Stencil Opening Sizes for Solder Paste Pads on PCB ...................................................................... 5-11

Figure 5-6: RoHS/Lead-Free Solder (SAC305/405 Tin-Silver-Copper) Reflow Profile ............................................................ 5-12

Figure 6-1: Linked List for Capabilities ......................................................................................................................................... 6-5

Figure 7-1: Example of a Generic XOR Tree ................................................................................................................................7-2

Figure 7-2: Sample of a Generic VOH/VOL Tree ......................................................................................................................... 7-5

© 2010 Advanced Micro Devices, Inc. AMD RS785E Databook 1.30

Proprietary List of Figures-1

Page 8

List of Figures

This page is left blank intentionally.

AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

List of Figures-2 Proprietary

Page 9

List of Tables

Table 1-1: Possible Configurations for the PCIe® General Purpose Links ....................................................................................1-3

Table 1-2: Graphics Device ID and Graphics Engine Clock Speed .............................................................................................1-10

Table 1-3: Pin Type Codes ............................................................................................................................................................1-10

Table 1-4: Acronyms and Abbreviations ......................................................................................................................................1-11

Table 2-1: Supported DDR2 Components ......................................................................................................................................2-4

Table 2-2: DDR2 Memory Row and Column Addressing ..............................................................................................................2-4

Table 2-3: Supported DDR3 Components ......................................................................................................................................2-5

Table 2-4: DDR3 Memory Row and Column Addressing ..............................................................................................................2-5

Table 2-5: LVDS 24-bit TFT Single Pixel per Clock (Single Channel) Signal Mapping ..............................................................2-7

Table 2-6: LVDS 24-bit TFT Dual Pixel per Clock (Dual Channel) Signal Mapping ...................................................................2-8

Table 2-7: Single Link Signal Mapping for DVI/HDMI™ .........................................................................................................2-10

Table 2-8: Dual-Link Signal Mapping for DVI ............................................................................................................................2-11

Table 2-9: Support for HDMI™ Packet Type ...............................................................................................................................2-12

Table 2-10: VGA DAC Characteristics ........................................................................................................................................2 -13

Table 3-1: CPU HyperTransport™ Interface ..................................................................................................................................3-5

Table 3-2: Side-Port Memory Interface ..........................................................................................................................................3-5

Table 3-3: 1 x 16 or 2 x 8 Lane PCI Express® Interface for External Graphics ............................................................................3-6

Table 3-4: 1 x 4 Lane A-Link Express II Interface for Southbridge ...............................................................................................3-6

Table 3-5: 6 x 1 Lane PCI Express® Interface for General Purpose External Devices ..................................................................3-6

Table 3-6: PCI Express® Interface for Miscellaneous PCI Express® Signals ...............................................................................3-6

Table 3-7: Clock Interface ...............................................................................................................................................................3-7

Table 3-8: CRT Interface ................................................................................................................................................................3-7

Table 3-9: LVDS Interface ..............................................................................................................................................................3-8

Table 3-10: TMDS Interface Multiplexed on the PCI Express® Graphics Interface (Dual-Link DVI) .........................................3-9

Table 3-11: TMDS Interface Multiplexed on the PCI Express® Graphics Interface (HDMI™ on Lane 0-3) ............................3-10

Table 3-12: TMDS Interface Multiplexed on the PCI Express® Graphics Interface (HDMI™ on Lane 4-7) ............................3-10

Table 3-13: Miscellaneous TMDS Interface Signals ....................................................................................................................3-10

Table 3-14: DisplayPort™/Emdebbed DisplayPort Interface Multiplexed on the PCI Express® Graphics Interface .................3-11

Table 3-15: Miscellaneous DisplayPort™/Emdebbed DisplayPort Signals .................................................................................3-11

Table 3-16: Power Management Pins ...........................................................................................................................................3-12

Table 3-17: Miscellaneous Pins ....................................................................................................................................................3-12

Table 3-18: Power Pins .................................................................................................................................................................3-13

Table 3-19: Ground Pins ...............................................................................................................................................................3-14

Table 3-20: Strap Definitions for the RS785E ..............................................................................................................................3-15

Table 4-1: Timing Requirements for HyperTransport® Reference Clock (100MHz) Output by the Clock Generator .................4-1

Table 4-2: PCI Express® Differential Clock (GFX_REFCLK, GPPSB_REFCLK, 100MHz) AC Characteristics ......................4-2

Table 4-3: Timing Requirements for REF_CLKP Used as OSCIN (14.3181818MHz) .................................................................4-2

Table 4-4: Timing Requirements for the LVDS Interface ..............................................................................................................4-3

Table 4-5: RS785E Power Rail Power-up Sequence ......................................................................................................................4-4

Table 4-6: LCD Power Up/Down Timing .......................................................................................................................................4-5

Table 5-1: Maximum and Minimum Ratings ..................................................................................................................................5-1

Table 5-2: DC Characteristics for 3.3V TTL Signals .....................................................................................................................5-2

Table 5-3: DC Characteristics for DDC Signals (DDC Mode) .......................................................................................................5-2

Table 5-4: DC Characteristics for AUX Signals (AUX Mode) ......................................................................................................5-2

Table 5-5: DC Characteristics for POWERGOOD .........................................................................................................................5-2

Table 5-6: DC Characteristics for HyperTransport™ and PCI-E Differential Clock (HT_REFCLK, GFX_REFCLK,

GPPSB_REFCLK, 100MHz) ..........................................................................................................................................................5-3

Table 5-7: DC Characteristics for REFCLK_P as OSCIN Input (14.3181818MHz) .....................................................................5-3

Table 5-8: DC Characteristics for the Memory Interface when Supporting DDR2 ........................................................................5-3

Table 5-9: DC Characteristics for the Memory Interface when Supporting DDR3 ........................................................................5-3

Table 5-10: DC Characteristics for the TMDS Interface Multiplexed on the PCI Express® Gfx Lanes .......................................5-4

Table 5-11: Electrical Requirements for the LVDS Interface .........................................................................................................5-5

© 2010 Advanced Micro Devices, Inc. AMD RS785E Databook 1.30

Proprietary List of Tables-1

Page 10

List of Tables

Table 5-12: Electrical Specifications for the DisplayPort Interface ...............................................................................................5-6

Table 5-13: RS785E Thermal Limits ..............................................................................................................................................5-7

Table 5-14: RS785E 528-Pin FCBGA Package Physical Dimensions ...........................................................................................5-9

Table 5-15: Recommended Board Solder Reflow Profile - RoHS/Lead-Free Solder ..................................................................5-12

Table 6-1: ACPI States Supported by the RS785E .........................................................................................................................6-1

Table 6-2: ACPI Signal Definitions ................................................................................................................................................6-1

Table 6-3: Standard PCI Configuration Space Header Type 0 .......................................................................................................6-2

Table 6-4: PCI Status Register ........................................................................................................................................................6-3

Table 6-5: Capabilities Pointer (CAP_PTR) ...................................................................................................................................6-3

Table 6-6: Power Management Register Block ..............................................................................................................................6-3

Table 6-7: Power Management Control/Status Register (PMCSR) ................................................................................................6-4

Table 6-8: Capability Identifier (CAP_ID) .....................................................................................................................................6-4

Table 6-9: Next Item Pointer (NEXT_ITEM_PTR) .......................................................................................................................6-5

Table 6-10: Power Management Capabilities – PMC .....................................................................................................................6-6

Table 7-1: Pins on the Test Interface ..............................................................................................................................................7-1

Table 7-2: Example of an XOR Tree ..............................................................................................................................................7-2

Table 7-3: RS785E XOR Tree ........................................................................................................................................................7-3

Table 7-4: Truth Table for the VOH/VOL Tree Outputs ................................................................................................................7-5

Table 7-5: RS785E VOH/VOL Tree ...............................................................................................................................................7-7

AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

List of Tables-2 Proprietary

Page 11

1.1 Introducing the RS785E

The RS785E is a ninth-generation Integrated Graphics Processor (IGP) for embedded systems that integrates a DirectX®

10.1-compliant Shader Model 4.1 graphics core and a system controller in a single chip. It supports AM3 and S1g3-socket

CPUs, which include the AMD Phenom™ II and Caspian-series processors. The RS785E integrates an AMD M82-based

graphics engine, dual display, an LVDS interface, a TMDS interface, DisplayPort capability, and Northbridge

functionality in a single BGA package. This high level of integration and scalability enables manufacturers to offer

enthusiast level capabilities and performance while helping to minimize board space and system cost.

Robust and Flexible Core Logic Features

The RS785E combines graphics and system logic functions in a single chip using a 21mm body BGA package, reducing

overall solution area. For optimal system and graphics performance, the RS785E supports a high speed HyperTransport™

interface to the AMD processor, running at a data rate of up to 4.4 GT/s and supporting both HT 1.0 and HT 3.0 protocols.

The RS785E is ideally suited for 64-bit operating systems, and supports platform configurations with greater than 4GB of

system memory. The rich PCI Express

PCI Express external graphics controllers and up to six other PCI Express peripherals (up to seven when using only 8

lanes for external graphics, or up to eight when not using external graphics), all supporting the PCI Express 2.0 standard

with data rates of up to 5.0GT/s. These capabilities are complemented by the advanced I/O features of AMD’s

SB800-series Southbridges.

Designed for Windows Vista

Chapter 1

Overview

®

(PCIe®) expansion capabilities of RS785E include support for one x16 or two x8

®

The RS785E delivers a compelling Windows Vista experience. It harnesses the increased bandwidth of HyperTransport

3.0 to a DirectX 10.1 graphics core, which provides the 3D rendering power needed to generate the Windows Vista

desktop even under the most demanding circumstances. The AMD M82-based graphics core employs a unified shader

architecture to deliver excellent 3D performance across the whole spectrum of 3D applications. It meets all current

Windows Vista Premium Logo requirements.

Leading Multimedia Capabilities

The RS785E incorporates AMD’s Unified Video Decoder (UVD) 2.0 technology, which provides dedicated hardware

decode of the H.264, VC-1, and MPEG-2 video formats used for HD contents and Blu-ray disks. The RS785E also

incorporates the innovative AMD Avivo™ HD display architecture, providing users with amazing visual quality.

Advanced scaling and color correction capabilities, along with increased precision through the entire display pipeline,

ensure an exceptional image on CRT monitors, LCD panels, and any other display device. Dual DisplayPort output

capability provides the ability to interface to the next generation of digital display devices. That is complemented by an

integrated TMDS interface, configurable to enable DVI/HDMI™ and support HDCP, allowing compatibility with even

the most modern high definition televisions without the additional cost of external components.

*Note: AMD Avivo™ HD is a technology platform that includes a broad set of capabilities offered by certain AMD

Radeon™ products. Support for any AMD Avivo™ HD capability is subject to qualification of the RS785E ASIC. Full

enablement of some AMD Avivo™ HD capabilities may require complementary products.

Low Power Consumption and Industry Leading Power Manage ment

The RS785E is manufactured using the power efficient nm technology, and it supports a whole range of industry

standards and includes additional power management features over the RS780E. In addition to comprehensive support for

the ACPI specification, the exclusive AMD PowerPlay™ technology (enhanced with new adaptive frame buffer

compression and AMD PowerShift™ features) minimizes the RS785E's power consumption by adjusting graphics core

performance and core voltage to the task and usage environment. System power can be further reduced through the

dedicated local frame buffer interface supported by the RS785E. The integrated UVD dramatically reduces CPU loading

and hence overall power consumption during Blu-ray video and HD contents playback.

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-1

Page 12

Software Compatibility

The graphics driver for the RS785E is fully compatible with all other AMD Radeon™ class graphics controllers from

AMD. A single driver can support multiple graphics configurations across AMD’s product lines, including the AMD

Radeon family and the AMD chipset family. In addition, this driver compatibilit y allo ws the RS7 85E to benefit

immediately from AMD's software optimization and from the advanced Windows

and Linux

Enhanced Mode

The RS785E also supports an enhanced mode of operation that provides a higher graphics engine speed. The enhanced

mode requires a higher mamaximum core voltage and thermal design power. Refer to section 1.5, “Graphics Device ID

and Graphics Engine Clock Speed,” section 5.1, “Electrical Characteristics,” and section 5.2.1, “RS785E Thermal

Limits,” for details.

®

support available in the Radeon family drivers.

1.2 RS785E Features

1.2.1 CPU HyperTransport™ Interface

•

Supports 16-bit up/down HyperTransport (HT) 3.0 interface up to 4.4 GT/s.

• Supports 200, 400, 600, 800, and 1000 MHz HT1 frequencies.

• Supports 1.6, 1.8, 2.0, and 2.2 GHz HT3 frequencies.

• Supports AMD AM3 and S1g3-socket CPUs, including the AMD Phenom II and Caspian-series processors.

• Supports LDTSTOP interface and CPU link stutter mode.

RS785E Features

®

XP, Windows Vista®, Windows 7®,

1.2.2 Memory Interface

Supports an optional dedicated local frame buffer (side-port) of up to 128MB through a 16-bit interface. Note,

•

however, that the memory interface is optimized for a 64MB local frame buffer. As such, the system BIOS will

downsize the side-port size if a 128MB memory device is populated.

• New highly flexible memory architecture allows asymmetric side-port and shared system memory frame buffer sizes.

Supported configurations include UMA only and UMA+side-port (interleave mode).

• New dynamic memory allocation scheme improves performance and reduces power simultaneously.

• Support for DDR2 system memories up to DDR2-800, with a maximum memory clock speed of 364MHz. Memory

clock is independent of any other clock source and can therefore be set to any frequency equal to or less than

364MHz, allowing the use of lower speed side-port memories.

• Support for DDR3 system memories up to DDR3-800, with a maximum memory clock speed of 400MHz. Memory

clock is independent of any other clock source and can therefore be set to any frequency equal to or less than

400MHz (DDR3-800), allowing the use of lower speed side-port memories.

• Support one memory device of x16 width (see section 2.2.1.1, “Supported DDR2 Components,” on page 2-4.and

section 2.2.2.1, “Supported DDR3 Components,” on page 2-5, for details).

• Asynchronous HyperTransport and memory controller interface speeds.

• Supports DDR SDRAM self refresh mechanism.

• Supports dynamic CKE and ODT for power conservation.

1.2.3 AMD HyperMemory™

• Supports AMD HyperMemory™*.

* Note: Includes dedicated and shared memory. The amount of HyperMemory available is determined by various factors.

For details, please consult your AMD CSS representative.

1.2.4 PCI Express® Interface

•

Supports PCIe Gen2 (version 2.0).

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-2 Proprietary

Page 13

RS785E Features

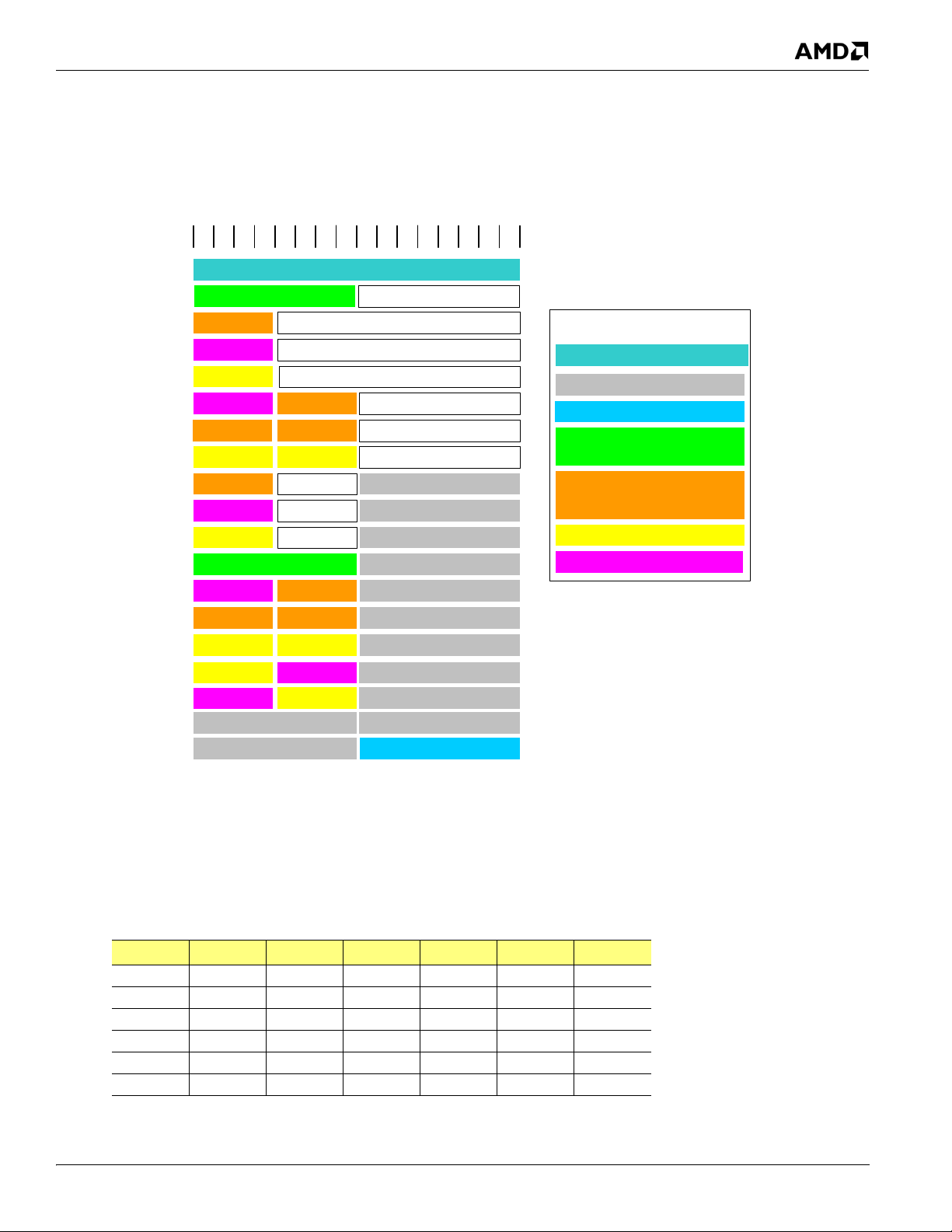

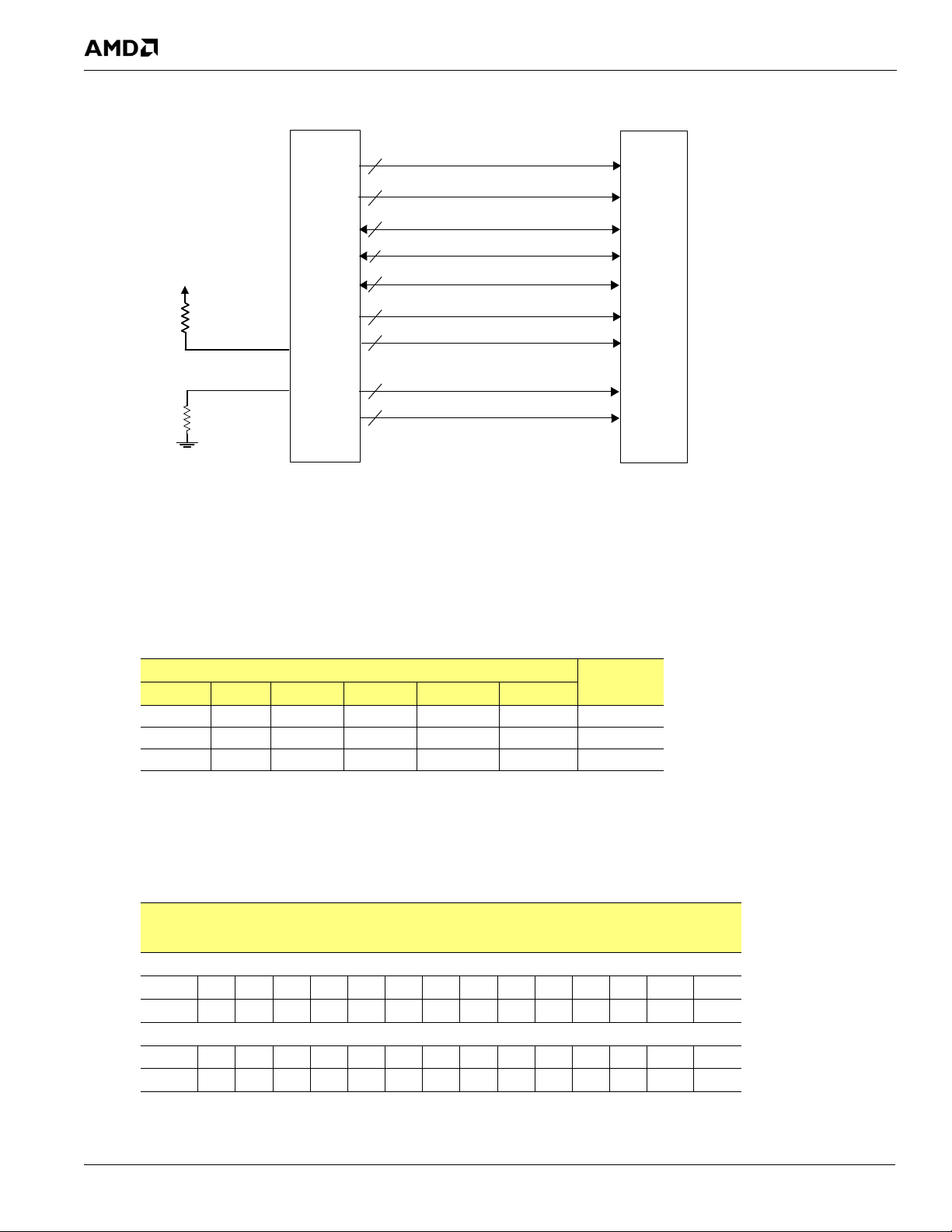

01 32 456789101112131415

PCI-E x16

PCI-E x8 External Graphics

DL-DVI

PCI-E x16 External Graphics

TMDS e nab lin g D u al-L in k

DVI (DL-D V I)

LEGEND

Not Used

TMDS enabling Single-Link

DVI (SL-DVI)

DisplayPort (DP)

TMDS enabling HDMI

PCI-E x16 Interface

HDMI

SL-DVI

Not Used

DP

DP

Not Used

SL-DVI Not Used

HDMI Not Used

DP Not Used

DL-DVI

PCI-E x8

SL-DVI

PCI-E x8

PCI-E x8

DPDP

HDMI Not Used

DP Not Used

SL-DVI Not Used

PCI-E x8

PCI-E x8

PCI-E x8

PCI-E GPP Device

PCI-E x8 PCI-E GPP Device

PCI-E x8

DP

PCI-E x8

DP

HDMI

HDMI

PCI-E x8 PCI-E x8

SL-DVI Not UsedSL-DVI

SL-DVIHDMI

PCI-E x8

SL-DVI

• Optimized peer-to-peer and general purpose link performance.

• Highly flexible PCI Express implementation to suit a variety of platform needs.

• A dual-port, x16 graphics interface, configurable to any one of the modes illustrated in Figure 1-1:

• Supports programmable lane reversal for the graphics link to ease motherboard layout when the end device does not

support lane reversal.

• Supports six general purpose lanes, for up to six devices on specific ports. Possible configurations are listed in

Table 1-1.

Table 1-1 Possible Configurations for the PCIe® General Purpose Links

GPP1 x4 x4 x2 x2 x2 x1

GPP2-----x1

GPP3 - - x2 x1 x2 x1

GPP4---x1-x1

GPP5 x2 x1 x2 x1 x1 x1

GPP6 - x1 - x1 x1 x1

Figure 1-1 Possible Configurations for the x16 PCIe

Config. B Config. C Config. C2 Config. E Config. K Config. L

®

Graphics Interface

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-3

Page 14

• Supports x1, x2, x4, x8, x12 and x16 polarity inversion.

1.2.5 A-Link Express II Interface

One x4 A-Link Express II interface for connection to an AMD Southbridge. The A-Link Express II is a proprietary

•

interface developed by AMD basing on the PCI Express technology, with additional Northbridge-Southbridge

messaging functionalities.

• Supports programmable lane reversal to ease motherboard layout.

1.2.6 2D Acceleration Features

•

Highly-optimized 128-bit engine, capable of processing multiple pixe ls per clock.

• Hardware acceleration of Bitblt, line drawing, polygon and rectangle fills, bit masking, monochrome expansion,

panning and scrolling, scissoring, and full ROP support (including ROP3).

• Optimized handling of fonts and text using AMD proprietary techniques.

• Game acceleration including support for Microsoft's DirectDraw

Blit, and Masked Blit.

• Acceleration in 1/8/15/16/32-bpp modes:

• Pseudocolor mode for 8bpp

• ARGB1555 and RGB565 modes for 16bpp

• ARGB8888 mode for 32bpp

• Significant increase in the High-End Graphics WinBench

• Setup of 2D polygons and lines.

• Support for GDI extensions:

• In Windows XP and Windows Vista: Alpha BLT, Transparent BLT, and Gradien t Fi ll.

RS785E Features

®

: Double Buffering, Virtual Sprites, Transparent

®

score due to capability for C18 color expansion.

• In Windows 7: Alpha BLT, Transparent BLT, Color Fill BLT, Stretch BLT, and Clear Type BLT.

• Hardware cursor (up to 64x64x32bpp), with alpha channel for direct support of Windows XP, Windows Vista and

Windows 7 alpha cursor.

1.2.7 3D Acceleration Features

•

DirectX 10.1 compliant, including full speed 32-bit floating point per component operations

• Shader Model 4.1 geometry and pixel support in a unified shader architecture:

• Full speed 32-bit floating point processing per component.

• High dynamic range rendering with floating point blending, texture filtering and anti-aliasing support.

• High performance dynamic branching and flow control.

• Nearly unlimited shader instruction store, using an advance caching system.

• Advanced shader design, with ultra-threading sequencer for high efficiency operations.

• Advanced, high performance branching support, including static and dynamic branching.

• 32-bit floating point components for high dynamic range computations.

• Full anti-aliasing on render surfaces up to and including 128-bit floating point formats.

• Support for OpenGL

®

2.0

• Anti-Aliasing Filtering:

• 2x/4x/8x modes.

• Sparse multi-sample algorithm with gamma correction, programmable sample patterns, and centroid sampling.

• Temporal anti-aliasing.

• Adaptive anti-aliasing mode.

• Lossless color compression (up to 8:1) at all resolutions, up to and including widescreen HDTV.

• Anisotropic Filtering:

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-4 Proprietary

Page 15

RS785E Features

• 2x/4x/8x/16x modes

• Up to 128-tap texture filtering.

• Adaptive algorithm with performance (bi-linear) and quality (tri-linear) options.

• Improved quality mode due to improved subpixel precision, higher precision LOD computation s, and

• Advanced Texture Compression (3Dc+™ ):

• High quality 4:1 compression for normal maps and luminance maps.

• Works with any single-channel or two-channel data format.

• HW support to overcome "Small batch" issues in CPU limited applications.

• 3D resources virtualized to a 32-bit addressing space, for support of large numbers of render targets and textures.

• New vertex cache and vertex fetch design, to increase vertex throughput from previous generations.

• Full support of 64-bit and 128-bit textures and surfaces, which can be 4x to 8x faster than previous generation of HW.

• Up to 8K x 8K textures, including 128 bpp texture are supported.

• New multi-level texture cache to give optimal performance, greater than 8x the previous designs.

• High efficiency ring bus memory controller:

• Programmable arbitration logic maximizes memory efficiency, software upgradeable.

• Fully associative texture, color, and Z cache design.

• New hierarchical Z and stencil buffers with early Z Test.

• New lossless Z-buffer compression for both Z and stencil.

• Fast Z-Buffer Clear.

• Z cache optimized for real-time shadow rendering.

• Z and color compression resources virtualized to a 32-bit addressing space, for support of multiple render targets

rotationally invariant LOD computations.

and textures simultaneously.

1.2.8 Motion Video Acceleration Features

Video scaling and fully programmable YCrCb to RGB color space conversion for full-speed video playback and fully

•

adjustable color controls.

• Adaptive de-interlacing eliminates video artifacts caused by displaying interlaced video on non-interlaced displays,

and by analyzing image and using optimal de-interlacing function on a per-pixel basis.

• Motion video acceleration for HD contents and Blu-ray technology.

• Dedicated UVD (Unified Video Decoder) 2.0 hardware for H.264,VC-1, and MPEG-2 decode:

• H.264 implementation is based on the ISO/IEC 14496-10 spec.

• VC-1 implementation is based on the SMPTE 421M spec.

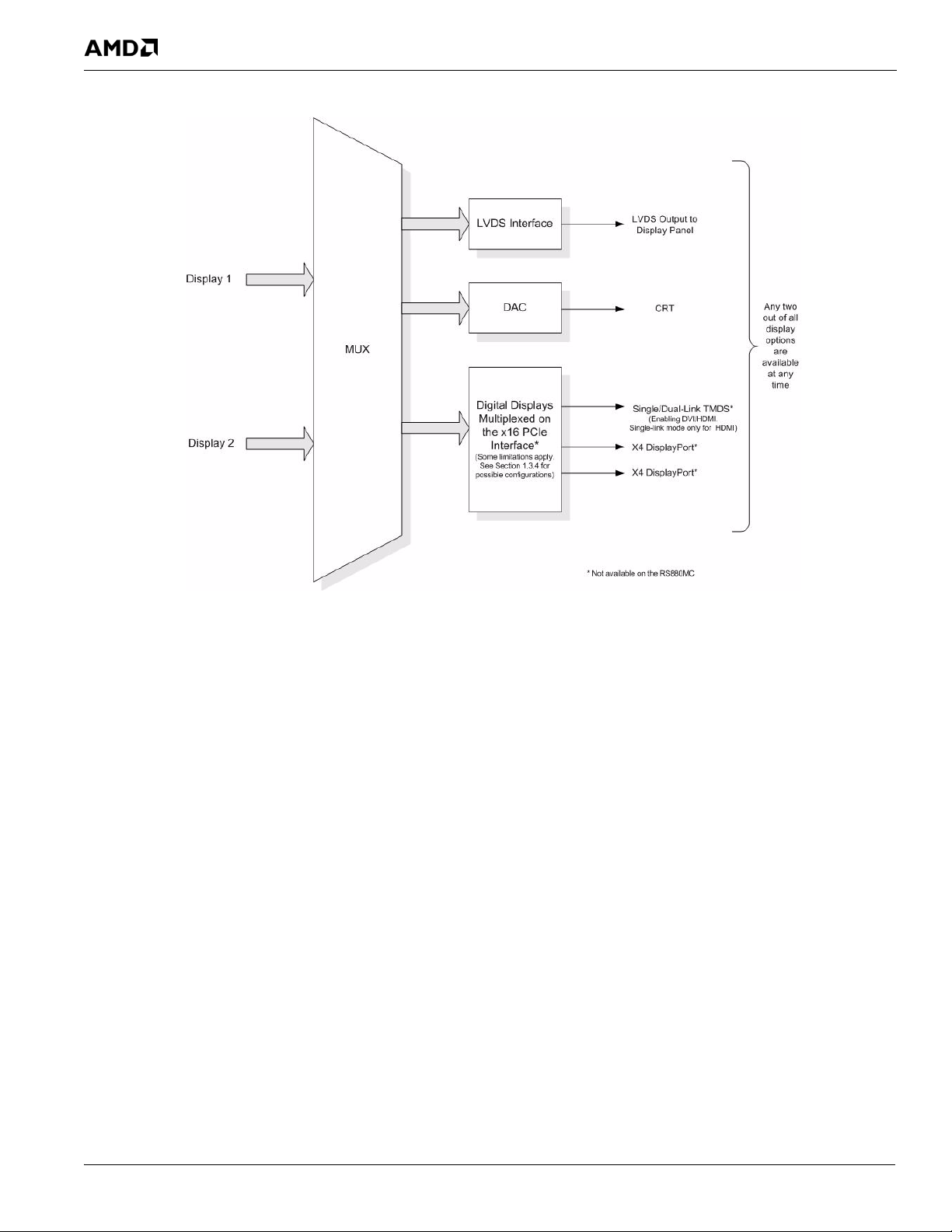

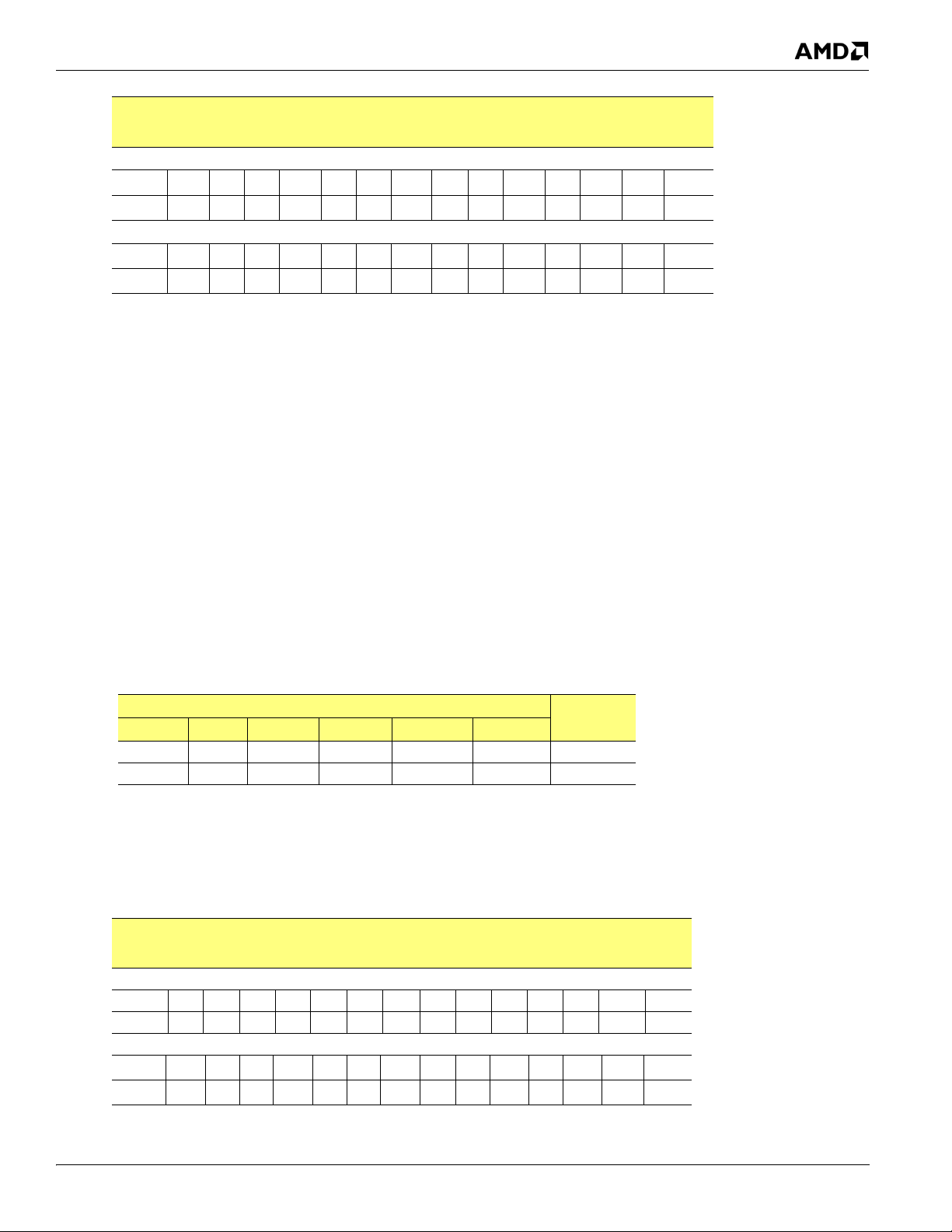

1.2.9 Multiple Display Features

General

• Dual independent displays. Possible configurations are illustrated in Figure 1-2.

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-5

Page 16

RS785E Features

Figure 1-2 RS785E Multiple Display Options

• Resolution, refresh rates, and display data can be completely independent for the two display paths.

• Each display controller supports true 30 bits per pixel throughout the display pipe.

• Each display path supports VGA and accelerated modes, video overlay, hardware cursor, hardware icon, and palette

gamma correction.

• Supports both interlaced and non-interlaced displays.

• Full ratiometric expansion ability is supported for source desktop modes up to 1920 pixels/line.

• Maximum DAC frequency of 400 MHz.

• Supports 8, 16, 32, and 64-bpp depths for the main graphics layer:

• For 32-bpp depth, supports xRGB 8:8:8:8, xRGB 2:10:10:10, sCrYCb 8:8:8:8, and xCrYCb 2:10:10:10 data

formats.

• For 64-bpp depth, supports xRGB 16:16:16:16 data format.

• Independent gamma, color conversion and correction controls for main graphics layer.

• Support for DDC1 and DDC2B+ for plug and play monitors.

• 8-bit alpha blending of graphics and video overlay.

• Hardware cursor up to 64x64 pixels in 2 bpp, full color AND/XOR mix, and full color 8-bit alpha blend.

• Hardware icon up to 128x128 pixels in 2 bpp, with two colors, transparent, and inverse transparent. AND/XOR

mixing. Supports 2x2 icon magnification.

• Virtual desktop support.

• Support for flat panel displays via VGA.

• Configurable to support flat panel displays or TVs via DVI/HDMI.

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-6 Proprietary

Page 17

RS785E Features

• Integrated HD audio controller for HDMI audio data.

VGA Output

• Maximum resolutions supported by the VGA output for different refresh rates are:

• 2048x1536 @85Hz (pixel clock at 388.5MHz) for 4:3 format

• 2560x1440 @75Hz (pixel clock at 397.25MHz) for 16:9 format

• 2456x1536 @60Hz (pixel clock at 320MHz) for 16:10 format

1.2.10 Integrated LVDS Interface

•

Integrated dual-link 24-bit LVDS interface.

• 110 MHz pixel clock rate per link; up to 220 MHz for dual-link mode.

• FPDI-2 compliant; compatible with receivers from National Semiconductor, Texas Instruments, and THine.

• OpenLDI compliant excluding DC balancing.

• Programmable internal spread spectrum controller for the signals.

1.2.11 DVI/HDMI™

• Supports a TMDS interface, enabling DVI or HDMI* (passing HDMI CTS v1.3b), which is multiplexed on the PCIe

external graphics interface.

• 1620 Mbps/channel with 162 MHz pixel clock rate per link.

• Supports industry standard EIA-861B video modes including 480p, 720p, 1080i, and 1080p (for a full list of currently

supported modes, contact you AMD CSS representative). Maximum resolutions supported by various modes are:

• Single-link DVI: 1600x1200 @60Hz with standard timings, and 1920x1200 @60Hz with reduced blanking

timings.

• Dual-link DVI: 2560x1600 @60Hz.

• HDMI: 1080p.

• Supports YCbCr 4:4:4 and 4:2:2 modes with HDMI.

• HDMI basic audio support at 32, 44.1 or 48 kHz. Supports two-channel uncompressed audio data, and, for Windows

Vista platforms only, 5.1-channel audio data and DTS. HD audio device compatible with the Microsoft HD audio

driver.

• HDCP support for two independent display streams with on-chip key storage. Also available when the TMDS

interface runs in dual-link mode.**

Notes: * CEC is not supported.

** HDCP content protection support is only available to HDCP licensees and can only be enabled when connected

to an HDCP-capable receiver.

1.2.12 DisplayPort™ Interface

•

Supports all mandatory features of the VESA DisplayPort Standard, Version 1.1, plus the following optional features:

• 10-bit support.

• YCbCr 4:4:4 and 4:2:2 support.

• HDCP support

• Optional test pattern support.

• Supports two independent displays over the PCIe interface for external graphics (see Figure 1-1,“Possible

Configurations for the x16 PCIe® Graphics Interface,” on page 1-3 for details).

• Supports 4, 2, or 1-lane transmission.

• Supports both the 2.7 Gbps and 1.62 Gbps link symbol rates.

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-7

Page 18

• Supports the Auxiliary Channel (AUX CH).

• Supports a maximum resolution of 2560x1600 @60Hz with 4 lanes.

• Supports Embedded DisplayPort™ (eDP™) features as described in the VESA eDP Standard, Version 1.

1.2.13 Integrated HD Audio Controller and Codec

•

Integrated HD Audio codec supports linear PCM and AC3 (5.1) audio formats for HDMI output.

• Separate logical chip function.

• Can encrypt data onto one associated HDMI output.

• Uses Microsoft UAA driver.

• Internally connected to the integrated HDMI, or HDMI-enabled interface, hence no external cable required.

• Support for basic audio (32, 44.1 or 48 KHz stereo) and AC3 or DTS at the same sample rates.

1.2.14 System Clocks

•

Support for an external clock chip to generate side-port memory, PCIe, and A-Link Express II clocks. Alternatively,

internal generation for these clocks, with clock input from an SB800-series Southbridge, can be used (subject to

characterization with actual RS785E and SB800-series devices).

1.2.15 Power Management Features

RS785E Features

•

Single chip solution in 55nm, 1.1V CMOS technology.

• Supports ACPI 2.0 for S0, S3, S4, and S5 states.

• Full IAPC (Instantly Available PC) power management support.

• Static and dynamic power management support (APM as well as ACPI) with full VESA DPM and Energy Star

compliance.

• The Chip Power Management Support logic supports four device power states defined for the OnNow Architecture—

On, Standby, Suspend, and Off. Each power state can be achieved by software control bits.

• Hardware controlled intelligent clock gating enables clocks only to active fun ctional blocks, and is completely

transparent to software.

• Dynamic self-refresh for the side-port memory.

• Support for Cool'n'Quiet™ via FID/VID change.

• Support for AMD PowerNow!™.

• Clocks to every major functional block are controlled by a unique dynamic clock switching technique that is

completely transparent to the software. By turning off the clock to the block that is idle or not used at that point, the

power consumption can be significantly reduced during normal operation.

• Supports AMD Vari-Bright™, AMD PowerXpress™, and AMD PowerPlay™ (enhanced with the AMD

PowerShift™ feature).

• Supports dynamic lane reduction for the PCIe graphics interface when coupled with an AMD-based graphics device,

adjusting lane width according to required bandwidth.

1.2.16 PC Design Guide Compliance

The RS785E complies with all relevant Windows Logo Program (WLP) requirements from Microsoft for WHQL

certification.

1.2.17 Test Capability Features

The RS785E has a variety of test modes and capabilities that provide a very high fault coverage and low DPM (Defect Per

Million) ratio:

• Full scan implementation on the digital core logic through ATPG (Automatic Test Pattern Generation Vectors).

• Dedicated test logic for the on-chip custom memory macros to provide complete coverage on these modules.

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-8 Proprietary

Page 19

Software Features

• A JTAG test mode to allow board level testing of neighboring devices.

• An EXOR tree test mode on all the digital I/O's to allow for proper soldering verification at the board level.

• A VOH/VOL test mode on all digital I/O’s to allow for proper verification of output high and output low values at the

board level.

• Access to the analog modules to allow full evaluation and characterization.

• IDDQ mode support to allow chip evaluation through current leakage measurements.

These test modes can be accessed through the settings on the instruction register of the JTAG circuitry.

1.2.18 Additional Features

•

Integrated spread spectrum PLLs on the memory and LVDS interface.

1.2.19 Packaging

Single chip solution in 55nm, 1.1V low power CMOS technology.

•

• 528-FCBGA package, 21mmx21mm.

1.3 Software Features

• Supports Microsoft Windows XP, Windows Vista, Windows 7, and Linux.

• BIOS ability to read EDID 1.1, 1.2, and 1.3.

• Ability to selectively enable and disable several devices including CRT, LCD, and DFP.

• Register-compatible with VGA standards, BIOS-compatible with VESA VBE2.0.

• Supports corporate manageability requirements such as DMI.

• ACPI support.

• Full Write Combining support for maximum performance of the CPU.

• Full-featured, yet simple Windows utilities:

• Calibration utility for WYSIWYG color

• Independent brightness control of desktop and overlay

• End user diagnostics

• Drivers meet Microsoft's rigorous WHQL criteria and are suitable for systems with the "Designed for Windows"

logos.

• Comprehensive OS and API support.

• Hot-key support (Windows ACPI 2.0 or AMD Event Handler Utility where appropriate).

• Extensive power management support.

• Rotation mode support in software.

• Dual CRTC, simultaneous view, extended desktop support (Windows XP, Windows Vista, and Windows 7)

• DirectX 10.1 support.

• Switchable overlay support.

• H.264 playback support.

• Supports AMD OverDrive™ utility.

***Warning*** AMD and ATI processors are intendedto be operated only within their associated specifications and factory settings. Operating the AMD or ATI processor outside of specification or in

excess of factory settings, including but not limited to overclocking, may damage the processor and/or lead to other problems, including but not limited to, damage to the system components (including the

motherboard and components thereon (e.g. memory)), system instabilities (e.g. data loss and corrupted images), shortened processor, system component and/or system life and in extreme cases, total

system failure. AMD does not provide support or service for issues or damages related to use of an AMD or ATI processor outside of processor specifications or in excess of factory settings.

• Supports Hybrid CrossFire™ .

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-9

Page 20

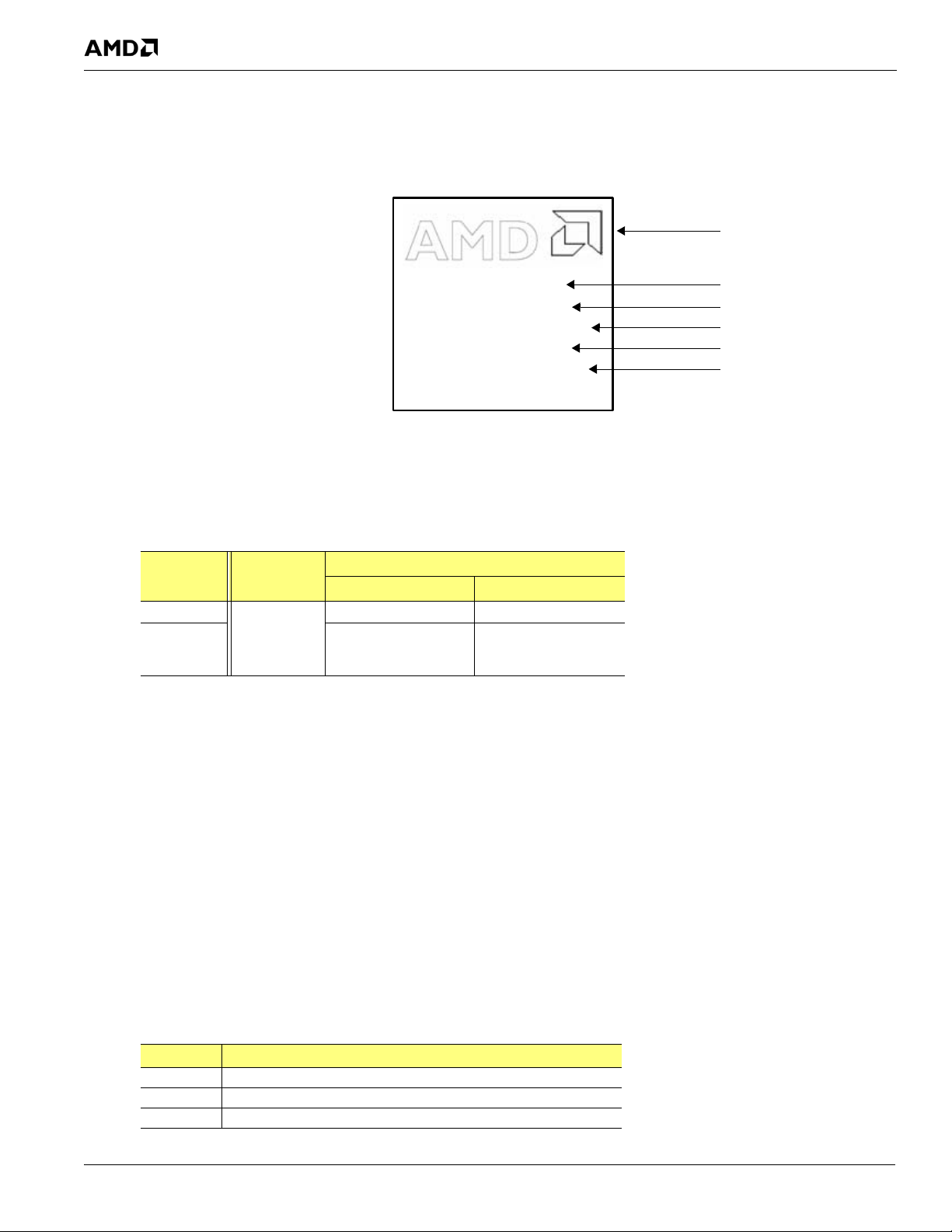

1.4 Branding Diagram

RADEON IGP

YYWW

MAD E IN T AIWA N

WXXXXX

216-0752001

* YY - Assembly Start Year

WW - Assembly Start Week

Part Number

Date Code*

AMD Product Type

AMD Logo

Wafer Lot Number

Country of Origin

Note: The branding can be in laser, ink, or mixed laser-and-ink marking.

Branding Diagram

Figure 1-3 RS785E ASIC A11 Production Branding

1.5 Graphics Device ID and Graphics Engine Clock Speed

Table 1-2 Graphics Device ID and Graphics Engine Clock Speed

Variant

RS785E

RS785E

(Enhanced

Mode)

Note:

* The maximum graphics engine clock speed of 590 MHz of the enhanced mode requires the core

voltage to go up to 1.25V.

Graphics

Device ID

0x9712

Graphics Engine Clock Speed ( MHz)

Min. Max.

200 500

200 590*

1.6 Conventions and Notations

The following conventions are used throughout this manual.

1.6.1 Pin Names

Pins are identified by their pin names or ball references. Multiplexed pins sometimes assume alternate “functional names”

when they perform their alternate functions, and these “functional names” are given in Chapter 3, “Pin Descriptions and

Strap Options.”

All active-low signals are identified by the suffix ‘#’ in their names (e.g., MEM_RAS#).

1.6.2 Pin Types

The pins are assigned different codes according to their operational characteristics. These codes are listed in Table 1-3.

Table 1-3 Pin Type Codes

I Digital Input

O Digital Output

OD Open Drain

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-10 Proprietary

Code Pin Type

Page 21

Conventions and Notations

Table 1-3 Pin Type Codes (Continued)

Code Pin Type

I/O Bi-Directional Digital Input or Output

I/OD Digital Input or Open Drain

M Multifunctional

Pwr Power

Gnd Ground

A-O Analog Output

A-I Analog Input

A-I/O Analog Bi-Directional Input/Output

A-Pwr Analog Power

A-Gnd Analog Ground

Other Pin types not included in any of the categories above

1.6.3 Numeric Representation

Hexadecimal numbers are appended with “h” (Intel assembly-style notation) whenever there is a risk of ambiguity. Other

numbers are in decimal.

Pins of identical functions but different running integers (e.g., “GFX_TX7P, GFX_TX6P,... GFX_TX0P”) are referred to

collectively by specifying their integers in square brackets and with colons (i.e., “GFX_TX[7:0]P”). A similar short-hand

notation is used to indicate bit occupation in a register. For example, NB_COMMAND[15:10] refers to the bit positions

10 through 15 of the NB_COMMAND register.

1.6.4 Register Field

A field of a register is referred to by the format of [Register Name].[Register.Field]. For example,

“NB_MC_CNTL.DISABLE_BYPASS” is the “DISABLE_BYPASS” field of the register “NB_MC_CNTL.”

1.6.5 Hyperlinks

Phrases or sentences in blue italic font are hyperlinks to other parts of the manual. Users of the PDF version of this manual

can click on the links to go directly to the referenced sections, tables, or figures.

1.6.6 Acronyms and Abbreviations

The following is a list of the acronyms and abbreviations used in this manual.

Table 1-4 Acronyms and Abbreviations

Acronym Full Expression

ACPI Advanced Configuration and Power Interface

A-Link-E A-Link Express interface between the IGP and the Southbridge.

BGA Ball Grid Array

BIOS

BIST Built In Self Test.

BLT Blit

bpp bits per pixel

CEC Consumer Electronic Control

CPIS Common Panel Interface Specification

CRT Cathode Ray Tube

CSP Chip Scale Package

DAC Digital to Analog Converter

DBI Dynamic Bus Inversion

Basic Input Output System. Initialization code stored in a ROM or Flash RAM used to start up a

system or expansion card.

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-11

Page 22

Table 1-4 Acronyms and Abbreviations (Continued)

Acronym Full Expression

DDC

DDR Double Data Rate

DFP Digital Flat Panel. Monitor connection standard from VESA.

DP DisplayPort

DPM Defects per Million

DTV Digital TV

DVD Digital Video Disc

DVI

DVS Digital Video Stream

eDP Embedded DisplayPort

EPROM Erasable Programmable Read Only Memory

FIFO First In, First Out

FPDI Flat Panel Display Interface

GDI Graphics Device Interface

GND Ground

GPIO General Purpose Input/Output

HDCP High-Bandwidth Digital Content Protection

HDMI High Definition Multimedia Interface

HDTV High Definition TV. The 1920x1080 and the 1280x720 modes defined by ATSC.

HPD Hot Plug Detect

iDCT inverse Discrete Cosine Transform

IDDQ Direct Drain Quiescent Current

IGP

JTAG Joint Test Access Group. An IEEE standard.

LVDS Low Voltage Differential Signaling

MB Mega Byte

MPEG

NTSC

PAL Phase Alter nate Line. The standard definition TV system used in Europe and other areas.

PCI Peripheral Component Interface

PCIe PCI Express

PCMCIA

PLL Phase Locked Loop

POST Power On Self Test

PD Pull-down Resistor

PU Pull-up Resistor

ROP Raster Operation

SDRAM Synchronous Dynamic RAM

TMDS Transition Minimized Differential Signaling

UMA Unified Memory Architecture

UV Chrominance (also CrCb). Corresponds to the color of a pixel.

UVD Unified Video Decoder

UXGA Ultra Extended Graphics Array

VBI Vertical Blank Interval

VESA Video Electronics Standards Association

Display Data Channel. A VESA standard for communicating between a computer system and

attached display devices.

Digital Video Interface. Monitor connection standard from the DDWG (Digital Display Work

Group).

Integrated Graphics Processor. A single device that integrates a graphics processor and a

system controller.

Motion Pictures Experts Group. Refers to compressed video image streams in either MPEG-1

or MPEG-2 formats.

National Television Standards Committee. The standard definition TV system used in North

America and other areas.

Personal Computer Memory Card International Association. It is also the name of a standard

for PC peripherals promoted by the Association.

Conventions and Notations

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-12 Proprietary

Page 23

Conventions and Notations

Table 1-4 Acronyms and Abbreviations (Continued)

Acronym Full Expression

VGA Video Graphics Adapter

VRM Voltage Regulation Module

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 1-13

Page 24

This page is left blank intentionally.

Conventions and Notations

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

1-14 Proprietary

Page 25

Chapter 2

HyperTransport™

Unit

CPU

Interface

Register Interface

UVD**

Setup

Engine2DEngine

3D

Engine

Overlay

Root

MUX

Display 1& 2

CRT

Memory Controller

AMD CPU

BIF

Complex

Optional 16-bit

DDR2/DDR3

Memory Channel*

TMDS, enabling DVI/HDMI

SB

A-Link-E II

Interface

GPP Interface

PCIe

®

(6 x 1 Lanes)

Expansion

Slots or

On-board

Devices

(1 x 4 Lanes)

DisplayPorts

(Multiplexed on PCIe

®

Gfx Lanes)

(Multiplexed on PCIe

®

Gfx Lanes)

LVDS

External

Graphics

Gfx Interface

PCIe

®

(1x16 or 2x8 Lanes)

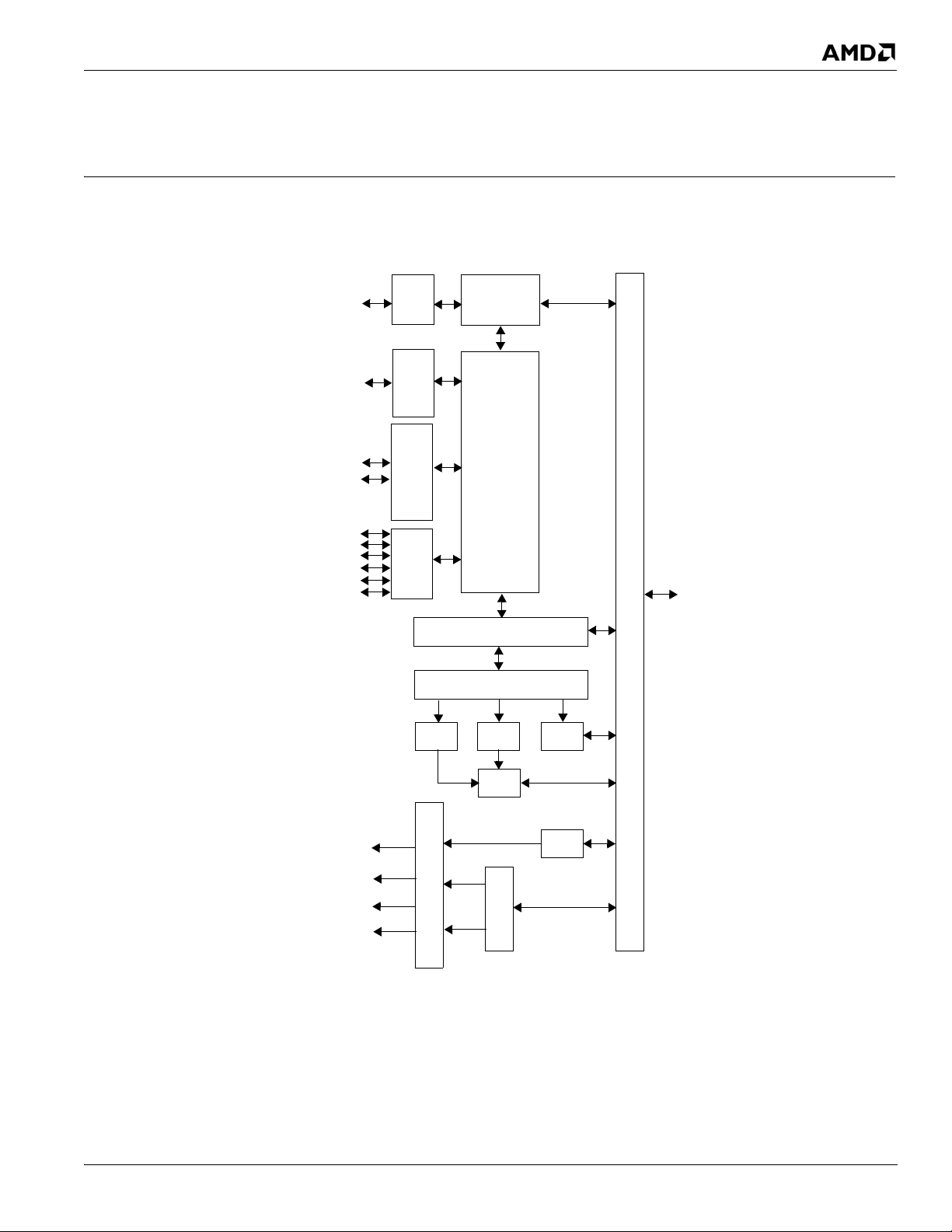

Functional Descriptions

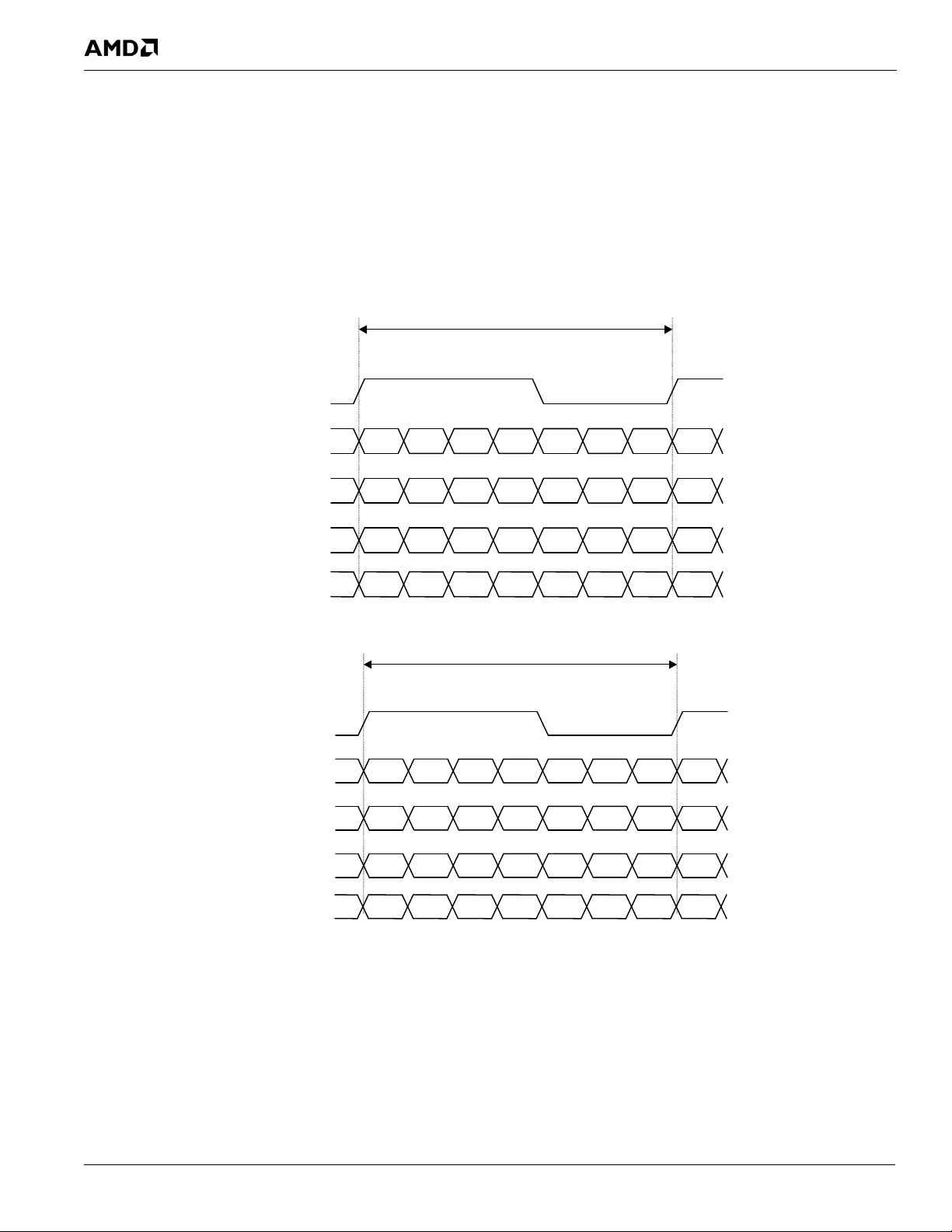

This chapter describes the functional operation of the major interfaces of the RS785E system logic. Figure 2-1, “RS785E

Internal Block Diagram,” illustrates the RS785E internal blocks and interfaces.

Figure 2-1 RS785E Internal Block Diagram

© 2010 Advanced Micro Devices, Inc. 47991 AMD RS785E Databook 1.30

Proprietary 2-1

Page 26

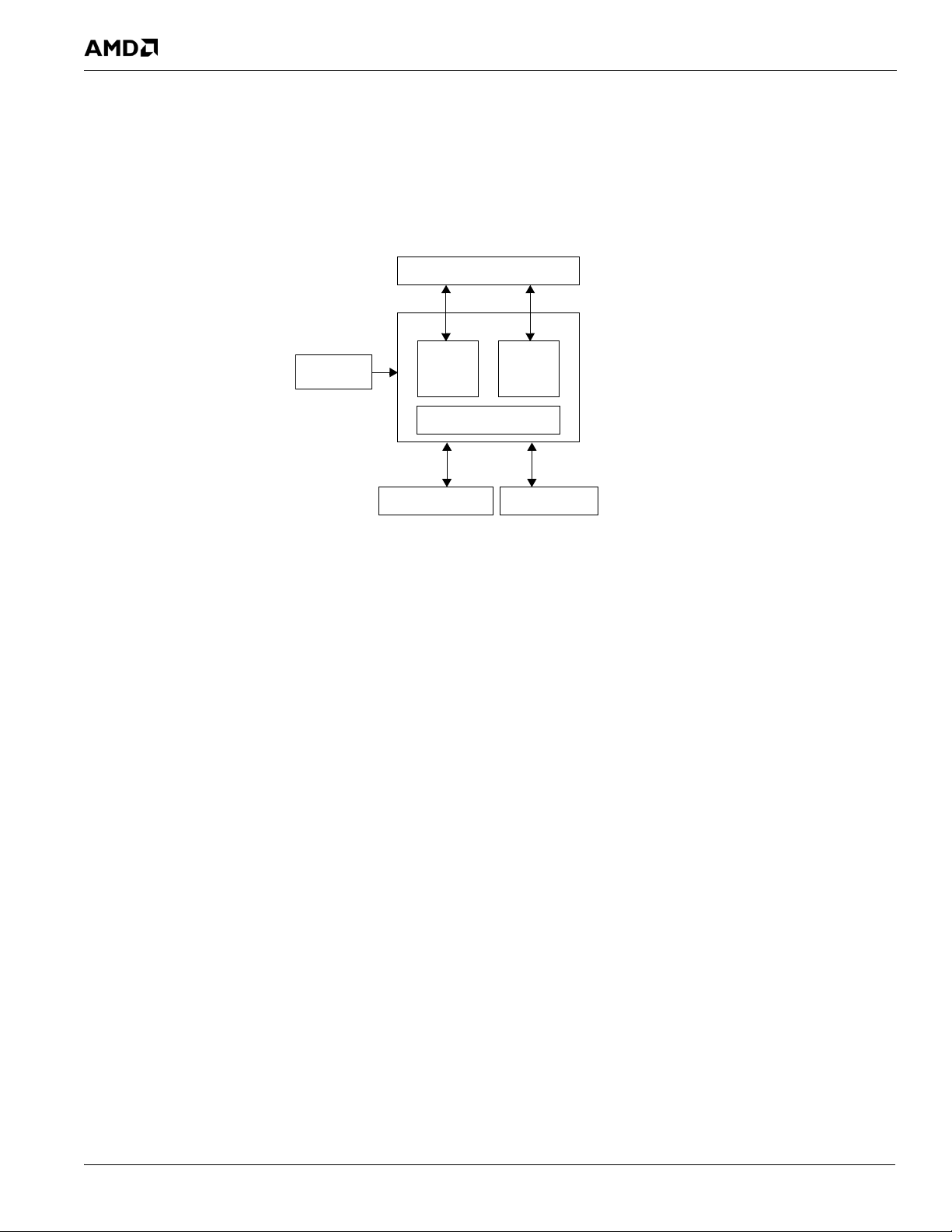

2.1 Host Interface

HT Interface to CPU (PHY)

Configuration

Registers

Root Complex

Memory Controller

LTA

LRA

SCH

Data Link Layer

Protocol/Transacti o n La ye r

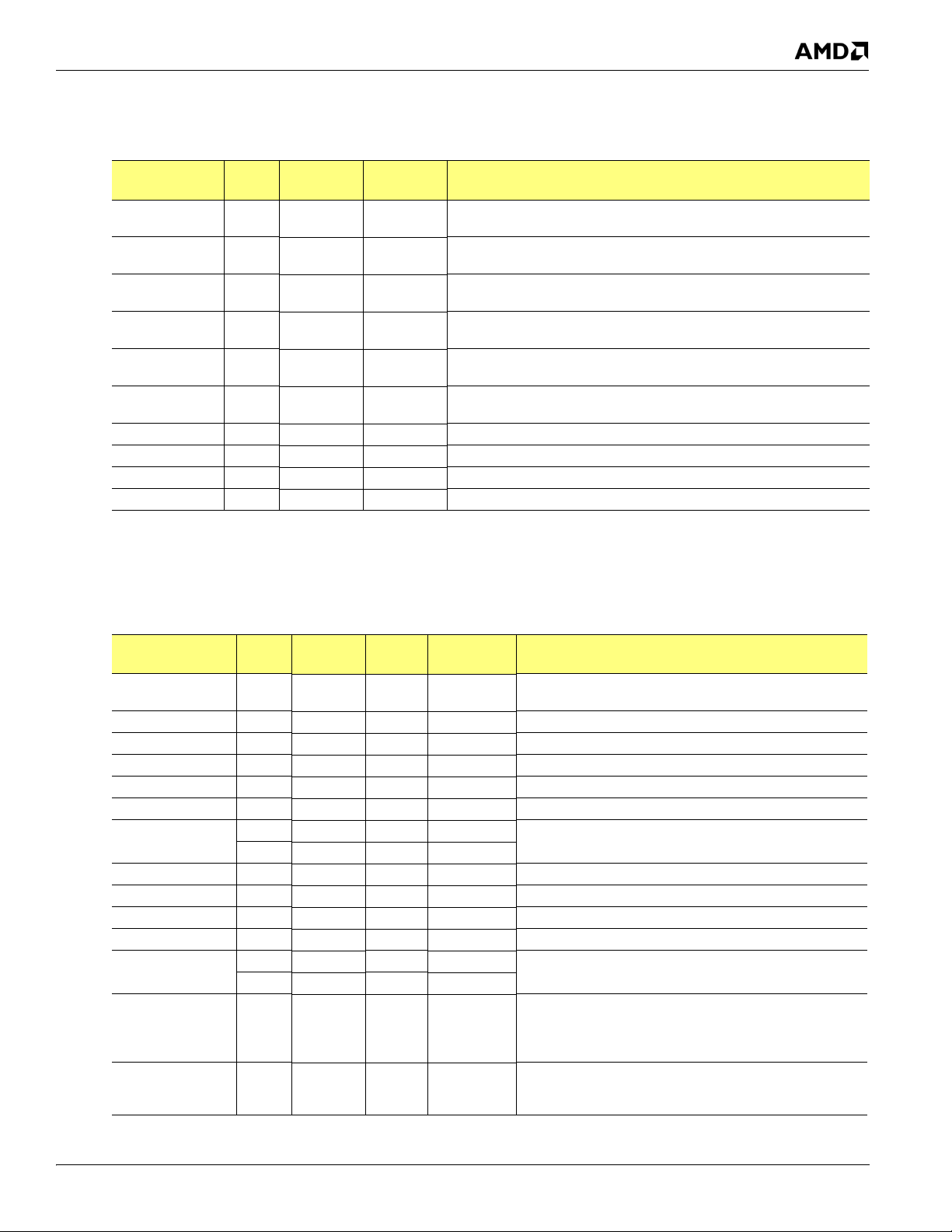

The RS785E is optimized to interface with AMD processors through the HyperTransport

presents an overview of the HyperTransport

HyperTransport I/O Link Specification from the HyperTransport Consortium. Figure 2-2, “Host Interface Block

Diagram,” illustrates the basic blocks of the host bus interface of the RS785E.

Host Interface

TM

TM

interface. For a detailed description of the interface, please refer to the

interface. This section

Figure 2-2 Host Interface Block Diagram

The HyperTransport (HT) Interface, formerly known as the LDT (Lightning Data Transport) interface, is a high speed,

packet-based link implemented on two unidirectional buses. It is a point-to-point interface where data can flow both

upstream and downstream at the same time. The commands, addresses, and data travel in packets on the HyperTransport

link. Lengths of packets are in multiples of four bytes. The HT link consists of three parts: the physical layer (PHY), the

data link layer, and the protocol/transaction layer. The PHY is the physical interface between the RS785E and the CPU.

The data link layer includes the initialization and configuration sequences, periodic redundancy checks,

connect/disconnect sequences, and information packet flow controls. The protocol layer is responsible for maintaining

strict ordering rules defined by the HT protocol.

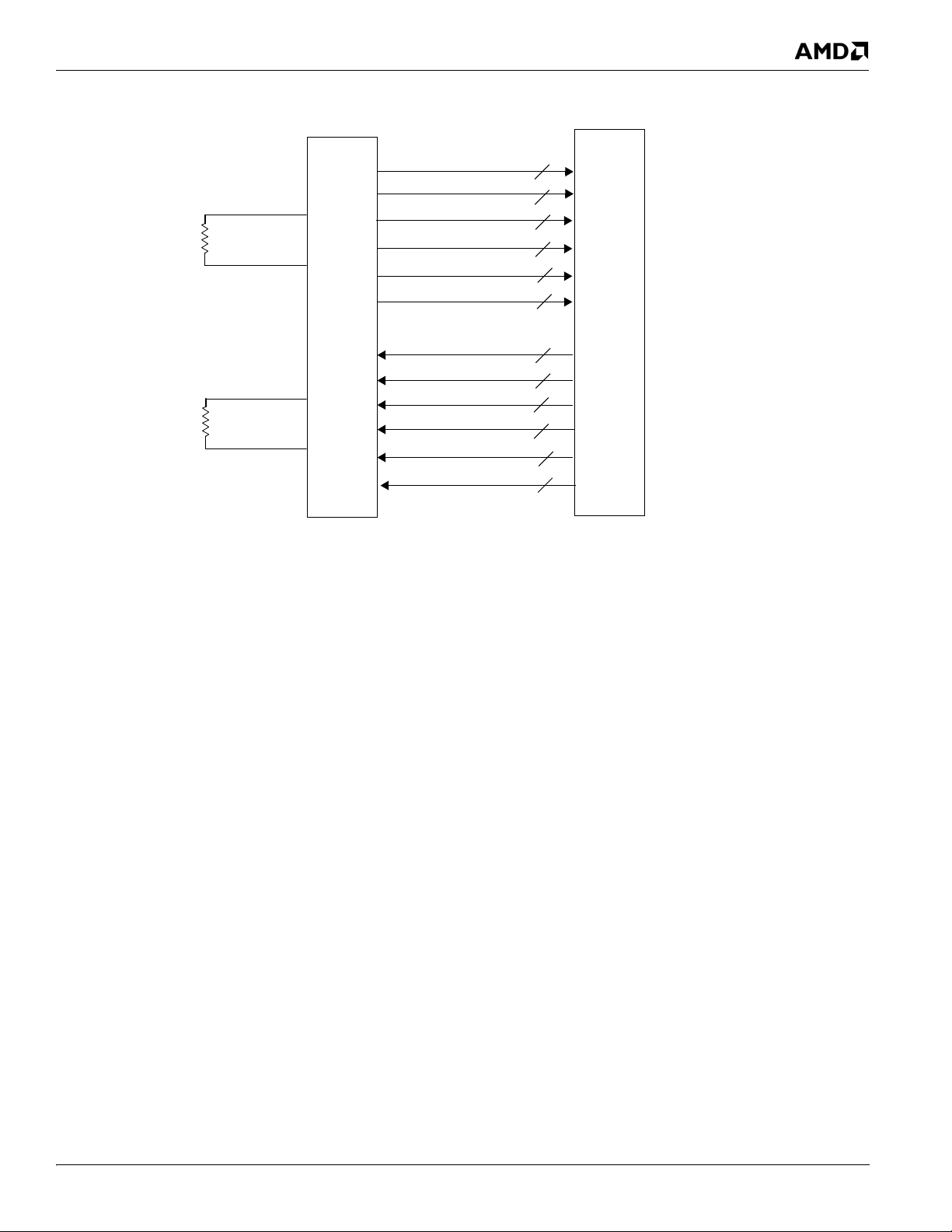

The RS785E HyperTransport bus interface consists of eighteen unidirectional differential data/control pairs and two

differential clock pairs in each of the upstream and downstream direction. On power up, the HT link is 8-bit wide and runs

at a default speed of 400MT/s. After negotiation, carried out by the HW and SW together, the link width can be brought

up to 16-bit and the interface can run up to 4.4GT/s. The interface is illustrated in Figure 2-3, “RS785E Host Bus

Interface Signals.” The signal name and direction for each signal is shown with respect to the processor. Note that the

signal names may be different from those used in the pin listing of the RS785E. Detailed descript ions of the si gnals are

given in section 3.3, “CPU HyperTransport™ Interface‚’ on page 3-5.

47991 AMD RS785E Databook 1.30 © 2010 Advanced Micro Devices, Inc.

2-2 Proprietary

Page 27

Side-Port Memory Interface

HT_RXCADN

2

2

RS785E

CPU

HT_RXCADP

HT_RXCTLN

HT_RXCTLP

HT_RXCLKN

HT_RXCLKP

16

16

HT_TXCADN

2

2

HT_TXCADP

HT_TXCTLN

HT_TXCTLP

HT_TXCLKN

HT_TXCLKP

16

16

2

2

2

2

HT_TXCALP

HT_RXCALN

HT_RXCALP

HT_TXCALN

2.2 Side-Port Memory Interface

In order to significantly decrease system power and increase graphics performance, the RS785E provides an optional

side-port memory interface for dedicated frame buffer memory, to be used exclusively for the integrated graphics core.

The side-port memory interface can significantly reduce system power by allowing the CPU to stay in its lowest power

state during periods of inactivity. Screen refreshes are fetched from the side-port memory, and there is no need to "wake

up" the CPU to fetch screen refresh data.

The RS785E memory controller is unique and highly optimized. It operates in 16-bit mo de at very high speed (up to

DDR2-800 and DDR3-800), and has a programmable interleaved mode that significantly increases the memory

bandwidth and reduces data latency to the integrated graphics core. The additional bandwidth provided to the internal

graphics core will also aid the RS785E in reaching and exceeding Microsoft's Windows Vista

requirements.

2.2.1 DDR2 Memory Interface

Figure 2-4, “RS785E Side-Port Memory Interface,” on page 2-4 illustrates the side-port memory interface of the

RS785E.

RS785E memory controller features and limitations:

• Supports a single memory device up to 128MB of physical size. However, as the memory interface is

optimized for a 64MB local frame buffer, the system BIOS will downsize the side-port memory if a 128MB

memory device is populated.

• Controls a single rank of DDR2 devices in 16-bit memory configuration.

• Supports device sizes of 256, 512, and 1024 Mbits, and a device width of x16.

• As the memory controller supplies only one chip select signal, only devices with one chip selec t are supp orte d.

• A wide range of DDR2 timing parameters, configurations, and loadings are programmable via the RS785E

memory controller configuration registers.