Page 1

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

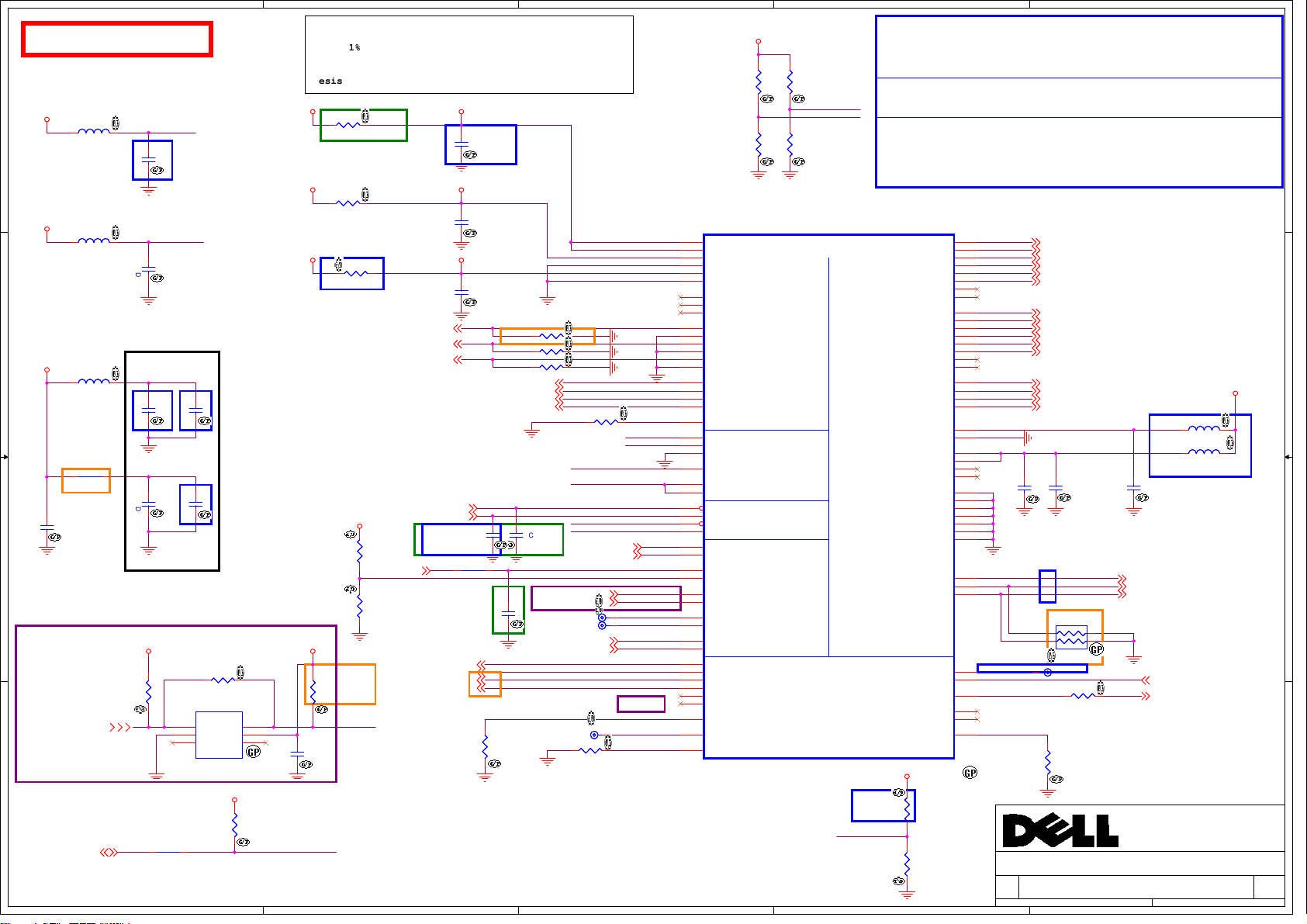

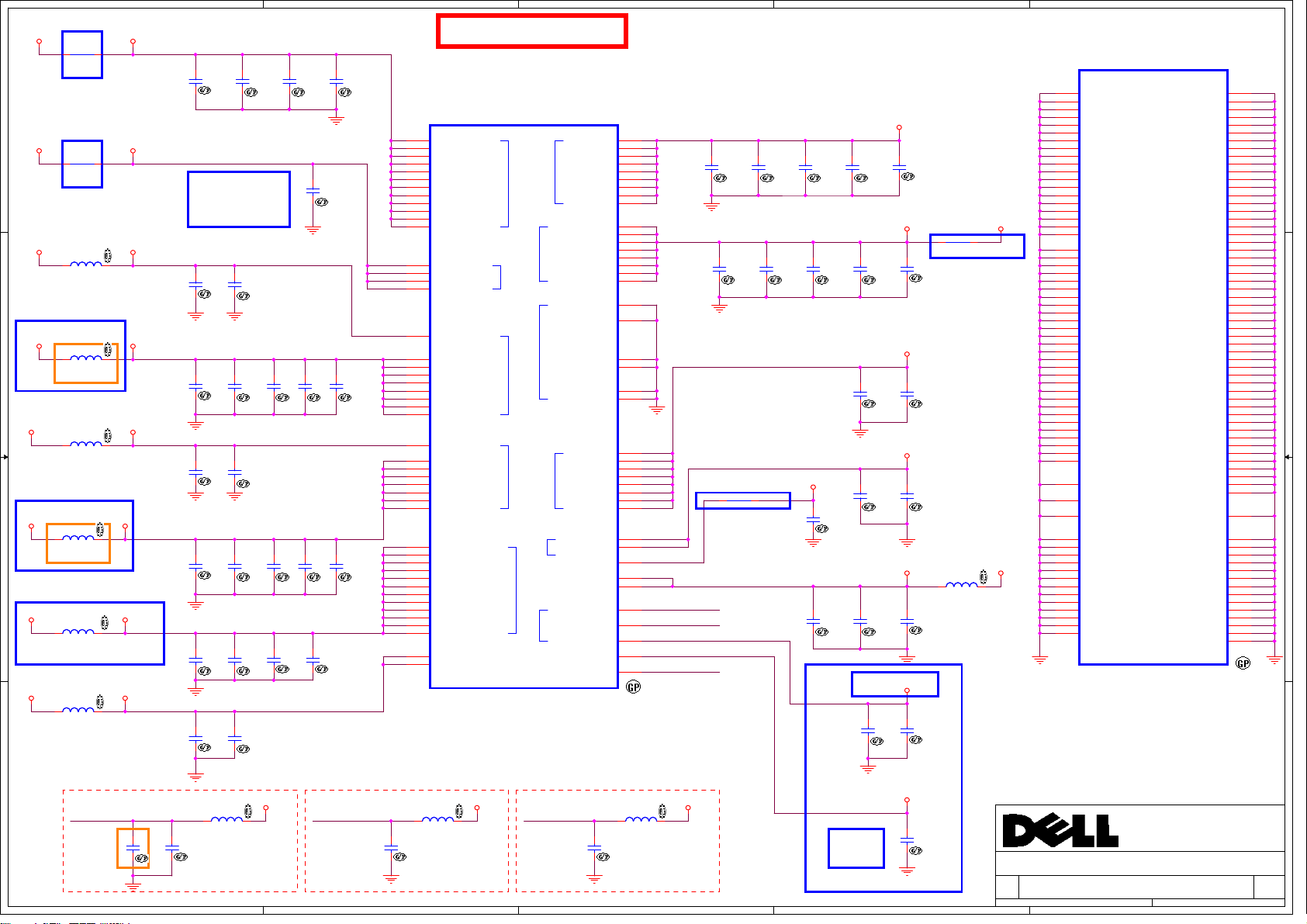

Berry Discrete/UMA Schematics Document

D D

AMD Danube CPU S1g4

AMD GPU Madison-LP/M96-LP M2

C C

RS880M + SB820M

2010-03-08

B B

REV : A00

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

DY : Nopop Component

5

4

3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cover Page

Cover Page

Cover Page

1 95Monday, March 08, 2010

1 95Monday, March 08, 2010

1 95Monday, March 08, 2010

1

A00

A00

A00

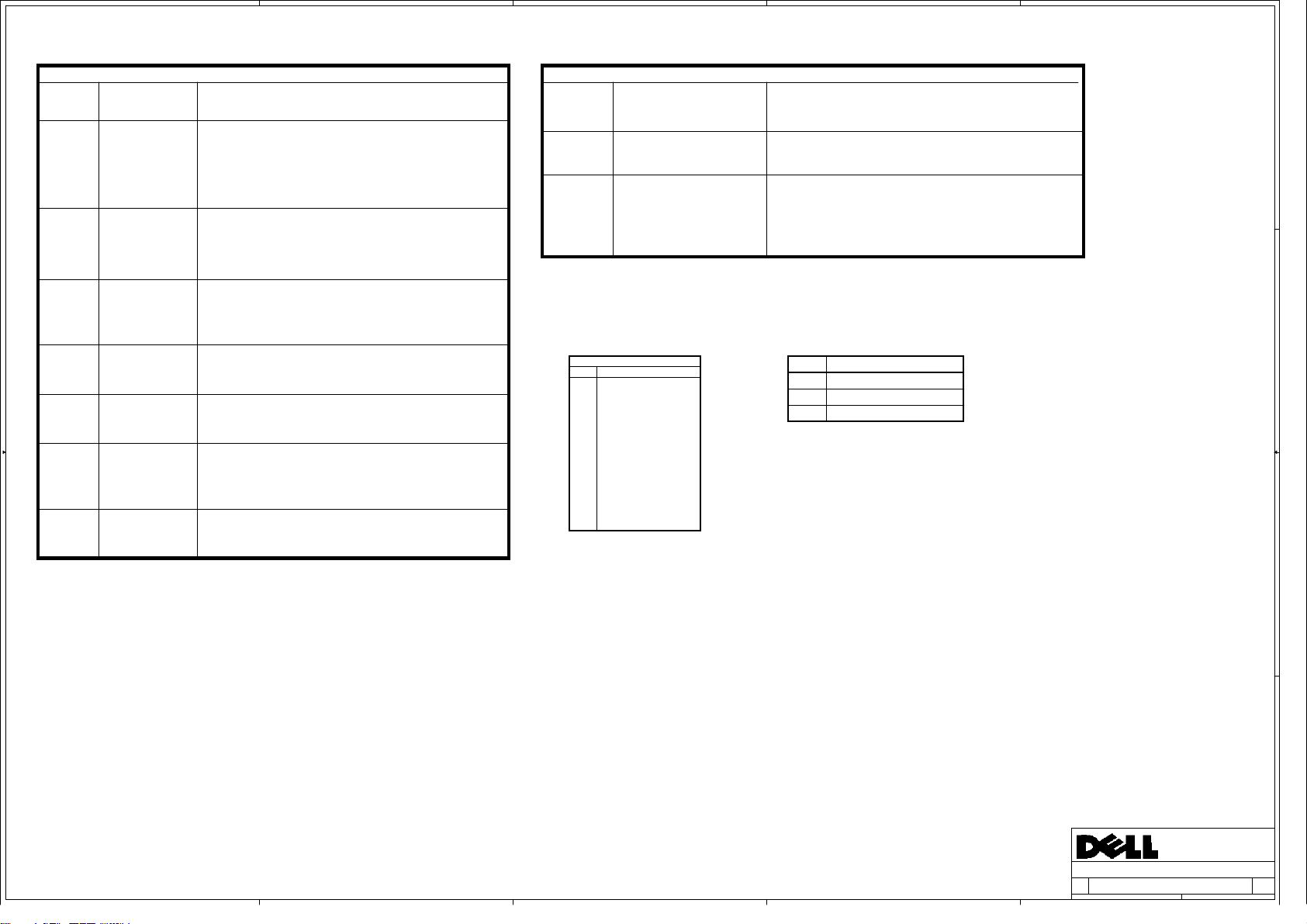

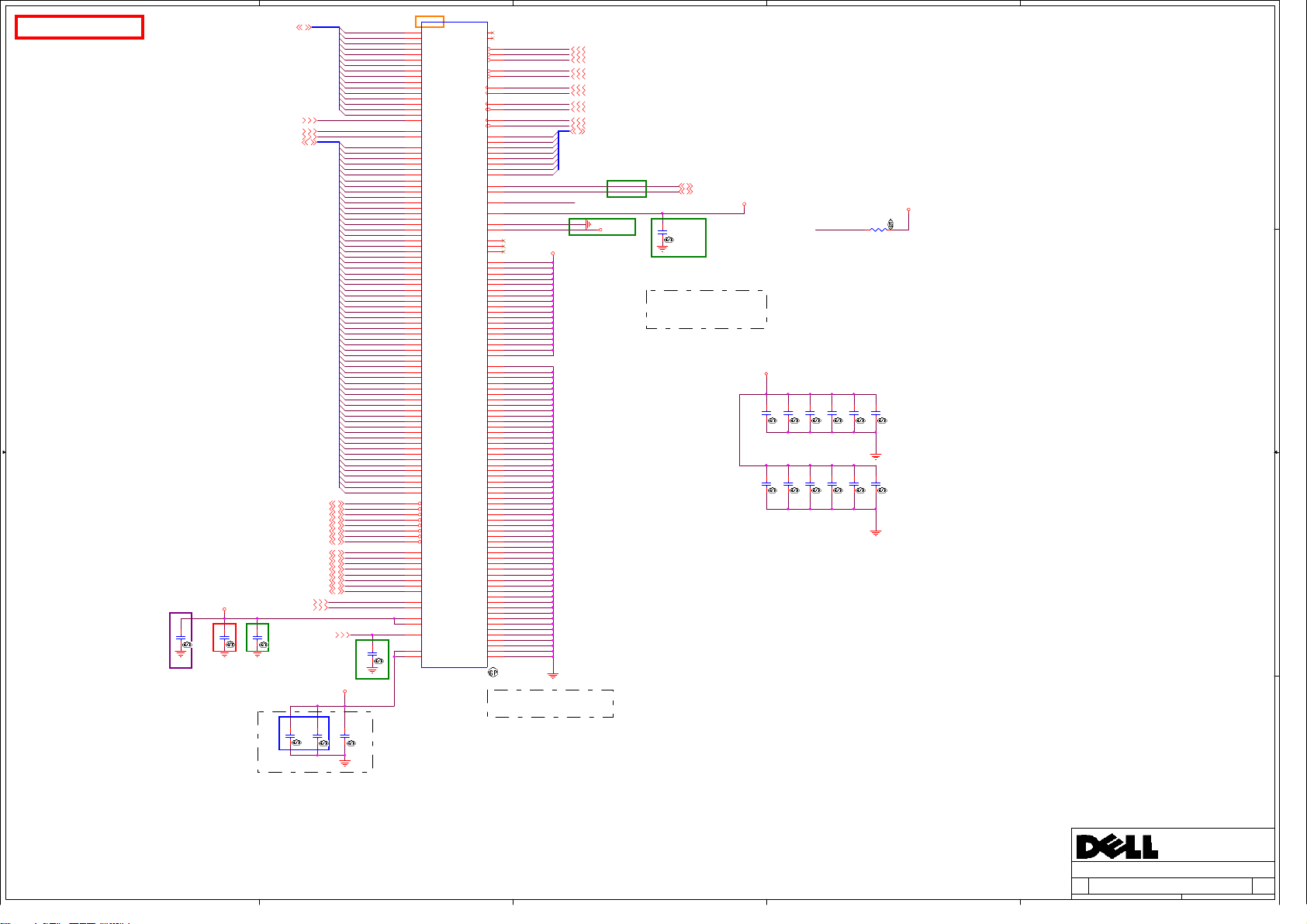

Page 2

5

2

2

28,

3

3

3

3

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

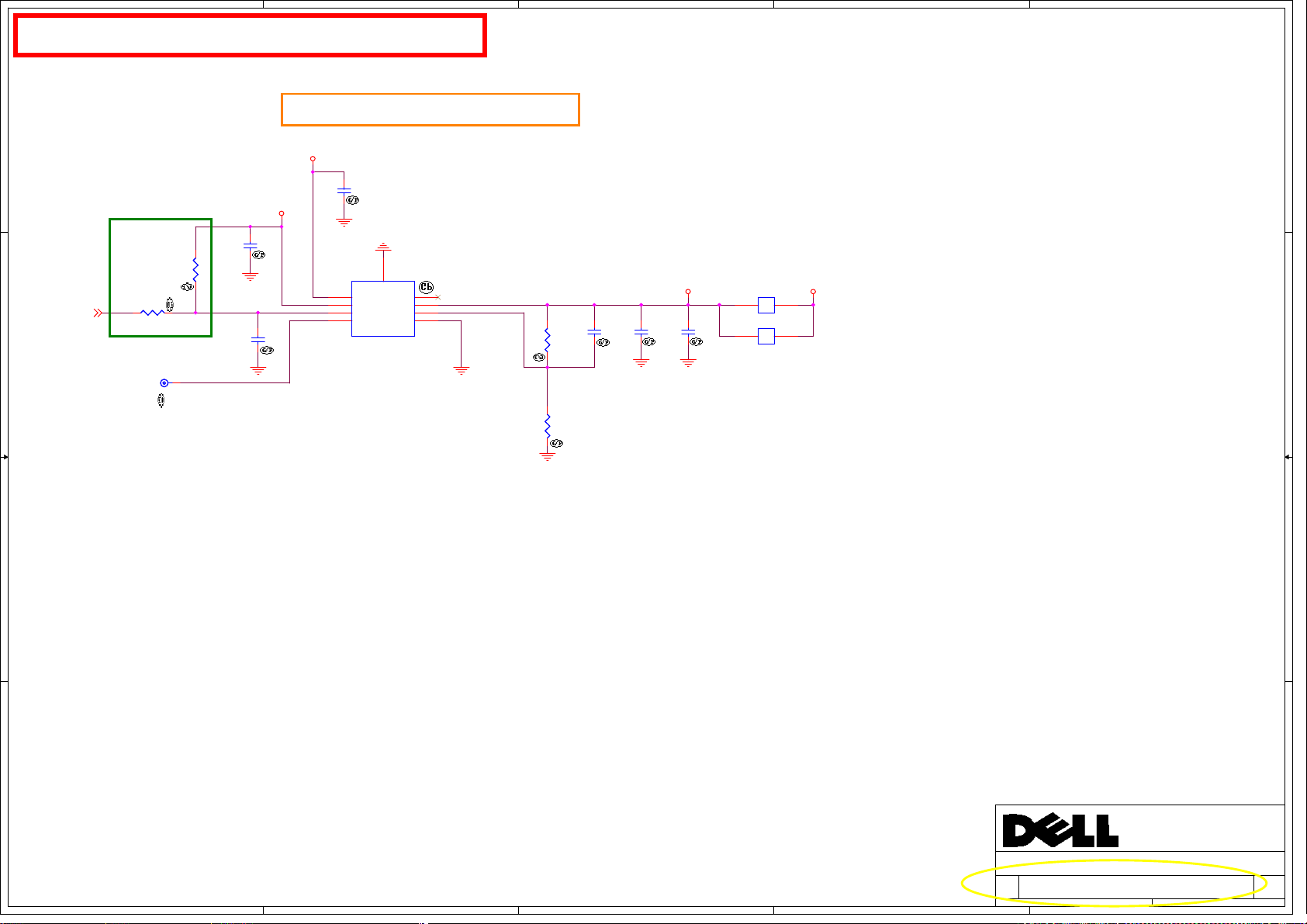

CHARGER

Project code :91.4HH01.001

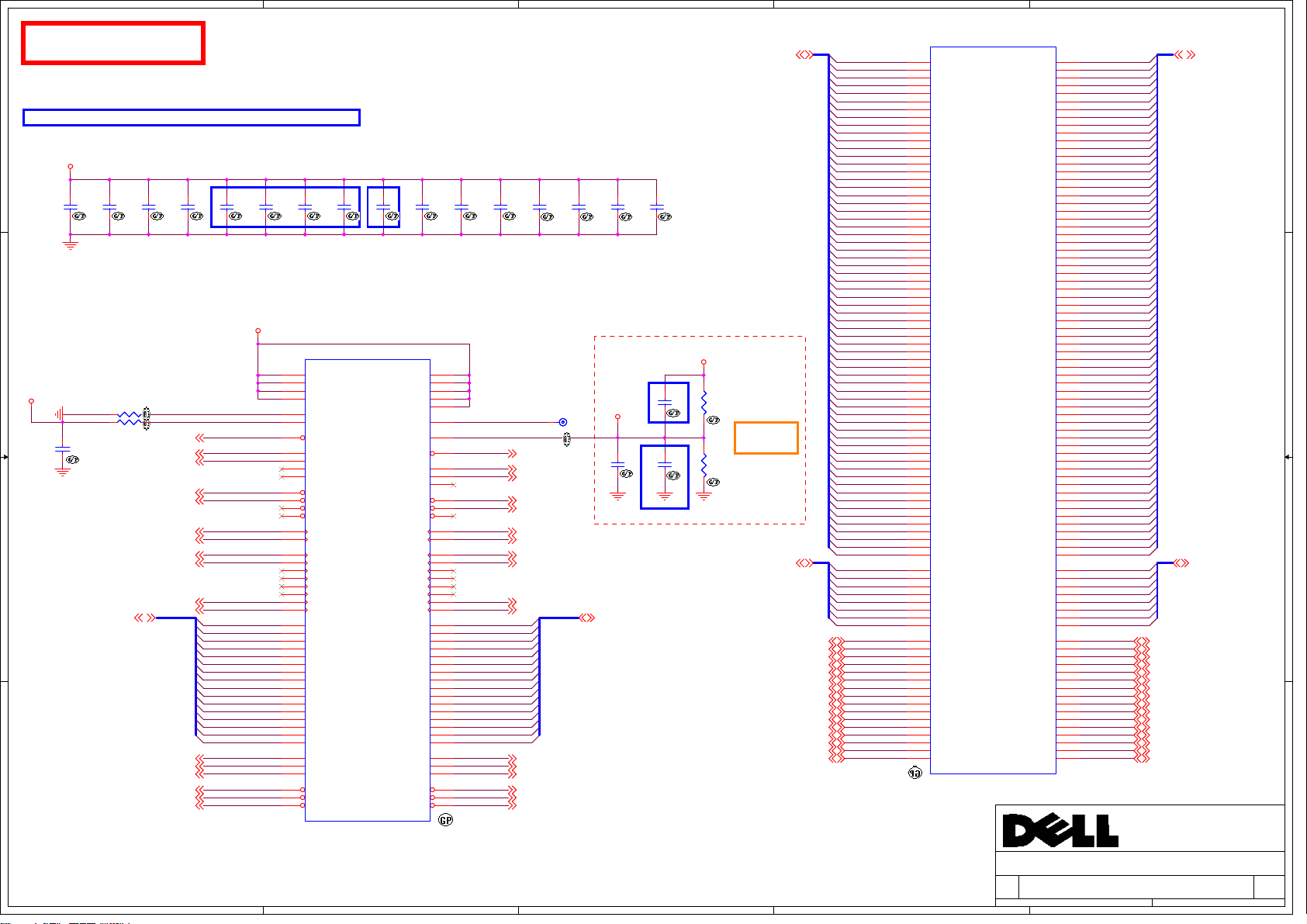

Berry DG15 Discrete/UMA Block Diagram

PCB P/N :

Revision :X-Build

AMD Champlain

D D

VRAM

64Mx16bx8 (1GB)

85,86,87,88

4

CPU S1G4

35W Max

8,9,10,11

DDR III 1333

DDR III 1333

DDRIII

800/1066/1333

DDRIII

800/1066/1333

DDR3

800MHz

OUT

AMD Graphic

M96-M2 LP

HDMI

C C

LCD Conn

(LVDS & Camera Conn.)

57

54

HDMI(Share PCIe x 4)

LVDS(Dual Channel)

80,81,82,83

PCIe x 16

North Bridge

CPU I/F

AMD RS880M

LVDS, CRT I/F

INTEGRATED GRAHPICS

HyperTransport

16X16

IN

12,13,14,15

SIDE-PORT

64Mx16bx1 (1GB)

A-LINK

4X4

CRT

RGB CRT

South Bridge

AMD SB820M

CRT Board

USB x 2

B B

CardReader

Connector

77

Realtek

RTS5159

USB2.0 x 2

Card Reader

Connector

78

USB2.0

14 USB 2.0 ports

ETHERNET (10/100/1000Mb)

High Definition Audio

2 PCIE GPP

6 SATA ports

ACPI 1.1

LPC I/F

PCI/PCI BRIDGE

20,21,22,23,24

USB 2.0

LPC Bus

SD/SDIO/MMC

MS/MS Pro/xD

Azalia

Internal Analog MIC

MIC IN

A A

HP1

CODEC

&

OP AMP

IDT 92HD79B1

AZALIA

30

SATA

HDD

59 59

SATA

ODD

SPI

Flash ROM

2MB

NUVOTON

NPCE781BA0DX

Touch

62 68 25

PAD

2CH SPEAKER

5

4

3

DIMM1

DIMM2

VRAM

PCIE x 1

USB 2.0 x 1

SATA x 1

PCIE x 2& USB 2.0 x 2

KBC

68

KB

18

19

14

37

USB 2.0 x 1

USB 2.0 x 1

ThermalInt.

EMC2102

Fan

58

2

I/O Board

Connector

76

Camera Conn

(LVDS & Camera Conn.)

Bluetooth Conn

39

RJ45

CONN

10/100 NIC

Realtek RTL8103T

USB x 1

E-SATA/USB

COMBO

MiniCard x 2

WLAN&WWAN

54

73

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

BQ24745

INPUTS

+DC_IN_SS

+VCHGR

OUTPUTS

+PWR_SRC

SYSTEM DC/DC

RT8205B

INPUTS

+PWR_SRC

OUTPUTS

+3.3V_RTC_LDO

+5V_ALW

+3.3V_ALW

CPU VDDR

RT9025

INPUTS OUTPUTS

+1.5V_SUS

+CPU_VDDR

CPU CORE

ISL6265AHRTZ-T-GP

INPUTS

+PWR_SRC

OUTPUTS

+VCC_CORE

+VDDNB

AMD RS880M CORE

RT8209

INPUTS OUTPUTS

+PWR_SRC

+NB_VDDC

AMD SB820M S5 POWER

RT9025

INPUTS

+3.3V_ALW

OUTPUTS

+1.1V_ALW

DDR III SUS&VTT

RT8207

INPUTS

+PWR_SRC

OUTPUTS

+1.5V_SUS

DDR III SUS&VTT

RT8207

INPUTS

+PWR_SRC

OUTPUTS

+0.75V_DDR_VTT

AMD GPU CORE

RT8208B

INPUTS

OUTPUTS

+VGA_CORE+PWR_SRC

PCB LAYER

L1: Top

L2: VCC

L3: Signal

L4: Signal

L5: GND

L6: Bottom

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

2 95Thursday, March 04 , 2010

2 95Thursday, March 04 , 2010

2 95Thursday, March 04 , 2010

1

46

48

47

50

48

49

49

89

A00

A00

A00

45

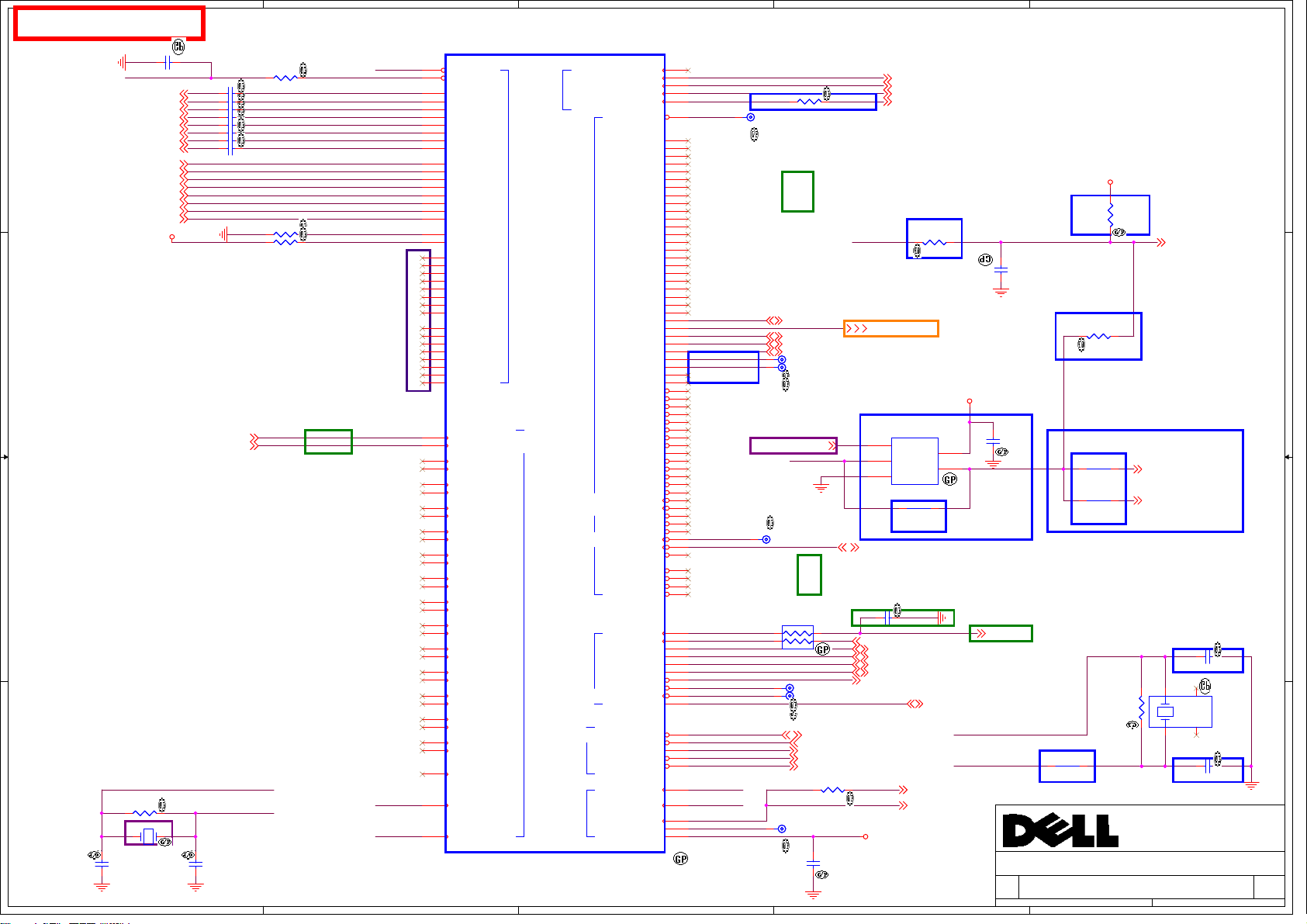

Page 3

A

WWW.AliSaler.Com

WWW.AliSaler.Com

B

C

D

E

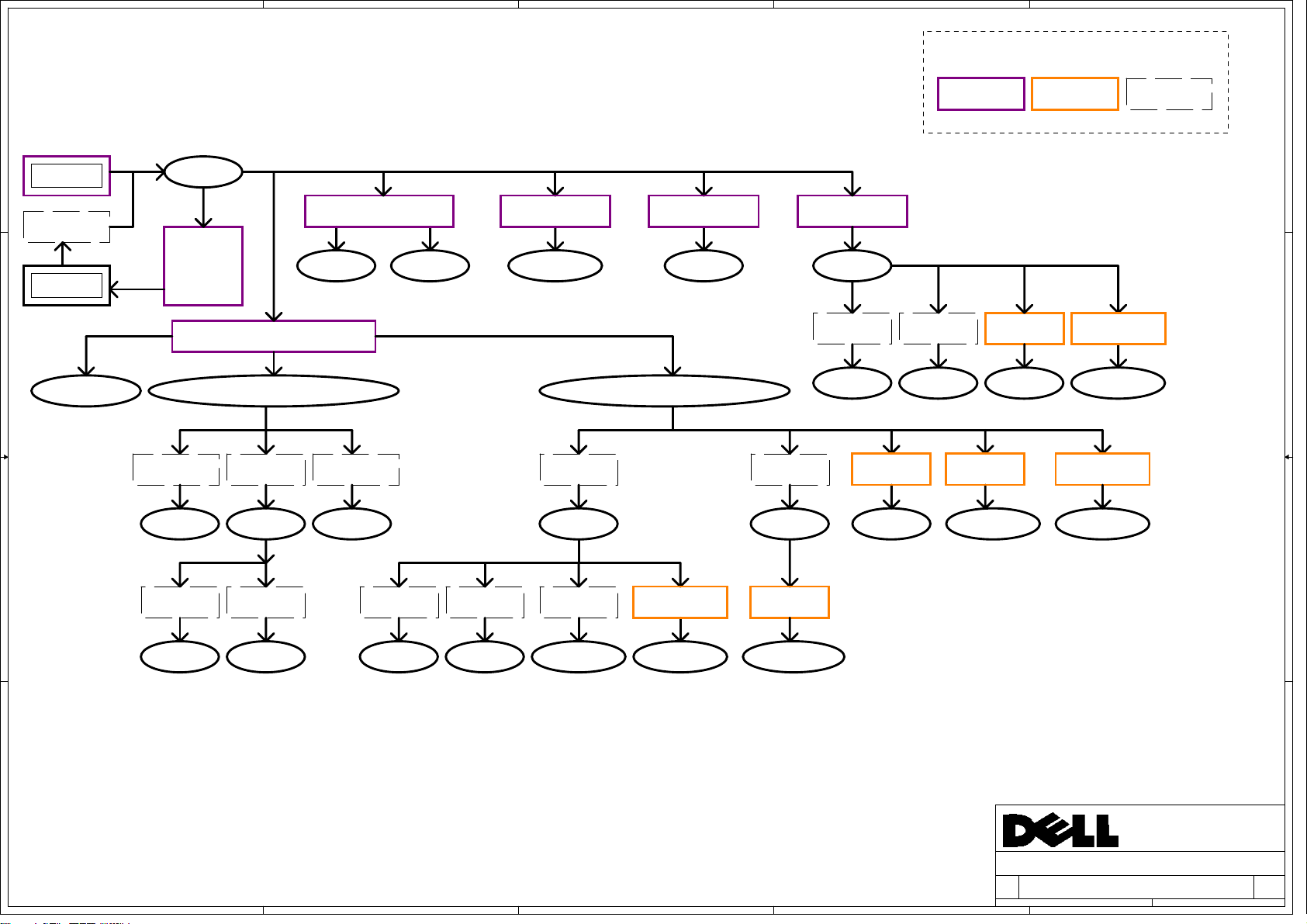

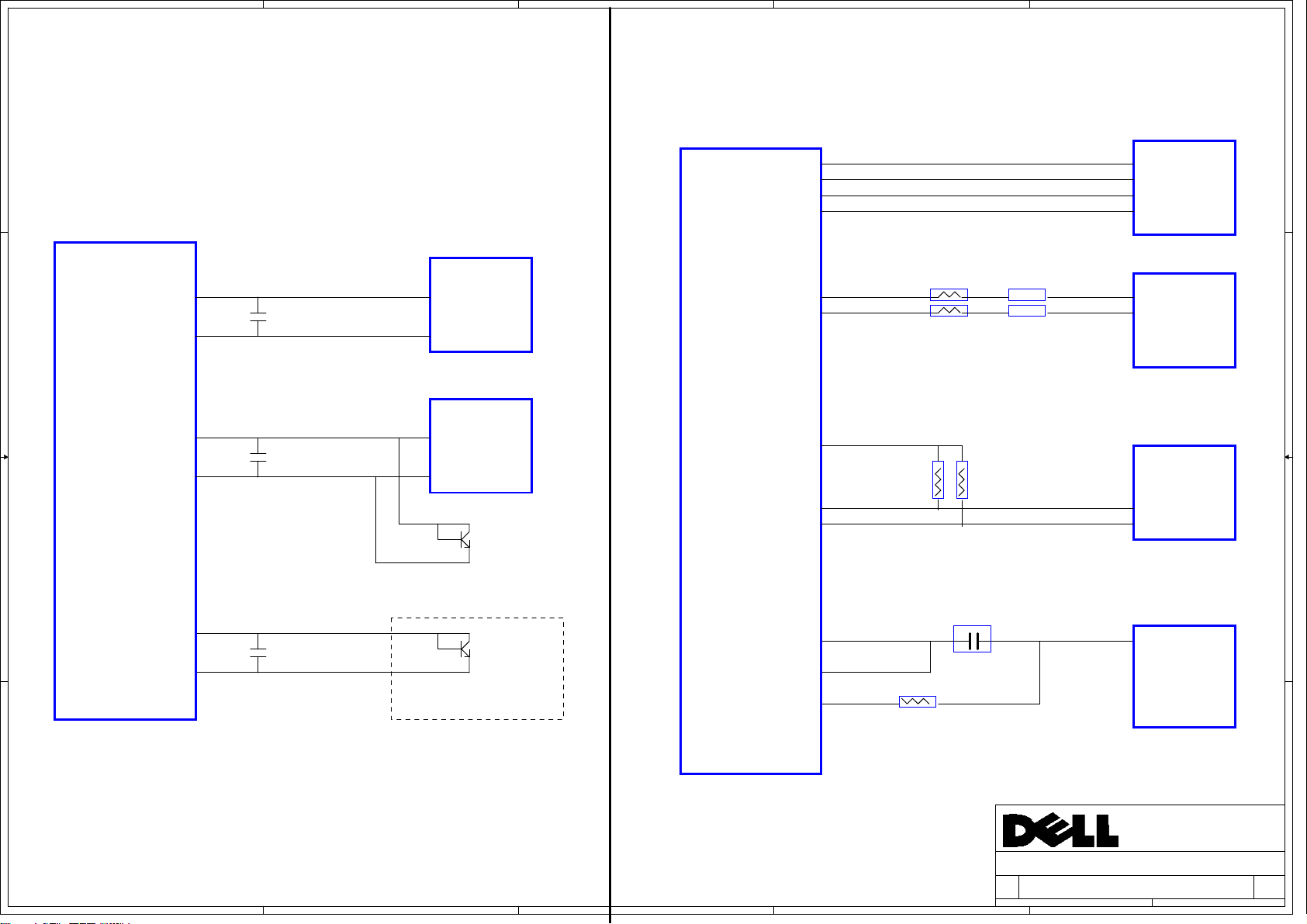

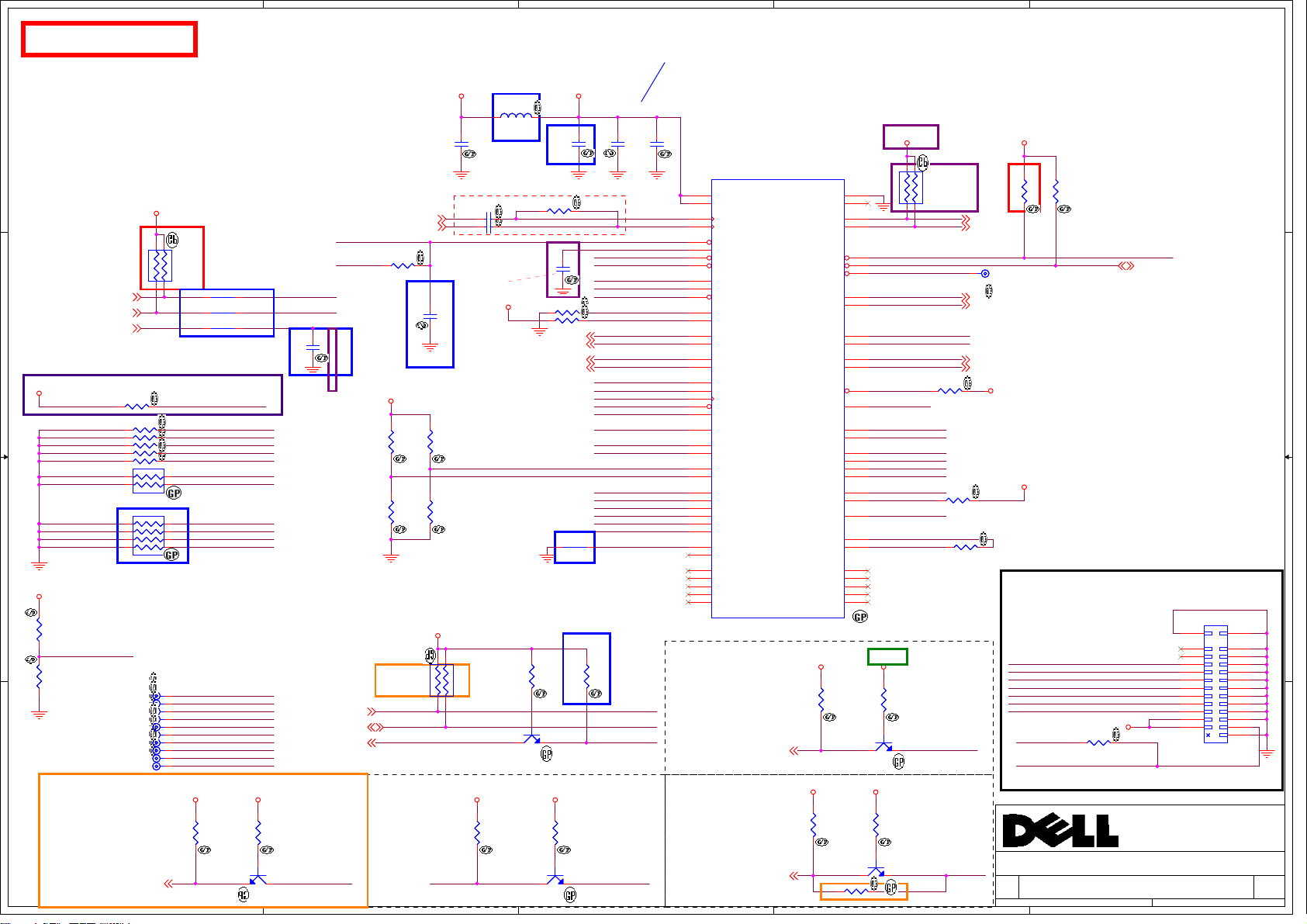

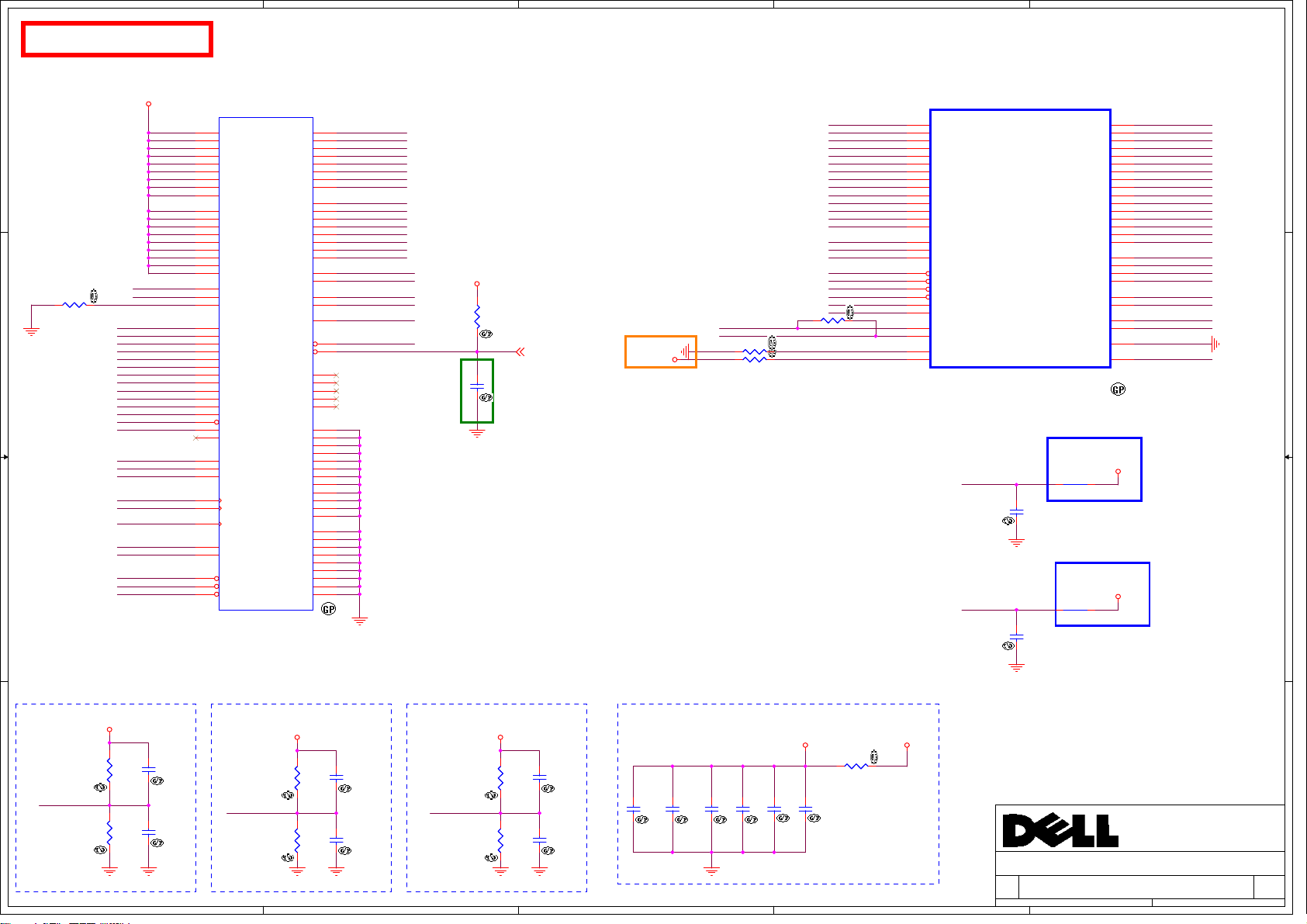

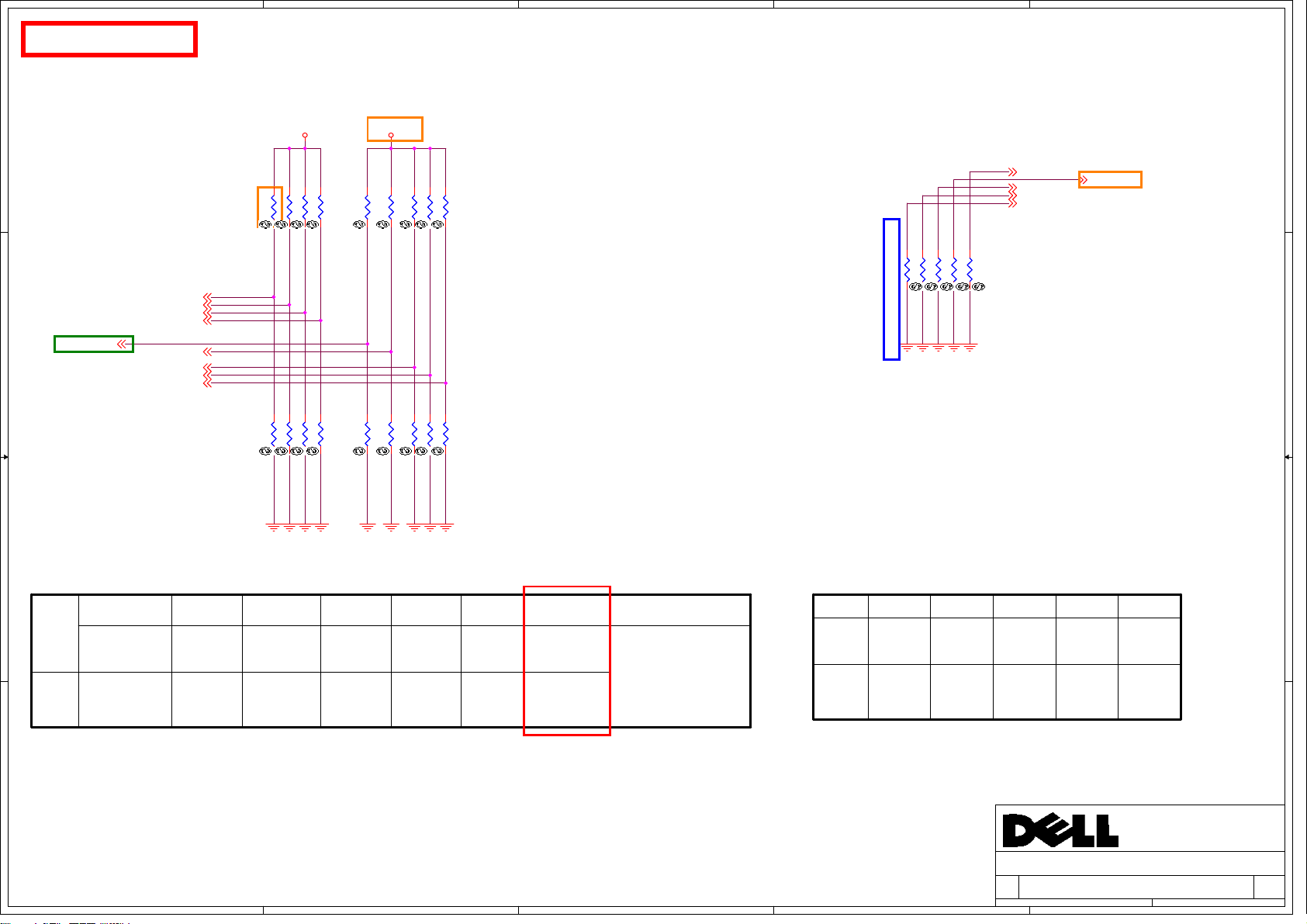

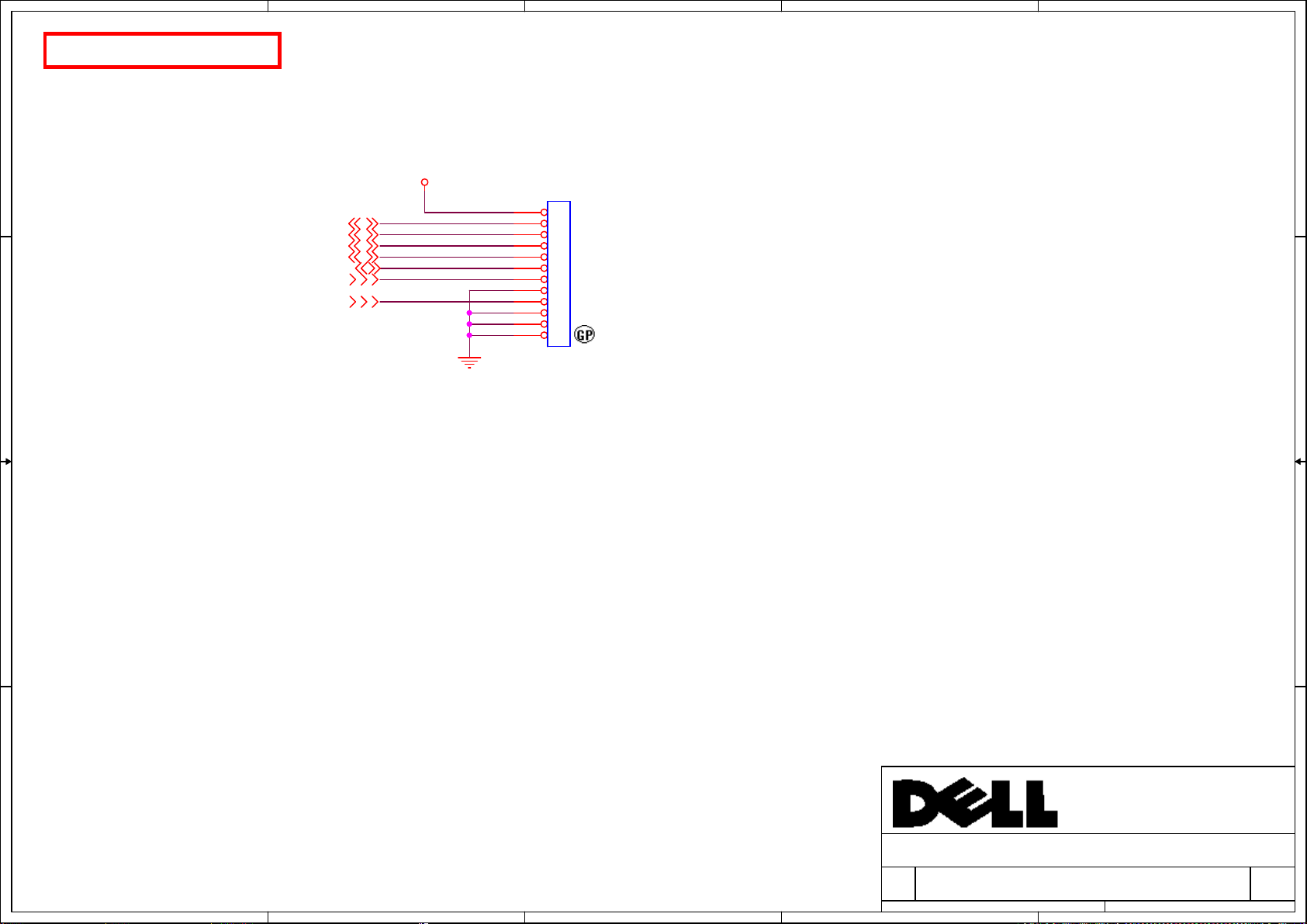

Power Shape

Regulator LDO Switch

Power Block Diagram

4 4

Adapter

+PWR_SRC

ISL6265AHRTZ RT8209EGQW RT8207

RT8208B

AO4407A

Charger

BQ24745

Battery

3 3

+3.3V_RTC_LDO

2 2

+VCHGR

UP7534

+5V_USB1

RESISTER

RT8205B

+5V_ALW

AO4468

+5V_RUN

RESISTER

+VCC_CORE

UP7534

+5V_USB2

+VDDNB(CPU)

SI2301BDS

G5285T11U

AO4468

+3.3V_RUN

RTS5159

+1.1V_RUN

+3.3V_ALW

RT9013-25PB

PA102FMG

+3.3V_LAN

RTL8103T

+1.5V_SUS+VGA_CORE

AO4468

+1.5V_RUN

+1.8V_RUN

AO4468 APL5930

+1.5V_RUN_VGA +1.0V_RUN_VGA

APL5930

APL5930

+1.8V_RUN_VGA

RT9025

VDDR(CPU)

RT9025

+1.1V_ALW

+PVDD

1 1

A

+AVDD

+3.3V_RUN_VGA

B

+LCDVDD

+3.3V_RUN_CARD

+2.5V_RUN

C

+1.2V_LOM

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Power Block Diagram

Power Block Diagram

Power Block Diagram

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Taipei Hsien 221, Taiwan, R.O.C.

3 95Thursday, March 04 , 2010

3 95Thursday, March 04 , 2010

3 95Thursday, March 04 , 2010

E

A00

A00

A00

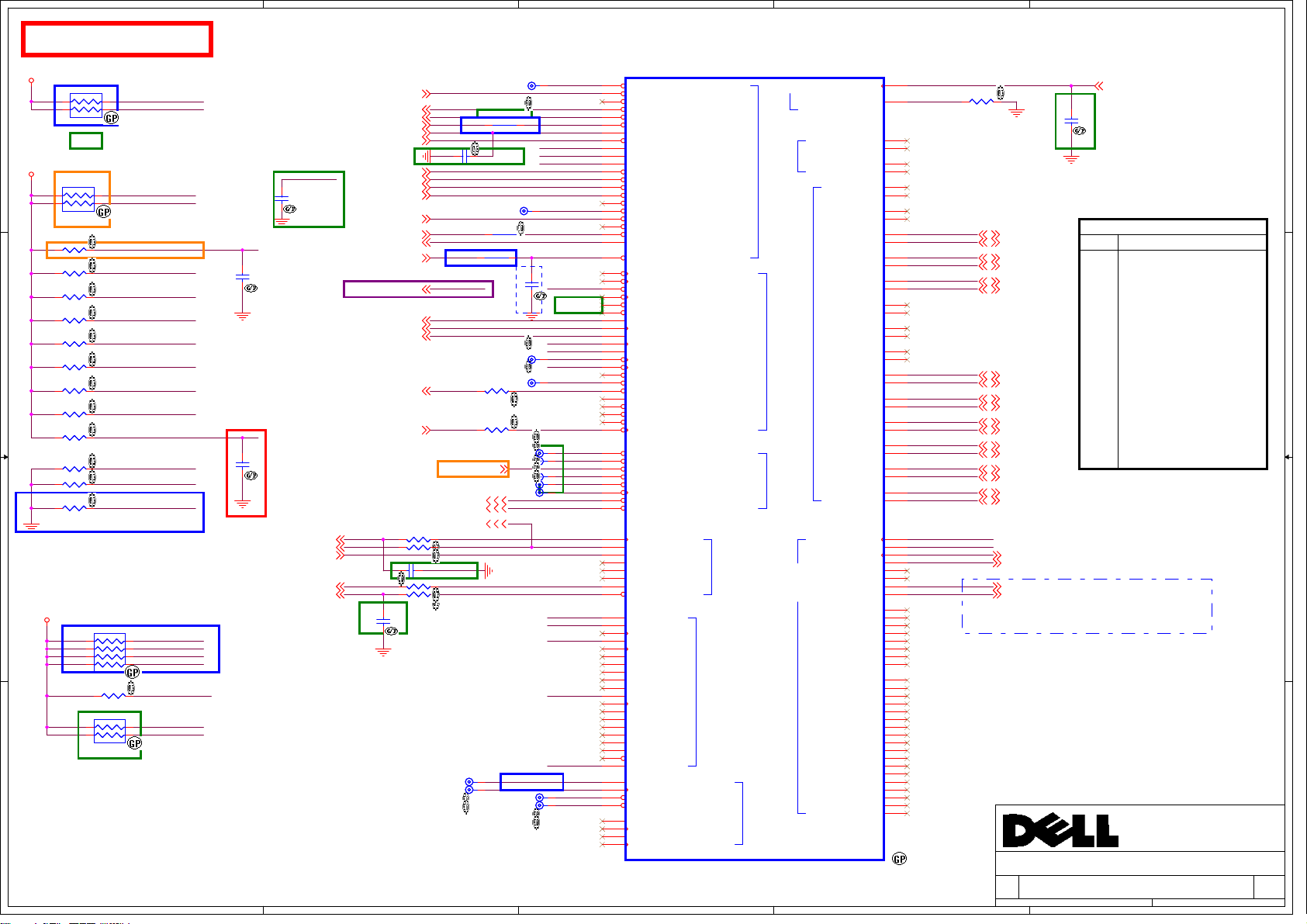

Page 4

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

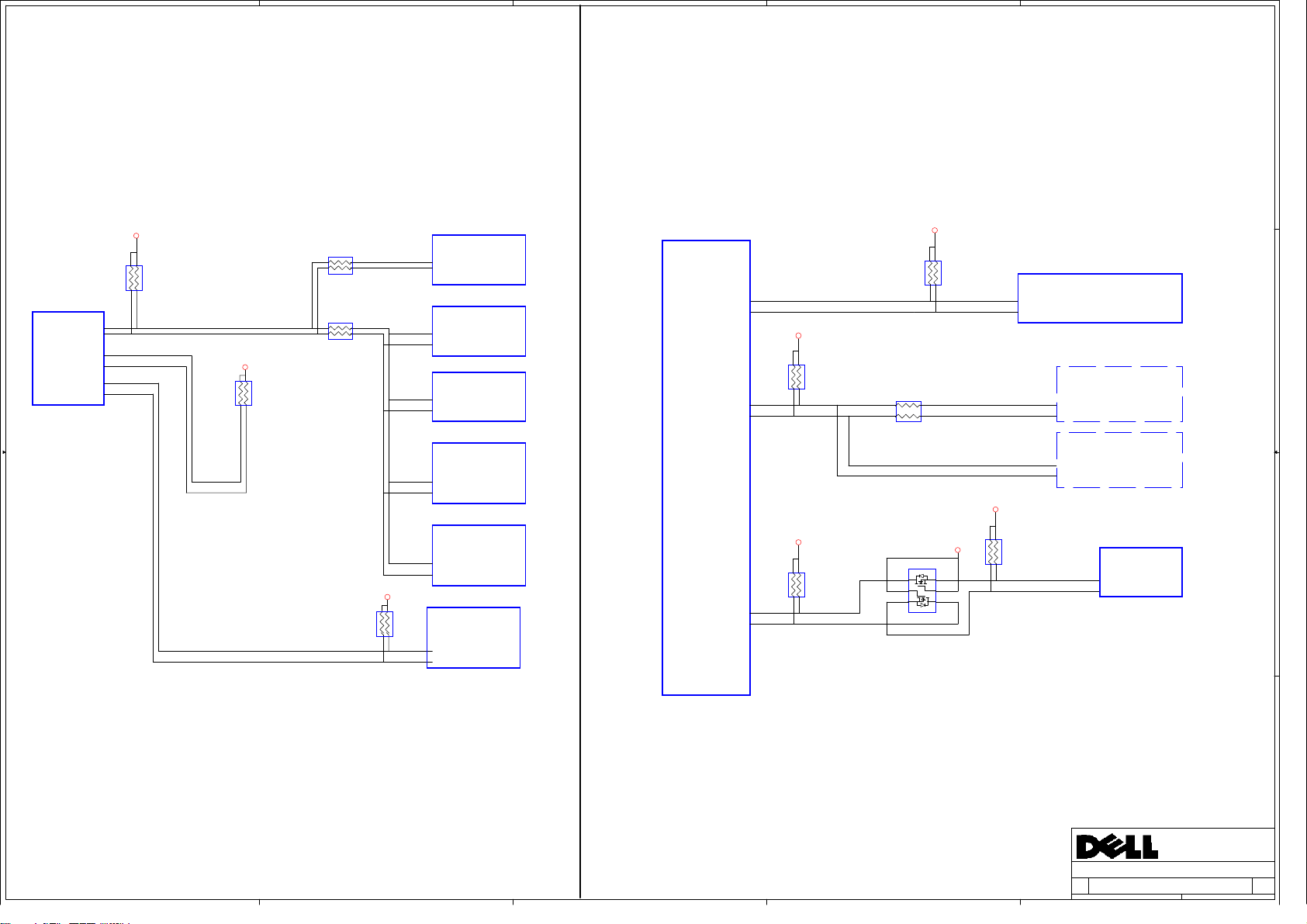

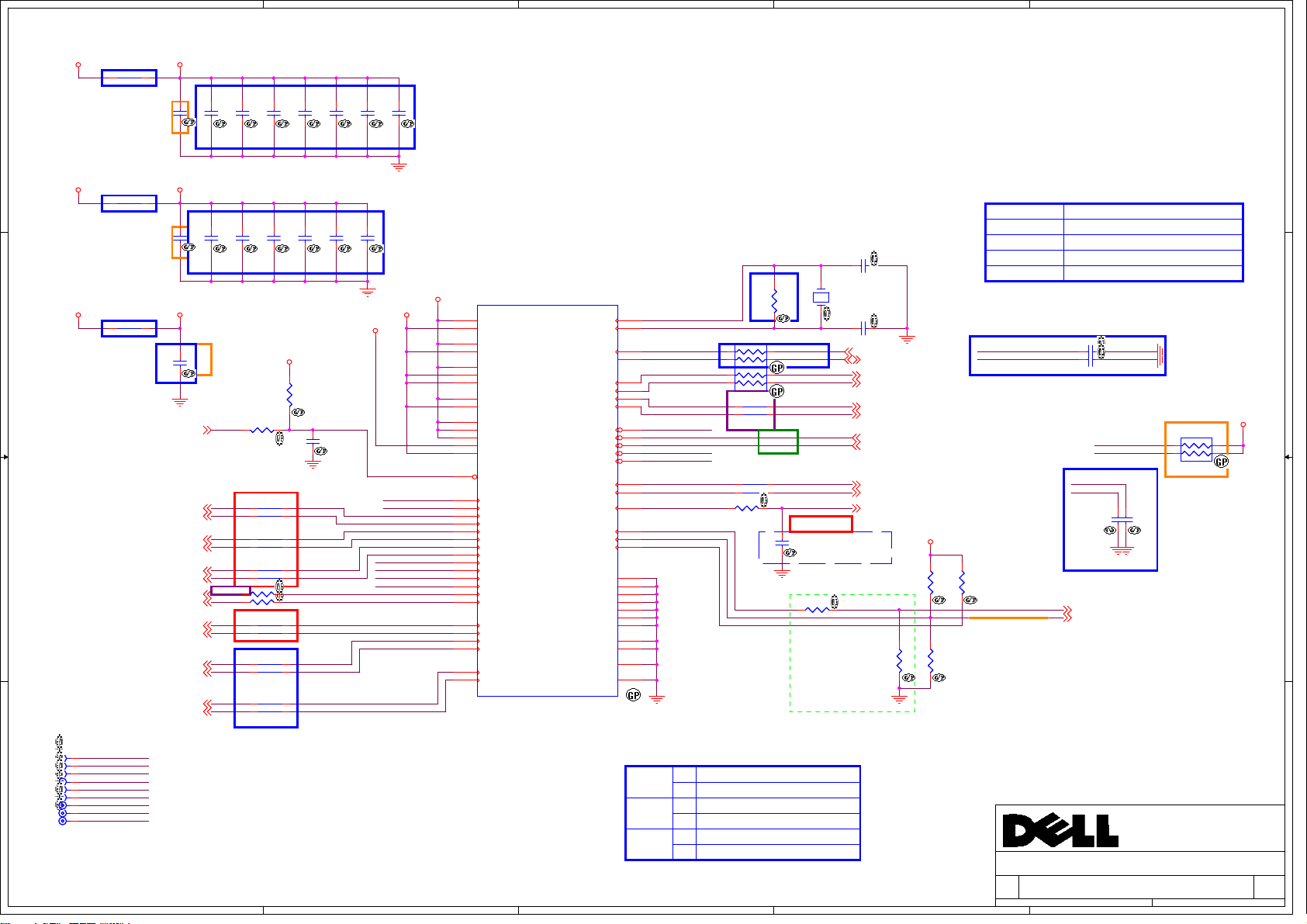

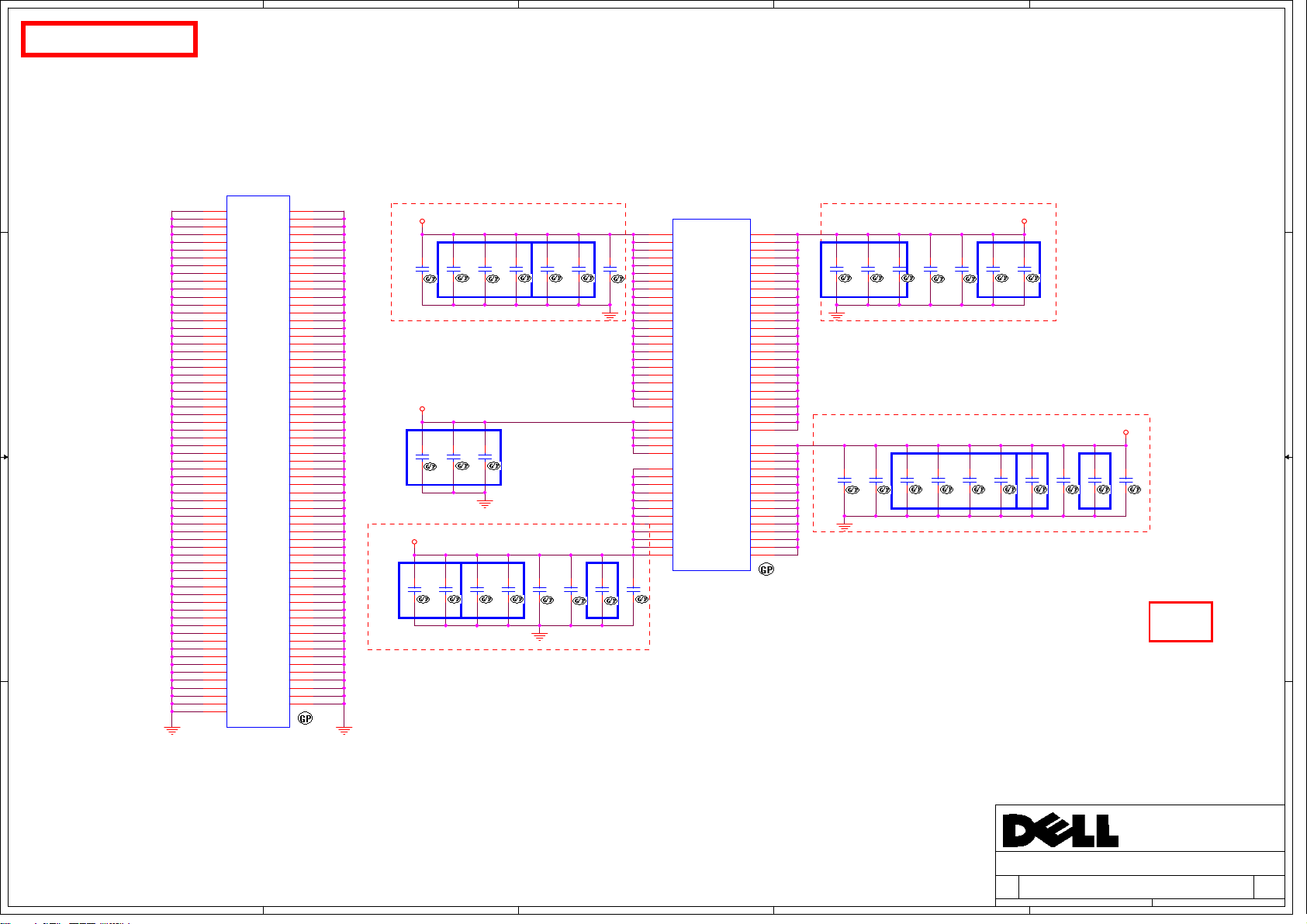

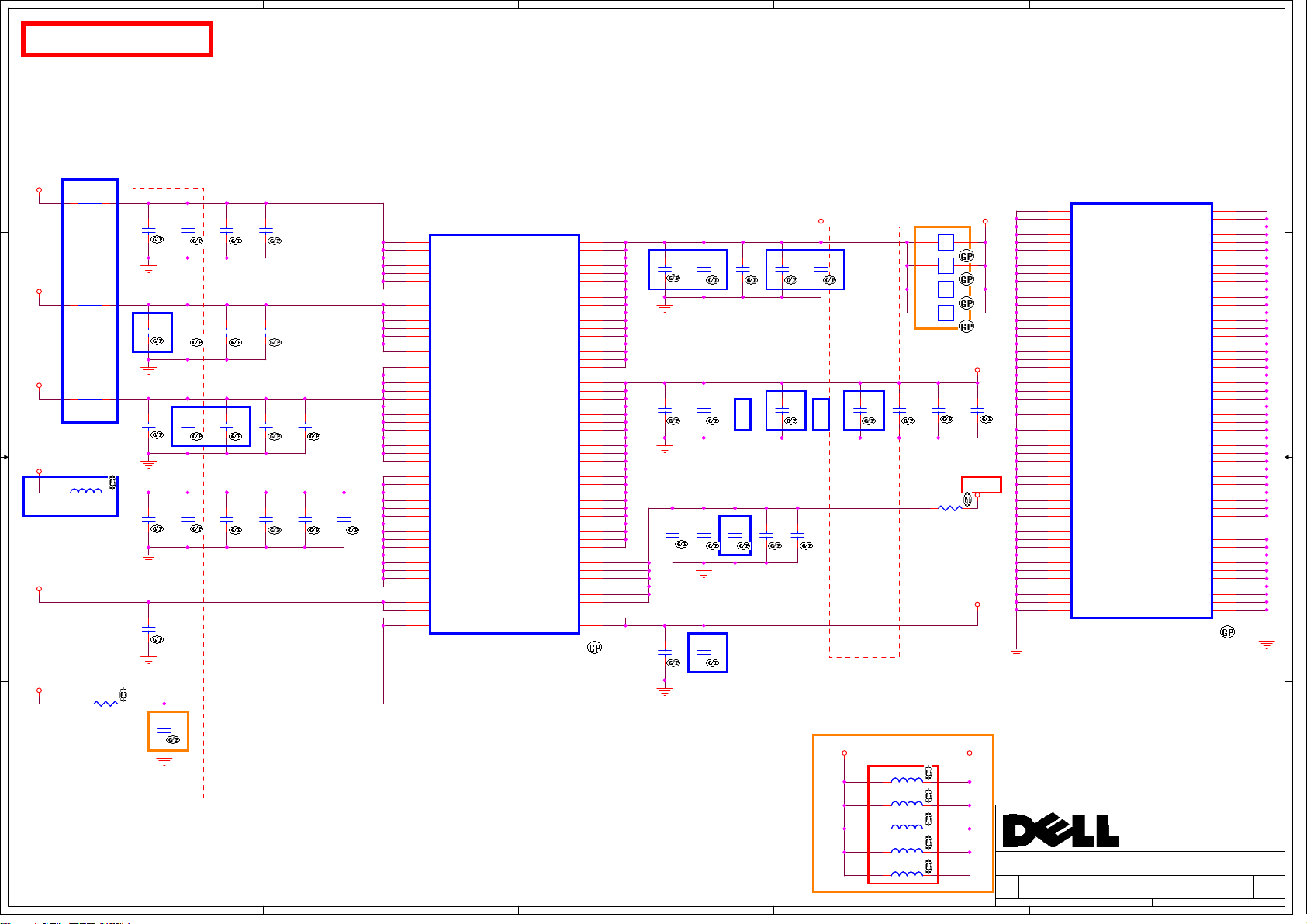

SB820M SMBus Block Diagram

D D

+3.3V_RUN

CLK GEN

SB_SMBCLK

SRN2K2J

SB820M

C C

B B

SCL0

SDA0

SCL1

SDA1

SCL3_LV/IMC_GPIO13

SDA3_LV/IMC_GPIO14

SMB_CLK

SMB_DATA

CPU_SIC

CPU_SID

SB_SMBCLK_R

SB_SMBDATA_R

+3.3V_ALW

SRN10KJ-5-GP

SRN1KJ-7-GP

SB_SMBDATA

+1.5V_SUS

SCL

SDA

SMBus Address:0xD2

SB_SMBCLK

SB_SMBDATA

DIMM 1

SCL

SDA

SMBus Address:0xA0,0x30

SB_SMBCLK

SB_SMBDATA

DIMM 2

SCL

SDA

SMBus Address:0xA4,0x34

WWAN

MINI CARD

SB_SMBCLK

SMB_CLK

SB_SMBDATA

SMB_DATA

SMBus address:

WLAN

MINI CARD

SMB_CLKSB_SMBCLK

SMB_DATA

SB_SMBDATA

SMBus address:

CPU S1G4

SIC

CPU_SIC

SID

CPU_SID

NPCE781

KBC SMBus Block Diagram

+5V_RUN

SRN10KJ-5-GP

TPDATA

KBC

GPIO61/SCL2

GPIO62/SDA2

PSDAT1

SCL1

SDA1

TPCLKPSCLK1

BAT_SCL

BAT_SDA

KBC_SCL1

KBC_S

DA1

+KBC_PWR

+3.3V_ALW

SRN4K7J-8-GP

SRN4K7J-8-GP

SRN100J-3-GP

2N7002SPT

PBAT_SMBCLK1

PBAT_SMBDAT1

+3.3V_RUN

TPDATA

TPCLK

+3.3V_RUN

TouchPad Conn.

TPDATA

TPCLK

SMBus address:

Battery Conn.

CLK_SMB

DAT_SMB

BQ24745RHDR

SCL

SDA

SMBus address:0x12

SRN4K7J-8-GP

THERM_SCL

THERM_SDA

SMBus address:0x7A

Thermal

SCL

SDA

SMBus address:

A A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

1

4 95Thursday, March 0 4, 2010

4 95Thursday, March 0 4, 2010

4 95Thursday, March 0 4, 2010

A00

A00

A00

5

Title

Title

Title

SMBUS BLOCK DIAGRAM

SMBUS BLOCK DIAGRAM

SMBUS BLOCK DIAGRAM

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

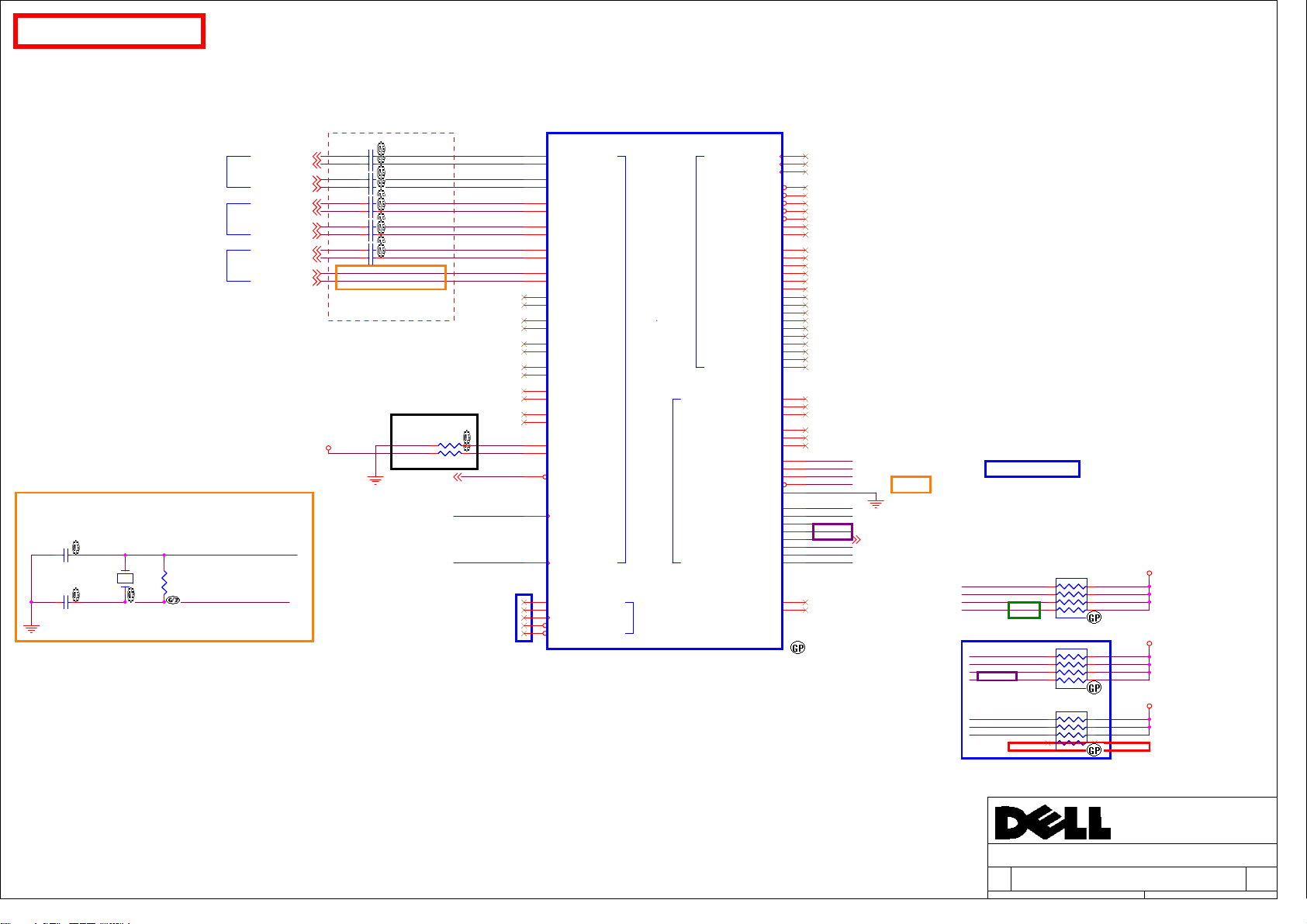

Page 5

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

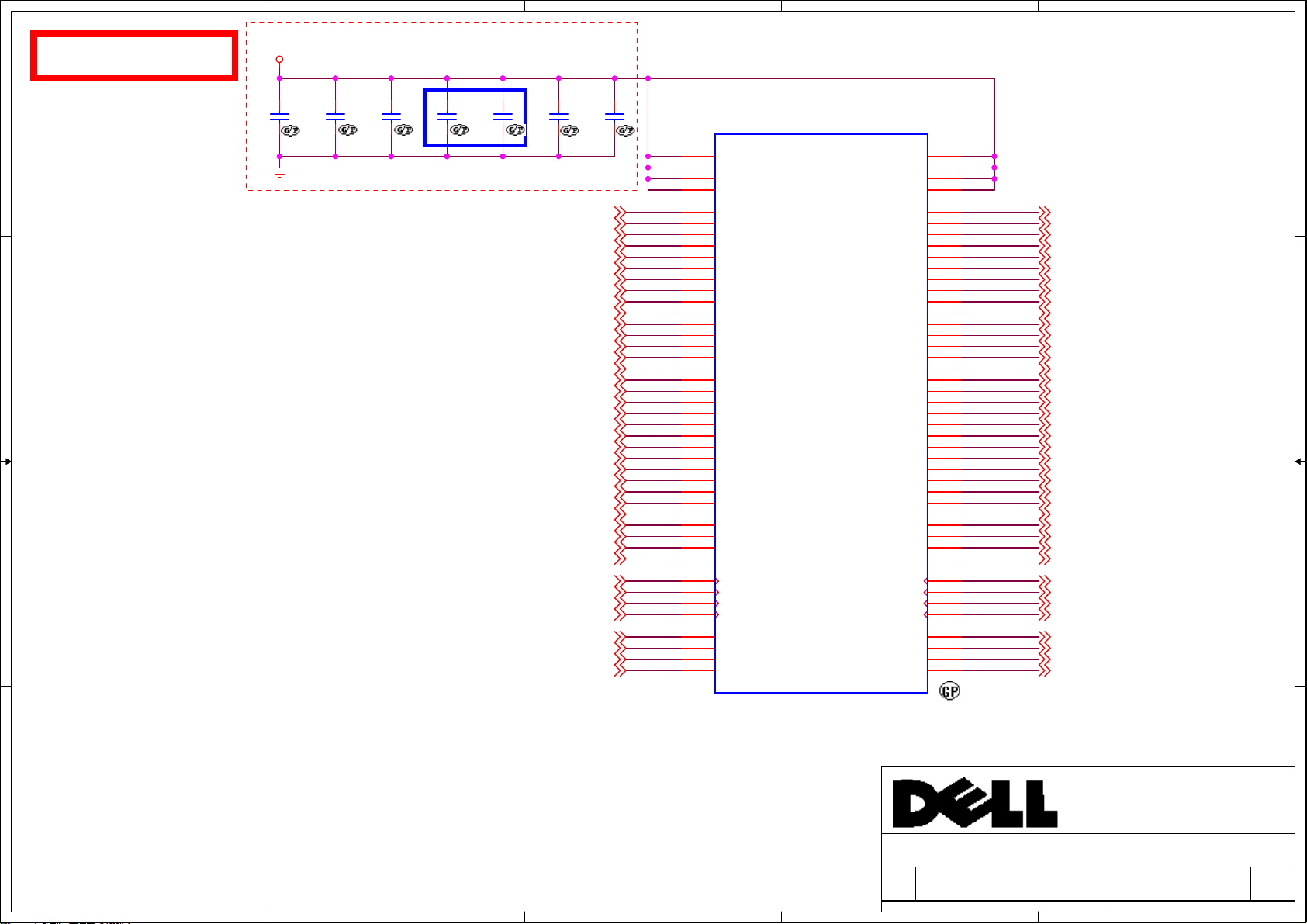

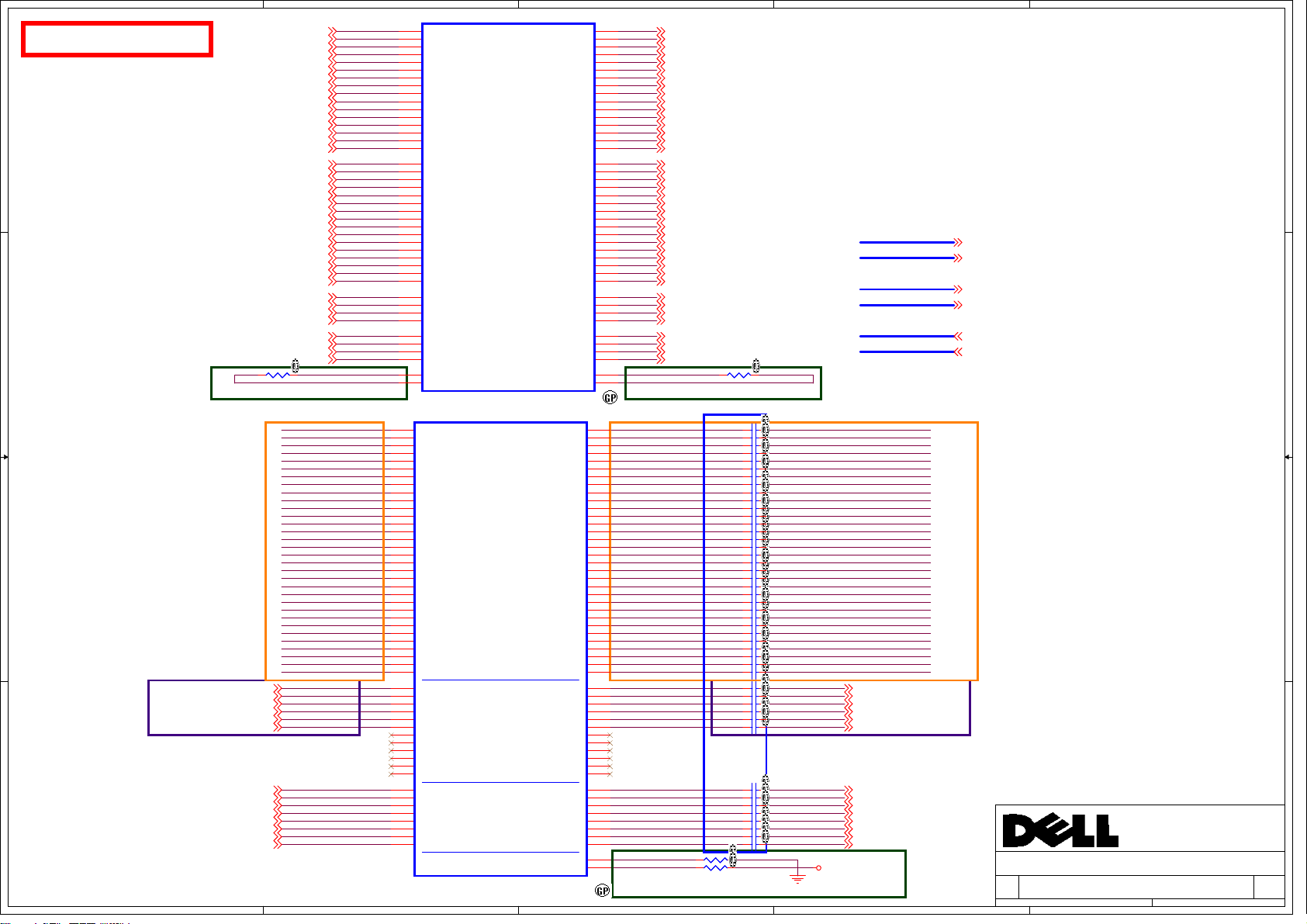

Thermal Block Diagram

D D

CPU

H_THERMDA

DP1

SC470P50V3JN-2GP

H_THERMDC

C C

DN1

Thermal

EMC2102

DP2

VGA_THERMDA

SC470P50V3JN-2GP

DN2

VGA_THERMDC

THERMDA

THERMDC

DPLUS

DMINUS

GPU

PMBS3904

Audio Block Diagram

SPKR_PORT_D_L+

SPKR_PORT_D_L-

SPKR_PORT_D_R-

SPKR_PORT_D_R+

HP1_PORT_B_L

HP1_PORT_B_R

Codec

92HD79B1

VREFOUT_A_OR_F

HP0_PORT_A_L

HP0_PORT_A_R

AUD_SPK_L+

AUD_SPK_L-

AUD_SPK_R-

AUD_SPK_R+

AUD_HP1_JACK_L

P1_JACK_R

AUD_H

AUD_VREFOUT_B

AUD_EXT_MIC_L

AUD_EXT_MIC_R

60D4R2F

60D4R2F

4K7R2J-2-GP

AUD_HP1_JACK_L1

Bead

AUD_HP1_JACK_R1

Bead

4K7R2J-2-GP

SPEAKER

60

HP

OUT

60

MIC

IN

60

B B

SC1U10V3KX-3GP

EMC2102_DP3

DP3

PMBS3904

DN3

SC470P50V3JN-2GP

EMC2102_DN3

System sensor, put

between CPU and NB.

A A

5

4

3

PORT_C_L

PORT_C_R

VREFOUT_C

AUD_INT_MIC_R_L

AUD_INT_MIC_R_L

AUD_VREFOUT_C

30

4K7R2J-2-GP

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

INT_MIC_L_R

Internal

MIC

60

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

THERMAL/AUDIO BLOCK DIAGRAM

THERMAL/AUDIO BLOCK DIAGRAM

THERMAL/AUDIO BLOCK DIAGRAM

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

5 95Thursday, March 04 , 2010

5 95Thursday, March 04 , 2010

5 95Thursday, March 04 , 2010

1

A00

A00

A00

Page 6

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

SB820M Strapping

Capture from 45484 Rev. 1.02 AMD SB8xx-Series Southbridge Design Guide

Name Strap Name Schematic Note

LPCCLK0

D D

EC_PWM3

EC_PWM2

LPCCLK1

PCICLK1

C C

ECEnableStrap

{ROMTYPE_1,

T

YPE_0 }

ROM

CLKGEN

BIF_GEN2_

COMPLIANCE_Strap

PCICLK2 BootFailTmrEn

PCICLK3 DefaultStrapMode

PCICLK4 CPUClkSel

AZ_SDOUT CoreSpeedMode

B B

Embedded Controller (EC)

0 V – Disabled

*

3.3 V - Enabled

ROMTYPE_1 ROMTYPE_0 ROM TYPE

3.3V 0V

3.3V

3.3V

0V 0V

0V 3.3V

*

SPI ROM

Reserved

Firmware Hub

LPC ROM

(supports both LPC and PMC ROM types)

Defines clock generator

*

External clock mode: Use 100-M Hz PCIeR

0V –

3.3V–

k as reference clock and gener ate i

cloc

nternal clocks only.

Integrated clock mode: Use 25- MHz crystal

clock and generate both intern al and external clocks

Set PCIe to Gen II mode

Force PCIe interface at Gen I mode

0V–

PCIe interfacce is at Gen II m ode

*

3.3V-

Not Applicable to SB820M but p rovision for

pull-down is required.

Watchdog function

*

*

Disable the boot fail timer fu nction

0V–

Enable the boot fail timer fu nction

3.3V-

Default Debug Straps

Disable Debug Straps.

0V–

Select external Debug Straps

3.3V–

CPU/NB HT Clock Selection

Reserved.

0V–

*

Required setting for integrate d clock mode.

3.3V–

This strap is not used if the strap CLKGEN is

configured for external clock generator mode.

Slow down core clock for low power platform.

0V–

3.3V-

Performance mode

Low Power mode

*

RS880M Strapping

Capture from 46113_rs880m_ds_nda_1.03

DAC_VSYNC

DAC_HSYNC

SUS_STAT#

STRAP_DEBUG_BUS_GPIO

_ENABLE#

SIDE_PORT_EN#

LOAD_EEPROM_STRAPS#

USB Table PCIE

Pair

USB

Device

USB0 (I/O Board/ESATA)

0

USB1 (I/O Board)

1

USB2 (CRT Board)

2

USB3 (CRT Board)

3

WLAN USB

4

WWAN USB

5

RESERVED

6

RESERVED

7

RESERVED

8

BLUETOOTH

9

CARD READER

10

CAMERA (LVDS CONN)

11

RESERVED

12

RESERVED

13

Schematic NoteStrap FunctionName

Enables debug bus access

through memory I/O pads and GPIOs.

0: Enable

1: Disable

*

Indicates if memory side-port is available or not

0: Available(UMA)

1: Not available(Discrete)

Selects loading of strap values from EEPROM.

0: I2C master can load strap values from EEPROM if

connected, or use default values if EEPROM is not

connected. Please refer to RS880M's reference

schematics for system level implementation details.

1: Use default values

*

Routing

RS880M

MiniCard WLANLANE0

LANE1

LANE2

LAN

MiniCard WWAN

A A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

1

6 95Thursday, March 0 4, 2010

6 95Thursday, March 0 4, 2010

6 95Thursday, March 0 4, 2010

A00

A00

A00

5

Title

Title

Title

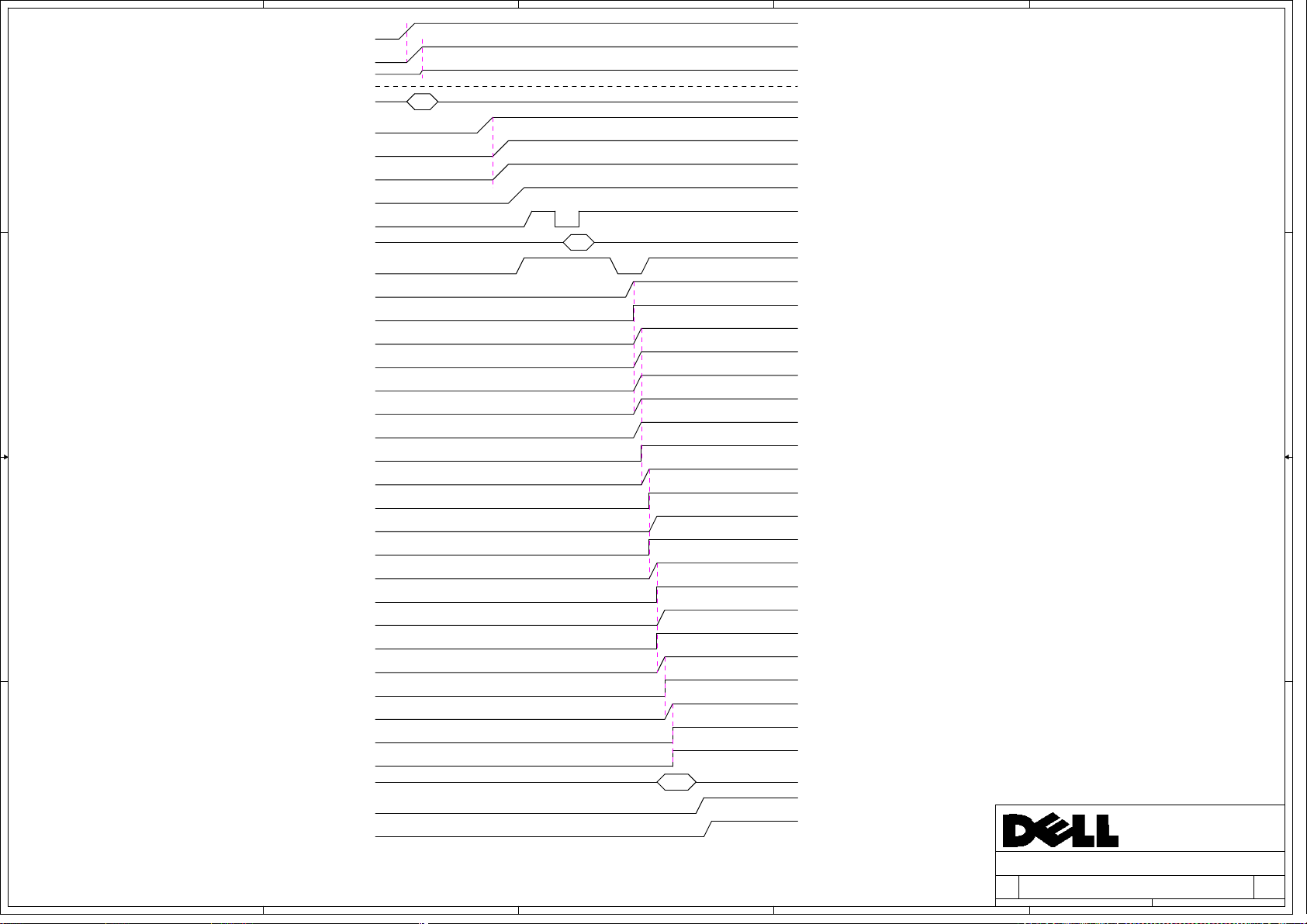

Table of Content

Table of Content

Table of Content

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Page 7

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

+3.3V_CL K_VDD+3.3V_RU N

R702

R702

1 2

0R0603-P AD

0R0603-P AD

1231-1

D D

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C701

C701

9/22

+3.3V_RU N +3.3V_ CLK_VDDIO

R703

R703

1 2

0R0603-P AD

0R0603-P AD

1231-1

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C710

C710

DY

DY

9/22

+3.3V_RU N +3.3V_ CLK_VDDREF

R701

R701

1 2

0R0603-P AD

0R0603-P AD

C C

1231-1

1119-3

SB_PW RGD(21 ,41)

WLAN

(100MHz)

WWAN(100MHz)

LAN(100MHz)

B B

VGA(27MHz)

NB(100MHz)

SB(100MHz)

TP701TP701

TP702TP702

TP703TP703

TP704TP704

TP705TP705

TP706TP706

A A

TP707TP707

TP709TP709

TP708TP708

TP_CLK_ SRC6

1

TP_CLK_ SRC6#

1

TP_CLKR EQ0#

1

TP_CLKR EQ3#

1

TP_CLKR EQ4#

1

TP_CLK_ SRC4

1

TP_CLK_ SRC4#

1

R_NB_GP P_CLK

1

R_NB_GP P_CLK#

1

CLK_PCIE_ WLAN(76)

CLK_PCIE_ WLAN#(76)

CLK_PCIE_ WWAN(76)

CLK_PCIE_ WWAN#(76)

CLK_PCIE_ LAN(76)

CLK_PCIE_ LAN#(76)

CLK_VGA _27M_SS(82)

CLK_VGA _27M_NSS(82)

NB_GPPS B_CLK(13)

NB_GPPS B_CLK#(13)

SB_PCIE_C LK(20)

SB_PCIE_C LK#(20)

CLK_NBH T_CLK(13)

CLK_NBH T_CLK#(13)

5

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

9/22

C721

C721

1113-2

+3.3V_CLK_VDD (40 mils)

12

12

C703

C703

C704

C704

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

12

C712

C712

C713

C713

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

R706

R706

1 2

DY

DY

0R2J-2-GP

0R2J-2-GP

RN702

RN702

2 3

1

0R4P2R-P AD

0R4P2R-P AD

RN710

RN710

2 3

1

0R4P2R-P AD

0R4P2R-P AD

RN703

RN703

2 3

1

0R4P2R-P AD

0R4P2R-P AD

R713 47R2J-2-G P

R713 47R2J-2-G P

1 2

R714 33R2J-2-G P

R714 33R2J-2-G P

1 2

RN704

RN704

2 3

1

0R4P2R-P AD

0R4P2R-P AD

RN705

RN705

2 3

1

0R4P2R-P AD

0R4P2R-P AD

RN706

RN706

2 3

1

0R4P2R-P AD

0R4P2R-P AD

10/1

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

+3.3V_RU N

10KR2J-3-GP

10KR2J-3-GP

RN

RN

RN

RN

RN

RN

DIS

DIS

DIS

DIS

RN

RN

RN

RN

RN

RN

12

C705

C705

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

C714

C714

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

R705

R705

EC702

EC702

SC10P50 V2JN-4GP

SC10P50 V2JN-4GP

DY

DY

4

4

10/5

4

10/5

4

4

4

12

C706

C706

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

C715

C715

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

+3.3V_CL K_VDDREF

12

12

C708

C708

C707

C707

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1119-3

12

C717

C717

C716

C716

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

+3.3V_CL K_VDDIO

CLKGEN_ PD#

R_VGA_2 7M_SS_CLK

R_VGA_2 7M_NSS_CLK

NB_GPPS B_CLK_R

NB_GPPS B_CLK#_R

SB_PCIE_C LK_R

SB_PCIE_C LK#_R

CLK_NBH T_CLK_R

CLK_NBH T_CLK#_R

1119-3

12

C709

C709

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

+3.3V_CL K_VDD

R_NB_GP P_CLK

R_NB_GP P_CLK#

CLK_MINI1_R

CLK_MINI1#_R

CLK_SRC 2

CLK_SRC 2#

LAN_CLK _R

LAN_CLK #_R

TP_CLK_ SRC4

TP_CLK_ SRC4#

TP_CLK_ SRC6

TP_CLK_ SRC6#

4

U701

U701

26

VDDATIG

25

VDDATIG_IO

48

VDDCPU

47

VDDCPU_IO

16

VDDSRC

17

VDDSRC_IO

11

VDDSRC_IO

35

VDDSB_SRC

34

VDDSB_SRC_IO

40

VDDSATA

4

VDD

55

VDDHTT

56

VDDREF

63

VDD48

51

PD#

22

SRC0T_LPRS

21

SRC0C_LPRS

20

SRC1T_LPRS

19

SRC1C_LPRS

15

SRC2T_LPRS

14

SRC2C_LPRS

13

SRC3T_LPRS

12

SRC3C_LPRS

9

SRC4T_LPRS

8

SRC4C_LPRS

SRC6T/SATAT_LPRS42GNDSATA

41

SRC6C/SATAC_LPRS

6

SRC7T_LPRS/27MHZ_SS

5

SRC7C_LPRS/27MHZ_NS

37

SB_SRC0T_LPRS

36

SB_SRC0C_LPRS

32

SB_SRC1T_LPRS

31

SB_SRC1C_LPRS

54

HTT0T_LPRS/66M

53

HTT0C_LPRS/66M

ICS9LPRS4 80BKLFT-GP

ICS9LPRS4 80BKLFT-GP

71.09480.A03

71.09480.A03

1st 71.09480.A03

2nd 71.08628.003

ATIG0T_LPRS

ATIG0C_LPRS

ATIG1T_LPRS

ATIG1C_LPRS

CPUKG0T_LPRS

CPUKG0C_LPRS

REF0/SEL_HTT66

REF1/SEL_SATA

NB ALINK

(100MHz)

SB PCIE

(100MHz)

VGA Madison

(27MHz)

SMBCLK

SMBDAT

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

48MHZ_0

REF2/SEL_27

GNDATIG

GND

GNDHTT

GNDREF

GNDCPU

GND48

GNDSRC

GNDSRC

GNDSB_SRC

GND

X1

X2

61

62

2

3

30

29

28

27

23

45

44

39

38

50

49

64

59

58

57

43

24

7

52

60

46

1

10

18

33

65

SEL_HTT66

FS0

SEL_SATA

FS1

SEL_27MHz

S2

F

* default

3

CLKGEN_ X1

CLKGEN_ X2

SB_SMBC LK_CK

SB_SMBD ATA_CK

GFX_CLK P

GFX_CLK N

NB_GFX_ CLK_R

NB_GFX_ CLK_R#

10/2

TP_CLKR EQ0#

WLAN _CLK_REQ#

WW AN_CLK_REQ #

TP_CLKR EQ3#

TP_CLKR EQ4#

CPU_HT_ CLK

CPU_HT_ CLK#

48M_CLK

FS0

SB_14M_ CLK

FS2

1

*0

1*

0

1

*

0

X-14D31818M-37GP

12

R704

R704

DY

DY

RN712

RN712

4

SRN33J-5 -GP-U

SRN33J-5 -GP-U

RN709

RN709

4

SRN0J-6-G P

SRN0J-6-G P

4

X-14D31818M-37GP

12

10/1

0114-2

1

2 3

1

DIS

DIS

2 3

0R4P2R-P AD

0R4P2R-P AD

1

2 3

RN707

RN707

1MR2J-L2-GP

1MR2J-L2-GP

RN

RN

9/23

RN

RN

0R4P2R-P AD

0R4P2R-P AD

1

4

2 3

RN708

RN708

R710 22R2J-2-G PR710 22R2J -2-GP

1 2

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

1116-9

EC703

EC703

12

DY

DY

R715 158R2F-G PR715 158R2F-G P

MHz 3.3V single ended HTT clock

66

100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

100 MHz spreading differential SRC clock

27MHz non-spreading singled clock on pin 5

27MHz spread clock on pin 6

and

100MHz differential spreading SRC clock

For EMI

1 2

Place together

C718

C718

1 2

SC12P50 V2JN-3GP

SC12P50 V2JN-3GP

X701

X701

C719

C719

1 2

SC12P50 V2JN-3GP

SC12P50 V2JN-3GP

SB_SMBC LK_R (18,21)

SB_SMBD ATA_R (18,21)

CLK_PCIE_ VGA (8 0)

CLK_PCIE_ VGA# (80)

NB_GFX_ CLK (13)

NB_GFX_ CLK# (13)

WLAN _CLK_REQ# (76)

WW AN_CLK_REQ # (76)

CPU_CLK (10)

CPU_CLK # (10)

USB_48M _CLK (21)

CLKREQ# MAP

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

0107-1

SB_SMBC LK_CK

SB_SMBD ATA_CK

VGA(100MHz)

CPU_CLK(200MHz)

SB820M_USB(48MHz)

+3.3V_RU N

8K2R2J-3-GP

8K2R2J-3-GP

8K2R2J-3-GP

8K2R2J-3-GP

12

12

R711

R711

R712

R712

0105-3

90D9R2F-1-GP

90D9R2F-1-GP

8K2R2J-3-GP

8K2R2J-3-GP

12

12

R718

R718

R717

R717

DY

DY

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Clock Generator ICS9LPRS480

Clock Generator ICS9LPRS480

Clock Generator ICS9LPRS480

Size Document N umber Rev

Size Document N umber Rev

Size D

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

No use

CLKSRC1 WLAN

CLKSRC2 WWAN

CLKSRC3 LAN

No u

se

1 2

C722 SC47P50V 2JN-3GPC722 SC47P50V 2JN-3GP

1 2

C723 SC47P50V 2JN-3GPC723 SC47P50V 2JN-3GP

Need External PU Resistor

CPU_CLK

CPU_CLK #

SC10P50V2JN-4GPDYEC704

SC10P50V2JN-4GP

WLAN _CLK_REQ#

WW AN_CLK_REQ #

EC704

12

DY

12

DY

EC705

SC10P50V2JN-4GPDYEC705

SC10P50V2JN-4GP

1

2 3

SRN10KJ -5-GP

SRN10KJ -5-GP

0105-1

RN711

RN711

+3.3V_RU N

4

0225-2

NB_14M_ CLK (13)

SB_14M_ CLK (21)

ocument Nu mber Rev

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

NB OSCIN(14MHz)

SB OSCIN(14MHz)

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

7 95Thursday, March 04 , 2010

7 95Thursday, March 04 , 2010

7 95Thursday, March 04 , 2010

1

A00

A00

A00

Page 8

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

+1.1V_RUN

SSID = CPU

D D

C C

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C801

C801

12

SKT-BGA638H176

B B

1'nd 62.10055.111

2'nd

62.10055.171

Place close to socket

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

DY

DY

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C802

C802

DY

DY

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C803

C803

12

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C804

C804

12

1119-3

HT_NB_CPU_CAD_H0(12)

HT_NB_CPU_CAD_L0(12)

HT_NB_CPU_CAD_H1(12)

HT_NB_CPU_CAD_L1(12)

HT_NB_CPU_CAD_H2(12)

HT_NB_CPU_CAD_L2(12)

HT_NB_CPU_CAD_H3(12)

HT_NB_CPU_CAD_L3(12)

HT_NB_CPU_CAD_H4(12)

HT_NB_CPU_CAD_L4(12)

HT_NB_CPU_CAD_H5(12)

HT_NB_CPU_CAD_L5(12)

HT_NB_CPU_CAD_H6(12)

HT_NB_CPU_CAD_L6(12)

HT_NB_CPU_CAD_H7(12)

HT_NB_CPU_CAD_L7(12)

HT_NB_CPU_CAD_H8(12)

HT_NB_CPU_CAD_L8(12)

HT_NB_CPU_CAD_H9(12)

HT_NB_CPU_CAD_L9(12)

HT_NB_CPU_CAD_H10(12)

HT_NB_CPU_CAD_L10(12)

HT_NB_CPU_CAD_H11(12)

HT_NB_CPU_CAD_L11(12)

HT_NB_CPU_CAD_H12(12)

HT_NB_CPU_CAD_L12(12)

HT_NB_CPU_CAD_H13(12)

HT_NB_CPU_CAD_L13(12)

HT_NB_CPU_CAD_H14(12)

HT_NB_CPU_CAD_L14(12)

HT_NB_CPU_CAD_H15(12)

HT_NB_CPU_CAD_L15(12)

HT_NB_CPU_CLK_H0(12)

HT_NB_CPU_CLK_L0(12)

HT_NB_CPU_CLK_H1(12)

HT_NB_CPU_CLK_L1(12)

HT_NB_CPU_CTL_H0(12)

HT_NB_CPU_CTL_L0(12)

HT_NB_CPU_CTL_H1(12)

HT_NB_CPU_CTL_L1(12)

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C805

C805

12

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C806

C806

12

C807

C807

12

1.1V(1.5A) for VLDT

CPU1A

CPU1A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

DANUBE

DANUBE

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

1 OF 6

1 OF 6

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

HT_CPU_NB_CAD_H0 (12)

HT_CPU_NB_CAD_L0 (12)

HT_CPU_NB_CAD_H1 (12)

HT_CPU_NB_CAD_L1 (12)

HT_CPU_NB_CAD_H2 (12)

HT_CPU_NB_CAD_L2 (12)

HT_CPU_NB_CAD_H3 (12)

HT_CPU_NB_CAD_L3 (12)

HT_CPU_NB_CAD_H4 (12)

HT_CPU_NB_CAD_L4 (12)

HT_CPU_NB_CAD_H5 (12)

HT_CPU_NB_CAD_L5 (12)

HT_CPU_NB_CAD_H6 (12)

HT_CPU_NB_CAD_L6 (12)

HT_CPU_NB_CAD_H7 (12)

HT_CPU_NB_CAD_L7 (12)

HT_CPU_NB_CAD_H8 (12)

HT_CPU_NB_CAD_L8 (12)

HT_CPU_NB_CAD_H9 (12)

HT_CPU_NB_CAD_L9 (12)

HT_CPU_NB_CAD_H10 (12)

HT_CPU_NB_CAD_L10 (12)

HT_CPU_NB_CAD_H11 (12)

HT_CPU_NB_CAD_L11 (12)

HT_CPU_NB_CAD_H12 (12)

HT_CPU_NB_CAD_L12 (12)

HT_CPU_NB_CAD_H13 (12)

HT_CPU_NB_CAD_L13 (12)

HT_CPU_NB_CAD_H14 (12)

HT_CPU_NB_CAD_L14 (12)

HT_CPU_NB_CAD_H15 (12)

HT_CPU_NB_CAD_L15 (12)

HT_CPU_NB_CLK_H0 (12)

HT_CPU_NB_CLK_L0 (12)

HT_CPU_NB_CLK_H1 (12)

HT_CPU_NB_CLK_L1 (12)

HT_CPU_NB_CTL_H0 (12)

HT_CPU_NB_CTL_L0 (12)

HT_CPU_NB_CTL_H1 (12)

HT_CPU_NB_CTL_L1 (12)

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

CPU_HT_LINK I/F_(1/4)

CPU_HT_LINK I/F_(1/4)

CPU_HT_LINK I/F_(1/4)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

5

A4

Date: Sheet of

Date: Sheet of

4

3

Date: Sheet of

2

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

A00

A00

A00

8 95Thursday, March 04, 2010

8 95Thursday, March 04, 2010

8 95Thursday, March 04, 2010

1

Page 9

5

WWW.AliSaler.Com

WWW.AliSaler.Com

SSID = CPU

1231-2

Set empty: C905,C906,C903,C909,C913,C910,C915

D D

+CPU_VD DR

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C901

C901

12

C C

+1.5V_SU S

R901 39D2R2F -L-GPR901 39D2R2F -L-GP

R903 39D2R2F -L-GPR903 39D2R2F -L-GP

12

C917

C917

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

B B

MEM_MA_ ADD[0..15](18) MEM_MB_ ADD[0..15] (19)

A A

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C902

C902

12

1 2

1 2

DDR3_A_ DRAMRST#(18)

MEM_MA0 _ODT0(18 )

MEM_MA0 _ODT1(18 )

MEM_MA0 _CS#0(18)

MEM_MA0 _CS#1(18)

MEM_MA_ CKE0(18)

MEM_MA_ CKE1(18)

MEM_MA_ CLK0_P(18)

MEM_MA_ CLK0_N(18 )

MEM_MA_ CLK1_P(18)

MEM_MA_ CLK1_N(18 )

MEM_MA_ BANK0(18)

MEM_MA_ BANK1(18)

MEM_MA_ BANK2(18)

MEM_MA_ RAS#(18)

MEM_MA_ CAS#(18)

MEM_MA_ WE#(18)

5

C903

C903

12

DY

DY

Place near to CPU

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C913

C913

C904

12

DY

DY

C904

12

+CPU_VD DR

MEMZN

MEM_MA_ ADD0

MEM_MA_ ADD1

MEM_MA_ ADD2

MEM_MA_ ADD3

MEM_MA_ ADD4

MEM_MA_ ADD5

MEM_MA_ ADD6

MEM_MA_ ADD7

MEM_MA_ ADD8

MEM_MA_ ADD9

MEM_MA_ ADD10

MEM_MA_ ADD11

MEM_MA_ ADD12

MEM_MA_ ADD13

MEM_MA_ ADD14

MEM_MA_ ADD15

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C914

C914

12

1119-3

D10

C10

B10

AD10

AF10

AE10

H16

T19

V22

U21

V19

T20

U19

U20

V20

J22

J20

N19

N20

E16

F16

Y16

AA16

P19

P20

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

R20

R23

J21

R19

T22

T24

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C905

C905

12

12

DY

DY

DY

DY

0.9V, 1.25A--DDR1066

1.05V, 1.75A---DDR1333

CPU1B

CPU1B

VDDR

VDDR

VDDR

VDDR

MEMZP

MEMZN

MA_RESET#

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS#0

MA0_CS#1

MA1_CS#0

MA1_CS#1

MA_CKE0

MA_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_RAS#

MA_CAS#

MA_WE#

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C906

C906

1231-2

DANUBE

DANUBE

VDDR_SENSE

4

SC1000P50V3JN-GP-U

SC1000P50V3JN-GP-U

C907

C907

12

2 OF 6

2 OF 6

VDDR

VDDR

VDDR

VDDR

VDDR

MEMVREF

MB_RESET#

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS#0

MB0_CS#1

MB1_CS#0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS#

MB_CAS#

MB_WE#

4

C915

C915

12

DY

DY

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

SC1000P50V3JN-GP-U

SC1000P50V3JN-GP-U

SC1000P50V3JN-GP-U

SC1000P50V3JN-GP-U

C908

C908

12

12

DY

DY

TP_CPU_ VDDR_SENSE

MEM_MB_ ADD0

MEM_MB_ ADD1

MEM_MB_ ADD2

MEM_MB_ ADD3

MEM_MB_ ADD4

MEM_MB_ ADD5

MEM_MB_ ADD6

MEM_MB_ ADD7

MEM_MB_ ADD8

MEM_MB_ ADD9

MEM_MB_ ADD10

MEM_MB_ ADD11

MEM_MB_ ADD12

MEM_MB_ ADD13

MEM_MB_ ADD14

MEM_MB_ ADD15

4.7UF*4

0.22UF*4

1000PF*4

180PF*4

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C909

C909

C910

C910

12

DY

DY

+0.75V_S US_CPU_M_VRE F

TP901DYTP901

1

DY

DDR3_B_ DRAMRST# (19 )

MEM_MB0 _ODT0 (19)

MEM_MB0 _ODT1 (19)

MEM_MB0 _CS#0 (19)

MEM_MB0 _CS#1 (19)

MEM_MB_ CKE0 (19)

MEM_MB_ CKE1 (19)

MEM_MB_ CLK0_P (19)

MEM_MB_ CLK0_N (1 9)

MEM_MB_ CLK1_P (19)

MEM_MB_ CLK1_N (1 9)

MEM_MB_ BANK0 (19)

MEM_MB_ BANK1 (19)

MEM_MB_ BANK2 (19)

MEM_MB_ RAS# (19)

MEM_MB_ CAS# (19)

MEM_MB_ WE# (19)

12

SC180P50V2JN-1GP

SC180P50V2JN-1GP

C911

C911

1119-1

C916

C916

12

1119-3

SC1000P50V3JN-GP-U

SC1000P50V3JN-GP-U

12

3

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C919

C919

3

C912

C912

12

+1.5V_SU S

1KR3F-GP

1KR3F-GP

12

C918

C918

R902

12

12

R902

1KR3F-GP

1KR3F-GP

12

R905

R905

C920

C920

CLOSE TO CPU

M_A_DQ[6 3..0](18)

1117-8

Remove

M_A_DM[7 ..0](18)

2

3 OF 6

3 OF 6

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ1 0

M_A_DQ1 1

M_A_DQ1 2

M_A_DQ1 3

M_A_DQ1 4

M_A_DQ1 5

M_A_DQ1 6

M_A_DQ1 7

M_A_DQ1 8

M_A_DQ1 9

M_A_DQ2 0

M_A_DQ2 1

M_A_DQ2 2

M_A_DQ2 3

M_A_DQ2 4

M_A_DQ2 5

M_A_DQ2 6

M_A_DQ2 7

M_A_DQ2 8

M_A_DQ2 9

M_A_DQ3 0

M_A_DQ3 1

M_A_DQ3 2

M_A_DQ3 3

M_A_DQ3 4

M_A_DQ3 5

M_A_DQ3 6

M_A_DQ3 7

M_A_DQ3 8

M_A_DQ3 9

M_A_DQ4 0

M_A_DQ4 1

M_A_DQ4 2

M_A_DQ4 3

M_A_DQ4 4

M_A_DQ4 5MEMZP

M_A_DQ4 6

M_A_DQ4 7

M_A_DQ4 8

M_A_DQ4 9

M_A_DQ5 0

M_A_DQ5 1

M_A_DQ5 2

M_A_DQ5 3

M_A_DQ5 4

M_A_DQ5 5

M_A_DQ5 6

M_A_DQ5 7

M_A_DQ5 8

M_A_DQ5 9

M_A_DQ6 0

M_A_DQ6 1

M_A_DQ6 2

M_A_DQ6 3

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS 0(18)

M_A_DQS #0(18)

M_A_DQS 1(18)

M_A_DQS #1(18)

M_A_DQS 2(18)

M_A_DQS #2(18)

M_A_DQS 3(18)

M_A_DQS #3(18)

M_A_DQS 4(18)

M_A_DQS #4(18)

M_A_DQS 5(18)

M_A_DQS #5(18)

M_A_DQS 6(18)

M_A_DQS #6(18)

M_A_DQS 7(18)

M_A_DQS #7(18)

G12

MA_DATA0

F12

MA_DATA1

H14

MA_DATA2

G14

MA_DATA3

H11

MA_DATA4

H12

MA_DATA5

C13

MA_DATA6

E13

MA_DATA7

H15

MA_DATA8

E15

MA_DATA9

E17

MA_DATA10

H17

MA_DATA11

E14

MA_DATA12

F14

MA_DATA13

C17

MA_DATA14

G17

MA_DATA15

G18

MA_DATA16

C19

MA_DATA17

D22

MA_DATA18

E20

MA_DATA19

E18

MA_DATA20

F18

MA_DATA21

B22

MA_DATA22

C23

MA_DATA23

F20

MA_DATA24

F22

MA_DATA25

H24

MA_DATA26

J19

MA_DATA27

E21

MA_DATA28

E22

MA_DATA29

H20

MA_DATA30

H22

MA_DATA31

Y24

MA_DATA32

AB24

MA_DATA33

AB22

MA_DATA34

AA21

MA_DATA35

W22

MA_DATA36

W21

MA_DATA37

Y22

MA_DATA38

AA22

MA_DATA39

Y20

MA_DATA40

AA20

MA_DATA41

AA18

MA_DATA42

AB18

MA_DATA43

AB21

MA_DATA44

AD21

MA_DATA45

AD19

MA_DATA46

Y18

MA_DATA47

AD17

MA_DATA48

W16

MA_DATA49

W14

MA_DATA50

Y14

MA_DATA51

Y17

MA_DATA52

AB17

MA_DATA53

AB15

MA_DATA54

AD15

MA_DATA55

AB13

MA_DATA56

AD13

MA_DATA57

Y12

MA_DATA58

W11

MA_DATA59

AB14

MA_DATA60

AA14

MA_DATA61

AB12

MA_DATA62

AA12

MA_DATA63

E12

MA_DM0

C15

MA_DM1

E19

MA_DM2

F24

MA_DM3

AC24

MA_DM4

Y19

MA_DM5

AB16

MA_DM6

Y13

MA_DM7

G13

MA_DQS_H0

H13

MA_DQS_L0

G16

MA_DQS_H1

G15

MA_DQS_L1

C22

MA_DQS_H2

C21

MA_DQS_L2

G22

MA_DQS_H3

G21

MA_DQS_L3

AD23

MA_DQS_H4

AC23

MA_DQS_L4

AB19

MA_DQS_H5

AB20

MA_DQS_L5

Y15

MA_DQS_H6

W15

MA_DQS_L6

W12

MA_DQS_H7

W13

MA_DQS_L7

2

CPU1C

CPU1C

M_B_DQ0

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

DANUBE

DANUBE

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

C11

M_B_DQ1

A11

M_B_DQ2

A14

M_B_DQ3

B14

M_B_DQ4

G11

M_B_DQ5

E11

M_B_DQ6

D12

M_B_DQ7

A13

M_B_DQ8

A15

M_B_DQ9

A16

M_B_DQ1 0

A19

M_B_DQ1 1

A20

M_B_DQ1 2

C14

M_B_DQ1 3

D14

M_B_DQ1 4

C18

M_B_DQ1 5

D18

M_B_DQ1 6

D20

M_B_DQ1 7

A21

M_B_DQ1 8

D24

M_B_DQ1 9

C25

M_B_DQ2 0

B20

M_B_DQ2 1

C20

M_B_DQ2 2

B24

M_B_DQ2 3

C24

M_B_DQ2 4

E23

M_B_DQ2 5

E24

M_B_DQ2 6

G25

M_B_DQ2 7

G26

M_B_DQ2 8

C26

M_B_DQ2 9

D26

M_B_DQ3 0

G23

M_B_DQ3 1

G24

M_B_DQ3 2

AA24

M_B_DQ3 3

AA23

M_B_DQ3 4

AD24

M_B_DQ3 5

AE24

M_B_DQ3 6

AA26

M_B_DQ3 7

AA25

M_B_DQ3 8

AD26

M_B_DQ3 9

AE25

M_B_DQ4 0

AC22

M_B_DQ4 1

AD22

M_B_DQ4 2

AE20

M_B_DQ4 3

AF20

M_B_DQ4 4

AF24

M_B_DQ4 5

AF23

M_B_DQ4 6

AC20

M_B_DQ4 7

AD20

M_B_DQ4 8

AD18

M_B_DQ4 9

AE18

M_B_DQ5 0

AC14

M_B_DQ5 1

AD14

M_B_DQ5 2

AF19

M_B_DQ5 3

AC18

M_B_DQ5 4

AF16

M_B_DQ5 5

AF15

M_B_DQ5 6

AF13

M_B_DQ5 7

AC12

M_B_DQ5 8

AB11

M_B_DQ5 9

Y11

M_B_DQ6 0

AE14

M_B_DQ6 1

AF14

M_B_DQ6 2

AF11

M_B_DQ6 3

AD11

M_B_DM0

A12

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

CPU_DDR_(2/4)

CPU_DDR_(2/4)

CPU_DDR_(2/4)

M_B_DM1

B16

M_B_DM2

A22

M_B_DM3

E25

M_B_DM4

AB26

M_B_DM5

AE22

M_B_DM6

AC16

M_B_DM7

AD12

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

1

M_B_DQ[6 3..0] (19)

M_B_DM[7 ..0] (19)

M_B_DQS 0 (19)

M_B_DQS #0 (19)

M_B_DQS 1 (19)

M_B_DQS #1 (19)

M_B_DQS 2 (19)

M_B_DQS #2 (19)

M_B_DQS 3 (19)

M_B_DQS #3 (19)

M_B_DQS 4 (19)

M_B_DQS #4 (19)

M_B_DQS 5 (19)

M_B_DQS #5 (19)

M_B_DQS 6 (19)

M_B_DQS #6 (19)

M_B_DQS 7 (19)

M_B_DQS #7 (19)

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

9 95Thursday, March 04 , 2010

9 95Thursday, March 04 , 2010

9 95Thursday, March 04 , 2010

1

A00

A00

A00

Page 10

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

SSID = CPU

1119-1

L1001

L1001

1 2

SC180P50V2JN-1GP

SC180P50V2JN-1GP

PBY160808 T-330Y-N-GP

D D

+1.5V_RU N

10/5

4

RN1001

RN1001

SRN300J -3-GP

SRN300J -3-GP

1

2 3

CPU_LDT _RST#(20)

CPU_LDT _PWRGD(20,42)

CPU_LDT _STOP#(13 ,20)

C C

1 2

R1001 0R0402-P ADR1001 0R0402-P AD

1 2

R1002 0R0402-P ADR1002 0R0402-P AD

1 2

R1003 0R0402-P ADR1003 0R0402-P AD

CPU_CLK(200MHz)

For HDT DBG

1231-1

CPU_R_L DT_RST#

CPU_R_L DT_PWRGD

CPU_R_L DT_STOP#

11/6

CPU_R_L DT_RST#

HDT_RST _R#

C1008

SC10P50V2JN-4GP

C1008

SC10P50V2JN-4GP

12

9/11 S1g4 no support LDTREQ#

+1.5V_RU N

R1012 300R2J-4-GP

R1012 300R2J-4-GP

1 2

DY

DY

R1013 300R2J-4-GP

R1013 300R2J-4-GP

1 2

DY

DY

R1014 300R2J-4-GP

R1014 300R2J-4-GP

1 2

DY

DY

R1016 300R2J-4-GP

R1016 300R2J-4-GP

1 2

DY

DY

R1017 1KR2J-1-GPR1017 1KR2J-1-GP

1 2

R1025 1KR2J-1-GPR1025 1KR2J-1-GP

1 2

RN1002 SRN1KJ-7 -GPRN1 002 SRN1KJ-7 -GP

1

2 3

RN1004

RN1004

1

2

3

4 5

SRN1KJ-8 -GP

B B

+1.5V_SU S

R1026

R1026

1KR2J-1-G P

1KR2J-1-G P

1 2

CPU_TES T27

R1029

R1029

300R2J-4 -GP

300R2J-4 -GP

DY

DY

1 2

SRN1KJ-8 -GP

TP1001TP1001

TP1003TP1003

TP1004TP1004

TP1005TP1005

TP1006TP1006

TP1007TP1007

TP1008TP1008

TP1009TP1009

TP1010TP1010

TP1011TP1011

1229-1

A A

CPU_PRO CHOT#_EC(37)

5

CPU_LDT _REQ#

CPU_DBR DY

TP_CPU_ TEST14

TP_CPU_ TEST15

CPU_TES T23

CPU_TES T12

4

8

7

6

1

1

1

1

1

1

1

1

1

1

+3.3V_RU N

CPU_TES T18

CPU_TES T19

CPU_TES T20

CPU_TES T21

CPU_TES T24

CPU_TES T22

TP_CPU_ VDDIO_SUS_FB_H

TP_CPU_ VDDIO_SUS_FB_L

TP_CPU_ TEST28_H

TP_CPU_ TEST28_L

TP_CPU_ TEST17

TP_CPU_ TEST16

TP_CPU_ TEST15

TP_CPU_ TEST14

TP_CPU_ TEST8

TP_CPU_ TEST7

8K2R2J-3-GP

8K2R2J-3-GP

12

R1040

R1040

+1.5V_RU N

2K2R2J-2-GP

2K2R2J-2-GP

12

1

2

Q1005

Q1005

PMBS390 4-1-GP

PMBS390 4-1-GP

R1039

R1039

3

1129-1

510R2F-L -GP

510R2F-L -GP

CPU_SIC(21)

CPU_SID(21)

TALERT#(21,39)

CPU_PRO CHOT#

CPU_CLK(7)

CPU_CLK #(7)

R1009

R1009

1 2

DY

DY

0R2J-2-GP

0R2J-2-GP

EC1001

12

DY

1231-2

+1.5V_SU S

12

12

R1018

R1018

DY

DY

12

12

R1020

R1020

510R2F-L -GP

510R2F-L -GP

For old HDT tool (3.3V level)

9/22

RN1005

RN1005

SRN1KJ-7 -GP

SRN1KJ-7 -GP

4

DY

DY

+1.5V_SU S

PBY160808 T-330Y-N-GP

C1001

C1001

33R, 3A

12

11/6

Cloce To CPU

C1005 SC3900P 50V2KX-2GPC 1005 SC3900P50V2KX -2GP

C1006 SC3900P 50V2KX-2GPC 1006 SC3900P50V2KX -2GP

R1008 1 69R2F-GPR1008 1 69R2F-GP

1 2

1 2

0108-5

Close CPU

SCD01U16V2KX-3GPDYEC1001

SCD01U16V2KX-3GP

R1019

R1019

510R2F-L -GP

510R2F-L -GP

R1022

R1022

510R2F-L -GP

510R2F-L -GP

4

1

2 3

10KR2J-3-GP

10KR2J-3-GP

12

DY

DY

+1.1V_RU N

R1010 44D2R2F -GPR1010 44D2R2F -GP

R1011 44D2R2F -GPR1011 44D2R2F -GP

CPU_VDD 0_RUN_FB_H(47)

CPU_VDD 0_RUN_FB_L(47)

CPU_VDD 1_RUN_FB_H(47)

CPU_VDD 1_RUN_FB_L(47)

1231-1

312

PMBS390 4-1-GP

PMBS390 4-1-GP

R1037

R1037

Q1004 P MBS3904-1-GP

Q1004 P MBS3904-1-GP

LYAOUT:ROUTE VDDA TRACE APPROX.

50mils WIDE(USE 2X25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

+2.5V_RU N_VDDA+2.5V_RU N

2.5V(250mA) for VDDA

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C1002

2K2R2J-2-GP

2K2R2J-2-GP

Q1001

Q1001

1 2

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1 2

1 2

1 2

12

R1032

R1032

+1.8V_RU N+3.3V_R UN

2K2R2J-2-GP

2K2R2J-2-GP

DY

DY

312

DY

DY

C1007

C1007

12

DY

DY

R1023

R1023

0R0402-P AD

0R0402-P AD

1231-11231-1

11/6

1KR2J-1-GP

1KR2J-1-GP

12

R1036

R1036

C1002

12

CPU_R_L DT_PWRGD

CPU_R_L DT_STOP#

CPU_LDT _REQ#

CPU_SIC

CPU_SID

CPU_ALE RT#

CPU_DBR DY

CPU_TMS

CPU_TCK

CPU_TRS T#

CPU_TDI

CPU_TES T23

CPU_TES T18

CPU_TES T19

CPU_TES T25_H

CPU_TES T25_L

CPU_TES T21

CPU_TES T20

CPU_TES T24

CPU_TES T22

CPU_TES T12

CPU_TES T27

CPU_TES T9

12

R1033

R1033

CPU_ALE RT#

HDT_RST _R#HDT_RST #

12

CPU_SIC

CPU_SID

SC3300P50V3KX-1GP

SC3300P50V3KX-1GP

C1003

C1003

CPUCLK_ IN

CPUCLK_ IN#

CPU_HTR EF0

CPU_HTR EF1

3

C1004

C1004

12

F10

AF4

AF5

AE6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

AB8

AF7

AE7

AE8

AC8

AF8

AA6

F8

F9

A9

A8

B7

A7

C6

R6

P6

F6

E6

Y6

G9

E9

E8

C2

A3

A5

B3

B5

C1

CPU_PW RGD_SVID_REG(47)

CPU1D

CPU1D

VDDA

VDDA

CLKIN_H

CLKIN_L

RESET#

PWROK

LDTSTOP#

LDTREQ#

SIC

SID

ALERT#

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST#

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD#A3

RSVD#A5

RSVD#B3

RSVD#B5

RSVD#C1

H_THERM TRIP#(21,37,39,4 2,82)

DANUBE

DANUBE

THERMTRIP#

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

+KBC_PW R

10KR2J-3-GP

10KR2J-3-GP

RSVD#W18

PROCHOT#

MEMHOT#

THERMDC

THERMDA

TEST28_H

TEST28_L

TEST29_H

TEST29_L

RSVD#H18

RSVD#H19

RSVD#AA7

RSVD#D5

RSVD#C5

8K2R2J-3-GP

8K2R2J-3-GP

4 OF 6

4 OF 6

M11

VSS

W18

A6

SVC

A4

SVD

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

DBREQ#

AE9

TDO

J7

H8

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

C3

TEST7

K8

TEST10

C4

TEST8

C9

C8

H18

H19

AA7

D5

C5

11/11

+1.5V_RU N

2K2R2J-2-GP

R1027

R1027

312

PMBS390 4-1-GP

PMBS390 4-1-GP

+1.8V_RU N+3.3V_RU N

2K2R2J-2-GP

2K2R2J-2-GP

R1034

R1034

Q1003 PM BS3904-1-GPQ1003 PMBS390 4-1-GP

312

1 2

DY

DY

2K2R2J-2-GP

Q1002

Q1002

12

DY

DY

12

R1041 0R2J-2-GP

R1041 0R2J-2-GP

1225-4

+1.5V_SU S

9/25

4

RN1006

RN1006

SRN1KJ-7 -GP

SRN1KJ-7 -GP

1

2 3

CPU_PRO CHOT#

CPU_MEM HOT#

TP_CPU_ VDDIO_SUS_FB_H

TP_CPU_ VDDIO_SUS_FB_L

R1015

CPU_DBR EQ#

CPU_TDO

TP_CPU_ TEST28_H

TP_CPU_ TEST28_L

TP_CPU_ TEST17

TP_CPU_ TEST16

TP_CPU_ TEST15

TP_CPU_ TEST14

TP_CPU_ TEST7

CPU_TES T10

TP_CPU_ TEST8

CPU_TES T29H

CPU_TES T29L

12

12

R1035

R1035

R1015

1 2

300R2J-4 -GP

300R2J-4 -GP

1 2

R1021 300R3-GP

R1021 300R3-GP

1 2

R1024 80D6R2F-L-GPR 1024 80D6R2F -L-GP

R1028

R1028

CPU_THE RMTRIP#

CPU_R_L DT_PWRGD

0112-2

2

+1.5V_SU S

9/14

300R2J-4-GP

300R2J-4-GP

1KR2J-1-GP

1KR2J-1-GP

12

12

R1007

R1007

R1006

R1006

CPU_SVC (47)

CPU_SVD (47)

CPU_THE RMTRIP#

1

TP1002TP1002

S1G4 not support MEMHOT

H_THERM DC (39)

H_THERM DA (39)

CPU_VDD NB_RUN_FB_H (47)

CPU_VDD NB_RUN_FB_L (47 )

+1.5V_SU S

+1.1V_RU N

DY

DY

CPU_PRO CHOT# (20)

LAYOUT: Route FBCLKOUT_H/L

differentially impedance 80

HDT Connectors

CPU_DBR EQ#

CPU_DBR DY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRS T#

CPU_TDOC PU_TDO

CPU_R_L DT_RST#

1.5V

HDT_RST #

.3V

3

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU_Control&Debug_(3/4)

CPU_Control&Debug_(3/4)

CPU_Control&Debug_(3/4)

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1.5V_SU S

1 2

DY

DY

R1038 0R2J-2-GP

R1038 0R2J-2-GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

1

HDT1

HDT1

1

DY

DY

3

5

7

9

11

13

15

17

19

21

23

SMC-CONN 26A-FP

SMC-CONN 26A-FP

10 95Thu rsday, March 04, 2010

10 95Thu rsday, March 04, 2010

10 95Thu rsday, March 04, 2010

2

4

6

8

10

12

14

16

18

20

22

24

26

A00

A00

A00

Page 11

5

WWW.AliSaler.Com

WWW.AliSaler.Com

4

3

2

1

SSID = CPU

D D

6 OF 6

6 OF 6

CPU1F

CPU1F

AA4

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AB2

VSS

AB7

VSS

AB9

VSS

AB23

VSS

AB25

VSS

AC11

VSS

AC13

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC21

VSS

AD6

C C

B B

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

H21

H23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B4

VSS

B6

VSS

B8

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D6

VSS

D8

VSS

D9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E4

VSS

F2

VSS

F11

VSS

F13

VSS

F15

VSS

F17

VSS

F19

VSS

F21

VSS

F23

VSS

F25

VSS

H7

VSS

H9

VSS

VSS

VSS

J4

VSS

VSS

VSS

VSS

DANUBE

DANUBE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+1.5V_SU S

1231-2

(36A) for 35W S1G4 VDD

+VCC_CO RE +VCC_CO RE

+VDDNB

Bottom Side Decoupling Bottom Side Decoupling

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SCD22U10V2KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1103

C1103

C1101

DY

DY

C1101

12

12

12

1231-2 1231-2

22uF *2

10uF *2

0.22uF *1

0.01uF *1

180pF *1

0.9V(4A) for VDDNB

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

DY

DY

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1115

C1115

C1116

C1116

12

12

SCD22U10V2KX-1GP

C1104

C1104

C1105

C1105

12

12

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

C1102

C1102

C1107

C1107

C1106

C1106

12

12

1119-3

C1117

C1117

22UF *3

1231-2

1.5V(

3A) for VDDIO

Bottom Side Decoupling

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C1131

C1131

C1130

C1130

12

12

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD1U10V2KX-5GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C1132

C1132

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1119-1

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

C1120

C1133

C1133

C1120

C1135

C1134

C1134

12

C1135

12

12

CPU1E

CPU1E

G4

VDD

H2

VDD

J9

VDD

J11

VDD

J13

VDD

J15

VDD

K6

VDD

K10

VDD

K12

VDD

K14

VDD

L4

VDD

L7

VDD

L9

VDD

L11

VDD

L13

VDD

L15

VDD

M2

VDD

M6

VDD

M8

VDD

M10

VDD

N7

VDD

N9

VDD

N11

VDD

K16

VDDNB

M16

VDDNB

P16

VDDNB

T16

VDDNB

V16

VDDNB

H25

VDDIO

J17

VDDIO

K18

VDDIO

K21

VDDIO

K23

VDDIO

K25

VDDIO

L17

VDDIO

M18

VDDIO

M21

VDDIO

M23

VDDIO

M25

VDDIO

N17

VDDIO

C1121

C1121

12

5 OF 6

5 OF 6

DANUBE

DANUBE

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

DY

DY

12

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

C1108

C1108

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1110

C1110

C1109

C1109

12

12

DY

DY

1119-3

22uF *2

10uF *2

0.22uF *1

0.01uF *1

180pF *1

Place near to CPU

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

DY

DY

SC180P50V2JN-1GP

C1118

C1118

12

12

DY

DY

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C1119

C1119

C1122

C1122

12

DY

DY

DY

DY

1119-3

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1111

C1111

12

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C1123

C1123

12

0.01UF *1

0.1UF *2

0.22UF *4

4.7UF *4

180PF *2

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1112

C1112

C1141

C1141

12

12

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C1125

C1125

C1124

C1124

12

12

DY

DY

DY

DY

1231-2 1231-2

1119-3

10UF *2

0.22UF *2

180PF *1

C1114

C1114

+1.5V_SU S

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

C1129

C1126

C1126

C1127

C1127

12

12

DY

DY

C1129

C1128

C1128

12

12

9/14

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU_Power_(4/4)

CPU_Power_(4/4)

CPU_Power_(4/4)

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

Berry AMD Discrete/UMA

1

of

11 95Thu rsday, March 04, 2010

11 95Thu rsday, March 04, 2010

11 95Thu rsday, March 04, 2010

A00

A00

A00

Page 12

5

WWW.AliSaler.Com

WWW.AliSaler.Com

HT_CPU_ NB_CAD_H0(8)

SSID = N.B

RS880M : 71.RS880.M05

D D

C C

Place < 100mils from pin C23 and A24

B B

9/11

WLAN

LAN

WWAN

A A

A-LINK

5

ALINK_NBR X_SBTX_P0(20)

ALINK_NBR X_SBTX_N0(20)

ALINK_NBR X_SBTX_P1(20)

ALINK_NBR X_SBTX_N1(20)

ALINK_NBR X_SBTX_P2(20)

ALINK_NBR X_SBTX_N2(20)

ALINK_NBR X_SBTX_P3(20)

ALINK_NBR X_SBTX_N3(20)

HT_CPU_ NB_CAD_L0(8)

HT_CPU_ NB_CAD_H1(8 )

HT_CPU_ NB_CAD_L1(8)

HT_CPU_ NB_CAD_H2(8 )

HT_CPU_ NB_CAD_L2(8)

HT_CPU_ NB_CAD_H3(8 )

HT_CPU_ NB_CAD_L3(8)

HT_CPU_ NB_CAD_H4(8 )

HT_CPU_ NB_CAD_L4(8)

HT_CPU_ NB_CAD_H5(8 )

HT_CPU_ NB_CAD_L5(8)

HT_CPU_ NB_CAD_H6(8 )

HT_CPU_ NB_CAD_L6(8)

HT_CPU_ NB_CAD_H7(8 )

HT_CPU_ NB_CAD_L7(8)

HT_CPU_ NB_CAD_H8(8 )

HT_CPU_ NB_CAD_L8(8)

HT_CPU_ NB_CAD_H9(8 )

HT_CPU_ NB_CAD_L9(8)

HT_CPU_ NB_CAD_H10(8)

HT_CPU_ NB_CAD_L10(8)

HT_CPU_ NB_CAD_H11(8)

HT_CPU_ NB_CAD_L11(8)

HT_CPU_ NB_CAD_H12(8)

HT_CPU_ NB_CAD_L12(8)

HT_CPU_ NB_CAD_H13(8)

HT_CPU_ NB_CAD_L13(8)

HT_CPU_ NB_CAD_H14(8)

HT_CPU_ NB_CAD_L14(8)

HT_CPU_ NB_CAD_H15(8)

HT_CPU_ NB_CAD_L15(8)

HT_CPU_ NB_CLK_H0(8)

HT_CPU_ NB_CLK_L0(8)

HT_CPU_ NB_CLK_H1(8)

HT_CPU_ NB_CLK_L1(8)

HT_CPU_ NB_CTL_H0(8)

HT_CPU_ NB_CTL_L0(8)

HT_CPU_ NB_CTL_H1(8)

HT_CPU_ NB_CTL_L1(8)

R1201 301R2F-GPR 1201 301 R2F-GP

1 2

9/15

PCIE_NRX_ GTX_P15

PCIE_NRX_ GTX_N15

PCIE_NRX_ GTX_P14

PCIE_NRX_ GTX_N14

PCIE_NRX_ GTX_P13

PCIE_NRX_ GTX_N13

PCIE_NRX_ GTX_P12

PCIE_NRX_ GTX_N12

PCIE_NRX_ GTX_P11

PCIE_NRX_ GTX_N11

PCIE_NRX_ GTX_P10

PCIE_NRX_ GTX_N10

PCIE_NRX_ GTX_P9

PCIE_NRX_ GTX_N9

PCIE_NRX_ GTX_P8

PCIE_NRX_ GTX_N8

PCIE_NRX_ GTX_P7

PCIE_NRX_ GTX_N7

PCIE_NRX_ GTX_P6

PCIE_NRX_ GTX_N6

PCIE_NRX_ GTX_P5

PCIE_NRX_ GTX_N5

LANE REVERSAL

PCIE_NRX_ GTX_P4

PCIE_NRX_ GTX_N4

PCIE_NRX_ GTX_P3

PCIE_NRX_ GTX_N3

PCIE_NRX_ GTX_P2

PCIE_NRX_ GTX_N2

PCIE_NRX_ GTX_P1

PCIE_NRX_ GTX_N1

PCIE_NRX_ GTX_P0

PCIE_NRX_ GTX_N0

PCIE_RXP0(7 6)

PCIE_RXN0(76)

PCIE_RXP1(7 6)

PCIE_RXN1(76)

PCIE_RXP2(7 6)

PCIE_RXN2(76)

4

U1A

U1A

Y25

HT_RXCAD0P

Y24

HT_RXCAD0N

V22

HT_RXCAD1P

V23

HT_RXCAD1N

V25

HT_RXCAD2P

V24

HT_RXCAD2N

U24

HT_RXCAD3P

U25

HT_RXCAD3N

T25

HT_RXCAD4P

T24

HT_RXCAD4N

P22

HT_RXCAD5P

P23

HT_RXCAD5N

P25

HT_RXCAD6P

P24

HT_RXCAD6N

N24

HT_RXCAD7P

N25

HT_RXCAD7N

AC24

HT_RXCAD8P

AC25

HT_RXCAD8N

AB25

HT_RXCAD9P

AB24

HT_RXCAD9N

AA24

HT_RXCAD10P

AA25

HT_RXCAD10N

Y22

HT_RXCAD11P

Y23

HT_RXCAD11N

W21

HT_RXCAD12P

W20

HT_RXCAD12N

V21

HT_RXCAD13P

V20

HT_RXCAD13N

U20

HT_RXCAD14P

U21

HT_RXCAD14N

U19

HT_RXCAD15P

U18

HT_RXCAD15N

T22

HT_RXCLK0P

T23

HT_RXCLK0N

AB23

HT_RXCLK1P

AA22

HT_RXCLK1N

M22

HT_RXCTL0P

M23

HT_RXCTL0N

R21

HT_RXCTL1P

R20

HT_RXCA LP HT_TXCA LP

HT_RXCA LN

C23

A24

RS880M-1 -GP

RS880M-1 -GP

U1B

U1B

D4

GFX_RX0P

C4

GFX_RX0N

A3

GFX_RX1P

B3

GFX_RX1N

C2

GFX_RX2P

C1

GFX_RX2N

E5

GFX_RX3P

F5

GFX_RX3N

G5

GFX_RX4P

G6

GFX_RX4N

H5

GFX_RX5P

H6

GFX_RX5N

J6

GFX_RX6P

J5

GFX_RX6N

J7

GFX_RX7P

J8

GFX_RX7N

L5

GFX_RX8P

L6

GFX_RX8N

M8

GFX_RX9P

L8

GFX_RX9N

P7

GFX_RX10P

M7

GFX_RX10N

P5

GFX_RX11P

M5

GFX_RX11N

R8

GFX_RX12P

P8

GFX_RX12N

R6

GFX_RX13P

R5

GFX_RX13N

P4

GFX_RX14P

P3

GFX_RX14N

T4

GFX_RX15P

T3

GFX_RX15N

AE3

GPP_RX0P

AD4

GPP_RX0N

AE2

GPP_RX1P

AD3

GPP_RX1N

AD1

GPP_RX2P

AD2

GPP_RX2N

V5

GPP_RX3P

W6

GPP_RX3N

U5

GPP_RX4P

U6

GPP_RX4N

U8

GPP_RX5P

U7

GPP_RX5N

AA8

SB_RX0P

Y8

SB_RX0N

AA7

SB_RX1P

Y7

SB_RX1N

AA5

SB_RX2P

AA6

SB_RX2N

W5

SB_RX3P

Y5

SB_RX3N

RS880M-1-GP

RS880M-1-GP

4

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

PART 1 OF 6

PART 1 OF 6

PART 2 OF 6

PART 2 OF 6

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

A5

GFX_TX0P

B5

GFX_TX0N

A4

GFX_TX1P

B4

GFX_TX1N

C3

GFX_TX2P

B2

GFX_TX2N

D1

GFX_TX3P

D2

GFX_TX3N

E2

GFX_TX4P

E1

GFX_TX4N

F4

GFX_TX5P

F3

GFX_TX5N

F1

GFX_TX6P

F2

GFX_TX6N

H4

GFX_TX7P

H3

GFX_TX7N

H1

GFX_TX8P

H2

GFX_TX8N

J2

GFX_TX9P

J1

GFX_TX9N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4