Am186 and Am188 Family

Instruction Set Manual

February, 1997

© 1997 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products

without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for

a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD

assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the

information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

Trademarks

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am186, Am188, and E86 are trademarks of Advanced Micro Devices, Inc.

FusionE86 is a service mark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

PREFACE

INTRODUCTION AND OVERVIEW

AMD has a strong history in x86 architecture and its E86™ family meets customer

requirements of low system cost, high performanc e, quali ty vendor reput ation, quic k time

to market, and an easy upgrade strategy.

™

The 16-bit Am186

of the original 8086 and 8088 microcontrol lers, and currently includes the 80C186, 80C188,

80L186, 80L188, Am186EM, Am186EMLV, Am186ER, Am186ES, Am186ESLV,

Am188EM, Am188EMLV, Am188ER, Am188ES, and Am188ESLV. Throughout this

manual, the term

as well as future members based on the same core.

The Am186EM/ER/ES and Am188EM/ES/ER microcontrollers build on the 80C186/

80C188 microcontroller cores and offer 386-class performance while lowering system cost.

Designers can reduce the cost, size, and power consumpti on of embedded systems, while

increasing performance and functionali ty. This is achieved by integrating key system

peripherals onto the microcont roll er. These l ow- cost, high- perfo rma nce mi croco ntrol ler s for

emb ed de d s ys te ms provide a natural migra tion path for 80C186/80C188 designs t hat need

performance and cost enhancements.

and Am188™ family of microcontrollers is based on the architecture

Am186 and Am188 microcontrollers

refers to any of these microcontr ollers

PURPOSE OF THIS MANUAL

Each member of the Am186 and Am188 f amily of microcontrollers shares the standa rd 186

instruction set. This manual descri bes that inst ruction set. Detai ls on technica l featur es of

family members can be found in the user’s manual for that specific device. Additional

information is available in the form of data sheets, application notes, and other

documentation provided with software products and hardware-development tools.

INTENDED AUDIENCE

This manual is intended for computer hardware and software engineers and system

architects who are designing or are consideri ng de signing systems based on the Am186

and Am188 family of microcontrollers.

MANUAL OVERVIEW

The information in this manual is organized into 4 chapters and 1 appendix.

n Chapter 1 provides a programming overview of the Am186 and Am188

microcontrollers, including the register set, instruction set, memory organization and

address generation, I/O space, segments, data types, and addressing modes.

n Chapter 2 offers an instruction set overview, detailing the format of the instructions.

n Chapter 3 contains an instruction set l isting, both by functional type and in alphabeti cal

order.

n Chapter 4 describes in de tail each instruction in t he Am186 and Am188 microcontrollers

instruction set.

n Appendix A provides an instruction set summary table, as well as a guide to the

instruction set by hex and binary opcode.

Introduction and Overview

iii

AMD DOCUMENTATION

E86 Family

ORDER NO. DOCUMENT TITLE

19168 Am186EM and Am188EM Microc ontrol lers Da ta She et

Hardware document atio n for th e Am186E M, Am186EMLV , Am188 EM, and

Am188EMLV microcont rolle rs: pi n descr iption s, fun ctional desc ripti ons, abs olute maximum rat ings, oper ating rang es, swi tchin g char acter isti cs and wa veforms, connecti on diag rams a nd pinou ts, an d pack age physi cal dime nsions .

20732 Am186ER and Am188ER Microc ontr oller s Data Sh eet

Hardware docu mentation for the Am186ER and Am188E R microcontrollers: pin

descriptions, functional descripti ons, absolute maximum rat ings, operating ranges, switchin g characterist ics and waveforms, connection diagr ams and pinouts,

and package physi cal di mensio ns.

20002 Am186ES and Am188ES Mic rocontr olle rs Data Sh eet

Hardware document atio n for th e Am186E S, Am186ESL V, Am188ES , and

Am188ESLV microcontrollers: pin descriptions, functional descriptions, absolute

maximum ratings, operating ranges, switching characteristics and waveforms,

connection diagr ams an d pinout s, and package p hysic al dime nsions .

20071 E86 Family Suppor t Too ls Brie f

Lists avail able E86 family sof tware and hard ware developme nt tools, as well as

contact information for suppliers.

SM

19255 FusionE86

Provides info rmat ion on t ool s that s peed a n E86 f amily e mbedde d produc t to

market. Include s products fr om expert suppl iers of emb edded develo pment solutions.

Catalog

21058 FusionE86 Develop ment To ols Refe renc e CD

Provides a sing le-so urce multim edia to ol for cus tomer eva luatio n of AMD pr oducts as well as Fusion partner tools and technologies that support the E86 family

of microcontr ollers an d microp rocessor s. Techn ical do cumentatio n for the E86

family is included on the CD in PDF format.

To order literature, contact the nearest AMD sales of f i c e or c a l l 8 00- 2 22- 9 3 2 3 ( in t h e U. S .

and Canada) or dir ect dial from any loca tion 51 2-60 2-5651 . Li terat ure is also avail able i n

pos ts cr ip t an d P DF fo rm at s on th e AMD w eb si te . To access the AMD home page, go to http:/

/www.amd.com.

iv

Introduction and Overview

TABLE OF CONTENTS

PREFACE INTRODUCTION AND OVERVIEW III

PURPOSE OF THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . III

INTENDED AUDIENCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . III

MANUAL OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . III

AMD DOCUMENTATIONiv

E86 Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iv

CHAPTER 1 PROGRAMMING

1.1 REGISTER SET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.1.1 Processor Status Flags Register . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2 INSTRUCTION SET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.3 MEMORY ORGANIZATION AND ADDRESS GENERATION. . . . . . . . . .1-3

1.4 I/O SPACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

1.5 SEGMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

1.6 DATA TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

1.7 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-7

Register and Immediate Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Memory Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

CHAPTER 2 INSTRUCTION SET OVERVIEW

2.1 OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.2 INSTRUCTION FORMAT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.2.1 Instruction Prefixes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.2.2 Segment Override Prefix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.2.3 Opcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.2.4 Operand Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.2.5 Displacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.6 Immediate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.3 NOTATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.4 USING THIS manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.4.1 Mnemonics and Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.4.2 Forms of the Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.4.3 What It Does . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.4.4 Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.4.5 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.4.6 Operation It Performs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.7 Flag Settings After Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

2.4.8 Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.9 Tips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.4.10 Related Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

CHAPTER 3 INSTRUCTION SET LISTING

3.1 INSTRUCTION SET BY TYPE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

3.1.1 Address Calculation and Translation . . . . . . . . . . . . . . . . . . . . . .3-1

3.1.2 Binary Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

Table of Contents

v

3.1.4 Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

3.1.5 Control Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.6 Data Movement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-5

3.1.7 Decimal Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.1.8 Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.1.9 Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.1.10 Logical Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.1.11 Processor Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.1.12 String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.2 INSTRUCTION SET in alphabetical order . . . . . . . . . . . . . . . . . . . . . . . .3-11

CHAPTER 4 INSTRUCTION SET

4.1 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

AAA ASCII Adjust AL After Addition..................................................... 4-2

AAD ASCII Adjust AX Before Division..................................................4-4

AAM ASCII Adjust AL After Multiplication.............................................4-6

AAS ASCII Adjust AL After Subtraction................................................4-8

ADC Add Numbers with Carry............................................................4-10

ADD Add Numbers ............................................................................ 4-14

AND Logical AND ............................................................................... 4-17

BOUND Check Array Index Against Bounds ........................................... 4-19

CALL Call Procedure ........................................................................... 4-21

CBW Convert Byte Integer to Word..................................................... 4-24

CLC Clear Carry Flag......................................................................... 4-26

CLD Clear Direction Flag ................................................................... 4-29

CLI Clear Interrupt-Enable Flag........................................................4-31

CMC Complement Carry Flag.............................................................4-33

CMP Compare Components............................................................... 4-34

CMPS Compare String Components..................................................... 4-36

CWD Convert Word Integer to Doubleword......................................... 4-40

DAA Decimal Adjust AL After Addition ...............................................4-42

DAS Decimal Adjust AL After Subtraction.......................................... 4-45

DEC Decreme nt Numbe r by One ....................... ...... ....... ...... ....... ...... 4-48

DIV Divide Unsigned Numbers ......................................................... 4-50

ENTER Enter High-Level Procedure.......................................................4-53

ESC Escape....................................................................................... 4-56

HLT Halt............................................................................................. 4-57

IDIV Divide Integers ........................................................................... 4-60

IMUL Multiply Integers......................................................................... 4-63

IN Input Component from Port........................................................ 4-67

INC Increment Number by One ...... ...... ....... ...... ...... ....... ...... ....... ...... 4-69

INS Input String Component from Port ............................................. 4-71

INT Generate Interrupt...................................................................... 4-73

IRET Interrupt Return..........................................................................4-76

JA Jump If Above .................................................. .......................... 4-78

JAE Jump If Above or Equal.............................................................. 4-80

JB Jump If Below...... ....... ...... ....... ...... ....... ...... ...... ....... ...... .............4-82

JBE Jump If Below or Equal .............................................................. 4-84

JC Jump If Carry.............................................. ...... ....... ...... ....... ...... 4-86

JCXZ Jump If CX Register Is Zero....................................................... 4-87

JE Jump If Equal ............................................. ...... ....... ...... ....... ...... 4-89

vi

Table of Contents

JG Jump If Greater ................................................ .......................... 4-91

JGE Jump If Greate r or Equal.................................. ....... ...... ....... ...... 4-93

JL Jump If Less........ ....... ...... ....... ...................................... ....... ...... 4-95

JLE Jump If Less or Equal ................................................................4-97

JMP Jump Unconditionally....... ....... ...... ....... ...... ...... ....... ...... ....... ...... 4-99

JNA Jump If Not Above....................................................................4-102

JNAE Jump If Not Above or Equal .....................................................4-103

JNB Jump If Not Below.................................................................... 4-104

JNBE Jump If Not Below or Equal......................................................4-105

JNC Jump If Not Carry.....................................................................4-106

JNE Jump If Not Equal.....................................................................4-107

JNG Jump If Not Greater.................................................................. 4-109

JNGE Jump If Not Greater or Equal...................................................4-110

JNL Jump If Not Less ...................................................................... 4-111

JNLE Jump If Not Less or Equal........................................................ 4-112

JNO Jump If Not Overflow................................................................ 4-113

JNP Jump If Not Parity.....................................................................4-115

JNS Jump If Not Sign.......................................................................4-116

JNZ Jump If Not Zero ...................................................................... 4-118

JO Jump If Overflow .............................................. ........................ 4-119

JP Jump If Parity ................................................... ........................ 4-121

JPE Jump If Parity Even..................................................................4-122

JPO Jump If Parity Odd ................................................................... 4-124

JS Jump If Sign.. ...... ....... ...... ....... ...... ....................................... .... 4-126

JZ Ju mp If Zero............... ...... ....................................... ...... ....... .... 4-128

LAHF Load AH with Flags.................................................................. 4-129

LDS Load DS with Segment and Register with Offset..................... 4-131

LEA Load Effective Address ........................................................... 4-133

LEAVE Leave High-Level Procedure............................ .................... .... 4-135

LES Load ES with Segment a nd Register with Of fset.......................... 4-138

LOCK Lock the Bus ............................................................................ 4-140

LODS Load String Component...........................................................4-141

LOOP Loop While CX Register Is Not Zero....................... ...... ....... .... 4-146

LOOPE Loop If Equal............................................................................4-148

LOOPNE Loop If Not Equal ..................................................................... 4-150

LOOPZ Loop If Zero.............................................................................. 4-152

MOV Move Comp one nt................................. ...... ...... ....... ...... ....... .... 4-153

MOVS Move String Component .................................. ....... ...... ....... .... 4-156

MUL Multiply Unsigned Numbers ..................................................... 4-160

NEG Two’s Complement Negation...................................................4-163

NOP No Operation............................................................................ 4-165

NOT One’s Complement Negation...................................................4-167

OR Logical Inclusive OR ................................................................ 4-169

OUT Output Component to Port ....................................................... 4-171

OUTS Output String Component to Port............................................. 4-173

POP Pop Component from Stack.....................................................4-175

POPA Pop All 16-Bit General Registers from Stack................................ 4-178

POPF Pop Flags from Stack............................................................... 4-180

PUSH Push Component onto Stack ................................................... 4-181

Table of Contents

vii

PUSHA Push All 16-Bit General Registers onto Stack.......................... 4-184

PUSHF Push Flags onto Stack .............................................................4-186

RCL Rotate through Carry Left......................................................... 4-187

RCR Rotate through Carry Right ...................................................... 4-189

REP Repeat......................................................................................4-191

REPE Repeat While Equal ................................................................. 4-193

REPNE Repeat While Not Equal........................................................... 4-197

REPZ Repeat While Zero ................................................................... 4-201

RET Return from Procedure............................................................. 4-202

ROL Rotate Left................................................................................4-205

ROR Rotate Right .............................................................................4-207

SAHF Store AH in Flags..................................................................... 4-209

SAL Shift Arithmetic Left................. ...... ....... ...... ...... ....... ...... ....... .... 4-211

SAR Shift Arithmetic Right............................ ...... ...... ....... ...... ....... .... 4-214

SBB Subtract Numbers with Borrow ................................................4-216

SCAS Scan String for Component......................................................4-219

SHL Shift Left........................................ ....... ...... ...... ....... ...... ....... .... 4-224

SHR Shift Righ t......................... ....... ...... ....... ...... .............................. 4-225

STC Set Carry Flag..........................................................................4-228

STD Set Direction Flag.....................................................................4-231

STI Set Interrupt-Enable Flag.........................................................4-235

STOS Store String Component........................................................... 4-237

SUB Subtract Numbers....................................................................4-240

TEST Logical Compare...................................................................... 4-243

WAIT Wait for Coprocessor ............................................................... 4-245

XCHG Exchange Components............................................................ 4-246

XLAT Translate Table Index to Component....................................... 4-248

XOR Logical Exclusive OR ...............................................................4-251

APPENDIX A INSTRUCTION SET SUMMARY

INDEX

viii

Table of Contents

LIST OF FIGURES

Figure 1-1 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Figure 1-2 Processor Status Flags Register (FLAGS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-2

Figure 1-3 Physical-Address Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 1-4 Memory and i/O Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

Figure 1-5 Supported Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Figure 2-1 Instruction Mnemonic and Name Sample . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-2 Instruction Forms Table Sample . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

LIST OF TABLES

Table 1-1 Segment Register Selection Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-2 Memory Addressing Mode Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Table 2-1 mod field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

Table 2-2 aux field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 2-3 r/m field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 3-4 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Table of Contents

ix

x

Table of Contents

CHAPTER

PROGRAMMING

1

All members of the Am186 and Am188 family of microcontrollers contain the same basic

set of registers, in structions, and addressing modes, and are compatible with the or iginal

industry-standard 186/188 parts.

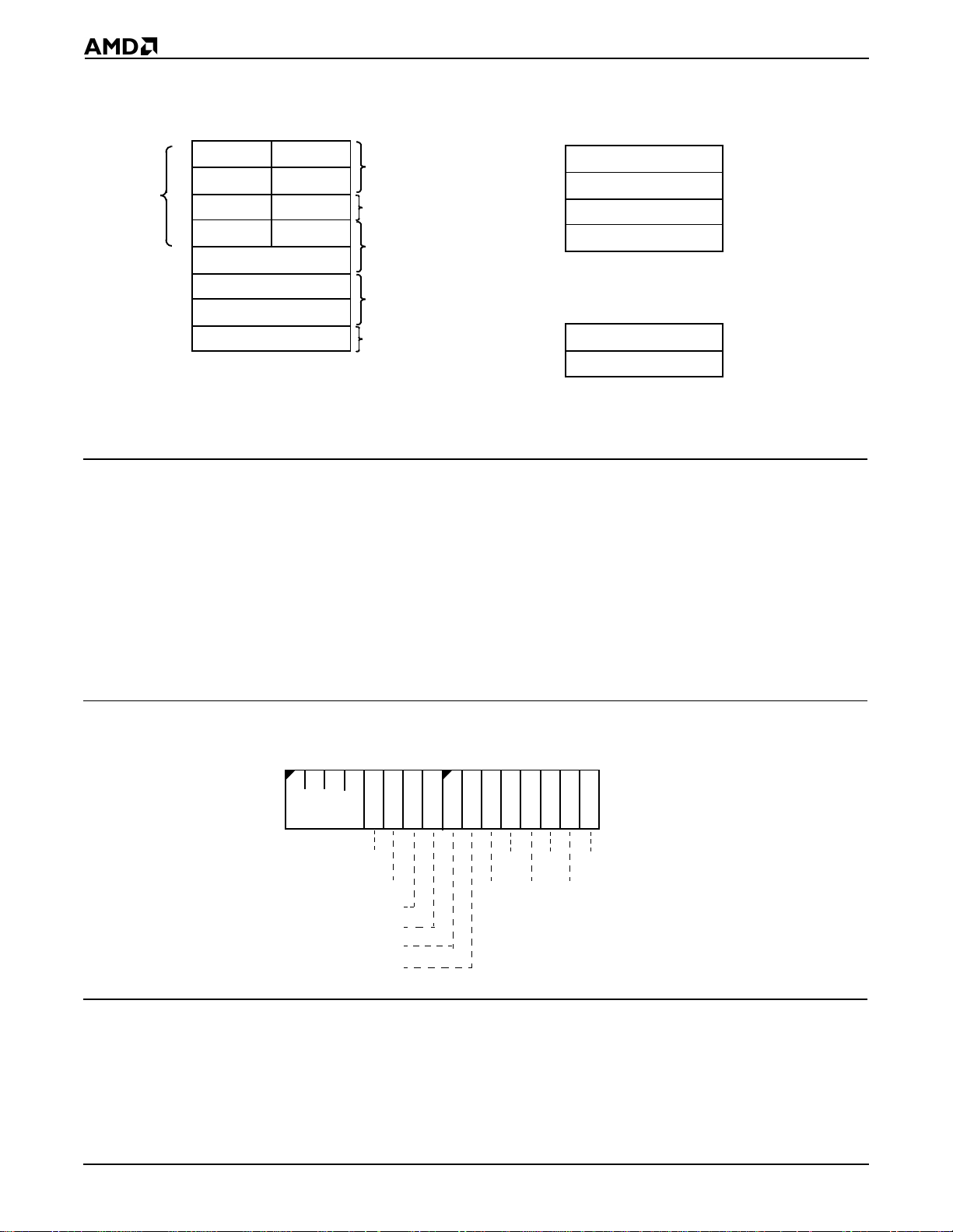

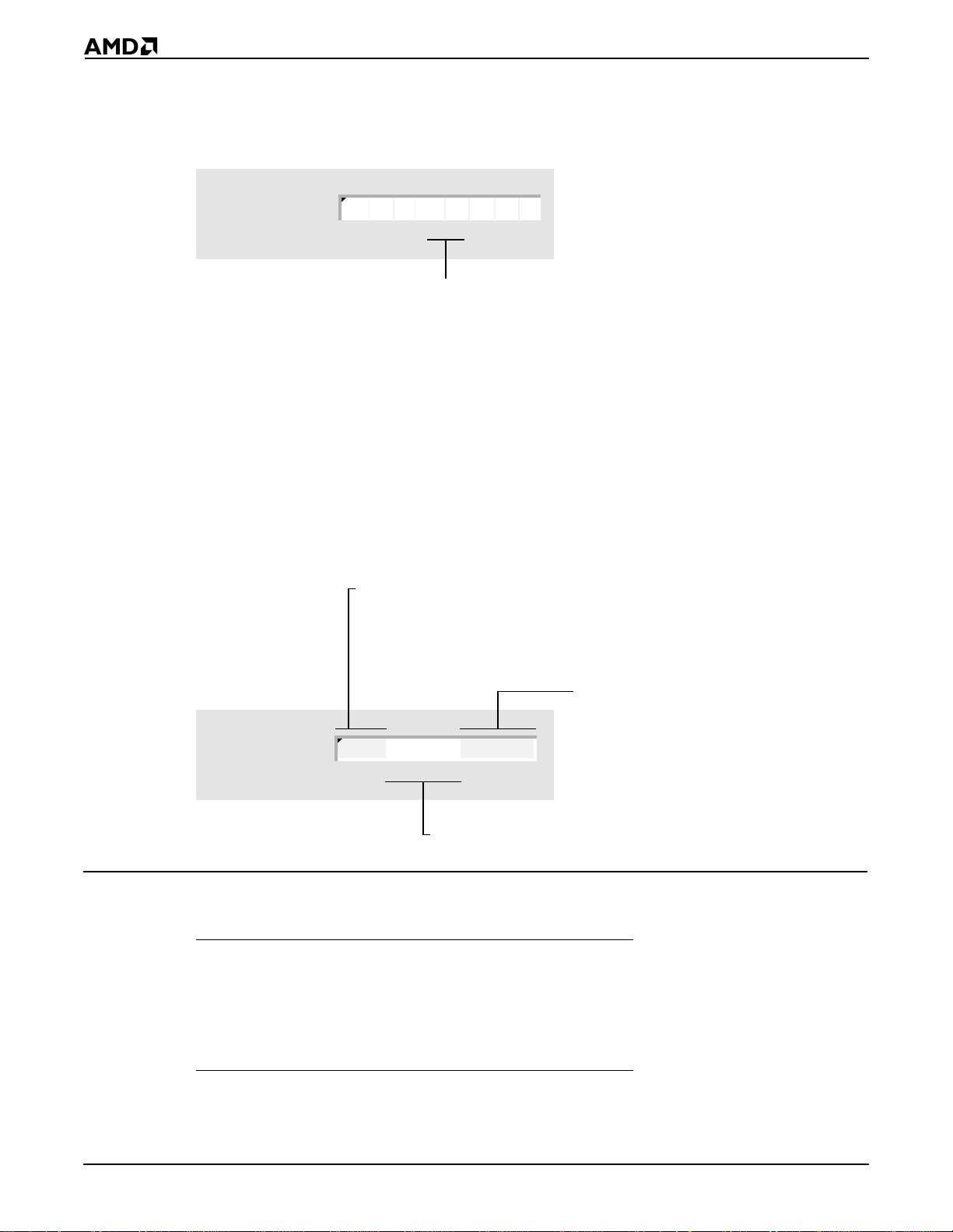

1.1 REGISTER SET

The base architecture for Am186 and Am188 microcontroller s has 14 registers (see Fi gure

1-1), which are controlled by the instructions detailed in this manual. These registers are

grouped into the following categories.

n General Registers—Eight 16-bit general purpose r egisters ca n be used for arit hmetic

and logical operands. Four of these ( AX, BX, CX, and DX) can be used as 16-bit registers

or split into pairs of se parate 8-bit register s (AH, AL, BH, BL, CH, CL, DH, an d DL). The

Destination Index (DI) and Source Index (SI) general-purpose registers are used for

data movement and string instructions. The Base Point er (BP) and St ack Pointer (SP)

general-purpose register s are used for the stack segment and point to the bottom and

top of the stack, respectively.

– Base and Index Registers—Four of the general-purpose registers (BP, BX, DI, and

SI) can also be used to determine offset addresses of operands in memory. These

registers can contain base addresses or indexes to part icular locations within a

segment. The addressin g mode selects the specific registers for operand and address

calculations.

– Stack Pointer Register—All stack operations (POP, POPA, POPF, PUSH, PUSHA,

PUSHF) utilize the stack pointer. The Stack Pointer (SP) register is always offset

from the Stack Segment (SS) register, and no segment override i s all owed.

n Segment Registers—Four 16-bit special-purpose registers (CS, DS, ES, and SS)

select, at any given time, the segments of memory that are immediately addressable

for code (CS), data (DS and ES), and stack (SS) memory.

n Status and Control Registers—Two 16-bi t special-purpose register s record or alter certain

aspects of the pr ocess or st ate—the Inst ruct ion Pointe r (IP) regis ter co ntai ns the o ffset

address of the ne xt s equenti al instru cti on to be ex ecut ed and th e Proc esso r Stat us Flags

(FLAGS) register contains status and control flag bits (see Figure 1-2).

Note that all members of the Am186 and Am188 family of microcontr ollers have additional

peripheral registers, which are exte rnal to the processor. These peripheral registers are

not directly ac cessible by the i nstruction set. However, because the processor treats t hese

peripheral registers like memory, instructio ns that have operands that access memory can

also access peripheral r egiste rs. The above proc essor re gis ters, as well as the addi tional

peripheral registers, are described in the user’s manual for each specific part.

Programming

1-1

Figure 1-1 Register Set

16-Bit

Register

Name

Byte

Addressable

(8-Bit

Register

Names

Shown)

7 0 7 0

AX

DX

CX

BX

BP

SI

DI

SP

AH

DH

CH

BH

base pointer

source index

destination index

15 0

General

Registers

AL

DL

CL

BL

Special

Register

Functions

Multiply/Divide

I/O Instructions

Loop/Shift/Repeat/Count

Base Registers

Index Registers

Stack Pointer

Register

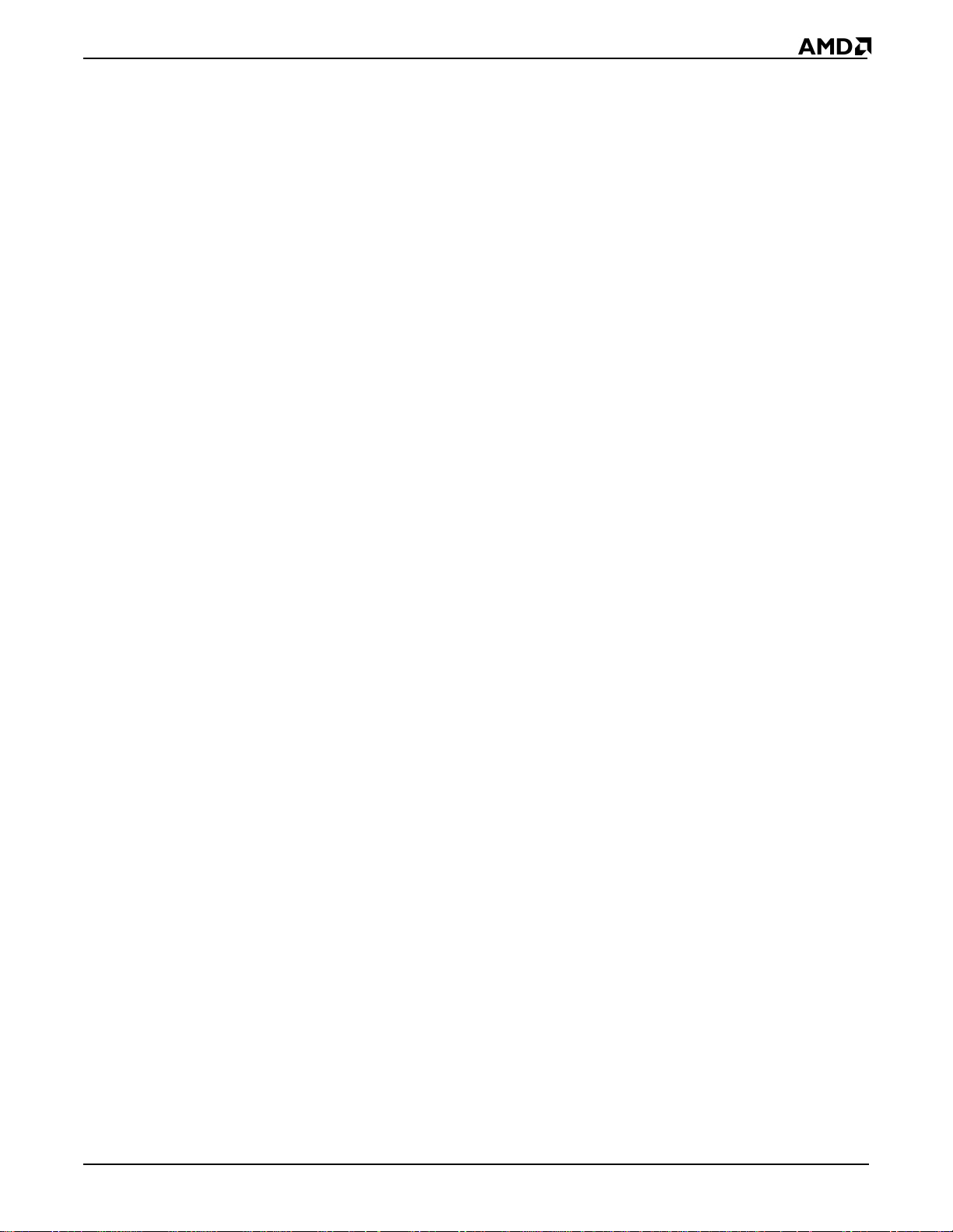

1.1.1 Processor Status Flags Register

The 16-bit processor stat us flags regi ster (see Figure 1- 2) records specific characte ristic s

of the result of logical and arithmeti c instructions (bits 0, 2, 4 , 6, 7, and 11) and controls the

operation of the microcontroller within a given operating mode (bits 8, 9, and 10).

16-Bit

Name

CS

DS

SS

ES

FLAGS

15 0

Segment Registers

15 0

IP

Status and Control

Registers

Code Segment

Data Segment

Stack Segment

Extra Segment

Processor Status Flags

Instruction Pointer

After an instruction is executed, the value of a flag may be set (to 1), cleared/reset (to 0),

unchanged, or undefined. The term

undefined

of the instruc tion is not preserved, and the value of the flag after the instruction is executed canno t

be predicted. The docu mentat ion for ea ch i nstru ctio n ind ica tes ho w each flag bit i s aff ect ed by

that instruction.

Figure 1-2 Processor Status Flags Register (FLAG S)

15

Reserved

OF

DF

IF

TF

SF

ZF

70

AF

Res

Bits 15–12—Reserved.

means that the fla g value prior to the execu tion

PF

CF

Res

Res

1-2

Bit 11: Overflow Flag (OF)—Set if the signed result cannot be expressed within the number

of bits in the destination operand, cleared o ther wise.

Programming

Bit 10: Direction Flag (DF)—Causes string instructions to auto decrement the appropriate

index registers when set. Clearing DF causes auto-increment. See the CLD and STD

instructions, respectively, for how to clear and set the Direction Flag.

Bit 9: Interrupt-Enable Flag (IF)—When set, enables maskable interrupts to cause the

CPU to transfer control to a locati on sp ecifi ed by an i nter rupt v ector. See t he CLI and STI

instructions, respectively, for how to clear and set the Interrupt-Enable Flag.

Bit 8: Trace Flag (TF)—When set, a trace interrupt occurs after instructions execute. TF

is cleared by the t race interr upt after t he processor st atus flags are pushed onto t he stack.

The trace service routine can continue tracing by popping the flags back with an IRET

instruction.

Bit 7: Sign Flag (SF)—Set equal to high-order bit of result (set to 0 if 0 or positive, 1 if

negative).

Bit 6: Zero Flag (ZF)—Set if result is 0; clear ed otherwise.

Bit 5: Reserved

Bit 4: Auxiliary Carry (AF)—Set on carry f rom or borrow to the low-or der 4 bits of the AL

general-purpose register; cleared otherwise.

Bit 3: Reserved

Bit 2: Parity Flag (PF)—Set if low-order 8 bi ts of resul t contain an ev en number of 1 bits;

cleared otherwise.

Bit 1: Reserved

Bit 0: Carry Flag (CF)—Set on high- order bit c arry or borr ow; cleared ot herwise . See the

CLC, CMC, and STC instructions, respectively, f or how to clear, toggl e, and set the Carry

Flag. You can use CF to indicate the outcome of a procedure, such as when searching a

string for a charact er. For inst ance, if t he character i s found, you c an use STC to set CF to

1; if the character is not found, you can use CLC to clear CF to 0. Then, subsequent

instructions that do not aff ect CF c an use its val ue to det ermine t he a ppropri ate course of

action.

1.2 INSTRUCTION SET

Each member of the Am186 and Am188 f amily of microcontrollers shares the standa rd 186

instruction set. An instruction can reference from zero to several operands. An operand

can reside in a register , in the inst ruction itself, or in memory. Specif ic operand addressi ng

modes are discussed on page 1-7.

Chapter 2

instructions.

in both functional and alphabetical order.

provides an overview of the instruction set, describing the format of the

Chapter 3

lists all the instruc tions for the Am186 and Am188 microcontr ollers

Chapter 4

details each ins tru c tion.

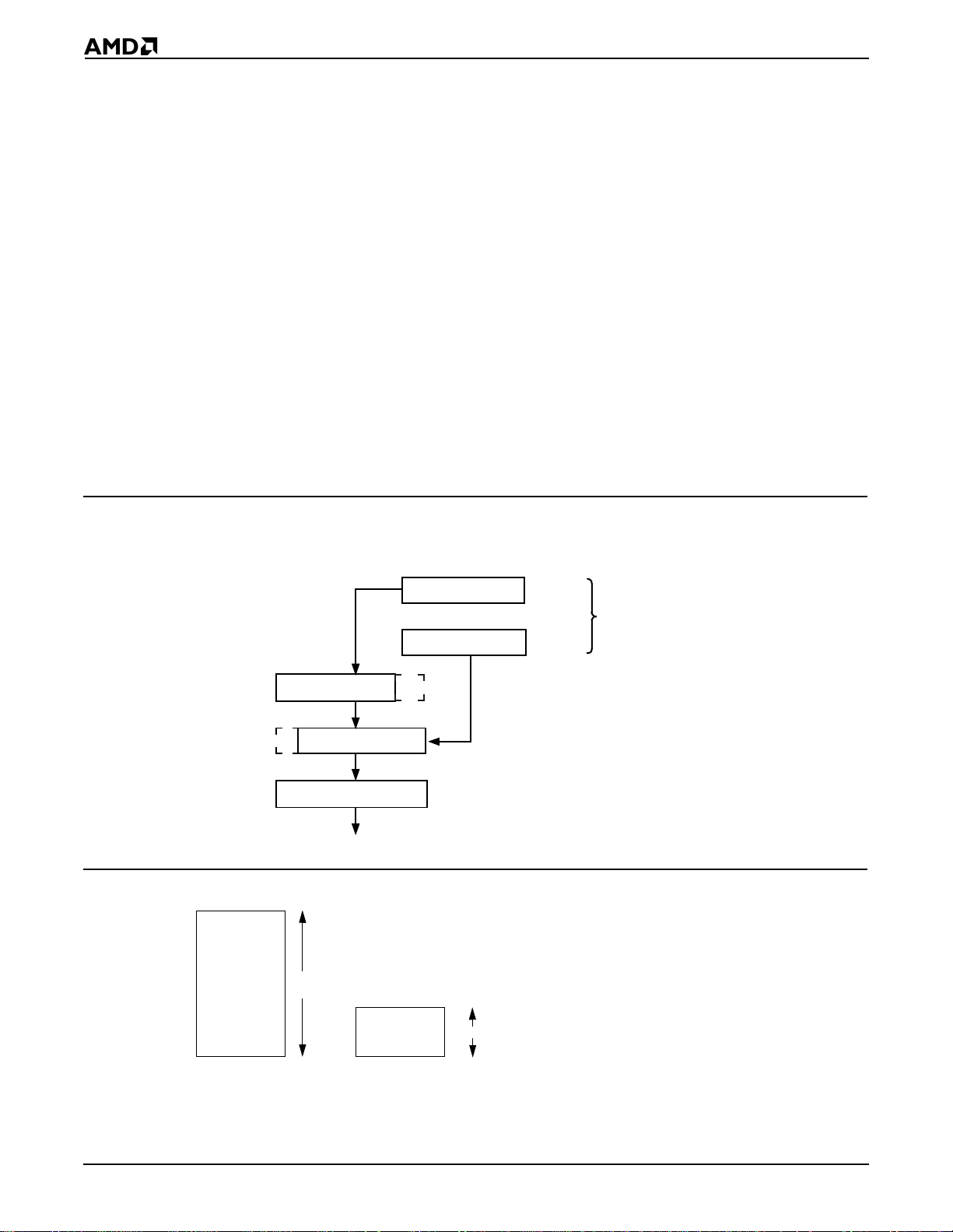

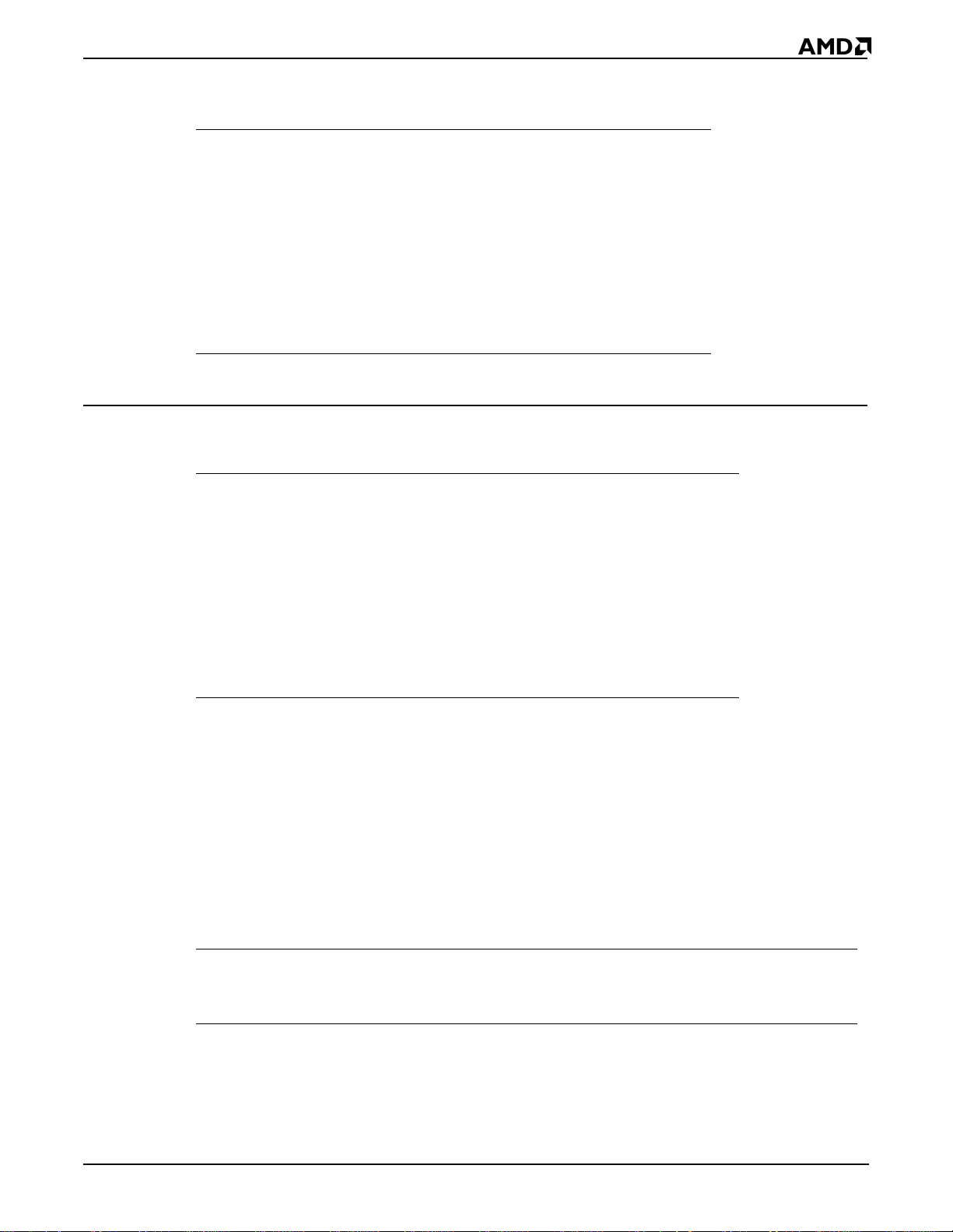

1.3 MEMORY ORGANIZATION AND ADDRESS GENERATION

The Am186 and Am188 microcontrollers organize memory in sets of segments. Memory

is addressed using a two-component address that consists of a 16-bit segment value and

a 16-bit offset. Each segment is a linear contiguous sequence of 64K (2

memory in the processor’s address space. The offset is the number of bytes from the

beginning of the segment (the segment address) to t he data or instruction which is being

accessed.

16

) 8-bit bytes of

The processor forms the physical address of the target location by taking the segment

address, shifting it to the left 4 bits (multi plying by 16), and adding this to the 16-b it offset.

Programming

1-3

The result is a 20-bit address of the target data or instruction. This al low s f or a 1- Mby te phys ica l

address size.

For example, if the segment register is loaded with 12A4h and the offset i s 0022h, the

resultant address is 12A62h (see Figure 1-3). To find the result:

1. The segment register contains 12A4h.

2. The segment register is shifted 4 places and is now 12A40h.

3. The offset is 0022h.

4. The shifted segment address (12A40h) is added to the offset (00022h) to get 12A62h.

5. This address is placed on the address bus pins of the controller.

All instructions that addr ess operands in memory must s pecify (implicitly or expl icitly) a 16-

bit segment value and a 16-bi t offset value. The 1 6-bit segmen t values are contain ed in one

of four internal segment registers (CS, DS, ES, and SS). See "Addressing Modes” on page

1-7 for more information on calculating the segment and offset values. See "Segments" on

page 1-5 for more information on the CS, DS, ES, and SS registers.

In addition to memory spac e, all Am186 an d Am188 microcontrol lers provi de 64K of I/O space

(see Figure 1-4). The I/O space is described on page 1-5.

Figure 1-3 Physical-Address Generation

Shift Left

4 Bits

1 2 A 4 0

19 0

0 0 0 2 2

15 0

1 2 A 6 2

19 0

To Memory

Figure 1-4 Memory and i/O Space

Memory

Space

1M

1 2 A 4

15 0

0 0 2 2

15 0

Physical Address

Segment

Base

Logical Address

Offset

1-4

I/O

Space

64K

Programming

1.4 I/O SPACE

The I/O space consists of 64K 8-bit or 32K 16-bit port s. The IN and OUT instructions address

the I/O space with either an 8-bit port addr ess specified in the instruction, or a 16-bit port

address in the DX register. 8-bit port addresses are zero-extended so that A15–A8 are

Low. I/O port addresses 00F8h through 00FFh are reserved. The Am186 and Am188

microcontrollers provide spe cific instructions for addressing I/O spac e.

1.5 SEGMENTS

The Am186 and Am188 microcontrollers use four segment registers:

1. Data Segment (DS): The processor assumes that all accesses to the program’s

variables are from the 64K space pointed to by the DS register. The data segment holds

data, operands, etc.

2. Code Segment (CS): This 64K space is the def ault location for all instructions. All code

must be executed from the code segment.

3. Stack Segment (SS): The processor uses the SS register to perform operations that

involve the stack, such as pushes and pops. The st ack segment i s used for t emporar y

space.

4. Extra Segment (ES): Usually this segment is used for l a rge string operations and for

large data structures. Certain str ing i n structions assume the extra segment as the

segment portion of the address. The extra segment is also used (by using segment

override) as a spare data segment.

When a segment register is not specified for a da ta movement instruction, it’s assumed to

be a data segment. An instruction prefix can be used to override the segment regist er (see

"Segment Override Prefix" on page 2-2).For speed and compact instruction encoding, the

segment register used for phy sical-address generation is impli ed by the addre ssing mode

used (see Table 1-1).

Table 1-1 Segment Register Selection Rules

Memory Reference Ne eded Segment Register Used Implicit Segment Selection Rule

Local Data Data (DS) All data references

Instructions Code (CS) Instructions (including immedi ate data)

Stack Stack (SS) All stack pushes and pops

Any memory references that use the BP registe r

External Data (Global) Extra (ES) All string instruction references that use th e DI register as an index

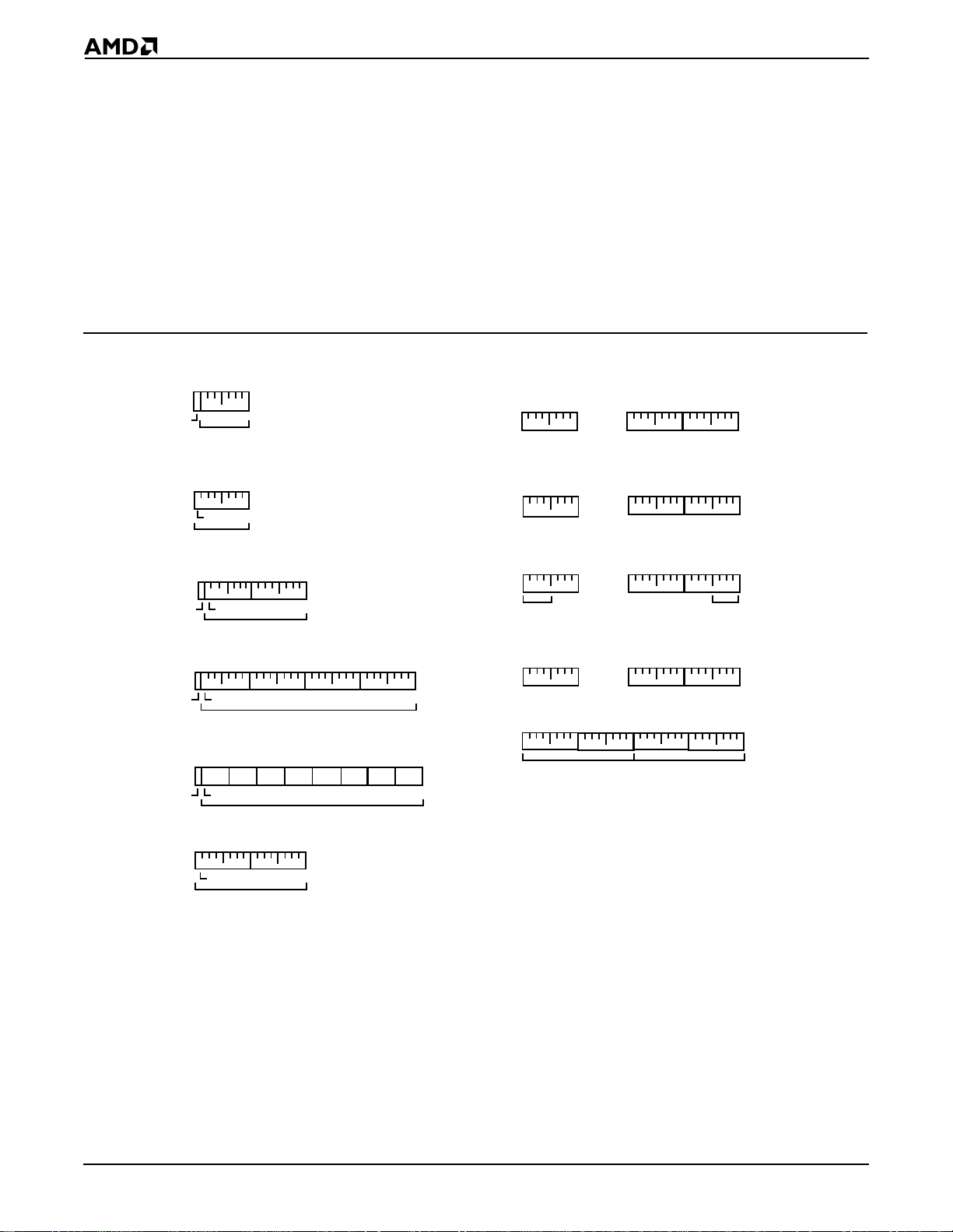

1.6 DATA TYPES

The Am186 and Am188 microcontrollers directly support the following data types:

n Integer—A signed binary numeric value contai ned in an 8-bit byte or a 16-bit word. All

operations assume a two’s complement representation.

n Ordinal—An unsigned binary numeric va lue contained in an 8-bit byte or a 16-bit word.

n Double Word—A signed binary numeric value contained in two sequential 16-bit

addresses, or in a DX::AX register pair.

n Quad Word—A signed binary numeric value contained in four sequential 16-bit

addresses.

n BCD—An unpacked byte representation of the decimal digits 0–9.

Programming

1-5

n ASCII—A byte representation of alp hanumeric and c ontrol charact ers using the ASCII

standard of character representation.

n Packed BCD—A packed byte representation of two decimal digits (0–9). One digit is

stored in each nibble (4 bits) of the byte.

n String—A contiguous sequence of by tes or words. A string can contain fr om 1 byte up

to 64 Kbyte.

n Pointer—A 16-bit or 32-bit quantit y, composed of a 16-bit of fset component or a 16-bit

segment base component plus a 16-bit offset component.

In general, individual data elements must fit within defined segment limits. Figure 1-5

graphically represents the data types supported by the Am186 and Am188 microcont rollers.

Figure 1-5 Supported Data Types

Signed

Byte

Sign Bit

Unsigned

Byte

Signed

Word

Sign Bit

Signed

Double

Word

Sign Bit

Signed

Quad

Word

Sign Bit

Unsigned

Word

7 0

Magnitude

7 0

MSB

Magnitude

+1 0

1514 8 7 0

MSB

Magnitude

+3 +2 +1 0

31 1615 0

MSB

Magnitude

63 48 47 32 31 16 15 0

+3 +2 +1+6 +5 +4 +0+7

MSB

Magnitude

+1 0

015

MSB

Magnitude

Binary

Coded

Decimal

(BCD)

ASCII

Packed

BCD

String

Pointer

+N

7 0

+1

7 0 7 0

. . .

BCD

Digit N

+N

7 0 7 0 7 0

BCD

Digit 1

+1 0

BCD

Digit 0

. . .

ASCII

Character

7 0

N

+N +1 0

ASCII

Character

7 0 7 0

Character

1

. . .

Most

Significant Digit

+N

7

0

Significant Digit

+1 0

7 0

7 0

. . .

Byte/WordN

+3 +2 +1 0

Segment Base

Byte/Word1 Byte/Word0

Offset

0

ASCII

0

Least

1-6

Programming

1.7 ADDRESSING MODES

The Am186 and Am188 microcontrollers use eight categories of addressing modes to

specify operands. Two addressing modes are provided for instructions that operate on

register or immediate operands; six modes are provided to specify the location of an

operand in a memory segment.

Register and Immediate Operands

1. Register Operand Mode—The operand is located in one of the 8- or 16-bit registers.

2. Immediate Operand Mode—The operand is included in the instruction.

Memory Operands

A memory-operand address consists of two 16-bit components: a segment value and an

offset. The segment value is supplied by a 16-bit segme nt register either i mplicitly chosen

by the addressing mode (described below) or expli citly chosen by a segment override prefix

(see "Segment Override Prefix" on page 2-2). The offset, also called the effective address,

is calculated by summing any combination of the following three address elements:

n Displacement—an 8-bit or 16- bit i mmediat e valu e cont aine d in th e ins truct ion

n Base—contents of either the BX or BP base regi ster s

n Index—contents of either th e SI or DI index registe rs

Any carry from the 16-bit addition is ignored. Eight-bit displacements ar e sign-extended to

16-bit values.

Combinations of the above three address elements define the following six memory

addressing modes (see Table 1-2 for examples).

1. Direct Mode—The operand off set i s contain ed in the ins tructi on as an 8 - or 16- bit

displacement element.

2. Register Indirect Mode—The op eran d offset is in o ne of the BP, BX, DI, or SI re giste rs.

3. Based Mode—The operand offset is the sum of an 8- or 16-bit displacement and the contents

of a base regist er (BP or BX).

4. Indexed Mode—The operand offset is th e sum of an 8 - or 16- bit dis placeme nt an d the

contents of an index register (DI or SI).

5. Based Indexed Mode—The operand o ffset is the su m of the co nten ts of a b ase regis ter

(BP or BX) and an index register (DI or SI).

6. Based Indexed Mode with Displacement—The op erand of fset i s the sum of a base

register’s conten ts, an index regis ter’ s conte nts, an d an 8- bit or 16-b it disp lac ement .

Table 1-2 Memory Addressing Mode Examples

Addressing Mode Example

Direct mov ax, ds:4

Register Indirect mov ax, [si]

Based mov ax, [bx]4

Indexed mov ax, [si]4

Based Indexed mov ax, [si][bx]

Based Indexed with Displacement mov ax, [si][bx]4

Programming

1-7

1-8

Programming

CHAPTER

INSTRUCTION SET OVERVIEW

2

2.1 OVERVIEW

The instruction set used by the Am186 and Am188 family of microcontrollers is identical to

the original 8086 and 8088 instruction set, with the addition of seven instructions (BOUND,

ENTER, INS, LEAVE, OUTS, POPA, and PUSHA), and the enhancement of nine

instructions (immediate operands were added to IMUL, PUSH, RCL, RCR, ROL, ROR,

SAL/SHL, SAR, and SHR). In addition, three valid instructions are not suppo rt ed with the

necessary processor pinout (ESC, LOCK and WAIT). All of these instr uctions are mar ked

as such in their description.

2.2 INSTRUCTION FORMAT

When assembling code, an assembler replaces each instructi on statement with its

machine-language equivalent. In mach ine langu age, all i nstructi ons conform to one basic

format. However, the length of an instruction in machi ne language varies depending on the

operands used in the instruction and the operation that the instruction performs.

An instruction can reference from zero to several operands. An operand can reside in a

register, in the instruction itself, or in memory.

The Am186 and Am188 microcontrolle rs use the foll owing instruction f ormat. The shortest

instructions consist of only a single opcode byte.

Instruction Prefixes

Segment Override Prefix

Opcode

Operand Address

Displacement

Immediate

2.2.1 Instruction Pref ix es

The REP, REPE, REPZ, REPNE and REPNZ prefixes can be used to repeatedly execute

a single string instruction.

The LOCK prefix may be combined with the instruction and segment over ride prefixes, and

causes the processor to assert its bus LOCK signal while the instruction that follows

executes.

Instruction Set Overview

2-1

2.2.2 Segment Override Prefix

To override the default segment register, place the following byte in fro nt of the instruction,

where RR determines which register is used. Only one segment override prefix can be

used per instruction.

Segment Override

Prefix

0 0 1 1 1 0

2.2.3 Opcode

This specifies the machine- language opcode for an in struction. The format for the opcodes

is described on page 2-5. Although most instructions use only one opcode byte, the AAD

(D5 0A hex) and AAM (D4 0A hex) instructions use two opcodes.

2.2.4 Operand Address

The following illustration shows the structure of the operand address byte. The operand

address byte controls the addressing for an instruction.

Along with

interpreted as a register or the address of a memory operand. For a memory

operand, the Modifi er field also indicates whether t he operand is addressed direc tly

or indirectly. For indi rectly addressed memory operands, the Modifier field specifies

the number of bytes of d isplacem ent that ap pear in the ins truction. Se e Table 2-1

for

R R

00 = ES Register

01 = CS Register

10 = SS Register

11 = DS Register

r/m

mod

values.

01234567

, the Modifier field d etermines w hether the Regi ster/Memory field is

Operand Address mod aux r/m

Table 2-1 mod field

mod Description

11

00 DISP = 0, disp-low and disp-high are absent

01 DISP = disp-low sign-extended to 16-bits, disp-high

10 DISP = disp-high: disp-low

r/m

is treated as a

is absent

mod

Along with

specifies a genera l register or the address of a

memory operand. See Table 2-3 for

01234567

The Auxiliary field specifies an opcode extension or a register

that is used as a second operand. See Table 2-2 for

reg

field

, the Register/Memory field

aux

r/m

values.

values

2-2

Instruction Set Overview

Table 2-2 aux field

aux If mod=11 and w=0 If mod=11 and w=1

000 AL AX

001 CL CX

010 DL DX

011 BL BX

100 AH SP

101 CH BP

110 DH SI

111 BH DI

* – When mod≠11, depends on instruction

Table 2-3 r/m field

r/m Description

000 EA* = (BX)+(SI)+DISP

001 EA = (BX)+(DI)+DISP

010 EA = (BP)+(SI)+DISP

011 EA = (BP)+(DI)+DISP

100 EA = (SI)+DISP

101 EA = (DI)+DISP

110 EA = (BP)+DISP (except if mod=00, then EA = disp-high:disp:low)

111 EA = (BX)+DISP

* – EA is the Effective Address

2.2.5 Displacement

The displacement is an 8- or 16- bit immediate value to be adde d to the offset portion of the

address.

2.2.6 Immediate

The immediate bytes contain up to 16 bits of immediate data.

2.3 NOTATION

This parameter Indicates that

: The component on the left is the segment for a component located in

memory. The component on the right is the offset.

:: The component on the left is concatenated with the component on the right.

Instruction Set Overview

2-3

2.4 USING THIS MANUAL

Each instruction is detailed in Chapter 4. The following sections explain the format used

when describing each instruction.

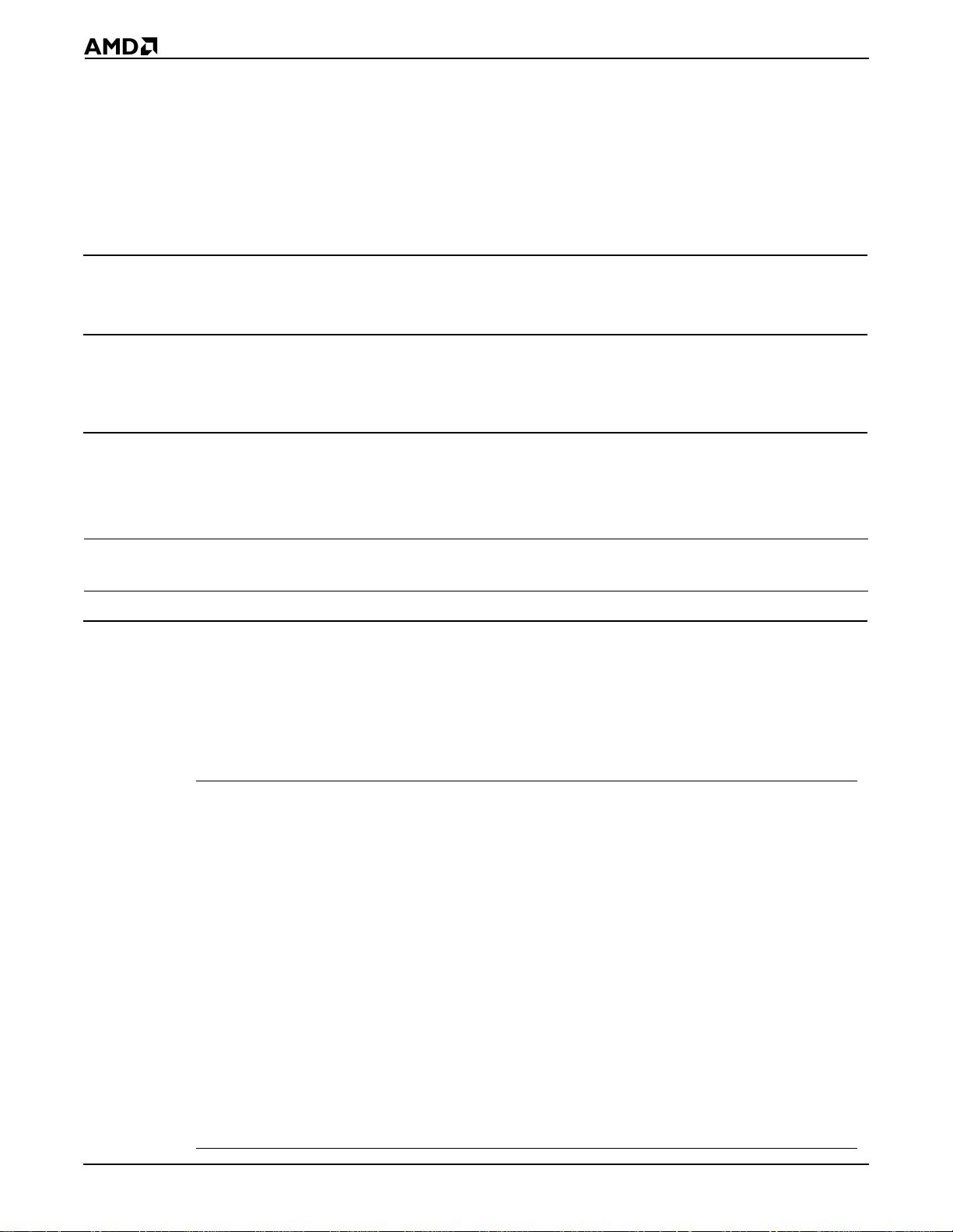

2.4.1 Mnemonics and Names

The primary assembly-language mnemoni c and its name appear at the top of the first page

for an instruction (see Figure 2-1) . Some inst ructions have additional mnemonics that

perform the same operation. These synonyms are listed below the primary mnemonic.

Figure 2-1 Instruction Mnemon ic and Name Sample

MUL Multiply Unsigned Numbers

2.4.2 Form s of th e In s truction

Many instructions have more than one form. The forms for each instruc tion are lis ted in a

table just below the mnemonics (see Figure 2-2).

Figure 2-2 Instruction For ms Tab l e Sa m ple

Form Opcode Description

MUL

MUL

r/m8

r/m16

Form

F6

F7

/4

/4

AX=(r/m byte)•AL 26–28/32–34 26–28/32–34

DX::AX=(r/m word)•AX 35–37/41–43 35–37/45–47

The Form column specifies the syntax for t he d if ferent forms of an instruction. Each form

includes an instruction mnemonic and zero or more oper ands. Items in italics are

placeholders for operand s that must be provided. A placeholder indi cates the size and type

of operand that is allowed.

This operand Is a placeholder for

imm8

imm16

m

m8

m16

m16&16

m16:16

moffs8

moffs16

ptr16:16

r8

r16

r/m8

r/m16

rel8

rel16

sreg

An immediate byte: a signed number between –128 and 127

An immediate word: a signed number betwe en –327 68 and 327 67

An operand in memory

A byte string in memory pointed to by DS:SI or ES:DI

A word string in memory pointed to by DS:SI or ES:DI

A pair of words in memory

A doubleword in memory that contains a full address (segment:offset)

A byte in memory that contains a signed, relative offset displacement

A word in memory that contains a signed, relative offset displacement

A full address (segment:offset)

A general byte register: AL, BL, CL, DL, AH, BH, CH, or DH

A general word register: AX, BX, CX, DX, BP, SP, DI, or SI

A general byte register or a byte in memory

A general word register or a word in memory

A signed, relative offset displacement between –128 and 127

A signed, relative offset displac em ent betw een –32768 and 32767

A segment register

Clocks

Am186 Am188

2-4

Instruction Set Overview

Opcode

The Opcode column specifies the machi ne-language opcodes for th e different forms of an

instruction. (For instruction prefixes, this column also includes the prefi x.) Each opcode

includes one or more numbers in hexadeci mal format, and zero or more parameters, which

are shown in italics. A parameter prov ides informat ion about the cont ents of t he Operand

Address byte for that particular form of the inst ruction.

This parameter Indicates that

/0–/

/

r

/

sr

cb

cd

cw

ib

iw

rb

rw

7

/0 The aux field is 0.

/1 The aux field is 1.

/2 The aux field is 2.

/3 The aux field is 3.

/4 The aux field is 4.

/5 The aux field is 5.

/6 The aux field is 6.

/7 The aux field is 7.

The Auxiliary (aux) Field in the Operand Address byte specifies an

extension (from 0 to 7) to the opcode instead of a register. So for example,

the opcode for adding (ADD) an immediate byte to a general byte register

ib

or a byte in memory is "80 /0

"mod 000 r/m", where mod and r/m are as defined in "Operand Address"

on page 2-2.

The Auxiliary (aux) field in the Operand Address byte specifies a register

instead of an opcode extension. If the Opcode byte specifies a byte register,

the registers are assigned as follows: AL=0, CL=1, DL=2, BL=3, AH=4,

CH=5, DH=6, and BH=7. If the Opcode byte specifies a word register, the

registers are assigned as follows: AX=0, CX=1, DX=2, BX=3, SP=4, BP=5,

SI=6, and DI=7.

The Auxiliary (aux) field in the Operand Address byte specifies a segment

register as follows: ES=0, CS=1, SS=2, and DS=3.

The byte following the Opcode byte specifies an offset.

The doubleword following the Opcode byte specifies an offset and, in some

cases, a segment.

The word following the Opcode byte specifies an offset and, in some cases,

a segment.

The parameter is an immediate byte. The Opcode byte determines whether

it is interpreted as a signed or unsigned number.

The parameter is an immediate word. The Opcode byte determines whether

it is interpreted as a signed or unsigned number.

The byte register operand is specified in the Opcode byte. To determine

the Opcode byte for a particular register, add the hexadecimal value on the

left of the plus sign to the value of

AL=0, CL=1, DL=2, BL= 3, AH=4, CH=5, DH=6, and BH=7. So for example,

the opcode for moving an immediate byte to a register (MOV) is "B0+

So B0–B7 are valid opcodes, and B0 is "MOV AL,

The word register operand is specified in the Opcode byte. To determine

the Opcode byte for a particular register, add the hexadecimal value on the

left of the plus sign to the value of

AX=0, CX=1, DX=2, BX=3, SP=4, BP=5, SI=6, DI=7.

". So the second byte of the opcode is

rb

for that register, as follows:

imm8

".

rw

for that register, as follows:

rb

".

Instruction Set Overview

2-5

Description

The Description column contains a brief synopsis of each form of the instruction.

Clocks

The Clocks columns (one for the Am186 and one for the Am188 microcontrollers ) specify

the number of clock cycles required for the different forms of an instruction.

This parameter Indicates that

/

,

n

2.4.3 What It Does

This section contains a brief description of the operation the instruction performs.

2.4.4 Syntax

This section shows the syntax for the instruction. Instructions with more than one mnemonic

show the syntax for each mnemonic.

The number of clocks required for a register operand is different than the

number required for an operand located in memory. The number to the

left corresponds with a register operand; the number to the right

corresponds with an operand located in memory.

The number of clocks depends on the result of the condition tested. The

number to the left corresponds with a True or Pass result, and the number

to the right corresponds with a False or Fail result.

The number of clocks depends on the number of times the instruction is

n

repeated.

is the number of repetitions.

2.4.5 Description

This section contains a more in-depth descript ion of the instruction.

2-6

Instruction Set Overview

2.4.6 Operation It Performs

This section uses a combination of C-language and assembler syntax t o describe the

operation of the instruction in detail. In some cases, pseudo-code functions are used to

simplify the code. These functions and the actions they perform are as follows:

Pseudo-Code Function Action

cat(

componenta,componentb

execute(

interrupt(

interruptRequest() Return True if the microcontroller receives a maskable

leastSignificantBit(

mostSignificantBit(

nextMostSignificantBit(

nmiRequest() Return True if the microcontroller receives a nonmaskable

operands() Return the number of operands present in the instruction.

pop() Read a word from the top of the stack, increment SP, and

pow(n,

push(

resetRequest() Return True if a device resets the microcontroller by asserting

serviceInterrupts() Service any pending interrupts.

size(

stopExecuting() Suspend execution of current instruction sequence.

instruction

type

) Issue an interrupt request to the microcontroller.

component

component

component

) Execute the instruction.

component

component

) Raise component to the nth power.

) Decrement SP and copy the component to the top of the

) Return the size of the component in bits.

) Component A is concatenated with component B.

component

interrupt request.

) Return the least significant bit of the component.

) Return the most significant bit of the component.

) Return the next most significant bit of the component.

interrupt request.

return the value.

stack.

the RES

signal.

2.4.7 Flag Settings After In struction

This section identifies the flags that are set, cleared, modified according to the result,

unchanged, or left undefined by the instruction. Each instruction has the graphic below,

and shows values for the flag bits after the instruction is performed. A "?" in the bit field

indicates the value is undefined; a "–" i ndicates the bit value is unchanged. See "Processor

Status Flags Register" on page 1-2 for more information on the flags.

Processor Status

Flags Register

? = undefined; – = unchanged

reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OF DF IF TF SF ZF AF PF CF

2.4.8 Examples

This section contains one or more examples t hat illustrate possible use s for the instruction.

The beginning of each example is marked with a printout icon ; a summary of the example’s

function appears next to it. The exampl e code foll ows the summary. Not e that some of the

examples use assembler directives: CONST (def ine constant d ata), DB (defi ne byte), DD

(define double), DW (define word), EQU (equate), LENGTH (length of array), PROC (begin

procedure), SEGMENT (define segment), SIZE (return integer size) and TYPE (return

integer type).

res res res

? = unknown; – = unchanged

Instruction Set Overview

2-7

2.4.9 Tips

This section contains hints and i deas about some of the way s in which the i nstructi on can

be used.

Tips are marked with this icon.

2.4.10 Related Instructions

This section lists other instructions rel ated to the described instruction.

2-8

Instruction Set Overview

CHAPTER

INSTRUCTION SET LISTING

3

This chapter lists all the instructions for the Am186 and Am188 family of microcontrol lers.

The instructions are first grouped by type (see page 3-1) and then listed in alphabetical

order (see page 3-11)

3.1 INSTRUCTION SET BY TYPE

The instructions can be classified into groups according to the type of operation they

perform. Instructions that are used for more than one purpose are listed under each category

to which they belong. The functional groups are:

n "Address Calculation and Translation" on page 3-1

n "Binary Arithmetic" on page 3-2

n "Block-Structured Language" on page 3-3

n "Comparison" on page 3-3

n "Control Transfer" on page 3-3

n "Data Movement" on page 3-5

n "Decimal Arithmetic" on page 3-6

n "Flag" on page 3-7

n "Input/Output" on page 3-8

n "Logical Operation" on page 3-8

n "Processor Control" on page 3-9

n "String" on page 3-9

3.1.1 Address Calculation and Translat ion

Address Calculation Instructions

Mnemonic Name See Page

LDS Load DS with Segment and Register with Offset 4-131

LEA Load Effective Address 4-133

LES Load ES with Segment and Register with Offset 4-138

Address Translation Instructions

Mnemonic Name See Page

XLAT Translate Table Index to Component 4-248

XLATB Translate Table Index to Byte (

Synonym for

XLAT) 4-248

Instruction Set Listing

3-1

3.1.2 Binary Arithmetic

The microcontroller supports binary arit hmetic using numbers represented in the two’s

complement system. The t wo’s complement system uses the high bit of an integer (a signed

number) to determine the sign of the number. Unsigned numbers have no sign bit.

Binary Addition Instructions

Mnemonic Name See Page

ADC Add Numbers with Carry 4-10

ADD Add Numbers 4-14

INC Increment Number by One 4-69

Binary Subtraction Instructions

Mnemonic Name See Page

DEC Decrement Number by One 4-48

SBB Subtract Numbers with Borrow 4-216

SUB Subtract Numbers 4-240

Binary Multiplication Instructions

Mnemonic Name See Page

IMUL Multiply Integers 4-63

MUL Multiply Unsigned Numbers 4-160

SAL Shift Arithmetic Left 4-211

SHL Shift Left (

Binary Divis ion Instruct ions

Mnemonic Name See Page

DIV Divide Unsigned Numbers 4-50

IDIV Divide Integers 4-60

SAR Shift Arithmetic Right 4-214

SHR Shift Right 4-225

Binary Conversion Instructions

Mnemonic Name See Page

CBW Convert Byte Integer to Word 4-24

CWD Convert Word Integer to Doubleword 4-40

NEG Two’s Complement Negation 4-163

Synonym for

SAL) 4-211

3-2

Instruction Set Listing

3.1.3 Block-Structu red Language

Block-Structured Language Instructions

Mnemonic Name See Page

ENTER Enter High-Level Procedure 4-53

LEAVE Leave High-Level Procedure 4-135

3.1.4 Comparison

General Comparison Instructions

Mnemonic Name See Page

CMP Compare Comp one nts 4-34

TEST Logical Compare 4-243

String Compari s on Instructions

Mnemonic Name See Page

CMPS Compare String Components 4-36

CMPSB Compare String Bytes (

CMPSW Compare String Words (

SCAS Scan String for Component 4-219

SCASB Scan String for Byte (

SCASW Scan String for Word (

Synonym for

Synonym for

Synonym for

Synonym for

CMPS) 4-36

CMPS) 4-36

SCAS) 4-219

SCAS) 4-219

3.1.5 Control Transfer

Conditional Jump Instructions to Use after Integer Comparisons

Mnemonic Name See Page

JG Jump If Greater 4-91

JGE Jump If Greater or Equal 4-93

JL Jump If Less 4-95

JLE Jump If Less or Equal 4-97

JNG Jump If Not Greater (

JNGE Jump If Not Greater or Equal (

JNL Jump If Not Less (

JNLE Jump If Not Less or Equal (

Synonym for

Synonym for

Synonym for

JLE) 4-97

Synonym for

JGE) 4-93

JL) 4-95

JG) 4-91

Instruction Set Listing

3-3

Conditional Jump Instructions to Use after Unsigned Number Comparisons

Mnemonic Name See Page

JA Jump If Above 4-78

JAE Jump If Above or Equal 4-80

JB Jump If Below 4-82

JBE Jump If Below or Equal 4-84

JNA Jump If Not Above (

JNAE Jump If Not Above or Equal (

JNB Jump If Not Below (

JNBE Jump If Not Below or Equal (

Conditional Jump Instructions That Test for Equality

Mnemonic Name See Page

JE Jump If Equal 4-89

JNE Jump If Not Equal 4-107

Conditional Jump Instructions That Test Flags

Mnemonic Name See Page

JC Jump If Carry (

JNC Jump If Not Carry (

JNO Jump If Not Overflow 4-113

JNP Jump If Not Parity (

JNS Jump If Not Sign 4-116

JNZ Jump If Not Zero (

JO Jump If Overflow 4-119

JP Jump If Parity (

JPE Jump If Parity Even 4-122

JPO Jump If Parity Odd 4-124

JS Jump If Sign 4-126

JZ Jump If Zero (

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

JBE) 4-84

Synonym for

JAE) 4-80

Synonym for

JB) 4-82

JAE) 4-80

JPO) 4-124

JNE) 4-107

JPE) 4-121

JE) 4-89

JB) 4-82

JA) 4- 78

3-4

Conditional Interrupt Instructions

Mnemonic Name See Page

BOUND Check Array Index Against Bounds 4-19

IDIV Divide Integers 4-60

INTO Generate Interrupt If Overflow (

Instruction Set Listing

Conditional form of

INT) 4-73

Conditional Loop Instructions

Mnemonic Name See Page

JCXZ Jump If CX Register Is Zero 4-87

LOOP Loop While CX Register is Not Zero 4-146

LOOPE Loop If Equal 4-148

LOOPNE Loop If Not Equal 4-150

LOOPNZ Loop If Not Zero (

LOOPZ Loop If Zero (

Unconditional Transfer Instructions

Mnemonic Name See Page

CALL Call Procedure 4-21

INT Generate Interrupt 4-73

IRET Interrupt Return 4-76

JMP Jump Unconditionally 4-99

RET Return from Procedure 4-202

3.1.6 Data Movement

Synonym for

Synonym for

LOOPNE) 4-150

LOOPE) 4-148

General Movement Instructi ons

Mnemonic Name See Page

MOV Move Component 4-153

XCHG Exchange Components 4-246

String Movement Instructions

Mnemonic Name See Page

LODS Load String Component 4-141

LODSB Load String Byte (

LODSW Load String Word (

MOVS Move String Component 4-156

MOVSB Move String Byte (

MOVSW Move String Word (

STOS Store String Component 4-237

STOSB Store String Byte (

STOSW Store String Word (

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

LODS) 4-141

LODS) 4-141

MOVS) 4- 15 6

MOVS) 4-156

STOS) 4-237

STOS) 4-237

Instruction Set Listing

3-5

Stack Movement Inst r uctions

Mnemonic Name See Page

POP Pop Component from Stack 4-175

POPA Pop All 16-Bit General Registers from Stack 4-178

POPF Pop Flags from Stack 4-180

PUSH Push Component onto Stack 4-181

PUSHA Push All 16-Bit General Registers onto Stack 4-184

PUSHF Push Flags onto Stack 4-186

General I/O Movement Instructions

Mnemonic Name See Page

IN Input Component from Port 4-67

OUT Output Component to Port 4-171

String I/O Movement Instructions

Mnemonic Name See Page

INS Input String Component from Port 4-71

INSB Input String Byte from Port (

INSW Input String Word from Port (

OUTS Output String Component to Port 4-173

OUTSB Output String Byte to Port (

OUTSW Output String Word to Port (

Synonym for

Synonym for

Synonym for

Synonym for

INS) 4-71

INS) 4-71

OUTS) 4-17 3

OUTS) 4-173

Flag Movemen t Instructions

Mnemonic Name See Page

LAHF Load AH with Flags 4-129

SAHF Store AH in Flags 4-209

3.1.7 Decimal Arithmetic

In addition to binary arithmetic, the microcontroller supports arithmetic using numbers

represented in the binary-coded decimal (BCD) system. The BCD system uses four bits to

represent a single decimal digit. When two decimal digits are stored in a byte, the number

is called a

packed

number is called an

To perform decimal arithmetic, the microcon troller uses a subset of the binary arithmetic

instructions and a special set of instructions that convert unsigned binary numbers to

decimal.

Arithmetic Instructions That Are Used with Decimal Numbers

Mnemonic Name See Page

ADD Add Numbers 4-14

DIV Divide Unsigned Numbers 4-50

MUL Multiply Unsigned Numbers 4-160

SUB Subtract Numbers 4-240

decimal number. When only one decimal digit is stored in a byte, the

unpacked

decimal number.

3-6

Instruction Set Listing

Unpacked-Decimal Adjustment Instructions

Mnemonic Name See Page

AAA ASCII Adjust AL After Addition 4-2

AAD ASCII Adjust AX Before Division 4-4

AAM ASCII Adjust AL After Multiplication 4-6

AAS ASCII Adjust AL After Subtraction 4-8

Packed-Decimal Adjustment Instructions

Mnemonic Name See Page

DAA Decimal Adjust AL After Addition 4-42

DAS Decimal Adjust AL After Subtraction 4-45

Consider using decimal arithmetic instead of binary arithmetic under the following

circumstances:

n When the numbers you are using represent only decimal quantities.

Manipulating numbers in binary and converting them back and fort h between binary and

decimal can introduce rounding errors.

n When you need to read or write many ASCII numbers.

Converting a number between ASCII and decimal is simpler than converting it between

ASCII and binary.

3.1.8 Flag

Single-Flag Instructions

Mnemonic Name See Page

CLC Clear Carry Flag 4-26

CLD Clear Direction Flag 4-29

CLI Clear Interrupt-Enable Flag 4-31

CMC Complement Carry Flag 4-33

RCL Rotate through Carry Left 4-187

RCR Rotate through Carry Right 4-189

STC Set Carry Flag 4-228

STD Set Direction Flag 4-231

STI Set Interrupt-Enable Flag 4-235

Multiple-Flag Instructions

Mnemonic Name See Page

POPF Pop Flags from Stack 4-180

SAHF Store AH in Flags 4-209

Instruction Set Listing

3-7

3.1.9 Input/Output

General I/O Instructions

Mnemonic Name See Page

IN Input Component from Port 4-67

OUT Output Component to Port 4-171

String I/O Instructions

Mnemonic Name See Page

INS Input String Component from Port 4-71

INSB Input String Byte from Port (

INSW Input String Word from Port (

OUTS Output String Component to Port 4-173

OUTSB Output String Byte to Port (

OUTSW Output String Word to Port (

3.1.10 Logical Operation

Boolean Operation Instructions

Mnemonic Name See Page

Synonym for

Synonym for

Synonym for

Synonym for

INS) 4-71

INS) 4-71

OUTS) 4-17 3

OUTS) 4-173

AND Logical AND 4-17

NOT One’s Complement Negation 4-167

OR Logical Inclusive OR 4-169

XOR Logical Exclus ive OR 4-251

Shift Instructions

Mnemonic Name See Page

SAL Shift Arithmetic Left 4-211

SAR Shift Arithmetic Right 4-214

SHL Shift Left (

SHR Shift Right 4-225

Rotate Instructions

Mnemonic Name See Page

RCL Rotate through Carry Left 4-187

RCR Rotate through Carry Right 4-189

ROL Rotate Left 4-205

ROR Rotate Right 4-207

Synonym for

SAL) 4-211

3-8

Instruction Set Listing

3.1.11 Processo r Control

Processor Control Instructions

Mnemonic Name See Page

HLT Halt 4-57

LOCK Lock the Bus 4-140

NOP No Operation 4-165

Coprocessor Interface Instructions

Mnemonic Name See Page

ESC Escape 4-56

WAIT Wait for Coproces sor 4-245

3.1.12 String

A string is a contiguous sequence of components st ored in memory. For example, a string

might be composed of a list of ASCII characters or a table of numbers.

A string instruction operates on a single component in a str ing. To manipulate more than

one component in a string, the string instruct ion

REPZ) can be used to repeatedly execute the same string instruction.

prefixes

(REP/REPE/REPNE/REPNZ/

A string instruction uses an index register as the offset of a component in a string. Most

string instructions operate on only one string, in which case they use either the Source

Index (SI) register or the Destin ation Index (DI) register. St ring instructions that oper ate on

two strings use SI as the offset of a component in one string and DI as the offset of the

corresponding component in the other string.

After executing a string instruction, the microcontroller automatically increments or

decrements SI and DI so that they contain the offsets of the next components in their strings.

The microcontroller determines the amount by which the index registers must be

incremented or decremented based on the size of the components.

The microcontroller can process the components of a string in a forward direction (from

lower addresses to higher addresses), or in a backward direct ion (fr om higher addresses

to lower ones). The microcont roller use s the value of the Direction Fl ag (DF) to determine

whether to increment or decrement SI and DI. If DF is cleared to 0, the microcontroller

increments the index registers; otherwise, it decrements them.

String-Instru ct ion Prefixes

Mnemonic Name See Page

REP Repeat 4-191

REPE Repeat Whil e Equal 4-193

REPNE Repeat While Not Equal 4-197

REPNZ Repeat While Not Zero (

REPZ Repeat While Zero (

Synonym for

Synonym for

REPNE) 4-197

REPE) 4-193

Instruction Set Listing

3-9

String Direction Instructions

Mnemonic Name See Page

CLD Clear Direction Flag 4-29

STD Set Direction Flag 4-231

String Movement Instructions

Mnemonic Name See Page

LODS Load String Component 4-141

LODSB Load String Byte (

LODSW Load String Word (

MOVS Move String Component 4-156

MOVSB Move String Byte (

MOVSW Move String Word (

STOS Store String Component 4-237

STOSB Store String Byte (

STOSW Store String Word (

String Compari s on Instructions

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

LODS) 4-141

LODS) 4-141

MOVS) 4-156

MOVS) 4-156

STOS) 4-237

STOS) 4-237

Mnemonic Name See Page

CMPS Compare String Components 4-36

CMPSB Compare String Bytes (

CMPSW Compare String Words (

SCAS Scan String for Component 4-219

SCASB Scan String for Byte (

SCASW Scan String for Word (

String I/O Instructions

Mnemonic Name See Page

INS Input String Component from Port 4-71

INSB Input String Byte from Port (

INSW Input String Word from Port (

OUTS Output String Component to Port 4-173

OUTSB Output String Byte to Port (

OUTSW Output String Word to Port (

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

CMPS) 4-36

CMPS) 4-36

SCAS) 4-219

SCAS) 4-219

INS) 4-71

INS) 4-71

OUTS) 4-17 3

OUTS) 4-173

3-10

Instruction Set Listing

3.2 INSTRUCTION SET IN ALPHABETICAL ORDER

Table 3-1 provides an alphabetical list of the instruction set for the Am186 and Am188

microcontrollers.

Table 3-1 Instruction Set

Mnemonic Instruction Name See Page

AAA ASCII Adjust AL After Addition 4-2

AAD ASCII Adjust AX Before Division 4-4

AAM ASCII Adjust AL After Multiplication 4-6

AAS ASCII Adjust AL After Subtraction 4-8

ADC Add Numbers with Carry 4-10

ADD Add Numbers 4-14

AND Logical AND 4-17

BOUND Check Array Index Against Bounds 4-19

CALL Call Procedure 4-21

CBW Convert Byte Integer to Word 4-24

CLC Clear Carry Flag 4-26

CLD Clear Direction Flag 4-29

CLI Clear Interrupt-Enable Flag 4-31

CMC Complement Carry Flag 4-33

CMP Compare Comp one nts 4-34

CMPS Compare String Components 4-36

CMPSB Compare String Bytes (

CMPSW Compare String Words (

CWD Convert Word Integer to Doubleword 4-40

DAA Decimal Adjust AL After Addition 4-42

DAS Decimal Adjust AL After Subtraction 4-45

DEC Decrement Number by One 4-48

DIV Divide Unsigned Numbers 4-50

ENTER Enter High-Level Procedure 4-53

ESC Escape 4-56

HLT Halt 4-57

IDIV Divide Integers 4-60

IMUL Multiply Integers 4-63

IN Input Component from Port 4-67

INC Increment Number by One 4-69

INS Input String Component from Port 4-71

INSB Input String Byte from Port (

INSW Input String Word from Port (

INT Generate Interrupt 4-73

INTO Generate Interrupt If Overflow (

IRET Interrupt Return 4-76

JA Jump If Above 4-78

JAE Jump If Above or Equal 4-80

JB Jump If Below 4-82

JBE Jump If Below or Equal 4-84

JC Jump If Carry (

JCXZ Jump If CX Register Is Zero 4-87

Synonym for

Synonym for

Synonym for

Synonym for

Synonym for

CMPS) 4-36

CMPS) 4-36

INS) 4-71

INS) 4-71

Conditional form of

JB) 4-82

INT) 4-73

Instruction Set Listing

3-11

Table 3-1 Instruction Set (continued)

Mnemonic Instruction Name See Page

JE Jump If Equal 4-89

JG Jump If Greater 4-91

JGE Jump If Greater or Equal 4-93

JL Jump If Less 4-95

JLE Jump If Less or Equal 4-97

JMP Jump Unconditionally 4-99

JNA Jump If Not Above (

JNAE Jump If Not Above or Equal (

JNB Jump If Not Below (

JNBE Jump If Not Below or Equal (

JNC Jump If Not Carry (

JNE Jump If Not Equal 4-107

JNG Jump If Not Greater (

JNGE Jump If Not Greater or Equal (

JNL Jump If Not Less (

JNLE Jump If Not Less or Equal (

JNO Jump If Not Overflow 4-113

JNP Jump If Not Parity (

JNS Jump If Not Sign 4-116

JNZ Jump If Not Zero (

JO Jump If Overflow 4-119

JP Jump If Parity (

JPE Jump If Parity Even 4-122

JPO Jump If Parity Odd 4-124

JS Jump If Sign 4-126

JZ Jump If Zero (

LAHF Load AH with Flags 4-129

LDS Load DS with Segment and Register with Offset 4-131

LEA Load Effective Address 4-133

LEAVE Leave High-Level Procedure 4-135

LES Load ES with Segment and Register with Offset 4-138

LOCK Lock the Bus 4-140

LODS Load String Component 4-141

LODSB Load String Byte (

LODSW Load String Word (

LOOP Loop While CX Register Is Not Zero 4-146