Page 1

查询AM186ED供应商

PRELIMINARY

Am186TMED/EDLV

High Performance, 80C186- and 80C188-Compatible,

16-Bit Embedded Microcontrollers

DISTINCTIVE CHARACTERISTICS

n E86TM family 80C186- and 80C188-compatible

microcontroller with enhanced bus interface

– Lower system cost with higher performance

– 3.3-V ± 0.3-V operation (Am186EDLV

microcontrollers)

n Programmable DRAM Controller

– Supports zero-wait-state operation with 50-ns

DRAM at 40 MHz, 60-ns @ 33 M Hz, 70- ns @ 25

MHz

– Includes programmable CAS

refresh capability

n High performance

– 20-, 25-, 33-, and 40-MHz operating frequencies

– Zero-wait-state operation at 40 MHz with 70-ns

static memory

– 1-Mbyte memory address space

– 64-Kbyte I/O space

n Enhanced features provide improved memory

access and remove the requirement for a 2x clock

input

– Nonmultiplexed address bus

– Processor operates at the clock input frequency

– 8-bit or 16-bi t program mable b us sizi ng includ ing

8-bit boot option

n Enhanced integrated peripherals

– 32 programmable I/O (PIO) pins

– Two full-featured asynchronou s seri al ports allo w

full-duplex, 7-bit, 8-bit, or 9-bit data transfers

-before-RAS

– Serial port hardware handshaking with CTS

RTS, ENRX, and RTR selectable for each port

– Improved serial port operation enhances 9-bit

DMA support

– Independent serial port baud rate generators

– DMA to and from the serial ports

– Watchdog timer can generate NMI or reset

– A pulse-width demodulation option

– A data strobe, tr ue asynchronous bus interfac e

option included for DEN

– Reset configuration register

n Familiar 80C186 peripherals

– Two independent DMA channels

– Programmable interrupt controller with up to 8 ex-

ternal and 8 internal interrupts

– Three programmable 16-bit timers

– Programmable memory and peripheral

chip-select logic

– Programmable wait state generator

– Power- save cl oc k div id er

n Software-compatible with the 80C186 and

80C188 microcontrollers with widely available

native development tools, applications, and

system software

n A compatible evolution of the Am186EM,

Am186ES, and Am186ER microcontrollers

n Available in the following packages:

– 100-pin, thin quad flat pack (TQFP)

– 100-pin, plastic quad flat pack (PQFP)

RA

,

FT

GENERAL DESCRIPTION

The Am186TMED/EDLV microcontrollers are part of the

AMD E86

croprocessors based on the x86 architecture. The

Am186ED/EDLV microcontrollers are the ideal upgrade

for 80C186/188 designs requiring 80C186/188 compatibility, increased performance, serial communications, a

direct bus interface, and more than 64K of memory.

The Am186ED/EDLV microcontrollers integrate a complete DRAM control ler to ta ke adv antage of low DRAM

costs. This reduces memory subsystem costs while

maintaining SRAM performance.The Am186ED/EDLV

microcontrollers a lso integrate t he functions of a CPU,

nonmultiplexed address bus, three timers, watchdog

timer, chip selects, interrupt controller, two DMA controllers, two asynchronous serial ports, programmable bus

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this pro duct. AMD reserves t he right to change or discontinue work o n this proposed

product without notice. AMD, the AMD logo, and combinations there of are tra dema rks of Adva nced Micr o Devices,

Inc.

TM

family of embedded mic roco ntrollers a nd mi-

D

sizing, and programmable I/O (PIO) pins on one chip.

Compared to the 80C186/188 microcontrollers, the

Am186ED/EDLV microcontrollers enable designers to

reduce the size, power consumption, and cost of embedded systems, whi le i nc reas in g r eli ab ili ty, functionality, and performance.

The Am186ED/EDLV microcontrollers have been

designed to meet the most common requirements of

embedded products developed for the communications,

office automation, mass storage, and general

embedded markets. Specific applications include

PBXs, multiplexers, modems, disk drives, hand-held

and desktop terminals, fax machines, printers,

photocopiers, and industrial controls.

Publication# 21336 Rev: A Amendment/0

Issue Date: May 1997

Page 2

PRELIMINARY

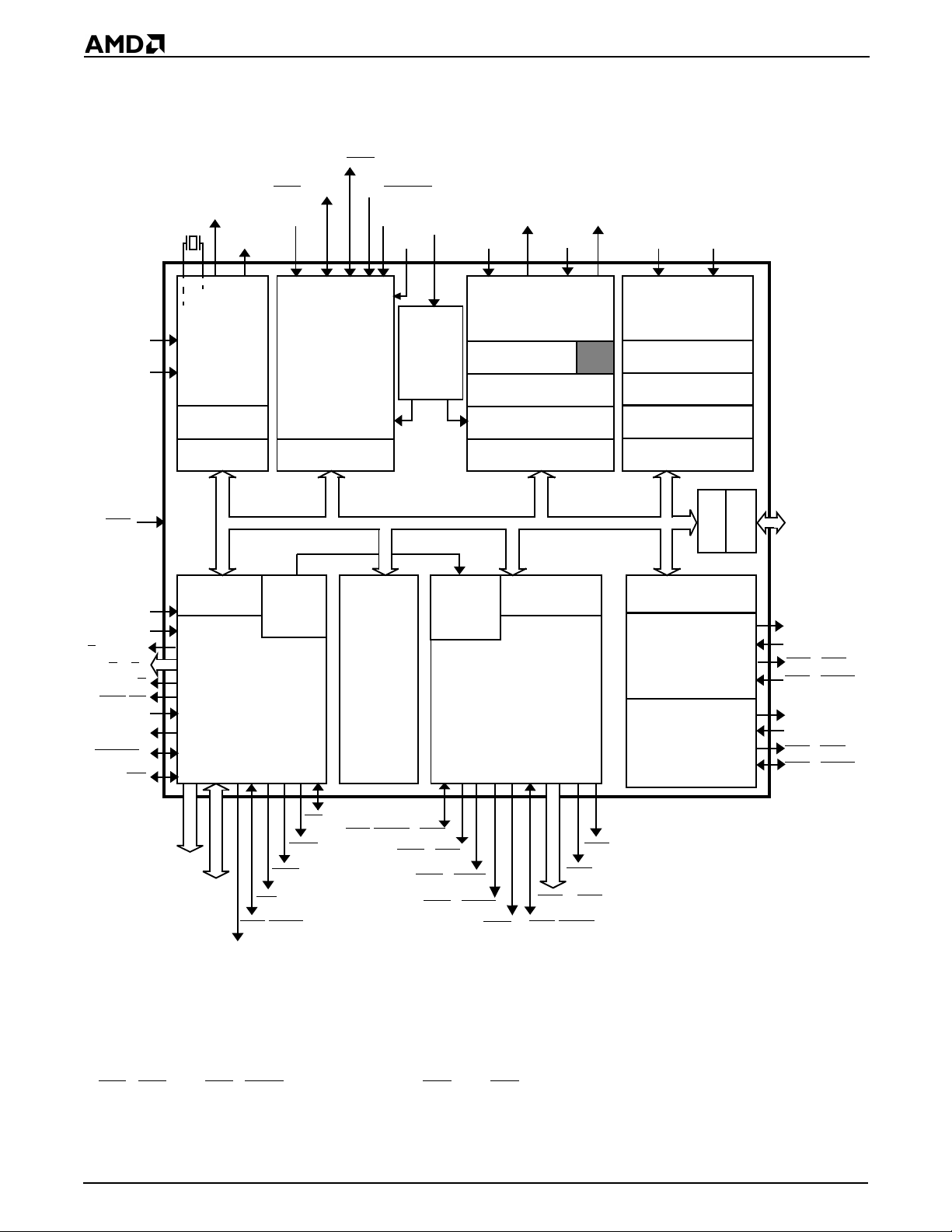

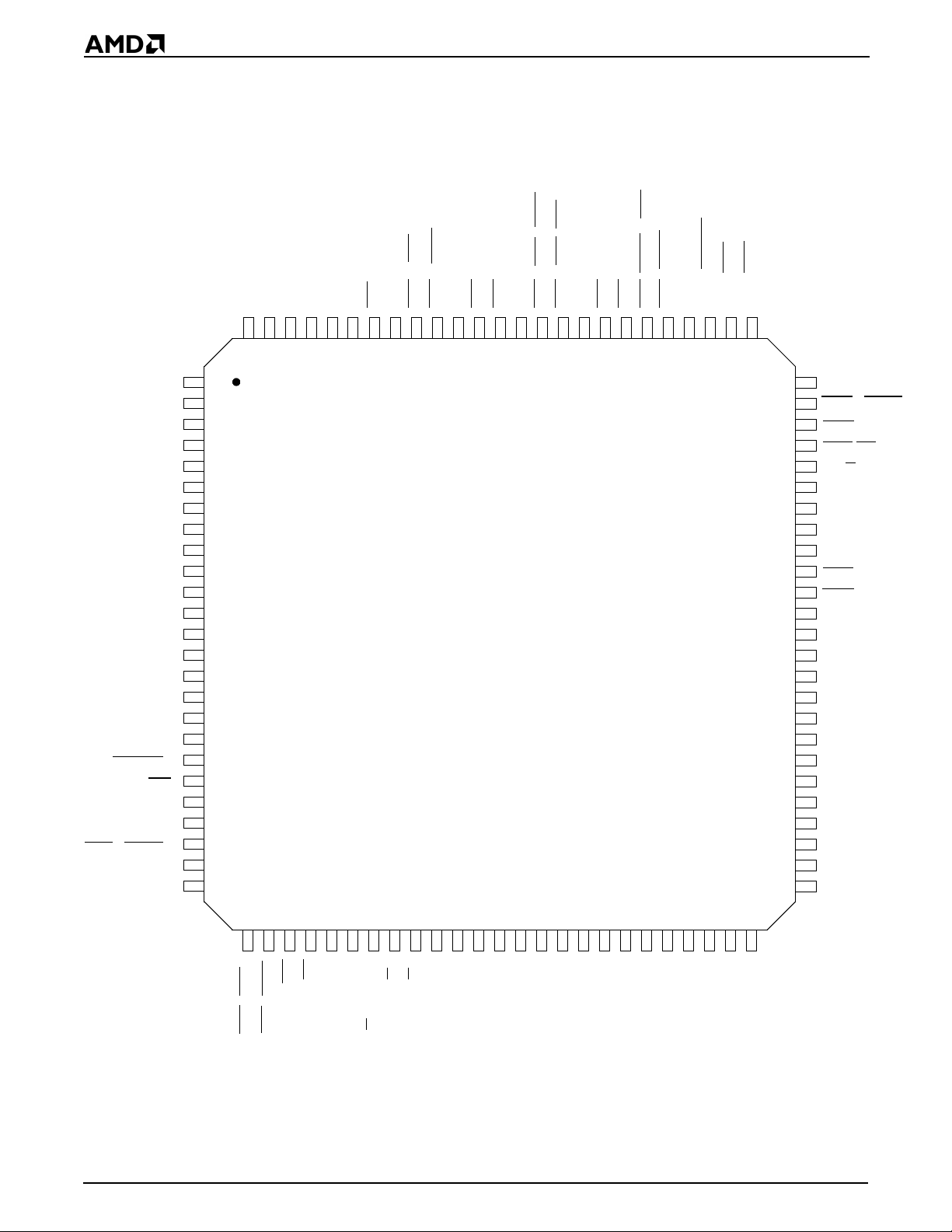

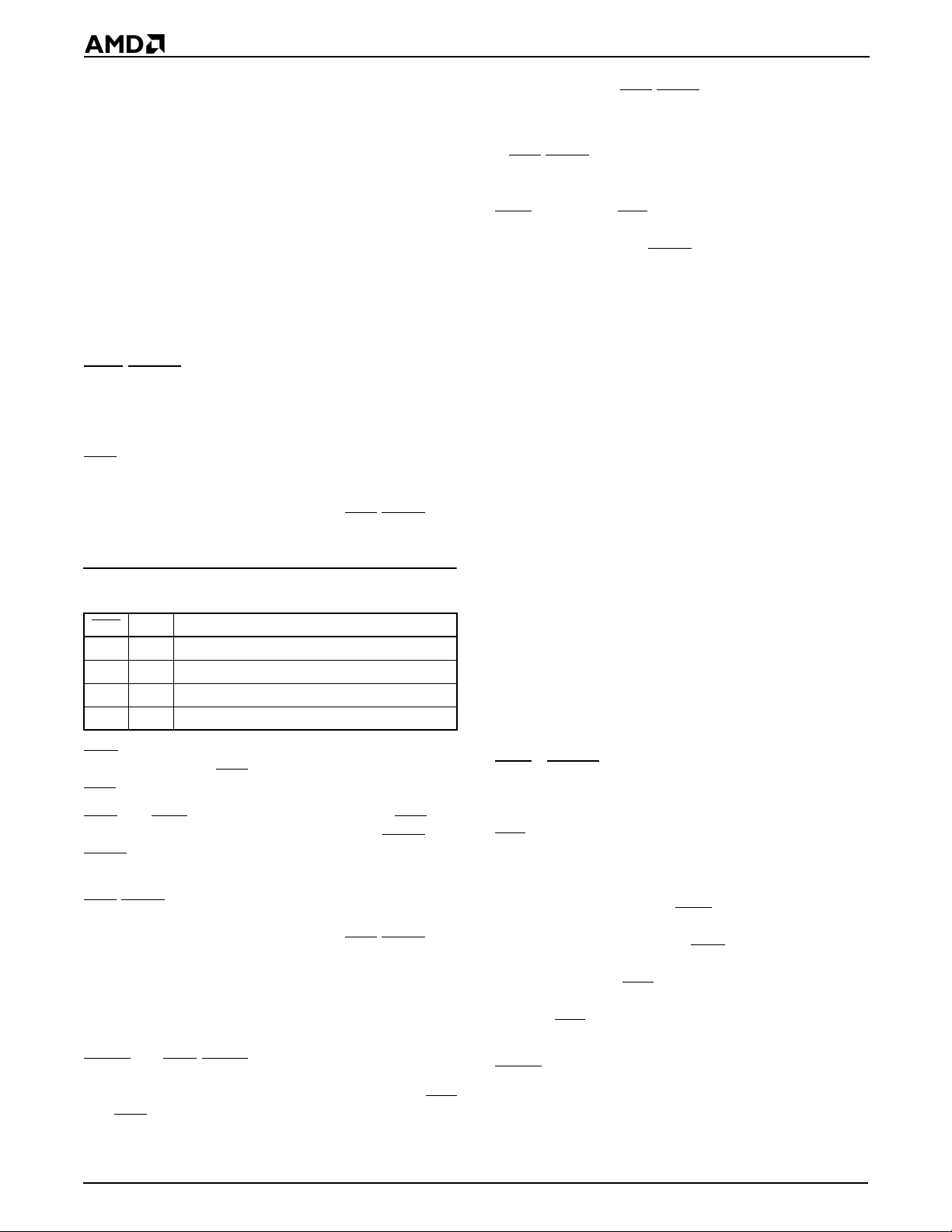

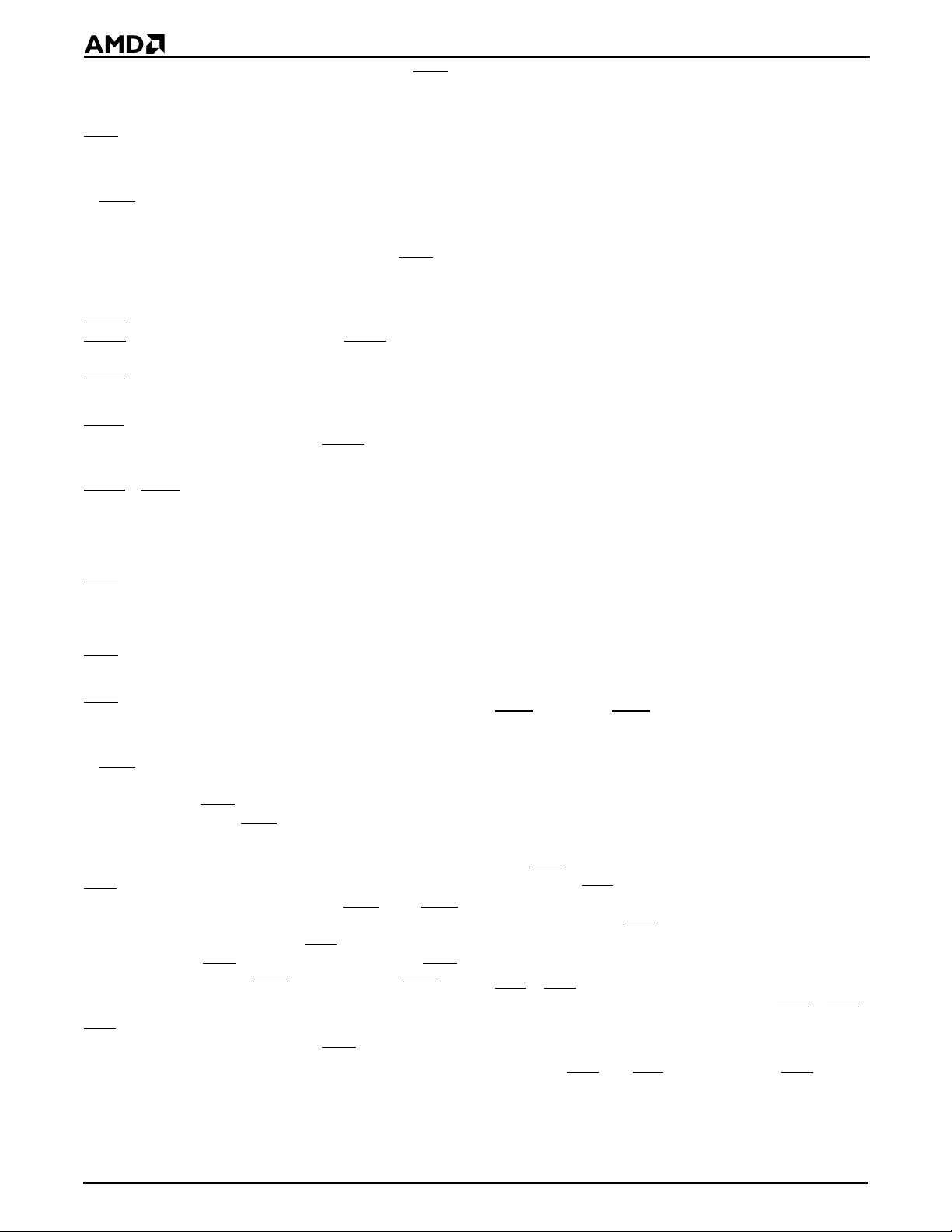

Am186ED/EDLV MICROCONTROLLERS BLOCK DIAGRAM

V

CC

GND

RES

ARDY

SRDY

S2/BTSEL

S1–S0

DT/R

DEN/DS

HOLD

HLDA

S6/CLKDIV2

UZI

INT3/INTA

CLKOUTA

CLKOUTB

X2

X1

Clock and

Power

Management

Unit

Watchdog

Timer (WDT)

Control

Registers

Control

Registers

Bus

Interface

Unit

1/IRQ

INT6–INT4**

Interrupt

Control Unit

Control

Registers

Refresh

Control

Unit

INT2/INTA

0/PWD**

INT1/SELECT

INT0

NMI

Demod-

Execution

Unit

PWD**

Pulse

Width

ulator

(PWD)

TMROUT0 TMROUT1

TMRIN0 TMRIN1

Timer Control

Unit

01 2 0 1

Max Count B

Registers

Max Count A

Registers

16-Bit Coun t

Registers

Control

Registers

DRAM

Control

Unit

Chip-Select

Control

Registers

Unit

DRQ0/INT5** DRQ1/INT6**

20-Bit Destination

FT

Asynchronous

Asynchronous

RA

DMA

Unit

20-Bit Source

Pointers

Pointers

16-Bit Coun t

Registers

Control

Registers

Control

Control

Registers

Serial Port 0

Serial Port 1

Unit

Registers

PIO

PIO31–

PIO0*

TXD0

RXD0

RTS0/RTR0

CTS0/ENRX0

TXD1

RXD1

RTS1/RTR1**

CTS1/ENRX1**

RD

WHB

A19–A0

D

AD15–AD0

Notes:

*All PIO signal s are shared with o the r physical pins. Se e th e pin de sc riptions beginning on page 21 and Table 2 on page 29 for

information on shared functions.

1/RTR1 and CTS1/ENRX1 are multiplexed with PCS3 and PCS2, respectively. See the pin descriptions beginning on

** RTS

page 21.

2 Am186ED/EDLV Microcontrollers

ALE

BHE

WLB

WR

/ADEN

LCS/ONCE0/RAS0

MCS3/RAS1

MCS

MCS1/UCAS

2/LCAS

MCS0

PCS

UCS

PCS6/A2

PCS

3–PCS0**

/ONCE1

5/A1

Page 3

PRELIMINARY

,

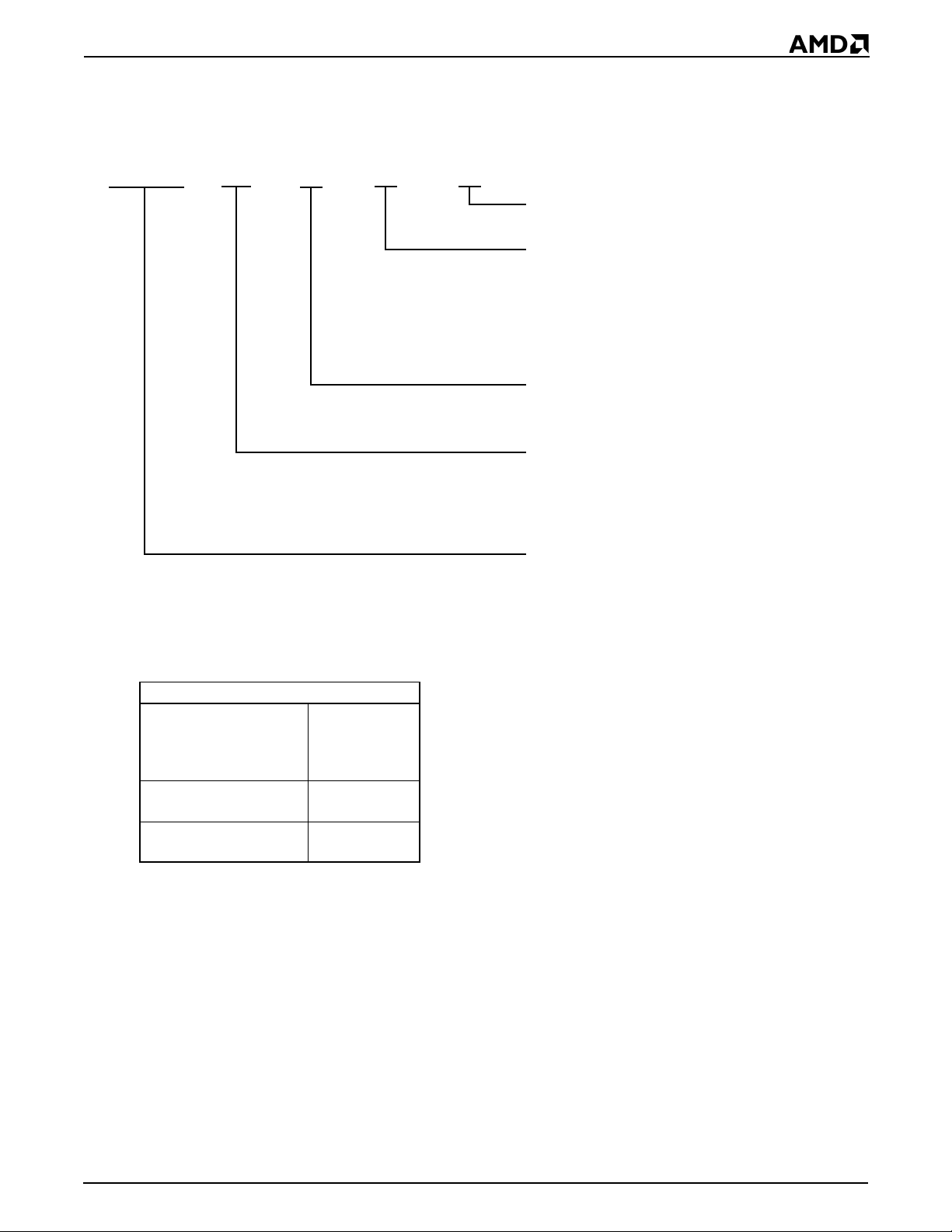

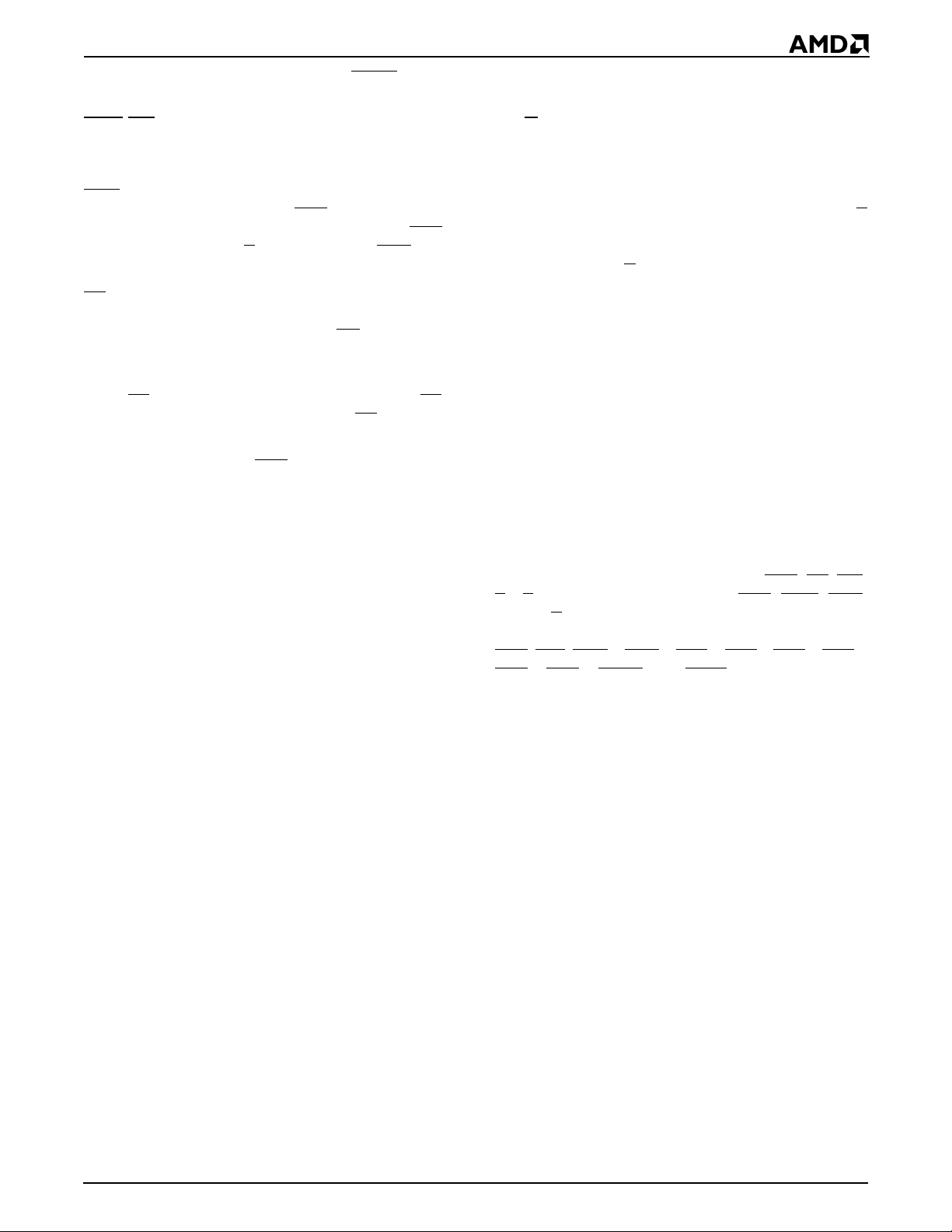

ORDERING INFORMATION

Standard Products

AMD standard products are available in s everal package s and operating ranges. The order num ber (valid combi nation) is formed

by a combination of the elements below.

-40 K C \WAm186TMED/EDLV

LEAD FORMING

\W=Trimmed and Formed

TEMPERAT URE RANGE

C= ED Commercial (T

C = EDLV Commercial (T

I = ED Industrial (T

where: TC= case temperature

where: T

PACKAGE TYPE

V=100-Pin Thin Quad Flat Pack (TQFP)

K=100-Pin Plastic Quad Flat Pack (PQFP)

SPEED OPTION

–20 = 20 MHz

–25 = 25 MHz

–33 = 33 MHz

–40 = 40 MHz

= ambient temperature

A

=0°C to +100°C)

C

=0°C to +70°C)

C

=–40°C to +85°C)

A

Valid Combinations

Am186ED–20

Am186ED–25

Am186ED–33

Am186ED–40

Am186ED–20

Am186ED–25

Am186EDLV–20

Am186EDLV–25

Note:

D

The industrial version of the Am186ED is

offered only in the PQFP package.

VC\W or

KC\W

RA

1

KI\W

VC\W or

KC\W

DEVICE NUMBER/DESCRIPTION

Am186ED = High-Performance, 80C186-Compatible,

16-Bit Embedded Microcontroller

Am186EDLV = High-Performance, 80L186-Compatible

Low-Voltage, 16-Bit Embedded Microcontroller

V alid combinations list c onfigurations planned to be

supported in volume for this device. Consult the

local AMD sales office to confirm availability of

specific valid combinations and to check on newly

released combinations.

Note: The industrial version of the Am186ED as

well as the Am186EDL V are available in 20 and 25

MHz operating frequencies only.

The Am186ED and Am186EDLV microcon trollers

are all functionally the same except for their DC

characteristics and available frequencies.

Note: There is no 188 version of the Am186ED/

EDLV. The same 8-bit external bus capabilities

can be achieved us ing the 8-bit bo ot capability and

programmable bus sizing options.

FT

Valid Combinations

Am186ED/EDLV Microcontrollers 3

Page 4

PRELIMINARY

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS ........................................................................................... 1

GENERAL DESCRIPTION .......................................................................................................... 1

AM186ED/EDLV MICROCONTROLLERS BLOCK DIAGRAM ................................................... 2

ORDERING INFORMATION ....................................................................................................... 3

Standard Products ........................................................................................................... 3

RELATED AMD PRODUCTS .............................................................................................. ........ 9

E86 Family Devices ...................................................................................................... 9

Related Documents . ........................... .. .. ............. ... .. ............. .. ... ............. .. .. .................. 10

Third-Party Development Support Products .................................................................. 10

Customer Serv i ce ...... ........................... .. .. .............. .. .. ........................... .. .. ............. .. ... .. 10

KEY FEATURES AND BENEFITS ............................. .. .. .. .................................. .. .. .. .. ............... 10

Application Co n s id e ra t io n s ........ .......................... ... .. ............. .. ... ............. .. .. ............. ... .. .11

COMPARING THE AM186ED/EDLV TO THE AM186ES/ESLV MICROCONTROLLERS ........ 12

Integrated DRAM Controller ........................................................................................... 12

Enhanced Refresh Control Unit ..................................................................................... 13

Option to Overlap DRAM with PCS

Additional Serial Port Mode for DMA Support of 9-bit Protocols .................................... 13

Option to Boot from 8- or 16-bit Memory ....................................................................... 13

Improved External Bus Master Support ......................................................................... 13

PSRAM Controller Removed ......................................................................................... 13

TQFP CONNECTION DIAGRAMS AND PINOUTS .................................................................. 14

Top Side View—100-Pin Thin Quad Flat Pack (TQFP) .............................. .. .. ............... 14

TQFP PIN DESIGNATIONS ....................................................................................................... 15

Sorted by Pin Number .................................................................................................... 15

Sorted by Pin Name ....................................................................................................... 16

PQFP CONNECTION DIAGRAMS AND PINOUTS .................................................................. 17

Top Side View—100-Pin Plastic Quad Flat Pack (PQFP) .............................................17

PQFP PIN DESIGNATIONS................................................................................ .. .. .. .. ............... 18

Sorted by Pin Number .................................................................................................... 18

Sorted by Pin Name ....................................................................................................... 19

LOGIC SYMBOL—AM186ED/EDLV MICROCONTROLLERS ................................................. 20

PIN DESCRIPTIONS ................................................................................................................. 21

Pins That Are Used by Emulators .................................................................................. 21

Pin Terminology ............................................................................................................. 21

A19–A0 (A19/PIO9, A18/PIO8, A17/PIO7) .................................................................... 21

AD15–AD8 ..................................................................................................................... 21

AD7–AD0 ....................................................................................................................... 21

ALE ................................................................................................................................ 21

ARDY ............................................................................................................................. 22

D

/ADEN ...... ......... ....... ......... ......... ...... ......... ......... ......... ...... ......... ......... ......... ...... ..... 22

BHE

CLKOUTA ...................................................................................................................... 22

CLKOUTB ...................................................................................................................... 22

0/ENRX0/PIO21 ..... ........... ........... ......... ........... ........... ......... ........... ........... ........... .. 2 2

CTS

/DS/PIO5 ................................................................................................................ 23

DEN

DRQ0/INT5/PIO12 ......................................................................................................... 23

DRQ1/INT6/PIO13 ......................................................................................................... 23

/PIO4 ..................................................................................................................... 23

DT/R

GND ............................................................................................................................... 23

HLDA ............................................................................................................................. 23

HOLD ............................................................................................................................. 23

INT0 ............................................................................................................................... 24

INT1/SELECT

................................................................................................................ 24

RA

............................................................................... 13

FT

4 Am186ED/EDLV Microcontrollers

Page 5

PRELIMINARY

INT2/INTA0/PWD/PIO31 ... ............. .............. ............. ........... ............. ............. .............. .. 24

INT3/INTA

INT4/PIO30 .................................................................................................................... 25

LCS

MCS

MCS

MCS2

MCS3

NMI ................................................................................................................................ 26

PCS

PCS

PCS

PCS

PCS

PIO31–PIO0 (Shared) ............................................................................... .. .. .. ............... 28

............. .................... .................... ................. .................... .................... .................. .. 28

RD

RES

RTS

RXD0/PIO23 .................................................................................................................. 30

RXD1/PIO28 .................................................................................................................. 30

2/BTSEL ...................................................................................................................... 30

S

1–S0 ............................................................................................................................ 30

S

S6/CLKDIV

SRDY/PIO6 .................................................................................................................... 30

TMRIN0/PIO 11 ........... .............. ............. ........... ............. .............. ............. ........... ........... 31

TMRIN1/PIO0 ................................................................................................................ 31

TMROUT0/PIO10 .......................................................................................................... 31

TMROUT1/PIO1 ............................................................................................................ 31

TXD0/PIO22 ......... ......... ........ ....... ......... ......... ......... ...... ......... ......... ....... ........ ......... ....... 31

TXD1/PIO27 ......... ......... ........ ....... ......... ......... ......... ...... ......... ......... ....... ........ ......... ....... 31

UCS

/PIO26 ...................................................................................................................... 31

UZI

................................................................................................................................ 31

V

CC

WHB

WLB

................................................................................................................................. 32

WR

X1 ......... ....... .... ....... ....... ...... ..... ...... ....... .... ....... ....... ...... ..... ...... ....... ....... .... ....... ...... ..... .. 32

X2 ......... ....... .... ....... ....... ...... ..... ...... ....... .... ....... ....... ...... ..... ...... ....... ....... .... ....... ...... ..... .. 32

FUNCTIONAL DESCRIPTION ..................................... ............................................... .............. 33

Memory Organization ..................................................................................................... 33

I/O Space ....................................................................................................................... 33

BUS OPERATION ...................................................... ...... .........................................................34

BUS INTERFACE UNIT ............................... .. ........................ .. ............................................... ... 36

Nonmultiplexed Address Bus ......................................................................................... 36

DRAM Address Multiplexing .......................................................................................... 36

Programmable Bus Sizing ............................................................................................. 37

Byte-Write Enables ........................................................................................................ 37

Data Strobe Bus Interface Option .................................................................................. 37

DRAM INTERFACE ................................................................................................................... 37

PERIPHERAL CONTROL BLOCK ............................... .. .. .................................. .. .. .. .. ............... 38

Reading and Writing the PCB .................................. .. .. .. .. .................................. .. .. .. .. .... 38

1/IRQ ....... ......................... ...................... ........................ ........................ ....... 24

/ONCE0/RAS0 ........................................................................................................ 25

0/PIO14 ...... ................. .................... .................... .................... .................. ............. 25

1/UCAS/PIO15 ... .................... .................... .................. .................... .................... .. 25

/LCAS/PIO24 ....................................................................................................... 25

/RAS1/PIO25 ....................................................................................................... 26

1/PIO17, PCS0/PIO16 ........ .................... ................. .................... .................... ....... 26

2/CTS1/ENRX1/PIO18 ........................................................................................... 27

3/RTS1/RTR1/PIO19 ............ ................................................................ .................. 27

5/A1/PIO3 ............................................................................................................... 27

6/A2/PIO2 ............................................................................................................... 28

............. ......... ......... ...... ......... ......... ....... ........ ......... ......... ....... ......... ........ ......... ....... 28

0/RTR0/PIO20 ........................................................................................................ 30

2/PIO29 ....................................................................................................... 30

FT

/ONCE1 .................................................................................................................. 31

............ ......... ......... ...... ......... ......... ....... ........ ......... ......... ....... ......... ........ ......... ....... 31

............................................................................................................................... 32

RA

D

Am186ED/EDLV Microcontrollers 5

Page 6

PRELIMINARY

CLOCK AND POWER MANAGEMENT .................................................................................... 40

Phase-Locked Loop ...................................... ................................................................. 40

Crystal-Driven Clock Source .......................................................................................... 40

External Source Clock ................................................................................................... 41

System Clocks ............................................................................................................... 41

Power-Save Op e ra t io n ........ .............. .. .. .......................... ... .. ............. .. ... ............. .. .. ....... 4 1

Initialization and Processor Reset ................. .. ........................ .. ....................... .............. 41

Reset Configuration Register ......................................................................................... 41

CHIP-SELECT UNIT .................................................................................................................. 42

Chip-Select Timing ......................................................................................................... 42

Ready and Wait-State Programming ............................................................................. 42

Chip-Select Overlap ....................................................................................................... 42

Upper Memory Chip Select ............................................................................................ 43

Low Memory Chip Select ............................................................................................... 43

Midrange Memory Chip Selects ..................................................................................... 43

Peripheral Chip Selects ....................... ....................................................................... ... 43

REFRESH CONTROL UNIT ...................................................................................................... 44

INTERRUPT CONTROL UNIT ............. .. ............................................... .................................... 44

TIMER CONTROL UNIT ............................................................................................................ 45

Watchdog Timer ............................................................................................................. 45

PULSE WIDTH DEMODULATION ............................................................................................ 45

DIRECT MEMORY ACCESS .................................................................................................... 46

DMA Operation ...... .. .. .............. .. .. ............. ... .. ............. .. .. ........................... .. .. .............. .. 46

DMA Channel Control Registers ....................................................................................47

DMA Priority ........................ .. ... ............. .. .. ........................... .. .. .............. .. .. ............. .. ... .. 47

ASYNCHRONOUS SERIAL PORTS ............................................ .. ...... ..................................... 47

DMA Transfers through the Serial Port ............... ....................... .................................... 48

PROGRAMMABLE I/O (PIO) PINS ........................................................................................... 48

ABSOLUTE MAXIMUM RATINGS ............................................................................................ 49

OPERATING RANGES ............................... .. ............................................................................ 49

DC CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL OPERATING RANGES . 49

CAPACITANCE ......................................................................................................................... 50

POWER SUPPLY CURRENT ............................................................... ...... .............................. 50

THERMAL CHARACTERISTICS ............................................................................................... 51

TQFP Package ................................................. .. .. .................................. .. .. .. .. ............... 51

Typical Ambient Temperatures....................................................................................... 52

COMMERCIAL AND INDUSTRIAL SWITCHING CHARACTERISTICS AND WAVEFORMS .. 57

Key to Switchin g Wa v e fo r m s ..... .. .. .............. .. .. ........................... .. .. ............. .. ... ............. 57

Alphabetical Key to Switching Parameter Symbols ....................................................... 58

Numerical Key to Switching Parameter Symbols ........................................................... 61

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................. 65

READ CYCLE WAVEFORMS ................................................................................................... 66

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................. 68

WRITE CYCLE WAVEFORMS ..................................... ............................................... .............. 69

D

OPERATING RANGES ............................................................................................... 64

Read Cycle (20 MHz and 25 MHz) ................................................................................ 64

Read Cycle (33 MHz and 40 MHz) ................................................................................ 65

OPERATING RANGES ............................................................................................... 67

Write Cycle (20 MHz and 25 MHz) ................................................................................67

Write Cycle (33 MHz and 40 MHz) ................................................................................68

RA

FT

6 Am186ED/EDLV Microcontrollers

Page 7

PRELIMINARY

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

OPERATING RANGES ............................................................................................... 70

DRAM ............................................................................................................................ 70

DRAM Read Cycle Timing with No-Wait States ............................................................ 71

DRAM Read Cycle Timing with Wait State(s) ................................................................ 71

DRAM Write Cycle Timing with No-Wait States ............................................................. 72

DRAM Write Cycle Timing With Wait State(s) ............................................................... 72

DRAM CAS

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

OPERATING RANGES ............................................................................................... 74

Interrupt Acknowledge Cycle (20 MHz and 25 MHz) ....................................... .............. 74

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................. 75

Interrupt Acknowledge Cycle (33 MHz and 40 MHz) ....................................... .............. 75

INTERRUPT ACKNOWLEDGE CYCLE WAVEFORMS ........................................................... 76

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

OPERATING RANGES ............................................................................................... 77

Software Halt Cycle (20 MHz and 25 MHz) ................................................................... 77

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................. 77

Software Halt Cycle (33 MHz and 40 MHz) ................................................................... 77

SOFTWARE HALT CYCLE WAVEFORMS .............................................................................. .78

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

OPERATING RANGES ............................................................................................... 79

Clock (20 MHz and 25 MHz) .......................................................................................... 79

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................. 80

Clock (33 MHz and 40 MHz) .......................................................................................... 80

CLOCK WAVEFORMS .............................................................................................................. 81

Clock Waveforms—Active Mode ................................................................................... 81

Clock Waveforms—Power-Save Mode .......................... ....................... .........................81

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

OPERATING RANGES ............................................................................................... 82

Ready and Peripheral (20 MHz and 25 MHz) ................................................................ 82

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................. 82

Ready and Peripheral (33 MHz and 40 MHz) ................................................................ 82

SYNCHRONOUS, ASYNCHRONOUS, AND PERIPHERAL WAVEFORMS ............................ 83

Synchronous Ready Waveforms ................................................................................... 83

Asynchronous Ready Waveforms ................................................ .................................. 83

Peripheral Waveforms ....................... ............................................................................ 83

SWITCHING CHARACTERISTICS OVER COMMERCIAL AND INDUSTRIAL

OPERATING RANGES ............................................................................................... 84

Reset and Bus Hold (20 MHz and 25 MHz) ............................ ....................................... 84

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES ................ 84

RESET AND BUS HOLD WAVEFORMS ...................................... .. .. .. .. .................................. .. .85

TQFP PHYSICAL DIMENSIONS ............................................................................................... 87

PQFP PHYSICAL DIMENSIONS ..................................................... .. .. .................................... .88

D

Reset and Bus Hold (33 MHz and 40 MHz) ............................ ....................................... 84

Reset Waveforms .......................................................................................................... 85

Signals Related to Reset Waveforms .............................. ....................... .......................85

Bus Hold Wavefo rms—Entering .... ... ............. .. .. ............. ... .. .......................... ... .. ........... 86

Bus Hold Waveforms—Leaving ..................................................................................... 86

-before-RAS Cycle Timing .......................................................................... 73

FT

RA

Am186ED/EDLV Microcontrollers 7

Page 8

PRELIMINARY

LIST OF FIGURES

Figure 1 Am186ED Microcontroller Example System Design .............................................. 11

Figure 2 80C186 Microcontroller Example System Design ................................................. 12

Figure 3 Two-Component Address ......................................................................................33

Figure 4 16-Bit Mode—Normal Read and Write Operation ................................................. 34

Figure 5 16-Bit Mode—Read and Write with Address Bus Disable In Effect ....................... 35

Figure 6 8-Bit Mode—Normal Read and Write Operation ................................................... 35

Figure 7 8-Bit Mode—Read and Write with Address Bus Disable in Effect ......................... 36

Figure 8 Am186ED/EDLV Microcontrollers Oscillator Configurations ................................. 40

Figure 9 Clock Organization ................................................................................................ 41

Figure 10 DMA Unit Block Diagram ....................................................................................... 47

Figure 11 Typical I

Figure 12 Typical I

Figure 13 Thermal Resistance(°C/Wat t) ......... ........... ......... ........... ........... ........... ......... ......... 51

Figure 14 Thermal Character is tics Equations .............. ........................... .. .. .............. .. .. ......... 51

Figure 15 Typical Ambient Temperatures for PQFP with a 2-Layer Board ............................ 53

Figure 16 Typical Ambient Temperatures for TQFP with a 2-Layer Board ............................ 54

Figure 17 Typical Ambient Temperatures for PQFP with a 4-Layer to 6-Layer Board ..........55

Figure 18 Typical Ambient Temperatures for TQFP with a 4-Layer to 6-Layer Board ........... 56

LIST OF TABLES

Versus Frequency for Am186EDLV Microcontroller .............................50

cc

Versus Frequency for Am186ED Microcontroller ................................. 50

cc

Table 1 Data Byte Encoding ............................................................................................... 22

Table 2 Numeric PIO Pin Designations ............................ ............................................... ... 29

Table 3 Alphabetic PIO Pin Designations ........................................................................... 29

Table 4 Bus Cycle Encoding ............................................................................................... 30

Table 5 Segment Register Selection Rules ........................................................................ 33

Table 6 DRAM Pin Interface ................................ .. .. .. .................................. .. .. .. .. ............... 37

Table 7 Programming the Bus Width of Am186ED/EDLV Microcontrollers ........................ 37

Table 8 Peripheral Control Block Register Map ........................................... .......................39

Table 9 Am186ED/EDLV Microcontrollers Maximum DMA Transfer Rates ....................... 46

Table 10 Typical Power Consumption Calculation fo r the Am186EDLV Microcontroller ...... 50

Table 11 Thermal Characteristics (°C/Watt) ......................................................................... 51

Table 12 Typical Power Consumption Calculation ............................................................... 52

Table 13 Junction Temperature Calculation ......................................................................... 52

Table 14 Typical Ambient Temperatures (°C) for PQFP with a 2-Layer Board .................... 53

Table 15 Typical Ambient Temperatures (°C) for TQFP with a 2-Layer Board .................... 54

Table 16 Typical Ambient Temperatures (°C) for PQFP with a 4-Layer to 6-Layer Board ... 55

Table 17 Typical Ambient Temperatures (°C) for TQFP with a 4-Layer to 6-Layer Board ... 56

RA

FT

D

8 Am186ED/EDLV Microcontrollers

Page 9

PRELIMINARY

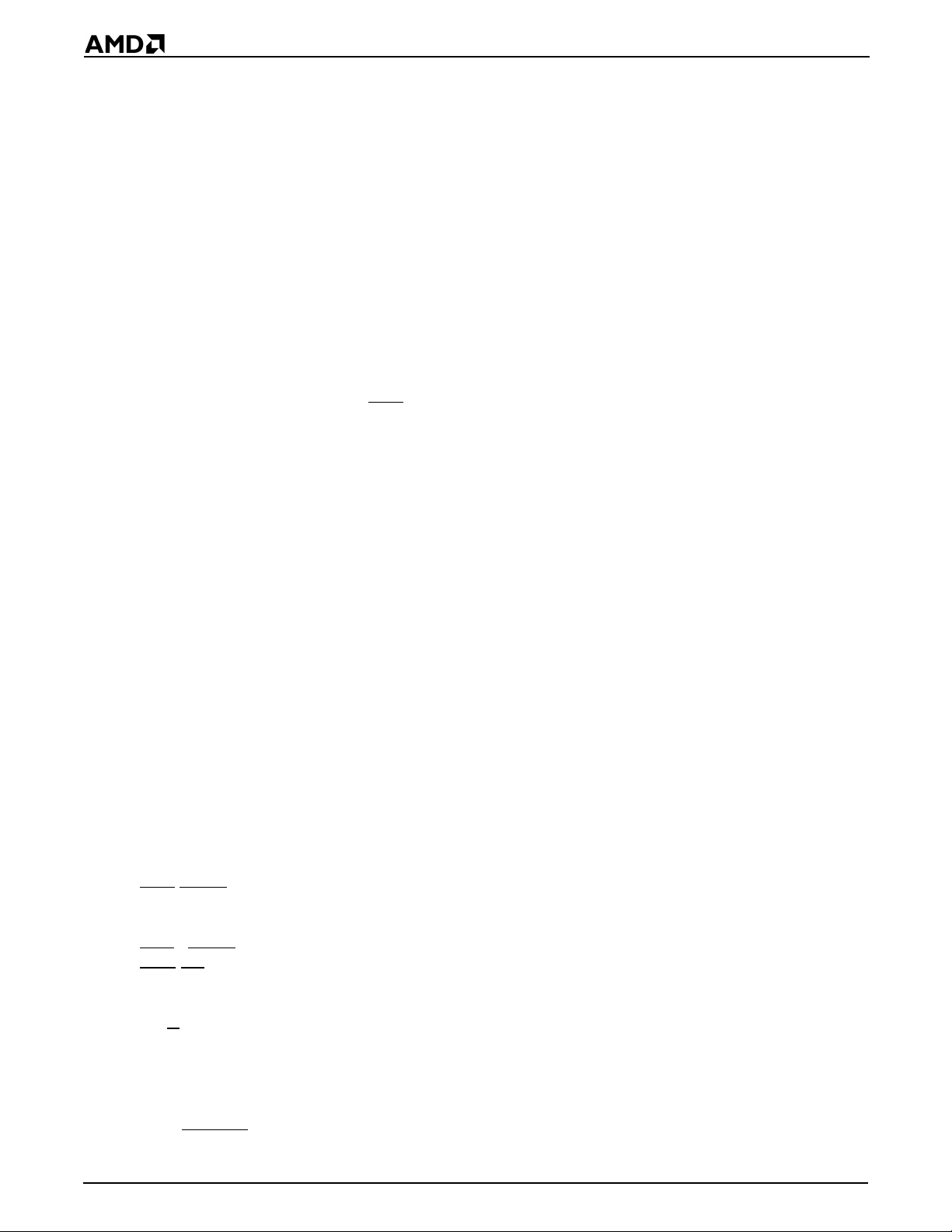

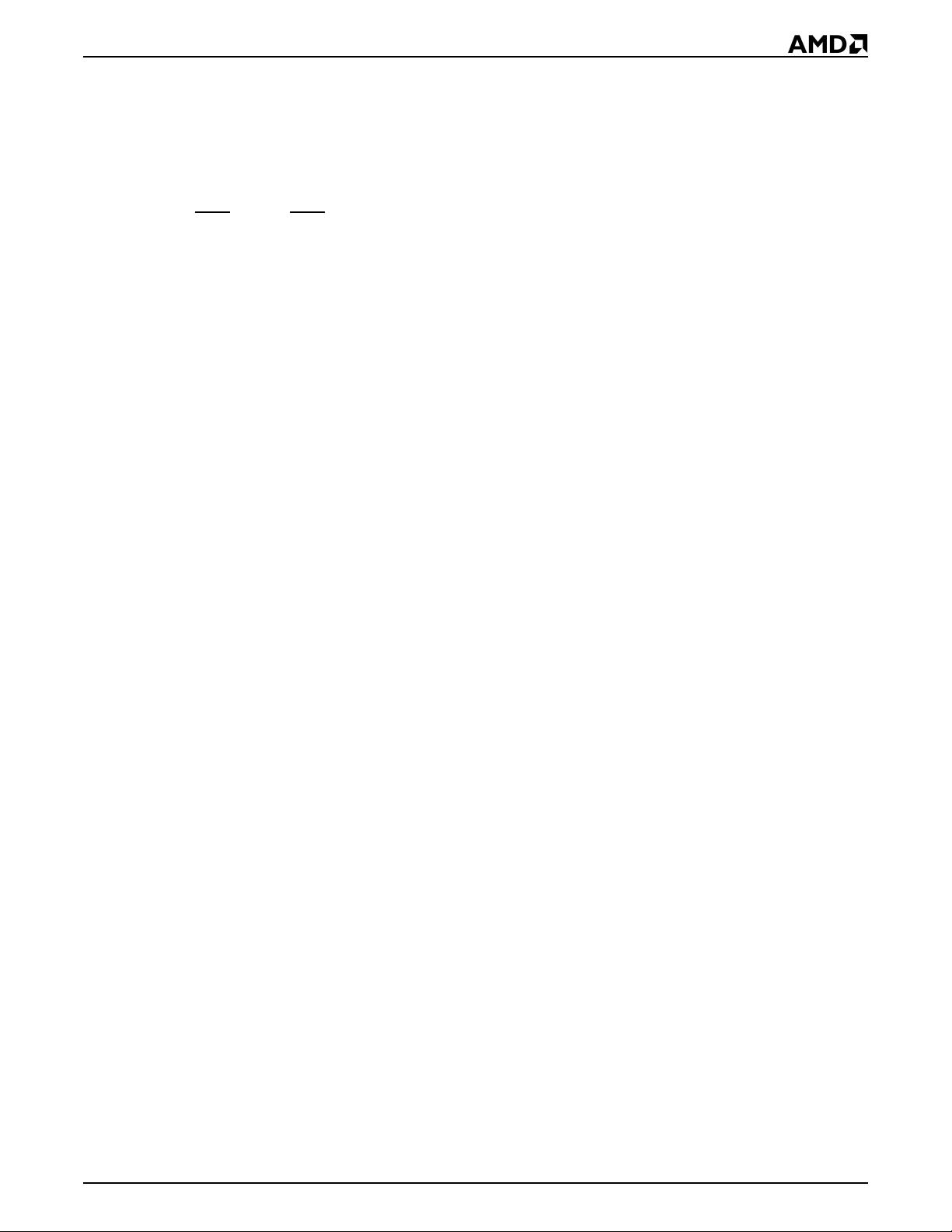

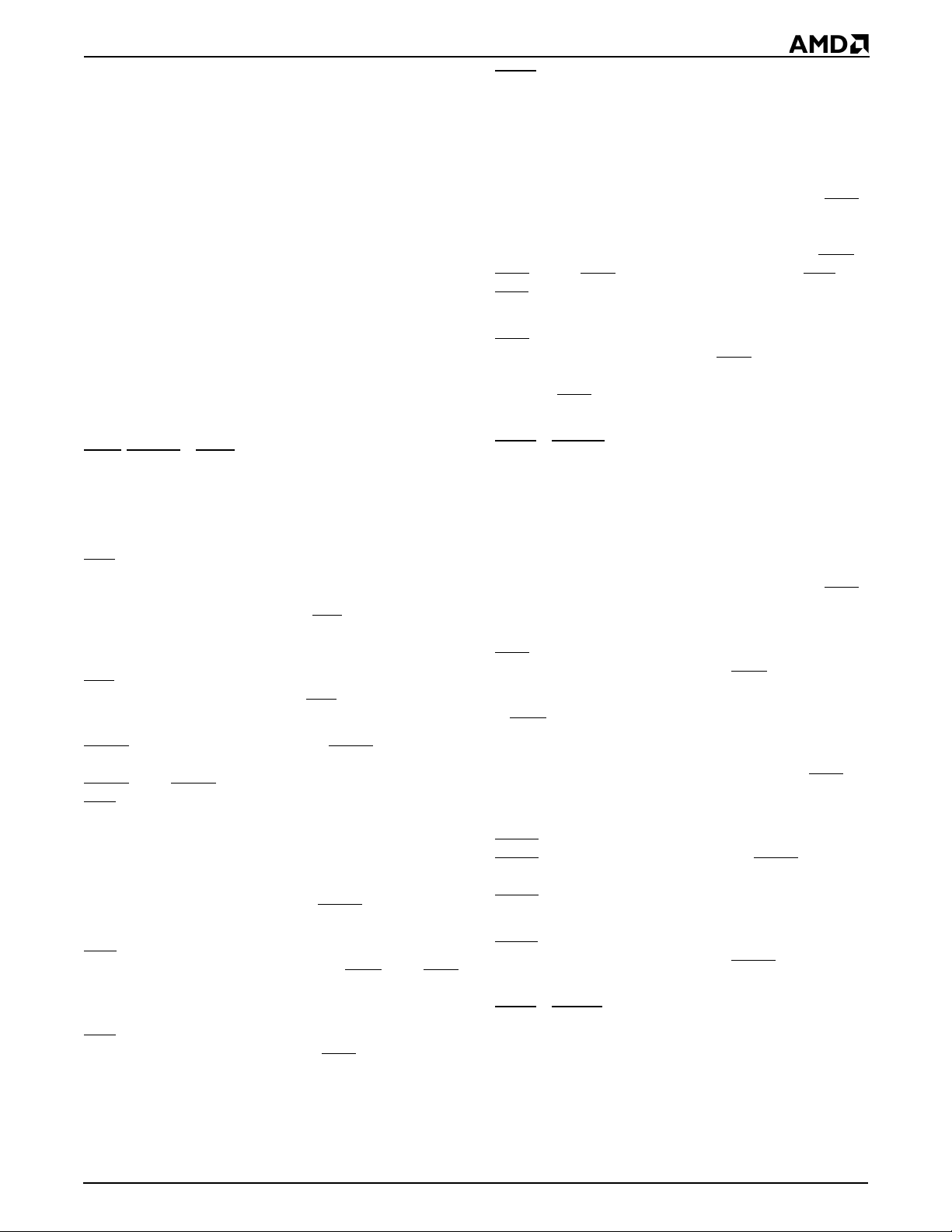

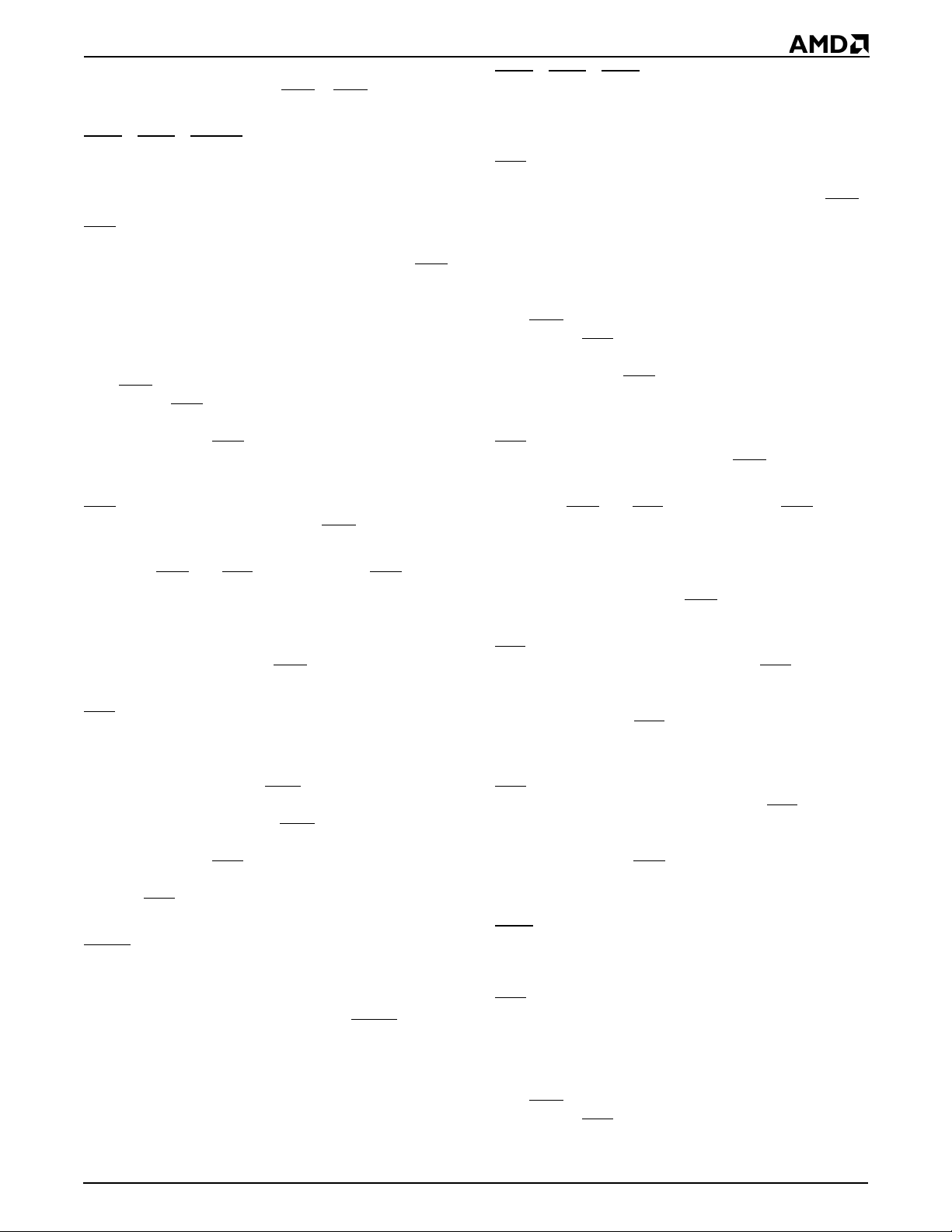

Microprocessors

AT Peripheral

Microcontrollers

186 Peripheral

Microcontrollers

Am386SX/DX

Microprocessors

ÉlanSC300

Microcontroller

80C186 and 80C188

Microcontrollers

80L186 and 80L188

Microcontrollers

The E86 Family of Embedded Microprocessors and Microcontrollers

Am486DX

Microprocessor

ÉlanSC310

Microcontroller

Am186EM and

Am188EM

Microcontrollers

Am186EMLV &

Am188EMLV

Microcontrollers

™

K86

Future

ÉlanSC400

Microcontroller

Am186ES and

Am188ES

Microcontrollers

Am186ESLV &

Am188ESLV

Microcontrollers

Time

ÉlanSC410

Microcontroller

Am186ER and

Am188ER

Microcontrollers

Microcontroller

Am486

Future

Am186ED

32-bit Future

Am186 and

Am188 Future

RELATED AMD PRODUCTS

E86 Family Devices

Device Description

80C186 16-bit microcontroller

80C188 16-bit microcontroller with 8-bit external data bus

80L186 Low-voltage, 16-bit microcontroller

80L188 Low-voltage, 16-bit microcontroller with 8-bit external data bus

Am186EM High-performance, 80C186-compatible, 16-bit embedded microcontroller

Am188EM High-performance, 80C188-compatible, 16-bit embedded microcontroller with 8-bit external data bus

Am186EMLV High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller

Am188EMLV High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit

Am186ES High-performance, 80C186-compatible, 16-bit embedded microcontroller

Am188ES High-performance, 80C188-compatible, 16-bit embedded microcontroller with 8-bit external data bus

Am186ESLV High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller

Am188ESLV High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit

Am186ED High-performance, 80C186- and 80C188-compatible, 16-bit embedded microcontroller with 8- or 16Am186EDLV High-performance, 80C186- and 80C188-compatible, low-voltage, 16-bit embedded microcontroller

Am186ER High-performance, 80C186-compatible, low-voltage, 16-bit embedded microcontroller with 32 Kbyte

Am188ER High-performance, 80C188-compatible, low-voltage, 16-bit embedded microcontroller with 8-bit

™

Élan

SC300 High-performance, highly integrated, low-voltage, 32-bit embedded microcontroller

ÉlanSC310 High-performance, single-chip, 32-bit embedded PC/AT microcontroller

ÉlanSC400 Single-chip, low-power, PC/AT-compatible microcontroller

ÉlanSC410 Single-chip, PC/AT- compatible microcontroller

Am386®DX High-performance, 32-bit embedded microprocessor with 32-bit external data bus

Am386®SX High-performance, 32-bit embedded microprocessor with 16-bit external data bus

Am486®DX High-performance, 32-bit embedded microprocessor with 32-bit external data bus

external data bus

RA

external data bus

D

bit external data bus

with 8- or 16-bit external data bus

of internal RAM

external data bus and 32 Kbyte of internal RAM

FT

Am186ED/EDLV Microcontrollers 9

Page 10

PRELIMINARY

Related Documents

The following documents provide additional

information regarding the Am186ED/EDLV

microcontrollers:

n

Am186ED/EDLV Microcontrollers User’s Manual

order # 21335

n

Am186 and Am188 Family Ins truction Set Manu al

order # 21267

n

FusionE86SM Catalog

n

E86 Family Support Tools Brief

n FusionE86 Development Tools Reference CD,

order # 21058

Third-Party Development

Support Products

The FusionE86SM Program of Partnerships for

Application Solutions prov ides the custo mer with an

array of products designed to meet critical time-tomarket needs. Products and solutions available from

the AMD FusionE86 partners include emulators,

hardware and software debuggers, board-level

products, and software development tools, among

others.

, order # 19255

, order # 20071

To download documents and software, ftp to

ftp.amd.com and log on as anonymous using your

E-mail address as a passw ord. Or via your web

browser, go to ftp://ftp.amd.com.

Questions, reques ts, and input concerning AM D’s

,

WWW pages can be sent via E-mail to

webmaster@amd.com.

,

Documentation and Literature

Free E86 family information such as data books, user’s

manuals, data sheets, application notes, the

FusionE86 Partner Solutions Catalog, and other literature is available with a s imple phone call. Intern ationally, contact your local AMD sales office for complete

E86 family literature.

Literature Ordering

(800) 222-9323 Toll-free for U.S. and Canada

(512) 602-5651 Direct dial worldwide

(512) 602-7639 fax

(800) 222-9323 AMD Facts-On-Demand™

fax information service, tollfree for U.S. and Canada

In addition, mature development tools and applications

for the x86 platform are widely available in the general

marketplace.

Customer Service

The AMD customer service network includes U.S.

offices, international offices, and a customer training

center. Expert technical assista nce is available from

the worldwide staff of AMD field application engineers

and factory support staff to answer E86 family

hardware and software development questions.

Hotline and World Wide Web Support

For answers to technical questions, AMD provides a

toll-free number for direct access to our corporate

applications hotline. Also available is the AMD World

Wide Web home page and FTP site, which provides the

latest E86 family product info rmation, including

technical informati on and data on upcoming product

releases.

For technical support questions on all E86 products, send E-mail to lpd.support@amd.com.

Corporate Applications Hotline

(800) 222-9323 Toll-free for U.S. and Canada

44-(0) 1276-803-299 U.K. and Europe hotline

World Wide Web Home Page and FTP Site

To access the AMD home page go to:

http://www.amd.com.

D

RA

KEY FEATURES AND BENEFITS

The Am186ED/EDLV microcontrollers extend the AMD

family of microcon trollers based on the indus try-standard x86 architecture. The Am186ED/EDLV microcontrollers are a higher-perfo rmance, highly integrated

version of the 80C186/188 microprocessors, offering

an attractive migration path. In addition, the Am186ED/

EDLV microcontrollers offer application-specific features that can enhance t he system functi onality of the

Am186ES/ESLV and Am188ES/ESLV microcontrollers. Upgrading to the Am186ED/EDLV microcontrollers is an attractive solution for several reasons:

n Programmable DRAM controller—Enables sys-

tem designers to take advantage of low-cost DRAM

and fully utilize the performance and flexibility of the

x86 architecture. The DRAM controller supports

zero wait-state performance with 50-ns DRAM at 40

MHz, or, if required, can be programm ed with wait

states. The Am186ED/EDLV microcontrollers provide a CAS

n Minimized total syst em cost—New and en-

hanced peripherals and on-chip system interface

logic on the Am 186ED/EDLV microcontrollers r educe the cost of existing 80C186/188 designs.

n X86 software compatibility—80C186/188-com-

patible and upward-compatible with the other members of the AMD E86 family.

FT

-before-RAS refresh unit.

10 Am186ED/EDLV Microcontrollers

Page 11

PRELIMINARY

n Enhanced performance—The Am186ED/EDLV

microcontrollers increase the perform ance of

80C186/188 systems, and the nonmultiplexed address bus offers unbuffered access to memory.

n Enhanced functionality—The enhanced on-chip

peripherals of the Am186ED/EDLV microcontrollers

include two asynchronous serial ports, 32 PIOs, a

watchdog timer, additional interrupt pins, a pulse

width demodulation option, DMA directly to and from

the serial ports, 8-bit and 16-bit p rogrammable bus

sizing, a 16-bit reset configuration register, and enhanced chip-select functionality.

Application Considerations

The integration enhance men ts of the Am186ED/EDLV

microcontrollers provide a high-perfor mance, low- system-cost solution for 16-bit embedded mic rocontroller

designs. The nonmultiplexed address bus eliminates

the need for system-s upp or t l ogic to i nte rfa ce me mory

devices, while the multiplexed address/data bus maintains the value of previously engineered, customerspecific perip herals and circuits withi n the upgraded

design.

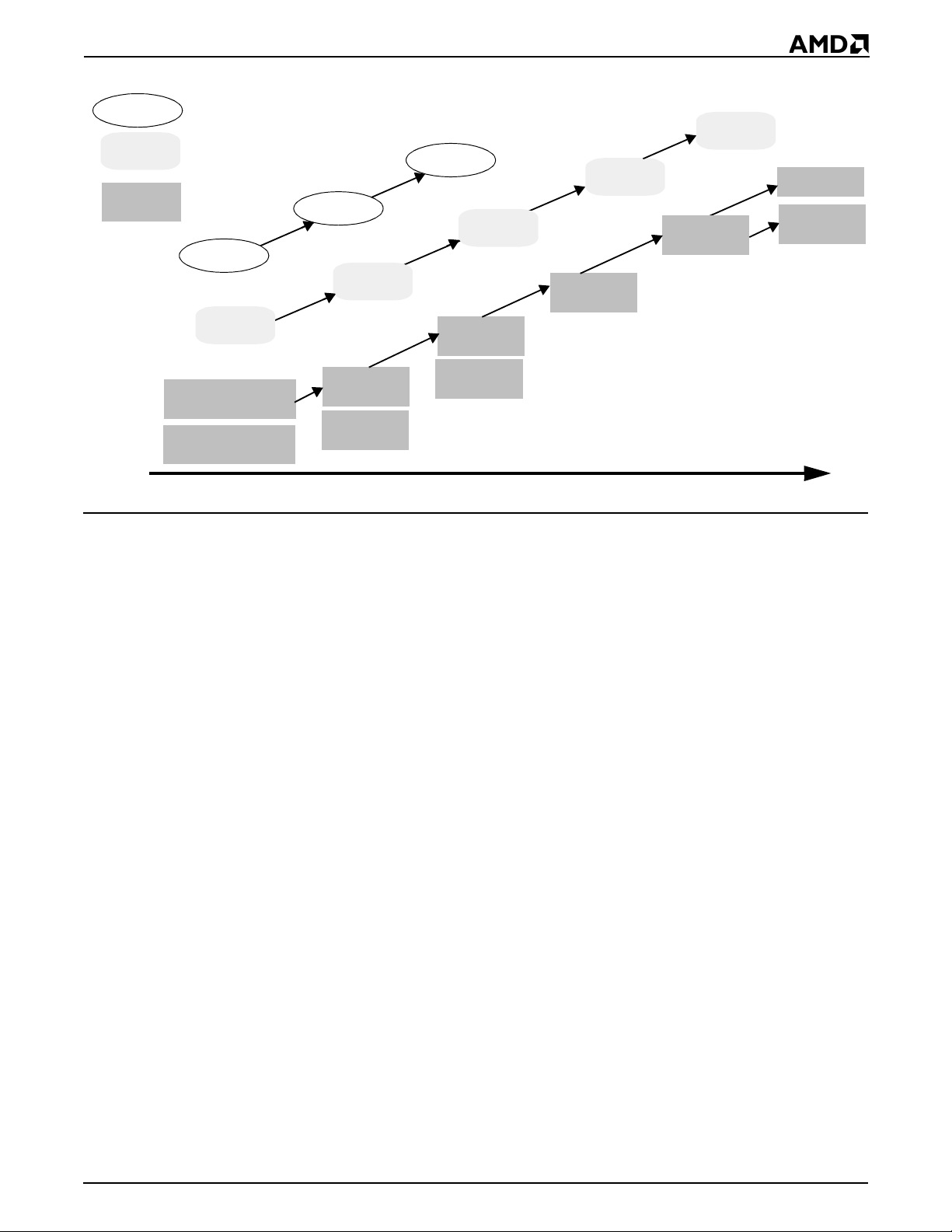

Figure 1 illust rates an example syst em design that

uses the integrated pe riphe ral s et to ac hi ev e high per formance with reduced system cost.

Clock Generation

The integrated clock generation circuitry of the

Am186ED/EDLV microcontrollers enables the use of a

1x crystal frequency. The Am186ED design in Figure 1

achieves 40-MHz CPU operation, while using a 40MHz crystal.

Memory Interface

The Am186ED/EDLV microcontrollers integrate a versatile memory controller which supports direct memory

accesses to DRA M, SR AM, Fl ash, EPROM, a nd R OM.

No external glue logic is requi re d and al l requi r ed co ntrol signals are provided. The peripheral chip selects

have been enhanced to allow them to overlap the

DRAM. This allows a sm all 1.5K portio n of the DRAM

memory space to be used for perip herals without b us

contention.

The improved memory timing specifications of the

Am186ED/EDLV microcontrollers allow for zero-waitstate operation at 40 MHz using 50-ns DRAM, 70-ns

SRAM, or 70-ns Flash memory. For 60-ns DRAM one

wait state is required at 40 MHz and zero wait states at

33 MHz and below. For 70-ns DRAM two wait states

are required at 40 MHz, one wait state at 33 MHz, and

zero wait states at 25 MHz and below. This reduces

overall system cost by enablin g the use of common ly

available memory speeds and taking advantage of

DRAM’s lower cost pe r bit over SRAM.

Figure 1 also shows a n implementation of an RS-232

console or modem communica tions port. Th e RS-232

to CMOS voltage-level converter is required for the

electrical interface with the external device.

D

RA

FT

Figure 1. Am186ED Microcontroller Example

System Design

Direct Memory Interface Example

Figure 1 illustrates the direct memory interface of the

Am186ED microcontroller. The processor’s A19–A0

bus connects to the mem ory address inputs, the AD

bus connects to the data inputs and outputs, and the

chip selects connect to the memory chip-select inputs.

The odd A1–A17 address pins connect to the DRAM

multiplexed address bus.

The RD

(OE

WR

pin. The UCAS

output connects to the DRAM Outpu t Enable

) pin for read oper ation s. Write op erations use th e

output connected to the DRAM Write Enable (WE)

and LCAS pins provide byte selection.

0-6

Am186ED/EDLV Microcontrollers 11

Page 12

PRELIMINARY

COMPARING THE Am186ES/ESLV TO THE Am186ED/EDLV MICROCONTROLLERS

Compared to the Am186ES/ESLV microcontrollers, the

Am186ED/EDLV microcontrollers have the following

additional features:

n Integrated DRAM controller

n Enhanced refresh control unit

n Option to overlap DRAM with peripheral chip select

(PCS)

n Additional serial port mode for DMA support of 9-bit

protocols

n Option to boot from 8- or 16-bit memory

n Improved external bus master support

n PSRAM controller removed

Figure 1 shows an examp le system using a 4 0-MHz

Am186ED microcontroller. Figure 2 shows a

comparable system implementation with an 80C186.

Because of its superior integration, the Am186ED/

EDLV system does not require the support devices that

are required on the 80C186 example system. In

addition, the Am186ED/EDLV microcontrollers provide

significantly bette r performance with its 4 0-MHz clock

rate.

Integrated DRAM Controller

The integrated DRAM controller directly interfaces

DRAM to support no-wait sta te DRAM interface up to

40 MHz. Wait states can be inser ted to support slower

DRAM. All signals required by the DRAM are

generated on the Am186ED/EDLV microcontrollers

and no external logic is required. The DRAM

multiplexed address p ins are connected to the odd

address pins startin g with A1 on the Am186ED/E DLV

microcontrollers to MA0 on the DRAM. The correct row

and column addresses are generated on these pins

during a DRAM access. The UCAS

to select whic h b yt e of th e D RA M i s a cce ss ed dur in g a

read or write. The RAS

DRAM which starts at 00000h in the address map and

is bounded by the lower memory size selected in the

LMCS register. RAS

DRAM which ends at FFFFFh and is bounded by the

upper memory size in the UMCS register. When RAS

is enabled, UCS

either, or both DRAM banks can be activated.

is automaticall y disabled. Neither,

0 controls the lower bank of

1 controls the up per bank of

and LCAS are used

1

25

RA

D

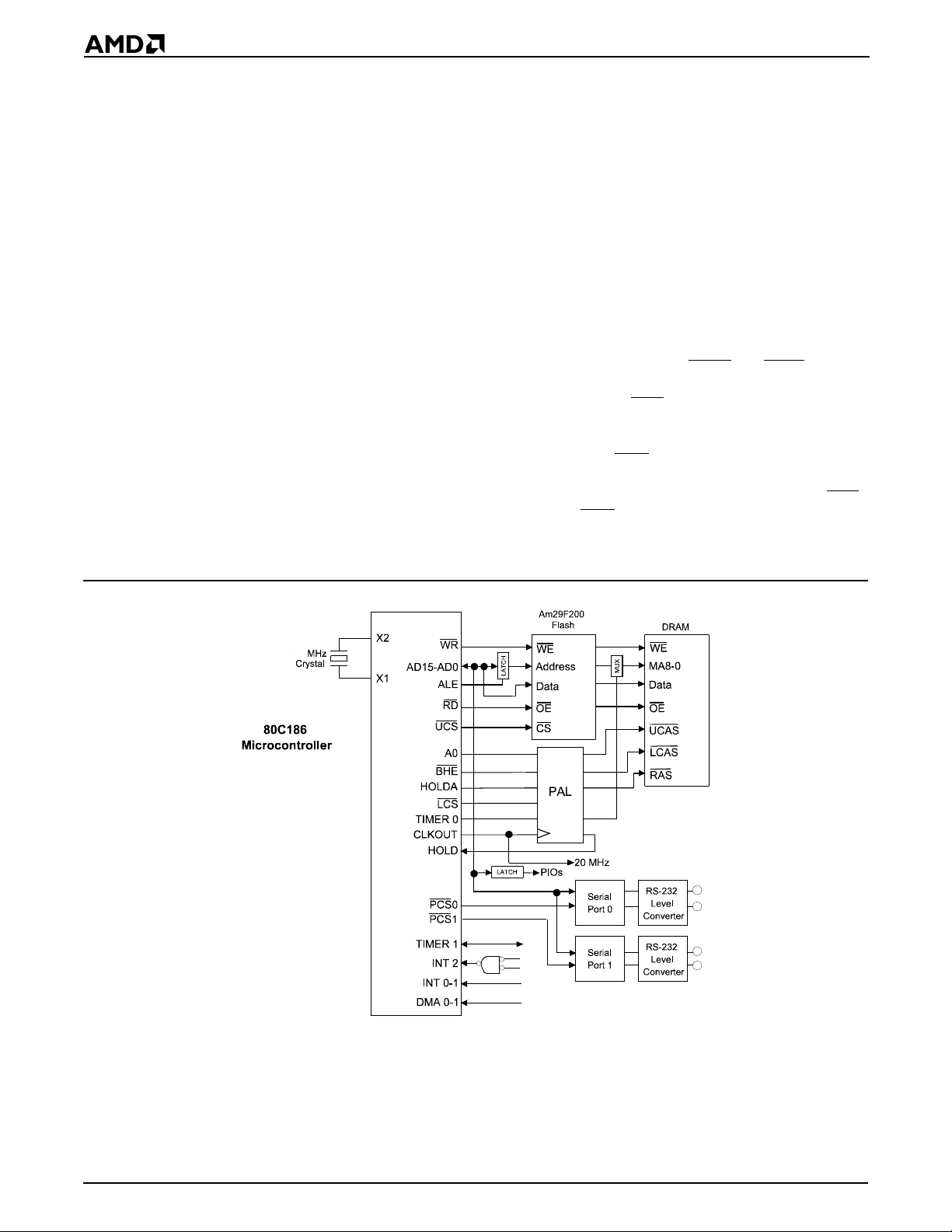

Figure 2. 80C186 Microcontroller Example System Desig n

FT

12 Am186ED/EDLV Microcontrollers

Page 13

PRELIMINARY

Enhanced Refresh Control Unit

The refresh control unit (RCU) is enhanced with two

additional bits in the refresh counter to allow for longer

refresh periods. The address generated dur ing a

refresh has been fixed to FFFFFh. When either bank of

DRAM is enabled and the RCU is enabled, a CAS

before-RAS

time period coded into the refresh counter.

Option to Overlap DRAM with PCS

The peripheral chip selects (PCS0–PCS6) can overlap

DRAM blocks with different wait states without external

or internal b us contention. The RAS

assert along with the appropriate PCS

LCAS

erroneously or driv in g the dat a bus during a read . The

must have the same or higher number of wait

PCS

states than the DRAM. The PCS

determined by the LSIZ or USIZ bus widths as

programmed in the AUXCON register.

Additional Serial Port Mode for DMA

Support of 9-bit Protocols

A mode 7 was added to the serial port which enhances

the direct memory access (DMA) support for 9-bit

protocols. Using mode 2, the serial port can be

programmed to interrupt only if the 9th bit is set,

ignoring all 9th bit cleared byte receptions. Mode 3

receives all bytes, whether the 9th bit is set or cleared.

Mode 7 also receives all bytes whether the 9th bit is set

or cleared, but now an interrupt is generated when the

9th bit is set. This allows the DMA to service all

receptions, but also allows the CPU to int er ve ne when

the trailer (9th bit set) is received. In all modes using

DMA, the interrupts other than transmitter ready and

character received interrupts can still be generated.

This allows the DMA to handle the stan dard sending

and receiving charac ters wh ile the CP U can interv ene

when a non-standard event (e.g., framing error)

occurs.

refresh will be generated based on the

0 or RAS1 will

. The UCAS and

will not assert, preventing the DRAM from writing

bus width will be

RA

entire memor y map can be se t to 16-bit or 8-b it or

mixed between 8-bit and 16-bit based on the USIZ,

LSIZ, MSIZ, and IOSIZ bits in the AUXCON register.

Improved External Bus Master Support

When the bus is arbitrated away from the Am186ED/

-

EDLV microcontrollers usi ng the HOLD pin, the chip

selects are dr iven High (negated ) and then held H igh

with an internal ~10-koh m pullup. Thi s allows exter nal

bus masters to assert the chip selects by externally

pulling them L ow, without having to co mbine the chi p

selects from the Am186ED/EDLV microcontrollers and

the external bus master in logic external to the

Am186ED/EDLV microcontrollers. Th is internal pullup

is activated for any bus arbitration, even if the pin is

being used as a PIO input.

PSRAM Controller Removed

The PSRAM mode found on the A m186ES/ESLV

microcontrollers h as been remov ed and replace d with

a DRAM controller. This includes removal of the variant

PSRAM LCS

timing and refresh strobe on MCS3.

FT

Option to Boot from 8- or 16-bit Memory

The Am186ED/EDLV microcontrollers can boot from 8or 16-bit-wide non-volatile memory, based on the state

of the S

floating, an internal pullup sets the boot mode option to

16-bit. If S

reset, the boot mode option is for 8-bit. The status of

2/BTSEL pin is latched on the rising edge of reset.

the S

If the 8-bit boot option is selected, the width of the

memory region assoc iated with UCS

in the AUXCON register. This allows for cheaper 8-bitwide memory to be used for booting the

microcontroller, while speed-critical code and data can

be executed from 16-bit-wide lower memory. Eight-bit

or 16-bit-wide peripher als can be used i n the memory

area between LCS

D

2/BTSEL pin. If S2/BTSEL is pulled High or left

2/BTSEL is pulled resistiv ely Low during

can be changed

and UCS or in the I/O s pace. The

Am186ED/EDLV Microcontrollers 13

Page 14

PRELIMINARY

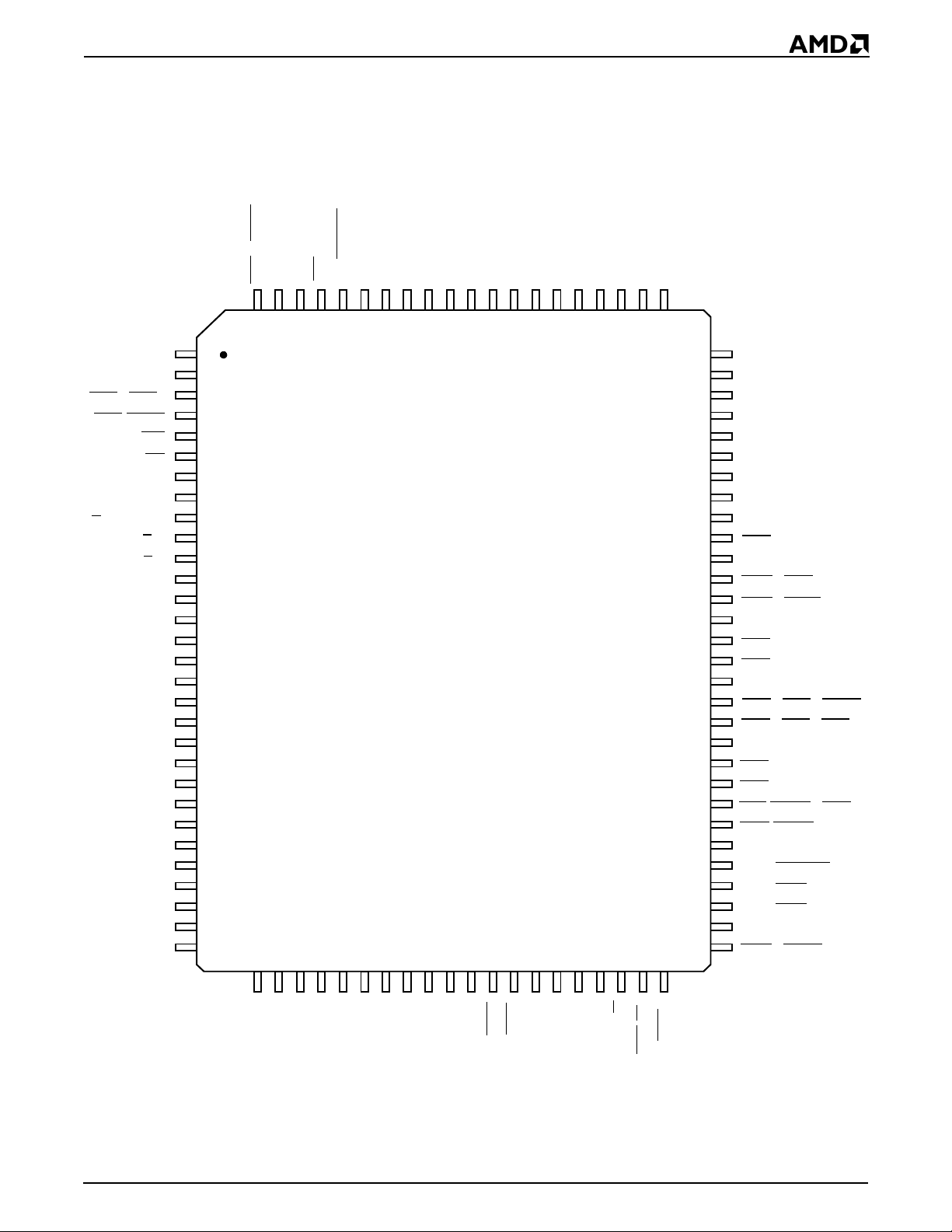

TQFP CONNECTION DIAGRAMS AND PINOUTS

Am186ED/EDLV Microcontrollers

Top Side View—100-Pin Thin Quad Flat Pack (TQFP)

2/LCAS

AD0

AD8 2

AD1 3

AD9 4

AD2 5

AD10 6

AD3 7

AD11 8

AD4 9

AD12 10

AD5 11

GND GND

AD13 13

AD6 14

V

AD14 16

AD7 17

AD15 18

S6/CLKDIV2

UZI

TXD1 21

RXD1 22

CTS0/ENRX0

RXD0 24

TXD0 25

99 DRQ1/IN T6

98 TMRIN0

97 TMROUT0

96 TMROUT1

95 TMRIN194939291908988878685848382818079 INT0

Am186ED/EDLV Microcontrollers

RA

CC

12

15

19

20

23

100 DRQ0/INT5

1

D

272829

3/

GND

MCS RAS1

RES

323334

MCS

35

1

0

CC

V

PCS

37

PCS

38

GND

/RTS1/RTR1

/CTS1/ENRX1

3

2

CC

PCS

PCS

V

40

41

/PWD

0

1/IRQ

ONCE

6/A2

5/A1

/0/RAS0

PCS

PCS

LCS

FT

44

SELECT

INTA

/1

UCS ONCE

INTA

78 INT1/

77 INT2/

76 INT3/

75 INT4

74

73

72

71

70 NMI

69 SRDY

68 HOLD

67 HLDA

66

65

64

63 A0

62 A1

61

60 A2

59 A3

58 A4

57 A5

56 A6

55 A7

54 A8

53 A9

52 A10

51 A11

MCS

MCS0

DEN/DS

DT/R

WLB

WHB

V

CC

1/UCAS

CC

X1 36

GND

X2

V

CLKOUTA 39

GND

CLKOUTB

S1

RD

WR

ALE 30

ARDY 31

BHE/ADEN

RTS0/RTR0 26

Note:

Pin 1 is marked for orientation.

14 Am186ED/EDLV Microcontrollers

S0

S2/BTSEL

CC

V

A19 42

A18 43

A17 45

A16 46

A15 47

A14 48

A13 49

A12 50

Page 15

PRELIMINARY

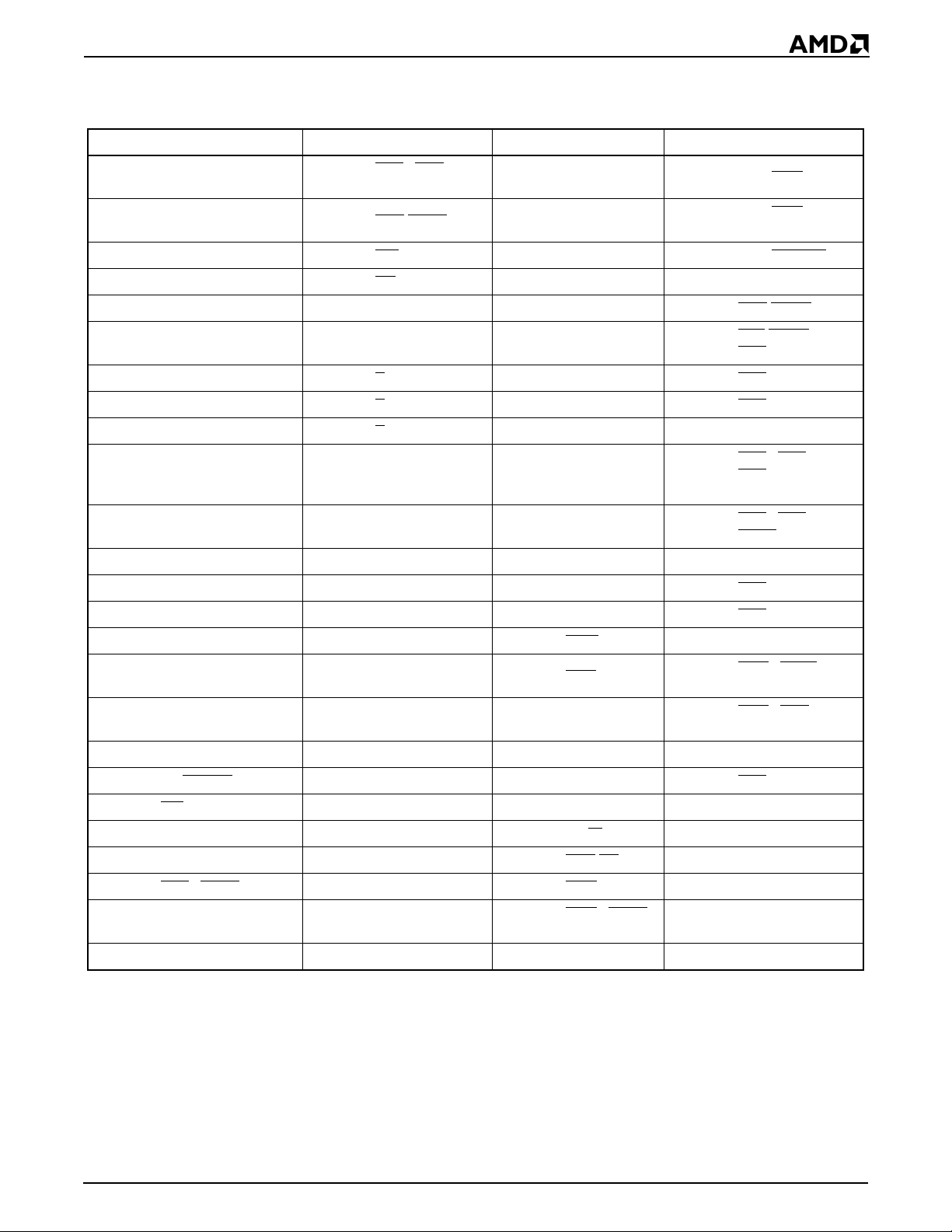

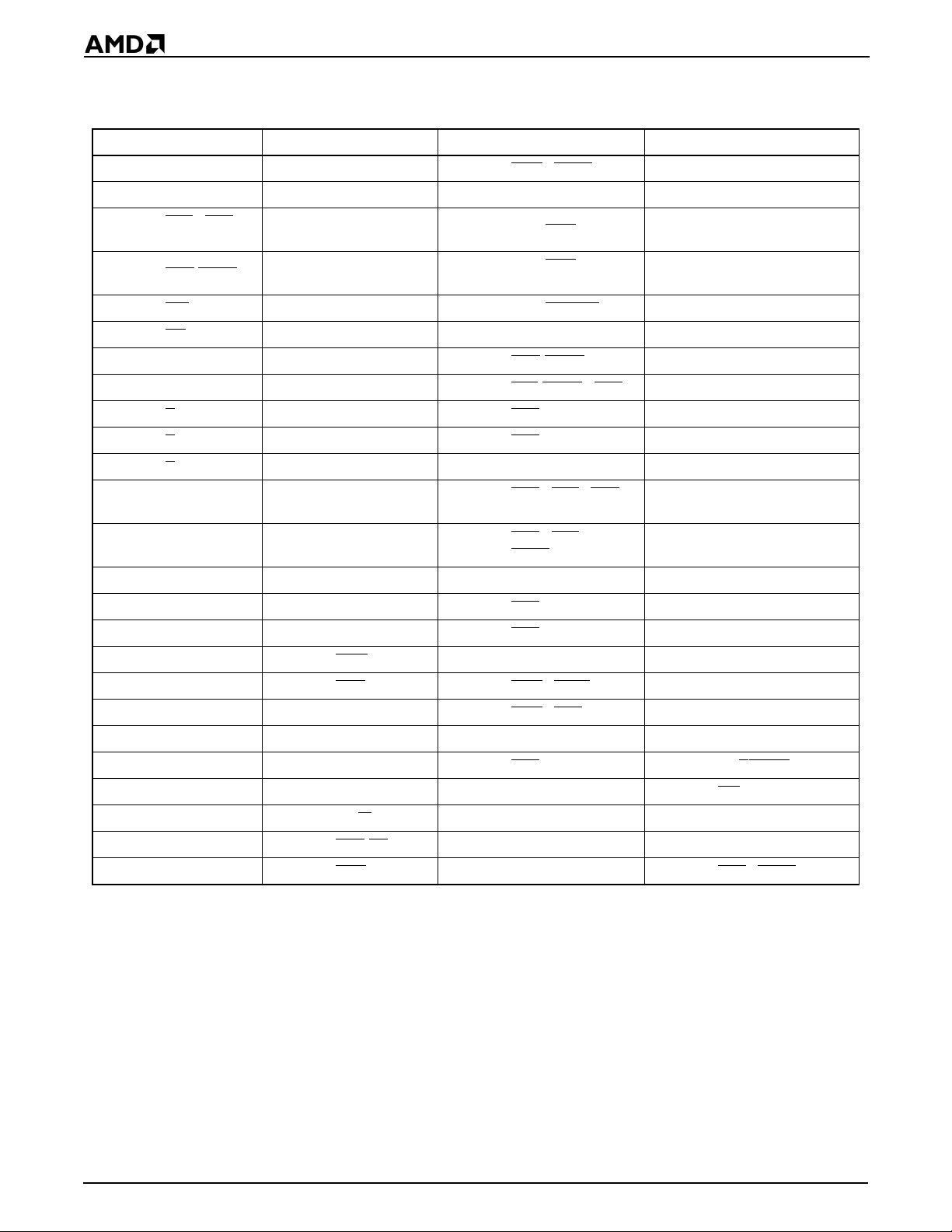

TQFP PIN DESIGNATIONS—Am186ED/EDLV Microcontrollers

Sorted by Pin Number

Pin No. Name Pin No. Name Pin No. Name Pin No. Name

1AD0 26

RTS0/RTR0/

PIO20

51 A11 76 INT3/INTA

1/IRQ

2 AD8 27 BHE

3AD1 28WR

4 AD9 29 RD 54 A8 79 INT0

5 AD2 30 ALE 55 A7 80 UCS/ONCE1

6 AD10 31 ARDY 56 A6 81

7AD3 32S2/BTSEL 57 A5 82 PCS6/A2/PIO2

8AD11 33S

9AD4 34S

10 AD12 35 GND 60 A2 85

11AD5 36X1 61V

12GND 37X2 62A1 87GND

13 AD13 38 V

14 AD6 39 CLKOUTA 64 GND 89 PCS

15 V

16 AD14 41 GND 66 WLB 91

CC

40 CLKOUTB 65 WHB 90 V

/ADEN 52 A10 77

53 A9 78 INT1/SELECT

1 58A4 83PCS5/A1/PIO3

0 59A3 84V

86

CC

CC

63 A0 88 PCS1/PIO17

FT

INT2/INTA0/PWD/

PIO31

/ONCE0/

LCS

0

RAS

CC

PCS

3/RTS1/

1/

RTR

PIO19

2/CTS1/

PCS

1/PIO18

ENRX

0/PIO16

CC

2/LCAS/

MCS

PIO24

3/RAS1/

17 AD7 42 A19/PIO9 67 HLDA 92

18 AD15 43 A18/PIO8 68 HOLD 93 GND

19 S6/CLKDIV

20 UZI/PIO26 45 A17/PIO7 70 NMI 95 TMRIN1/PIO0

21 TXD1/PIO27 46 A16 71 DT/R/

22 RXD1/PIO28 47 A15 72 DEN

23 CTS0/ENRX0/PIO21 48 A14 73 MCS0/PIO14 98 TMRIN0/PIO11

24 RXD0/PIO23 49 A13 74

25 TXD0/PIO22 50 A12 75 INT4/PIO30 100 DRQ0/INT5/PIO12

D

2/PIO29 44 V

RA

CC

69 SRDY/PIO6 94 RES

PIO4 96 TMROUT1/PIO1

/DS/PIO5 97 TMROUT0/PIO10

1/UCAS/

MCS

PIO15

99 DRQ1/INT6/PIO13

MCS

PIO25

Am186ED/EDLV Microcontrollers 15

Page 16

PRELIMINARY

TQFP PIN DESIGNATIONS—Am186ED/EDLV Microcontrollers

Sorted by Pin Name

Pin Name No. Pin Name No. Pin Name No. Pin Name No.

A0 63 AD5 11 GND 87 RXD1 22

A1 62 AD6 14 GND 93 S

A2 60 AD7 17 HLDA 67 S

A3 59 AD8 2 HOLD 68 S2/BTSEL 32

A4 58 AD9 4 INT0 79

A5 57 AD10 6 INT1/SELECT

A6 56 AD11 8

A7 55 AD12 10 INT3/INTA

A8 54 AD13 13 INT4/PIO30 75

A9 53 AD14 16 LCS

A10 52 AD15 18 MCS

A11 51 ALE 30

A12 50 ARDY 31 MCS

A13 49 BHE

A14 48 CLKOUTA 39 NMI 70 V

A15 47 CLKOUTB 40 PCS

A16 46

/ADEN 27 MCS3/RAS1/PIO25 92 UZI/PIO26 20

0/ENRX0/

CTS

PIO21

23 PCS

INT2/INTA

PIO31

MCS

PIO15

0/PWD/

1/IRQ 76 TMRIN1/PIO0 95

/ONCE0/RAS0 81 TMROUT1/PIO1 96

0/PIO14 73 TXD0/PIO22 25

1/UCAS/

2/LCAS/PIO24 91 UCS/ONCE180

0/PIO16 89 V

1/PIO17 88 V

78 SRDY/PIO6 69

77 TMRIN0/PIO11 98

74 TXD1 21

FT

034

133

LKDIV2/

S6/C

PIO29

TMROUT0/

PIO10

CC

CC

CC

19

97

15

38

44

2/CTS1/

A17/PIO7 45 DEN

A18/PIO8 43 DRQ0/INT5/PIO12 100

A19/PIO9 42 DRQ1/INT6/PIO13 99 PCS

AD0 1 DT/R/PIO4 71 PCS6/A2/PIO2 82 WHB 65

AD1 3 GND 12 RD

AD2 5 GND 35 RES

AD3 7 GND 41 RTS0/RTR0/PIO20 26 X1 36

AD4 9 GND 64 RXD0/PIO23 24 X2 37

D

/DS/PIO5 72

RA

PCS

1/PIO18

ENRX

3/RTS1/RTR1/

PCS

PIO19

5/A1/PIO3 83 V

86 V

85 V

29 WLB 66

94 WR 28

CC

CC

CC

61

84

90

16 Am186ED/EDLV Microcontrollers

Page 17

PRELIMINARY

PQFP CONNECTION DIAGRAMS AND PINOUTS

Am186ED/EDLV Microcontrollers

Top Side View—100-Pin Plastic Quad Flat Pack (PQFP)

RXD0

TXD0

RTS0/RTR0

BHE/ADEN

WR

RD

ALE

ARDY

S2/BTSEL

S

1

0

S

GND

X1

X2

V

CC

CLKOUTA

CLKOUTB

GND

A19

A18

V

CC

A17

A16

A15

A14

A13

A12

A11

A10

A9

S6/CLKDIV2

UZI

TXD1

RXD1

CTS0/ENRX0

99989796959493929190898887868584838281

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

D

28

29

30

100

Am186ED/EDLV Microcontrollers

RA

31323334353637383940414243444546474849

AD7

AD15

V

AD14

CC

AD6

AD13

GND

AD5

AD4

AD12

AD9

AD2

AD3

AD10

AD11

80

79

78

77

76

75

74

73

72

71

70

69

50

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

FT

AD1

AD8

AD0

DRQ0/INT5

DRQ1/INT6

TMRIN0

TMROUT0

TMROUT1

TMRIN1

RES

GND

MCS3/RAS1

MCS

2/LCAS

V

CC

PCS0

PCS

1

GND

PCS2/CTS1/ENRX1

PCS

3/RTS1/RTR1

V

CC

PCS5/A1

6/A2

PCS

LCS/ONCE0/RAS0

UCS/ONCE1

INT0

INT1/SELECT

INT2/INTA0/PWD

INT3/INTA1/IRQ

INT4

1/UCAS

MCS

Note:

Pin 1 is marked for orientation.

A8

A7

A6

CC

A1

A2

A3

A4

A5

Am186ED/EDLV Microcontrollers 17

A0

V

GND

WHB

WLB

HLDA

HOLD

NMI

SRDY

DT/R

MCS0

DEN/DS

Page 18

PRELIMINARY

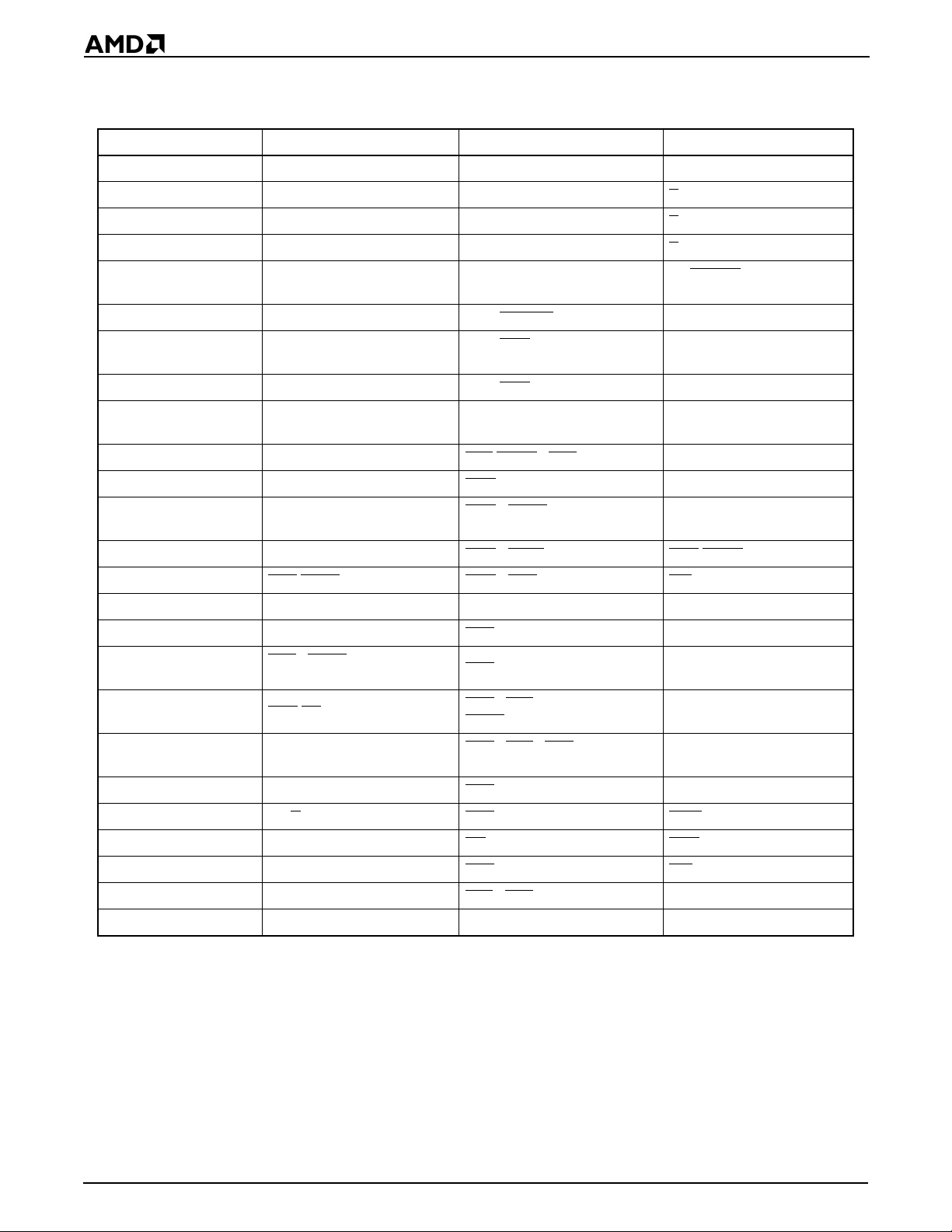

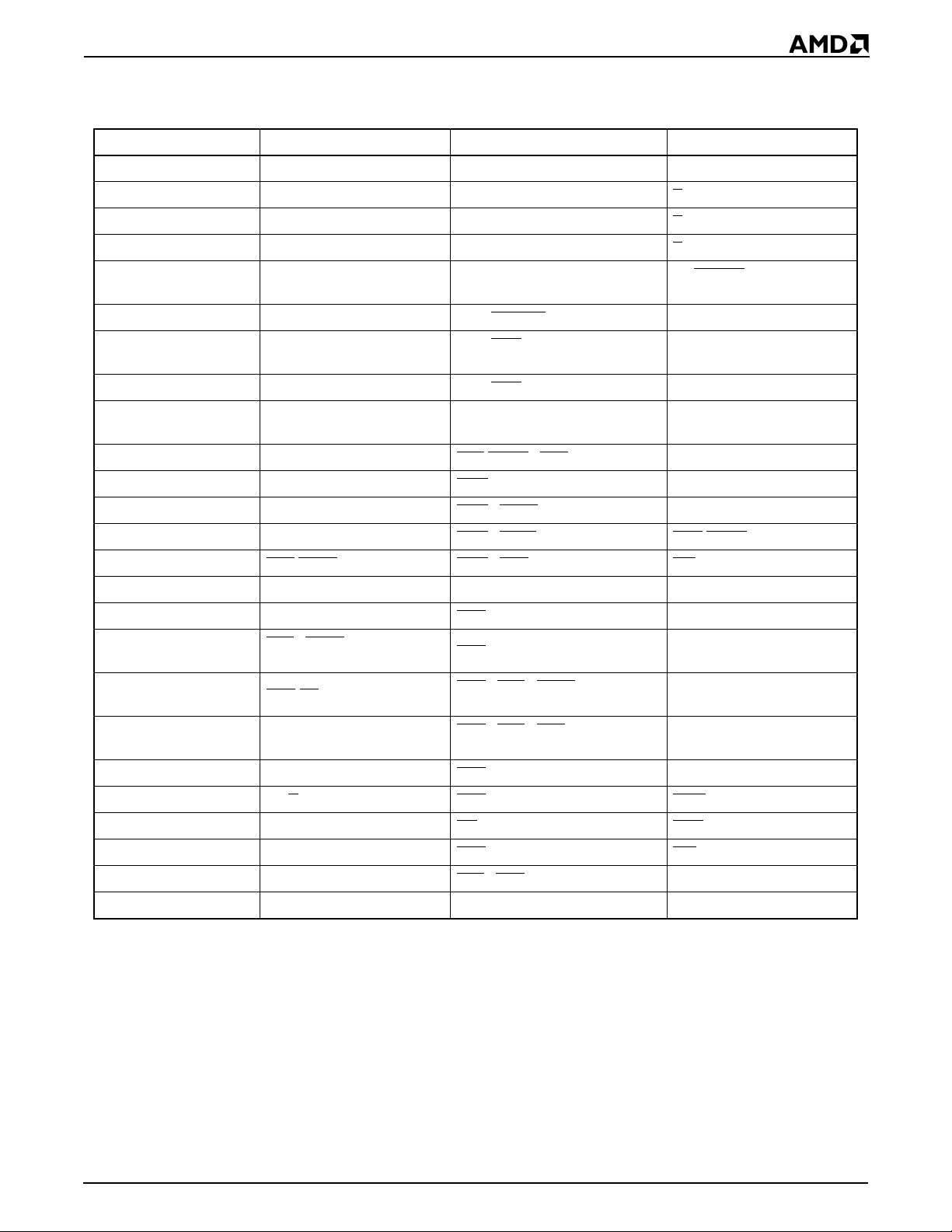

PQFP PIN DESIGNATIONS—Am186ED/EDLV Microcontrollers

Sorted by Pin Number

Pin No. Name Pin No. Name Pin No. Name Pin No. Name

1 RXD0/PIO23 26 A13 51 MCS1/UCAS/PIO15 76 DRQ1/INT6/PIO13

2 TXD0/PIO22 27 A12 52 INT4/PIO30 77 DRQ0/INT5/PIO12

0/RTR0/

RTS

3

PIO20

28 A11 53 INT3/INTA

1/IRQ 78 AD0

4BHE

5WR

6RD

7 ALE 32 A7 57 UCS

8 ARDY 33A6 58LCS/ONCE0/RAS083AD10

9S

10 S

11 S0 36A3 61V

12 GND 37 A2 62

13 X1 38 V

14 X2 39 A1 64 GND 89 GND

15 V

16 CLKOUTA 41 GND 66 PCS

17 CLKOUTB 42 WHB

18 GND 43 WLB 68 MCS2/LCAS/PIO24 93 AD14

19 A19/PIO9 44 HLDA 69 MCS

/ADEN 29 A10 54

30 A9 55 INT1/SELECT 80 AD1

31 A8 56 INT0 81 AD9

2/BTSEL 34A5 59PCS6/A2/PIO2 84 AD3

1 35A4 60PCS5/A1/PIO3 85 AD11

63

67 V

CC

CC

40 A0 65 PCS1/PIO17 90 AD13

INT2/INTA

PIO31

CC

PCS

PIO19

PCS

ENRX

CC

0/PWD/

/ONCE182AD2

3/RTS1/RTR1/

2/CTS1/

1/PIO18

79 AD8

86 AD4

87 AD12

88 AD5

FT

0/PIO16 91 AD6

92 V

3/RAS1/PIO25 94 AD7

CC

20 A18/PIO8 45 HOLD 70 GND 95 AD15

21 V

22 A17/PIO7 47 NMI 72 TMRIN1/PIO0 97 UZI

23 A16 48 DT/R/

24 A15 49 DEN/DS/PIO5 74 TMROUT0/PIO10 99 RXD1/PIO28

25 A14 50 MCS

CC

46 SRDY/PIO6 71 RES 96 S6/CLKDIV2/PIO29

RA

PIO4 73 TMROUT1/PIO1 98 TXD1/PIO27

0/PIO14 75 TMRIN0/PIO11 100 CTS0/ENRX0/PIO21

/PIO26

D

18 Am186ED/EDLV Microcontrollers

Page 19

PRELIMINARY

PQFP PIN DESIGNATIONS—Am186ED/EDLV Microcontrollers

Sorted by Pin Name

Pin Name No. Pin Name No. Pin Name No. Pin Name No.

A0 40 AD5 88 GND 70 RXD1/PIO28 99

A1 39 AD6 91 GND 89 S

A2 37 AD7 94 HLDA 44 S

A3 36 AD8 79 HOLD 45 S2/BTSEL 9

A4 35 AD9 81 INT0 56

A5 34 AD10 83 INT1/SELECT

A6 33 AD11 85

A7 32 AD12 87 INT3/INTA

A8 31 AD13 90 INT4/PIO30 52

A9 30 AD14 93 LCS

A10 29 AD15 95 MCS

A11 28 ALE 7 MCS

A12 27 ARDY 8 MCS2/LCAS/PIO24 68 UCS/ONCE157

A13 26 BHE

A14 25 CLKOUTA 16 NMI 47 V

A15 24 CLKOUTB 17 PCS0/PIO16 66 V

A16 23

A17/PIO7 22 DEN

/ADEN 4MCS3/RAS1/PIO25 69 UZI/PIO26 97

0/ENRX0/

CTS

PIO21

/DS/PIO5 49

INT2/INTA

PWD/PIO31

100 PCS

PCS

PIO18

0/

1/I RQ 53 TMRIN1/PIO0 72

/ONCE0/RAS0 58 TMROUT1/PIO1 73

0/PIO14 50 TXD0/PIO22 2

1/UCAS/PIO15 51 TXD1/PIO27 98

1/PIO17 65 V

2/CTS1/ENRX1/

55 SRDY/PIO6 46

54 TMRIN0/PIO11 75

FT

63 V

011

110

LKDIV2/

S6/C

PIO29

TMROUT0/

PIO10

CC

CC

CC

CC

96

74

15

21

38

61

3/RTS1/RTR1/

A18/PIO8 20 DRQ0/INT5/PIO12 77

A19/PIO9 19 DRQ1/INT6/PIO13 76 PCS

AD0 78 DT/R

AD1 80 GND 12 RD 6WLB 43

AD2 82 GND 18 RES

AD3 84 GND 41 RTS

AD4 86 GND 64 RXD0/PIO23 1 X2 14

D

RA

/PIO4 48 PCS6/A2/PIO2 59 WHB 42

PCS

PIO19

5/A1/PIO3 60 V

0/RTR0/PIO20 3 X1 13

62 V

71 WR 5

CC

CC

67

92

Am186ED/EDLV Microcontrollers 19

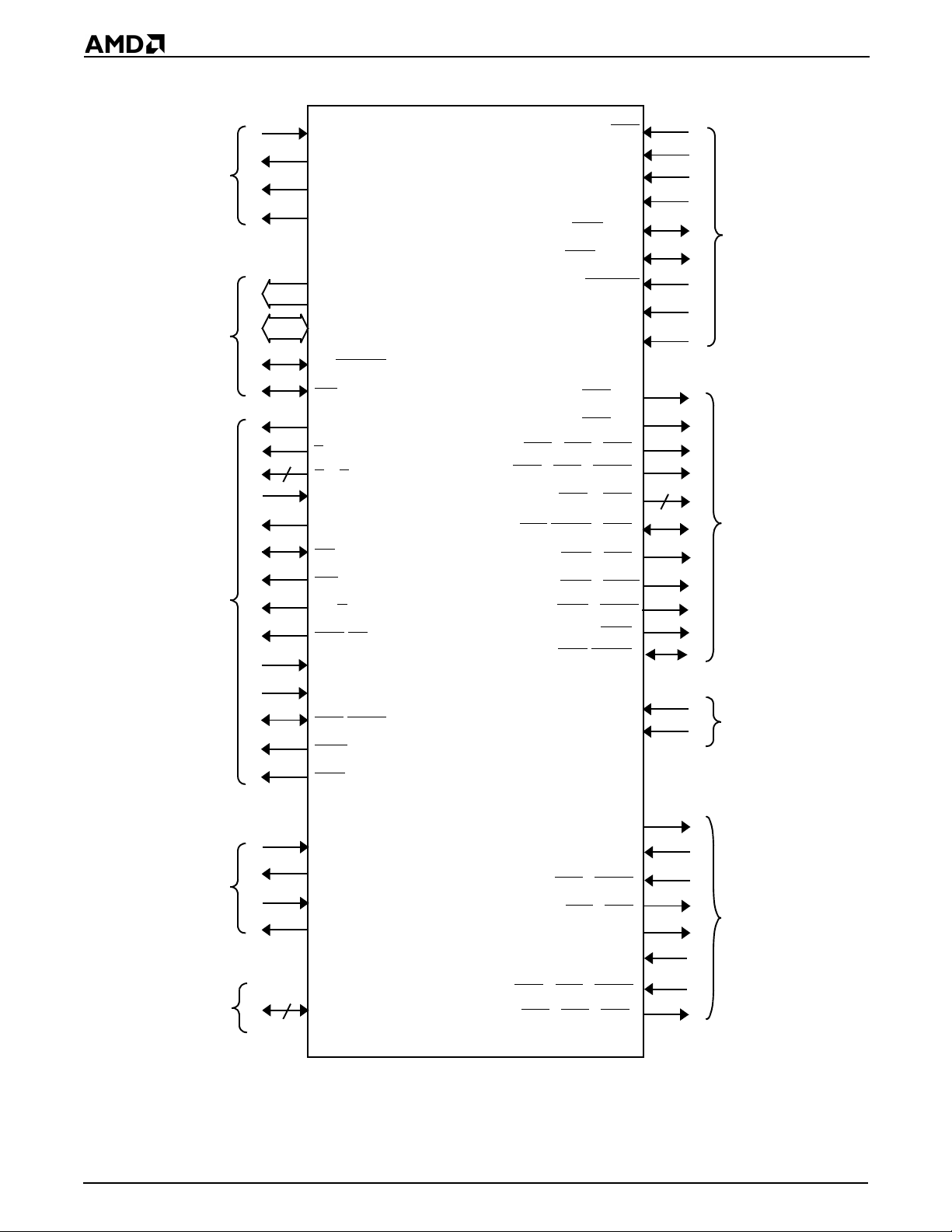

Page 20

PRELIMINARY

LOGIC SYMBOL—Am186ED/EDLV MICROCONTROLLERS

Clocks

Address an d

Address/Data Buses

Bus Control

X1

X2

CLKOUTA

CLKOUTB

20

16

2

A19–A0

AD15–AD0

S6/CLKDIV2

UZI

ALE

2/BTSEL

S

S1–S0

HOLD

HLDA

RD

WR

DT/R

DEN/DS

ARDY

*

*

*

*

*

INT3/INTA1/IRQ

INT2/INTA0/PWD

INT1/SELECT

PCS3/RTS1/RTR1

2/CTS1/ENRX1

PCS

PCS

LCS

/ONCE0/RAS0

MCS3/RAS1

MCS2/LCAS

MCS1/UCAS

UCS/ONCE1

RES

DRQ1/INT6

DRQ0/INT5

INT4

INT0

NMI

PCS6/A2

PCS5/A1

1–PCS0

FT

MCS0

*

Reset Control and

Interrupt Service

*

*

*

*

*

2

*

Memory and

Peripheral Control

*

*

*

*

*

SRDY

BHE/ADEN

WHB

WLB

DRQ1/INT6

DRQ0/INT5

*

*

DMA Control

RA

TXD0

32

TMRIN0

TMROUT0

TMRIN1

TMROUT1

PIO32–PIO0

CTS

RTS0/RTR0

2/CTS1/ENRX1

PCS

PCS

3/RTS1/RTR1

RXD0

0/ENRX0

TXD1

RXD1

*

Timer Control

D

Programmable

I/O Control

Notes:

* These signals are the normal function of a pin that can be used as a PIO. See Pin Descriptions beginning on page21 and

Table 2 on page 29 for information on shared function.

** All PIO signals are shared with other physical pins.

*

*

*

shared

**

*

*

*

*

Asynchronous

Serial Port Control

*

*

*

*

20 Am186ED/EDLV Microcontrollers

Page 21

PRELIMINARY

PIN DESCRIPTIONS

Pins That Are Used by Emulators

The following pins are used by emulators: A19–A0,

AD7–AD0, ALE, BHE

LKDIV2, and UZI.

S6/C

Many emulators require S6/CLKDIV

configured in their no rmal function ality as S6 a nd U ZI

not as PIOs. If BHE

edge of RES

functionality.

Pin Terminology

The following terms are used to describe the pins:

Input—An input-only pin.

Output—An output-only pin.

Input/Output—A pin that can be either input or output

(I/O).

Synchronous—Synchronous inp uts must meet setup

and hold times in r elation to CLK OUTA. Synchronous

outputs are synchronous to CLKOUTA.

Asynchronous—Inputs or outputs that are

asynchronous to CLKOUTA.

A19–A0

(A19/PIO9, A18/PIO8, A17/PIO7)

Address Bus (output, three-state, synchronous)

These pins supply nonmultiplexed memory or I/O

addresses to the system one half of a CLKOUTA period

earlier than the multiplexed address and data bus

(AD15–AD0). During a bus hold or reset condition, the

address bus is in a high-impedance state.

While the Am186ED/EDLV microcontrollers are directly

connected to DRAM, A19–A0 will serve as the

nonmultiplexe d address bus for SRAM, FLASH ,

PROM, EPROM, and peripherals. The odd address

pins (A17, A15, A13, A11, A9, A7, A5, A3, and A1) will

have both the row and column address during a DRAM

space access. The odd address signals connect

directly to the row and column multiplexed address bus

of the DRAM. The even address pins (A1 8, A16, A14,

A12, A10, A8, A6, A4, A2, and A0) and A19 will have

the initial address asserted during the full DRAM

access. These signals will not transition during a

DRAM access.

AD15–AD8

Address and Data Bus (input/output, three-state,

synchronous, level-sensitive)

AD15–AD8—These time -multiplexed pins supply

memory or I/O addresses and data to the system. This

bus can supply an address to the syste m during the

first period of a bus cycle (t

, S6 and UZI are configured in their normal

D

/ADEN, CLKOUTA, RD, S2–S0,

2 and UZI to be

/ADEN is held Low during the rising

RA

). It supplies data to the

1

system during th e remaining p eriods of that cyc le (t

, and t4).

t

3

The address phase of these pins can be disabled. See

the ADEN

WHB

, t3, and t

t

,

2

During a bus hold or reset co ndition, the address an d

data bus is in a high-impedance state.

During a power-on reset, the address and data bus

pins (AD15–AD0) can als o be used to load system

configuration information into the internal reset

configuration register.

When accesses are made to 8-bit-wide memory

regions, AD15–AD8 drive thei r corr esp ond in g addr e ss

signals throughout the access. If the disable address

phase and 8-bit mode are sel ected (see the ADEN

description with the BHE/ADEN pin), then AD 15–AD8

are three-stated during t

corresponding address signal from t

AD7–AD0

Address and Data Bus (input/output, three-state,

synchronous, level-sensitive)

These time-multiplexed pin s supply partial memor y or

I/O addresses, as well as data, to the system. This bus

supplies the low- order 8 bits of an address to th e

system during the first p eriod of a bu s c ycl e (t

supplies data to the system during the remaining

periods of that cycle (t

AD0 supplies the data for both high and low bytes.

The address phase of these pins can be disabled. See

the ADEN

When WLB

during t

During a bus hold or reset co ndition, the address an d

data bus is in a high-impedance state.

During a power-on reset, the address and data bus

pins (AD15–AD0) can als o be used to load system

configuration information into the internal reset

configuration register.

ALE

Address Latch Enable (output, synchronous)

This pin indicates to the system that an address appears on the addre ss and data bus (AD15–AD0) . The

address is guaran teed to be v alid on t he trailing edge

of ALE. This pin is three-stated during ONCE mode.

ALE is three-stated and held resistively Low during a

bus hold condition. In addition, ALE has a weak internal

pulldown resistor that is active dur ing re set, so tha t an

external device does not get a spurious ALE during

reset.

description w ith the BHE/ADEN pin. When

is deasserted, these pins are three-stated during

4.

and driven with their

1

to t4.

2

FT

, t3, and t4). In 8-bit mode, AD7–

2

pin description with the BHE/ADEN pin.

is deasserted, these pins are t hree-state d

, t3, and t

2

4.

), and it

1

,

2

Am186ED/EDLV Microcontrollers 21

Page 22

PRELIMINARY

ARDY

Asynchronous Ready (input, asynchronous,

level-sensitive)

This pin is a true asy nch ronou s r ea dy that indicates to

the microcontroller th at the addressed m emory space

or I/O device will com plete a data transfer. The ARDY

pin is asynchr onous to CLKOU TA and is active High.

T o guarantee the number of wait states inserted, ARDY

or SRDY must be synchronized to CLKOUTA. If the

falling edge of ARDY is not synchronized to CLKOUTA

as specified, an additional clock period can be added.

To always assert the ready condition to the

microcontroller, tie ARDY High. If the system does no t

use ARDY, tie the pin Low to yield control to SRDY.

BHE/ADEN

Bus High Enable (three-state, output,

synchronous)

Address Enable (input, internal pullup)

BHE

—During a memory access, this pin and the leastsignificant address bit (AD0 or A 0) indicate to the

system which bytes of the data bus (upper, lower, or

both) participate in a bus cycle. The BHE

AD0 pins are encoded as shown in Table 1.

/ADEN and

not drive the address during t

pullup resistor o n BHE

required. Disabling the addres s phase reduces power

consumption.

/ADEN is held Low on power-on reset, the AD

If BHE

bus drives both addresse s an d data, re gardles s of the

DA bit setting. The pin is sampled on the rising edge of

. (S6 and UZI also assume their normal

RES

functionality in this instan ce. See Table 2 on page29.)

The internal pullup on ADEN

Note: For 8-b it accesses, AD15–AD8 are driv en with

addresses during the t

setting of the DA bit in the UMCS and LMCS registers.

CLKOUTA

Clock Output A (output, synchronous)

This pin supplies the internal clock to the sy stem.

Depending on the value of the system configuration

register (SYS CON), CLKOUTA operates at either the

PLL frequency (X1), the power-save frequency, or is

held Low. CLKOUTA remains active during reset and

bus hold conditions.

All AC timing specs that use a clock relate to

CLKOUTA.

2–t4

. There is a we ak intern al

1

/ADEN so no externa l pullup is

is ~9 kohm.

bus cycle, regard les s of t he

Table 1. Data Byte Encoding

BHE AD0 Type of Bus Cycle

00Word Transfer

01High Byte Transfer (Bits 15–8)

1 0 Low Byte Transfer (Bits 7–0)

11Reserved

is asserted during t1 and remains asserted

BHE

through t

BHE

WLB

AD0 for High and Low byte-write en ables. UCAS

LCAS

DRAM devices.

BHE

using the multiplexed address and data (AD) bus. A