Page 1

100G Development Kit, Stratix IV GT Edition Reference

Manual

100G Development Kit, Stratix IV GT Edition

Reference Manual

101 Innovation Drive

San Jose, CA 95134

www.altera.com

MNL-01057-1.0

Subscribe

Page 2

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat.

& Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective

holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance

with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or

liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera

customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or

services.

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 3

Contents

Chapter 1. Overview

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Development Board Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Handling the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Chapter 2. Board Components

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Board Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Featured Device: Stratix IV GT Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

I/O Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

MAX II CPLD EPM2210 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–11

Configuration, Status, and Setup Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Embedded USB-Blaster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Fast Passive Parallel Download . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

JTAG Programming Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–19

Status Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

Status LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

Board Jumpers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

Push-Button Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

Setup Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

Board settings DIP switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

Clock Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–24

PLL Frequency Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–28

Single-Ended Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–29

General User Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–29

User Push-Button Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–29

User LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–30

User DIP Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–31

LCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–32

Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–33

SSRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–35

Components and Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–38

Transceiver Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–38

QSFP Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–39

SFP+ Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–40

CFP Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–42

Interlaken Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–45

External Memory Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–48

DDR3 Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–49

QDR II Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–56

Ethernet RGMII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–64

Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–65

Power Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–65

Power Distribution System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–65

Power Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–67

Statement of China-RoHS Compliance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–69

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 4

iv Contents

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 5

The 100G Development Kit, Stratix® IV GT Edition allows you to evaluate the

performance the Stratix IV GT transceivers and the low power benefits of the device

itself. This document provides the detailed pin-out and component reference

information required to create FPGA designs that interface with all components on

the board.

f For information about setting up the Stratix IV GT 100G development board and

using the included software, refer to the 100G Development Kit, Stratix IV GT Edition

User Guide.

General Description

1. Overview

The Stratix IV GT 100G development board provides a hardware platform for

evaluating the performance and signal integrity features of the Altera

®

Stratix IV GT

devices. The board features the following major component blocks:

■ EP4S100G5F45I1 FPGA

■ 0.95-V core

■ 1932-Pin FineLine BGA

■ EPM2210F324C3N, MAX II 256-pin CPLD

■ FPGA Configuration

■ MAX

■ 1-Gb flash storage for two configuration images (factory and user)

■ On-Board USB-Blaster

■ JTAG header for external USB-Blaster with the Quartus II Programmer

■ On-Board Memory

■ Four 2-Gb DDR3 SDRAM

■ Four 72-Mb QDR II SRAM

■ Status and Setup Elements

■ FPGA Clock Sources

®

II+Flash Fast Passive Parallel (FPP) configuration

®

(FBGA) package

TM

using the Quartus® II Programmer

■ Clock Outputs and Triggers

■ General User Input/Output

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 6

1–2 Chapter 1: Overview

General Description

■ Components and Interfaces

■ 10/100/1000 Ethernet PHY and RJ-45 jack

■ 36 transceiver channels

■ One channel for SFP+ interface

■ One channel for SFP+ with EDC interface

■ Four channels for QSFP interface

■ 10 channels for CFP interface

■ 20 channels for Interlaken interface

■ Power

■ 14-V to 20-V DC input

■ 2.5-mm barrel Jack for DC power input

■ On/Off power slide switch

■ On-board power measurement circuitry

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 7

Chapter 1: Overview 1–3

EP4S100G5F1932

CPLD

(x32)

User LEDs,

Push-Buttons

USB

Blaster

10/100/1000

Ethernet

RJ45

Jack

4 MB QDR II

(x18)

64 MB

SRAM

Flash

CFP

QSFP

Clocks

& PLL

DDR3 SDRAM

(x32)

SFP+

SFP+

with EDC

Interlaken

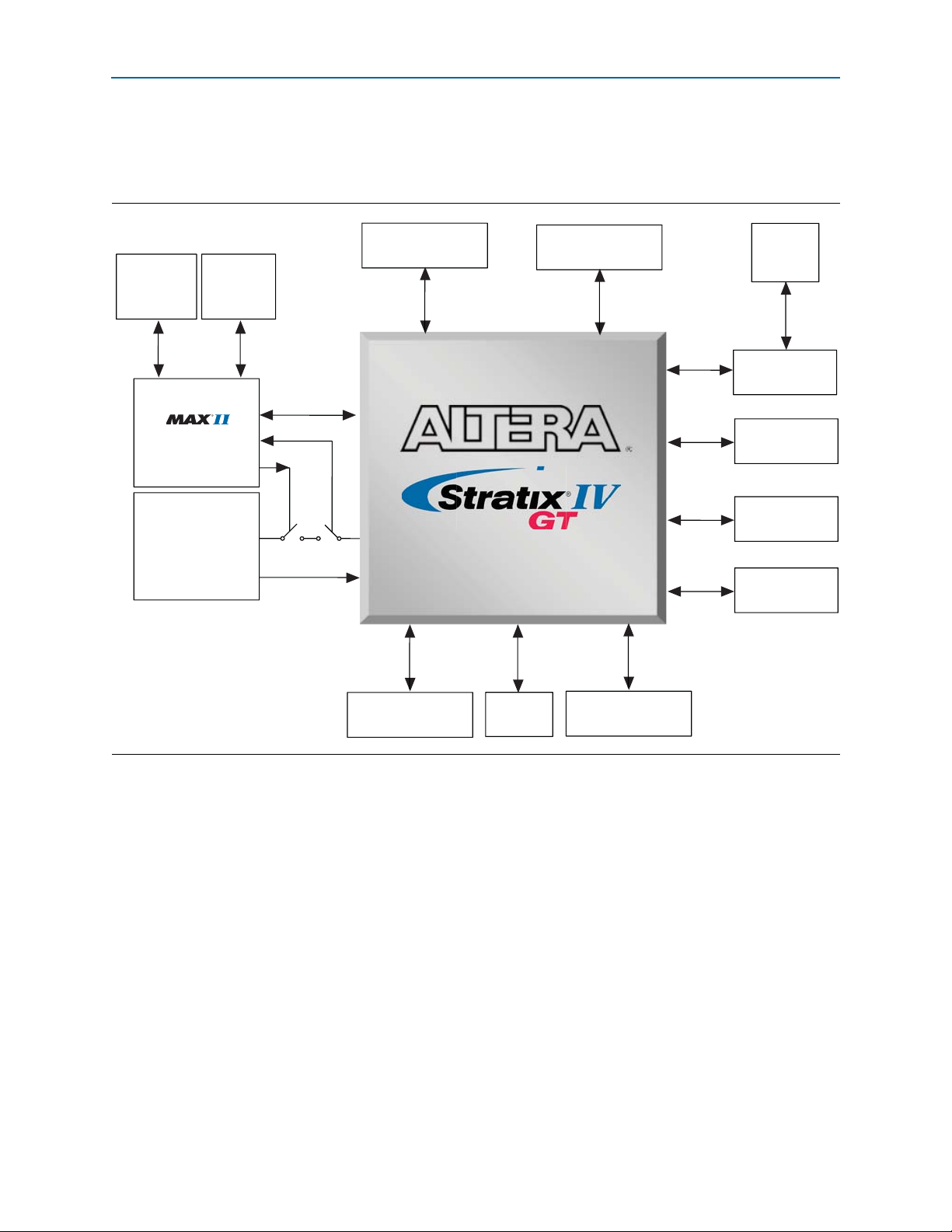

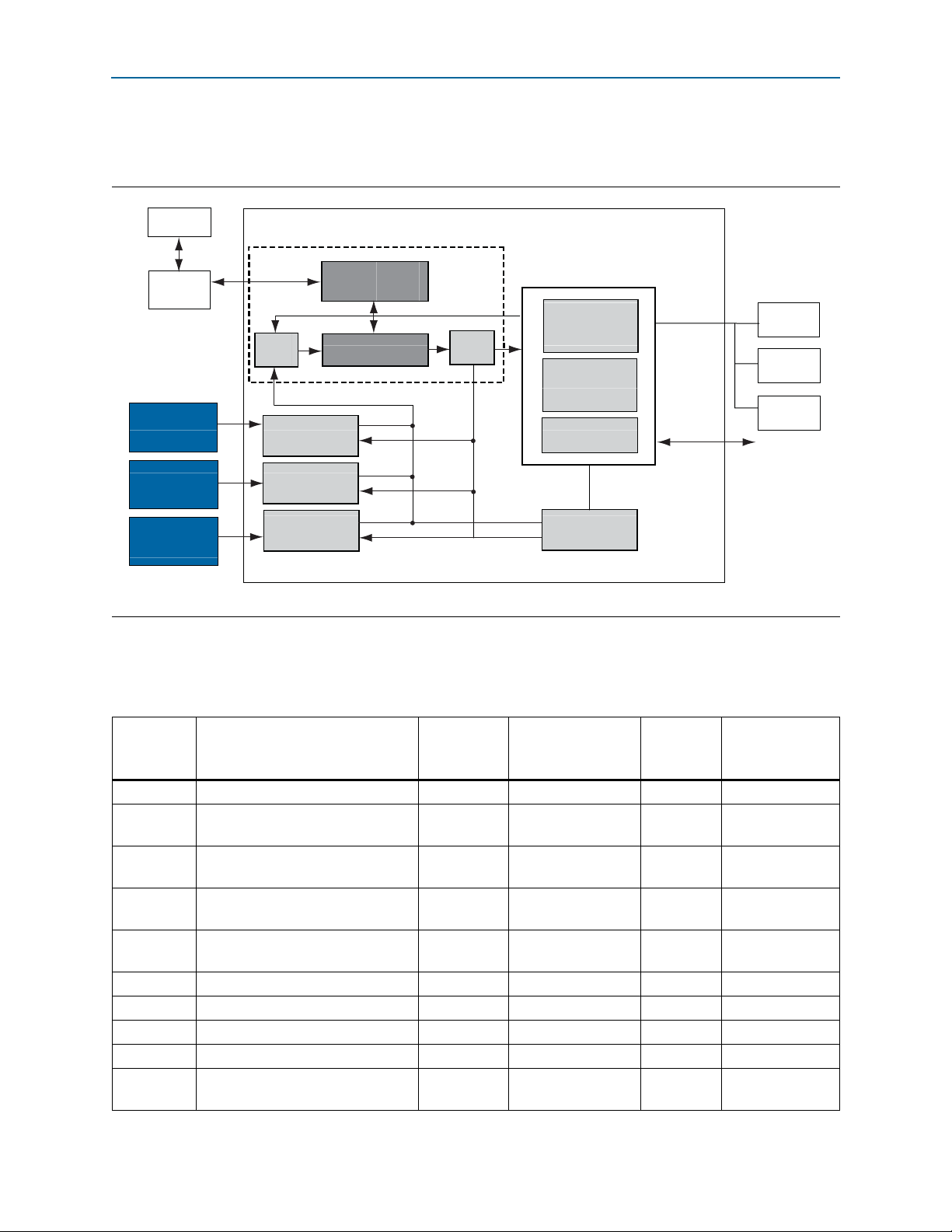

Development Board Block Diagram

Development Board Block Diagram

Figure 1–1 shows the block diagram of the Stratix IV GT 100G development board.

Figure 1–1. Stratix IV GT 100G Development Board Block Diagram

Handling the Board

When handling the board, it is important to observe the following static discharge

precaution:

c Without proper anti-static handling, the board can be damaged. Therefore, use

anti-static handling precautions when touching the board.

The Stratix IV GT 100G development board must be stored between –40º C and

100º C. The recommended operating temperature is between 0º C and 55º C.

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 8

1–4 Chapter 1: Overview

Handling the Board

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 9

Introduction

1 A complete set of schematics, a physical layout database, and GERBER files for the

f For information about powering up the board and installing the development kit

2. Board Components

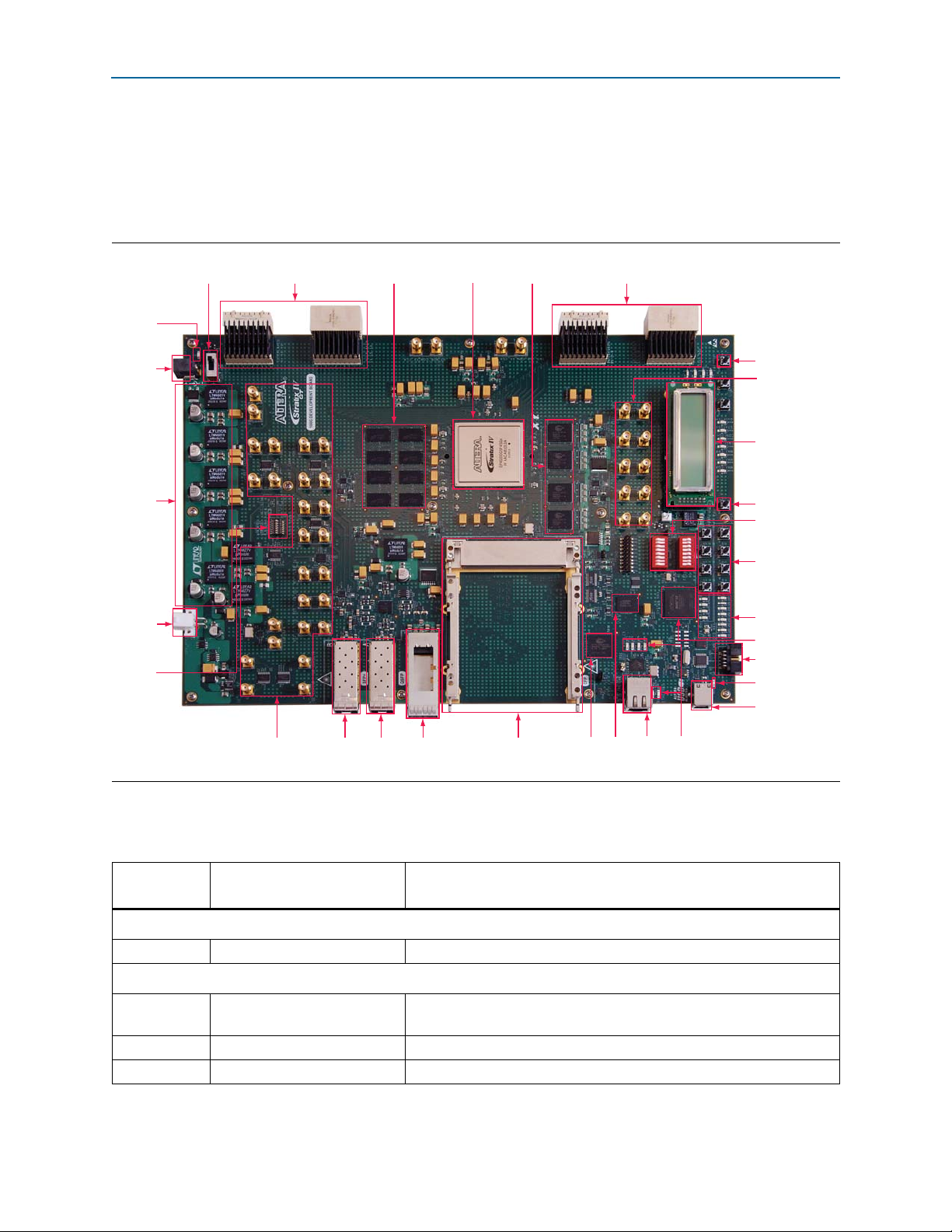

This chapter introduces all the important components on the Stratix IV GT 100G

development board. Figure 2–1 illustrates major component locations and Ta bl e 2– 1

provides a brief description of all features of the board.

development board reside in the Stratix IV GT 100G development kit installation

directory.

software, refer to the 100G Development Kit, Stratix IV GT Edition User Guide.

This chapter consists of the following sections:

■ “Board Overview”

■ “Featured Device: Stratix IV GT Device” on page 2–6

■ “MAX II CPLD EPM2210 System Controller” on page 2–11

■ “Configuration, Status, and Setup Elements” on page 2–17

■ “Clock Circuitry” on page 2–24

■ “General User Input/Output” on page 2–29

■ “Flash Memory” on page 2–33

■ “SSRAM” on page 2–35

■ “Components and Interfaces” on page 2–38

■ “Power” on page 2–65

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 10

2–2 Chapter 2: Board Components

Board Overview

Board Overview

This section provides an overview of the Stratix IV GT 100G development board,

including an annotated board image and component descriptions. Figure 2–1

provides an overview of the board features.

Figure 2–1. Overview of the Stratix IV GT 100G Development Board Features

Power LED

(D7)

DC Power

Jack (J1)

Power

Regulators

Auxiliary

Power

Jack (J2)

Board

Settings

DIP Switch

(SW2)

Power Switch (SW1)

Interlaken Channel 10-19 (J5, J30)

DDR3 Memory

(U28-U31, U36-U39)

Stratix IV GT FPGA

(U44)

QDR II Memory

(U47-U50)

Interlaken Channel 0-9 (J39, J57)

Factory Push-Buttons

(S12)

Clock Circuitry

LCD Display (J59)

CPU Reset Push-Buttons

(S9)

User DIP Switches

(SW3, SW4)

User Push-Buttons

(S5-S8)

User LEDs (D28-D35)

MAX II CPLD (U72)

JTAG Connector (J61)

Embedded

USB-Blaster

Activity LED (D27)

Embedded

USB-Blaster (J60)

Clock Circuitry

SFP Port

B (J31)

SFP Port

A (J32)

QSFP

(J34)

CFP

(J37)

SSRAM

(U57)

Flash

Memory

(U65)

RJ45 Jack

(J49)

Ethernet

Status LEDs

(D12-D17)

Ethernet

Tab le 2 –1 describes the components and lists their corresponding board references.

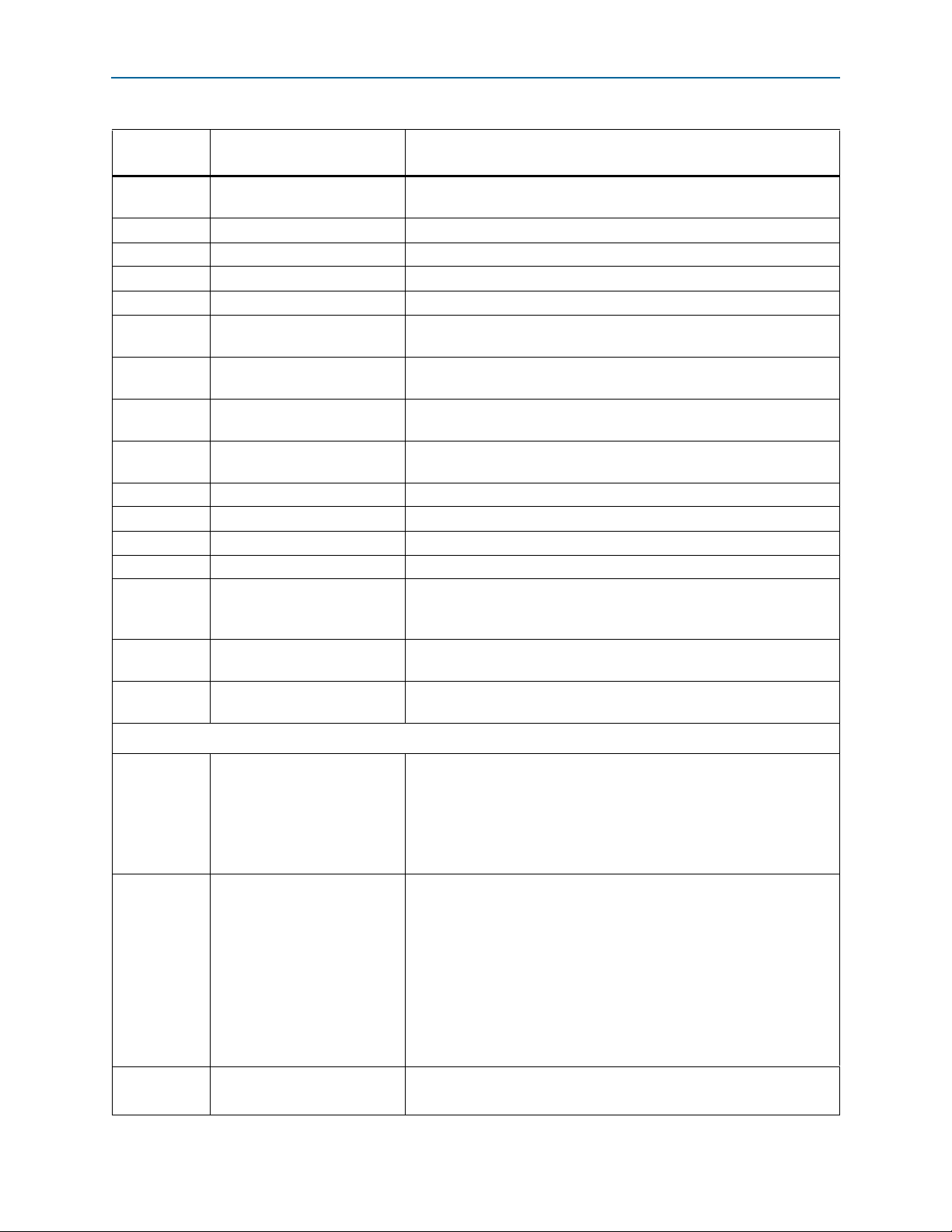

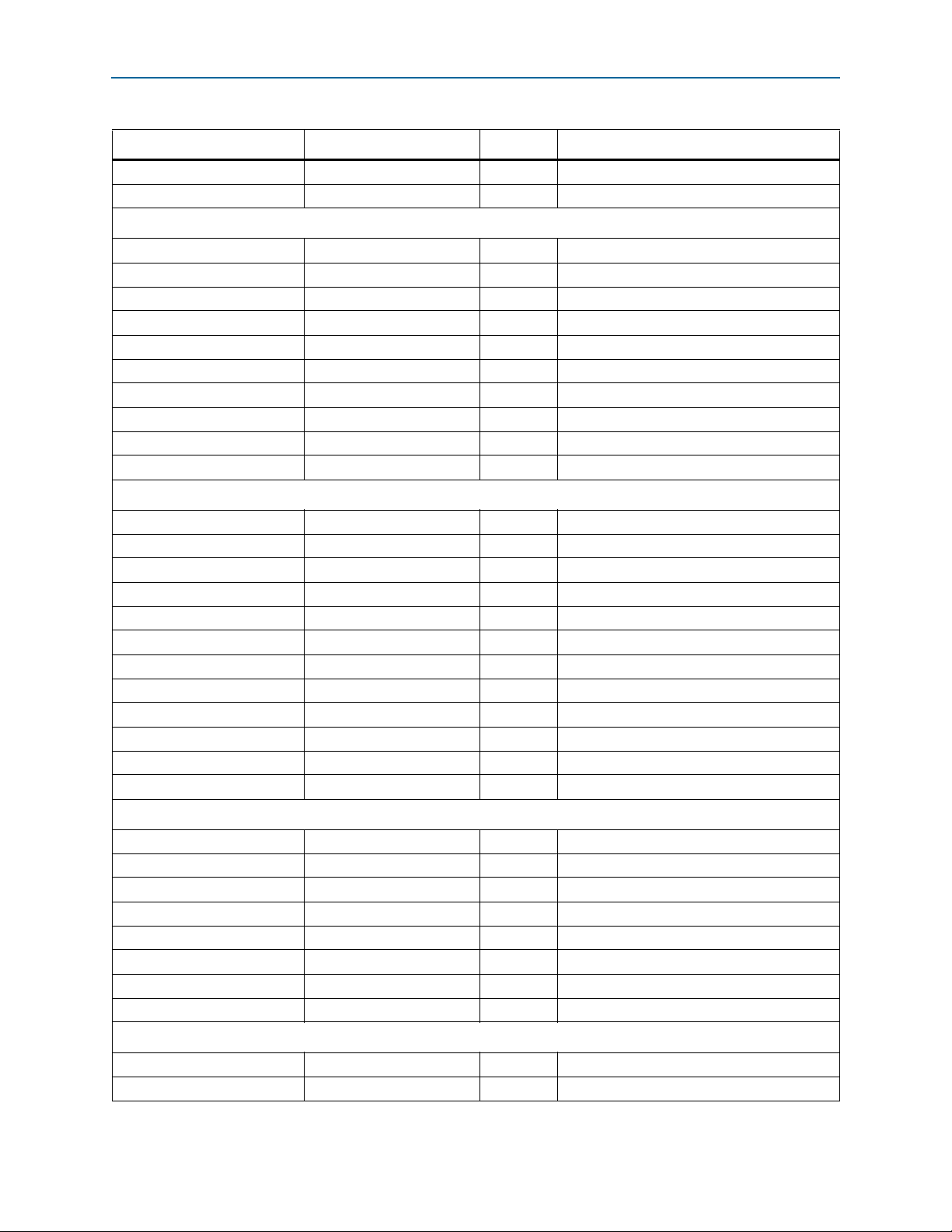

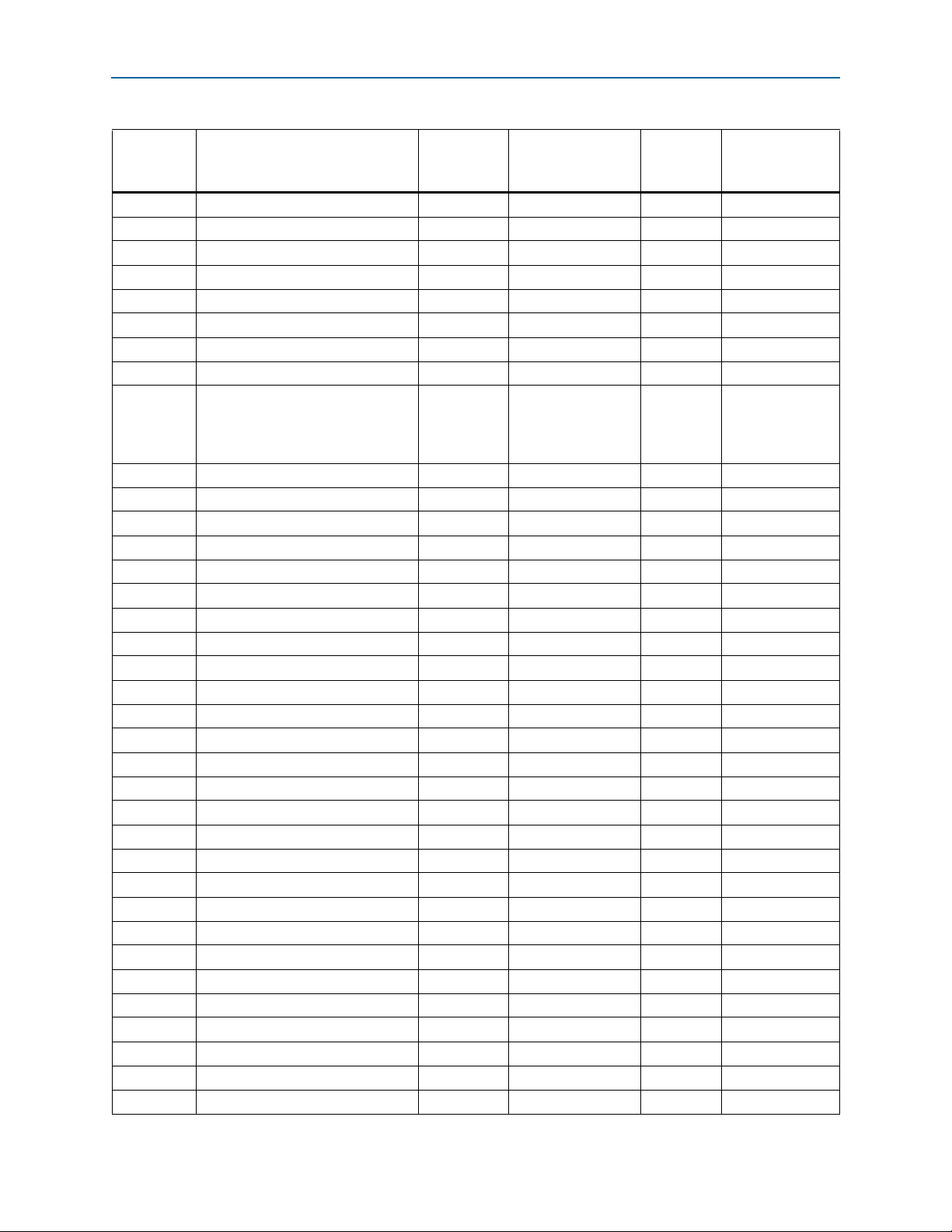

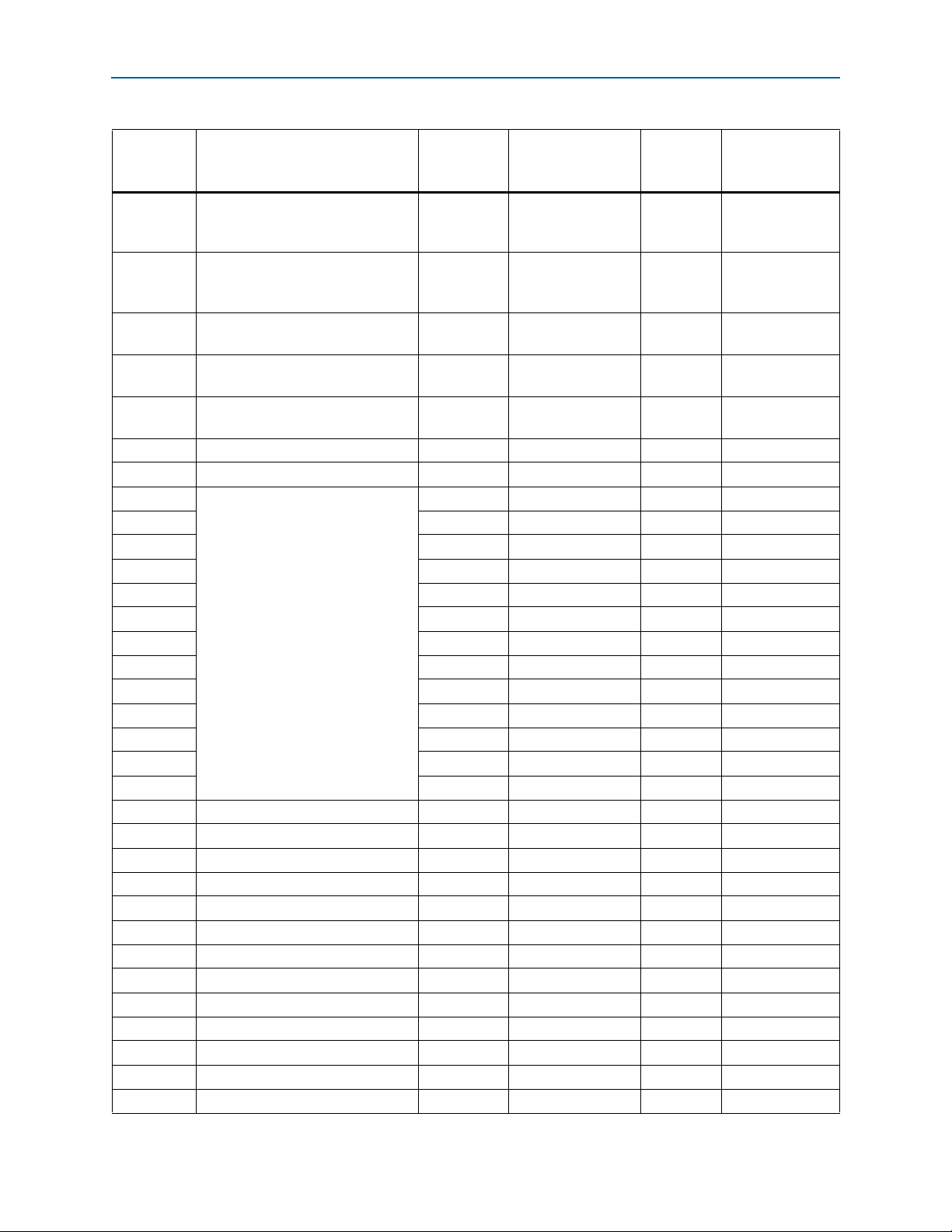

Table 2–1. Stratix IV GT 100G Development Board Components (Part 1 of 5)

Board

Reference

Type Description

Featured Devices

U44 FPGA EP4S100G5F45I1 Stratix IV GT device in a 1932-Pin FBGA package.

Configuration, Status, and Setup Elements

D25, D20,

D19, D26

Configuration status LEDs LEDs to indicate the status of FPP configuration.

D7 Power LED Blue LED to indicate the board power status.

D27 USB-Blaster LED Green LED to indicate the embedded USB-Blaster activity status.

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 11

Chapter 2: Board Components 2–3

Board Overview

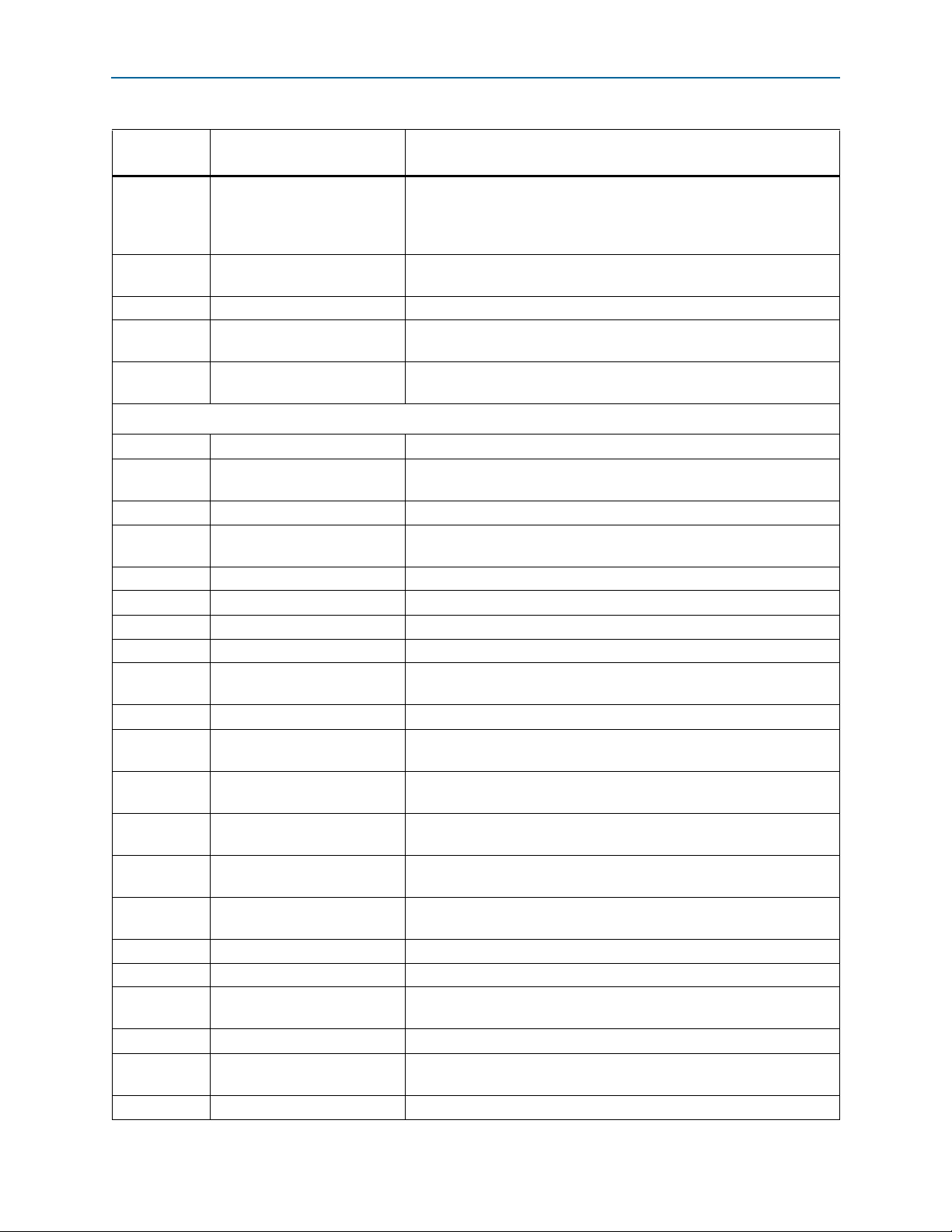

Table 2–1. Stratix IV GT 100G Development Board Components (Part 2 of 5)

Board

Reference

D12-D17

Ethernet status LEDs Shows the Ethernet connection speed as well as transmit or receive

Type Description

activity.

D26 Factory LED Illuminates when the factory design is being loaded into the FPGA.

D36 Load LED Illuminates when the FPGA is being loaded.

D38 Error LED Illuminates when the FPGA configuration from flash fails.

D40 Configuration done LED Illuminates when the FPGA is configured.

J40 USB_DISABLE

J41 JTAG_EN

J61 JTAG programming header

J58

JTAG for embedded

USB-Blaster MAX II CPLD

Manually disables the embedded USB-Blaster when you install the

jumper. Otherwise, the embedded USB-Blaster is enabled.

Enables the MAX II CPLD EPM2210 System Controller to be in the JTAG

chain when shunted

JTAG programming header for connecting an Altera USB-Blaster dongle

to program the FPGA and MAX II CPLD devices.

JTAG for embedded USB-Blaster MAX II CPLD device programming.

S9 CPU reset push-button Press to reset the FPGA logic.

S10 PGM_SEL push-button Selects design file to load into the FPGA.

S11 Load push-button Initiates loading of the FPGA.

S12 Factory push-button Initiates loading of factory design into the FPGA.

II CPLD EPM2210 System Controller functions such as

SW2

Board settings DIP switch Controls the MAX

clock enable, power and temperature monitor, as well as voltage settings

for transceivers and SMA clock input control.

U72 MAX II CPLD (System)

U80

MAX II CPLD (Embedded

USB-Blaster)

Altera EPM2210F324C3N, MAX II 256-pin CPLD for MAX II+FPP

configuration.

Altera EPM240M100C4N, MAX II CPLD for embedded USB-Blaster

circuitry.

Clock Circuitry

J6, J12

J21, J28

J18, J25

SMA input clocks

J19, J26

J3, J14

J10, J11

J7, J13

J22, J29

J17, J24

J27, J20

SMA output clocks

J4, J15

J8, J9

J45, J52

J47, J54,

J46, J53

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

SMA input clock for XCVR

reference clock

Reference clock for Interlaken side LVDS.

Differential clock for Interlaken side LVDS.

Reference clock for line side LVDS.

Differential clock for line side LVDS.

Single-ended clock inputs.

644.53125-MHz LVDS clock.

Reference clock SMA output for Interlaken side LVDS.

Differential clock SMA output for Interlaken side LVDS.

Reference clock SMA output for line side LVDS.

Differential clock SMA output for line side LVDS.

Single-ended clock SMA outputs.

Optical clock SMA source.

PLL output of FPGA.

XCVR reference clock for external clock source (LVPECL or LVDS).

Page 12

2–4 Chapter 2: Board Components

Board Overview

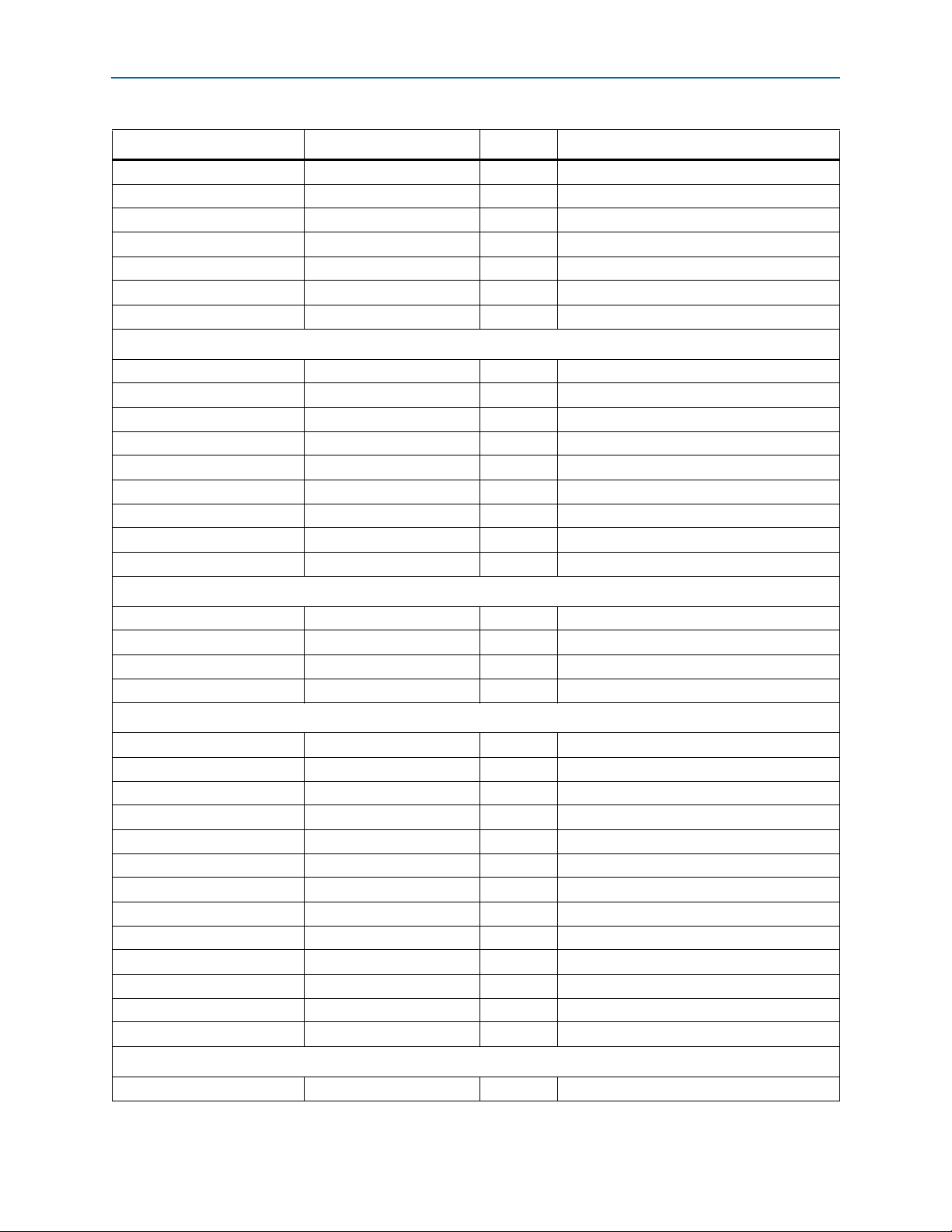

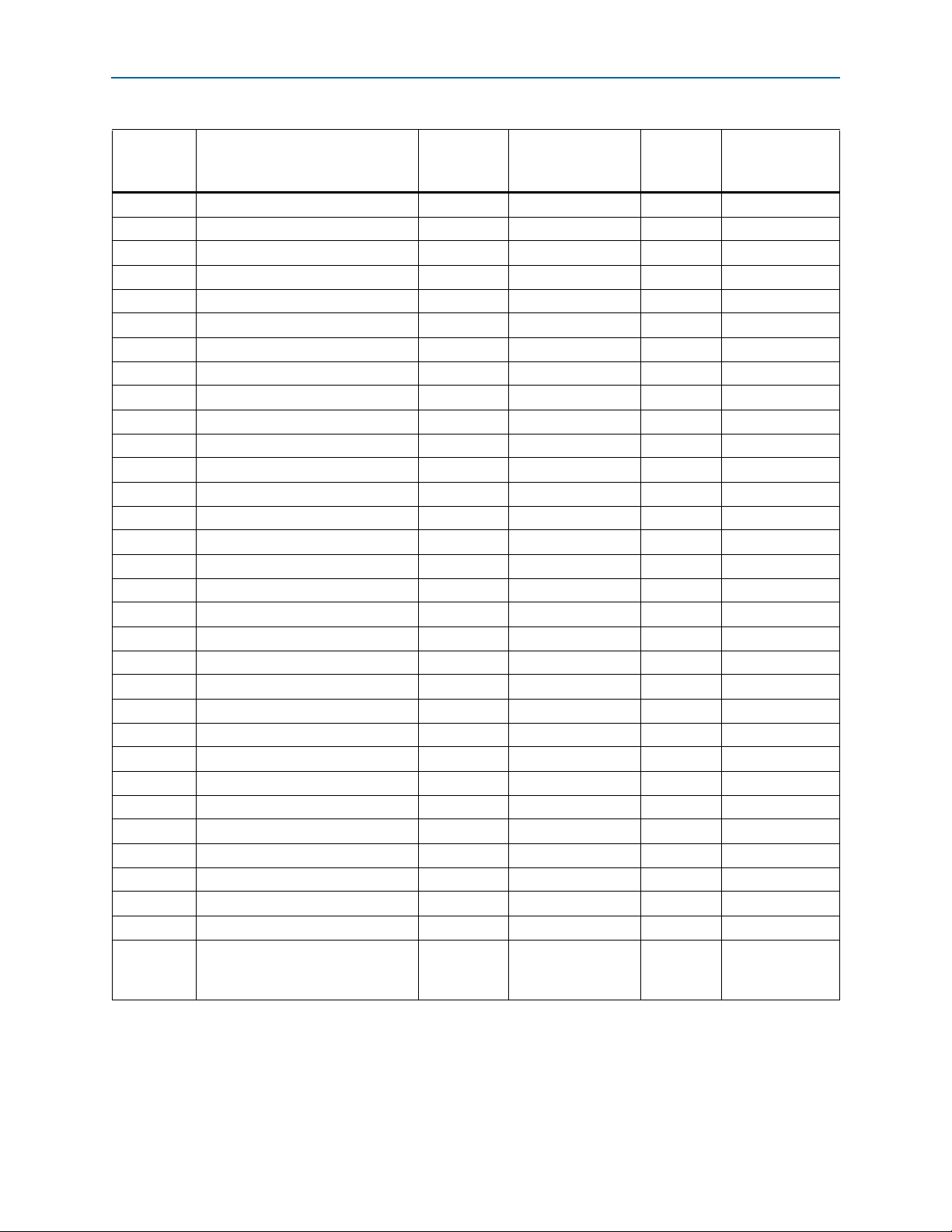

Table 2–1. Stratix IV GT 100G Development Board Components (Part 3 of 5)

Board

Reference

Type Description

U13 LVPECL to LVDS buffer 644.53125MHz LVDS clock buffer.

U15, U18, U19

U16

U20

Differential to LVDS clock

buffer

Differential divide-by-4 clock

divider

Differential to LVDS clock

buffer

Differential clock buffer (2 to 4) distributed to CMU and dedicated

differential clock inputs on the vertical banks of the FPGA.

Divide-by-4 clock circuit to provide the required clock to EDC and CFP.

Differential clock buffer (2 to 6) distributed to CMU of the FPGA and to

clock dividers for the optical clock.

U21, U22, U56 External programmable PLLs On-board programmable PLL clock source with buffers.

U14, U17 Single-ended clock buffer Single-ended clock buffer provided to each side of the FPGA.

X1

644.53125-MHz LVPECL

oscilator

644.53-MHz clock to the FPGA transceivers.

X3 50-MHz oscillator 50-MHz Nios CPU clock (CMOS).

Y1, Y2, Y3 25-MHz crystal clock 25-MHz reference clock for external PLLs.

General User Input and Output

D21–D24 User LEDs Four green LEDs for the MAX II CPLD EPM2210 System Controller.

D28–D35 FPGA LEDs Eight green LEDs for the FPGA.

J59 Character LCD Connector which interfaces to the provided 16 character × 2 line LCD

module.

S1–S4 User push-buttons

User push-buttons connected to the MAX II CPLD EPM2210 System

Controller.

S5–S8 FPGA user push-buttons User push-buttons connected to the Stratix IV GT device.

SW3

SW4

Bank of eight user DIP

switches

Bank of eight user DIP

switches

User DIP switches connected to the MAX II CPLD EPM2210 System

Controller.

User DIP switches connected to the FPGA.

Memory Devices

U28-U31,

DDR3 x16 port 4 x32 independent DDR3 memory port.

U36-U39

U47-U50 QDR II x18/x18 port 4 x18 independent (18-bit read and 18-bit write) QDR II memory port.

U65 Flash memory

Synchronous burst mode flash device which provides 1-Gb non-volatile

memory port.

Components and Interfaces

J34 QSFP_TX_P/_N[3:0]

QSFP XCVR interface (4-channels).

QSFP_RX_P/_N[3:0]

J37

CFP_TX_P/_N[9:0]

CFP_RX_P/_N[9:0]

CFP XCVR interface (10-channels).

J31 SFP+ interface SFP+ XCVR interface port B.

J32 SFP+ interface with EDC SFP+ XCVR interface port A.

J48 I/O connector General purpose expansion connector with 10 user-definable I/Os

connected to the MAX II CPLD EPM2210 System Controller.

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 13

Chapter 2: Board Components 2–5

Board Overview

Table 2–1. Stratix IV GT 100G Development Board Components (Part 4 of 5)

Board

Reference

Type Description

Halo HFJ11-1G02E RJ-45 connector with integrated magnetic which

J49 RJ-45 connector

provides a 10/100/1000 Ethernet connection via a Marvell 88E1111 PHY

and the FPGA-based Altera Triple Speed Ethernet MegaCore function in

RGMII mode.

J5, J30, J39,

Interlaken interface Provides 20 transceiver channels for Interlaken.

J57

U66 10/100/1000 Ethernet PHY Marvell 88E1111 triple speed Ethernet PHY.

J60 USB Type-B connector

U79 USB PHY

Embedded USB-Blaster JTAG for programming the FPGA via a Type-B

USB cable.

FT245BL USB PHY device for configuring the FPGA using embedded

USB-Blaster.

Power

J1 DC power jack 14-V – 20-V DC power jack.

SW1

Power switch Switch to power on or off the board when power is supplied from the DC

power input jack.

U5 5-V switching regulator Supplies 5-V power to the dual switcher and other regulators for biasing.

U6 2.5-V switcher power supply

Supplies 2.5-V power to VCCIO, VCCPD, VCC_CLKIN, and VCC_PGM on

the Stratix IV GT device.

U7, U8 Dual 1.5-V switching regulator Supplies 1.5-V power to the VCCIO on the FPGA and external memory.

U9 3.3-V switcher power supply Supplies 3.3-V power.

U10 12-V switcher power supply Supplies 12-V power.

U11, U12 Dual switching regulator Supplies 0.95-V power to the FPGA core.

U27

VCCHIP (0.95V) linear

regulator

Supplies 0.95-V power to VCCHIP on the FPGA.

U26 VCCPT (1.5 V) linear regulator Supplies 1.5-V power to VCCPT on the FPGA.

U35

U42

U43

U45

U73, U74

VCC_AUX /and VCCA (2.5 V)

linear regulator

VCCL_GXB (1.2 V) linear

regulator

VCCH_GXB (1.4 V) linear

regulator

VCCT_GXB (1.2 V) linear

regulator

VCCR_GXB (1.2 V) linear

regulator (shared output)

Supplies 2.5-V power to VCC_AUX and VCCA on the FPGA.

Supplies 1.2-V power to the VCCL_GXB on the FPGA.

Supplies 1.4-V power to the VCCH_GXB on the FPGA.

Supplies 1.2-V power to the VCCT_GXB on the FPGA.

Supplies 1.2-V power to the VCCR_GXB on the FPGA.

U51, U52 ADC 8/16 Channel 24-bit Monitors the current or voltage of all FPGA power rails

U53, U54 4.25-V linear regulator Supplies 4.25-V power for current monitor circuit.

U55

VCCA_GXB (3.3 V) linear

regulator

Supplies 3.3-V power to the VCCA_GXB on the FPGA.

U60 VCCD (0.95 V) linear regulator Supplies 0.95 V power to VCCD on the FPGA.

U68 2.5-V linear regulator

Supplies 2.5-V power to the MAX II CPLD EPM2210 System Controller

for i/Os.

U23, U24, U59 3.3-V linear regulator Supplies 3.3-V power to the external PLLs.

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 14

2–6 Chapter 2: Board Components

Featured Device: Stratix IV GT Device

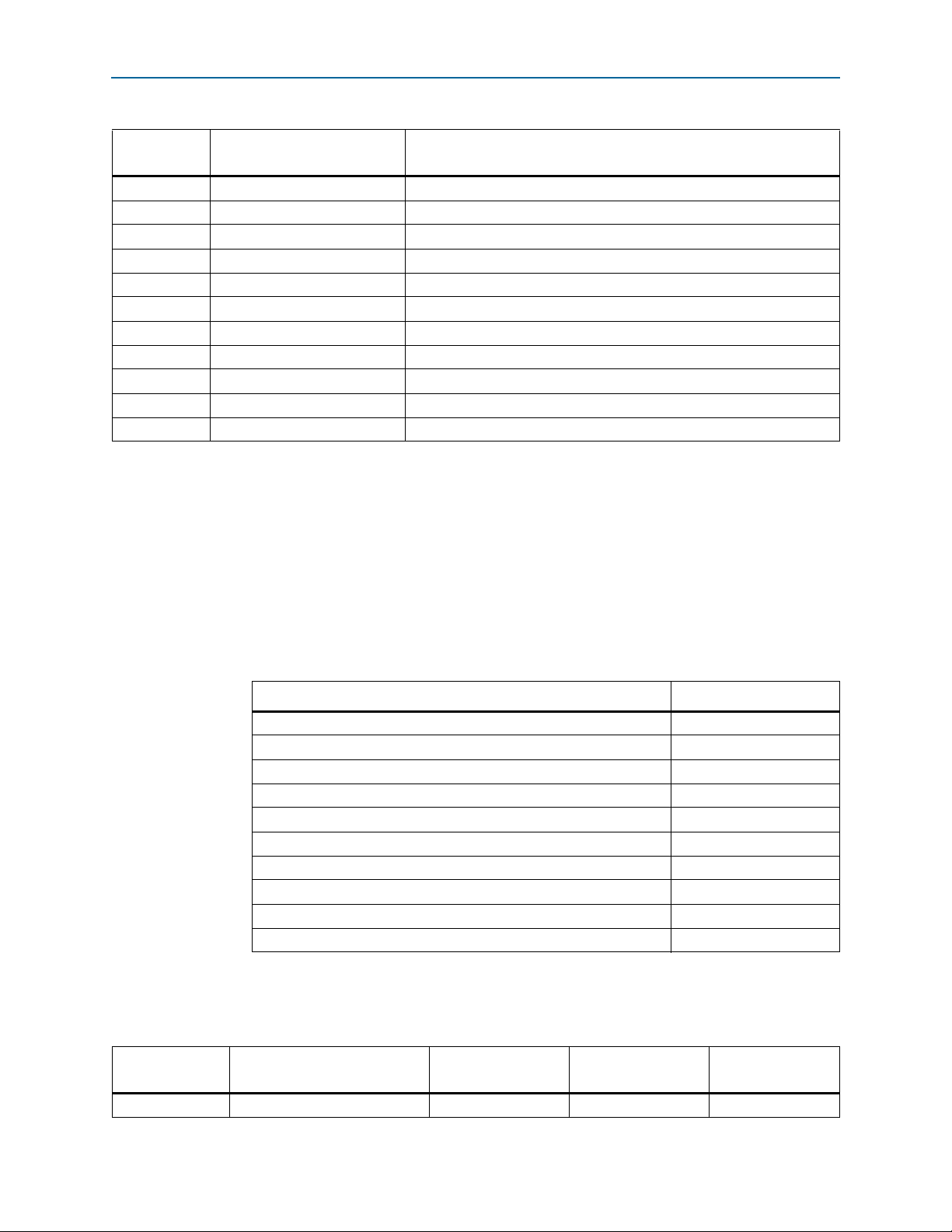

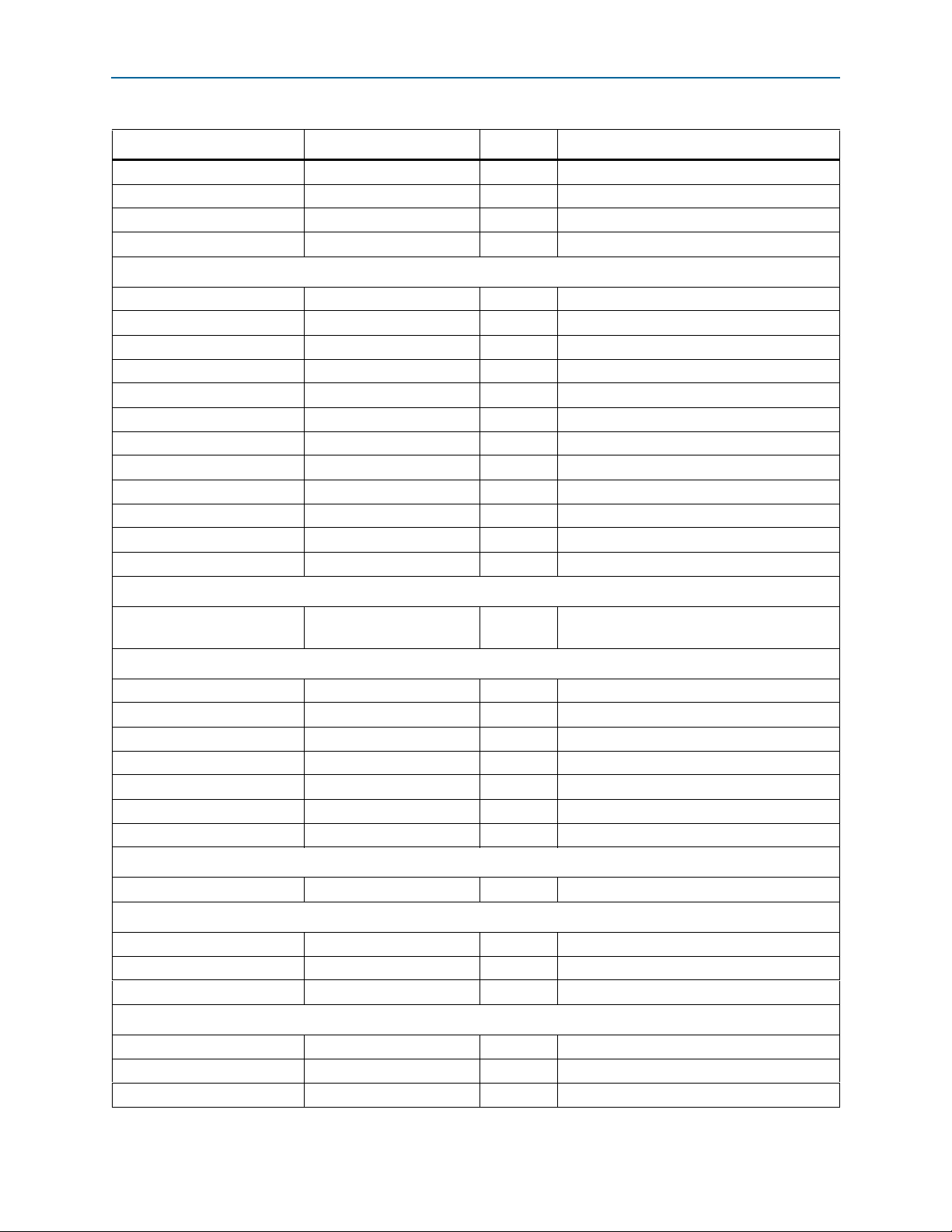

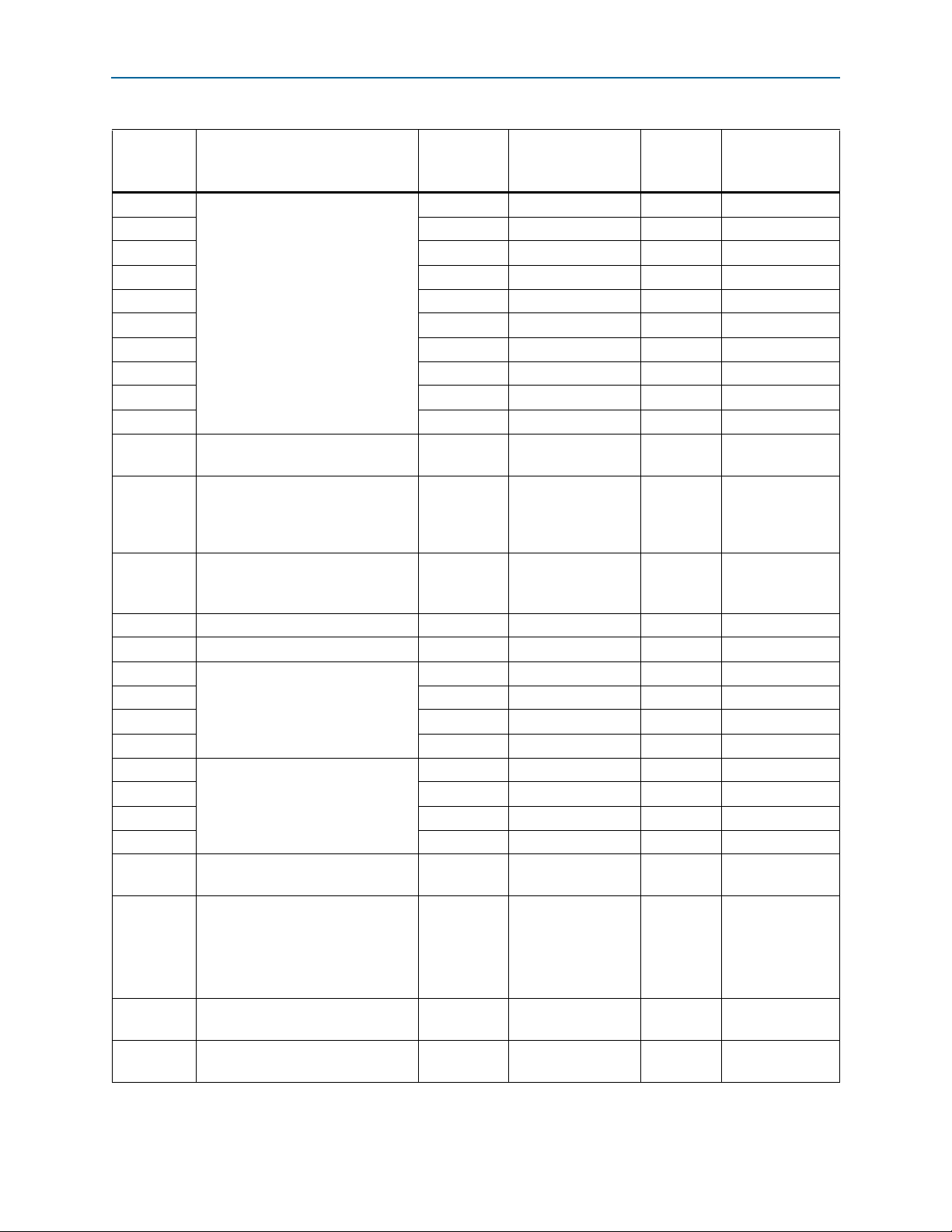

Table 2–1. Stratix IV GT 100G Development Board Components (Part 5 of 5)

Board

Reference

Type Description

U69 1.1-V linear regulator Supplies 1.1-V power to the 10/100/1000 Ethernet PHY.

U71 2.5-V linear regulator Supplies 2.5-V power to the USB port.

U70 LM95235 temperature sensor Monitors the FPGA temperature.

U77 3.3-V switching regulator Supplies 3.3-V power to the MAX II CPLD EPM2210 System Controller.

U33 5-V switching regulator Supplies 5-V power to the optical regulators.

U41 3.3-V linear regulator Supplies 3.3-V power to QSFP and SFP+.

U58 1.8-V linear regulator Supplies 1.8-V power to QDR II VDD.

U25 1.2-V linear regulator Supplies 1.2-V power to EDC.

U40 1.8-V linear regulator Supplies 1.8-V power to EDC.

U86 1.2-V linear regulator Supplies 1.2-V power to the translator device for CFP.

U81, U87, U88 0.75-V V

regulator Supplies 0.75 VTT/V

TT/VREF

to external memories and termination.

REF

Featured Device: Stratix IV GT Device

The Stratix IV GT 100G development board features the EP4S100G5F45I1 Stratix IV

GT FPGA device (U44) in a 1932-pin FBGA package.

f For more information about the Stratix IV GT devices, refer to the Stratix IV Device

Handbook.

Tab le 2 –2 describes the features of the Stratix IV GT EP4S100G5F45I1 device.

Table 2–2. Stratix IV GT Device EP4S100G5F45I1 Features

Features EP4S100G5F45I1

ALMs 212,480

Equivalent LEs 531,200

M9K RAM Blocks (256 × 72 bits) 1,280

M144K Blocks (2048 × 72 bits) 64

Total Memory (MLAB + M9K + M144K) Kbits 27,376

Total Transceiver Channels 48

18-bit × 18-bit Multipliers 1,024

PLLs 12

Maximum User I/O pins 781

Package Type 1932-pin FBGA

Tab le 2 –3 lists the Stratix IV GT component reference and manufacturing

information.

Table 2–3. Stratix IV GT Device Component Reference and Manufacturing Information

Board Reference Description Manufacturer

U44 Stratix IV GT F1932, Lead Free Altera

Corporation EP4S100G5F45I1 www.altera.com

Manufacturing

Part Number

Manufacturer

Website

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 15

Chapter 2: Board Components 2–7

Featured Device: Stratix IV GT Device

I/O Resources

Figure 2–2 shows the bank organization and I/O count for the EP4S100G5F45I1

device in the 1932-pin FBGA package.

Figure 2–2. Stratix IV GT Device I/O Bank Diagram (Note 1)

Number

of I/Os

Bank

Name

40 Bank 1A

Bank 8B 48

Bank 8A 48

Bank 7C 32

Bank 8C 32

Bank 7A 48

Bank 7B 48

Bank 6A 38

21 Bank 1C

21 Bank 2C

13 Bank 2A

41 Bank 2B

Bank

4 (1)

GXBL2

Bank

4 (1)

GXBL1

Bank

4 (1)

GXBL0

48 Bank 3A

EP4S100G3

EP4S100G4

EP4S100G5

48 Bank 3B

32 Bank 3C

32 Bank 4C

Note to Figure 2–2:

(1) There are two additional PMA-only transceiver channels in each transceiver bank.

Tab le 2 –4 summarizes the FPGA I/O usage by function on the Stratix IV GT 100G

development board. I/O direction is with respect to the FPGA.

Table 2–4. Stratix IV GT I/O Usage Summary (Part 1 of 5)

Bank 6C 22

Bank 5C 19

Bank 5B 12

Bank 5A 42

Bank

Bank

Bank

Bank

Name

4 (1)

4 (1)

4 (1)

Number

of I/Os

GXBR2

GXBR1

GXBR0

48 Bank 4A

48 Bank 4B

Function I/O Type I/O Count Description

FPGA Transceiver Clocks

Reference clock from buffer LVDS input 12 Diff REFCLK input

Programmable clock LVDS input 2 Diff REFCLK input

SMA diff clock inputs LVDS input 6 Diff REFCLK input

FPGA Global Clocks

50-MHz clock 2.5-V CMOS input 1 Global clock

Ethernet receive clock 2.5-V CMOS input 1 Global clock

Single-ended clock from buffer 2.5-V CMOS input 4 Single-ended global clock

Differential clock from buffer LVDS input 4 Diff global clock

DDR3 clock from buffer LVDS input 8 Diff global clock

QDR II clock from buffer LVDS input 8 Diff global clock

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 16

2–8 Chapter 2: Board Components

Featured Device: Stratix IV GT Device

Table 2–4. Stratix IV GT I/O Usage Summary (Part 2 of 5)

Function I/O Type I/O Count Description

SMA diff clock input LVDS input 2 Diff global clock

SMA diff I/O or clock output — 2 Diff global I/O or clock output

Flash/SSRAM

ADDR[26:1] 2.5-V CMOS input 26 Flash address bus

DATA[31:0] 2.5-V CMOS input 32 Flash data bus

SSRAM_OEn 2.5-V CMOS output 1 SSRAM output enable

SSRAM_BWn[3:0] 2.5-V CMOS output 4 SSRAM byte write select

SSRAM_BWEn 2.5-V CMOS output 1 SSRAM byte write enable

SSRAM_ADVn 2.5-V CMOS output 1 SSRAM advance input

SSRAM_ADSCn 2.5-V CMOS output 1 SSRAM address strobe from controller

SSRAM_ADSPn 2.5-V CMOS output 1 SSRAM address strobe from processor

SSRAM_CE1n 2.5-V CMOS output 1 SSRAM chip enable

SSRAM_CLK 2.5-V CMOS output 1 SSRAM clock

DDR3 SDRAM (Four each)

DDR3_BA[2:0] 1.5-V SSTL output 12 DDR3 bank address

DDR3_DQS_P/_N[3:0] Diff 1.5-V SSTL input 32 DDR3 data strobe

DDR3_ADDR[12:0] 1.5-V SSTL output 52 DDR3 address

DDR3_DQ[31:0] 1.5-V SSTL input 128 DDR3 data

DDR3_CKE 1.5-V SSTL output 4 DDR3 clock enable

DDR3_CK_P/_N Diff 1.5-V SSTL input 8 DDR3 clock

DDR3_CSn 1.5-V SSTL output 4 DDR3 chip select

DDR3_Wen 1.5-V SSTL output 4 DDR3 write enable

DDR3_RASn 1.5-V SSTL output 4 DDR3 RAS#

DDR3_CASn 1.5-V SSTL output 4 DDR3 CAS#

DDR3_RSTn 1.5-V SSTL output 4 DDR3 reset

DDR3_ODT 1.5-V SSTL output 4 DDR3 on-die termination

QDR II SRAM (Four each)

QDR2_ADDR[20:0] 1.5-V SSTL output 84 QDR II address

QDR2_Q[17:0] 1.5-V SSTL input 72 QDR II data output

QDR2_D[17:0] 1.5-V SSTL output 72 QDR II data input

QDR2_BWSn[1:0] 1.5-V SSTL output 8 QDR II byte write select

QDR2_WPSn 1.5-V SSTL output 4 QDR II write port select

QDR2_RPSn 1.5-V SSTL output 4 QDR II read port select

QDR2_K_P/_N Diff 1.5-V SSTL output 8 QDR II clock input

QDR2_CQ_P/_N Diff 1.5-V SSTL input 8 QDR II echo clock

QSFP

QSFP_RX_P/_N[3:0] Transceiver Channel 8 QSFP receive channel

QSFP_TX_P/_N[3:0] Transceiver Channel 8 QSFP transmit channel

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 17

Chapter 2: Board Components 2–9

Featured Device: Stratix IV GT Device

Table 2–4. Stratix IV GT I/O Usage Summary (Part 3 of 5)

Function I/O Type I/O Count Description

QSFP_MOD_SELn 2.5-V CMOS output 1 QSFP module select

QSFP_RSTn 2.5-V CMOS output 1 QSFP reset

QSFP_SCL 2.5-V CMOS output 1 QSFP serial 2-wire clock

QSFP_SDA 2.5-V CMOS bidirectional 1 QSFP serial 2-wire data

QSFP_INTERRUPT 2.5-V CMOS input 1 QSFP interrupt

QSFP_MOD_PRSn 2.5-V CMOS input 1 QSFP module present

QSFP_LP_MODE 2.5-V CMOS output 1 QSFP low power mode

SFP+ (Two each)

SFP_RX_P/_N Transceiver Channel 4 SFP+ receive channel

SFP_TX_P/_N Transceiver Channel 4 SFP+ transmit channel

SFP_TXDISABLE 2.5-V CMOS output 2 SFP+ transmitter disable

SFP_RATESEL[1:0] 2.5-V CMOS output 4 SFP+ rate select

SFP_MOD_ABS 2.5-V CMOS input 2 SFP+ module absent

SFP_SCL 2.5-V CMOS output 2 SFP+ serial 2-wire clock

SFP_SDA 2.5-V CMOS bidirectional 2 SFP+ serial 2-wire data

SFP_TXFAULT 2.5-V CMOS input 2 SFP+ transmitter fault

SFP_LOS 2.5-V CMOS input 2 SFP+ loss of signal

EDC

EDC_MDC 2.5-V CMOS output 1 EDC management data I/O clock

EDC_MDIO 2.5-V CMOS bidirectional 1 EDC management data I/O data

EDC_GPIO[1:0] 2.5-V CMOS input 2 EDC general purpose I/O

EDC_RESETn 2.5-V CMOS output 1 EDC reset

CFP

CFP_RX_P/_N[9:0] Transceiver Channel 20 CFP receive channel

CFP_TX_P/_N[9:0] Transceiver Channel 20 CFP transmit channel

CFP_PRG_CNTL[3:1] 2.5-V CMOS input 3 CFP programmable control I/O

CFP_PRTADR[4:0] 2.5-V CMOS output 5 CFP MDIO port address

CFP_MDC 2.5-V CMOS output 1 CFP management data I/O clock

CFP_MDIO 2.5-V CMOS bidirectional 1 CFP management data I/O data

CFP_MOD_RST 2.5-V CMOS output 1 CFP module reset

CFP_TX_DIS 2.5-V CMOS output 1 CFP transmitter disable

CFP_RX_LOS 2.5-V CMOS input 1 CFP loss of signal

CFP_PRG_ALRM[3:1] 2.5-V CMOS input 3 CFP programmable alarm

CFP_GLB_ALRM 2.5-V CMOS input 1 CFP global alarm

CFP_MOD_LOPWR 2.5-V CMOS output 1 CFP low power mode

CFP_MOD_ABS 2.5-V CMOS input 1 CFP module absent

Interlaken

INT_RX_P/_N[19:0] Transceiver channel 40 Interlaken receive channel

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 18

2–10 Chapter 2: Board Components

Featured Device: Stratix IV GT Device

Table 2–4. Stratix IV GT I/O Usage Summary (Part 4 of 5)

Function I/O Type I/O Count Description

INT_TX_P/_N[19:0] Transceiver channel 40 Interlaken transmit channel

INT_LSB_CON_TX_CLK_P/_N 1.2-V PCML 2 Interlaken reference clock input (LSB)

INT_MSB_CON_TX_CLK_P/_N 1.2-V PCML 2 Interlaken reference clock input (MSB)

INT_FLOW_CONTROL Signals 2.5-V CMOS 12 Interlaken flow control

MAX_STRATIX Bridge

FLASH_CONTROL 2.5-V CMOS output 1 FPGA flash control

MS_FLASH_BYTEN 2.5-V CMOS output 1 FPGA LCD write enable

MAX_STRATIX_RW 2.5-V CMOS output 1 FPGA Flash write enable

MAX_STRATIX_RDY 2.5-V CMOS output 1 FPGA Flash output enable

MAX_STRATIX_A[0] 2.5-V CMOS output 1 MAX output enable

MAX_STRATIX_A[1] 2.5-V CMOS output 1 MAX write enable

MAX_STRATIX_A[2] 2.5-V CMOS output 1 MAX chip select

MAX_STRATIX_A[3] 2.5-V CMOS output 1 FPGA LCD chip select

MAX_STRATIX_D[0] 2.5-V CMOS output 1 FPGA flash reset

MAX_STRATIX_D[1] 2.5-V CMOS output 1 MAX_STRATIX_D[1]

MAX_STRATIX_D[2] 2.5-V CMOS output 1 MAX_STRATIX_D[2]

MAX_STRATIX_D[3] 2.5-V CMOS output 1 MAX_STRATIX_D[3]

USB-Blaster

JTAG USB-Blaster or JTAG

header

2.5-V CMOS 5

Built-in USB-Blaster or JTAG 0.1-inch header

for debug purposes.

FPP Configuration

FPGA DCLK 2.5-V CMOS input 1 FPP Dclk

FPGA D[7:0] 2.5-V CMOS input 8 FPP data

MSEL [2:0] 2.5-V CMOS input 3 Dedicated configuration pins

NCONFIG 2.5-V CMOS input 1 Dedicated configuration pins

NSTATUS 2.5-V CMOS inout 1 Dedicated configuration pins

NCE 2.5-V CMOS input 1 Dedicated configuration pins

CONFIG_DONE 2.5-V CMOS inout 1 Dedicated configuration pins

Resets

CPU_RESETn 2.5-V CMOS input 1 Nios

®

II CPU Reset

Switches, Buttons, LEDS

User Push-buttons 2.5-V CMOS input 6 6 User Push-buttons

User DIP Switches 2.5-V CMOS input 8 8 User DIP Switches

User LEDS 2.5-V CMOS output 8 8 User LEDs (Green)

Ethernet

TXD[3:0] 2.5-V CMOS output 4 Ethernet Transmit RGMII Data Bus

TXEN 2.5-V CMOS output 1 Ethernet Transmit Enable

GTXCLK 2.5-V CMOS output 1 Ethernet Transmit Clock

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 19

Chapter 2: Board Components 2–11

MAX II CPLD EPM2210 System Controller

Table 2–4. Stratix IV GT I/O Usage Summary (Part 5 of 5)

Function I/O Type I/O Count Description

RXD[3:0] 2.5-V CMOS input 4 Ethernet Receive RGMII Data Bus

RXDV 2.5-V CMOS input 1 Receive Data Valid

RXCLK 2.5-V CMOS input 1 Receive Clock

MDC 2.5-V CMOS input 1 Ethernet MII Clock

MDIO 2.5-V CMOS bidirectional 1 Ethernet MII Data

ENET_RESET 2.5-V CMOS output 1 Ethernet reset

ENET_LED_LINK1000 2.5-V CMOS output 1 Ethernet LINK1000 LED

Device I/O Total: 916

MAX II CPLD EPM2210 System Controller

The board utilizes the EPM2210 System Controller, an Altera MAX II CPLD, for the

following purposes:

■ FPGA configuration from flash memory

■ Power consumption monitoring

■ Temp er a ture m on it or in g

■ Virtual JTAG interface for PC-based power and temperature GUI

■ Control registers for clocks

■ Control registers for Remote System Update

■ Control registers for general purpose I/O and PFL.

■ Register with CPLD design revision and board information (read-only)

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 20

2–12 Chapter 2: Board Components

MAX1619

Controller

Information

Register

EMB

Blaster

MAX II Device

Si5338

Controller

SLD-HUB

PFL

FSM BUS

Power

Measure

Results

Virtual-JTAG

PC

Temperature

Measure

Results

FPGA

LTC2418

Controller

FLASH

Decoder

Encoder

GPIO

JTAG Control

SRAM

Control

Register

Fast Configuration

Downloader

Si5338

Programmable

Oscillator

MAX II CPLD EPM2210 System Controller

Figure 2–3 illustrates the MAX II CPLD EPM2210 System Controller's functionality

and external circuit connections as a block diagram.

Figure 2–3. MAX II CPLD EPM2210 System Controller Block Diagram

Tab le 2 –5 lists the I/O signals present on the MAX

Controller. The signal names and functions are relative to the MAX

II CPLD EPM2210 System

II device (U72).

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 1 of 6)

EPM2210

Pin Number

Description Type

U72.U18 MAX_Stratix Bridge signal Bidirectional

U72.U16

U72.R13

U72.V15

U72.P13

U72.U14 EDC serial 2-wire clock Output

U72.N12 EDC serial 2-wire data Bidirectional

U72.T14 EDC write protect Output

U72.V12 50-MHz oscillator clock enable Output

U72.C2

Si5338 serial 2-wire clock for

memory PLL

Si5338 serial 2-wire data for

memory PLL

Si5338 serial 2-wire clock for

transceiver PLL

Si5338 serial 2-wire data for

transceiver PLL

Dual frequency control signal for

SFP+ interface clocks.

Output

Bidirectional

Output

Bidirectional

Output

Schematic Signal

MS_FLASH_BYTEN

SI5338_MEM_SCL

SI5338_MEM_SDA

SI5338_PLL_SCL

SI5338_PLL_SDA

CLK_SFP_SEL

Name

EDC_SCL

EDC_SDA

EDC_WP

CLK50_EN

Stratix IV

GT Device

Pin Name

U44.AP34 —

— U22.12, U56.12

— U22.19, U56.19

— U21.12

— U21.19

— U32.J1, U34.6

— U32.H1, U34.5

— U34.7

— X3.1

— U46.2

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Other

Connections

Page 21

Chapter 2: Board Components 2–13

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 2 of 6)

EPM2210

Pin Number

Description Type

U72.J13 50-MHz clock input Input

U72.H17 FPGA initialization LED Output

U72.J1 Power monitor SPI clock Output

U72.H6 Power monitor SPI input data Output

U72.K1 Power monitor SPI output data Input

U72.M3 Loads factory image into the FPGA Output

U72.A9 FSM bus flash byte enable feature Output

U72.D9 FSM bus flash chip enable Input

Control signal from the FPGA to

U72.R14

indicate flash information being

passed through the MAX_STRATIX

Output

interface.

U72.E9 FSM bus flash output enable Output

U72.B9 FSM bus flash ready Output

U72.F9 FSM bus flash reset Output

U72.A8 FSM bus flash write enable Output

U72.B15 FPGA configuration done Input

U72.A15 Initiates new image to the FPGA Output

U72.B18 FPGA configuration data Output

U72.D14 FPGA configuration data Output

U72.A17 FPGA configuration data Output

U72.E13 FPGA configuration data Output

U72.B16 FPGA configuration data Output

U72.D13 FPGA configuration data Output

U72.C15 FPGA configuration data Output

U72.F12 FPGA configuration data Output

U72.C14 FPGA configuration clock Output

U72.E12 FPGA configuration error Input

U72.E11 FSM bus flash address Bidirectional

U72.B14 FSM bus flash address Bidirectional

U72.B13 FSM bus flash address Bidirectional

U72.A12 FSM bus flash address Bidirectional

U72.A13 FSM bus flash address Bidirectional

U72.C13 FSM bus flash address Bidirectional

U72.C12 FSM bus flash address Bidirectional

U72.D10 FSM bus flash address Bidirectional

U72.A7 FSM bus flash address Bidirectional

U72.B6 FSM bus flash address Bidirectional

U72.B7 FSM bus flash address Bidirectional

Schematic Signal

Name

CLKIN_50_MAX

CONFIGN_LED

CSENSE_SCK

CSENSE_SDI

CSENSE_SDO

FACTORY

FLASH_BYTEN

FLASH_CEN

FLASH_CONTROL

FLASH_OEN

FLASH_RDYBSYN

FLASH_RESETN

FLASH_WEN

FPGA_CONF_DONE

FPGA_CONFIGN

FPGA_DATA0

FPGA_DATA1

FPGA_DATA2

FPGA_DATA3

FPGA_DATA4

FPGA_DATA5

FPGA_DATA6

FPGA_DATA7

FPGA_DCLK

FPGA_STATUSN

FSM_A1

FSM_A2

FSM_A3

FSM_A4

FSM_A5

FSM_A6

FSM_A7

FSM_A8

FSM_A9

FSM_A10

FSM_A11

Stratix IV

GT Device

Pin Name

Other

Connections

— U67.5

— U40.2

— U61.5

— U61.4

— U62.5

— S12.2

—U65.F7

—U65.F2

U44.AR34 —

— U65.G2

— U65.A4

— U65.B5

— U65.A5

U44.AW38 TP7

U44.BA36 TP10

U44.AA33 TP13

U44.Y32 TP14

U44.P38 TP15

U44.P37 TP16

U44.U38 TP17

U44.U37 TP18

U44.R40 TP19

U44.P39 TP20

U44.AY9 TP9

U44.AY36 TP11

U44.AR6 U65.E2

U44.AL13 U65.E2, U57.R6

U44.AV6 U65.C2, U57.P6

U44.AN6 U65.A2, U57.A2

U44.AA14 U65.B2, U57.A10

U44.AN39 U65.D3, U57.B2

U44.T6 U65.C3, U57.B10

U44.P7 U65.A3, U57.P2

U44.Y14 U65.B6, U57.N6

U44.AA31 U65.A6, U57.P3

U44.AJ7 U65.C6, U57.P4

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 22

2–14 Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 3 of 6)

EPM2210

Pin Number

Description Type

U72.C7 FSM bus flash address Bidirectional

U72.A5 FSM bus flash address Bidirectional

U72.B5 FSM bus flash address Bidirectional

U72.A4 FSM bus flash address Bidirectional

U72.A6 FSM bus flash address Bidirectional

U72.B3 FSM bus flash address Bidirectional

U72.B11 FSM bus flash address Bidirectional

U72.E8 FSM bus flash address Bidirectional

U72.C8 FSM bus flash address Bidirectional

U72.C11 FSM bus flash address Bidirectional

U72.B8 FSM bus flash address Bidirectional

U72.C4 FSM bus flash address Bidirectional

U72.B4 FSM bus flash address Bidirectional

U72.A2 FSM bus flash address Bidirectional

U72.B1 FSM bus flash address Bidirectional

U72.E10 FSM bus flash data Bidirectional

U72.A14 FSM bus flash data Bidirectional

U72.F10 FSM bus flash data Bidirectional

U72.F11 FSM bus flash data Bidirectional

U72.C5 FSM bus flash data Bidirectional

U72.D7 FSM bus flash data Bidirectional

U72.F7 FSM bus flash data Bidirectional

U72.C6 FSM bus flash data Bidirectional

U72.D11 FSM bus flash data Bidirectional

U72.B12 FSM bus flash data Bidirectional

U72.F8 FSM bus flash data Bidirectional

U72.E7 FSM bus flash data Bidirectional

U72.D8 FSM bus flash data Bidirectional

U72.D5 FSM bus flash data Bidirectional

U72.D6 FSM bus flash data Bidirectional

U72.E6 FSM bus flash data Bidirectional

FPGA initialization done LED.

U72.H13

Indicates that the FPGA is in user

Output

mode

Schematic Signal

Name

FSM_A12

FSM_A13

FSM_A14

FSM_A15

FSM_A16

FSM_A17

FSM_A18

FSM_A19

FSM_A20

FSM_A21

FSM_A22

FSM_A23

FSM_A24

FSM_A25

FSM_A26

FSM_D0

FSM_D1

FSM_D2

FSM_D3

FSM_D4

FSM_D5

FSM_D6

FSM_D7

FSM_D8

FSM_D9

FSM_D10

FSM_D11

FSM_D12

FSM_D13

FSM_D14

FSM_D15

INIT_DONE_LED

Stratix IV

GT Device

Pin Name

Other

Connections

U44.AK6 U65.D6, U57.P8

U44.Y6 U65.B7, U57.P9

U44.AA6 U65.A7, U57.P10

U44.AF6 U65.C7, U57.P11

U44.AG6 U65.D7, U57.R2

U44.AD14 U65.E7, U57.R3

U44.AE14 U65.B3, U57.R4

U44.AE6 U65.C4, U57.R8

U44.AA7 U65.D5, U57.R9

U44.AD7 U65.D4, U57.R10

U44.AG7 U65.C5, U57.R11

U44.AJ6 U65.B8, U57.B1

U44.AH6 U65.C8, U57.A1

U44.Y15 U65.F8, U57.B11

U44.AA15 U65.G8

U44.AP9 U65.E3, U57.J10

U44.AR8 U65.H3, U57.J11

U44.N6 U65.E4, U57.K10

U44.P6 U65.H4, U57.K11

U44.AV8 U65.H5, U57.L10

U44.AV7 U65.E5, U57.L11

U44.AV10 U65.H6, U57.M10

U44.AU10 U65.E6, U57.M11

U44.AW8 U65.F3, U57.D10

U44.AW9 U65.G3, U57.D11

U44.AU9 U65.F4, U57.E10

U44.AU8 U65.G4, U57.E11

U44.AR7 U65.F5, U57.F10

U44.AT8 U65.G6, U57.F11

U44.AT6 U65.F6, U57.G10

U44.AT7 U65.G7, U57G11

— D39.2

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 23

Chapter 2: Board Components 2–15

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 4 of 6)

EPM2210

Pin Number

U72.N17

Description Type

Bidirectional

U72.M13 Bidirectional

U72.N18 Bidirectional

U72.M12 Bidirectional

U72.M16 Bidirectional

U72.L16 Bidirectional

U72.M17 Bidirectional

Spare I/Os on the MAX II device and

is designed as an I/O expander for

the FPGA. Data can be passed

through the MAX_STRATIX

interface.

U72.L15 Bidirectional

U72.M18 Bidirectional

U72.L14 Bidirectional

U72.M5

Initiates a load of the selected image

from the PFL

Input

Control signal between the MAX II

U72.R16

system controller and the MAX II

embedded USB-Blaster to indicate

Input

that configuration is done.

FPGA configuration done LED.

U72.T16

Indicates that the FPGA is loaded

Output

with the new image.

U72.T17 FPGA configuration error LED Output

U72.R15 FPGA configuration active LED Output

U72.V10 FPGA to MAX II I/O expander

U72.P10 Input

address bus

Input

U72.U11 Input

U72.R10 Input

U72.T15 FPGA to MAX II I/O expander data

U72.R12 Bidirectional

bus

Bidirectional

U72.V14 Bidirectional

U72.P12 Bidirectional

U72.T13

MAX_STRATIX interface ready

indicator

Input

Read-write signal for

MAX_STRATIX interface.

U72.V17

Control signal from the FPGA to

Input

indicate that the FPGA is accessing

the flash in BYTE mode.

U72.C17

U72.N1

Over-temperature indicator from the

temperature sense circuit

Push-button to select which image

to program into the FPGA

Input

Input

Schematic Signal

Name

LINE_SIDE0

LINE_SIDE1

LINE_SIDE2

LINE_SIDE3

LINE_SIDE4

LINE_SIDE5

LINE_SIDE6

LINE_SIDE7

LINE_SIDE8

LINE_SIDE9

LOAD

MAX_2_MAX_INITD

ONE

MAX_CONF_DONEn

MAX_ERROR

MAX_LOAD

MAX_STRATIX_A0

MAX_STRATIX_A1

MAX_STRATIX_A2

MAX_STRATIX_A3

MAX_STRATIX_D0

MAX_STRATIX_D1

MAX_STRATIX_D2

MAX_STRATIX_D3

MAX_STRATIX_RDY

MAX_STRATIX_RW

OVERTEMPn

PGM_SEL

Stratix IV

GT Device

Pin Name

Other

Connections

—J48.1

—J48.3

—J48.5

—J48.7

—J48.9

— J48.11

— J48.13

— J48.15

— J48.17

— J48.19

— S11.2

—U80.J6

— D37.2

— D38.2

— D36.2

U44.AN34 —

U44.AN33 —

U44.AT39 —

U44.AU39 —

U44.AF38 —

U44.W38 —

U44.AG31 —

U44.AK39 —

U44.AU37 —

U44.AU36 —

—

U70.4, D18.2,

D42.2

— S10.2

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 24

2–16 Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 5 of 6)

EPM2210

Pin Number

Description Type

Single-ended clock input (limited to

U72.J6

300 MHz) in the MAX II device from

Input

clock tree A structure.

Single-ended clock input (limited to

U72.K6

300 MHz) in the MAX II device from

Input

clock tree B structure.

U72.H5

U72.J2

U72.G18

Chip select for the first current

sense ADC

Chip select for the second current

sense ADC

Status indicator for programming

the FPGA

Output

Output

Output

U72.E15 Temperature sense clock Output

U72.C16 Temperature sense data Bidirectional

U72.K4

Bidirectional

U72.L2 Bidirectional

U72.L6 Bidirectional

U72.L3 Bidirectional

U72.L5 Bidirectional

U72.M1 Bidirectional

U72.L4 Bidirectional

U72.M2 Bidirectional

USB control and data interface.

Connects to the MAX II embedded

USB-Blaster to pass USB data.

U72.K2 Output

U72.L1 Output

U72.J5 Input

U72.K3 Input

U72.K5 Output

U72.R6 User DIP switch Input

U72.U4 User DIP switch Input

U72.T6 User DIP switch Input

U72.V4 User DIP switch Input

U72.N7 User DIP switch Input

U72.T5 User DIP switch Input

U72.P7 User DIP switch Input

U72.U5 User DIP switch Input

U72.C10 User LED Output

U72.A11 User LED Output

U72.C9 User LED Output

U72.B10 User LED Output

U72.U3 User push-button Input

Schematic Signal

Name

SE_CLKA_MAX

SE_CLKB_MAX

SENSE_CE0

SENSE_CE1

STATUSN_LED

TSENSE_SMB_CLK

TSENSE_SMB_DATA

USB_MAX_D0

USB_MAX_D1

USB_MAX_D2

USB_MAX_D3

USB_MAX_D4

USB_MAX_D5

USB_MAX_D6

USB_MAX_D7

USB_MAX_PWR_ENn

USB_MAX_RDn

USB_MAX_RXFn

USB_MAX_TXEn

USB_MAX_WR

USER_DIPSW0

USER_DIPSW1

USER_DIPSW2

USER_DIPSW3

USER_DIPSW4

USER_DIPSW5

USER_DIPSW6

USER_DIPSW7

USER_LED0

USER_LED1

USER_LED2

USER_LED3

USER_PB0

Stratix IV

GT Device

Pin Name

Other

Connections

— U14.19

— U17.19

— U63.4

— U62.4

— D41.2

— U70.8

— U70.7

— U80.L11

— U80.C11

— U80.D11

— U80.E11

— U80.F11

— U80.H11

— U80.L7

— U80.L8

— U80.L3

— U80.L5

— U80.L2

— U80.L4

— U80.L6

—SW3.1

—SW3.2

—SW3.3

—SW3.4

—SW3.5

—SW3.6

—SW3.7

—SW3.8

— D24.2

— D23.2

— D22.2

— D21.2

— S4.2

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 25

Chapter 2: Board Components 2–17

Configuration, Status, and Setup Elements

Table 2–5. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 6 of 6)

EPM2210

Pin Number

U72.P6 User push-button Input

U72.T4 User push-button Input

U72.R7 User push-button Input

U72.N3

U72.N5 Output

U72.N2 Output

U72.M4

U72.H1

U72.G7 Output

U72.J3 Output

U72.G6 LCD data bus Output

U72.H2 LCD data bus Output

U72.G5 LCD data bus Output

U72.H3 LCD data bus Output

U72.G4 LCD data bus Output

U72.G1 LCD data bus Output

U72.F6 LCD data bus Output

U72.G2 LCD data bus Output

Indicates which user Programmer

Object File (.pof) is loaded into the

FPGA

Indicates that factory .pof is loaded

into the FPGA

LCD control signals

Description Type

Output

Output

Output

Schematic Signal

Name

USER_PB1

USER_PB2

USER_PB3

USER1_POF

USER2_POF

USER3_POF

FACTORY_POF

LCD_CSn

LCD_D_Cn

LCD_WEn

LCD_DATA0

LCD_DATA1

LCD_DATA2

LCD_DATA3

LCD_DATA4

LCD_DATA5

LCD_DATA6

LCD_DATA7

Stratix IV

GT Device

Pin Name

— S3.2

— S2.2

— S1.2

— D19.2

— D20.2

— D25.2

— D26.2

—J59.6

—J59.4

—J59.5

—J59.7

—J59.8

—J59.9

— J59.10

— J59.11

— J59.12

— J59.13

— J59.14

Other

Connections

Tab le 2 –6 lists the MAX II CPLD EPM2210 System Controller component reference

and manufacturing information.

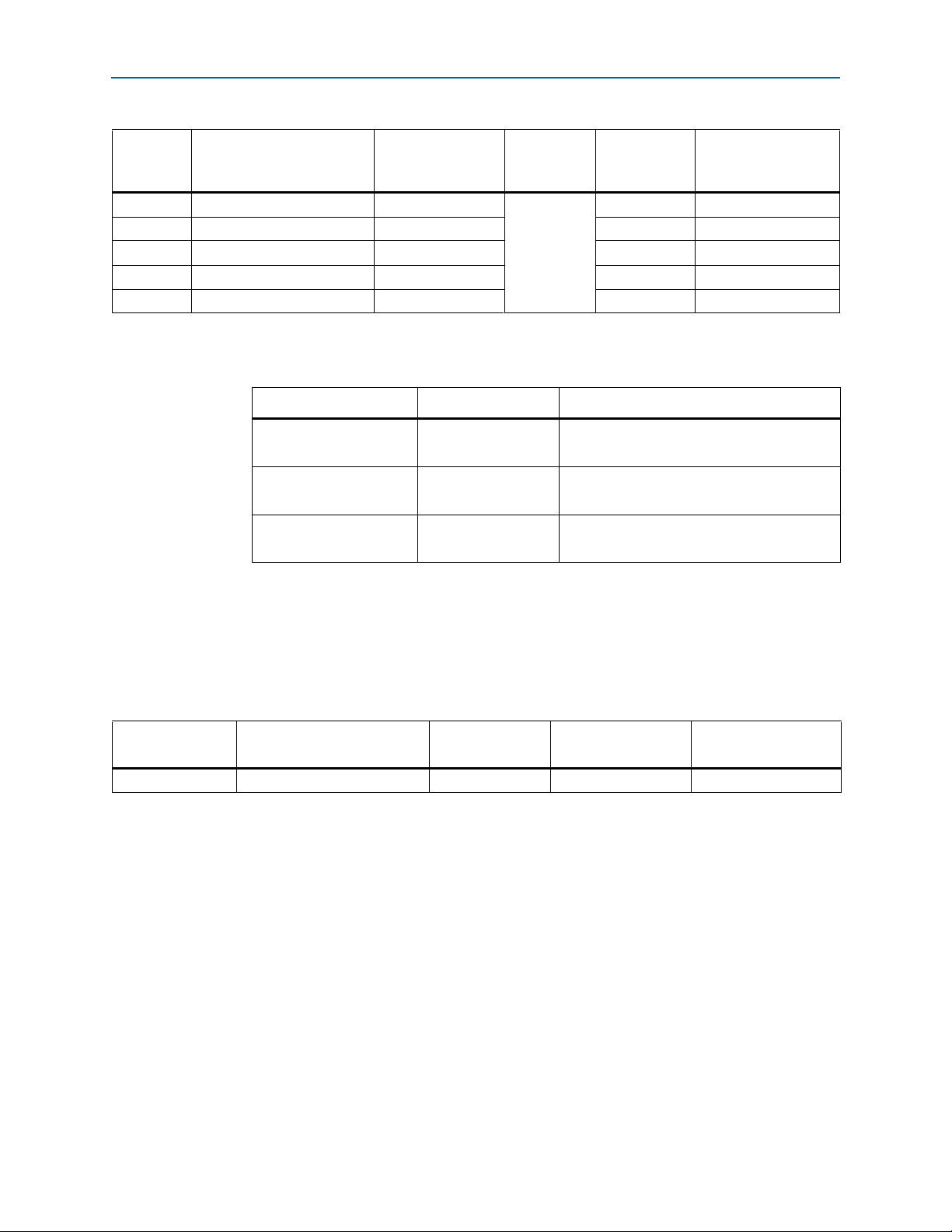

Table 2–6. MAX II CPLD EPM2210 System Controller Component Reference and Manufacturing Information

Board Reference Description Manufacturer

U72

IC - MAX II CPLD EPM2210

256FBGA -3 LF 1.8V VCCINT

Corporation EPM2210F256C3N www.altera.com

Altera

Manufacturing

Part Number

Manufacturer

Configuration, Status, and Setup Elements

This section describes the board’s configuration, status, and setup elements.

Configuration

The Stratix IV GT 100G development board supports three configuration methods:

■ Embedded USB-Blaster is the default method for configuring the FPGA at any

time using the Quartus II Programmer in JTAG mode with the supplied USB cable.

■ MAX II+Flash Fast Passive Parallel (FPP) download is used for configuring the

FPGA using stored images from flash memory on either power-up or pressing the

load (S11) push-button.

Website

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 26

2–18 Chapter 2: Board Components

USB Type-B

Connector

(J60)

FTDI

FT245BL

USB PHY

(U79)

USB FIFO BUS

EPM240M

MAX II

CPLD

JTAG

JTAG

JTAG Programming

Header (J61)

USB

Stratix IV GT

FPGA (U44)

■ JTAG programming header (J61) is used for configuring the FPGA using an

Configuration, Status, and Setup Elements

external USB-Blaster (not supplied) and the Quartus II Programmer.

The following sections describe each of these methods.

Embedded USB-Blaster

Figure 2–4 shows the block diagram for the embedded USB-Blaster. The USB-Blaster

is implemented using a USB Type-B connector (J60), a Future Technologies FT245BL

USB PHY device (U79), and an Altera EPM240M100C4N MAX II CPLD. This allows

the configuration of the FPGA using a USB cable directly connected between the USB

port on the board and a USB port of a PC running the Quartus II software.

The embedded USB-Blaster is automatically disabled when an external USB-Blaster is

connected to the JTAG chain at the JTAG programming header (J61).

Figure 2–4. Embedded USB-Blaster

Fast Passive Parallel Download

Figure 2–5 shows the block diagram for the MAX II+Flash FPP configuration. This

method is used for automatic configuration of the FPGA upon board power-up or

reset with the configuration programming image stored in the flash memory. The FPP

download controller is implemented within an Altera EPM240M100C4N MAX II

CPLD (U72). This CPLD controller, together with the Numonyx PC28F00AM29EWL

1-Gb CFI NOR-type flash memory (U65), performs the FPP configuration upon board

power-up or reset. The CPLD shares the flash interface with the FPGA. The

configuration program select push-button, PGM_SEL, (S10) selects between two .pof

files (factory or user) stored in the flash. The FPP controller uses the Altera Parallel

Flash Loader (PFL) megafunction to configure the FPGA by reading data from the

flash and converting it to FPP format. This data is written to the FPGA’s dedicated

configuration pins during configuration.

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 27

Chapter 2: Board Components 2–19

J61

U44

Stratix IV GT

Stratix IV GT

and MAX II

JTAG

Programming

Header

Jumper to remove

MAX II CPLD from

JTAG Programming Header

TDI

TMS

TCK

LAST_TDO

S4GT_TDI

S4GT_TDO

JTAG_TMS

JTAG_TCK

JTAG_TMS

JTAG_TCK

MAX_FPP_TDI

MAX_FPP_TDO

U72

MAX II CPLD

9

5

1

3

Configuration, Status, and Setup Elements

Figure 2–5 shows the MAX II+Flash FPP configuration.

Figure 2–5. MAX II+Flash FPP Configuration

FPP Configuration

Load

Push-Button (S11)

PGM_SEL

Push-Button (S10)

MAX II CPLD

(U72)

(D26)

USER_POF LED

FACTORY_POF LED

(D38)

(D19, D20, D25)

MAX_ERROR LED

Flash

Flash

Flash

(U65)

Stratix IV GT

FPGA

(U44)

After a power-up or load event, the MAX II CPLD (U72) automatically configures the

FPGA in FPP mode with either the pre-installed factory .pof file or a user .pof file.

Additionally, three green configuration status LEDs (D39, D40, D41) indicate the

status of the FPP configuration.

After configuration completes, you can determine which .pof image is loaded into the

FPGA by observing the

USER3_POF

LEDs (D19, D20, D25).

JTAG Programming Header

Figure 2–6 shows the schematic connections for the dedicated JTAG programming

header (J61). This header provides another method for configuring the FPGA (U44)

using an Altera USB-Blaster with the Quartus II Programmer running on a PC. The

MAX II JTAG configuration jumper allows the MAX II CPLD device to be removed

from the JTAG chain so that the FPGA is the only device on the JTAG chain.

Figure 2–6. JTAG Programming Header

FACTORY_POF

LED (D26) or the

USER1_POF, USER2_POF

,

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 28

2–20 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Status Elements

The development board includes board-specific status LEDs and switches for

enabling and configuring various features on the board, as well as a 16 character × 2

line LCD for displaying board power and temperature measurements. This section

describes these status and setup elements.

Status LEDs

Surface mount LEDs indicate the various status of the board. A logic 0 is driven on the

I/O port to turn the LED on while a logic 1 is driven to turn the LED off.

Tab le 2 –7 lists the LED board references, names, and functional descriptions.

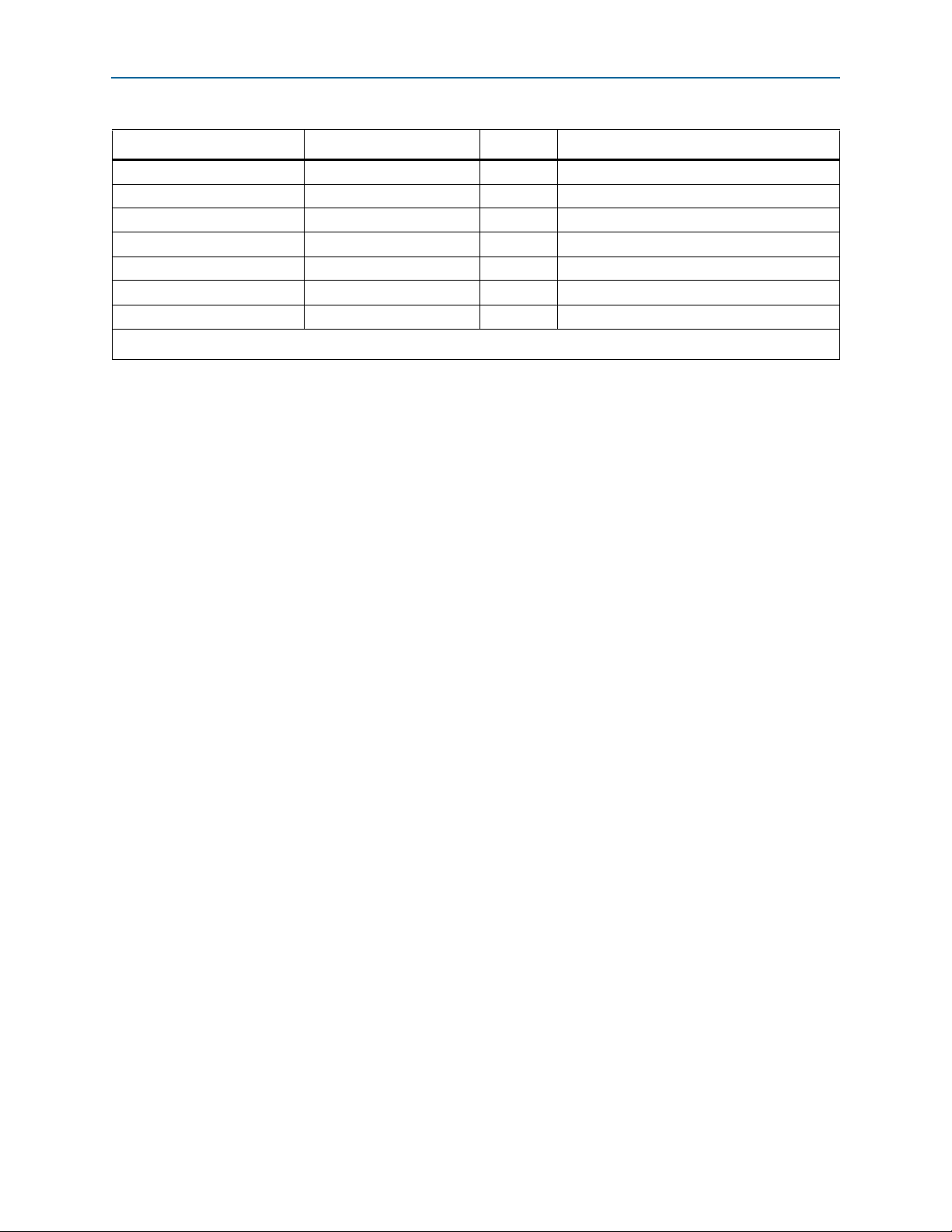

Table 2–7. Status LEDs

Board

Reference

D7 Power

D12 DUPLEX

D13 1000

D14 100

D15 10

D16 TX

D17 RX

D19,

D20,

D25

D26 Factory

D27 USB

LED Name LED Description

Blue LED. Illuminates when the board

power switch (SW1) is on. Driven by the

3.3-V regulator.

Green LED. Illuminates to indicate Ethernet

full duplex status. Driven by the Marvell

88E1111 PHY.

Green LED. Illuminates to indicate Ethernet

linked at 1000-Mbps connection speed.

Driven by the Marvell 88E1111 PHY.

Green LED. Illuminates to indicate Ethernet

linked at 100-Mbps connection speed.

Driven by the Marvell 88E1111 PHY.

Green LED. Illuminates to indicate Ethernet

linked at 10-Mbps connection speed.

Driven by the Marvell 88E1111 PHY.

Green LED. Blinks to indicate Ethernet PHY

transmit activity. Driven by the Marvell

88E1111 PHY.

Green LED. Blinks to indicate Ethernet PHY

receive activity. Driven by the Marvell

88E1111 PHY.

Green LED. Illuminates when the user .pof

User

image is successfully programmed into the

FPGA.

Green LED. Illuminates when the factory

.pof image is successfully programmed

into the FPGA.

Green LED. Blinks to indicate the

embedded USB-Blaster activity.

Schematic

Signal Name

———

ENET_LED_DUPLEX

ENET_LED_LINK1000

ENET_LED_LINK100

ENET_LED_LINK10

ENET_LED_TX

ENET_LED_RX

USER1_POF

USER2_POF

USER3_POF

FACTORY_POF

USB_LED

I/O

Standard

2.5-V

CMOS

3.3-V

CMOS

Other

Connections

U66.60,

U66.70

U66.73,

U44.AU35

U66.74,

U44.AU35

U66.64,

U66.76

U66.68,

U66.61

U66.69,

U66.65

U72.N3

U72.N5

U72.N2

U72.M4

U80.L1

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 29

Chapter 2: Board Components 2–21

Configuration, Status, and Setup Elements

Table 2–7. Status LEDs

Board

Reference

LED Name LED Description

Schematic

Signal Name

I/O

Standard

Other

Connections

Green LED. Illuminates when the MAX II

D36 Loading

CPLD is actively configuring the FPGA.

Driven by the MAX II System Controller

MAX_LOAD

U72.R15

CPLD.

D37 MAX_CONF

Green LED. Illuminates when the FPGA is

successfully configured. Driven by the

FPGA.

MAX_CONF_DONE

2.5-V

CMOS

U72.H17

Red LED. Illuminates when the MAX II

D38 Error

CPLD EPM2210 System Controller fails to

configure the FPGA. Driven by the MAX II

MAX_ERROR

U72.T17

CPLD EPM2210 System Controller.

Tab le 2 –8 lists the board-specific LEDs component references and manufacturing

information.

Table 2–8. Status LEDs Component References and Manufacturing Information

Board Reference

D12–D17, D19, D20, D25,

D26, D27, D36, D37

Device

Description

Manufacturer

Manufacturer

Part Number

Green LEDs Lumex Inc. SML-LX1206GC-TR www.lumex.com

Manufacturer

Website

D38 Red LED Lumex Inc. SML-LX1206IC-TR www.lumex.com

D7 Blue LED Lumex Inc. SML-LX1206USBC-TR www.lumex.com

Board Jumpers

Tab le 2 –9 lists the board jumper references, names, and functional descriptions.

Table 2–9. Board Jumpers

Board

Reference Jumper Name Description

J41

MAXII BYPASS

■ Jumper installed – the MAX II CPLD device (U72) is included in the JTAG

programming chain.

■ Jumper removed – the MAX II CPLD device (U72) is removed from the JTAG

programming chain.

J40

USB_DISABLEn

■ Jumper installed – the embedded USB-Blaster is disabled.

■ Jumper removed (default) – the embedded USB-Blaster is enabled.

Push-Button Switches

Board reference S9 is the CPU reset push-button switch, CPU_RESETn, which is an

input to the Stratix IV GT device. The CPU_RESETn is intended to be the master reset

signal for the FPGA design loaded into the Stratix IV GT device. The CPU_RESETn

signal must be enabled within the Quartus II software for this reset function to work.

Otherwise, the CPU_RESETn acts as a regular I/O pin. When enabled in the Quartus

II software, and then set to logic 1 on the board, this switch resets every register

within the FPGA.

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 30

2–22 Chapter 2: Board Components

Configuration, Status, and Setup Elements

Board references S10-S12 are push-button switches for MAX II+Flash FPP

configuration. Use the

PGM_SEL

(S10) push-button to select the configuration

programming image stored in the flash memory.

Tab le 2 –1 0 lists the push-button switches references, names, and functional

descriptions.

Table 2–10. Push-Button Switches

Board Reference Push-Button Switch Name Description

S9

S10

S11

S12

CPU_RESETn

PGM_SEL

LOAD

FACTORY

Reset signal for the FPGA.

Selects between two .pof files (factory or user) stored in the flash.

Initiates loading of the FPGA.

Initiates loading of factory design into the FPGA.

Tab le 2 –11 lists the push-button switches component references and the

manufacturing information.

Table 2–11. Push-Button Switches Component References and Manufacturing Information

Board Reference Device Description Manufacturer

S9–S12 Push-Button switches Panasonic Corporation EVQPAC07K www.panasonic.com

Manufacturer

Part Number

Manufacturer

Setup Elements

The development board includes the board settings DIP switch as part of the setup

elements.

Board settings DIP switch

The development board includes a board settings DIP switch which controls various

features specific to the board and the MAX

design.

Tab le 2 –1 2 lists the board settings DIP switch controls and descriptions.

Table 2–12. Board Settings DIP Switch Controls

Board

Reference

SW2.1

SW2.2

SW2.3

SW2.4

Disables the embedded USB-Blaster. USB_DISABLEn

Selects SMA or PLL for the

differential clock that goes to the

global clock inputs of clock A tree

structure.

Selects SMA or PLL that goes to the

transceivers of clock A tree structure.

Selects SMA or PLL for the

single-ended clock that goes to the

global clock inputs of clock A tree

structure.

Description

Schematic Signal

Name

DIFFCLKA_SEL

REFCLKA_SEL

SE_CLKA_SEL

II CPLD EPM2210 System Controller logic

I/O

Standard

2.5-V

Other

Connections

U80.H2

U19.3

U15.3

U14.3

Website

Settings (1)

1: Enabled

0: Disabled

1: PLL input

0: SMA input

1: PLL input

0: SMA input

1: SMA input

0: PLL input

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 31

Chapter 2: Board Components 2–23

Configuration, Status, and Setup Elements

Table 2–12. Board Settings DIP Switch Controls

Board

Reference

SW2.5

Description

Selects SMA or PLL for the

differential clock that goes to the

global clock inputs of clock B tree

Schematic Signal

Name

DIFFCLKB_SEL

I/O

Standard

Other

Connections

U18.3

structure.

SW2.6

SW2.7

Selects SMA or PLL that goes to the

transceivers of clock B tree structure.

Selects SMA or PLL for the

single-ended clock that goes to the

global clock inputs of clock B tree

REFCLKB_SEL

SE_CLKB_SEL

U20.28

2.5-V

U17.3

structure.

SW2.8

Note to Table 2–12:

(1) When the switch is in the OFF position, a logic 1 is selected while in the ON position, a logic 0 is selected.

Enables the 644.53125-MHz clock. CLK644_EN

X1.1

Tab le 2 –1 3 lists the board settings DIP switch component reference and

manufacturing information.

Table 2–13. Board Settings DIP Switch Component References and Manufacturing Information

Board

Reference

Device Description Manufacturer

Manufacturer

Part Number

Manufacturer Website

SW2 DIP switch Grayhill Corporation 76SB08ST www.grayhill.com

Settings (1)

1: PLL input

0: SMA input

1: SMA input

0: PLL input

1: SMA input

0: PLL input

1: Enabled

0: Disabled

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 32

2–24 Chapter 2: Board Components

Optical Clock B Out

(For Divide-by-4 Circuit)

Reference Clock A Out

(For Interlaken Side)

Reference Clock A In

(For Interlaken Side)

Buffered Differential

Clock A Out

Differential

Clock A In

Buffered Differential

Clock B Out

Differential

Clock B In

Reference Clock B

In (For Line Side)

Reference Clock B

Out (For Line Side)

644-MHz Clock Out

Single-Ended Clock In/Out B

Single-Ended Clock In/Out A

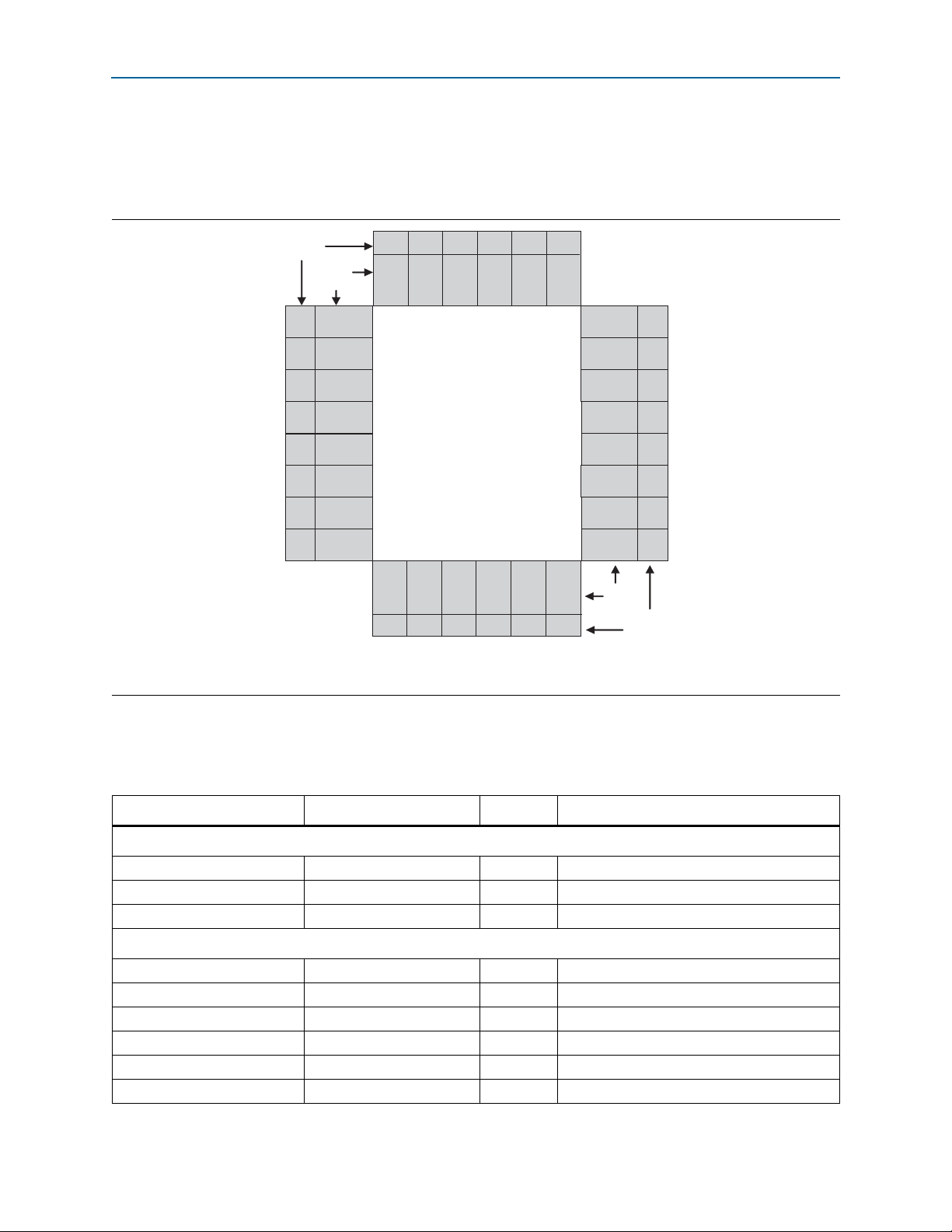

Clock Circuitry

Clock Circuitry

This section describes the clock tree structure for the Stratix IV GT 100G Development

board.

Figure 2–7 shows the Stratix IV GT 100G development board clock circuitry.

Figure 2–7. Stratix IV GT 100G Development Board Clock Circuitry

The clock tree structure for the board is distributed into two—clock A and clock B.

Clock A is for the Interlaken interface and clock B is for the line side interface. The

PLL/buffer device (Si5338) sources both clock trees which is then distributed to the

reference clock buffer (

DIFF_CLK

buffer fans out the clock to dedicated clock inputs on the vertical I/Os of the

FPGA. A third differential clock from the

clock buffer (

SE_CLK

REF_CLK

). The

) and to the differential clock buffer (

SE_CLK

DIFF_CLK

buffer distributes the clock to every side of the

buffer goes to the single-ended

DIFF_CLK

). The

FPGA.

The

REF_CLK

and 2 on the right side of the FPGA (or left side of the die). The

for clock A tree structure distributes its input clock to transceiver block 1

REF_CLK

for clock B

tree structure distributes the clock to all four transceiver blocks on the left side of the

FPGA (or right side of the die).

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 33

Chapter 2: Board Components 2–25

Reference

Clock

PLL

LVPECL

to

LVDS

Differential

Clock

Single-Ended

Clock

25 MHz

LVCMOS

644 MHz

Reference

Clock

PLL

Differential

Clock

LVPECL

25 MHz

(Same

oscillator as

in Clock A)

Divide-by-4

Circuit

LVDS

Clock A

Clock B

LVDS

LVDS

LVDS

LVDS

LVDS

LVDS

LVDS

LVDS

LVDS

LVDS

Interlaken Side

Line Side

LVPECL

LVPECL

Single-Ended

Clock

LVCMOS

XFP

CFP

Si5338

(Part A)

Si5338

(Part B)

Clock Circuitry

Figure 2–7 shows the Stratix IV GT 100G development board clock tree structure.

Figure 2–8. Stratix IV GT 100G Development Board Clock Tree Structure

The clock distribution path is done using the board settings DIP switch (SW2). This

DIP switch is located near the differential clock buffer B. Refer to Ta bl e 2– 12 on the

switch settings and descriptions. The

USB_DISABLEn

DIP switch is connected to the

MAX II device and controls the traffic that passes through the USB connector.

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 34

2–26 Chapter 2: Board Components

Clock Circuitry

Two PLL/buffer devices (Si5338) drive the DDR3 and QDR II interfaces clocks

directly to the FPGA clock pins (as shown in the Figure 2–9).

Figure 2–9. Memory Clocks

DDR3 Clocks

PLL

Stratix IV GT

25 MHz

Si5338

QDR II Clocks

PLL

Stratix IV GT

25 MHz

Si5338

Tab le 2 –1 4 lists the clock signal names, board references, and functional descriptions.

Table 2–14. Spread Spectrum Configuration DIP Switch Pin-Out (SW2) (Part 1 of 3)

Stratix IV

Board

Reference Description

U21.9 XCVR PLL clock for differential clock

Schematic

Signal Name

BUFFA1_DIFF_CLK_P

I/O

Standard

GT Device

Pin Name

— U19.6

buffer A

U21.10 XCVR PLL clock for differential clock

BUFFA1_DIFF_CLK_N — U19.7

buffer A

U21.13 XCVR PLL clock for reference clock

BUFFA2_REF_CLK_P — U15.6

buffer A

U21.14 XCVR PLL clock for reference clock

BUFFA2_REF_CLK_N — U15.7

buffer A

U21.17 XCVR PLL clock for differential clock

BUFFB1_DIFF_CLK_P — U18.6

buffer B

U21.18 XCVR PLL clock for differential clock

buffer B

U21.21 XCVR PLL clock for reference clock

BUFFB1_DIFF_CLK_N — U18.7

BUFFB2_REF_CLK_P — U20.16

LVDS

buffer B

U21.22 XCVR PLL clock for reference clock

BUFFB2_REF_CLK_N — U20.15

buffer B

U22.9 DDR3 PLL clock A DDR3_CLKA_P J21 —

U22.10 DDR3 PLL clock A DDR3_CLKA_N J20 —

U22.13 DDR3 PLL clock B DDR3_CLKB_P N24 —

U22.14 DDR3 PLL clock B DDR3_CLKB_N N23 —

U22.17 DDR3 PLL clock C DDR3_CLKC_P M22 —

U22.18 DDR3 PLL clock C DDR3_CLKC_N M21 —

U22.21 DDR3 PLL clock D DDR3_CLKD_P R23 —

Other

Connections

100G Development Kit, Stratix IV GT Edition Reference Manual September 2010 Altera Corporation

Page 35

Chapter 2: Board Components 2–27

Clock Circuitry

Table 2–14. Spread Spectrum Configuration DIP Switch Pin-Out (SW2) (Part 2 of 3)

Stratix IV

Board

Reference Description

U22.22 DDR3 PLL clock D DDR3_CLKD_N

Schematic

Signal Name

I/O

Standard

GT Device

Pin Name

P23 —

Other

Connections

U56.9 QDR II PLL clock A QDR2_CLKA_P AK21 —

U56.10 QDR II PLL clock A QDR2_CLKA_N AL22 —

U56.13 QDR II PLL clock B QDR2_CLKB_P AJ22 —

U56.14 QDR II PLL clock B QDR2_CLKB_N AK22 —

U56.17 QDR II PLL clock C QDR2_CLKC_P AJ24 —

U56.18 QDR II PLL clock C QDR2_CLKC_N AK23 —

U56.21 QDR II PLL clock D QDR2_CLKD_P AK24 —

U56.22 QDR II PLL clock D QDR2_CLKD_N AL25 —

U18.4 SMA input for differential clock buffer B SMA_DIFF_CLKIN_P1 —J19.1

U18.5 SMA input for differential clock buffer B SMA_DIFF_CLKIN_N1 —J26.1

U18.15 Differential clock buffer B to FPGA

BUFFB3_SE_CLK_P —J17.5

fabric

U18.14 Differential clock buffer B to FPGA

BUFFB3_SE_CLK_N —J17.6

LVDS

fabric

U18.12 Differential clock buffer B to SMA BUFFB_CLK_P —J20.1

U18.11 Differential clock buffer B to SMA BUFFB_CLK_N —J27.1

U20.6 SMA input for reference clock buffer B REFCLK_OSC_P —J18.1

U20.7 SMA input for reference clock buffer B REFCLK_OSC_N —J25.1

U20.3 Reference clock buffer B to transceivers REFCLK_QL0_P BB2 —

U20.4 REFCLK_QL0_N BB1 —

U20.18 REFCLK_QL1_P AK2 —

U20.19 REFCLK_QL1_N AK1 —

U20.12 REFCLK_QL2_P V2 —

U20.13 REFCLK_QL2_N V1 —

U20.10 REFCLK_QL3_P F2 —

U20.11 REFCLK_QL3_N F1 —

U17.4 SMA input for single-ended clock buffer

SE_CLKINB_SMA

—J14.1

B

U17.23 Single-ended clock buffer B SE_CLKB_L V7 —

U17.21 SE_CLKB_R AD39 —

2.5-V

CMOS

U17.19 SE_CLKB_MAX — U72.K6

U17.13 SE_CLKOUTB_SMA —J15.1

September 2010 Altera Corporation 100G Development Kit, Stratix IV GT Edition Reference Manual

Page 36

2–28 Chapter 2: Board Components

Clock Circuitry