Page 1

SERVICE MANUAL

Model:

PDP4294LV1

S a f e t y P re c a u t io n

T e c h n ic a l Sp e c i fi c a ti o n s

B lo c k Di a g r a m

C irc u it D i a g r a m

B a s ic O p e ra t i o n s & C i rc u it D e s c ri p ti on

M a i n I C S p e c i fi c a ti o n s

P r o d u c t S p e c if ic a t io n o f PD P M o dul e

T ro u b l e S h o o ti n g M a nua l o f P D P M o d u l e

S pa r e Pa r t Lis t

E x p l o d e d V ie w

If y ou f or g e t y o ur V - C hi p P a s s w o r d

S o f t w a r e U pg r a d e

This manual is the latest at t he time of printing, and doe s not

include th e modification which may b e ma de after th e printing,

by the co ns ta nt improvement of product.

Page 2

S a f e t y P r e c a u t i o n

CAUTION

RISK OF ELECTRIC SHOCK

DO NOT OPEN

A

CAUTION: TO REDUCE THE RISK OF

ELECTRIC SHOCK, DO NOT REMOVE COVER

(OR BACK). NO USER-SERVICEABLE PARTS

INSIDE. REFER SERVICING TO QUALIFIED

SERVICE PERSONNEL ONLY.

A

The lightning flash with arrowhead symbol,

within an equilateral triangle, is intended to

alert the user to the presence of uninsulated

“dangerous voltage” within the product’s enclo

sure that may be of sufficient magnitude to

constitute a risk of electric shock to persons.

The exclamation point within an equilateral

triangle is intended to alert the user to the

presence of important operating and

maintenance (servicing) instructions in the

literature accompanying the appliance.

PRECAUTIONS DURING

SERVICING

1. In addition to safety, other parts and

assemblies are specified for conformance with

such regulations as those applying to spurious

radiation. These must also be replaced only

with specified replacements.

Examples: RF converters, tuner units, antenna

selection switches, RF cables, noise-blocking

capacitors, noise-blocking filters, etc.

2. Use specified internal Wiring. Note especially:

1) Wires covered with PVC tubing

2) Double insulated wires

3) High voltage leads

3. Use specified insulating materials for hazardous

live parts. Note especially:

1) Insulating Tape

2) PVC tubing

3) Spacers (insulating barriers)

4) Insulating sheets for transistors

5) Plastic screws for fixing micro switches

4. When replacing AC primary side components

(transformers, power cords, noise blocking

capacitors, etc.), wrap ends of wires securely

about the terminals before soldering.

5. Make sure that wires do not contact heat

generating parts (heat sinks, oxide metal film

resistors, fusible resistors, etc.)

6. Check if replaced wires do not contact sharply

edged or pointed parts.

7. Make sure that foreign objects (screws, solder

droplets, etc.) do not remain inside the set.

MAKE YOUR CONTRIBUTION

TO PROTECT THE

ENVIRONMENT

Used batteries with the ISO symbol

\5<9

for recycling as well as small accumulators

(rechargeable batteries), mini-batteries (cells) and

starter batteries should not be thrown into the

garbage can.

Please leave them at an appropriate depot.

WARNING:

Before servicing this TV receiver, read the

SAFETY INSTRUCTION and PRODUCT

SAFETY NOTICE.

SAFETY INSTRUCTION

The service should not be attempted by anyone

unfamiliar with the necessary instructions on this

apparatus. The following are the necessary

instructions to be observed before servicing.

1. An isolation transformer should be connected in

the power line between the receiver and the

AC line when a service is performed on the

primary of the converter transformer of the set.

2. Comply with all caution and safety related

provided on the back of the cabinet, inside the

cabinet, on the chassis or picture tube.

3. To avoid a shock hazard, always discharge the

picture tube's anode to the chassis ground

before removing the anode cap.

4. Completely discharge the high potential voltage

of the picture tube before handling. The picture

tube is a vacuum and if broken, the glass will

explode.

Page 3

5. When replacing a MAIN PCB in the cabinet,

always be certain that all protective are

installed properly such as control knobs,

adjustment covers or shields, barriers, isolation

resistor networks etc.

6. When servicing is required, observe the original

lead dressing. Extra precaution should be given

to assure correct lead dressing in the high

voltage area.

7. Keep wires away from high voltage or high

tempera ture components.

8. Before returning the set to the customer,

always perform an AC leakage current check

on the exposed metallic parts of the cabinet,

such as antennas, terminals, screwheads, metal

overlay, control shafts, etc., to be sure the set

is safe to operate without danger of electrical

shock. Plug the AC line cord directly to the

AC outlet (do not use a line isolation

transformer during this check). Use an AC

voltmeter having 5K ohms volt sensitivity or

more in the following manner.

Connect a 1.5K ohm 10 watt resistor paralleled

by a 0.15pF AC type capacitor, between a

good earth ground (water pipe, conductor etc.,)

and the exposed metallic parts, one at a time.

Measure the AC voltage across the combination

of the 1.5K ohm resistor and 0.15 uF

capacitor. Reverse the AC plug at the AC

outlet and repeat the AC voltage measurements

for each exposed metallic part.

The measured voltage must not exceed 0.3V

RMS.

This corresponds to 0.5mA AC. Any value

exceeding this limit constitutes a potential

shock hazard and must be corrected

immediately.

The resistance measurement should be done

between accessible exposed metal parts and

power cord plug prongs with the power switch

"ON". The resistance should be more than

6M ohms.

AC VOLTMETER

PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in this

apparatus have special safety-related

characteristics.

These characteristics are offer passed

unnoticed by visual spection and the protection

afforded by them cannot necessarily be obtained

by using replacement components rates for a

higher voltage, wattage, etc.

The replacement parts which have these

special safety characteristics are identified by A

marks on the schematic diagram and on the parts

list.

Before replacing any of these components,

read the parts list in this manual carefully. The

use of substitute replacement parts which do not

have the same safety characteristics as specified

in the parts list may create shock, fire, or other

hazards.

9. Must be sure that the ground wire of the AC

inlet is connected with the ground of the

apparatus properly.

Good earth ground

such as the water

- pipe, conductor,

etc.

AC Leakage Current Check

1500 ohmi, lOwatt

Place this probe

on each exposed

metallic part

Page 4

Technical Specifications

MODEL : PDP4294LV1

42" Plasma Display

DATE FIRST ISSUED ISSUE

1

REVISIONS

ISSUED DATE DESCRIPTION RAISED BY :

RAISED BY CHECKED BY NUMBER OF PAGES

9

SPECIFICATION AGREED : SIGNATURE DATE

R & D DEPARTMENT

COMMERCIAL DEPARTMENT

PRODUCTION DEPARTMENT

Q/A DEPARTMENT

CUSTOMER

SPECIFICATION APPROVED : SIGNATURE : DATE

NOTE : Only docum ents stam p ed “C o ntr olled D o c u m ent” to b e u s e d for m anufactu re o f produ ction parts.

Page 5

CONTINUATION PAGE

Technical Specifications

PDP4294LV1

NUMBER 2 OF 9 PAGES

1. Standard Test Conditions

All tests shall be performed under the following conditions, unless otherwise specified.

1.1 Ambient light

1.2 Viewing distance :

1.3 Warm up time :

1.4 PDP Panel facing :

1.5 Measuring Equipment :

1.6 Magnetic field :

1.7 Control settings :

1.8 Power input :

1.9 Ambient temperature :

1.10 Display mode :

150ux (When measuring IB, the ambient luminance

^0.1Cd/m2)

50cm in front of PDP

30 minutes

no restricted

PC, Chroma 2225 signal generator (with Chroma digital

additional card) or equivalent, Minolta CA100 photometer

no restricted

Brightness, Contrast, Tint, Color set at Center(50)

1 00~240Vac

20°C ± 5°C (68°F ± 9°F)

31.5KHz/60Hz (Resolution 852 x 480)

1.11 Other conditions :

1.11.1 With image sticking protection of PDP module, the luminance will descend

by time on a same still screen and rapidly go down in 5 minutes. When

measuring the color tracking and luminance of a same still screen, be sure

to accomplish the measurement in one minute to ensure its accuracy.

1.11.2 Due to the structure of PDP, the extra-high-bright same screen should not

hold over 5 minutes for fear of branding on the panel.

Page 6

Technical Specifications

ELECTRICAL CHARACTERISTICS

2. Power Input

PDP4294LV1

CONTINUATION PAGE

NUMBER 3 OF 9 PAGES

2.1 Voltage

2.2 Input Current

2.3 Maximum Inrush Current

Test condition

2.4 Frequency

2.5 Power Consumption

Test condition

2.6 Power Factor

2.7 Withstanding voltage

3. Display

3.1 Screen Size

3.2 Aspect Ratio

3.3 Pixel Resolution

3.4 Peak Brightness

3.5 Contrast Ratio (Dark room)

3.6 Viewing Angle

3.7 OSD language

100 ~ 240VAC

3.5 / 1.5A

<30 A (FOR AC110V ONLY)

Measured when switched off for at least 20 mins

50Hz to 60Hz(±3Hz)

< 330W

full white display with maximum brightness and

contrast

Meets I EC 1000-3-2

1.5kVac or 2.2kVdc for 1 sec

42” Plasma display

16:9

852x480

1000 cd/m2 (Panel module without filter)

3000:1 (Panel module without filter)

Over 160°

English

4. Signal

4.1 AV & Graphic input

4.1.1 TV standard

4.1.2 TV Tuning system

4.1.3 CATV

4.1.4 Composite signal

4.1.5 Y,C Signal

4.1.6 Component signal

4.1.7 Graphic I/P

4.1.8 PnP compatibility

4.1.9 I/P frequency

NTSC

PLL 181Ch

125CH

CVBS

S-Video

Y, Pb/Cb, Pr/Cr, HDTV compatible

Analog: D-sub 15pin detachable cable

Digital: DVI

DDC 1.0

fH 31.5kHz to 60kHz/fV: 56.25Hz to 75Hz (640x480

recommended)

Page 7

Technical Specifications

4.2 Audio input

Audio I/P(L/Rx5)

4.3 Audio output

Audio O/P(L/Rx1) :

PDP4294LV1

1 for DVI / D-Sub

1 for Y/ Pb/Pr

1 for Y/ Cb/Cr

1 for CVBS

1 for S-Video

Monitor out(L/R)

CONTINUATION PAGE

NUMBER 4 OF 9 PAGES

4.4 Other function :

5. Environment

5.1 Operating environment

5.1.1 Temperature :

5.1.2 Relative humidity:

5.2 Storage and Transport

5.2.1 Temperature :

5.2.2 Relative humidity:

6. Panel Characteristics

6.1 Type :

6.2 Size :

6.3 Aspect ratio

6.4 Viewing angle

6.5 Resolution

6.6 Weight

6.7 Color

6.8 Contrast

6.9 Peak brightness :

PIP, 16:9, 4:3, Zoom

5° to 33°C

20% to 85%(non-condensing)

-20°C to 60°C(-4° to 140°F)

5% to 95%

LG V6

42”, 1005mm(width)x597mm(height)x61 mm(depth)±1

mm)

16:9

Over 160°

852x480

14.8kg ±0.5 kg (Net)

16.77 million colors by combination of 8 bits R,G,B digital

Average 60:1 (In a bright room with 150Lux at center)

Typical 3000:1 (In a dark room 1/25 White Window

pattern at center).

Typical 1000cd/m2 (1/25 White Window)

6.10 Color Coordinate Uniformity :

Test Pattern :

Contrast; Brightness and Color control at norma

setting

Full white pattern

Average of point A,B,C,D and E +/- 0.01

Page 8

CONTINUATION PAGE

Technical Specifications

PDP4294LV1

NUMBER 5 OF 9 PAGES

6.11 Color temperature : Contrast at center (50); Brightness center (50);

Color temperature set at Natural

x=0.285±0.02

y=0.293±0.02

6.12 Cell Defect Specifications

Subject to Panel supplier specification as appends.

7. Front Panel Control Button

7.1 CH Up / Down Button : Push the key to changing the channel up or down.

When selecting the item on OSD menu.

Volume Up/ Down Button : Push the key to increase the volume up or down.

When selecting the adjusting item on OSD menu

increase or decrease the data-bar.

Menu Button : Enter to the OSD menu.

Input Select Button : Push the key to select the input signals source.

7.2 Stand by Button : Switch on main power, or switch off to enter power

Saving modes.

7.3 Main Power Switch : Turn on or off the unit.

8. OSD Function

8.1 Audio : Adjust or Select Volume; Bass; Treble; Balance; SRS; BBE; AVC;

Int./Ext. Speaker.

8.2 Picture : Adjust or Select Brightness; Contrast; Sharpness; Scaling (Picture

changes According to Fill or One to One.; DNR; Video Format;

More options for Y/Pb/Pr and VGA ( H. Position, V. Position Phase,

Frequency)

8.3

OSD :

Position; OSD H. Position; OSD V. Position; OSD Timeout;

OSD Backgroud; Language.

8.4 Tools : Factory Reset; Source Scan; Blank Color; Turn Off Timer; Screen

Saver; Saver Mode.

8.5 TV : Edit Channels; Auto Fine Tune; Source.

8.6 CC-V Chip : TV Channel Blocking; Movie Blocking; Change Blocking Password;

Clear Password; CC Mode; CC Background.

Page 9

CONTINUATION PAGE

Technical Specifications

PDP4294LV1

NUMBER 6 OF 9 PAGES

9. Agency Approvals

Safety UL60950

Emissions FCC class B

10. Reliability

11.1 MTBF : 20,000 hours(Use moving picture signal at 25°C ambient)

11. Accessories : User manual x1, Remote control x1, Stand x1, Power cord x1

Battery x 2, Accessories box x 1.

Page 10

Technical Specifications

PDP4294LV1

NUMBER 7 OF 9 PAGES

12. Supportthe Signal Mode

The PDP can support the different from DVI or VGA Signal Mode in 24 kinds

CONTINUATION PAGE

NO. Resolution Horizontal

Frequency

(KHz)

Vertical

Frequency

(Hz)

Dot Clock

Frequency

(MHz)

1# 640 x400 31.47 70.08 25.17

2# 640 x400 37.90 85.00 31.5

3 640 x480 31.50 60.00 25.18

4 640 x480 35.00 67.00 30.24

5 640 x480 37.50 75.00 31.50

6 640 x480 37.86 72.81 31.50

7# 640 x480 43.30 85.00 36.00

8 800 x600 35.16 56.25 36.00

9 800 x600 37.90 60.32 40.00

10 800 x600 46.90 75.00 49.50

11 800 x600 48.08 72.19 50.00

12 800 x600 53.70 85.00 56.25

13 832 x624 49.00 75.00 57.27

14 1024 x768 48.40 60.00 65.00

15 1024 x768 56.50 70.00 75.00

16 1024 x768 60.00 75.00 78.75

17 1024 x768 68.70 85.00 94.50

18* 1152x864 54.53 60.00 80.37

19 1152x864 67.52 75.02 108.03

20* 1152x864 63.86 70.02 94.51

21 1280x1024 63.37 60.01 111.51

22 1280 x960 75.02 75.02 126.00

23 1280 x960 60.02 60.02 108.04

24# 1280x720 44.96 59.95 74.19

Note: DVI could not support * of signal mode.

VGA could not support # of signal mode.

- Press "DISPLAY” button to confirm the input signal format.

Note: Some data will be updated in five seconds if you change them.

Page 11

Technical Specifications

13. Remote Function+

PDP4294LV1

CONTINUATION PAGE

NUMBER 8 OF 9 PAGES

Mute

Intelligent Sound Control

PC

Volune up/down

Menu Left/Right

Up/Down

Left/Right

Button

Intelligent Picture Control

ZOOM plus/minus

Display

Sleep

Power on/off (Standby)

PIP

Video

Number Button/

Channel up/

Channel down/

Return

OSD exit

Input

SRS/BBE

Wide

Freeze

Full

MTS

Page 12

Technical Specifications

PHYSICAL CHARACTERISTICS

14. Power Cord

PDP4294LV1

CONTINUATION PAGE

NUMBER 9 OF 9 PAGES

Length :

Type :

15. Cabinet

15.1 Color :

15.2 Weight

Net weight

Gross weight

15.3 Dimensions(with stand)

Width

Height

Depth

1.8m nominal

optional

“Black” colour as defined by colour plaque reference number

73.9lbs (33.5kg)

87.i lbs(39.5kg)

45 inches (ii40m m)

28-3/8 inches (720mm)

i i -4/a inches (290mm)

Page 13

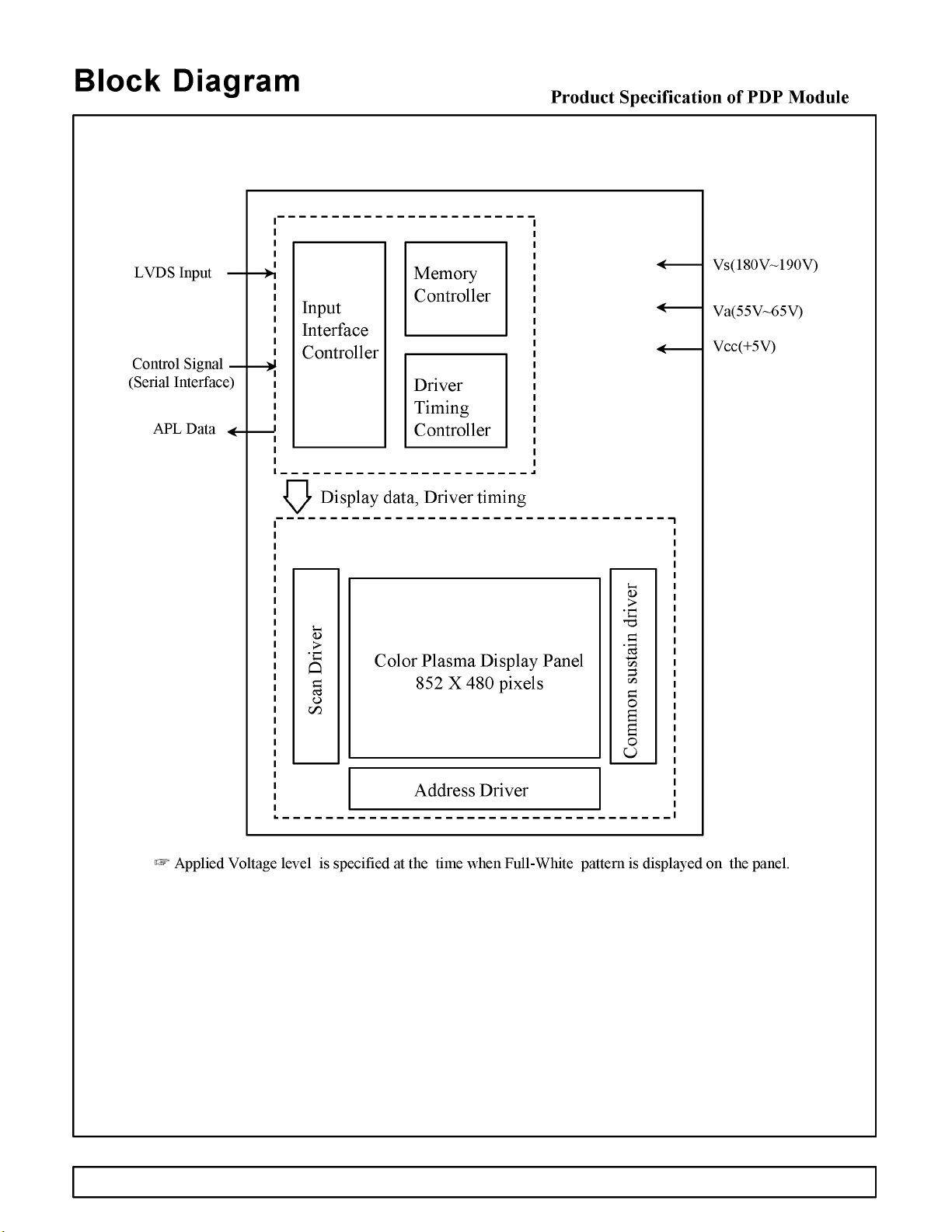

B l o c k D i a g r a m

Product Specification of PDP Module

LVDS Input

Control Signal —

(Serial Interface)

APL Data

Memory

Input

Interface

Controller

Display data, Driver timing

>

•c

Q

G

cd

O

GO

Controller

Driver

Timing

Controller

Color Plasma Display Panel

852 X 480 pixels

<u

>

•G

T3

cö

3

c

O

Vs(180V~190V)

Va(55V~65V)

Vcc(+5V)

o

o

Address Driver

Applied Voltage level is specified at the time when Full-White pattern is displayed on the panel.

Page 14

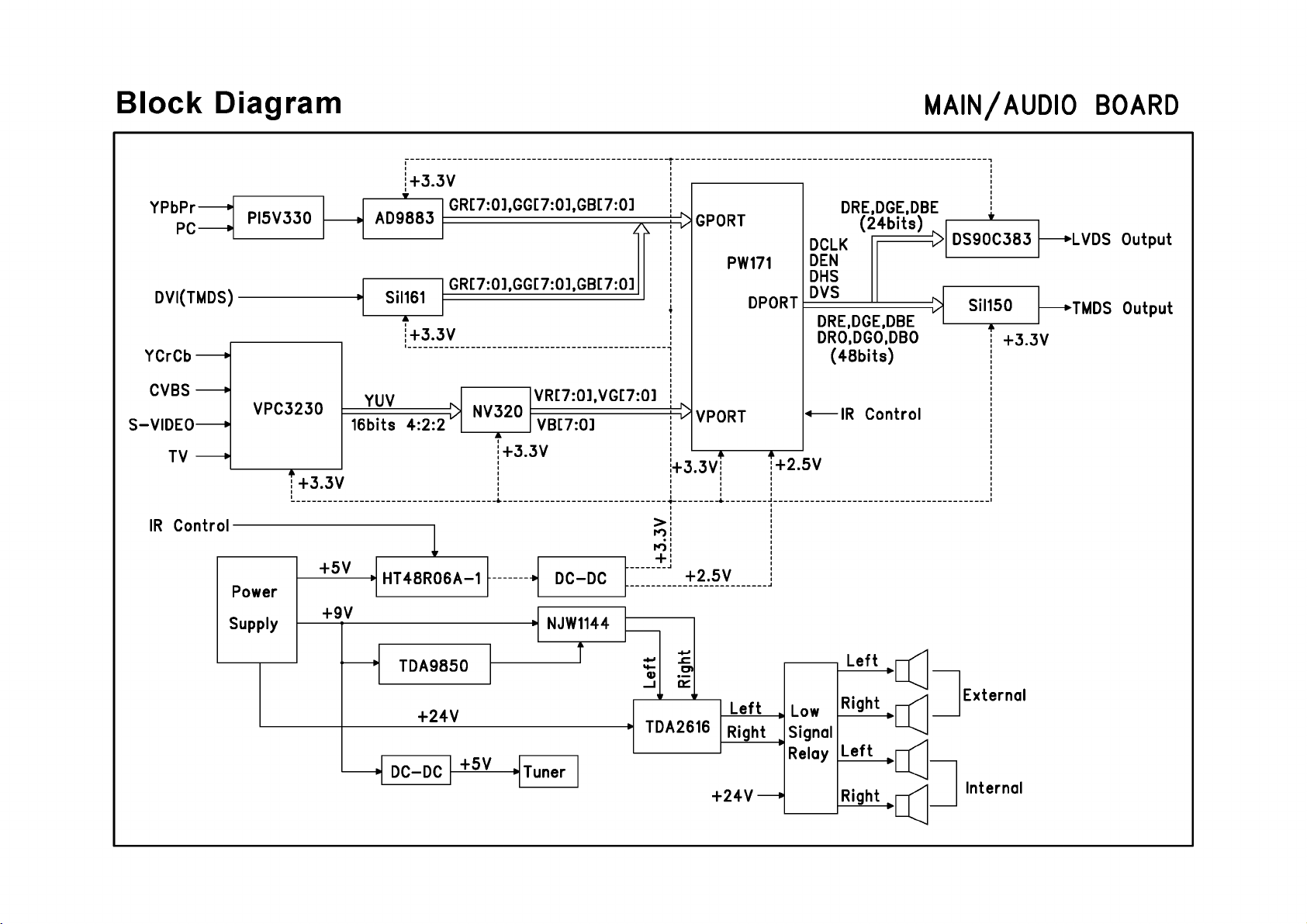

B l o c k D ia g r a m

MAIN/AUDIO BOARD

Page 15

C i r c u i t D i a g r a m

- Power supply board of PDP Module,

- Power supply board of PDP Module,

- Main (Video) board

- Audio/Tuner board

- Keypad board

- Remote control receiver board

- External L/R Speakers board

- Remote control board

Page 16

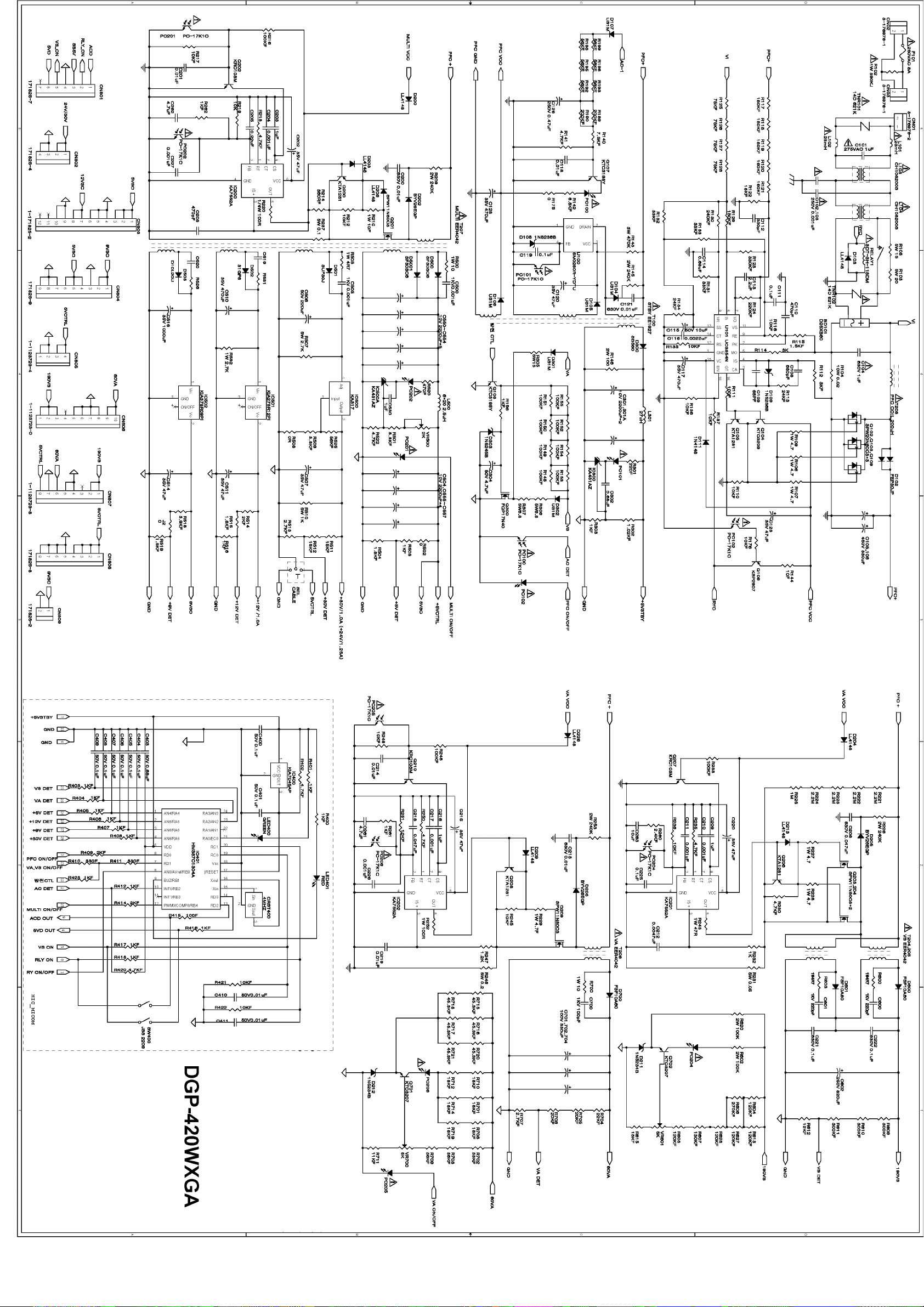

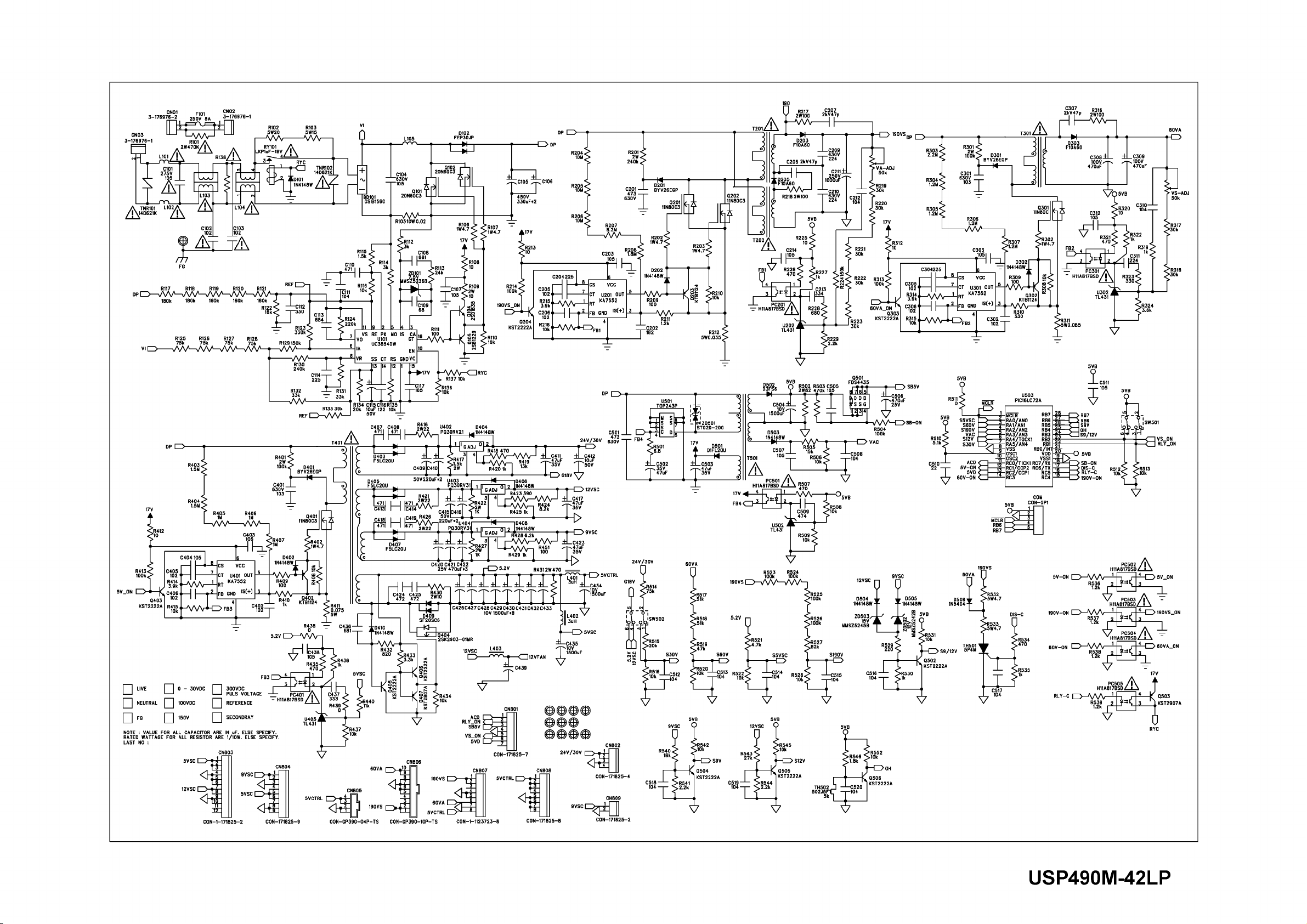

DGP-420WXGA

USP490M-42LP

Page 17

Page 18

□ LIVE

| | NEUTRAL Q 100VDC | | REFERENCE

□ rG

NOTE : VALUE FOR ALL CAPACITOR ARE IN uF. ELSE SPECIFY.

RATED WATTAGE FOR ALL RESISTOR ARE 1/10W. ELSE SPECIFY.

LAST NO :

Q 0 - 30VD 1 1 300VDC

| | 150V

1--1 PULS VOLTAGE

| | SECONDRAY

CON-171825-9 C0N-GP39Q-04P-TS

60VA [

5VCTRL

C0N-GP390-10P-TS CON-1-1123723-8

CON—171825—8

CON-171825-2

USP490M-42LP

Page 19

NPUT AFE

D

VCP3230

VVINT VUV[7:0] <

CB VVHS

RESETn VY[7:0] *

Y

SDA SCL

CR VVVS

STBLED VFIELD

POWER ON

05_VCP3230

TMDS

► DBO[7:0]

DHS

DENG

DENR

► DGE[7:0]

► DRE[7:0]

► DGO[7:0]

► DRO[7:0]

DCLK

DVS

9_DERB

► DBE[7:0]

VVCLK

MUTE

MUTE1

IR

NV320

SDA VG[7:0]

SCL VB[7:0]

VVHS VR[7:0]

RESETn VCLK

VVCLK VVS

NDSP_EN VHS

VY[7:0]

VUV[7:0]

VVVS

MISC

LED-G

ICSSTM

ICSCLK

ICSSTD

LED-R

ICSDAT

TXD

RDn

► D[7:0]

CS1n

STBLED

DVI PW171

RXCm

RX0m GPEN

RX1p GBE[7:0]

RX1m GVS

RX0p GBO[7:0]

GDFEOE GFBK

RX2m GHS

RX2p GGE[7:0]

RXCp GCLK

DCKEXT

MCKEXT

RESET

RESETn

POWER_ON

IRRCVR1

VPEN

RXD

NMI

G

RE

GRO[7:0]

GGO[7:0]

MEMORY

POWER LVDS

HDCBIN GBE[7:0] 4

HDYIN GRE[7:0] * 1

GAFEOE GHS

VGASEL GCLK

GVSYNC GFBK

GCOAST GGE[7:0] <

HDCRIN GVS

GRAIN

SCL

GBAIN

GBLKSPL

GGAIN

SDA

GHSYNC

DENG

DCLK

DVS

DHS

DTXON

RESET-2

SCL

SDA

CPUGO

PDPGO

PDWN

IRQ

DGE[7:0]

DRE[7:0]

DBE[7:0]

► D[15:0] DGE[7:0]

► A[19:0] DRO[7:0]

► VR[7:0] GCOAST

► VG[7:0] ROMOEn

► VB[7:0] TXD

► GRE[7:0] DENG

► GBO[7:0] DENR

► GBE[7:0] DHS

► GGO[7:0] SCL

► GRO[7:0]

► GGE[7:0]

8-ÎRRCVR1

► NDSP EN

SDA DBE[7:0]

GFBK DGO[7:0]

CS1n DRE[7:0]

VPPEN DBO[7:0]

RDn DCLK

NMI GBLKSPL

VCLK ROMWEn

GHS DVS

GCLK DENB

GVS

MCKEXT

RXD

RESET

DCKEXT

VPEN

VVS

VFIELD

GPEN

ICSCLK

ICSSTD

ICSSTM

ICSDAT

LED-R

LED-G

DTXON

VGASEL

GAFEOE

GDFEOE

VVINT

VHS

MUTE

SLEEP1

PIO3

CPUGO

PDPGO

RESET-2

PDWN

IRQ

C

B

A A

Page 20

AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD AVDD

I C34 I C35 I C36 | C37 C3B | C39 | C40 | C41 | C42 | C

M î M M î M

I 0 1uF |~0.1uF I 0 1uF I 0 1uF j 0 1uF ~|~ Ö1uF ~|~0 1uF j 0 1uF j 0 1uF | 0^

D

GASEL

HDCRIN

HDYIN

HDCBIN

GRAIN

GGAIN

GBAIN

GHSYNC

G SYNC

PVDD PVDD

î Î

I C50 I C

j 0 1uF j 0^

2

CS1

V33 V33 V33 V33 V33 V33 V33

C52 I C53 I C54 | C55 | C56 | C57 | C

T M T î M

1uF

- 0■1u^ 0■1u^ 0■1u^ 0■1u^ 0■1u^ 0■1uF

33

o

3333

A/B

15

OE

2

A1

5

A2

11

A3

A4

3

B1

6

B2

10

B3

B4

10

C6

C61

j 0 1i

01uF

U9 PI5 330

9 B

4

5 6

16

CC

4

9

12

B

GND

UBC GMID

74LV C126A

UBB

74LV C126A

CC

GMRED 47nF C62 GRIN GGE5

GMGRN GGE6

GMBLU

GBHSY ADSOGR

GB SY

CCCC

j 0 1i

GBLKSPL

C6

C66

01uF

SDA

SCL

GCOAST

C43

C5B

47uF

1uF

TP7 TPB

0 0

47nF C63

1nF C64

47nF C65

CC

O

P DD

o

C59

39nF

C60

GFLT1

39nF

R16

33 K

GFILT

GGIN GGE7

GSOGIN

GBIN

G REF RP20

C6B

C67 _

01 uF j 0^

1uF

A DD

o

DDDDDDDDD1 DDDDDD DD

>>>>>>>>>Q QQQQQQ >>

AA AAAAAAAA PP

33

FILT

SDA

SCL

AO

CLAMP

COAST

54

RAIN

GAIN

SOGIN

43

BAIN

HSYNC

SYNC

REFBYP

MIDSC

GGGGGGGGGGGGGGGGGGGG

U7

AD9BB3A_140

C44

01uF

33

o

U5

LM2937 SOT223

_SO BAT

2937 DNG

L V I

P DD

o

REDO

RED1

RED2

RED3

RED4

RED5

RED6

RED7

GREENO

GREEN1

GREEN2

GREEN3

GREEN4

GREEN5

GREEN6

GREEN7

BLUEO

BLUE1

BLUE2

BLUE3

BLUE4

BLUE5

BLUE6

BLUE7

DATACK

HSOUT

SOGOUT

SOUT

223 O

T2 V

3

77

76

74

73

72

71

9

B

7

5

4

3

2

19

1B

17

16

14

13

12

67

66

65

64

P DD

C45 C46 C47 C4B C49

01uF 47uF 01uF 01uF 47uF

ADR0 47R

ADR1

ADR2

ADR3

ADR4 47R

ADR5

ADR6

ADR7

ADGO 47R

ADG1

ADG2

ADG3

ADG4 47R

ADG5

ADG6

ADG7

ADB0 47R

ADB1

ADB2

ADB3

47R

ADB4

ADB5

ADB6

ADB7

ADCK

47R

ADHS

ADSOG

ADVS

cotoneo co

N/\/

N/^

N^/

N /S /

N/^

N^/

N /S /

N/^

N^/

N /S /

N /S /

N/^

N / S / '

’S/S/

N/^

N^/

N^'

N /S /

N /S /

CC

O

# 1

RP14 GRE0

GRE1

GRE2

GRE3

RP15 GRE4

GREb

GRE6

GRE7

RP16 GGE0

GGE2

GGE3

RP17 GGE4

RP1B GBE0

RP19 GBE4

U6

LM2937 SOT223

_SO BAT

L VI

ONO

223 O

T2 V

3

^ Y

11

74LVC126A

TP9

A DD

O

GRE[7:0]

GGE[7:0]

GBE[7:0]

GCLK

GFBK

G V S

GHS

C

B

GAFEOE

A A

Main (Video)

Page 21

OVCCOCVCC PVCCoAVCC

o

COCO CO 03

SISCDT

8

SCDT

QEO

QEi

QE2

QE3

QE4

QES

QEe

QE7

QE8

QE9

QEiO

Q E ii

QE i2

QE i3

QEi4

QE iS

QEie

QE i7

QE18

QE i9

QE2O

QE2i

QE22

QE23

QOO

QOi

QO2

QO3

QO4

QOS

QOe

QO7

QO8

QO9

QOiO

Q O ii

QO i2

QO i3

QOi4

QO iS

QOie

QO i7

QO18

QO i9

QO2O

QO 2i

QO22

QO23

ODCK

VSYNC

HSYNC

CTLi

CTL2

CTL3

SIBEO RP1

10

SIBE1

11

SIBE2

12

SIBE3

SIBE4 RP2

14

SIBE5

15

SIBEe

ie

SIBE7

17

SIGEO RP3

20

SIGE1

21

SIGE2

22

SIGE3

23

SIGE4 RP4

24

SIGE5

25

SIGEe

2e

SIGE7

27

SIREO RP5

30

SIRE1

31

SIRE2

32

SIRE3

33

SIRE4 RPe

34

SIRE5

35

SIREe

3e

SIRE7

37

SIBOO RP7

49

SIBO1

50

SIBO2

51

SIBO3

52

SIBO4 RP8

53

SIBO5

54

SIBOe

55

SIBO7

se

SIGOO RP9

59

SIGO1

60

SIGO2

ei

SIGO3

e2

SIGO4 RP10

e3

SIGO5

e4

SIGOe

es

SIGO7

ee

SIROO RP11

e9

SIRO1

70

SIRO2

71

SIRO3

72

SIRO4 RP12

73

SIRO5

74

SIROe

75

SIRO7

77

SICLK RP13

44

SIDE

4e

DE

SIVS

47

SIHS

48

40

42

SIIie i

CCCC

CCCC

U4

DDDDD

OOOOO oocJ

9e

90

91

85

se

80

81

93

94

4

1

7

3

9

2

99

CCCCC CCC

VVVVV VVV

OOOOO

RXOp

RXOm

RX ip

RX im

RX2p

RX2m

RXCp

RXCm

OCK_INV

PIXS

DFO

STAG_OUT

ST

PDO

PD

RSVD

DDDDD i23

NNNNN DDD

GGGGG NNN

OOOOO GGG

D

RXOp

RXOm

RX ip

RXim

RX2p

RX2m

RXCp

RXCm

GDFEOE

AVCC

RiS

SiO

SIRES GGEi

&

OVCC

o

100

___

___

__

Q TP1

'S /S /

'S /S /*

N/V*

'S /S /

N /S /

N /S /

N/S/*

N /S /

N /S /

N /S /

w

'S /S /*

N /S /

N /S /

w

'S /S /*

w

'S /S /*

w

w

N /S /

'S /S /'

N /S /

w

N/S/^

'S /S /

N /S /

N /S /

w

N /S /

N /S /

N /S /

N /S/ *

N /S /

N /S / *

N /S /

47R GBEO

47R GBE4

47R GGEO

GGE2

GGE3

47R GGE4

GGES

GGEe

GGE7

47R GREO

GREi

GRE2

GRE3

47R GRE4

GRES

OREO

GRE7

47R GBOO

GBOi PVCC

GBO2

GBO3

47R GBO4

GBOS

GBOe

GBO7

47R GGOO

GGOi

GGO2

GGO3

47R GGO4

GGOS

GGOe

GGO7

47R GROO

GROi

GRO2

GRO3

47R GRO4

GROS

GROe

GRO7

47R

GBE[7:O]

GGE[7:O]

GRE[7:O]

GBO[7:O] C

GGO[7:O]

GRO[7:O]

TP2 TP3 TP4 TPS TPe

0 0 0

u

VCC

o

C14

OiuF

V33T L iS OVCC

FB_42O_OHM_2OOMA Ç

Î

_______

V33T L ie CVCC

FB_42O_OHM_2OOMA 9

t

_______

V33T L i7 PVCC

FB_42O_OHM_2OOMA 9

Î

_______

V33T L18 AVCC

FB_42O_OHM_2OOMA 9

Î

_______

GCLK

GPEN

GVS

GHS

GFBK

U3

LM2937 _SOT223

VI

VO

DNG

BT

rv~\________________

rv~\________________

rv~\

_____________

- Î

rv~\________________

CiS

Cie

OiuF

47uF

OVCC OVCC OVCC OVCC OVCC

Ci7

iOuF

C23

iOuF

C27

C27 C2

10uF

C29

iOuF

V V V V V

I C18 C19 I C20 I C21 I C22

I O iuF |~0 1uF |~0 1uF I O iuF j O iuF

CVCC CVCC CVCC

V V V

C24 C2S C2e

j O iuF j O iu F j O iuF

j O iuF

AVC C AVCC AVCC AVCC

V V V V

I C30 C31 I C32 I C33

j O iuF |~0 1uF |~0 1uF j 0 1u

B

rocou^co cd

A A

Main (Video)

Page 22

V33

o

ROMOEn

-O 1

JP1

3

ROMWEn

R69

FWPn

A1

A2

A3

A4

Ab V33

A6 U17

A7

A8

A9

A10

A11

A12

A13

A14

A1b

A16

A17

A18

A19

D

V33

VPPEN

U16

26 13

CE

OE

WE

RP

WP

BYTE

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

V33

?

C16

T -

VPP

VCC

GND1

GND2

D10

D11

D12

D13

D14

D15

D16

D1

D2

D3

D4

D5

D6

D7

D8

D9

28

14

47

V33

o

D0

29

D1

D2

33

D3

3b

D4

38

Db

40

D6

42

D7

44

D8

30

D9

32

D10

34

D11

36

D12

39

D13

41

D14

43

D1b

4b

46

27

1

VPPON

FCEn

CEn

P2

132

R6^ ^ v . 10K VP1 1

V33

4

VPP

C167

22uF

Q4

3906

VP3

VP2

R67

1K

Q5

3904

V33

SCL

SDA

6 8

SCL VCC

SDA

NC0 WP

2

NC1

3 4

NC2 GND

24C16

7

C168

0.1uF

C

VCC

O

A2 A1

A4 A3

A6 Ab

A9 A8

A11 A10

A12

A14 A13

A17 A16

A19 A18

ROMOEn ROMWEn

D1b

D14 D6

Db D12

D4

D3 D10

D2

D9 D1

D8 D0

JP3

VCC

o

IRPn R72

IA20 R74

IA21 R7

V33

o

A7

A1b

D7

D13

A A

A[19:1] [

Main (Video)

B

Page 23

HDCR L1

J1

2 Y

3

4

CB

HDY L3

HDCB L5

FB_40_OHM_500MA HDCRF

FB_40_OHM_500MA HDYF

FB_40_0HM_500MA HDCBF.

FB_40_OHM_500MA

FB_40_OHM_500MA

L6 /-y-y FB_40_0HM_500MA

AVDD AVDD

HDCRIN

HDYIN

HDCBIN

o

AVDD

o

D

6

CR

9

YUV

Y

>CB

>CR

75 >75 >75

3 3

C1 “

D1 D2 D3

12pF

GVCC1 GVCC1

C2 m

12pF

C3

12pF

J2

27

NC1

DATA2/4_SHLD

DATA1/3_SHLD

H_PLUG_DET

DATA0/5_SHLD

28

NC2 A_GND2

SHELL1

DATA2-

DATA2+

DATA4-

DATA4+

DDC_CLK

DDC_DATA

A_VSYNC

DATA1-

DATA1+

DATA3-

DATA3+

+5V

GND

DATA0-

DATA0+

DATA5-

DATA5+

CLK_SHLD

CLK+

CLK-

A_RED

A_GREEN

A_BLUE

A_HSYNC

A_GND1

SHELL2

GVCC GVCC GVCC

V99L

BA

D6 D7

25

2

3

7

10 10

11

15

16

17

18

19

23

24

GVCC GVCC GVCC

>R4 ^

. 3.3K

<

GDC5V

VCC

> 3.3K

3

1 3

2

R5

• R9

3.3K

3

4

GVCC VCC

C11

GVCC

C5

0.1uF

NS

1uF

U2

GVCK

7

GSCL

6

GSDA

5

RX2m

RX2p

-t>i

RX1m

RX1p

-t>i

RX0m

RX0p

-t>i

RXCp

RXCm

-t>i

VCC GVCC1

L13

NS

VCLK

SCL

SDA

24LC21A

VCC

NC1

NC2

NC3

GND

_ C _

1 1

- C1_

1 I

J15

DB15HD_V

6

11

GGREEN L9

12

GBLUE

13

G5V

4

14

15

VCC

2

3

D4 D5

9L

V99

BAV

3

B k B

D11 D12

L7

GVCC1

1 1

C , I

GVCC1 GVCC1 GVCC1

> R6 S R7 > R8

S 3.3K S 3.3K S 3.3K

FB_40_0HM_500MA

°

L99VA

S 2K

CVCK

CSCL

CSDA

7

6

5

U1

VCLK

SCL

SDA

24LC21A

VCC

NC1

NC2

NC3

GND

GVCC1

4

ro fia rM_irifl caaiüa

o

C4

GRAIN

GGAIN

GBAIN

GHSYNC

GVSYNC

A A

C

Main (Video)

Page 24

SDA

SCL

V33 V33 V33 V33 V33

DRE[7:0] [

D

DGE[7:0] [

DBE[7:0]

DRE[7:0]

DGE[7:0]

DBE[7:0]

DRE0 47R

DRE1

DRE2

DRE3

DRE4

DRE5

DRE6

DRE7

DGE0 47R

DGE1

DGE2

DGE4

DGE5

DGE6

DBE0 47R

DBE1

DBE2

DBE3

DBE4

DBE5

DBE6

DRE0 47R

DRE1

DRE2

DRE3

DRE4 47R

DRE5

DRE6

DRE7

DGE0 47R

DGE1

DGE2

DGE3

DGE4 47R

DGE5

DGE6

DGE7

DBE0 47R

DBE1

DBE2

DBE3

DBE4 47R

DBE5

DBE6

DBE7

47R

47R

47R

W

'S /S /*

N/V*

w

N/S/

'S / S /'

W

N/V*

N/V*

N/S/'

W

w

'S /S /*

N/S/

w

'S /S /*

RP60 ARE0

“ AKE1“

“ AKE2“

ARE3

RP61 ARE4

-----------

ARE5”

-----------

ARE6“

ARE7

RP62

AGE1 ARE1

AGE2 ARE2

AGE3 ARE3

AGE4 ARE4

RP63

AGE5 ARE5

AGE6 ARE6

AGE7 ARE7

ABE0 AGE0

RP64

ABE1 AGE1

ABE2 AGE2

ABE3 AGE3

ABE4 AGE4

RP65

ABE5 AGE5

ABE6 AGE6

ABE7 AGE7

N /N / *

W

r y v j

k/s/J

N / S / '

w

w

w

N / N /'

w

w

ARE7

ARE0

ARE1

RP51\ RE2

ARE3

ARE4

-------

ARE5”

RP52VGE6

AGE1

RP5 ^GE2

” AGE3“

AGE4

RP54\ BE6

ABE7

ABE0

ABE1

ABE3

ABE4

m m ?

I C273 C274 | C275 | C276 | C27

10.1uF j 0.1uF 10.1uF 10.1uF 10.1i

DCLK

ABE0

ABE1

ABE2

ABE3

ABE4

ABE5

ABE6

DHS

DVS

DEN

ABE7

31

CLKIN

TXIN0

52

TXIN1

54

TXIN2

55

TXIN3

56

TXIN4

3

TXIN6

50

TXIN27

2

TXIN5

4

TXIN7

6

TXIN8

7

TXIN9

11

TXIN12

12

TXIN13

14

TXIN14

8

TXIN10

10

TXIN11

15

TXIN15

19

TXIN18

20

TXIN19

22

TXIN20

23

TXIN21

24

TXIN22

16

TXIN16

18

TXIN17

TXIN24

TXIN25

TXIN26

TXIN23

R F

PWRDN

33

O

C C C

C C C

> > >

TX0UT0

TX0UT0

TX0UT1

U31

DS90C383A

t- cnco'Tu iÜ Q Q ^ I ^

DDDDDNNNNN

ZZZZZÜÜÜÜC

OOOÜOOOOao.

TX0UT1

TX0UT2

TX0UT2

TX0UT3

TX0UT3

IXC0UI

TXC0UT

J13

R139

R140

3WSDA

3WSCL

3WSLE

PDWN

C0N20A

TXE0p

TXE1p

41

42

37

38

39

40

3WSDA 0

3WSCL 0 nyi

3WSLE 0

PDWN

TXE2p

TXECKp

TXE3p

SCL

SDA

R141

R142

R143

J14

C

JEA31

B

A A

Main (Video)

Page 25

Page 26

f-

C12<

"3!

=

C123 | |

| 0.1uF“ C125^= (

4 X 01uFX (

r-i.i-9 r-i.i'j r-i.1.1 r1u^ C146 1 C

__________

0.1uF 0.1uF 0.1uF 0.1uF

VCC

L

x

=j C1uFj ,

T. 01uI (:I ;

VSS

VSS

MD0

MD1

MD3

MD4

MD5

MD6

MD7

MD8

MD9

r

26

50

47

V33N

21

22 22

23 23

24 24

27 27

28 28

29 29

30 30

31 31

20 20

MA1 0

19

BA 3A

DQM0 14

LDQM

l_ 36

UDQM

35 35

CLK

34 34

V33N V33N

V33N

CKENCNC

MWE MWE

15 15

16 16

RAS

17 17

MCS- MCS-

18 18

1

VDD

25

VDD

VDDQ VSSQ

13 13

VDDQ VSSQ

VDDQ VSSQ

44 44

VDDQ VSSQ

HY57V161610D-7 HY57V161610D-7

MA10 19

DQM1

-

RAS

21

14

LDQM DQ

UDQM DQ

CLK

CKENCNC

1

VDD

25

VDD

VDDQ VSSQ

VDDQ VSSQ

VDDQ VSSQ

VDDQ VSSQ

VSS

VSS

V33N

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD29

MD30

MD31

26

50

?

| C113 | C114 | C115 | C116 | | | 1 C117 | C118 | C119

<-l->0.1u^--s0.1u^-»>0.1u^->0.1uM C120 I C121 I C12^-»>0.1u^->0.1u^-«0.1uF

I X7R I X7R I X7R I X7R ^i--Ü.1u^»>Ü.1u^->.Ü.1uM X7R I X7R I X7R

0603 0603 0603 0603 X7R X7R X7R 0603 0603 0603

V33N

0603 0603 0603

f ,

| C130_^ C13^ | C13^ | C133 | C134 | C13^ | C13^ | C13^ | C13^ | C139

^T^0.1ul^>.0.1ulW-K0.1ul^T^0.1ul^*%0.1ul^T^0.1ul^>.0.1ulW-K0.1ul^T^0.1ul^*%0.1uF

X7R X7R X7R X7R X7R X7R X7R X7R X7R X7R

<*T-s0.1ul^T^0.1ul^>.0.1ul^-K0.1uF

I

0uF X7R X7R X7R X7R

0603 0603 0603 0603

VCLK

VVS

VHS

VPEN

Main (Video)

Page 27

Page 28

GFBK -

GCLK

GPEN

GVS

D

GHS

GRE[7:0] |

GGE[7:0] [

GBE[7:0]

GRO[7:0] [

GGO[7:0]

GBO[7:0] [

V25

o

DDDDD

DDDDD

VVVVV

NS ^ ^ R82K25

GRE0

GRE1

GRE2

GRE3

GRE4

GRE5

GRE6

GRE7

GGE0 PA3

GGE1

GGE2

GGE3

GGE4

GGE5

GGE6

GGE7

GBE0

GBE1

GBE2

GBE3

GBE4

GBE5

GBE6

GBE7

GRO0

GRO1

GRO2

GRO3

GRO4

GRO5

GRO6

GRO7

GGO0

GGO1

GGO2

GGO3

GGO4

GGO5

GGO6

GGO7

GBO0

GBO1

GBO2

GBO3

GBO4

GBO5

GBO6

GBO7

L L29~ 0

DDDDD

DDDDD

VVVVV

A A

sqqqqqqqqqqSÖÖÖÖÖÖÖÖÖSSSSSSSSSSqqqqqqqqqqqqqqqqc

GCLK

K26 AF17

GPEN

GVS

GHS

GSOG

GFIELD

PLLCLK

U26 W4

GRE0

V 24

GRE1

V 23

GRE2

V25

GRE3

V 26

GRE4

W25

GRE5

W24

GRE6

W23

GRE7

H23

GGE0

G26

GGE1

H25

GGE2

P23

GGE3

P24

GGE4

P25

GGE5

P26

GGE6

R23

GGE7

. B25

GBE0

A26

GBE1

D24

GBE2

E23

GBE3

C25

GBE4

B26

GBE5

C26

GBE6

E24

GBE7

R24

GRO0

R25

GRO1

R26

GRO2

T23

GRO3

T24

GRO4

T25

GRO5

T26

GRO6

U25

GRO7

F23

GGO0

D25

GGO1

D26

GGO2

F24

GGO3

E25

GGO4

E26

GGO5

F25

GGO6

F26

GGO7

D21

GBO0

B22

GBO1

C22

GBO2

A23

GBO3

B23

GBO4

D22

GBO5

C23

GBO6

A24

GBO7

FB 11 OHM 500MA

DDD

DDD

VVV

012 34 56 789 01 234 56 789 01 234 56 789 01 234 567 89 012 34 56

GCLKOUT

GHSFOUT

GADCCLK

U18A

PW365

G raph ics Po rt

DDDDDDDDDDDDDDD

DDDDDDDDDDDDDDD

VVVVVVVVVVVVVVV

PW365 U18E

GFBK

GREF

GBLKSPL

GCOAST

M25

H26

J25

J23 _

124

M24

M26

VCLK C

VPEN

VVS

VHS

VFIELD

VR[7:0]

VG[7:0]

VB[7:0]

GBLKSPL

GCOAST

PA4

3WSCL

3WSDA

3WSLE

B16

VCLK

B18 M4

VPEN

A21 N1

VLAV

B21 N2

VVS

A22 N3

VHS

C21 N4

B10

A10

D11

C11

B11

A11

D12

C12

B12

A12

B13

A13

D14

C14

B14

A14

D15

C15

B15

A15

D16

C16

A16

V33

A9

VFIELD

VR0

VR1

VR2

VR3

VR4

VR5

VR6

VR7

VG0

VG1 '

VG2

VG3

VG4

VG5

VG6

VG7

VB0

VB1

VB2

VB3

VB4

VB5

VB6

VB7

VR0

VR1

VR2

VR3

VR4

VR5

VR6

VR7

VG0

VG1

VG2

VG3

VG4

VG5

VG6

VG7

VB0

VB1

VB2

VB3

VB4

VB5

VB6

VB7

I__L30'y~v

ö ö ö ö ö ö ö ö ö o o o o o o o o o o o o o

VVVVVVVVVCCCCCCCCCCCCC

VV VVVVVVVVVVVVVVVVVVVV

Pow e r a nd G roun d

SDA

SCL

U18B

PW365

FB_11_OHM_500MA

V3 PV 3P V3 PV 3P V3 P

PDWN

NDSP_EN

VGASEL

GAFEOE

ICSDAT

ICSCLK

ICSSTD

ICSSTM

GDFEOE

DTXON

PC6

379

R378 PIO5

V3P V3P V3P

V25V25

V3P

o

^ 22l

V25 V25 V25

^ ~ p 2uF |~Ö.1uF j~Ö.

MUTE

SLEEP1

in/ext

R380

4.7K

V25 V25 V25

C1

î î Î

C183 C184 C185

I 0.1uF~ p .1uF~j~ Ö.1uF I 0.1uF j 0.1uF j 0.

î î Î

C202 C203 C204

MUTE

SLEEP1

PIO4

V25 V25

î Î

C186 C

CPUEN A0

RESET A1

CLKIN

MCKEXT A3

DCKEXT A4

UCSRC A5

XTALI A6

XTALO A7

WDTEN A9

RXD A11

TXD A12

IRRCVR0 A14

IRRCVR1 A15

PORTA0 A17

PORTA1 A18

PORTA2 A19

PORTA3

PORTA4 D0

PORTA5

PORTA6

PORTA7

PW365 D3

PORTB0 D5

D6

PORTB1

PORTB2 D7

PORTB3 D8

PORTB4 D9

PORTB5 D10

PORTB6 D11

PORTB7 D12

PORTC0 D14

PORTC1 D15

PORTC2

PORTC3 RD

A7

PORTC4 WR

B8

PORTC5 BHEN

PORTC6

PORTC7

CPUTMS RAMWE

CPUTCLK CS0

CPUTDI CS1

CPUTDO

MODE0 EXTINT0

MODE1 EXTINT1

MODE2 EXTINT2

V25

V25 V25

V25C

C188 C189

F 0.1

DCLK

AD15

DVS

AC15

DHS

U18C

DENR

DENG

DENB

DRE0

AA26

DRE1

AA25

DRE2

AB26

DRE3

DRE4

DRE5

AC26

DRE6

AC25

DRE7

DGE0

AC24

DGE1

AD26

DGE2

AD23

DGE3

AC22

DGE4

DGE5

AF25

DGE6

AF24

DGE7

AE23

DBE0

DBE1

AD21

DBE2

AE22

DBE3

AE19

AE18

DBE6

AE17

DBE7

AF13

DRO0

AC12

DRO1

DRO2

AE12

DRO3

AF12

DRO4

AE11

DRO5

AF11

DRO6

DRO7

AF10

DGO0

AD9

DGO1

AC9

DGO2

DGO3

AD8

DGO4

AC8

DGO5

AF8

DGO6

AF7

DGO7

AE7

DBO0

AF6

DBO1

AE6

DBO2

AC6

DBO3

DBO4

AD5

DBO5

AF4

DBO6

AE3

DBO7

V3P V3P V3

^ 'p 2uF j 0.1uF~j~Ö.1uF j 0.1uF j 0.1uF j 0.j 0.1uF j 0^ ui22uF j 0.1uF

RRE1

RRE2

RRE3

47R

RRE4

RRE5

RRE6

RRE7

RGE0 47R

RGE1

RGE2

RGE3

47R

RGE4

RGE5

RGE6

RGE7

47R

RBE0

RBE1

RBE2

RBE3

RBE4 47R

RBE5

RBE6

RBE7

RRO0 47R

RRO1

RRO2

RRO3

RRO4 47R

RRO5

RRO6

RRO7

RGO0 47R

RGO1

RGO2

RGO3

RGO4 47R

RGO5

RGO6

RGO7

RBO0 47R

RBO1

RBO2

RBO3

47R

RBO4

RBO5

RBO6

RBO7

A1

V1 AC16

V2 AD16

A2

W1

V3

V4

W3

AA1

A8

AB2

AA3_ A10

A10

AC1

AB3

AD1

A13

AE1

AD2

AB4

A16

AC3

AF1

AE2

U18D D1

Misc D6

H2

K1

D4

K2

M3

D13

T3

T4

U1

ROMOE

oR2

ROMWE

RAMOE

P1 NS ^ \ / v R84

B R3 CS0n n c ScNr

R4

CS2

CS3n

12

CS3

G2 EINT0

H1__EINT2

F1

NMI

V25

0 C191 V25 V25 V25P V25P V3P V3P V3P V3P V3P V3P

1«

0.1

F > uF T TÎ T T T T T T T

A[19:0]

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

A14

A15

A16

A17

A18

A19

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

RDn

ROMOEn

ROMWR84 a3 ns

CS1n

CS2N1

CS3N1

VVINT

EINT1

EINT2

NMI

C172 C173 C174 C175 C176 C177 C178 C179 C180 C

M î M M î M

I 0.1uF I 0.1uF I 0.1uF I 0 .1uF j 0.1uF j 0.1uF ~|~ Ö.1uF j 0.1uF j 0.1uF | 0.

C192 C192C194 C195 | C196 C197 C198 C199 C200 C:

PW365

Disp la y P ort DBE5

B

Main (Video)

Page 29

0206

——0207 —■—0208 ——I

.....

. 0208 —— C20!

U19

DIE16

DIE17

DIE18

DIE19

DIE20

DIE21

DIE22

DIE23

8

DIE

DIE9

DIE10

DIE11

DIE12

DIE13

DIE14

DIE15

DIE0

15

DIE1

14 25

DIE2

13

DIE3

12

DIE4

11

DIE5

10

6

DIE

9

DIE7

DIO16

DIO17

DIO18

DIO19

DIO20

DIO21

DIO22

DIO23

DIO8

DIO9

DIO10

DIO11

DIO12

DIO13

DIO14

DIO15

DIO0

DIO1

DIO2

DIO3

DIO4

DIO5

DIO6

DIO7

80 79

IDCK

78 89

DE

76

HSYNC

77

VSYNC

CTL1

83

CTL2

82

CTL3

24

EDGE

25

PIXS

VCC

VCC

VCC

VCC

IVCC

IVCC

IVCC

IVCC

AVCC

AVCC

AVCC

PVCC1

PVCC2

TX2+

TX2-

TX1+

TX1-

TX0+

TX0-

TX0+

TX0-

EXT_SWING

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

GND

GND

GND

GND

GND

GND

AGND

AGND

AGND

AGND

PGND1

PGND2

45

_

TX2-

43 1X1+

42

39

_

TX0-

35 1X0+

TX0

34

32

26 15

PD

87

7

31

57

67

33

37

41

47

19

86

\

s

\

s

\

DGE0

DGE1

DGE2

DGE3

DGE4

)GE5 1

DGE6

DGE7

DBE0

DBE1

DBE2

DBE4

DBE5

DBE7

DHS

DVS

C229

47uF

RE0

RE1

RE2

RE3

RE4

RE5

RE6

RE7

DRO0

DRO1

DRO2

DRO3

RO4

RO5 V33L

RO6

RO7

GO0

GO1

GO2

GO3

GO4

GO5

GO6

GO7

BO0

BO1

BO2

BO3

BO4

BO5

6

BO

BO7

DRE[7:0]

DRO[7:0]

R92

10K

R95

NU

A A

R94

NC

R96

10K

V00

U20

LM2937 SOT223

VI VO

N

0227 0228 DBE4

G

DGO[7:0]

DBO[7:0]

DCLK

DENG

TAB

330pF I 330pF | 330pF

R93 400

—------

'^ ^ 021^ ^ 0211^ 0212^ 021^ ^ 0214

pF 330pF 330pF 330pF 330pF 330pF

- “ 0216 —p 0217 ' 0218

330pF 330pF 330pF 10uF

T

0222 _|_+ 0223 ^J_+ 0224 |

T

1 + 0223 _J+ 0224

100pF ,-"T'',-10uF T-»

______

DENR

DENG

DENB

>.10uF

T F T 22uF

DRE[7:0] DRE1

DGE[7:0] DGE1 DGO[7:0]

DBE[7:0] DBE1 DBO[7:0]

DRE0

DRE2

DRE3

DRE4

DRE5

DRE6

DRE7

DGE0

DGE2

DGE3

DGE4

DGE5

DGE6

DGE7

DBE0

DBE2

DBE3

DBE5

DBE

DBE7

____

6

Z T

1

0225 200+ Ohm

L

JP4

200+ Ohm

0:

10uF

L32

_rVVY"\_

200+ Ohm

V33L V33T

0226

V00

DRO2

DRO3

DRO4

DRO5

DRO6

DRO7

DGO0

DGO1

DGO2

DGO3

DGO4

DGO5

DGO6

DGO7

DBO0

DBO1

DBO3

DBO4

DBO5

6

DBO

DBO7

3L

4

1

=0215

).1uF

0221

0.1uF

R90 R91

0

DHS

DVS

__

>i=17

J6

SHELL1

DATA2-

DATA2+

DATA2/4_SHLD

DATA4-

DATA4+

DD0_0LK

DD0_DATA

A_VSYN0

DATA1-

10

DATA1+

11

DATA1/3_SHLD

DATA3-

13

DATA3+

u.

+5V

GND

H_PLUG_DET

DATA0-

18

DATA0+

19

DATA0/5_SHLD

DATA5-

DATA5+

22

0LK_SHLD

23

0LK+

24

0LK-

A_RED

A_GREEN

A_BLUE

A_HSYN0

A_GND1

A_GND2 N02

06

SHELL2

DVI_V

N01

27

28

D0LK

D

C

Main (Video)

Page 30

VCCV VCCV

SCL5V

SDA5V

VVVS

R22 NC R23

VVHS R25 33 R26

CCV2

069 R30

C7C

=0

I 56

560pF

VCCV VCC

.20MA

C74

C75

47uF

0.1uF

2

K

U10

SCL

SDA

16

SDO

13

VIN INTRO RED

HIN

VIDED

REF

SEN

SMS

ASEL

Z86229

L20

VDD

BOX

GREEN

BLUE

CSYNC

LPF

VSSA

12

17

11

R17

C280

p H

R20

13K

13K

R28

13K

C286

2K <K

C285

[4k =

C284

33pF

R31

C28

7^ '~33pF =

a

C71 C72

iF I 68nF 0

1uF R33 R34 R35

220nF

VBOX

VCCR

VCCG

VCCB

VVINI

SDA

.

• R2K ai

2

V33 VCC

G

s .

SN7002

1 D15 2

1N1183A

.

' R23K7 02

SCL

-----------

3

2

< R19

_ 22K

SDA5V

V33

G

. .

SN7002

D16

^

1N1183A

3

-----------

R38

_ 22K

SCL5V

L

:T ■

L

:T ■

1

:T ■

FB_42C_0HM_2CCM;

VAAV

m[

r-rsC1(

| 22u

L

0 .

1

:I 0 ■1:T ■

1

:I 0 ■

Main (Video)

47R

R45

47R VY7

47R VY3

47R VUV7

47R VUV3

VY6

VY5

VY4

VY2

VY1

VY0

VUV6

VUV5

VUV4

VUV2

VUV1

VUV0

VFIELD

VVVS

VVHS

VVCLK

/

/

/

/

/

/

/

/

/

/

/

/

/

VY[7:0]

VUV[7:0]

VAAV

Page 31

5 4 3 2

02_INPUT

OUTA

OUTB

NICAM OUTL

NICAM OUTB

D D

C C

SIF

SDA5V

SCL5V

SDA

02_INPUT

04_MCU+AMP

POWER_ON

MUTE

MUTE1

SCL

IR

I

03 NICAM

B B

04_MCU+AMP

A A

5 4 3 2

Page 32

C41 ^ C71 __

1000P ^ 220P^

1000P f— —y~

C58 5.$uH

1000PX

“ L5

-OULr-f-OUb—f

^5.6uH ^C74

X ^220P^1

L6

-----

f-OUL/-

C82 “*“5.6uH

1000P ^

~ L7

-----

HIL-

C63 5.6uH

1000P I

“ LS

vJUl

^ 5.6uH =bC77 <|

I J220P ¿1

±R100 - 4700P

----

*-

■ ieu-HH

~ R101 ' r

¿C75

I220P^1

■±- R102 “

' 3ÖU

C8S

100K 54700P

R24 zt C90

100K I 4700P

R25 ^C108

100K ^4700P

R103 -

-3&

C20

| | O.luF

O

L_

Mr-

C25

4.7u/16V

UVS7305M.FH

IN1A GND

IN1B V+

IN2A TONE-HA

IN2B TONE-HB

IN3A TONE-LA

IN3B TONE-LB

IN4A SRS/SS FIL1

IN4B SRS FIL2

IN5A BBE1A

IN5B BBE1B

IN6A BBE2A

IN6B BBE2B

i C26

l.7u/16V

MONA LINEA

MONB LINEB

SDA OUTA

SCL OUTB

VREF CSR

A6C CSB

CVA CTH

CVS CTL

Ul

NJW1144

VIN VOUT

GND

T

r i 6,; i I - / - i s 11 g5,=i 1

33nX -L33" Ji.inJ.

13C11 -j- -j- -j- -J-3.3n

--

1 C38

zö1u;

+5VI

l

1

SS C6 J-

+ 1.. ^

“I C9 C4 C7

|2.2n lOOn lOOn

C158

10uF/16V

C159

10uF/l6V

L $ 1u z i1u Z i

Z= C2

I 330n- -

T

C1

22n

7% C56

47u/18V

IR CD—

IN/EXTCD-

STBLED O-

P0WER_0N O-

R22 < Q5 *

01

LED RED -

L 1

>-

]

-----

]

-----

L w-

22K^SN°°02-

22K SSN7002 r

i--

+5VT 1

+5VT 2

GND 3

+5VIN 4

+5VIN 5

GND 6

+5V 7

+5V

GND 9

VIDEO A10

GND 1

STBLED 4

MUTE b

SDA b

SLEEP1 9

-D>h

D4

->h

-Oh

D2

-*h

10

8

i

J11

C0N10

J11A

C0N10

Audio/Tuner

Page 33

J5

C0N12

VSC

Q

C45

O.lu

_y+9v

_J+5V

— 9+5V

-OPOWER_ON

JP+5VIN

1

R18

2K

3 ^

PA3 PA4

PA2 PS5

PA1 PA6

PAO PA7

PB2 0SC2

PB1 0SC1

PBO VOD

VSS /RES

INT PCI

~ ^7

R53

0

—

- a POWER_ON

R64

—AA/~

+24VIN

O

C21 I

lOOn _

MUTE+V

-INV1 OUT1

GND OUT2

-INV2

INV1.2

-V

¡pAAr-

Q2

>3904

Hh

Q4

>3904

. C22

2 2200u/50V

C49

0.1u

Q1-A

IRF7314

L9

”11

sJJLr-

FB_420_0HM_200MA

C23:

22n

C34 :

22n

—«—

C27

1000u/50V

C36

1000u/50V

---£---

Q12

3904

R49

0

D6

1N4148

—N—

R37

X

3.3K ^ C163

^ O.lu

r

r

IN/EXT

Audio/Tuner

Page 34

6 I 5 4 3 2

D

D

+9V

C

AFSNDA

B

Audio/Tuner

A

Page 35

</> IQ

v) 'O

m jO

SP 1

s V

Öl-

s f l

Ul Iqo

m

GND 1

V0L_UP 2

V0L_DN 3

MENU 4

P_UP 5

P_DN 6

INPUT 7

POWER 8

GND 9

XS621

C0NN9

LED-G

B601

LED-R

O

o o

> >

(l_I i__i ,<

" 11 Ti

»R604

100

»R601

10K

-w -

R603

R602

—V\A-

270

180

B602

rh

.C602

OPEN

XS601

C0NN6

GND 1

+5V 2

IR_REC 3

+5VIN 4

RELAY 5

GND 6

D

B

SP-L SP-R

Keypad

Remote control receiver

External L/R Speakers

Page 36

D

VD701 y o —|

IN4148

VD702

IN4148

H 4

VD703

IN4148

■+€

p/ O—< i

Q K52

^ O H I

9K48

K64

X ° n

OK63

_gK51

_£K47

^O-Hl

?K44

B

O^O-H I

/''O —i / o -

OK62 9K61

^O H »

gK50

»

^O-H I

^K42

✓o-<»

QK38

^O-H I

<?K33

✓o-| /'o -, y o -|

OK32 0K31 OK30

^O-H I

^ O h i

j/O-i'

y'O-i i

gK19

^ O H I

^ O -n

gK11

✓OHI

gK7

✓CH i

g K3

^O H »

9K26

^ 0 - 0

?K22

^O H »

OK18

^O H »

9K14

^ / O h i

QK10

✓0-<>

gK6

gK28

«'OH I

OK24

^O H »

QK20

jp fO-*»

9 k16

O K12

✓OHI

QK8

✓OHI

gK 4

_JK27

_Jk23

_^K15

✓°-|

OK29

^ O -n

gK25

✓CM'

gK21

^ o -> >

_£K17

/ ( X i

_£K13

«/OH I

_JK9

j/O-i'

gK5

^O-i i

_g_K1

14

_ 2 fl.

_21

_22

_24.

N701

PT2222

UPD6122

-T ~ \ .

t

„ 100PF

11 Ih -f

10_J£

9

7 100

C702

O

G701 C703

455KHZ 100PF

__

B701

R702

w -

BT701

3V

I b

1 V701

8050

Remote control

Page 37

Basic Operations & Circuit Description

MODU LE

T h e r e a re 1 p c . p a n e l a n d 8 p c .s P C B in c lu d in g 2 p c .s Y / Z S u s ta in e r b o a rd , 2 p c .s Y D riv e

b o a r d , 2 p c . s X (le ft a n d rig h t) E x te n s io n P C B , 1 p c . C o n tr o l (S ig n a l In p u t) a n d 1 p c. P o w e r

b o a rd in th e M o d u le .

SET

T h e r e a re 5 p c .s P C B s in c lu d in g 1 p c. T u n e r /A u d io b o a rd , 1 p c. K e y p a d b o a rd , 1 p c .

R e m o te C o n tro l R e c e iv e r b o a rd , 1 p c. L /R S p e a k e r s a n d 1 p c . M a in (V id e o ) b o a rd in th e S E T .

Page 38

Parts position

Local key Main (Video) Tuner/Audio

Control (Signal Input)

Page 39

PCB function

1. Power:

(1). Input voltage: AC 110V~240V, 47Hz~63Hz.

Input range: AC 90V(Min)~265V(Max) auto regulation.

(2). To provide power for PCBs.

2. Main (Video InterFace) board: To converter TV signals, S signals, AV signals, Y Pb/

Cb Pr/Cr signals, DVI signals and D-SUB signals to digital ones and to transmit to

Control board.

3. Control board: Dealing with the digital signal for output to panel.

4. Y-Sustainer / Z-Sustainer board:

(1). Receiving the signals from Control and high voltage supply.

(2). Output scanning waveform for Module.

5. Y-Drive board: Receive signal from Y sustainer, output horizontal scanning wave

form to the panel.

6. X (left and right) extension board: Output addressing signals.

7. Tuner/Audio Board: Amplifying the audio signal to the internal or external speakers

of which selected.

To convert TV RF signal to video and audio signal to Main board.

Page 40

PCB failure analysis

1. CONTROL: a. Abnormal noise on screen. b. No picture.

2. MAIN (VIDEO): a. Lacking color, Bad color scale.

b. No voice.

c. No picture but with signals output, OSD and back light.

d. Abnormal noise on screen.

3. POWER: No picture, no power output.

4. Z - Sustainer: a. No picture.

b. Color not enough.

c. Flash on screen.

5. Y - Sustainer: Darker picture with signals.

6. Audio Bard: a. No voice. (Make sure status: Mute / Internal, External speaker)

b. Noise

7. Y/Z - Sustainer: The component working temperature is about 55oC.

If the temperature rises abnormal, this may be a error point.

Page 41

Basic operation of Plasma Display

1. After turning on power switch, power board sends 5Vst-by Volt to Micro Processor

IC waiting for ON signals from Key Switch or Remote Receiver.

2. When the ON signal from Key Switch or Remote Receiver is detected, Micro Processor

will send ON Control signals to Power. Then Power sends (5Vsc, 9Vsc, 24V and RLY

ON, Vs ON) to PCBs working. This time VIF will send signals to display back light,

OSD on the panel and start to search available signal sources. If the audio signals

input, them will be amplified by Audio AMP and transmitted to Speakers.

3. If some abnormal signals are detected (for example: over volts, over current, over

temperature and under volts), the system will be shut down by Power off.

Page 42

M a in I C S p e c i f i c a t i o n s

- PW171 Image Processor

- AD9883A 110MSPS/140MSPS Analog Interface for Flat Panel Displays

- NV320 Video Enhancement Processor

- VCP 323XD comb Filter Video Processor

- Si1161B Panel Link Receiver

- Z86229 NTSC Line 21 CCD Decoder

- TDA9850 BTSC stereo/SAP decoder

- NJW1144 Audio Processor

Page 43

d to result in a personal injury or loss of life. C

ustomers using or sel

Prelim

p i x e l w o r k s

General Description

PW171 is a highly integrated “system-on-a-chip” that interfaces

analog, digital, and video inputs in virtually any format to a flat panel

monitor or multimedia display. PW171 is pin-compatible with the

PW364.

An embedded SDRAM frame buffer and memory controller perform

frame rate conversion. Computer images from VGA to UXGA at

almost any refresh rate can be resized to fit on a fixed-frequency

target display device with any resolution up to UXGA with full 24-bit

color.

PW171 includes advanced second-generation image scaling that

provides completely programmable, horizontal and vertical image

scaling.

PW171 also includes advanced second-generation sync decoding

which provides full support for a wide variety of sync types. This

includes interlaced, progressive, sync-on-green, and TMDS DE (Data

Enable) only.

PW171 ImageProcessor supports NTSC or PAL video data with a 4:3

aspect ratio and 16:9 aspect ratio sources, such as DVD or HDTV.

Nonlinear scaling and separate horizontal and vertical scalers allow

these inputs to be resized optimally for the native resolution and

aspect ratio of the display device.

PW171 uses an integrated PLL to synchronize the display interface

timing to the input timing. This requires only a single external crystal

to generate all necessary clocks for the system.

An integrated OSD controller provides bit-mapped based OSDs with

16 colors from a 64K color palette. The OSD controller supports

transparent and translucent functions.

PW171 provides a Pulse Width Modulation (PWM) output for low cost

backlight or audio control.

With reference source code and an on-chip microprocessor,

manufacturers can develop feature-rich products with rapid time-to-

market. Programmable features include the user interface, custom

start-up screen, all automatic imaging features, and special screen

effects.

PW171 incorporates new features while maintaining backward

compatibility with the PW264 and PW364 ImageProcessors.

Product Specification:

PW171 ImageProcessor

XGA/SXGA/UXGA Flat Panel Display Controller IC

lling Pixelworks devices for use in such

inary

-►

ADOT M DS

Rete lver

PW171

Video

Decoder

□

i C-g-niputcr"

System Block Diagra m

Features

□Second-generation Image Scaling

□Second-generation Automatic Image Optimization

□Color Space Converter for graphics inputs

□Video processing

□ Picture-In-Picture (PIP)

□Frame rate conversion

□Color matrix for improved color temperature adjustment

□On-board PLLs to generate MCLK and DCLK

□On-screen display

□On-chip microprocessor

□JTAG debugging port

□8-bit, 9-bit, or 10-bit display outputs

□24-bit CPU Addressing

□ Hardware 2-Wire serial bus support

□ Hardware PWM output

Applications

□LCD Monitors

□Plasma Displays

□Multimedia Displays

Display

Device

Page 44

ANALO G 110 MSPS/140 MSPS Analog Interface

►

FEATURES

140 MSPS Maximum Conversion Rate

300 MHz Analog Bandwidth

0.5 V to 1.0 V Analog Input Range

500 ps p-p PLL Clock Jitter at 110 MSPS

3.3 V Power Supply

Full Sync Processing

Sync Detect for “Hot Plugging”

Midscale Clamping

Power-Down Mode

Low Power: 500 mW Typical

4:2:2 Output Format Mode

APPLICATIONS

RGB Graphics Processing

LCD Monitors and Projectors

Plasma Display Panels

Scan Converters

Microdisplays

Digital TV

DEVIC E S for Flat Panel Displays

AD9883A

FUNCTION A L BLOCK DIAG RAM

GENERAL DESCR IPTION

The AD9883A is a complete 8-bit, 140 MSPS monolithic analog

interface optimized for capturing RGB graphics signals from

personal computers and workstations. Its 140 M SPS encode

rate capability and full power analog bandwidth of 300 MHz

supports resolutions up to SXGA (1280 x 1024 at 75 Hz).

The AD9883A includes a 140 MHz triple ADC with internal

1.25 V reference, a P LL, and programmable gain, offset, and

clamp control. The user provides only a 3.3 V power supply,

analog input, and Hsync and C O AST signals. Three-state

CMOS outputs may be powered from 2.5 V to 3.3 V.

The AD9883A’s on-chip PLL generates a pixel clock from the

Hsync input. Pixel clock output frequencies range from 12 MHz to

140 MHz. PLL clock jitter is 500 ps p-p typical at 140 MSPS.

When the COAST signal is presented, the PLL maintains its

output frequency in the absence of Hsync. A sampling phase

adjustment is provided. Data, Hsync, and clock output phase

relationships are maintained. The AD9883A also offers full sync

processing for composite sync and sync-on-green applications.

A clamp signal is generated internally or may be provided by

the user through the CLAMP input pin. This interface is fully

programmable via a 2-wire serial interface.

Fabricated in an advanced CMOS process, the AD9883A is

provided in a space-saving 80-lead LQFP surface-mount plastic

package and is specified over the 0°C to 70°C temperature range.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:

Fax:

Page 45

n DSP C o r p o r a t io n N V32 0 D a t a S heet

NV320 Video Enhancement Processor

1.0 Introduction

The NV320 is a single-chip, programmable

video display processor providing advanced

features for progressive scan, high frame-rate

TV. The NV320 improves upon the functional

ity of the NV320P by handling non-standard

video input signals. Other feature enhance

ments include DCTI, Black Level Stretch, and

Saturation Control.

The NV320 offers the following features.

1.1 Highly Integrated Video Processor

• Three, on-chip, 10-bit Digital-to-Analog

Converters (DACs)

• Built-in memory controller supporting

SDRAM or SGRAM

• 0.35|i CMOS process

• 3.3V power supply with 5V tolerant I/Os

• Standard 208-pin PQFP

1.2 Video Input

• Multiple video input modes

- Data acquisition mode

- Line-locked mode

- DVD mode

• Multiple video input data formats

- Digital 16-bit YUV (4:2:2) or 12-bit YUV

(4:1:1)

- Digital 8-bit YUV (ITU-R 656)

- Digital 24-bit YUV (4:4:4)

1.3 Noise Reduction

• Motion adaptive noise reduction filter

1.4 Color Processing

• Built-in color space conversion

• Selectable output color space: YUV or

RGB

1.5 Video Processing

• Advanced, non-linear video processing

• Motion compensated deinterlacing

• Programmable peaking

• Non-linear interpolation

• Background coloring

• Anti-flickering circuitry

• NTSC/PAL to SDTV 480p format conver

sion

• Frame rate up-conversion (50Hz up to

75Hz for PAL, 60Hz up to 90Hz for NTSC)

• DCTI (Digital Color Transient Improve

ment)

• Black Level Stretch

• Saturation Control

1.6 Host Interface

• I2C interface

• No programming needed for default mode

application

1.7 General Description and Applications

The NV320 is a single chip digital video pro

cessor for progressive and digital TV applica

tions. It provides high quality video

processing including video noise reduction,

motion compensation, sharpness enhance

ment, and resolution enhancement. It also

provides frame rate conversion and progres

sive scan conversion with deinterlacing.

The NV320 is a CMOS mixed signal circuit

highly integrated with three, 10-bit digital-to-

analog converters controlled by the I2C inter

face. The NV320 accepts 16-bit YUV (4:2:2),

12-bit YUV (4:1:1), and 8-bit YUV (ITU-R 656)

simultaneously, or it accepts 24-bit YUV

(4:4:4) input from a front-end digital video

color decoder or from an analog-to-digital

converter. Additionally, NV320 supports multi

ple video input modes: acquisition mode, line-

locked mode, and DVD mode.

The NV320 has an on-chip detection logic

block that corrects non-standard input signals

before processing.

Applications for the NV320 chip are listed

here.

• Progressive scan televisions

• Digital televisions (the chip is DTV/HDTV

ready)

Page 46

n DSP C o r p o r a t io n N V32 0 D a t a S heet

• Internet televisions

• Home theater and multimedia televisions

• Video conferencing

3.0 Block Diagram of NV320

2.0 Ordering Information

Part

Number

Package

NV320

PQFP 208

Plastic quad flat pack

Description

Version

age, 208 leads

1.0

SD RAM /SGRAM

Interface

Figure 1. Block Diagram of NV320

Page 47

VPC 323xD Comb Filter Video Processor

1. I nt rod uc tio n

The VPC 323xD is a high-quality, single-chip video front-end, which is targeted for 4:3 and

16:9. 50/60 Hz and 100/120 Hz TV sets. It can be combined with other members of the

DIGIT3000 IC family (such as DDP 331x) and/or it can be used with 3rd-party products.

The main features of the VPC 323xD are

- High-performance adaptive 4H comb filter Y/C separator with adjustable vertical peaking.

- Multi-standard color decoder PAL/NTSC/SECAM including all substandards.

- Four CVBS, one S-VHS input, one CVBS output.

- Two RGB/YCrCb component inputs, one Fast Blank (FB) input.

- Integrated high-quality A/D converters and associated clamp and AGC circuits.

- Multi-standard sync processing.

- Linear horizontal scaling (0.25

- PAL+ preprocessing.

- Line-locked clock, data and sync, or 656-output interface.

- Peaking, contrast, brightness, color saturation and tint for RGB/YCrCb and CVBS/S-VHS.

- High-quality soft mixer controlled by Fast Blank.

- PIP processing for four picture sizes (1/4, 1/9, 1/16, or 1/36 of normal size) with 8-bit

resolution.

- Control interface for external field memory.

- I2C-bus interface.

- One 20.25-MHz crystal, few external components.

- 80-pin PQFP package.

...

4), as well as nonlinear horizontal scaling 'Panoramavision'.

Page 48

Sil 161B PanelLink® Receiver

Data Sheet

August 2002

General D escrip tion

The SiI 161B receiver uses PanelLink Digital

technology to support high-resolution displays up to

UXGA (25-165MHz). This receiver supports up to true

color panels (24 bits per pixel, 16M colors) with both

one and two pixels per clock.

All PanelLink products are designed on a scaleable

CMOS architecture, ensuring support for future

performance enhancements while maintaining the

same logical interface. System designers can be

assured that the interface will be stable through a

number of technology and performance generations.

PanelLink Digital technology simplifies PC and display

interface design by resolving many of the system level

issues associated with high-speed mixed signal design,

providing the system designer with a digital interface

solution that is quicker to market and lower in cost.

Features

Low Power Operation: 280mA max. current

consumption at 3.3V core operation

Time staggered data output for reduced ground

bounce and lower EMI

Sync Detect feature for Plug & Display

Cable Distance Support: over 5m with twisted

pair, fiber-optics ready

ESD tolerant to 5kV (HBM on all pins)

Compliant with DVI 1.0 (DVI is backwards

compatible with VESA® P&DTM, FPDI-2™ and

DFP)

HSYNC de-jitter circuitry enables stable operation

even when HSYNC contains jitter

Low power standby mode

Automatic entry into standby mode with clock

detect circuitry

Standard and Pb-free packages (see page 25).

Page 49

O

Pr e lim in a r y Pr o d u c t Sp ec ifica tio n

o

Z86 2 2 9

N

T o t a lly L og i c a l

FEATURES

Speed Pin Count/ Standard On-Screen Display Program

Devices (MHz) Package Types Temp. Range & Closed Captioning Rating Tim e of Day

Z86229 V 2 18-Pin DIP, SOIC 0°C to +70°C Yes Yes Yes

N T S C L in e 2 1 C C D D e c o d e r

Autom atic Data Extraction

Complete Stand-Alone Line 21 Decoder for Closed-

Captioned and Extended Data Services (XDS)

Preprogrammed to Provide Full Compliance with

EIA-608 Specifications for Extended Data Services

Automatic Extraction and Serial Output of Special