Page 1

LEC‐BTS

(Computer‐on‐Module)

Technical Reference

P/N50‐1Z173‐1000

Rev1.0

Advance Technologies. Automate the World.

Page 2

Disclaimer

Information in this document is provided in connection with ADLINK products. No license,

express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in ADLINK´s Terms and Conditions of Sale for such products,

ADLINK assumes no liability whatsoever, and ADLINK disclaims any express or implied warranty, relating to sale and/or use of ADLINK products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other

intellectual property right. If you intend to use ADLINK products in or as medical devices, you

are solely responsible for all required regulatory compliance, including, without limitation, Title

21 of the CFR (US), Directive 2007/47/EC (EU), and ISO 13485 & 14971, if any. ADLINK may

make changes to specifications and product descriptions at any time, without notice.

Trademarks

MS-DOS, Windows, Windows 95, Windows 98, Windows NT and Windows XP are trademarks of Microsoft Corporation. PS/2 is a trademark of International Business Machines, Inc.

Intel and Solid State Drive are trademarks of Intel Corporation. PC/104 is a registered trademark of the PC/104 Consortium. All other trademarks appearing in this document are the

property of their respective owners. CoreModule is a registered trademark, and ADLINK, Little Board, LittleBoard, MightyBoard, MightySystem, MilSystem, MiniModule, ReadyBoard,

ReadyBox, ReadyPanel, RuffSystem, and ReadySystem are trademarks of ADLINK Technology, Inc. All other marks are the property of their respective companies.

Revision History

Revision Reason for Change Date

1.0 Initial Release Dec/14

ADLINK Technology, Incorporated

www.adlinktech.com

© Copyright 2014 ADLINK Technology, Incorporated

Audience

This manual provides reference only for computer design engineers, including but not limited

to hardware and software designers and applications engineers. ADLINK Technology, Inc.

assumes you are qualified to design and implement prototype computer equipment.

ii

Page 3

LEC-BTS

Table of Contents

1 Overview ........................................................................................................................... 1

1.1 Block Diagram........................................................................................................................ 1

1.2 Major Components (ICs)........................................................................................................ 2

1.3 Connectors, Switches, and LEDs .......................................................................................... 3

1.4 Specifications......................................................................................................................... 5

2 Hardware ........................................................................................................................... 7

2.1 CPU ....................................................................................................................................... 7

2.2 Memory ................................................................................................................................. 7

3 Interfaces .......................................................................................................................... 7

3.1 18/24 Bit LVDS LCD ............................................................................................................. 8

3.2 HDMI (High-Definition Multimedia Interface) ......................................................................... 8

3.3 Camera CSI ........................................................................................................................... 8

3.4 Audio (HDA)........................................................................................................................... 8

3.5 PCI Express (PCIe)................................................................................................................ 8

3.6 Gigabit Ethernet .................................................................................................................... 8

3.7 USB Ports .............................................................................................................................. 8

3.8 SATA...................................................................................................................................... 8

3.9 I2C Bus .................................................................................................................................. 8

3.10 SPI ......................................................................................................................................... 9

3.11 Serial (UART)......................................................................................................................... 9

3.12 I2S.......................................................................................................................................... 9

3.13 SD/SDIO Interface ................................................................................................................. 9

3.14 eMMC Interface ..................................................................................................................... 9

3.15 GPIO ...................................................................................................................................... 9

3.16 LPC Debug ............................................................................................................................ 9

3.17 SMARC Interface Signals .................................................................................................... 10

3.18 Debug (DB40) ...................................................................................................................... 13

Appendix A Technical Support ......................................................................................... 15

iii

Page 4

iv

Page 5

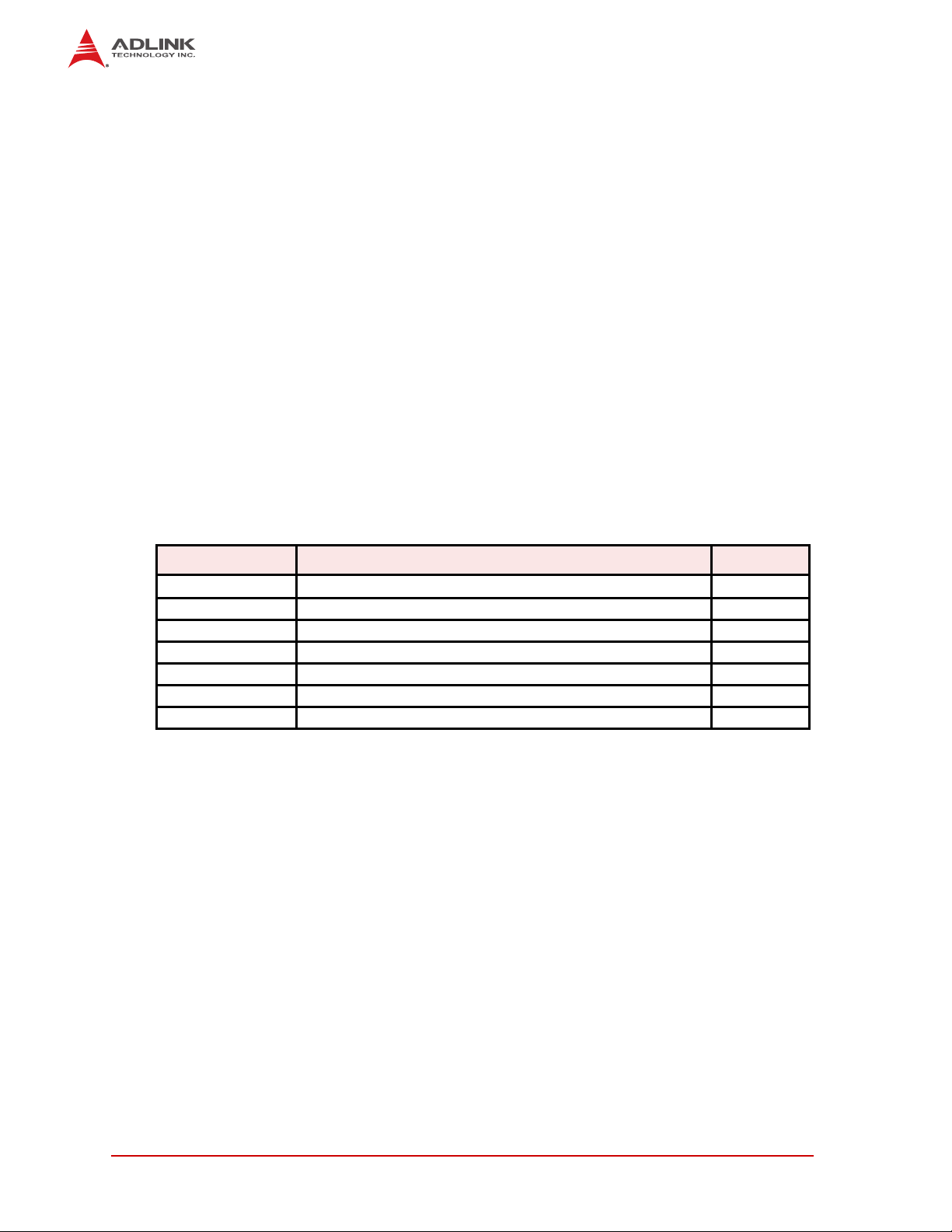

1 Overview

314-pin SMARC Connector

Intel®

E3800 Series

SoC

(System on Chip)

LVDS 18/24-bit

Single Channel

LVDS

Converter

RTD2136

DDI0

LPC

SPI

2x I2C

(GP/LVDS)

2x I2C (PM/CAM)

BOOT Select

Power Management

SDIO

DDI1 (HDMI)

LAN

Controller

i210IT

SATA0

Camera Support (CSI 4L/1L)

Audio (HDA and I2S)

USB 3.0 on AFB

USB 2.0, ports 0,1,2

PCIe x1, PCIe ports 1,2,3

PCIe x1

2x Serial (including RTS/CTS) +

PCU-UART (only RX/TX)

12x GPIO

(Five reserved for CSI)

SMB

MMC

GPIO

Expander

SMBus

INT

Gb

Ethernet

BMC

HWM

SPI

BIOS

Debug

DB40

Connector

DDR3L

1066/1333MHz

DDR3L

On-Board

2/4 GB

Memory

Power

Management

IC

IDTP9145

LEC_BTS_blk_diag_b

This initial manual version presents a general overview of the LEC-BTS. After reviewing this

document you should understand the following features of the LEC-BTS.

Functional Block Diagram

Major Component (IC) Locations and Descriptions

Connector, Switch, and LED Locations and Descriptions

Specifications

SMARC Interface Signal Definitions and Debug Interface Signal Definitions

LEC-BTS

NOTE: Refer to http://www.sget.org/standards/smarc.html

for SMARC specifications. Please

refer to BSP readme documents in the Quick Drive for BSP installation instructions.

1.1 Block Diagram

Figure 1-1 represents the component functions of the module.

Figure 1-1: Functional Block Diagram

Overview 1

Page 6

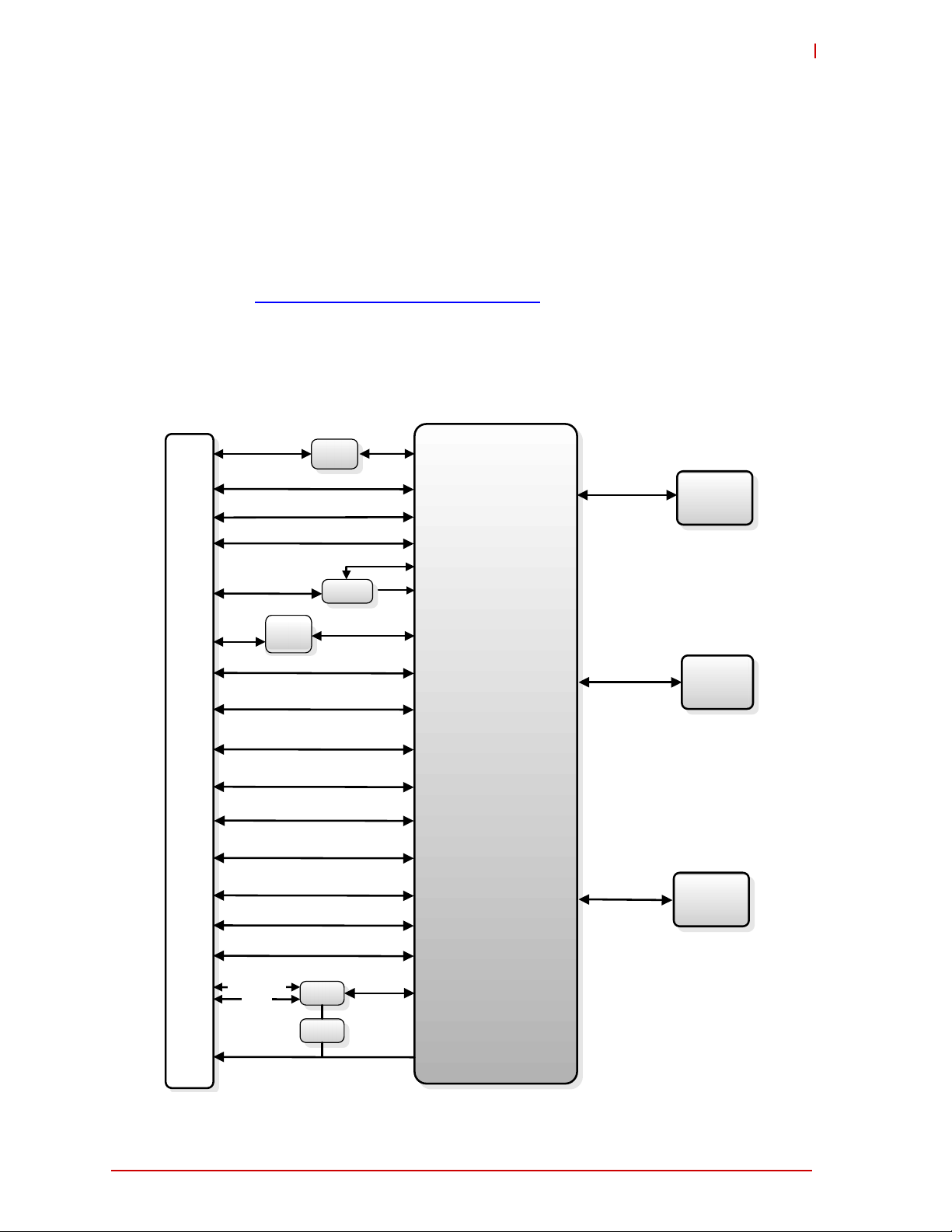

1.2 Major Components (ICs)

LEC_BTS_Top_Comp_a

U1

U26

U25

Key:

U1 - CPU

U25 - DDR3L SDRAM

U26 - DDR3L SDRAM

P156P74

Table 1-1 lists the major integrated circuits on the LEC-BTS, including a brief description of each

IC. Figures 1-2 and 1-3 show the locations of the major ICs.

Table 1-1: Major Integrated Circuit Descriptions and Functions

Chip Type Mfg. Model Description Function

CPU (U1) Intel E3815 (single core,

5W, 1.46GHz)

E3826 (dual core,

7W, 1.46GHz)

E3845 (quad core,

10W, 1.91GHz)

Ethernet

Intel WGI210IT SLIXT Single-port Gigabit

Controller

(U9 [bottom])

DDR3L

Micron MT41K256M16HA-125 On-board DDR3L,

SDRAM (U24

[bottom],

U25, U26

[top], U27

[bottom])

Atom, 22nm SoC

(System on Chip) with

Intel 64 architecture

Ethernet controller

1.35V, 4Gb,

32Mx16x8, non-ECC,

un-buffered System

Memory

Integrates

Processor Core,

Graphics and

Memory

Controller Hub,

and I/O Hub

Integrates GbE

MAC, PHY, and

SGMII/SerDes to

enable 10T/

100TX/1000T

Ethernet signals

using the PCIe x1

bus

Provides

high-speed data

transfer

Figure 1-2: Component Locations (Top Side)

2 Overview

Page 7

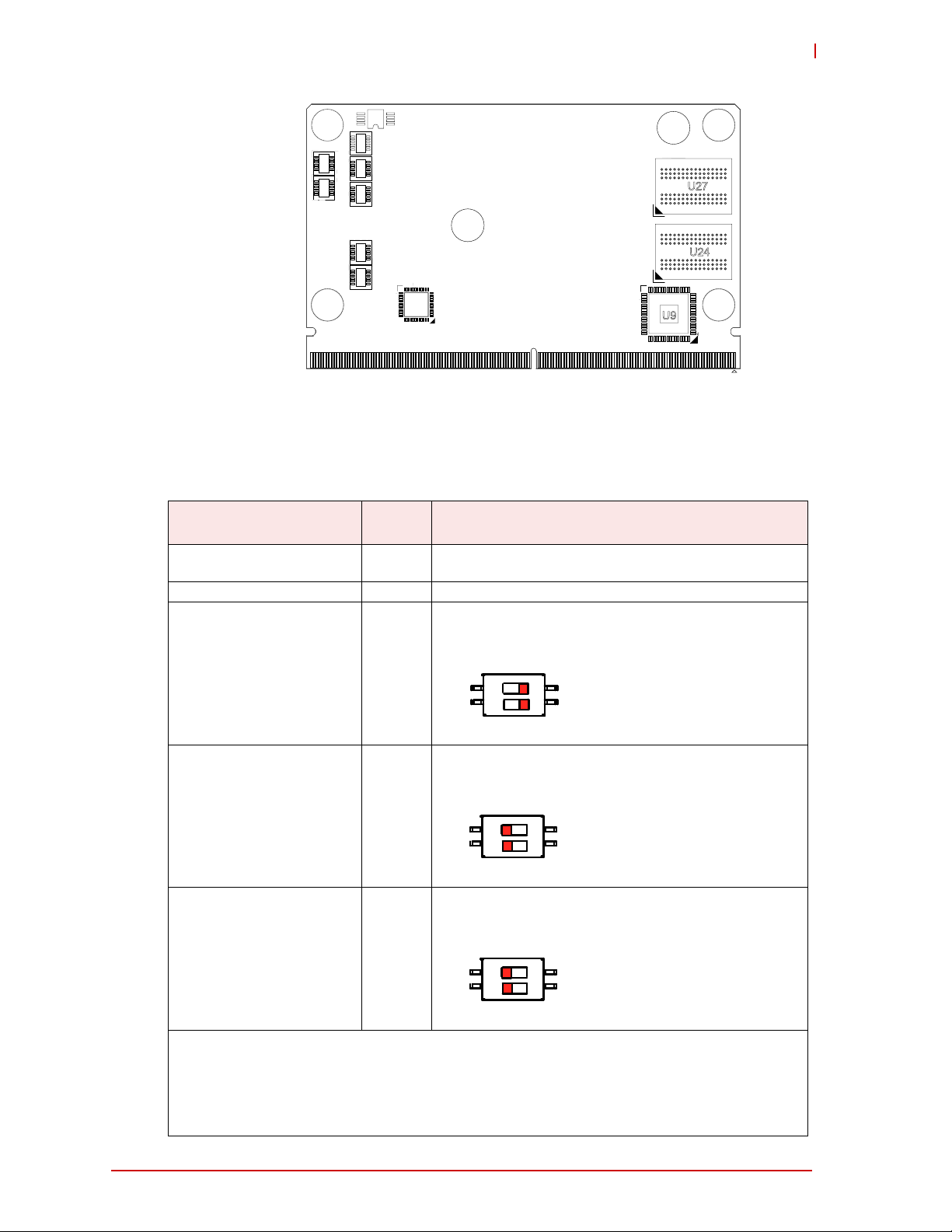

Figure 1-3: Component Locations (Bottom Side)

LEC_BTS_Bot_Comp_a

Key:

U9 - GbE Controller

U24 - DDR3L SDRAM

U27 - DDR3L SDRAM

U9

U24

U27

S75S158

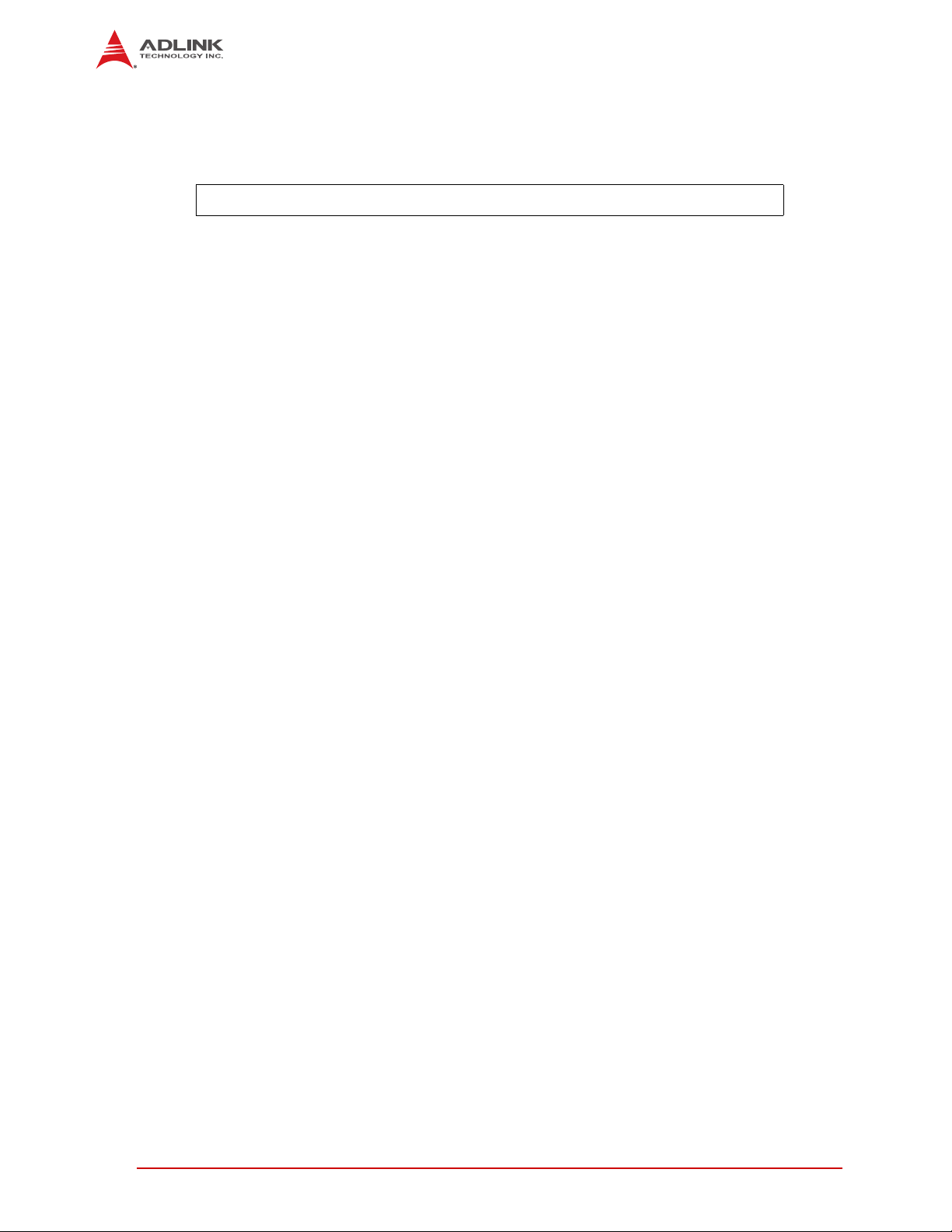

ON

1 2

(1 2)

LEC-BT_SW1_c

(4 3)

Switch Default Setting

ON

1 2

(1 2)

LEC-BT_SW2_b

(4 3)

Switch Default Setting

ON

1 2

(1 2)

LEC-BT_SW3_b

(4 3)

Switch Default Setting

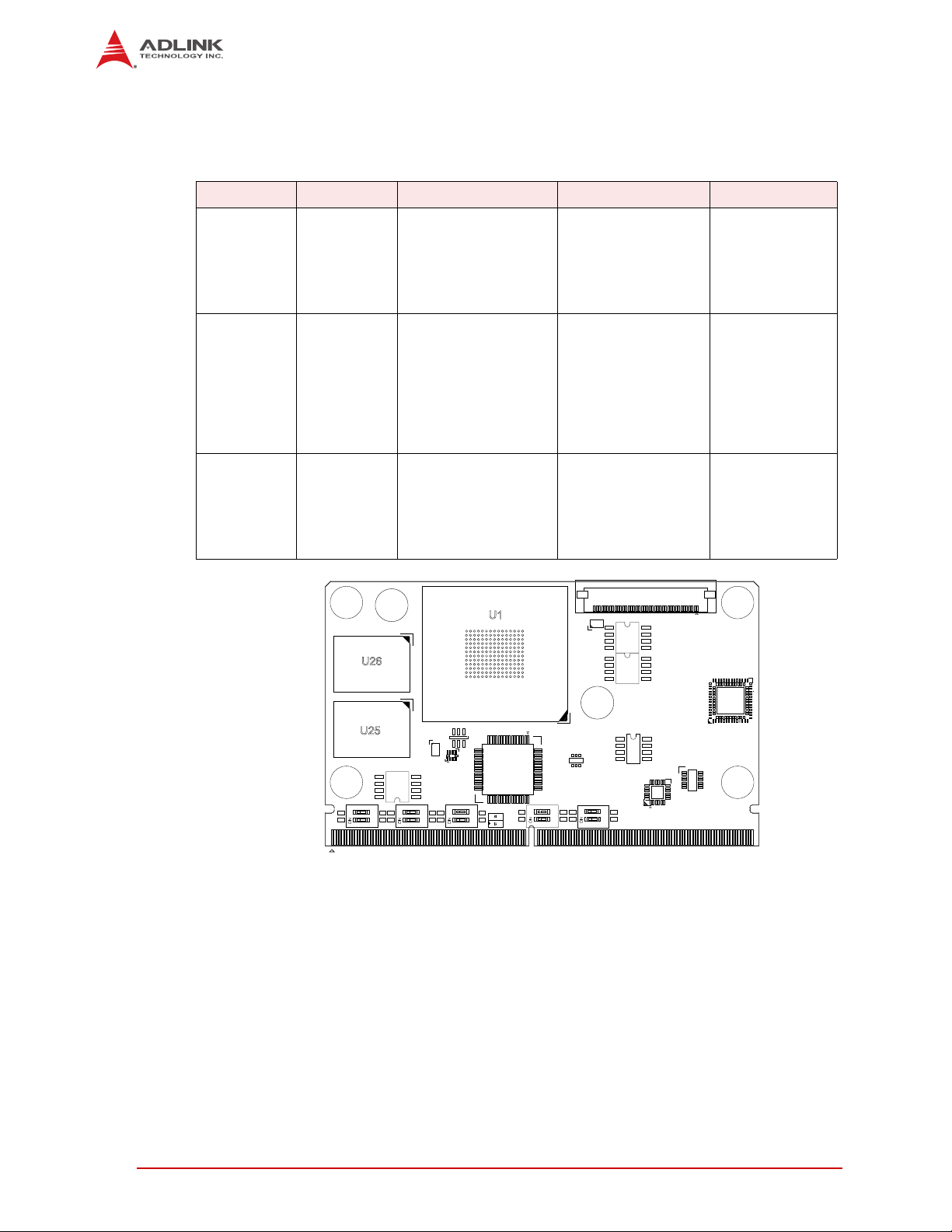

1.3 Connectors, Switches, and LEDs

Table 1-2 describes the connectors, switches, and LEDs shown in Figure 1-4.

Table 1-2: Module Connector Description

LEC-BTS

Reference

GF1 – SMARC P-S Top/

Board

Access

Bottom

Description

314-pin, MXM edge connector for Memory, Video, and I/O

functions.

CN1 Top 40-pin, DB40 connector for debug card

SW1 Top 4-pin dip switch for selecting CSI1 camera, 4L, Data1

configuration [default=off]

SW2 Top 4-pin dip switch for selecting CSI1 camera, 4L, Data2

configuration [default=on]

SW3 Top 4-pin dip switch for selecting CSI1 camera, 4L, Data3

configuration [default=on]

SW1, SW2, SW3 Configurations:

• Camera with 1 MIPI-CSI lane = SW1-SW3 switches all set to ON

• Camera with 2 MIPI-CSI lanes = SW1 (both OFF); SW2 (both ON); SW3 (both ON)

• Camera with 3 MIPI-CSI lanes = SW1 (both OFF); SW2 (both OFF); SW3 (both ON)

• Camera with 4 MIPI-CSI lanes = SW1-SW3 switches all set to OFF

Overview 3

Page 8

Table 1-2: Module Connector Description (Continued)

ON

1 2

(1 2)

LEC-BT_SW4_b

(4 3)

Switch Default Setting

ON

1 2

(1 2)

LEC-BT_SW5_b

(4 3)

Switch Default Setting

P156

P74

LEC_BTS_Top_Comp_a

SW1

SW2

SW3

SW5

CN1

LED1

LED2

SW4

Key:

CN1 - DB40 Bebug

GF1 - SMARC

LED1 - System Status

LED2 - Power ON

SW1 - CSI 1 Camera

SW2 - CSI 2 Camera

SW3 - CSI 3 Camera

SW4 - BIOS Defaults

SW5 - BIOS1-2 Select

GF1A

GF1B

SW4 Top 4-pin dip switch for loading BIOS setup defaults at Boot

Up:

1 = 18bit [default]

4 = 24bit

2 = off [default]

3 = on and selecting 18/24 bit LVDS modes

SW5 Top 4-pin dip switch for BIOS_SELECT:

1 = BIOS 2 [blue LED blinks fast]

4 = BIOS 1 and WDT Disable [default]

2 = BMC switches to BIOS 2 when BIOS 1 not detected

[default]

3 = Disables BIOS Detection Watchdog

LED1 Top Blue LED indicating system status activities for HW Reset,

SW Reset, Power Up, Power Down, Reset Button, and

Power Button

LED2 Top Green LED for Power On

LED3 Top Red LED for Watchdog Activity

Figure 1-4: Connector Locations (Top Side)

4 Overview

Page 9

1.4 Specifications

LEC_BTS_mech_dmn_a

1.4.1 Physical Specifications

Table 1-3 lists the physical dimensions of the module.

Table 1-3: Weight and Footprint Dimensions

Item Dimension

Weight 0.02 kg (0.05 lb)

Height (overall) 2.50 mm (0.098 inches)

Board thickness 1.27 mm (0.05 inches)

Width 50.00 mm (1.97 inches)

Length 82.00 mm (3.23 inches)

1.4.2 Mechanical Specifications

Overall height is measured from the upper board

surface to the top of the highest permanent

component (CN1 connector) on the upper board

surface. This measurement does not include the

cooling solution, which can vary. The cooling

solution will probably increase this dimension.

LEC-BTS

Figure 1-5: Mechanical Dimensions (Top Side)

NOTE: All dimensions are given in millimeters.

Overview 5

Page 10

1.4.3 Power Specifications

Table 1-4 provides the power requirements for this module.

Table 1-4: Power Supply Requirements

Parameter

Input Type Regulated DC voltage Regulated DC voltage Regulated DC voltage

In-rush

Voltage & Current

Typical Idle

Voltage & Current

BIT*

Voltage & Current

E3815 (5W)

Characteristics

Not yet measured Not yet measured Not yet measured

Not yet measured Not yet measured Not yet measured

Not yet measured Not yet measured Not yet measured

E3826 (7W)

Characteristics

E3845 (10W)

Characteristics

Operating configurations:

In-rush operating configuration - To be determined

Idle operating configuration - To be determined

*BIT = Burn-In-Test operating configuration - To be determined

1.4.4 Environmental Specifications

Table 1-5 provides the most efficient operating and storage condition ranges required for this

module.

Table 1-5: Environmental Requirements

Parameter Conditions

Temperature

Standard 0° to +60° C (+32° to +140° F)

Extended –40° to +85° C (–40° to +185° F)

Storage –55° to +85° C (–67° to +185° F)

Humidity

Operating 5% to 90% relative humidity, non-condensing

Non-operating 5% to 95% relative humidity, non-condensing

1.4.5 Thermal/Cooling Requirements

The LEC-BTS is designed to operate at its maximum CPU speed and requires a thermal solution. ADLINK offers one cooling option described in Table 1-6.

CAUTION: The overall system design must keep the ICs within their operating temperature

specifications.

Table 1-6: ADLINK Cooling Option

Cooling Option Description

Heat Spreader Provides a simple thermal platform on which to build a cooling solution.

CAUTION: The optional heat spreader plate requires another form of cooling, such as a fan.

A heat spreader plate is not a complete thermal solution for the LEC-BTS.

6 Overview

Page 11

LEC-BTS

2 Hardware

2.1 CPU

The LEC-BTS product family offers three versions of the Intel Atom E3800 Series CPU: the

E3815 (Single Core), the E3826 (Dual Core), and the E3845 (Quad Core). E3800 CPUs feature

the Intel 64 Architecture and are manufactured based on Intel’s 22-nanometer technology. Refer

to the CPU data sheet at:

http://www.intel.com/content/dam/www/public/us/en/documents/datasheets/atom-e3800-family-datasheet.pdf

2.2 Memory

The LEC-BTS employs one channel of 64-bit DDR3L on-board memory. Four SDRAM memory

chips provide up to 16Gb of low voltage non-ECC, unbuffered system memory. Refer to the

SDRAM data sheet at:

http://www.micron.com/products/dram/ddr3-sdram#fullPart&236=4Gb

3 Interfaces

This section provides descriptions of the interfaces and signals within the SMARC P-S (Primary-Secondary) connector.

http://www.sget.org/standards/smarc.html

P-S (Primary-Secondary) connector provides the following interfaces:

LVDS

HDMI

Camera CSIO

Audio

PCIe

Gb Ethernet

USB 2.0

USB 3.0

SATA

I2C

SPI

Serial

I2S

SD/SDIO

eMMC

GPIO

Debug

Refer to the SMARC specification at:

for definitions of the SMARC interfaces. The SMARC

NOTE: ADLINK Technology Inc. only supports the features/options tested and listed in this

manual. The main chips used in the LEC-BTS may provide more features or options than are

listed for the LEC-BTS, but some of these features or options are not supported on the

module and will not function as specified in the chip documentation.

Hardware 7

Page 12

3.1 18/24 Bit LVDS LCD

The LVDS interface is connected to the DDI0 interface of the SoC, while the translation is made

by a DisplayPort™-to-LVDS converter. (Refer to the Realtek RTD2136R-CG, DisplayPort-to-LVDS converter datasheet.)

NOTE: Backlight Enable, Display Enable, and PWMOUT are controlled from the BIOS setup.

3.2 HDMI (High-Definition Multimedia Interface)

The default setup defines the DDI1 port as HDMI and provides the following signals:

1 Clock pair

3 Data pairs

Service signals

The HDMI interface is compliant with the HDMI 1.4 specification.

3.3 Camera CSI

The LEC-BTS brings out signals for two MIPI-CSI 2.0 (serial) camera interfaces, the first with

clock and one data lane, the second with clock and up to four data lanes supporting up to 800

Mbit/s of actual pixels.

3.4 Audio (HDA)

The SoC provides an HDA controller, which communicates with internal or external CODECs

over the Intel HDA serial link. HDA signals are brought out through the I2S2 pins on the SMARC

connector and are multiplexed with LPE_I2S audio signals. When HDA is active, LPE audio is

disabled.

3.5 PCI Express (PCIe)

The CPU features four PCIe x1 ports, and the LEC-BTS module uses three of them for the PCIe

interface and one of them for the Gigabit Ethernet interface. The PCIe interface supports the

PCIe Base Specification 2.0 with a maximum signal rate of 5 GT/s and can be configured to support PCIe edge cards or Express Cards.

3.6 Gigabit Ethernet

The on-board Intel I210IT Ethernet controller uses PCIe x1 (v2.1) bus signals from the CPU to

enable 10T/100TX/1000T operation through integrated MAC, PHY, and SGMII/SerDes interfaces.

3.7 USB Ports

The USB interface originates from two host controllers on the CPU that provide three USB 2.0

ports and one USB 3.0 port. The two USB 2.0 ports use the USB 0-2 pins on the SMARC connector, and the USB 3.0 port uses the AFB_DIFF pins on the SMARC connector.

3.8 SATA

The SATA interface provides one port through the SATA0 pins on the SMARC connector. The

interface supports 1.5Gb/s and 3.0Gb/s.

3.9 I2C Bus

The LEC-BTS provides four interfaces through the I2C bus for General Purpose, Power Management, Camera, and LCD video I2C signals with operating speeds up to 400kHz. All I2C

interfaces have 1.8V pull ups with 2.2k resistors.

8 Interfaces

Page 13

LEC-BTS

3.10 SPI

The CPU implements an SPI controller, which supports two SPI Flash devices on the module for

BIOS storage.

3.11 Serial (UART)

The LEC-BTS provides three serial interfaces: Two ports are high-speed, 4-wire ports (with TX/

RX and RTS#/CTS#), and one port is 2-wire (with TX/RX only.)

3.12 I2S

The SMARC connector provides three pins for an LPE_I2S audio interface. The LPE_I2S interface is brought out through the I2S0 pins on the SMARC connector.

3.13 SD/SDIO Interface

Four parallel data lines comprise the SD/SDIO interface, supporting SD Card sockets.

3.14 eMMC Interface

The LEC-BTS provides one 8-bit eMMC interface port, brought out from the CPU through the

SDMMC pins on the SMARC connector.

3.15 GPIO

The LEC-BTS provides 12 GPIO signals from the CMOS device on the module. The GPIO signals can be utilized for General Purpose IOs as well as camera, HDA, PWM, TACH, and CAN

interfaces.

Table 3-1: GPIO Default Settings

SMARC Connector Pin Default Function

GPIO0 CAM0_PWR#

GPIO1 CAM1_PWR#

GPIO2 CAM0_RST#

GPIO3 CAM1_RST#

GPIO4 HDA_RST#

GPIO5 GPIO

GPIO6 GPIO

GPIO7 GPIO

GPIO8 GPIO

GPIO9 GPIO

GPIO10 GPIO

GPIO11 GPIO

3.16 LPC Debug

A 40-pin, front flip, DB40 connector allows access to debug and update the BIOS, BMC, and OS

code on the module. (Refer to “Debug (DB40)” on page 13.)

Interfaces 9

Page 14

3.17 SMARC Interface Signals

Table 3-2 provides the pin signals for the SMARC P-S connector. Refer to the SMARC specification at http://www.sget.org/standards/smarc.html

Table 3-2: SMARC P-S Connector (GF1) Signal Descriptions

Pin # Primary (Top Side) Pin # Secondary (Bottom Side)

P1 Not connected S2 Not connected

P2 GND S3 GND

P3 CSI1_CK+ S4 Not connected

P4 CSI1_CK- S5 I2C_CAM_CK

P5 Not connected S6 Not connected

P6 Not connected S7 I2C_CAM_DAT

P7 CSI1_D0+ S8 CSI0_CK+

P8 CSI1_D0- S9 CSI0_CKP9 GND S10 GND

P10 CSI1_D1+ S11 CSI0_D0+

P11 CSI1_D1- S12 CSI0_D0P12 GND S13 GND

P13 CSI1_D2+ S14 Not connected

P14 CSI1_D2- S15 Not connected

P15 GND S16 GND

P16 CSI1_D3+ S17 Not connected

P17 CSI1_D3 S18 Not connected

P18 GND S19 Not connected

P19 GBE_MDI3- S20 Not connected

P20 GBE_MDI3+ S21 Not connected

P21 GBE_LINK100# (Ethernet Speed

LED)

P22 GBE_LINK1000# (Ethernet Speed

LED)

P23 GBE_MDI2- S24 Not connected

P24 GBE_MDI2+ S25 GND

P25 GBE_LINK_ACT# (LAN Link LED) S26 SDMMC_D0

P26 GBE_MDI1- S27 SDMMC_D1

P27 GBE_MDI1+ S28 SDMMC_D2

P28 GBE_CTREF S29 SDMMC_D3

P29 GBE0_MDI0- S30 SDMMC_D4

P30 GBE0_MDI0+ S31 SDMMC_D5

P31 Not connected S32 SDMMC_D6

P32

P33 SDIO_WP S34 GND

P34 SDIO_CMD S35 SDMMC_CK

P35 SDIO_CD# S36 SDMMC_CMD

P36 SDIO_CK S37 SDMMC_RST#

P37 SDIO_PWR_EN S38 Not connected

P38 GND S39 I2S0_LRCK

P39 SDIO_D0 S40 I2S0_SDOUT

P40 SDIO_D1 S41 I2S0_SDIN

P41 SDIO_D2 S42 I2S0_CK

P42 SDIO_D3 S43 Not connected

GND

for definitions of the SMARC signals.

S1 Not connected

S22 Not connected

S23 Not connected

S33 SDMMC_D7

10 Interfaces

Page 15

Table 3-2: SMARC P-S Connector (GF1) Signal Descriptions (Continued)

P43 Not connected S44 Not connected

P44 Not connected S45 Not connected

P45 Not connected S46 Not connected

P46 Not connected S47 GND

P47 GND S48 I2C_GP_CK

P48 SATA0_TX+ S49 I2C_GP_DAT

P49 SATA0_TX- S50 I2S2_LRCK

P50 GND S51 I2S2_SDOUT

P51 SATA_RX+ S52 I2S2_SDIN

P52 SATA_RX- S53 I2S2_CK

P53 GND S54 SATA_ACT#

P54 SPI1_CS0# S55 Not connected

P55 Not connected S56 Not connected

P56 SPI1_CK S57 Not connected

P57 SPI1_DIN S58 Not connected

P58 SPI1_DO S59 Not connected

P59 GND S60 Not connected

P60 USB0+ S61 GND

P61 USB0- S62 USB3_TX+

P62 USB0_EN_OC# S63 USB3_TXP63 Not connected S64 GND

P64 Not connected S65 USB3_RX+

P65 USB1+ S66 USB3_RXP66

P67 USB1_EN_OC# S68 Not connected

P68 GND S69 Not connected

P69 USB2+ S70 GND

P70 USB2- S71 Not connected

P71 USB2_EN_OC# S72 Not connected

P72 PCIE_C_PRSNT# S73 GND

P73 PCIE_B_PRSNT# S74 Not connected

P74 PCIE_A_PRSNT# S75 Not connected

P75 PCIE_A_RST# S76 PCIE_B_RST#

P76 PCIE_C_CKREQ# S77 PCIE_C_RST#

P77 PCIE_B_CKREQ# S78 PCIE_C_RX+

P78 PCIE_A_CKREQ# S79 PCIE_C_RXP79 GND S80 GND

P80 PCIE_C_REFCK+ S81 PCIE_C_TX+

P81 PCIE_C_REFCK- S82 PCIE_C_TXP82 GND S83 GND

P83 PCIE_A_REFCK+ S84 PCIE_B_REFCK+

P84 PCIE_A_REFCK- S85 PCIE_B_REFCKP85 GND S86 GND

P86 PCIE_A_RX+ S87 PCIE_B_RX+

P87 PCIE_A_RX- S88 PCIE_B_RXP88 GND S89 GND

P89 PCIE_A_TX+ S90 PCIE_B_TX+

P90 PCIE_A_TX- P91 PCIE_B_TXP91 GND S92 GND

P92 HDMI_D2+ S93 Not connected

USB1-

Key Key

S67 GND

LEC-BTS

Interfaces 11

Page 16

Table 3-2: SMARC P-S Connector (GF1) Signal Descriptions (Continued)

P93 HDMI_D2- S94 Not connected

P94 GND S95 Not connected

P95 HDMI_D1+ S96 Not connected

P96 HDMI_D1- S97 Not connected

P97 GND S98 Not connected

P98 HDMI_D0+ S99 Not connected

P99 HDMI_D0- S100 Not connected

P100 GND S101 GND

P101 HDMI_CK+ S102 Not connected

P102 HDMI_CK- S103 Not connected

P103 GND S104 Not connected

P104 HDMI_HPD S105 Not connected

P105 HDMI_CTRL_CK S106 Not connected

P106 HDMI_CTRL_DAT S107 Not connected

P107 HDMI_CEC S108 Not connected

P108 GPIO0 / CAM0_PWR# [default] S109 Not connected

P109 GPIO1 / CAM1_PWR# [default] S110 GND

P110 GPIO2 / CAM0_RST# [default] S111 Not connected

P111 GPIO3 / CAM1_RST# [default] S112 Not connected

P112 GPIO4 / HDA_RST# [default] S113 Not connected

P113 GPIO5 [default] / _PWM_OUT

(PU, 47k, P1V8_S)

P114 GPIO6 [default] / TACHIN

(PU, 47k, P1V8_S)

P115 GPIO7 [default]

(PU, 47k, P1V8_S)

P116 GPIO8 [default] / CAN0_ERR#

(PU, 47k, P1V8_S)

P117 GPIO9 [default] / CAN1_ERR#

(PU, 47k, P1V8_S)

P118 GPIO10 [default]

(PU, 47k, P1V8_S)

P119 GPIO11 [default]

(PU, 47k, P1V8_S)

P120 GND P121 Not connected

P121 I2C_PM_CK S122 Not connected

P122 I2C_PM_DAT S123 Not connected

P123 BOOT_SEL0# S124 GND

P124 BOOT_SEL1# S125 LVDS0+

P125 BOOT_SEL2# S126 LVDS0P126 RESET_OUT# S127 LCD_BKLT_EN

P127 RESET_IN# S128 LVDS1+

P128 POWER_BTN# S129 LVDS1P129 SER0_TX S130 GND

P130 SER0_RX S131 LVDS2+

P131 SER0_RTS# S132 LVDS2P132 SER0_CTS# S133 LCD_VDD_EN

P133 GND S134 LVDS_CK+

P134 SER1_TX S135 LVDS_CKP135 SER1_RX S136 GND

P136 SER2_TX S137 LVDS3+

P137 SER2_RX S138 LVDS3-

S114 Not connected

S115 Not connected

S116 Not connected

S117 Not connected

S118 Not connected

S119 GND

S120 Not connected

12 Interfaces

Page 17

Table 3-2: SMARC P-S Connector (GF1) Signal Descriptions (Continued)

P138 SER2_RTS# S139 I2C_LCD_CK

P139 SER2_CTS# S140 I2C_LCD_DAT

P140 Not connected S141 LCD_BKLT_PWM

P141 Not connected S142 Not connected

P142 GND S143 GND

P143 Not connected S144 RSVD / EDP_HPD

P144 Not connected S145 WDT_TIME_OUT#

P145 Not connected S146 PCIE_WAKE#

P146 Not connected S147 VDD_RTC

P147 VDD_IN S148 LID#

P148 VDD_IN S149 SLEEP#

P149 VDD_IN S150 VIN_PWR_BAD#

P150 VDD_IN S151 CHARGING#

P151 VDD_IN S152 CHARGER_PRSNT#

P152 VDD_IN S153 CHARGER_STBY#

P153 VDD_IN S154 CARRIER_PWR_ON

P154 VDD_IN S155 FORCE_RECOV#

P155 VDD_IN S156 BATLOW#

P156 VDD_IN S157 TEST#

S158 GND

LEC-BTS

3.18 Debug (DB40)

Table 3-3 lists the pin signals of the CN1 connector, which provides 40 pins, 1 row, consecutive

sequence with 0.02" (0.50mm) pitch.

Table 3-3: Debug Interface Signals (CN1)

Pin # Signal

1 RESVD

2SMC_STATUS

3BIOS_MODE

4 SEL_BIOS

5POSTWDT_DIS#

6 SUS_S5#

7 SUS_S4#

8 SUS_S3#

9 CB_PWROK

10 CB_RESET#

11 SYS_RESET#

12 PWRBTN#

13 SMC_OCD0B

14 SMC_OCD0A

15 SMC_CLK

16 SMC_DATA

17 SMC_RESET_IN#

18 SMC_FLMD0

19 SMC_RXD6

20 SMC_TXD6

21

22 3V3_DUAL

23 3V3_SMC1

24 LPC_AD0

GND3

Interfaces 13

Page 18

Table 3-3: Debug Interface Signals (CN1) (Continued)

25 LPC_AD1

26 LPC_AD2

27 LPC_AD3

28 LPC_FRAME#

29 CLK33_LPC

30 RST#

31 BIOS_DIS0

32

33 LPC_3V3

34 SPI_BIOS_CLK

35 SPI_BIOS_MOSI

36 SPI_BIOS_MISO

37 SPI_BIOS_CS1#

38 SPI_BIOS_CS0#

39

40 VCC_SPI_IN

GND2

GND1

NOTE: The gray table cells denote ground.

14 Interfaces

Page 19

Appendix A Technical Support

Contact us should you require any service or assistance.

ADLINK Technology, Inc.

Address: 9F, No.166 Jian Yi Road, Zhonghe District

New Taipei City 235, Taiwan

ᄅקؑխࡉ৬ԫሁ 166 ᇆ 9 ᑔ

Tel: +886-2-8226-5877

Fax: +886-2-8226-5717

Email: service@adlinktech.com

Ampro ADLINK Technology, Inc.

Address: 5215 Hellyer Avenue, #110, San Jose, CA 95138, USA

Tel: +1-408-360-0200

Toll Free: +1-800-966-5200 (USA only)

Fax: +1-408-360-0222

Email: info@adlinktech.com

ADLINK Technology (China) Co., Ltd.

Address: Ϟ⍋Ꮦ⌺ϰᮄᓴ∳催⾥ᡔು㢇䏃 300 ো(201203)

300 Fang Chun Rd., Zhangjiang Hi-Tech Park,

Pudong New Area, Shanghai, 201203 China

Tel: +86-21-5132-8988

Fax: +86-21-5132-3588

Email: market@adlinktech.com

ADLINK Technology, Inc. provides a number of methods for contacting Technical Support listed

in Table A-1 below. Requests for support through Ask an Expert are given the highest priorities,

and usually will be addressed within one working day.

ADLINK Ask an Expert – This is a comprehensive support center designed to meet all

your technical needs. This service is free and available 24 hours a day through the

ADLINK web site at http://www.adlinktech.com/AAE/

base of Frequently Asked Questions, which will help you with the common information

requested by most customers. This is a good source of information to look at first for your

technical solutions. However, you must register online if you wish to use the Ask a Question feature.

ADLINK strongly suggests that you register with the web site. By creating a profile on the

ADLINK web site, you will have a portal page called “My ADLINK”, unique to you with

access to exclusive services and account information.

Personal Assistance – You may also request personal assistance by creating an Ask an

Expert account and then going to the Ask a Question feature. Requests can be submitted 24 hours a day, 7 days a week. You will receive immediate confirmation that your

request has been entered. Once you have submitted your request, you must log in to go

to the My Question area where you can check status, update your request, and access

other features.

Download Service – This service is also free and available 24 hours a day at

http://www.adlinktech.com

. For certain downloads such as technical documents and soft-

ware, you must register online before you can log in to this service.

. This includes a searchable data-

LEC-BTS

Table A-1: Technical Support Contact Information

Method Contact Information

Ask an Expert http://www.adlinktech.com/AAE/

Web Site http://www.adlinktech.com

Standard Mail

15

Page 20

Table A-1: Technical Support Contact Information (Continued)

ADLINK Technology Beijing

Address: ࣫ҀᏖ⍋⎔Ϟഄϰ䏃 1 োⲜ߯ࡼ E ᑻ 801 ᅸ(100085)

Rm. 801, Power Creative E, No. 1,

Shang Di East Rd., Beijing, 100085 China

Tel: +86-10-5885-8666

Fax: +86-10-5885-8626

Email: market@adlinktech.com

ADLINK Technology Shenzhen

Address: ⏅ഇᏖቅ⾥ᡔು催ᮄϗ䘧᭄ᄫᡔᴃು

A1 2 ὐ C (518057)

2F, C Block, Bldg. A1, Cyber-Tech Zone, Gao Xin Ave. Sec. 7,

High-Tech Industrial Park S., Shenzhen, 518054 China

Tel: +86-755-2643-4858

Fax: +86-755-2664-6353

Email: market@adlinktech.com

LiPPERT ADLINK Technology GmbH

Address: Hans-Thoma-Strasse 11, D-68163, Mannheim, Germany

Tel: +49-621-43214-0

Fax: +49-621 43214-30

Email: emea@adlinktech.com

ADLINK Technology, Inc. (French Liaison Office)

Address: 6 allée de Londres, Immeuble Ceylan

91940 Les Ulis, France

Tel: +33 (0) 1 60 12 35 66

Fax: +33 (0) 1 60 12 35 66

Email: france@adlinktech.com

ADLINK Technology Japan Corporation

Address: ͱ101-0045 ᵅҀ䛑ҷ⬄⼲⬄䤯ފ⬎ 3-7-4

⼲⬄ 374 ɛɳ 4F

KANDA374 Bldg. 4F, 3-7-4 Kanda Kajicho,

Chiyoda-ku, Tokyo 101-0045, Japan

Tel: +81-3-4455-3722

Fax: +81-3-5209-6013

Email: japan@adlinktech.com

ADLINK Technology, Inc. (Korean Liaison Office)

Address: 137-881 昢殾柢 昢爎割 昢爎堆嵢 326, 802 (昢爎壟, 微汾瘶捒娯)

802, Mointer B/D, 326 Seocho-daero, Seocho-Gu,

Seoul 137-881, Korea

Tel: +82-2-2057-0565

Fax: +82-2-2057-0563

Email: korea@adlinktech.com

ADLINK Technology Singapore Pte. Ltd.

Address: 84 Genting Lane #07-02A, Cityneon Design Centre

Singapore 349584

Tel: +65-6844-2261

Fax: +65-6844-2263

Email: singapore@adlinktech.com

ADLINK Technology Singapore Pte. Ltd. (Indian Liaison Office)

Address: #50-56, First Floor, Spearhead Towers

Margosa Main Road (between 16th/17th Cross)

Malleswaram, Bangalore - 560 055, India

Tel: +91-80-65605817, +91-80-42246107

Fax: +91-80-23464606

Email: india@adlinktech.com

16

Page 21

Table A-1: Technical Support Contact Information (Continued)

ADLINK Technology, Inc. (Israeli Liaison Office)

Address: 27 Maskit St., Corex Building

PO Box 12777

Herzliya 4673300, Israel

Tel: +972-77-208-0230

Fax: +972-77-208-0230

Email: israel@adlinktech.com

ADLINK Technology, Inc. (UK Liaison Office)

Tel: +44 774 010 59 65

Email: UK@adlinktech.com

LEC-BTS

17

Page 22

18

Loading...

Loading...