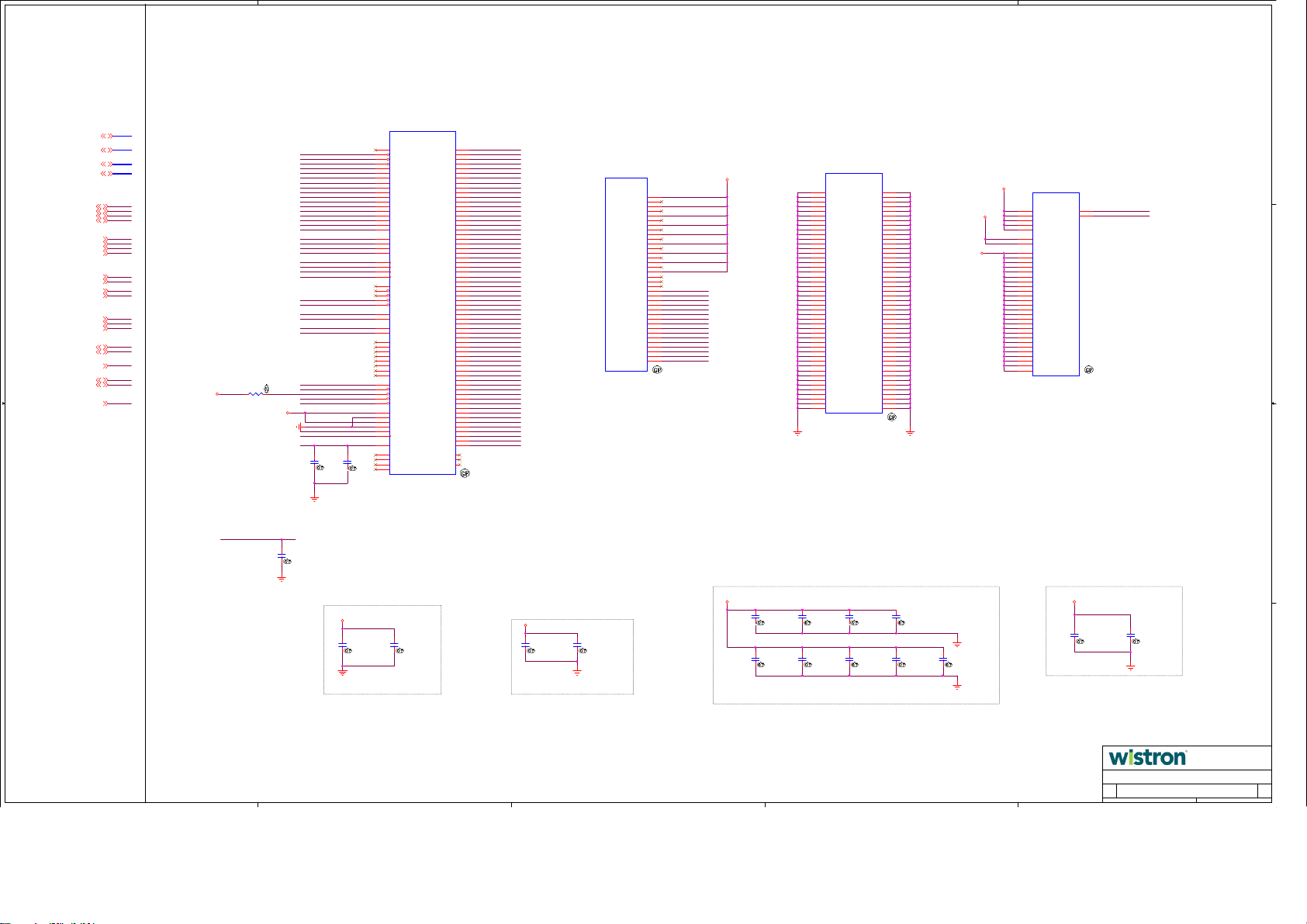

Acer Veriton M4640G Schematic

5

4

3

2

1

Commercial DT / M4.1 Chassis System

Project name: vHulk

SCH Ver: -1

D D

C C

B B

A A

PCB Number: 14065-1

PAGE

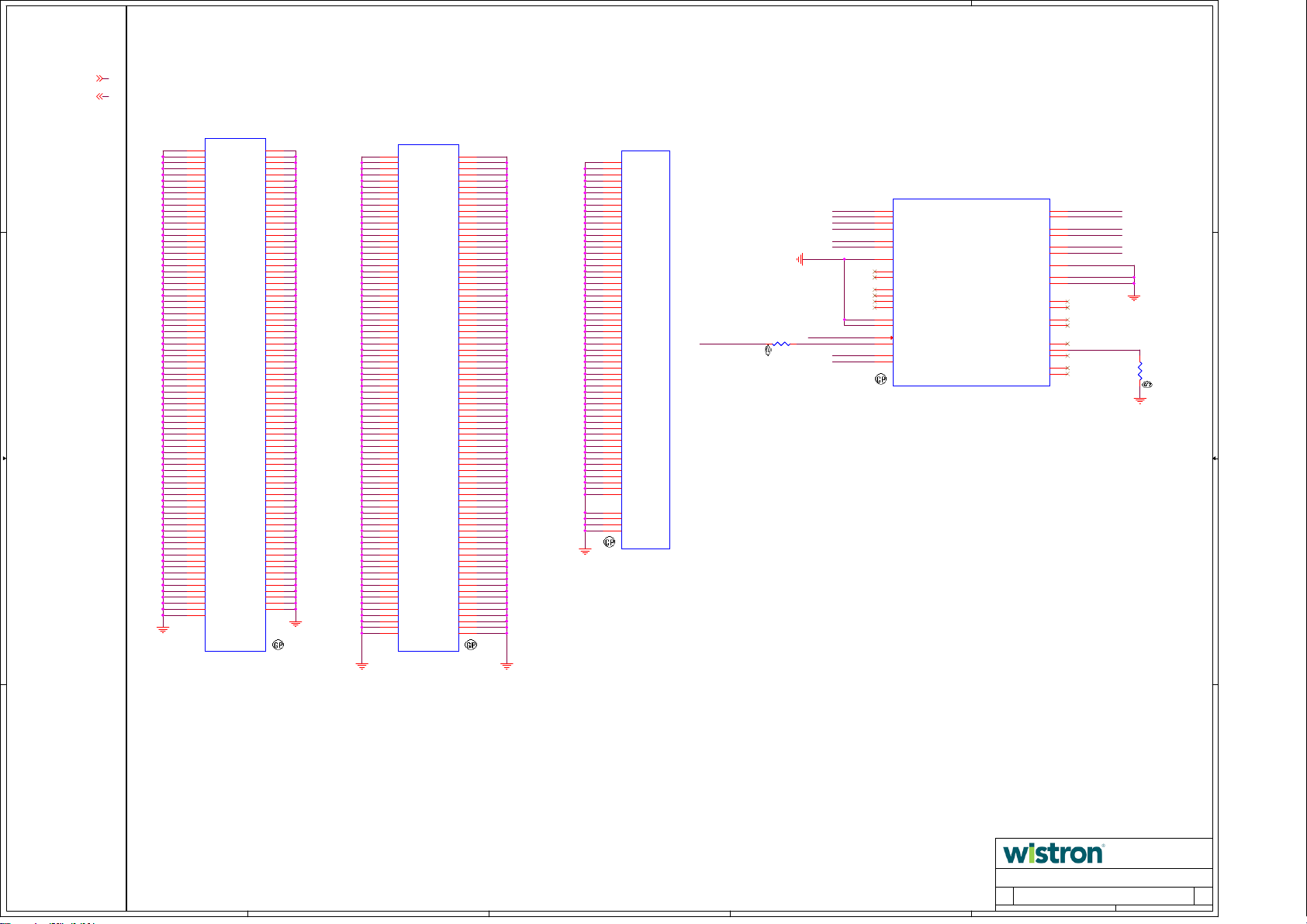

TITLE

01

COVER PAGE

02

BLOCK DIAGRAM

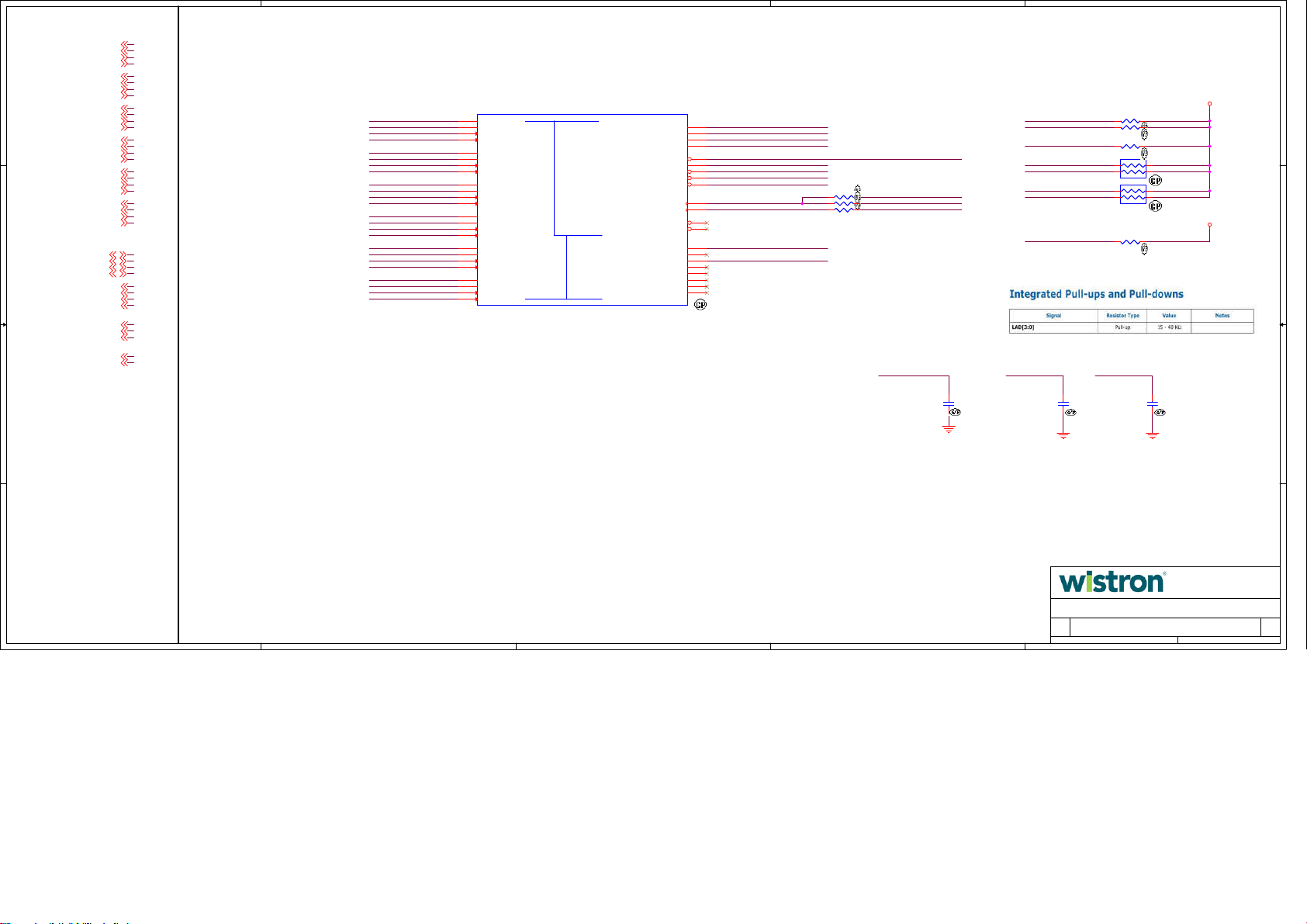

03 CPU (PCIE/DMI)

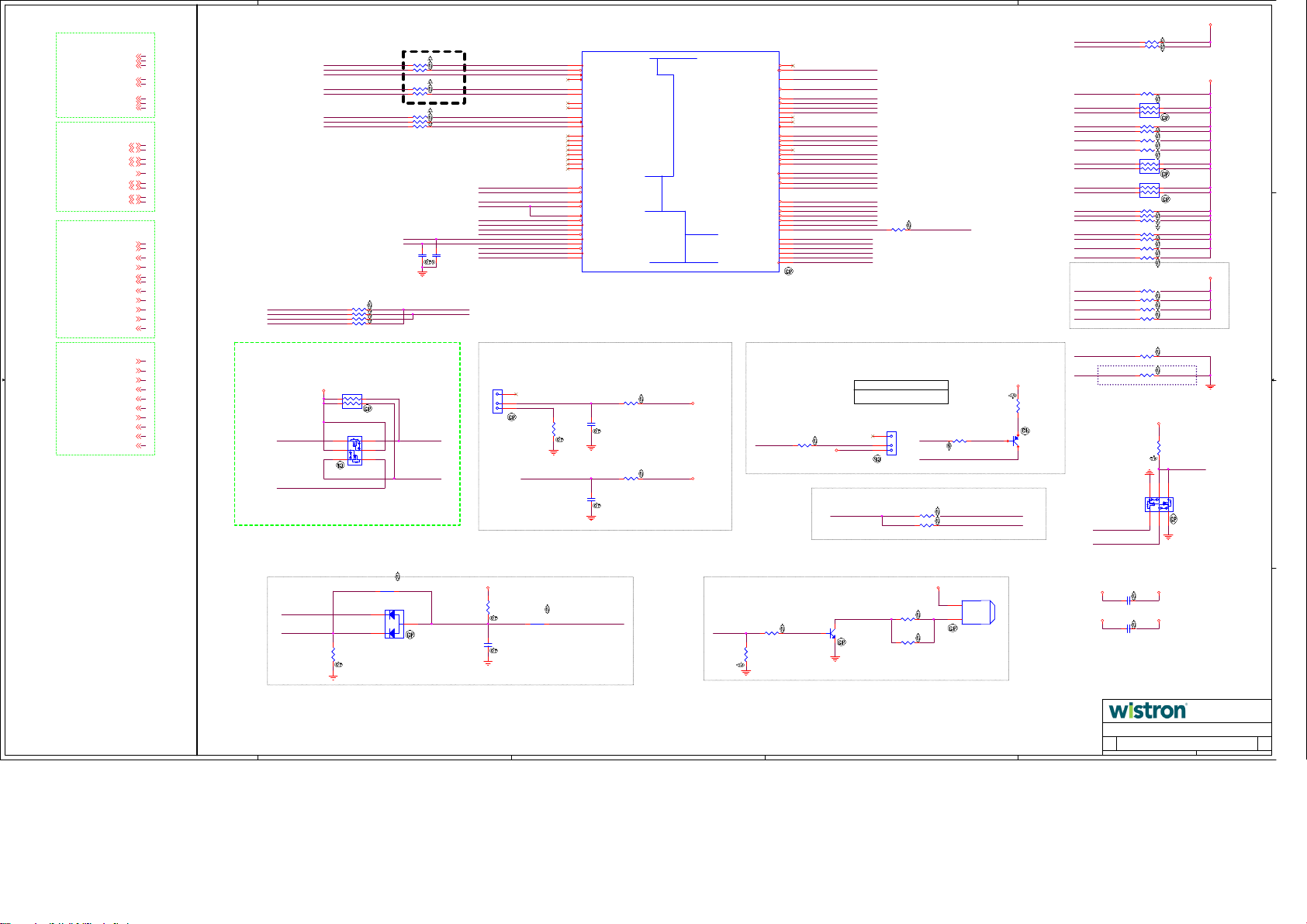

CPU (CFG/CLOCK/PM)

04

CPU (DDR_CHA)

05

06

CPU (DDR_CHB)

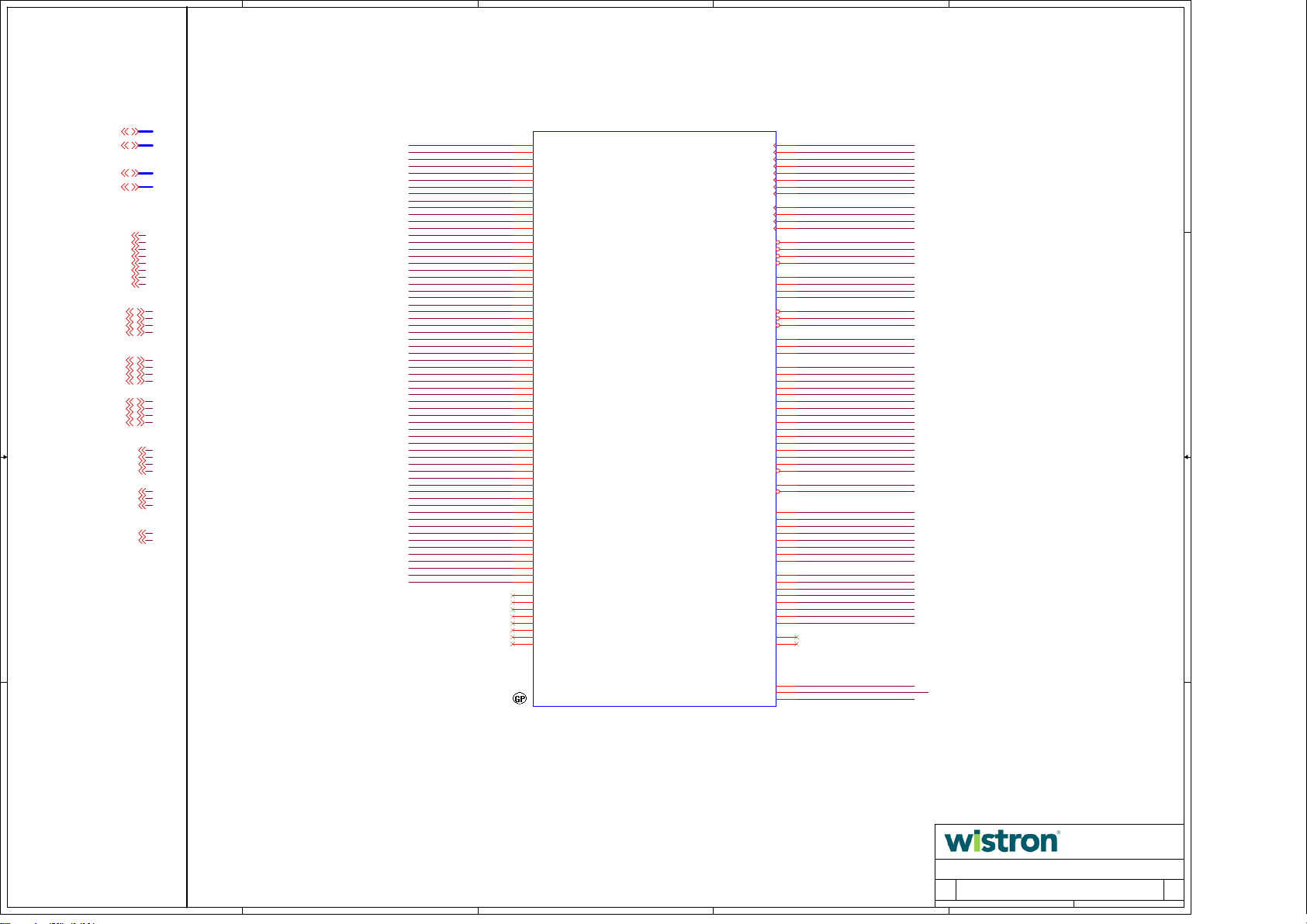

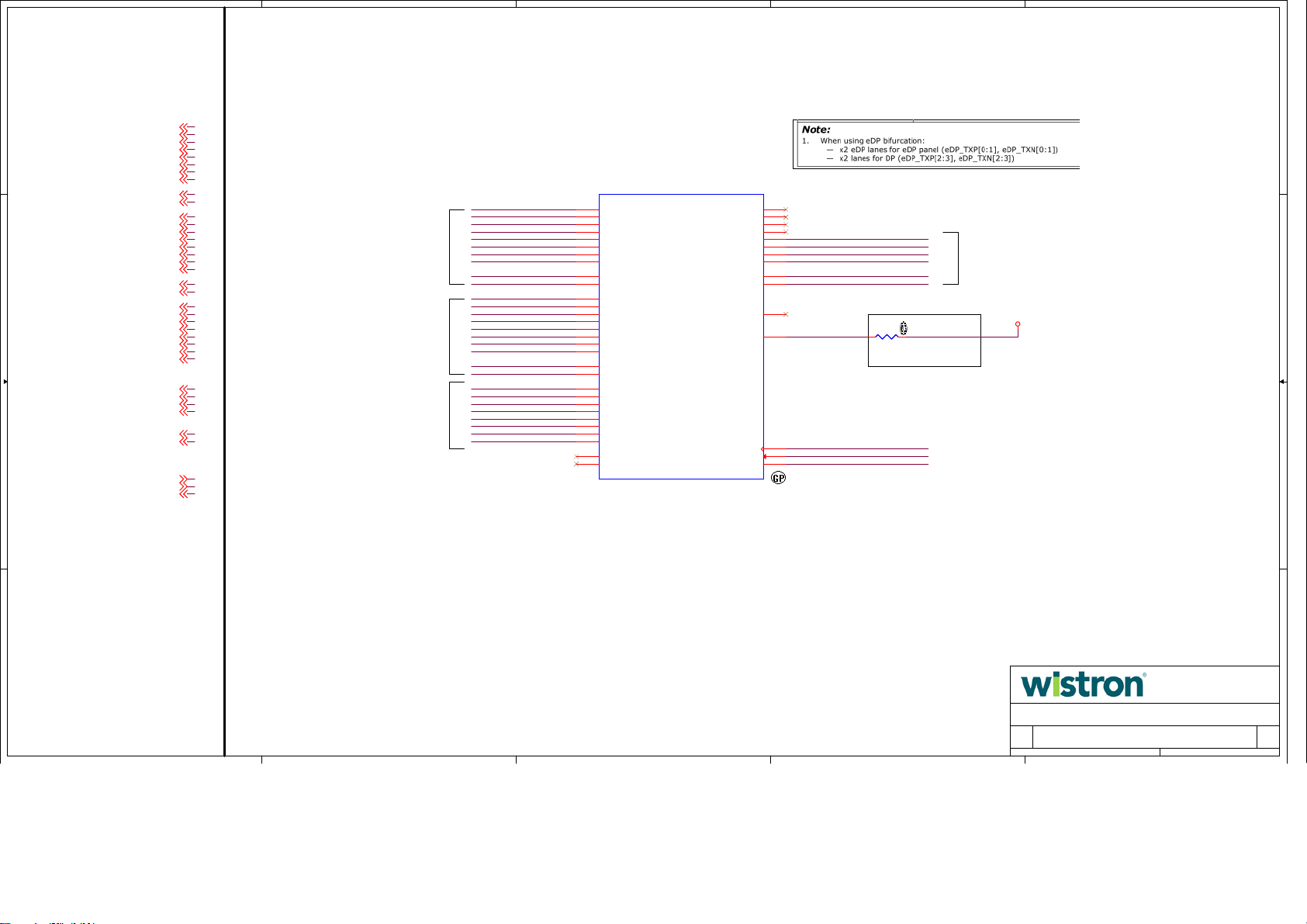

CPU (DDI/EDP)

07

08

CPU (CPU Power)

09

CPU (VSS)

10

CPU (Power CAP)

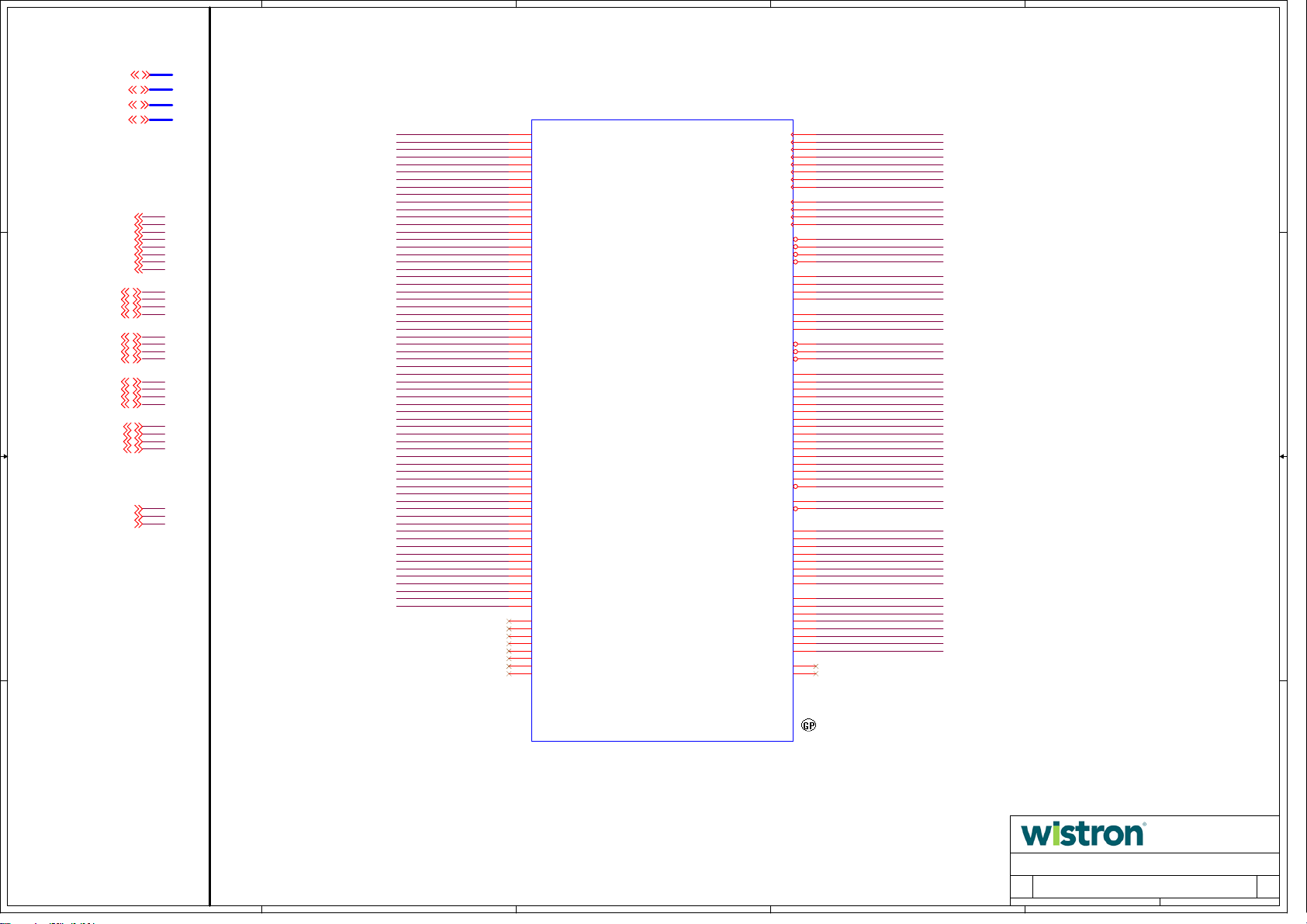

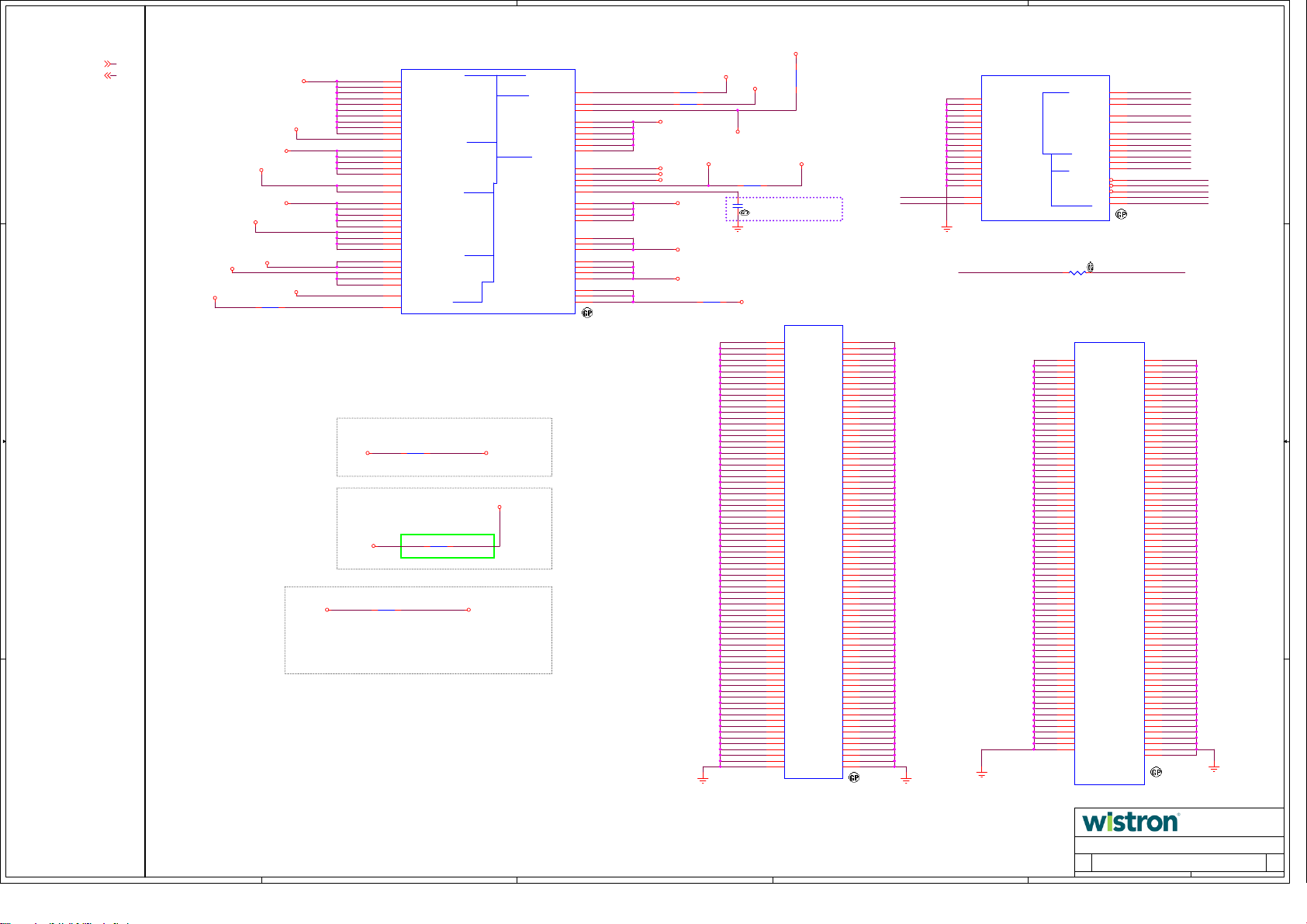

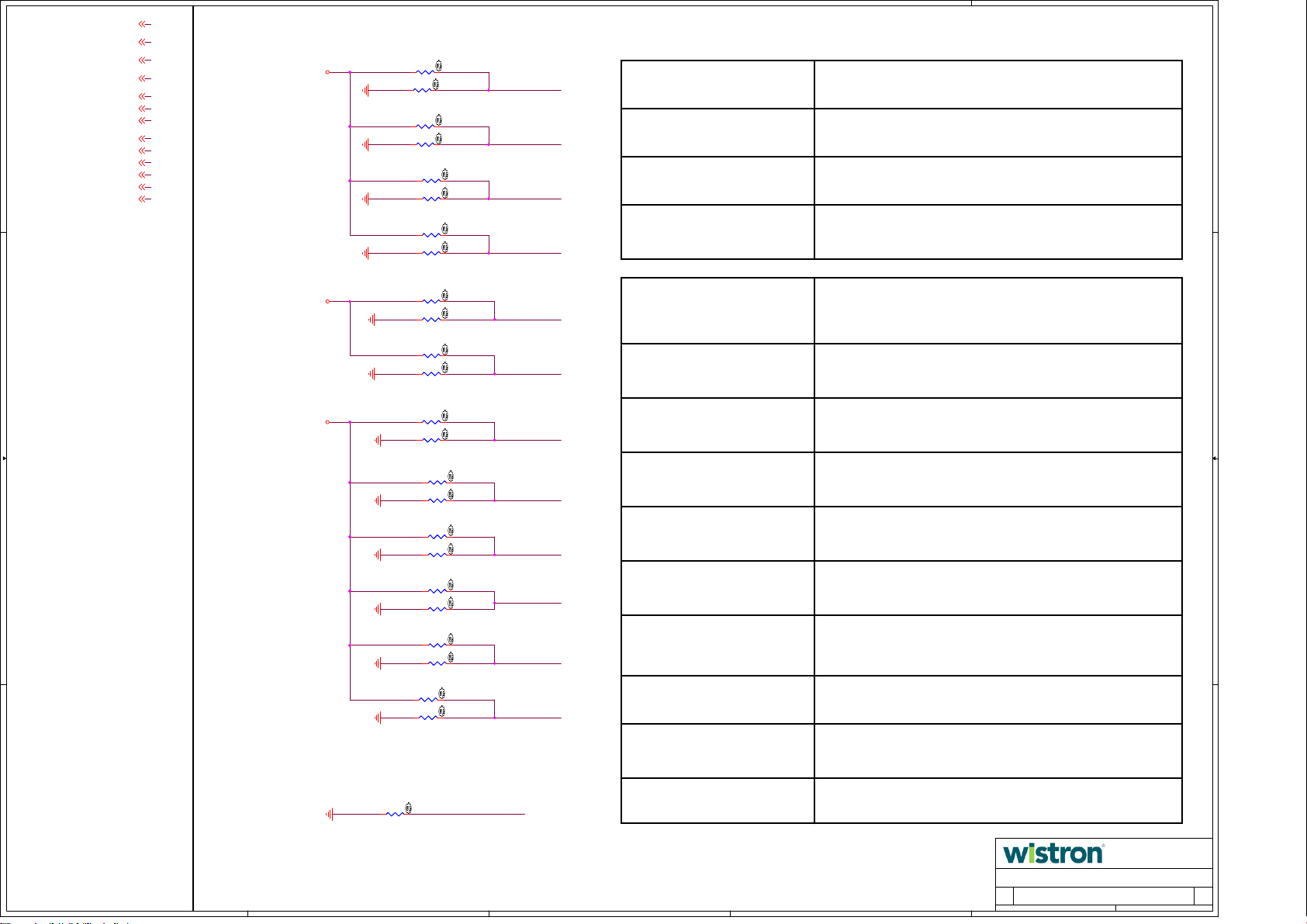

DDR DIMM_2

11

12

DDR DIMM_1

13

DDR DIMM_4

DDR DIMM_3

14

15

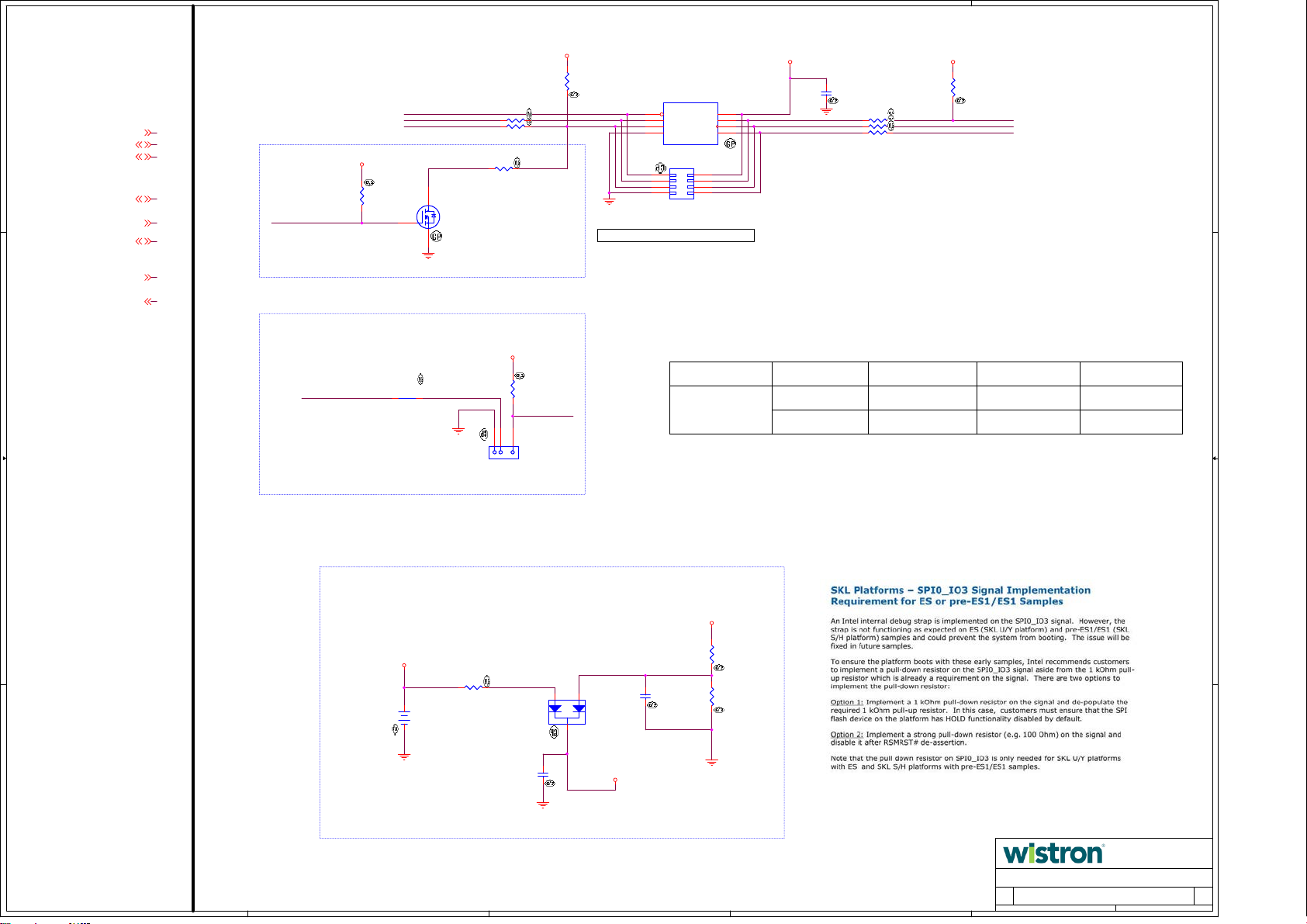

PCH (SPI/UART/I2C)

16

PCH (DMI/PCI-E/USB)DDI GP

17

PCH (PCI-E/SATA)

18

PCH (CLOCK/CL)

19

PCH (USB/ESPI)

20

PCH(GPIO/CPU/SMBUS/IHDA/JTAG)

21

PCH (POWER1)

22

PCH (POWER2)_PCH Strap

PCH Power CAP

23

SIO_ITE8733

24

25

Flash&RTC

Thermal&FAN

26

27

Audio Codec_ALC662

28

AMP_(R)

29

Audio IO_Front

Audio IO_Rear

30

LAN_RTL8111EPV

31

RJ45&Transformer

32

Card Reader_(R)

3

3

34

USB Charger_(R)

35

USB_Redrive_(R)

SB20_REAR PORT

36

U

37

USB20_FRONT HEADER

USB30_REAR PORT

38

USB30_FRONT HEADER

39

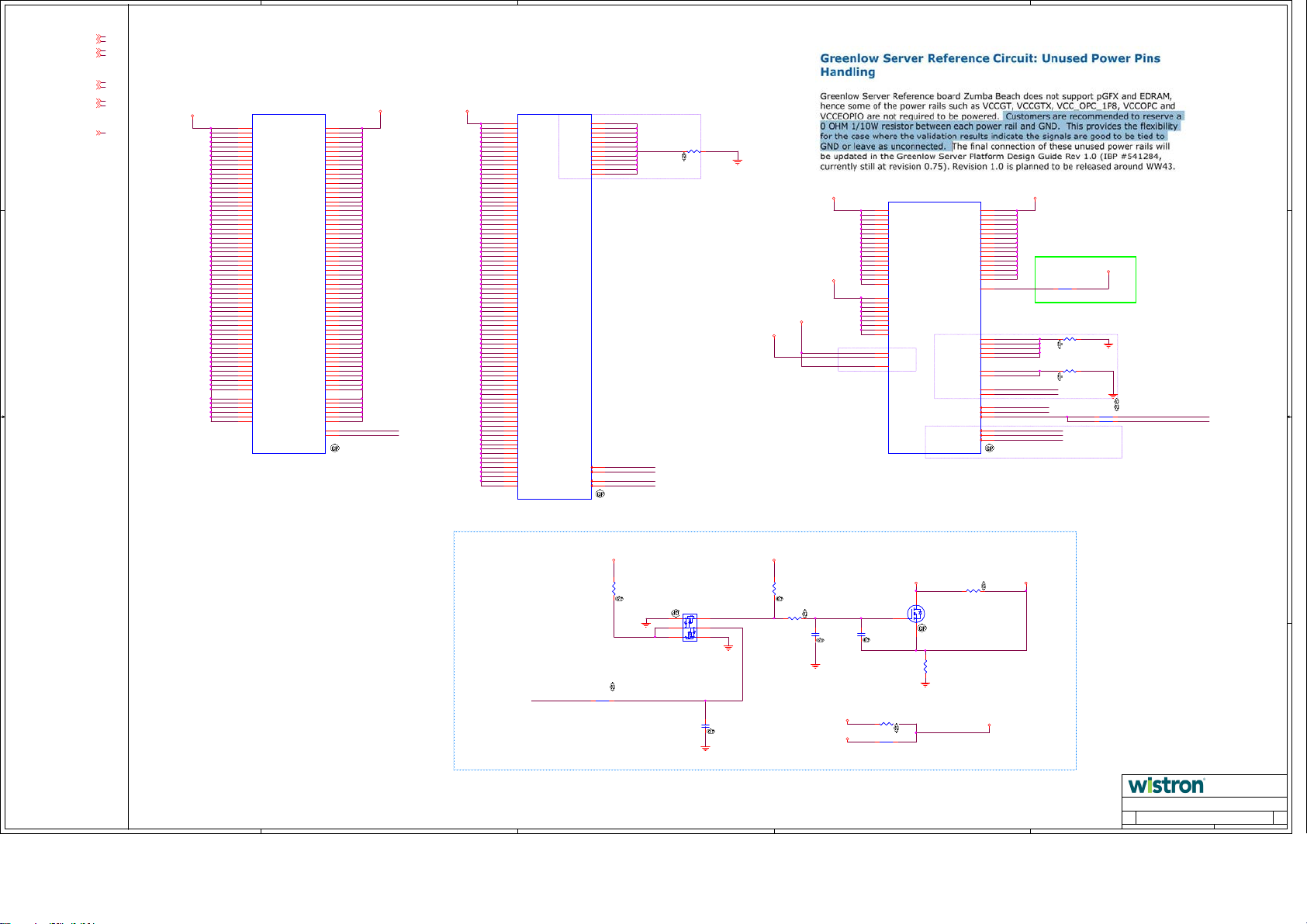

Power Plane EN Sequence

40

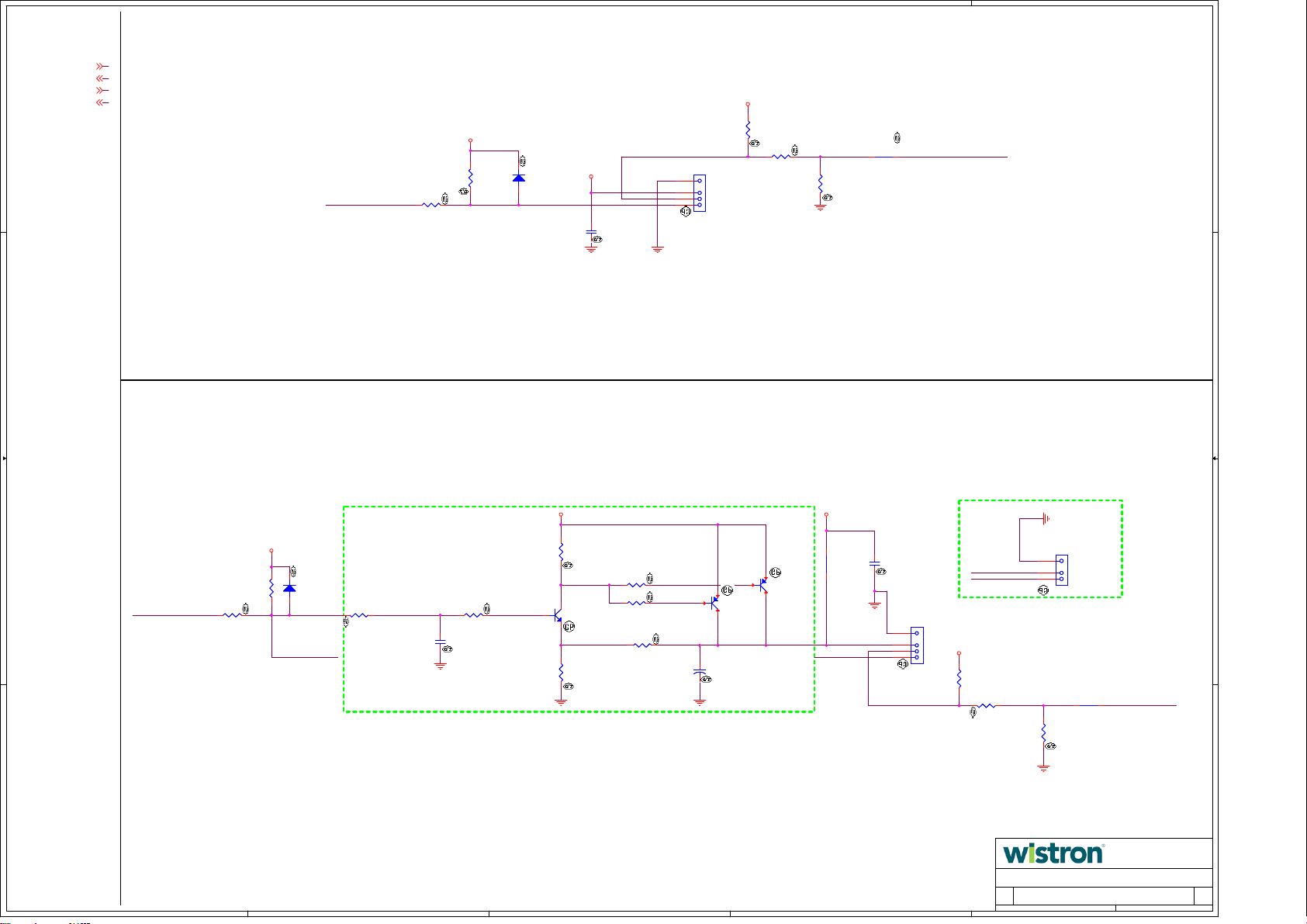

Dual Power

41

Switch power

42

43

ATX(BATT Conn)

Power Sequence(DDR4)

44

45

DCDC-3D3V&5V

VCORE & V_GT IC(NCP81203)

46

VCORE OUTPUT (NCP81151)

47

V_GT OUTPUT(NCP81151)

48

5V &3.3V(RT8243A)49

DDR_PWR (RT8207M)

50

PCH_1P0V(RT8237C) 105

51

52

VCC_SA(NCP5230M)

53

VCC_IO(RT8237C)

54 LDO_1P5V_1P8V_2P5V

5

PAGE

55

56 DP2

57

5

59

60

61

62

63

64

65

66

67

68

69

7

71

72

7

74

75

76

77

78

79

80

81

82

8

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

1

106

107

TITLE

DVI-D

DP1

DVI/CRT

8

P

CI bridge

HDD/ODD

Mini card-WLAN

Mini card-SSD_(R)

Mini card-NGFF

Front board

Others

IO Board_(R)

COM

Debug

LPT

G sensor_(R)

0

Thunderbolt_(R)

Thunderbolt_(R)

3

Thunderbolt_(R)

Thunderbolt_(R)

Thunderbolt_(R)

GPU_(R)

GPU_(R)

GPU_(R)

GPU_(R)

GPU_(R)

GPU VRAM 1&2_(R)

PU VRAM 3&4_(R)

G

PU VRAM 5&6_(R)

3

G

GPU VRAM 7&8_(R)

GPU CORE_(R)

GPU discrete power_(R)

GPU Switch_(R)

GPU Switch_(R)

GPU others_(R)

NFC_(R)

TPM

S2

P

Express Card

Smart Card

Scalar_(R)

MCU_(R)

Inter LAN

LAN Switch_(R)

XDP&ITP

Table of Content

GPIO table

POWER SEQUENCE

Power Block Diagram

04

SMBUS table

CLOCK MAP

RESET Flow CHART

Change History

4

Jomper SETTING

CMOS1

WP1

1-2 Short

1-2 Short

OBR1 1-2 Open

MECLR1 1-2 Short With Jumper to enable ME

With Jumper to Clear CMOS

With Jumper to enable WP

Without Jumper to recovery

BOM Configuration

(R_) : unmount

(E_) : SATA Express

(Q_) : Q170

(B_) : B150

(D_) : VGA

(W_) : For WST/FXC MB

(T_) : TPM on board

(S_) : For ECS MB

(H_) : TPM header

Key IC

CPU1

PCH1

U7901

U2701

U3

TPM1

U72

U54

U6506

Header

SPK1

AUDF1

FANC1

FANS1

CMOS1

OBR1

WP1

PCHDR1

LPT1

COM1

TPMH1

CSOPN1

MECLR1

Intel CPU Skylake S 65W

Intel PCH Q170/B150

ITE SIO IT8733F-DX

RealTek Audio Codec ALC662-VD

Realtek LAN RTL8111EPV-CG

NuvoTon TPM NPCT650AAAWX

INTEL LAN I219LM I219

ITE PCI Bridge IC IT8893E

Realtek converter RTD2168-CG

21.63415.204

21.62895.205

21.60626.104

21.60626.104

21.61445.103

21.60909.102

21.61445.103

021.60235.0204

021.60217.0213

21.62884.205

21.62900.210

21.62874.102

21.61445.103

3

PCB BOARD SIZE

4 Layer / 244 mm x 244 mm

Power sates

+12V

-12V

3.3V

3.0V

2.5V

1.2V

DIMM

PCH

CPU

2

12V_S0

12V_CPU_S0

-12V_S0

ATX_5VSB

+5V_AUX1

+5V_AUX2

5V

5V_USB20_RJUSB2

5V_USB30P1

5V_USB30P2

5V_USB30H1

5V_USB20P1

5V_USB20_RJUSB1

5V_USB20H2

5V_USB20H1

5V_USB30H2

5V_S0

5V_DVI

ATX_3.3VSB

3P3V_LAN

3P3V_S5

3D3V_VCCPGPPA_Sx

3D3V_1D8V_PCHSPI_Sx

3D3V_DVDDIO_AUDIO

DVDD_IO

3D3V_S0

3D3V_RTD2168

3V_VBAT1_G3

3V_VRTC_G3

3D3V_VCCPRTC

2D5V_VPP

VDDQ

DDR_VTT

1D0V_S5

1V_VCCF24_Sx

1V_VCCAMPHYPLL_Sx

1V_VCCAPLL_Sx

VCC_CORE

GFX_CORE

VCC_SA

VCC_IO

1V_VCCST_VCCPLL_S3

G3 EUP S4 S3 S0Name

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

COVER PAGE

COVER PAGE

COVER PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

Date: Sheet of

S5

O O O O

O O O

O

O

O O O O

O

O

1

O

O

O

O

OO

O

OOOO

O

OOOOOO

OO

OO

OO

OOOO

O

O

O

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

1 107Wednesday, September 23, 2015

1 107Wednesday, September 23, 2015

1 107Wednesday, September 23, 2015

-1

-1

-1

5

www.vinafix.com

4

3

2

1

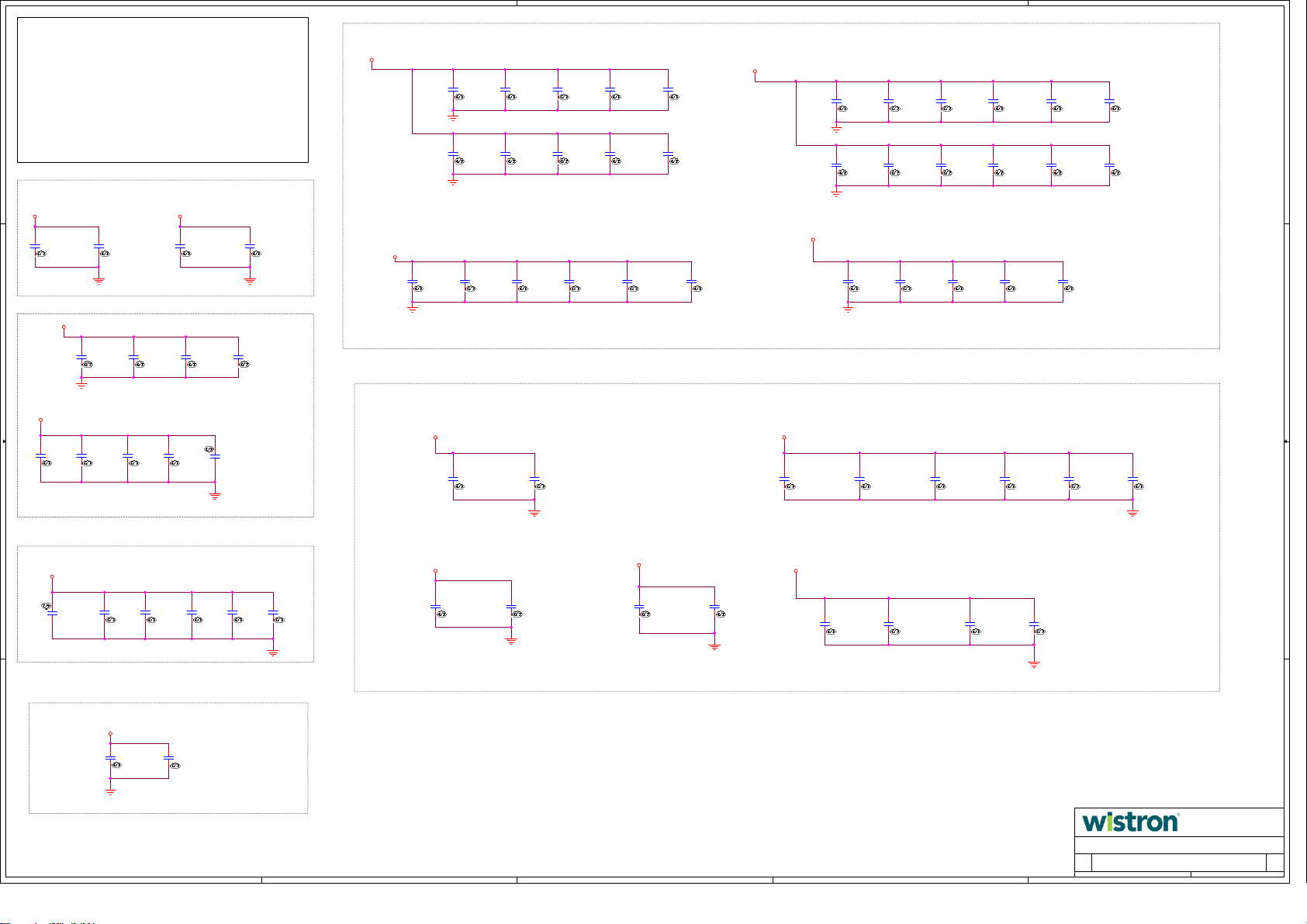

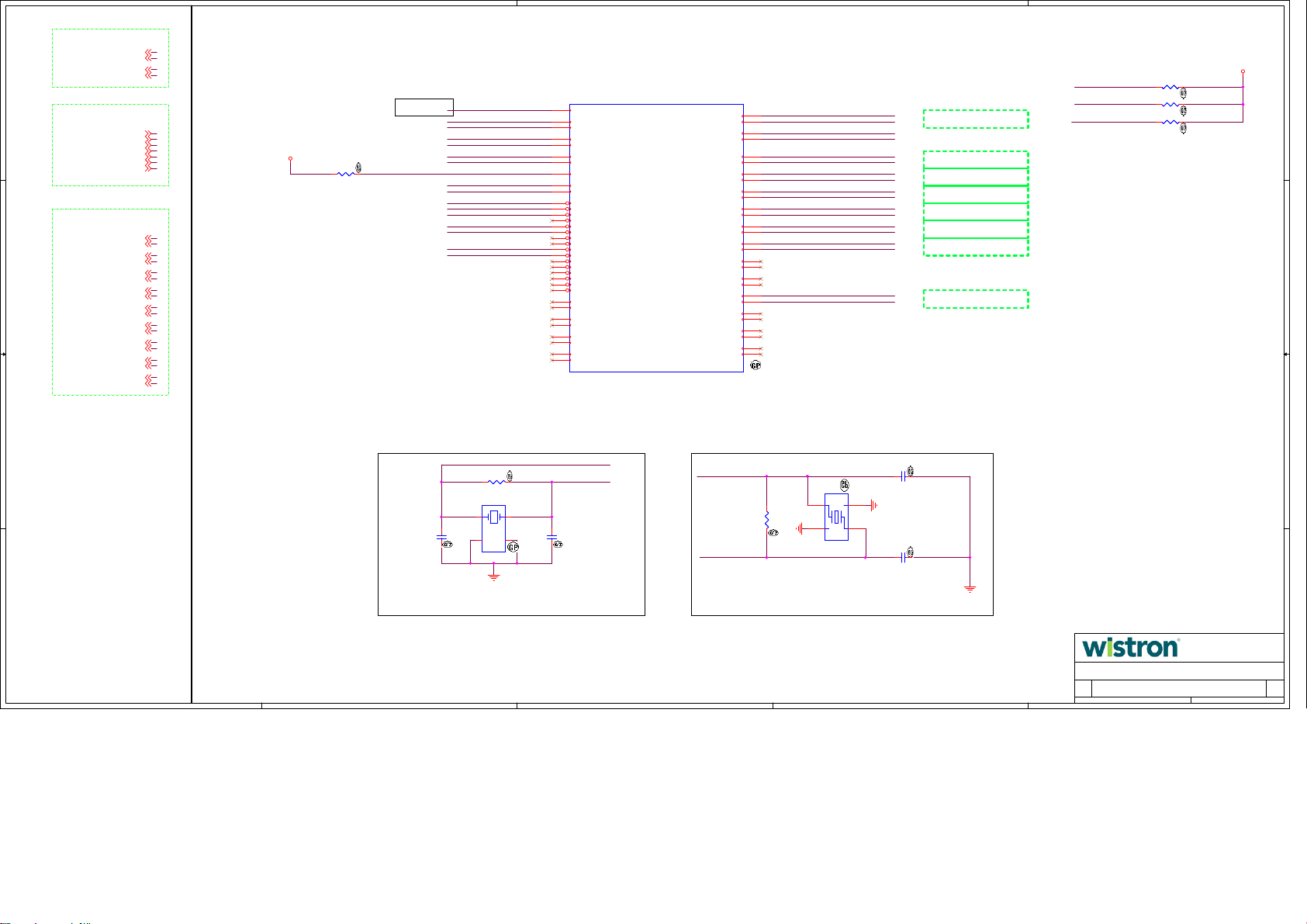

PROJECT NAME: vHULK

MB VERSION: -1

PCB BOARD SIZE:

D D

Internal Slot/Header

Front/Rear IO

Chipset

PCIEx16 slot

PCIE 3.0

CPU

Intel

Skylake-S

DDR4 CHA

DDR4 CHB

DDR4 DIMM *2

DDR4 DIMM *2

Display Port

DVI Port

DDI2

DDI3

DDI1

eDP

Display Port

DP to VGA

RGB

VGA PORT

DMI

Front USB 3.0 *2

Front USB 3.0 *2

C C

Front USB 2.0 *2

Front USB 2.0 *1

Rear USB 2.0 *2

(RJ45 USB conn)

Rear USB 3.0 *4

SATA PORT0

SATA Express

SATA PORT1

SATA PORT3

B B

SATA PORT4

SATA PORT5

USB 3.0

USB 3.0

USB 2.0

USB 2.0

USB 2.0

USB 3.0

SATA 3.0

SATA 3.0

SATA 3.0

SATA 3.0

SATA 3.0

PCH

SKL PCH-H

PCIE3.0

PCIE3.0

PCIE3.0

PCIE2.0/USB2.0

PCIE 2.0

PCIE3.0

SATA 3.0

SPI

LAN RTL8111EPV

RJ45 CONN/

USB2.0 x2 stack

Intel LAN I219LM

PCIE x1 Slot

PCIE x1 Slot

NGFF KEY E

TI PCI Bridge PCI Slot

NGFF KEY A

FLASH

TPM Header

Rear JACK

HP/MIC/LINE IN

Front header

HP/MIC

internal SPK

A A

5

Audio

ALC662

COM port Header

COM Port

4

HDA

COM

SIO

IT8732

3

LPC

FAN CTRL

TPM on board

CPU FAN

SYS FAN

<Core Design>

<Core Design>

PS2 KB/MSPrint Port

2

<Core Design>

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

2 107Wednesday, September 23, 2015

2 107Wednesday, September 23, 2015

2 107Wednesday, September 23, 2015

-1

-1

-1

5

4

3

2

1

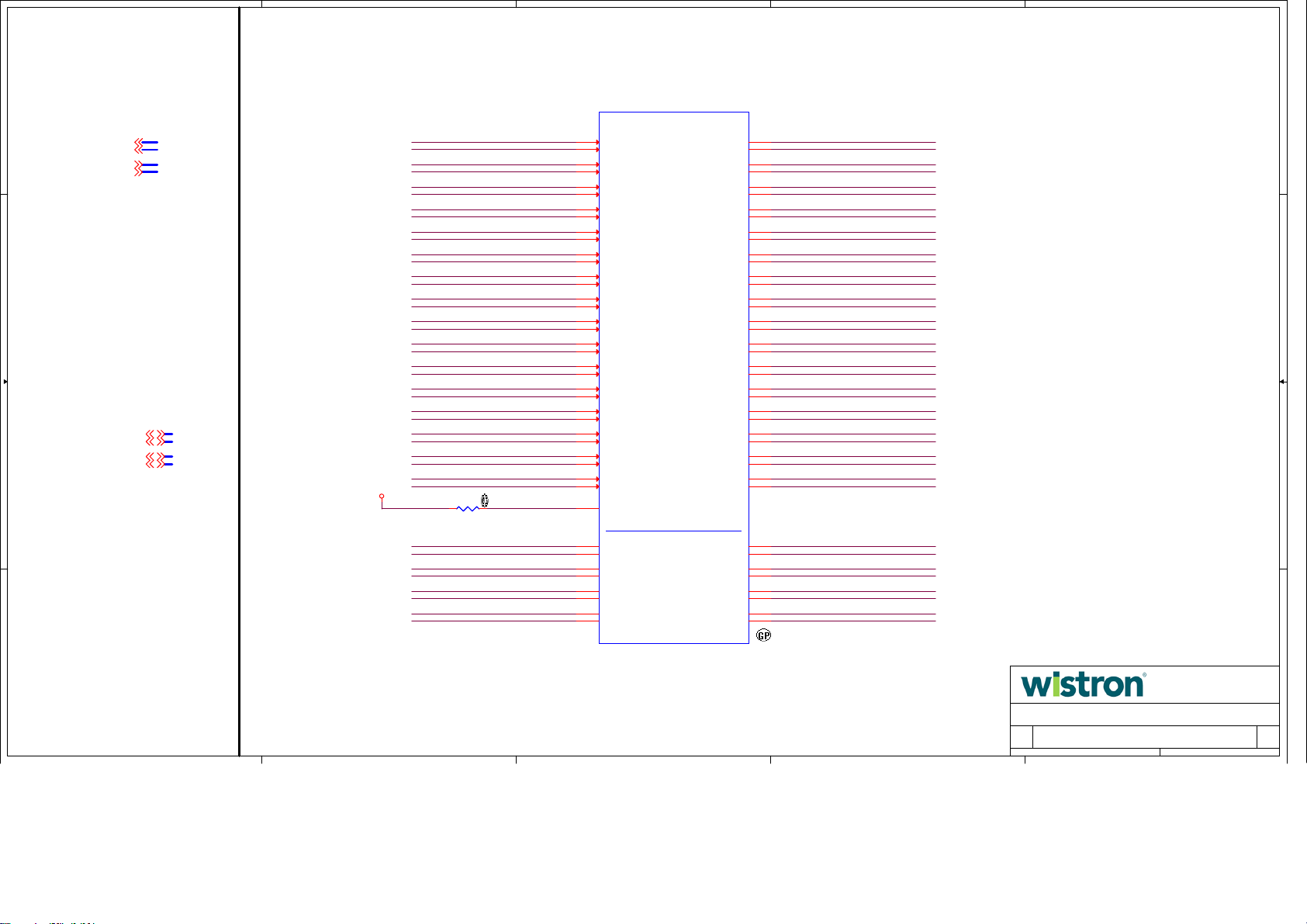

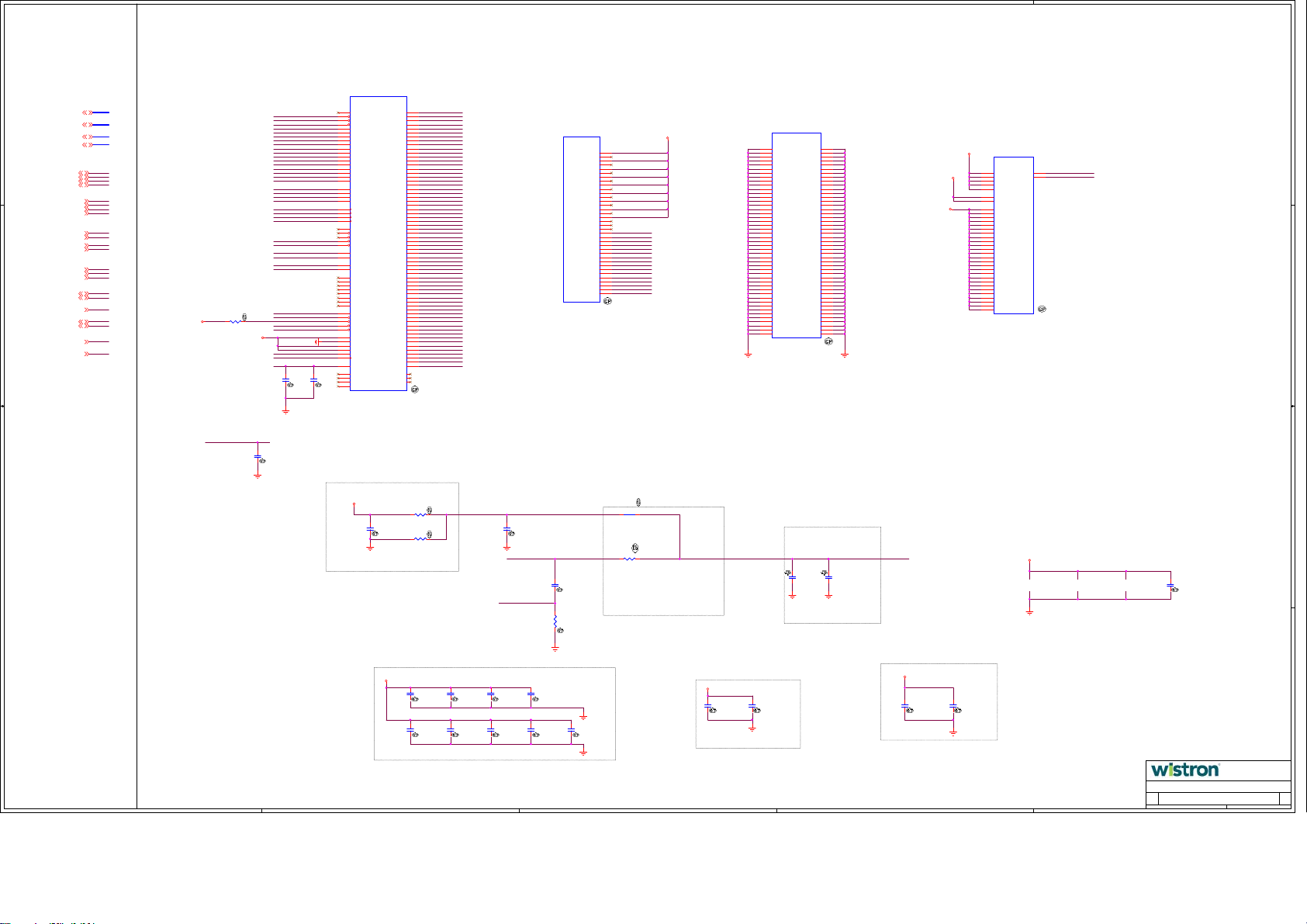

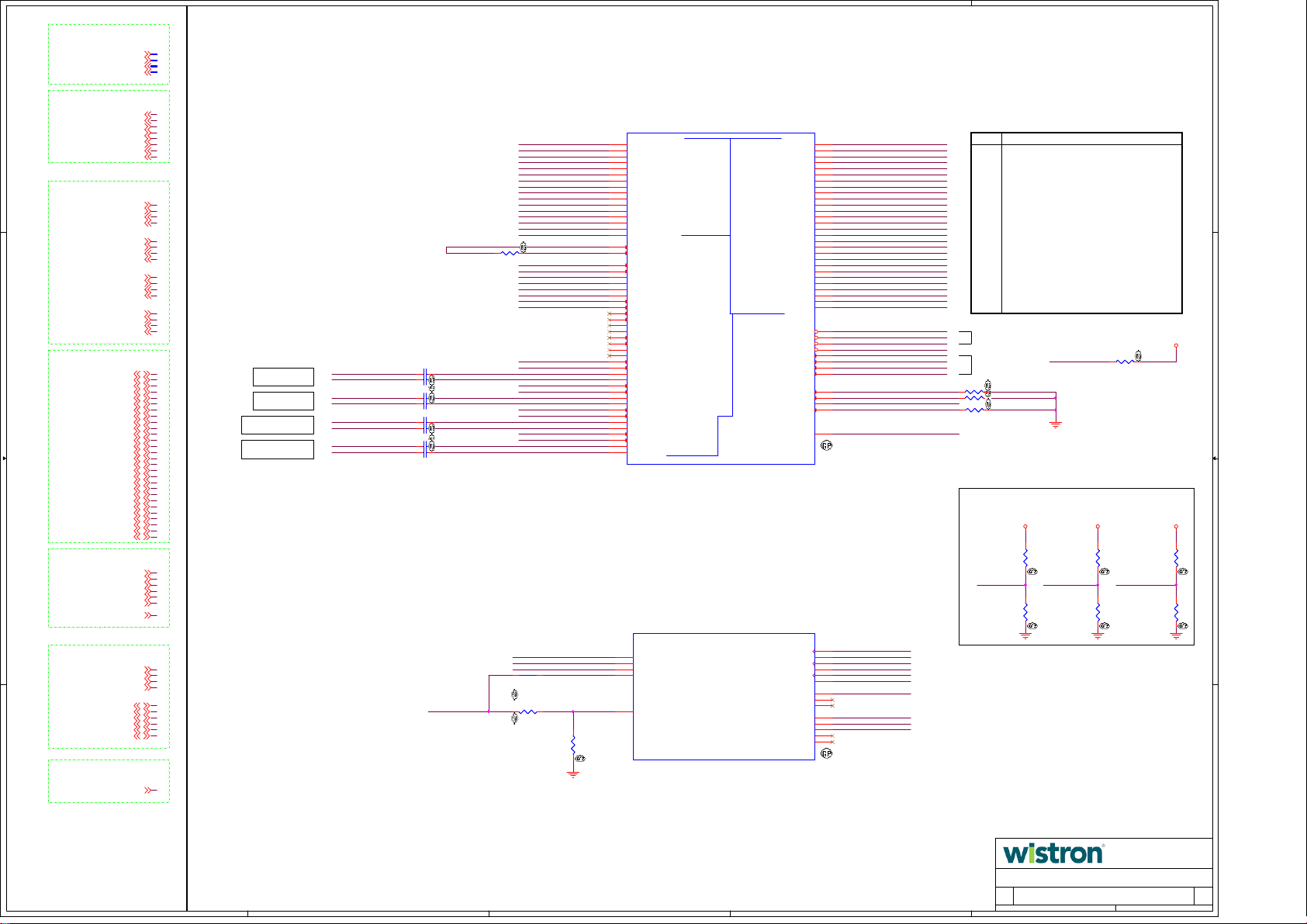

D D

PEG

4

PEG_RX_CPU_P0

PEG_RX_CPU_N0

PEG_RX_CPU_P1

PEG_RX_CPU_N1

PEG_RX_CPU_P2

PEG_RX_CPU_N2

PEG_RX_CPU_P3

PEG_RX_CPU_N3

PEG_RX_CPU_P4

PEG_RX_CPU_N4

PEG_RX_CPU_P5

PEG_RX_CPU_N5

PEG_RX_CPU_P6

PEG_RX_CPU_N6

PEG_RX_CPU_P7

PEG_RX_CPU_N7

PEG_RX_CPU_P8

PEG_RX_CPU_N8

PEG_RX_CPU_P9

PEG_RX_CPU_N9

PEG_RX_CPU_P10

PEG_RX_CPU_N10

PEG_RX_CPU_P11

PEG_RX_CPU_N11

PEG_RX_CPU_P12

PEG_RX_CPU_N12

PEG_RX_CPU_P13

PEG_RX_CPU_N13

PEG_RX_CPU_P14

PEG_RX_CPU_N14

PEG_RX_CPU_P15

PEG_RX_CPU_N15

1 2

R302

R302

24D9R2F-L-GP

24D9R2F-L-GP

DMI_RX_CPU_P0

DMI_RX_CPU_N0

DMI_RX_CPU_P1

DMI_RX_CPU_N1

DMI_RX_CPU_P2

DMI_RX_CPU_N2

DMI_RX_CPU_P3

DMI_RX_CPU_N3

PEG_RCOMP_CPU

PEG_TX_CPU_P[0..15]93

PEG_TX_CPU_N[0..15]93

PEG_RX_CPU_P[0..15]93

PEG_RX_CPU_N[0..15]93

C C

DMI

DMI_RX_CPU_P[0..3]16

DMI_RX_CPU_N[0..3]16

DMI_TX_CPU_P[0..3]16

B B

A A

DMI_TX_CPU_N[0..3]16

VCC_IO

5

CPU1C

CPU1C

SKYLAKE

SKYLAKE

PEG_RXP0

PEG_RXN0

PEG_RXP1

PEG_RXN1

PEG_RXP2

PEG_RXN2

PEG_RXP3

PEG_RXN3

PEG_RXP4

PEG_RXN4

PEG_RXP5

PEG_RXN5

PEG_RXP6

PEG_RXN6

PEG_RXP7

PEG_RXN7

PEG_RXP8

PEG_RXN8

PEG_RXP9

PEG_RXN9

PEG_RXP10

PEG_RXN10

PEG_RXP11

PEG_RXN11

PEG_RXP12

PEG_RXN12

PEG_RXP13

PEG_RXN13

PEG_RXP14

PEG_RXN14

PEG_RXP15

PEG_RXN15

PEG_RCOMP

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

3

AA4

AA5

AB4

AB3

AC4

AC5

B8

B7

C7

C6

D6

D5

E5

E4

F6

F5

G5

G4

H6

H5

J5

J4

K6

K5

L5

L4

M6

M5

N5

N4

P6

P5

R5

R4

T6

T5

U5

U4

L7

Y3

Y4

LGA1151

LGA1151

3 OF 12

3 OF 12

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

A5

A6

B4

B5

C3

C4

D2

D3

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

L1

L2

M2

M3

N1

N2

P2

P3

R2

R1

T2

T3

AC2

AC1

AD3

AD2

AE2

AE1

AF2

AF3

PEG_TX_CPU_P0

PEG_TX_CPU_N0

PEG_TX_CPU_P1

PEG_TX_CPU_N1

PEG_TX_CPU_P2

PEG_TX_CPU_N2

PEG_TX_CPU_P3

PEG_TX_CPU_N3

PEG_TX_CPU_P4

PEG_TX_CPU_N4

PEG_TX_CPU_P5

PEG_TX_CPU_N5

PEG_TX_CPU_P6

PEG_TX_CPU_N6

PEG_TX_CPU_P7

PEG_TX_CPU_N7

PEG_TX_CPU_P8

PEG_TX_CPU_N8

PEG_TX_CPU_P9

PEG_TX_CPU_N9

PEG_TX_CPU_P10

PEG_TX_CPU_N10

PEG_TX_CPU_P11

PEG_TX_CPU_N11

PEG_TX_CPU_P12

PEG_TX_CPU_N12

PEG_TX_CPU_P13

PEG_TX_CPU_N13

PEG_TX_CPU_P14

PEG_TX_CPU_N14

PEG_TX_CPU_P15

PEG_TX_CPU_N15

DMI_TX_CPU_P0

DMI_TX_CPU_N0

DMI_TX_CPU_P1

DMI_TX_CPU_N1

DMI_TX_CPU_P2

DMI_TX_CPU_N2

DMI_TX_CPU_P3

DMI_TX_CPU_N3

<Core Design>

<Core Design>

<Core Design>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

CPU(PCIE/DMI)

CPU(PCIE/DMI)

CPU(PCIE/DMI)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Hsichih, Taipei Hsien

1

-1

-1

3 107Wednesday, September 23, 2015

3 107Wednesday, September 23, 2015

3 107Wednesday, September 23, 2015

-1

5

4

3

2

1

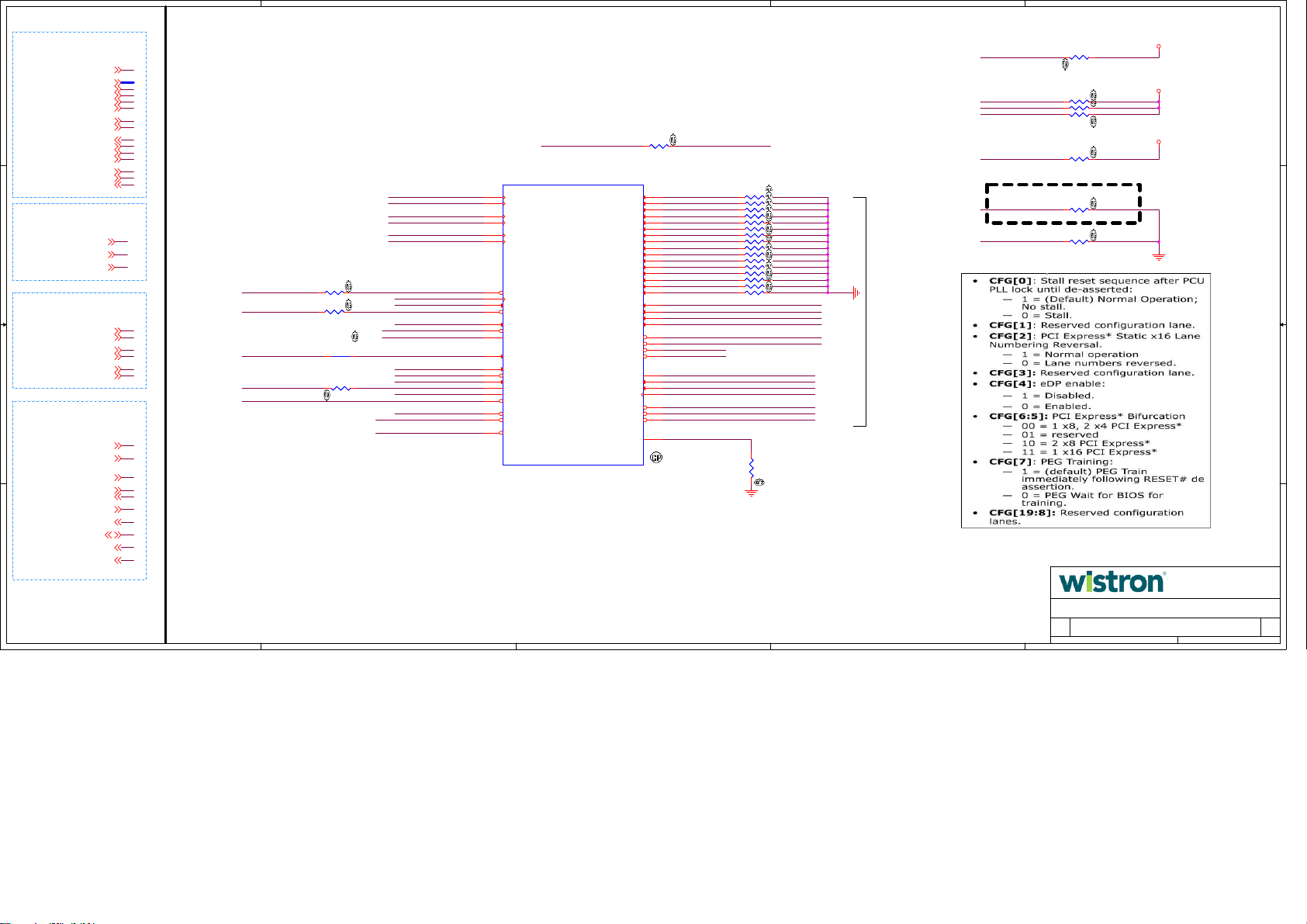

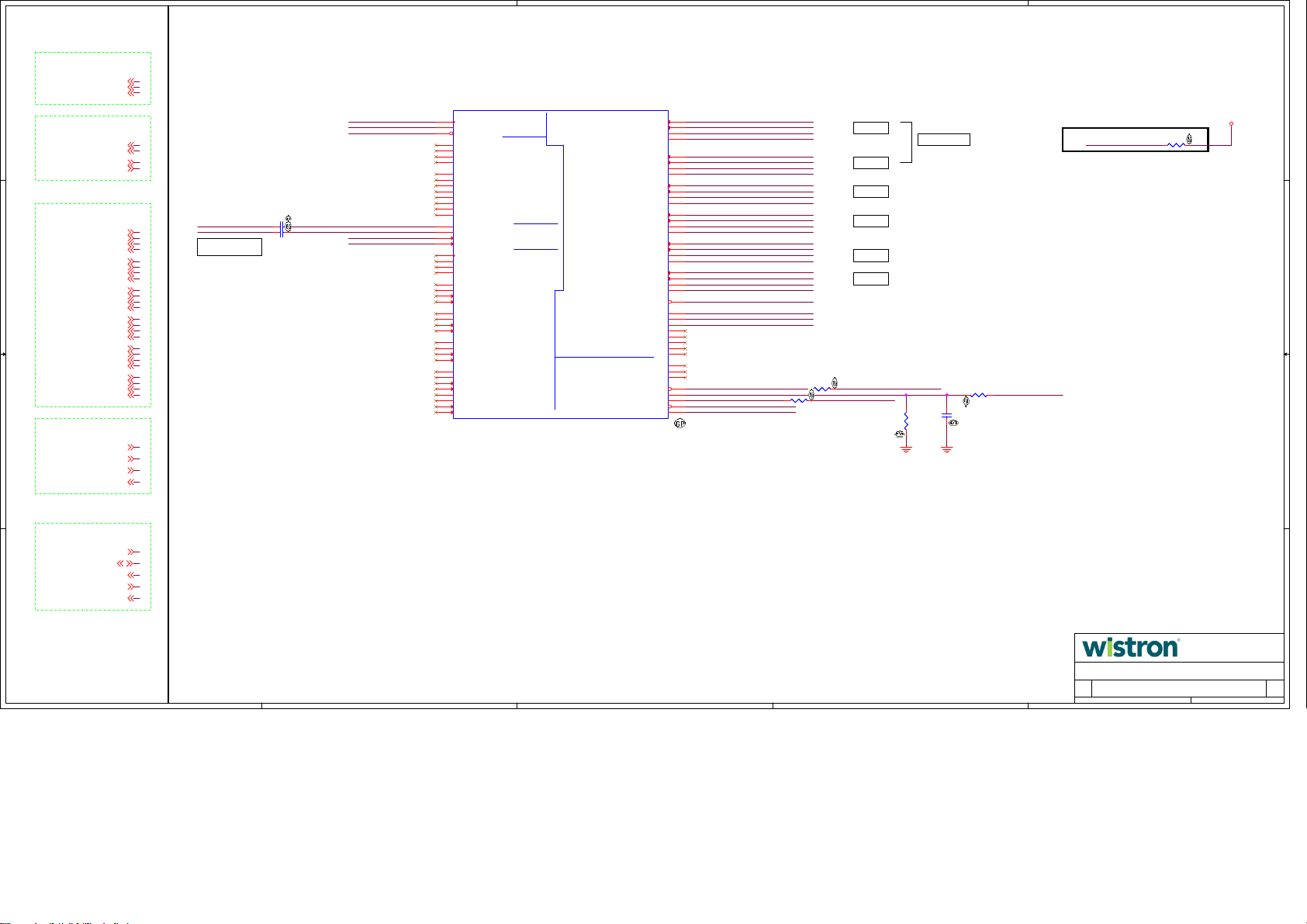

CPU XDP

XDP_PCUDEBUG<3>

CFG[0..15]

D D

SKL_PCUSTB_0_DP

SKL_PCUSTB_0_DN

SKL_PCUSTB_1_DP

SKL_PCUSTB_1_DN

BPM_CPU_N0

BPM_CPU_N1

H_TDO

H_TDI

H_TMS

H_TCK

H_TRST_N

H_PREQ_N

H_PRDY_N

SVID

C C

B B

A A

VIDSCK_VR146

VIDSOUT_VR146

VIDALERT#_VR146

CLOCK

CPU_BCLK_PCH18

CPU_BCLK_PCH#18

CPU_PCIBCLK_PCH18

CPU_PCIBCLK_PCH#18

CPU_CLK24M_PCH18

CPU_CLK24M_PCH#18

CONTROL

PROCHOT#_R46

DDR_VTT_CNTL44

CPU_VCCST_PWRGD40

H_PWRGD20

PLTRST_CPU_N17

PM_SYNC_CPU17

PM_DOWN_PCH17

PECI_CPU17,24

THERMTRIP#_CPU_R17

H_SKTOCC_N16

VIDALERT#_VR1 VIDALERT#_CPU

PROCHOT#_R PROCHOT#_CPU

CPU_VCCST_PWRGD

PM_DOWN_PCH

THERMTRIP#_CPU_R

5

1 2

R469 220R2J-L2-GPR469 220R2J-L2-GP

1 2

R467 100R2J-2-GPR467 100R2J-2-GP

R433

R433

1 2

0R0402-PAD-2-GP

0R0402-PAD-2-GP

R422 20R2J-3-GPR422 20R2J-3-GP

12

CPU_BCLK_PCH

CPU_BCLK_PCH#

CPU_PCIBCLK_PCH

CPU_PCIBCLK_PCH#

CPU_CLK24M_PCH

CPU_CLK24M_PCH#

VIDSCK_VR1

VIDSOUT_VR1

DDR_VTT_CNTL

TP_CPU_ZVM#

TP_CPU_AC37

CPU_VCCST_PWRGD_R

H_PWRGD

PLTRST_CPU_N

PM_SYNC_CPU

PM_DOWN_CPU

PECI_CPU

H_SKTOCC_N

SKL_CNL_N

CATERR#_CPU

4

CPU1E

CPU1E

W5

W4

W1

W2

K9

J9

E39

E38

E40

C39

AC36

AC38

AC37

U2

F8

E7

E8

D8

G7

D11

AB35

AB36

D13

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

CFG3 XDP_PCUDEBUG<3>

SKYLAKE

SKYLAKE

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

ZVM#

RSVD_AC37

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

LGA1151

LGA1151

5 OF 12

5 OF 12

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

BPM#0

BPM#1

BPM#2

BPM#3

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

R414

R414

1 2

1KR2J-1-GP

1KR2J-1-GP

H15

F15

F16

H16

F19

H18

G21

H20

G16

E16

F17

H17

G20

F20

F21

H19

E14

F14

G18

F18

D16

D17

G14

H14

H13

G12

F13

F11

F12

B9

B10

M11

3

TP_CPU_G14

TP_CPU_H14

CFG_RCOMP

CFG0

R416 1KR2J-1-GP(R_)R416 1KR2J-1-GP(R_)

CFG1

R418 1KR2J-1-GP(R_)R418 1KR2J-1-GP(R_)

CFG2

R419 1KR2J-1-GP(R_)R419 1KR2J-1-GP(R_)

CFG3

R420 1KR2J-1-GP(R_)R420 1KR2J-1-GP(R_)

CFG4

R431 1KR2J-1-GPR431 1KR2J-1-GP

CFG5

R429 1KR2J-1-GP(R_)R429 1KR2J-1-GP(R_)

CFG6

R430 1KR2J-1-GP(R_)R430 1KR2J-1-GP(R_)

CFG7

R417 1KR2J-1-GP(R_)R417 1KR2J-1-GP(R_)

CFG8

R426 1KR2J-1-GP(R_)R426 1KR2J-1-GP(R_)

CFG9

R432 1KR2J-1-GP(R_)R432 1KR2J-1-GP(R_)

CFG10

R423 1KR2J-1-GP(R_)R423 1KR2J-1-GP(R_)

CFG11

R428 1KR2J-1-GP(R_)R428 1KR2J-1-GP(R_)

CFG12

R424 1KR2J-1-GP(R_)R424 1KR2J-1-GP(R_)

CFG13

R425 1KR2J-1-GP(R_)R425 1KR2J-1-GP(R_)

CFG14

R427 1KR2J-1-GP(R_)R427 1KR2J-1-GP(R_)

CFG15

R458 1KR2J-1-GP(R_)R458 1KR2J-1-GP(R_)

SKL_PCUSTB_0_DN

SKL_PCUSTB_0_DP

SKL_PCUSTB_1_DN

SKL_PCUSTB_1_DP

BPM_CPU_N0

BPM_CPU_N1

H_TDO

H_TDI

H_TMS

H_TCK

H_TRST_N

H_PREQ_N

H_PRDY_N

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

R415

R415

49D9R2F-GP

49D9R2F-GP

For CPU XDP

2

SKL_CNL_N

VIDALERT#_VR1

VIDSOUT_VR1

PROCHOT#_R

H_SKTOCC_N

H_TCK

H_TRST_N

R21 10KR2J-3-GP(R_)R21 10KR2J-3-GP(R_)

R470 56R2F-1-GPR470 56R2F-1-GP

R471 100R2J-2-GPR471 100R2J-2-GP

R421 75R2F-2-GPR421 75R2F-2-GP

R477 10KR2J-3-GPR477 10KR2J-3-GP

H_TCK TERMINATION

PLACE NEAR CPU WITHIN 1.1 INCH

R403 51R2J-2-GPR403 51R2J-2-GP

PLace Any where

R407 51R2J-2-GP(R_)R407 51R2J-2-GP(R_)

12

1 2

1 2

1 2

1 2

1 2

1 2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU_(THERMAL/CLOCK/PM/CFG)

CPU_(THERMAL/CLOCK/PM/CFG)

CPU_(THERMAL/CLOCK/PM/CFG)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC_IO

1V_VCCST_VCCPLL_S3

3D3V_S5

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai W u Rd

21F, 88, Sec.1,Hsin Tai W u Rd

21F, 88, Sec.1,Hsin Tai W u Rd

1

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

4 107Wednesday, September 23, 2015

4 107Wednesday, September 23, 2015

4 107Wednesday, September 23, 2015

-1

-1

-1

5

M_DATA_A[0..63]12,14

M_A_A[0..16]12,14

M_A_DQS_DN[0..7]12,14

D D

C C

B B

M_A_DQS_DP[0..7]12,14

M_A_CLK014

M_A_CLK#014

M_A_CLK114

M_A_CLK#114

M_A_CLK212

M_A_CLK#212

M_A_CLK312

M_A_CLK#312

M_A_CKE014

M_A_CKE114

M_A_CKE212

M_A_CKE312

M_A_CS#014

M_A_CS#114

M_A_CS#212

M_A_CS#312

M_A_ODT014

M_A_ODT114

M_A_ODT212

M_A_ODT312

M_BA_A_112,14

M_BA_A_012,14

M_BG_A_112,14

M_BG_A_012,14

M_PARITY_A12,14

M_ALERT_A_N12,14

M_ACT_A_N12,14

4

CPU1A

CPU1A

M_DATA_A5

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A0

M_DATA_A6

M_DATA_A7

M_DATA_A13

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A8

M_DATA_A12

M_DATA_A14

M_DATA_A15

M_DATA_A21

M_DATA_A16

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A17

M_DATA_A22

M_DATA_A23

M_DATA_A25

M_DATA_A28

M_DATA_A27

M_DATA_A31

M_DATA_A29

M_DATA_A24

M_DATA_A30

M_DATA_A26

M_DATA_A32

M_DATA_A36

M_DATA_A34

M_DATA_A35

M_DATA_A33

M_DATA_A37

M_DATA_A39

M_DATA_A38

M_DATA_A44

M_DATA_A40

M_DATA_A47

M_DATA_A43

M_DATA_A41

M_DATA_A45

M_DATA_A46

M_DATA_A42

M_DATA_A49

M_DATA_A54

M_DATA_A53

M_DATA_A50

M_DATA_A52

M_DATA_A51

M_DATA_A48

M_DATA_A55

M_DATA_A61

M_DATA_A63

M_DATA_A60

M_DATA_A59

M_DATA_A62

M_DATA_A57

M_DATA_A58

M_DATA_A56

AE38

DDR0_DQ0

AE37

DDR0_DQ1

AG38

DDR0_DQ2

AG37

DDR0_DQ3

AE39

DDR0_DQ4

AE40

DDR0_DQ5

AG39

DDR0_DQ6

AG40

DDR0_DQ7

AJ38

DDR0_DQ8

AJ37

DDR0_DQ9

AL38

DDR0_DQ10

AL37

DDR0_DQ11

AJ40

DDR0_DQ12

AJ39

DDR0_DQ13

AL39

DDR0_DQ14

AL40

DDR0_DQ15

AN38

DDR0_DQ16/DDR0_DQ32

AN40

DDR0_DQ17/DDR0_DQ33

AR38

DDR0_DQ18/DDR0_DQ34

AR37

DDR0_DQ19/DDR0_DQ35

AN39

DDR0_DQ20/DDR0_DQ36

AN37

DDR0_DQ21/DDR0_DQ37

AR39

DDR0_DQ22/DDR0_DQ38

AR40

DDR0_DQ23/DDR0_DQ39

AW37

DDR0_DQ24/DDR0_DQ40

AU38

DDR0_DQ25/DDR0_DQ41

AV35

DDR0_DQ26/DDR0_DQ42

AW35

DDR0_DQ27/DDR0_DQ43

AU37

DDR0_DQ28/DDR0_DQ44

AV37

DDR0_DQ29/DDR0_DQ45

AT35

DDR0_DQ30/DDR0_DQ46

AU35

DDR0_DQ31/DDR0_DQ47

AY8

DDR0_DQ32/DDR1_DQ0

AW8

DDR0_DQ33/DDR1_DQ1

AV6

DDR0_DQ34/DDR1_DQ2

AU6

DDR0_DQ35/DDR1_DQ3

AU8

DDR0_DQ36/DDR1_DQ4

AV8

DDR0_DQ37/DDR1_DQ5

AW6

DDR0_DQ38/DDR1_DQ6

AY6

DDR0_DQ39/DDR1_DQ7

AY4

DDR0_DQ40/DDR1_DQ8

AV4

DDR0_DQ41/DDR1_DQ9

AT1

DDR0_DQ42/DDR1_DQ10

AT2

DDR0_DQ43/DDR1_DQ11

AV3

DDR0_DQ44/DDR1_DQ12

AW4

DDR0_DQ45/DDR1_DQ13

AT4

DDR0_DQ46/DDR1_DQ14

AT3

DDR0_DQ47/DDR1_DQ15

AP2

DDR0_DQ48/DDR1_DQ32

AM4

DDR0_DQ49/DDR1_DQ33

AP3

DDR0_DQ50/DDR1_DQ34

AM3

DDR0_DQ51/DDR1_DQ35

AP4

DDR0_DQ52/DDR1_DQ36

AM2

DDR0_DQ53/DDR1_DQ37

AP1

DDR0_DQ54/DDR1_DQ38

AM1

DDR0_DQ55/DDR1_DQ39

AK3

DDR0_DQ56/DDR1_DQ40

AH1

DDR0_DQ57/DDR1_DQ41

AK4

DDR0_DQ58/DDR1_DQ42

AH2

DDR0_DQ59/DDR1_DQ43

AH4

DDR0_DQ60/DDR1_DQ44

AK2

DDR0_DQ61/DDR1_DQ45

AH3

DDR0_DQ62/DDR1_DQ46

AK1

DDR0_DQ63/DDR1_DQ47

AU33

DDR0_ECC0

AT33

DDR0_ECC1

AW33

DDR0_ECC2

AV31

DDR0_ECC3

AU31

DDR0_ECC4

AV33

DDR0_ECC5

AW31

DDR0_ECC6

AY31

DDR0_ECC7

3

SKYLAKE

SKYLAKE

LGA1151

LGA1151

DDR0_BA0/DDR0_CAB4/DDR0_BA0

DDR0_BA1/DDR0_CAB6/DDR0_BA1

DDR0_BA2/DDR0_CAA5/DDR0_BG0

DDR0_RAS#/DDR0_CAB3/DDR0_MA16

DDR0_WE#/DDR0_CAB2/DDR0_MA14

DDR0_CAS#/DDR0_CAB1/DDR0_MA15

DDR0_MA0/DDR0_CAB9/DDR0_MA0

DDR0_MA1/DDR0_CAB8/DDR0_MA1

DDR0_MA2/DDR0_CAB5/DDR0_MA2

DDR0_MA5/DDR0_CAA0/DDR0_MA5

DDR0_MA6/DDR0_CAA2/DDR0_MA6

DDR0_MA7/DDR0_CAA4/DDR0_MA7

DDR0_MA8/DDR0_CAA3/DDR0_MA8

DDR0_MA9/DDR0_CAA1/DDR0_MA9

DDR0_MA10/DDR0_CAB7/DDR0_MA10

DDR0_MA11/DDR0_CAA7/DDR0_MA11

DDR0_MA12/DDR0_CAA6/DDR0_MA12

DDR0_MA13/DDR0_CAB0/DDR0_MA13

DDR0_MA14/DDR0_CAA9/DDR0_BG1

DDR0_MA15/DDR0_CAA8/DDR0_ACT#

DDR0_DQSN2/DDR0_DQSN4

DDR0_DQSN3/DDR0_DQSN5

DDR0_DQSN4/DDR1_DQSN0

DDR0_DQSN5/DDR1_DQSN1

DDR0_DQSN6/DDR1_DQSN4

DDR0_DQSN7/DDR1_DQSN5

DDR0_DQSP2/DDR0_DQSP4

DDR0_DQSP3/DDR0_DQSP5

DDR0_DQSP4/DDR1_DQSP0

DDR0_DQSP5/DDR1_DQSP1

DDR0_DQSP6/DDR1_DQSP4

DDR0_DQSP7/DDR1_DQSP5

1 OF 12

1 OF 12

DDR0_CKP0

DDR0_CKN0

DDR0_CKP1

DDR0_CKN1

DDR0_CKP2

DDR0_CKN2

DDR0_CKP3

DDR0_CKN3

DDR0_CKE0

DDR0_CKE1

DDR0_CKE2

DDR0_CKE3

DDR0_CS#0

DDR0_CS#1

DDR0_CS#2

DDR0_CS#3

DDR0_ODT0

DDR0_ODT1

DDR0_ODT2

DDR0_ODT3

DDR0_MA3

DDR0_MA4

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN0

DDR0_DQSN1

DDR0_DQSP0

DDR0_DQSP1

DDR0_DQSP8

DDR0_DQSN8

AW18

AV18

AW17

AY17

AW16

AV16

AT16

AU16

AY24

AW24

AV24

AV25

AW12

AU11

AV13

AV10

AW11

AU14

AU12

AY10

AY13

AV15

AW23

AW13

AV14

AY11

AW15

AU18

AU17

AV19

AT19

AU20

AV20

AU21

AT20

AT22

AY14

AU22

AV22

AV12

AV23

AU24

AY15

AT23

AF39

AK39

AP39

AU36

AW7

AU3

AN3

AJ3

AF38

AK38

AP38

AV36

AV7

AU2

AN2

AJ2

AV32

AU32

M_A_CLK0

M_A_CLK#0

M_A_CLK1

M_A_CLK#1

M_A_CLK2

M_A_CLK#2

M_A_CLK3

M_A_CLK#3

M_A_CKE0

M_A_CKE1

M_A_CKE2

M_A_CKE3

M_A_CS#0

M_A_CS#1

M_A_CS#2

M_A_CS#3

M_A_ODT0

M_A_ODT1

M_A_ODT2

M_A_ODT3

M_BA_A_0

M_BA_A_1

M_BG_A_0

M_A_A16

M_A_A14

M_A_A15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_BG_A_1

M_ACT_A_N

M_PARITY_A

M_ALERT_A_N

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

2

1

DDR CHANNEL A

DDR CHANNEL A

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

A A

5

4

<Core Design>

<Core Design>

<Core Design>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

CPU_(DDR_CHA)

CPU_(DDR_CHA)

CPU_(DDR_CHA)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Hsichih, Taipei Hsien

1

-1

-1

5 107Wednesday, September 23, 2015

5 107Wednesday, September 23, 2015

5 107Wednesday, September 23, 2015

-1

5

4

3

2

1

D D

C C

B B

M_B_A[0..16]11,13

M_DATA_B[0..63]11,13

M_B_DQS_DN[0..7]11,13

M_B_DQS_DP[0..7]11,13

M_B_CLK013

M_B_CLK#013

M_B_CLK113

M_B_CLK#113

M_B_CLK211

M_B_CLK#211

M_B_CLK311

M_B_CLK#311

M_B_CKE013

M_B_CKE113

M_B_CKE211

M_B_CKE311

M_B_CS#013

M_B_CS#113

M_B_CS#211

M_B_CS#311

M_B_ODT013

M_B_ODT113

M_B_ODT211

M_B_ODT311

M_BA_B_011,13

M_BA_B_111,13

M_BG_B_011,13

M_BG_B_111,13

M_ACT_B_N11,13

M_PARITY_B11,13

M_ALERT_B_N11,13

DIMM_CA_CPU_VREF_A12

M_VREF_DQ_DIM111

M_DATA_B4

M_DATA_B5

M_DATA_B7

M_DATA_B3

M_DATA_B1

M_DATA_B0

M_DATA_B6

M_DATA_B2

M_DATA_B13

M_DATA_B9

M_DATA_B14

M_DATA_B15

M_DATA_B12

M_DATA_B8

M_DATA_B10

M_DATA_B11

M_DATA_B16

M_DATA_B20

M_DATA_B22

M_DATA_B23

M_DATA_B17

M_DATA_B21

M_DATA_B18

M_DATA_B19

M_DATA_B28

M_DATA_B24

M_DATA_B30

M_DATA_B26

M_DATA_B25

M_DATA_B29

M_DATA_B27

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B38

M_DATA_B34

M_DATA_B36

M_DATA_B37

M_DATA_B39

M_DATA_B35

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B42

M_DATA_B41

M_DATA_B40

M_DATA_B47

M_DATA_B43

M_DATA_B52

M_DATA_B53

M_DATA_B55

M_DATA_B51

M_DATA_B48

M_DATA_B49

M_DATA_B54

M_DATA_B50

M_DATA_B61

M_DATA_B56

M_DATA_B63

M_DATA_B58

M_DATA_B60

M_DATA_B57

M_DATA_B59

M_DATA_B62

CPU1B

CPU1B

AD34

DDR1_DQ0/DDR0_DQ16

AD35

DDR1_DQ1/DDR0_DQ17

AG35

DDR1_DQ2/DDR0_DQ18

AH35

DDR1_DQ3/DDR0_DQ19

AE35

DDR1_DQ4/DDR0_DQ20

AE34

DDR1_DQ5/DDR0_DQ21

AG34

DDR1_DQ6/DDR0_DQ22

AH34

DDR1_DQ7/DDR0_DQ23

AK35

DDR1_DQ8/DDR0_DQ24

AL35

DDR1_DQ9/DDR0_DQ25

AK32

DDR1_DQ10/DDR0_DQ26

AL32

DDR1_DQ11/DDR0_DQ27

AK34

DDR1_DQ12/DDR0_DQ28

AL34

DDR1_DQ13/DDR0_DQ29

AK31

DDR1_DQ14/DDR0_DQ30

AL31

DDR1_DQ15/DDR0_DQ31

AP35

DDR1_DQ16/DDR0_DQ48

AN35

DDR1_DQ17/DDR0_DQ49

AN32

DDR1_DQ18/DDR0_DQ50

AP32

DDR1_DQ19/DDR0_DQ51

AN34

DDR1_DQ20/DDR0_DQ52

AP34

DDR1_DQ21/DDR0_DQ53

AN31

DDR1_DQ22/DDR0_DQ54

AP31

DDR1_DQ23/DDR0_DQ55

AL29

DDR1_DQ24/DDR0_DQ56

AM29

DDR1_DQ25/DDR0_DQ57

AP29

DDR1_DQ26/DDR0_DQ58

AR29

DDR1_DQ27/DDR0_DQ59

AM28

DDR1_DQ28/DDR0_DQ60

AL28

DDR1_DQ29/DDR0_DQ61

AR28

DDR1_DQ30/DDR0_DQ62

AP28

DDR1_DQ31/DDR0_DQ63

AR12

DDR1_DQ32/DDR1_DQ16

AP12

DDR1_DQ33/DDR1_DQ17

AM13

DDR1_DQ34/DDR1_DQ18

AL13

DDR1_DQ35/DDR1_DQ19

AR13

DDR1_DQ36/DDR1_DQ20

AP13

DDR1_DQ37/DDR1_DQ21

AM12

DDR1_DQ38/DDR1_DQ22

AL12

DDR1_DQ39/DDR1_DQ23

AP10

DDR1_DQ40/DDR1_DQ24

AR10

DDR1_DQ41/DDR1_DQ25

AR7

DDR1_DQ42/DDR1_DQ26

AP7

DDR1_DQ43/DDR1_DQ27

AR9

DDR1_DQ44/DDR1_DQ28

AP9

DDR1_DQ45/DDR1_DQ29

AR6

DDR1_DQ46/DDR1_DQ30

AP6

DDR1_DQ47/DDR1_DQ31

AM10

DDR1_DQ48

AL10

DDR1_DQ49

AM7

DDR1_DQ50

AL7

DDR1_DQ51

AM9

DDR1_DQ52

AL9

DDR1_DQ53

AM6

DDR1_DQ54

AL6

DDR1_DQ55

AJ6

DDR1_DQ56

AJ7

DDR1_DQ57

AE6

DDR1_DQ58

AF7

DDR1_DQ59

AH7

DDR1_DQ60

AH6

DDR1_DQ61

AE7

DDR1_DQ62

AF6

DDR1_DQ63

AR25

DDR1_ECC0

AR26

DDR1_ECC1

AM26

DDR1_ECC2

AM25

DDR1_ECC3

AP26

DDR1_ECC4

AP25

DDR1_ECC5

AL25

DDR1_ECC6

AL26

DDR1_ECC7

DDR CHANNEL B

DDR CHANNEL B

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

DDR1_RAS#/DDR1_CAB3/DDR1_MA16

DDR1_WE#/DDR1_CAB2/DDR1_MA14

DDR1_CAS#/DDR1_CAB1/DDR1_MA15

DDR1_BA0/DDR1_CAB4/DDR1_BA0

DDR1_BA1/DDR1_CAB6/DDR1_BA1

DDR1_BA2/DDR1_CAA5/DDR1_BG0

DDR1_MA0/DDR1_CAB9/DDR1_MA0

DDR1_MA1/DDR1_CAB8/DDR1_MA1

DDR1_MA2/DDR1_CAB5/DDR1_MA2

DDR1_MA5/DDR1_CAA0/DDR1_MA5

DDR1_MA6/DDR1_CAA2/DDR1_MA6

DDR1_MA7/DDR1_CAA4/DDR1_MA7

DDR1_MA8/DDR1_CAA3/DDR1_MA8

DDR1_MA9/DDR1_CAA1/DDR1_MA9

DDR1_MA10/DDR1_CAB7/DDR1_MA10

DDR1_MA11/DDR1_CAA7/DDR1_MA11

DDR1_MA12/DDR1_CAA6/DDR1_MA12

DDR1_MA13/DDR1_CAB0/DDR1_MA13

DDR1_MA14/DDR1_CAA9/DDR1_BG1

DDR1_MA15/DDR1_CAA8/DDR1_ACT#

DDR1_DQSN0/DDR0_DQSN2

DDR1_DQSN1/DDR0_DQSN3

DDR1_DQSN2/DDR0_DQSN6

DDR1_DQSN3/DDR0_DQSN7

DDR1_DQSN4/DDR1_DQSN2

DDR1_DQSN5/DDR1_DQSN3

DDR1_DQSP0/DDR0_DQSP2

DDR1_DQSP1/DDR0_DQSP3

DDR1_DQSP2/DDR0_DQSP6

DDR1_DQSP3/DDR0_DQSP7

DDR1_DQSP4/DDR1_DQSP2

DDR1_DQSP5/DDR1_DQSP3

2 OF 12

2 OF 12

DDR1_CKP0

DDR1_CKN0

DDR1_CKP1

DDR1_CKN1

DDR1_CKP2

DDR1_CKN2

DDR1_CKP3

DDR1_CKN3

DDR1_CKE0

DDR1_CKE1

DDR1_CKE2

DDR1_CKE3

DDR1_CS#0

DDR1_CS#1

DDR1_CS#2

DDR1_CS#3

DDR1_ODT0

DDR1_ODT1

DDR1_ODT2

DDR1_ODT3

DDR1_MA3

DDR1_MA4

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN6

DDR1_DQSN7

DDR1_DQSP6

DDR1_DQSP7

DDR1_DQSP8

DDR1_DQSN8

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AY29

AV29

AW29

AU29

AP17

AN15

AN17

AM15

AM16

AL16

AP15

AL15

AN18

AL17

AP16

AL18

AM18

AW28

AL19

AL22

AM22

AM23

AP23

AL23

AW26

AY26

AU26

AW27

AP18

AU27

AV27

AR15

AY28

AU28

AL20

AY25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

AN26

AB40

AC40

AC39

M_B_CLK0

M_B_CLK#0

M_B_CLK1

M_B_CLK#1

M_B_CLK2

M_B_CLK#2

M_B_CLK3

M_B_CLK#3

M_B_CKE0

M_B_CKE1

M_B_CKE2

M_B_CKE3

M_B_CS#0

M_B_CS#1

M_B_CS#2

M_B_CS#3

M_B_ODT0

M_B_ODT1

M_B_ODT2

M_B_ODT3

M_B_A16

M_B_A14

M_B_A15

M_BA_B_0

M_BA_B_1

M_BG_B_0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_BG_B_1

M_ACT_B_N

M_PARITY_B

M_ALERT_B_N

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

DIMM_CA_CPU_VREF_A

TP_DIMM_DQ0

M_VREF_DQ_DIM1

A A

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU (DDR_CHB)

CPU (DDR_CHB)

CPU (DDR_CHB)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

6 107Wednesday, September 23, 2015

6 107Wednesday, September 23, 2015

6 107Wednesday, September 23, 2015

1

-1

-1

-1

5

4

3

2

1

D D

DP_DATA_CPU_P057

DP_DATA_CPU_N057

DP_DATA_CPU_P157

DP_DATA_CPU_N157

DP_DATA_CPU_P257

DP_DATA_CPU_N257

DP_DATA_CPU_P357

DP_DATA_CPU_N357

DP_AUX_CPU_P57

DP_AUX_CPU_N57

DP2_DATA_CPU_P056

DP2_DATA_CPU_N056

DP2_DATA_CPU_P156

DP2_DATA_CPU_N156

DP2_DATA_CPU_P256

DP2_DATA_CPU_N256

DP2_DATA_CPU_P356

DP2_DATA_CPU_N356

C C

B B

DP2_AUX_CPU_P56

DP2_AUX_CPU_N56

DVI_DATA_CPU_P055

DVI_DATA_CPU_N055

DVI_DATA_CPU_P155

DVI_DATA_CPU_N155

DVI_DATA_CPU_P255

DVI_DATA_CPU_N255

DVI_DATA_CPU_P355

DVI_DATA_CPU_N355

DDI_VGA_DATA_CPU_N058

DDI_VGA_DATA_CPU_P058

DDI_VGA_DATA_CPU_N158

DDI_VGA_DATA_CPU_P158

DDI_VGA_AUX_CPU_P58

DDI_VGA_AUX_CPU_N58

AUD_AZACPU_SCLK20

AUD_AZACPU_SDO_R20

AUD_AZACPU_CPU_SDI20

FOR DP1

FOR DP2

FOR DVI-D

DP_DATA_CPU_P0

DP_DATA_CPU_N0

DP_DATA_CPU_P1

DP_DATA_CPU_N1

DP_DATA_CPU_P2

DP_DATA_CPU_N2

DP_DATA_CPU_P3

DP_DATA_CPU_N3

DP_AUX_CPU_P

DP_AUX_CPU_N

DP2_DATA_CPU_P0

DP2_DATA_CPU_N0

DP2_DATA_CPU_P1

DP2_DATA_CPU_N1

DP2_DATA_CPU_P2

DP2_DATA_CPU_N2

DP2_DATA_CPU_P3

DP2_DATA_CPU_N3

DP2_AUX_CPU_P

DP2_AUX_CPU_N

DVI_DATA_CPU_P0

DVI_DATA_CPU_N0

DVI_DATA_CPU_P1

DVI_DATA_CPU_N1

DVI_DATA_CPU_P2

DVI_DATA_CPU_N2

DVI_DATA_CPU_P3

DVI_DATA_CPU_N3

CPU1D

CPU1D

C21

DDI1_TXP0

D21

DDI1_TXN0

D22

DDI1_TXP1

E22

DDI1_TXN1

B23

DDI1_TXP2

A23

DDI1_TXN2

C23

DDI1_TXP3

D23

DDI1_TXN3

B13

DDI1_AUXP

C13

DDI1_AUXN

B18

DDI2_TXP0

A18

DDI2_TXN0

D18

DDI2_TXP1

E18

DDI2_TXN1

C19

DDI2_TXP2

D19

DDI2_TXN2

D20

DDI2_TXP3

E20

DDI2_TXN3

A12

DDI2_AUXP

B12

DDI2_AUXN

B14

DDI3_TXP0

A14

DDI3_TXN0

C15

DDI3_TXP1

B15

DDI3_TXN1

B16

DDI3_TXP2

A16

DDI3_TXN2

C17

DDI3_TXP3

B17

DDI3_TXN3

B11

DDI3_AUXP

C11

DDI3_AUXN

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

4 OF 12

4 OF 12

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

VBIOS set as DP

E10

D10

D9

C9

H10

G10

G9

F9

D12

E12

D14

M9

V3

V2

U1

DDI_VGA_DATA_CPU_N0

DDI_VGA_DATA_CPU_P0

DDI_VGA_DATA_CPU_N1

DDI_VGA_DATA_CPU_P1

DDI_VGA_AUX_CPU_P

DDI_VGA_AUX_CPU_N

eDP_RCOMP_CPU

AUD_AZACPU_SCLK

AUD_AZACPU_SDO_R

AUD_AZACPU_CPU_SDI

R703

R703

1 2

24D9R2F-L-GP

24D9R2F-L-GP

CAD NOTE:

PLACE RA INSIDE CPU CAVITY

FOR DP TO VGA

VCC_IO

<Core Design>

<Core Design>

A A

5

4

3

2

<Core Design>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

CPU (DDI/EDP)

CPU (DDI/EDP)

CPU (DDI/EDP)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

Date: Sheet of

Hsichih, Taipei Hsien

1

7 107Wednesday, September 23, 2015

7 107Wednesday, September 23, 2015

7 107Wednesday, September 23, 2015

-1

-1

-1

5

VCCGT_SENSE46

VSSGT_SENSE46

VCCCORE_SENSE46

VSSCORE_SENSE46

VCCSA_SENSE52

VCCIO_SENSE53

VSS_VCCSA_SSENSE52

D D

C C

B B

VSS_VCCIO_SSENSE53

SLP_S4_N20,24,42,44

VCC_CORE

CPU1G

CPU1G

A25

VCC_A25

A26

VCC_A26

A27

VCC_A27

A28

VCC_A28

A29

VCC_A29

A30

VCC_A30

B25

VCC_B25

B27

VCC_B27

B29

VCC_B29

B31

VCC_B31

B32

VCC_B32

B33

VCC_B33

B34

VCC_B34

B35

VCC_B35

B36

VCC_B36

B37

VCC_B37

C25

VCC_C25

C26

VCC_C26

C27

VCC_C27

C28

VCC_C28

C29

VCC_C29

C30

VCC_C30

C32

VCC_C32

C34

VCC_C34

C36

VCC_C36

D25

VCC_D25

D27

VCC_D27

D29

VCC_D29

D31

VCC_D31

D32

VCC_D32

D33

VCC_D33

D34

VCC_D34

D35

VCC_D35

D36

VCC_D36

E24

VCC_E24

E25

VCC_E25

E26

VCC_E26

E27

VCC_E27

E28

VCC_E28

E29

VCC_E29

E30

VCC_E30

E32

VCC_E32

E34

VCC_E34

E36

VCC_E36

F23

VCC_F23

F24

VCC_F24

F25

VCC_F25

F27

VCC_F27

F29

VCC_F29

F31

VCC_F31

G30

VCC_G30

G32

VCC_G32

H22

VCC_H22

H23

VCC_H23

H25

VCC_H25

H27

VCC_H27

H29

VCC_H29

H31

VCC_H31

AJ11

VCC_AJ11

AJ13

VCC_AJ13

AJ15

VCC_AJ15

AJ17

VCC_AJ17

AJ19

VCC_AJ19

AJ21

VCC_AJ21

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

VCC_H32

VCC_J21

VCC_F32

VCC_F33

VCC_F34

VCC_G23

VCC_G24

VCC_G25

VCC_G26

VCC_G27

VCC_G28

VCC_G29

VCC_J22

VCC_J23

VCC_J24

VCC_J25

VCC_J26

VCC_J27

VCC_J28

VCC_J29

VCC_J30

VCC_J31

VCC_K16

VCC_K18

VCC_K20

VCC_K21

VCC_K23

VCC_K25

VCC_K27

VCC_K29

VCC_K31

VCC_L14

VCC_L15

VCC_L16

VCC_L17

VCC_L18

VCC_L19

VCC_L20

VCC_L21

VCC_L22

VCC_L23

VCC_L24

VCC_L25

VCC_L26

VCC_L27

VCC_L28

VCC_L29

VCC_L30

VCC_M13

VCC_M14

VCC_M16

VCC_M18

VCC_M20

VCC_M22

VCC_M24

VCC_M26

VCC_M28

VCC_M30

VCC_AJ12

VCC_AJ14

VCC_AJ16

VCC_AJ18

VCC_AJ20

VCC_AJ22

VCC_SENSE

VSS_SENSE

7 OF 12

7 OF 12

H32

J21

F32

F33

F34

G23

G24

G25

G26

G27

G28

G29

J22

J23

J24

J25

J26

J27

J28

J29

J30

J31

K16

K18

K20

K21

K23

K25

K27

K29

K31

L14

L15

L16

L17

L18

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

M13

M14

M16

M18

M20

M22

M24

M26

M28

M30

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

C38

D38

4

VCC_CORE GFX_CORE

VCCCORE_SENSE

VSSCORE_SENSE

CPU1H

CPU1H

SKYLAKE

SKYLAKE

AA34

VCCGT

AA35

VCCGT

AA36

VCCGT

AA37

VCCGT

AA38

VCCGT

AB33

VCCGT

AB34

VCCGT

G36

VCCGT

G37

VCCGT

G38

VCCGT

G39

VCCGT

G40

VCCGT

H36

VCCGT

H38

VCCGT

H40

VCCGT

J36

VCCGT

J37

VCCGT

J38

VCCGT

J39

VCCGT

J40

VCCGT

K36

VCCGT

K38

VCCGT

K40

VCCGT

L34

VCCGT

L35

VCCGT

L36

VCCGT

L37

VCCGT

L38

VCCGT

L39

VCCGT

L40

VCCGT

M33

VCCGT

M34

VCCGT

M36

VCCGT

M38

VCCGT

M40

VCCGT

N34

VCCGT

N35

VCCGT

N36

VCCGT

N37

VCCGT

N38

VCCGT

N39

VCCGT

N40

VCCGT

P33

VCCGT

P34

VCCGT

P36

VCCGT

P38

VCCGT

P40

VCCGT

R34

VCCGT

R35

VCCGT

R36

VCCGT

R37

VCCGT

R38

VCCGT

R39

VCCGT

R40

VCCGT

T33

VCCGT

T34

VCCGT

T36

VCCGT

T38

VCCGT

T40

VCCGT

U34

VCCGT

U35

VCCGT

U36

VCCGT

U37

VCCGT

U38

VCCGT

U39

VCCGT

U40

VCCGT

V33

VCCGT

V34

VCCGT

V36

VCCGT

V38

VCCGT

V40

VCCGT

W34

VCCGT

W35

VCCGT

W36

VCCGT

W37

VCCGT

W38

VCCGT

Y33

VCCGT

Y34

VCCGT

Y36

VCCGT

Y38

VCCGT

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

LGA1151

LGA1151

VCCGTX_SENSE

VSSGTX_SENSE

VCCGTX_F35

VCCGTX_G34

VCCGTX_G35

VCCGTX_H33

VCCGTX_H34

VCCGTX_J33

VCCGTX_J35

VCCGTX_K32

VCCGTX_K34

VCCGTX_L31

VCCGTX_L33

VCCGTX_M32

VCCGT_SENSE

VSSGT_SENSE

8 OF 12

8 OF 12

FOR 4+4E CPU

F35

G34

G35

H33

H34

J33

J35

K32

K34

L31

L33

M32

F39

VCCGT_SENSE

F38

VSSGT_SENSE

F37

VCCGTX_SENSE

F36

VSSGTX_SENSE

3

VCC_GTX

R705 0R3J-0-U-GP(R_)R705 0R3J-0-U-GP(R_)

2

12

+VCCFUSEPRG

1V_VCCST_VCCPLL_S3

VCC_SA

VCC_IO

INTEL RECOMMAND

CPU1I

CPU1I

AA7

VCCSA

AB6

VCCSA

AB7

VCCSA

AB8

VCCSA

AC7

VCCSA

AC8

VCCSA

N7

VCCSA

P7

VCCSA

R7

VCCSA

T7

VCCSA

U7

VCCSA

Y6

VCCSA

Y7

VCCSA

Y8

VCCSA

W7

VCCSA

V7

VCCSA

AA6

VCCSA

AK11

VCCIO

AK14

VCCIO

AK24

VCCIO

AJ23

VCCIO

M8

VCCIO

P8

VCCIO

T8

VCCIO

U8

VCCIO

W8

VCCIO

V5

VCCST_V5

V6

VCCST_V6

V4

VCCPLL

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

VCC_OPC_1P8_AB37

VCC_OPC_1P8_AB38

VSS_SAIO_SENSE

VCCEOPIO_SENSE

VSSOPC_EOPIO_SENSE

VDDQ_AT18

VDDQ_AT21

VDDQ_AU13

VDDQ_AU15

VDDQ_AU19

VDDQ_AU23

VDDQ_AV11

VDDQ_AV17

VDDQ_AV21

VDDQ_AW10

VDDQ_AW14

VDDQ_AW25

VDDQ_AY12

VDDQ_AY16

VDDQ_AY18

VDDQ_AY23

VCCPLL_OC

VCCOPC_AJ30

VCCOPC_AJ27

VCCOPC_AJ28

VCCOPC_AJ29

VCCOPC_AK27

VCCEOPIO

VCCEOPIO

VCCSA_SENSE

VCCIO_SENSE

VCCOPC_SENSE

9 OF 12

9 OF 12

AT18

AT21

AU13

AU15

AU19

AU23

AV11

AV17

AV21

AW10

AW14

AW25

AY12

AY16

AY18

AY23

AJ9

AJ30

AJ27

AJ28

AJ29

AK27

AJ25

AJ26

AB37

AB38

AD5

AF4

AE4

AK21

AJ24

AK22

VCCPLL_OC

FOR 4+4E CPU

VCC_OPC

VCC_EOPIO

VCC_OPC_1P8_AB37

VCC_OPC_1P8_AB38

VCCSA_SENSE

VCCIO_SENSE

VSS_SENSE

TP_VCCOPC_SENSE

TP_VCCEOPIO_SENSE

TP_VSSOPC_EOPIO_SENSE

FOR 4+4E CPU

VDDQ

R701 0R0603-PADR701 0R0603-PAD

R706 0R3J-0-U-GP(R_)R706 0R3J-0-U-GP(R_)

R707 0R3J-0-U-GP(R_)R707 0R3J-0-U-GP(R_)

VDDQ

12

12

12

1 2

R5213 0R0402-PAD-2-GPR5213 0R0402-PAD-2-GP

1 2

R5214 0R0402-PAD-2-GPR5214 0R0402-PAD-2-GP

1

VSS_VCCSA_SSENSE

VSS_VCCIO_SSENSE

+5V_AUX1 +5V_AUX1

12

R77

R77

100KR2J-1-GP

100KR2J-1-GP

Q1

Q1

2345

1

SLP_S4_N_SFR_1

SLP_S4_N SLP_S4_N_SFR

A A

5

4

1 2

R85 0R0402-PAD-2-GPR85 0R0402-PAD-2-GP

6

2N7002EDW-2-GP

2N7002EDW-2-GP

(75.27002.F7C)

(75.27002.F7C)

12

C803

SCD1U25V3KX-GP

SCD1U25V3KX-GP

3

12

R78

R78

47KR2J-2-GP

47KR2J-2-GP

R84

R84

1 2

SLP_S4_N_SFR_GSLP_S4_N_SFR_2

10KR2J-3-GP

10KR2J-3-GP

12

12

C802

C802

SCD1U25V2KX-GP

SCD1U25V2KX-GP

VCC_CORE

R73

0R2J-2-GP

(R_)C803

(R_)

1V_VCCST_VCCPLL_S3

0R2J-2-GP

R76 0R0402-PAD-2-GPR76 0R0402-PAD-2-GP

C801

(R_)C801

(R_)

SCD1U25V3KX-GP

SCD1U25V3KX-GP

1 2

(R_)R73

(R_)

1 2

1D0V_S5

DS

G

V_CPU_ST_PLL_R

2

Q2

Q2

AO3418L-GP

AO3418L-GP

(84.03418.A31)

(84.03418.A31)

12

R83

4K7R2J-2-GP

4K7R2J-2-GP

(R_)R83

(R_)

R704 0R3J-0-U-GP(R_)R704 0R3J-0-U-GP(R_)

1 2

+VCCFUSEPRG

1V_VCCST_VCCPLL_S3

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU (CPU Power)

CPU (CPU Power)

CPU (CPU Power)

S

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

8 107Wednesday, September 23, 2015

8 107Wednesday, September 23, 2015

8 107Wednesday, September 23, 2015

-1

-1

-1

5

PROC_TRIGIN_CPU21

PROC_TRIGOUT_PCH21

D D

A11

A13

A15

A17

A24

A7

AA3

AA33

AA8

AB39

AB5

AC3

AC33

AC34

AC35

AC6

AD1

AD33

AD36

AD37

AD38

AD39

AD4

AD40

AD6

AD7

AD8

AE3

AE33

AE36

AE5

AE8

AF1

C C

B B

AF33

AF36

AF37

AF40

AG33

AG36

AH33

AH36

AH37

AH38

AH39

AH40

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK10

AK12

AK13

AK15

AK16

AK17

AK18

AK19

AK20

AK23

AK25

AK26

AK28

AF5

AF8

AG1

AG2

AG3

AG4

AG5

AG8

AH5

AH8

AJ1

AJ4

AJ5

AJ8

6 OF 12

6 OF 12

CPU1F

CPU1F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

AK29

VSS

AK30

VSS

AK36

VSS

AK37

VSS

AK40

VSS

AK5

VSS

AK6

VSS

AK7

VSS

AK8

VSS

AK9

VSS

AL1

VSS

AL11

VSS

AL14

VSS

AL2

VSS

AL21

VSS

AL24

VSS

AL27

VSS

AL3

VSS

AL30

VSS

AL36

VSS

AL4

VSS

AL5

VSS

AM11

VSS

AM14

VSS

AM17

VSS

AM19

VSS

AM24

VSS

AM27

VSS

AM30

VSS

AM31

VSS

AM32

VSS

AM33

VSS

AM34

VSS

AM35

VSS

AM36

VSS

AM37

VSS

AM38

VSS

AM39

VSS

AM40

VSS

AM5

VSS

AN1

VSS

AN10

VSS

AN11

VSS

AN14

VSS

AN16

VSS

AN19

VSS

AN22

VSS

AN23

VSS

AN24

VSS

AN27

VSS

AN30

VSS

AN36

VSS

AN4

VSS

AN5

VSS

AN6

VSS

AN7

VSS

AN8

VSS

AN9

VSS

AP11

VSS

AP14

VSS

AP24

VSS

AP27

VSS

AP30

VSS

AP36

VSS

AP37

VSS

AP40

VSS

AP5

VSS

AR1

VSS

AR11

VSS

AR14

VSS

AR16

VSS

AR17

VSS

AR18

VSS

AR19

VSS

AR2

VSS

AR20

VSS

AR21

VSS

4

CPU1K

CPU1K

AR24

VSS

AR27

VSS

AR3

VSS

AR30

VSS

AR31

VSS

AR32

VSS

AR33

VSS

AR34

VSS

AR35

VSS

AR36

VSS

AR4

VSS

AR5

VSS

AT10

VSS

AT11

VSS

AT12

VSS

AT13

VSS

AT14

VSS

AT17

VSS

AT24

VSS

AT25

VSS

AT26

VSS

AT27

VSS

AT28

VSS

AT29

VSS

AT30

VSS

AT31

VSS

AT32

VSS

AT34

VSS

AT36

VSS

AT37

VSS

AT38

VSS

AT39

VSS

AT40

VSS

AT5

VSS

AT6

VSS

AT7

VSS

AT8

VSS

AT9

VSS

AU1

VSS

AU25

VSS

AU30

VSS

AU34

VSS

AU4

VSS

AU5

VSS

AU7

VSS

AV2

VSS

AV26

VSS

AV28

VSS

AV30

VSS

AV34

VSS

AV38

VSS

AV5

VSS

AV9

VSS

AW3

VSS

AW30

VSS

AW32

VSS

AW34

VSS

AW36

VSS

AW5

VSS

AW9

VSS

AY27

VSS

AY30

VSS

AY5

VSS

AY7

VSS

AY9

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

B6

VSS

C12

VSS

C14

VSS

C16

VSS

C18

VSS

C20

VSS

C22

VSS

C24

VSS

C31

VSS

C33

VSS

C35

VSS

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

11 OF 12

11 OF 12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3

12 OF 12

12 OF 12

CPU1L

C37

C5

C8

C10

D24

D26

D28

D30

D37

D39

D4

D7

E11

E13

E15

E17

E19

E21

E23

E3

E31

E33

E35

E37

E6

E9

F1

F10

F22

F26

F28

F30

F4

F40

F7

G11

G13

G15

G17

G19

G22

G3

G31

G33

G6

H1

H21

H24

H26

H28

H30

H35

H37

H39

H4

H7

H9

J10

J12

L11

J16

J18

J20

J3

J32

J34

J6

K1

K14

K15

K17

K19

K22

K24

K26

K28

K30

K33

K35

K37

CPU1L

SKYLAKE

SKYLAKE

K39

VSS

K4

VSS

K7

VSS

L13

VSS

L3

VSS

L32

VSS

L6

VSS

L9

VSS

M1

VSS

M10

VSS

M12

VSS

M15

VSS

LGA1151

LGA1151

M17

VSS

M19

VSS

M21

VSS

M23

VSS

M25

VSS

M27

VSS

M29

VSS

M35

VSS

M37

VSS

M39

VSS

M4

VSS

M7

VSS

N3

VSS

N33

VSS

N6

VSS

N8

VSS

P1

VSS

P35

VSS

P37

VSS

P39

VSS

P4

VSS

R3

VSS

R33

VSS

R6

VSS

R8

VSS

T1

VSS

T35

VSS

T37

VSS

T39

VSS

T4

VSS

U3

VSS

U33

VSS

U6

VSS

V1

VSS

V35

VSS

V37

VSS

V39

VSS

V8

VSS

W3

VSS

W33

VSS

W6

VSS

Y35

VSS

Y37

VSS

Y5

VSS

A4

VSS_NCTF

B38

VSS_NCTF

C2

VSS_NCTF

D40

VSS_NCTF

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

PROC_TRIGOUT_PCH

R902

R902

20R2J-3-GP

20R2J-3-GP

12

2

TP_CPU_J8

TP_CPU_J7

TP_CPU_L8

TP_CPU_K8

TP_CPU_AV1

TP_CPU_AW2

PROC_TRIGIN_CPU

PROC_TRIGOUT_CPU

TP_CPU_L12

TP_CPU_K12

CPU1J

CPU1J

J8

RSVD_TP_J8

J7

RSVD_TP_J7

L8

RSVD_TP_L8

K8

RSVD_TP_K8

AV1

RSVD_TP_AV1

AW2

RSVD_TP_AW2

H8

RSVD_H8

K10

RSVD_K10

L10

RSVD_L10

J17

RSVD_J17

B39

RSVD_B39

J19

RSVD_J19

C40

RSVD_C40

G8

RSVD_G8

AY3

RSVD_AY3

D1

PROC_TRIGIN

B3

PROC_TRIGOUT

L12

RSVD_L12

K12

RSVD_K12

SKYLAKE-1

SKYLAKE-1

FOXCONN: 062.10015.0081

LOTES: 062.10015.0111

SKYLAKE

SKYLAKE

LGA1151

LGA1151

10 OF 12

10 OF 12

RSVD_TP_H11

RSVD_TP_H12

RSVD_TP_AW38

RSVD_TP_AV39

RSVD_AU39

RSVD_AU40

VSS_AT15

VSS_AR23

VSS_AR22

RSVD_J15

RSVD_J14

RSVD_AU9

RSVD_AU10

RSVD_J13

RSVD_K13

RSVD_J11

RSVD_D15

RSVD_K11

H11

H12

AW38

AV39

AU39

AU40

AT15

AR23

AR22

J15

J14

AU9

AU10

J13

K13

J11

D15

K11

1

TP_CPU_H11

TP_CPU_H12

TP_CPU_AW38

TP_CPU_AV39

TP_CPU_AU39

TP_CPU_AU40

TP_CPU_K13

12

R901

R901

560_5%

560_5%

0402

0402

(R_)

(R_)

A A

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU (VSS)

CPU (VSS)

CPU (VSS)

S

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

9 107Wednesday, September 23, 2015

9 107Wednesday, September 23, 2015

9 107Wednesday, September 23, 2015

-1

-1

-1

5

4

3

2

1

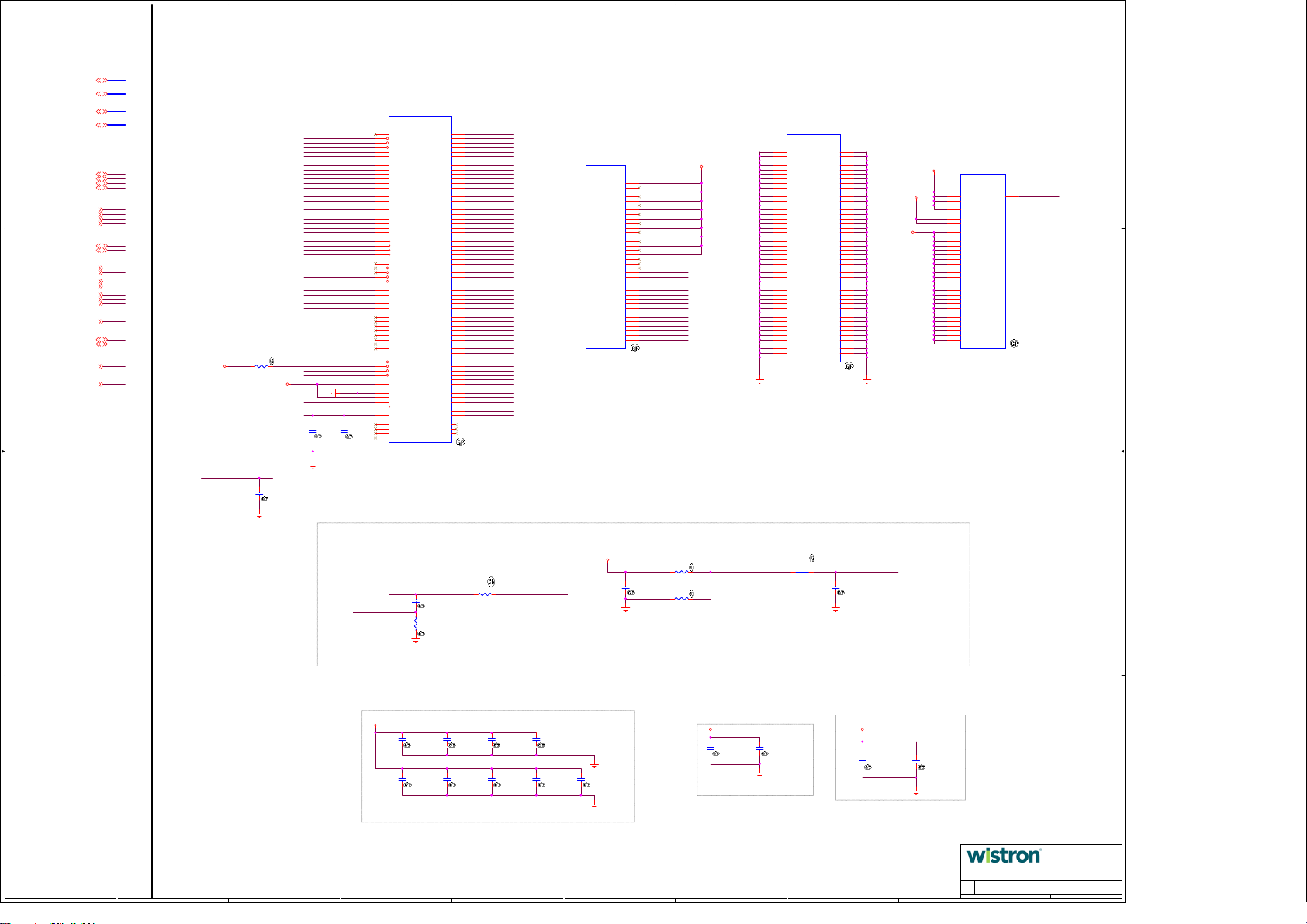

VCC_CORE

12

D D

12

PLACE ALL CAPS INSIDE CPU SOCKET CAVITY ON TOPSIDE

VCC_SA

12

C1091

C1091

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

C C

VDDQ

12

C1093

C1093

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1092

C1092

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

VDDQ

CAPS FOR DIMM

12

C1050

C1050

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

PLACE ALL CAPS SOCKET EDGE TOP

12

C1094

C1094

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1051

C1051

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1095

C1095

VCC_SA

12

C1097

C1097

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

C1099

C1099

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1052

C1052

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1096

C1096

(R_)

(R_)

1 2

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1098

C1098

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

C1053

C1053

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

VCC_CORE

12

C1037

C1037

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

CAD NOTE:

PLACE ALL ABOVE CAPS

ON TOP SIDE OF CPU CAVITY

GFX_CORE

12

12

C1020

C1020

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1030

C1030

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

CAD NOTE:

PLACE ALL BELLOW CAPS

ON BOTTOM SIDE NEAR CPU SOCKET

12

C1038

C1038

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PLACE CAPS AT

SOCKET EDGE 6 ON TOP & 6 ON BOTTOM

C1075

C1075

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

12

C1025

C1025

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1031

C1031

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1039

C1039

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

12

C1070

C1070

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

12

C1026

C1026

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1032

C1032

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1040

C1040

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

C1027

C1027

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

C1033

C1033

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1041

C1041

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

12

C1028

C1028

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1034

C1034

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

(R_)

(R_)

12

C1042

C1042

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

VCC_CORE

GFX_CORE

12

C1064

C1064

SC47U6D3V5MX-1-GP

SC47U6D3V5MX-1-GP

(R_)

(R_)

12

12

VCC_CORE

12

C1004

C1004

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1014

C1014

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

CAD NOTE:

PLACE ALL ABOVE CAPS

ON TOP SIDE OF CPU CAVITY

12

C1043

C1043

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

CAD NOTE:

PLACE CAPS AT

TOP SOCKET EDGE

12

C1005

C1005

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1015

C1015

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1044

C1044

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1006

C1006

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1016

C1016

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1045

C1045

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1007

C1007

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1017

C1017

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1046

C1046

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

PLACE CAPS ON BACKSIDE UNDER SOCKET CAVITY

12

C1065

C1065

SC47U6D3V5MX-1-GP

SC47U6D3V5MX-1-GP

(R_)

(R_)

12

C1067

C1067

SC47U6D3V5MX-1-GP

SC47U6D3V5MX-1-GP

(R_)

(R_)

12

C1059

C1059

SC47U6D3V5MX-1-GP

SC47U6D3V5MX-1-GP

(R_)

(R_)

12

C1008

C1008

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1018

C1018

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1047

C1047

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1062

C1062

SC47U6D3V5MX-1-GP

SC47U6D3V5MX-1-GP

(R_)

(R_)

12

C1009

C1009

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1019

C1019

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1063

C1063

SC47U6D3V5MX-1-GP

SC47U6D3V5MX-1-GP

(R_)

(R_)

B B

PLACE ALL CAPS INSIDE CPU SOCKET CAVITY ON TOPSIDE

VCC_IO

C1129

C1129

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

1 2

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1124

C1124

12

C1125

C1125

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1126

C1126

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1127

C1127

12

C1128

C1128

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

GFX_CORE

12

PLACE CAPS ON TOP SIDE

SOCKET CAVITY

C1077

C1077

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1081

C1081

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

GFX_CORE

12

C1088

C1088

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

12

C1089

C1089

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

(R_)

(R_)

GFX_CORE

PLACE CAPS ON TOP SIDE

SOCKET CAVITY

12

C1056

C1056

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1054

C1054

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1058

C1058

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1068

C1068

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

PLACE ALL CAPS OUTSIDE CPU SOCKET CAVITY ON TOPSIDE

1V_VCCST_VCCPLL_S 3

C1048

C1048

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

5

12

C1049

C1049

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

(78.1052 3.5FL)

(78.1052 3.5FL)

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU Power CAP

CPU Power CAP

CPU Power CAP

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Custom

Custom

Custom

vHulk

vHulk

vHulk

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai W u Rd

21F, 88, Sec.1,Hsin Tai W u Rd

21F, 88, Sec.1,Hsin Tai W u Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

10 107Wednesday, S eptember 23 , 2015

10 107Wednesday, S eptember 23 , 2015

10 107Wednesday, S eptember 23 , 2015

-1

-1

-1

12

A A

CAD NOTE:

PLACE CAPS AT

TOP SOCKET EDGE

5

4

3

2

1

CHANNEL B -- DIMM1

1 OF 4

1 OF 4

DIMM1A

DIMM1A

DIMM288_DDR4

DIMM288_DDR4

1/4

D D

C C

M_B_A[0..1 6]6,13

M_DATA_ B[0..63]6,13

M_B_DQS _DN[0..7]6,13

M_B_DQS _DP[0..7]6,13

M_BA_B_ 16,13

M_BA_B_ 06,13

M_BG_B_ 16,13

M_BG_B_ 06,13

M_B_CLK 36

M_B_CLK #36

M_B_CLK 26

M_B_CLK #26

M_B_CS# 36

M_B_CS# 26

M_B_CKE 36

M_B_CKE 26

M_PARIT Y_B6,13

M_ALERT _B_N6,13

M_ACT_B _N6,13

M_B_ODT 36

M_B_ODT 26

SM_DRAMR ST#_R12,13,14,20

SMB_DAT A_MAIN1 2,13,14,2 0,59,93,9 4

SMB_CLK _MAIN12,13 ,14,20,59 ,93,94

DIMM_CHB_V REF_C A13

M_VREF_ DQ_DIM16

R31133 240R2 F-1-GPR31133 240R2 F-1-GP

VDDQ

SM_DRAMR ST#_R

1 2

3D3V_S 0

12

C2012

C2012

SCD1U16 V2KX-3G P

SCD1U16 V2KX-3G P

(R_)

(R_)

M_B_A16

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

M_BA_B_ 1

M_BA_B_ 0

M_BG_B_ 1

M_BG_B_ 0

M_B_CLK 3

M_B_CLK #3

M_B_CLK 2

M_B_CLK #2

M_B_CS# 3

M_B_CS# 2

M_B_CKE 3

M_B_CKE 2

M_B_ODT 3

M_B_ODT 2

M_PARIT Y_B

SM_DRAMR ST#_R

DIMM1_EV ENT_N

M_ALERT _B_N

M_ACT_B _N

SMB_DAT A_MAIN

SMB_CLK _MAIN

DIMM_CHB_V REF_C A

12

C1134

C1134

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C15172

C15172

SC2D2U10V2KX-GP

SC2D2U10V2KX-GP

(R_)

(R_)

234

82

86

228

232

65

210

225

66

68

211

69

213

214

71

216

72

79

224

81

207

63

218

219

74

75

235

237

93

89

84

203

60

91

87

199

54

192

47

201

56

194

49

222

58

78

208

62

284

238

140

139

285

141

146

144

230

227

205

DDR4-28 8P-82-GP

DDR4-28 8P-82-GP

(022.100 10.0771 )

(022.100 10.0771 )

A17

A16_RAS#

A15_CAS#

A14_WE#

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

BA1

BA0

BG1

BG0

CK1

CK1#

CK0

CK0#

C2

S3#_C1

S2#_C0

S1#

S0#

CKE1

CKE0

ODT1

ODT0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

PAR

RESET#

EVENT#

ALERT#

ACT#

VDDSPD

SA2

SA1

SA0

SDA

SCL

VREFCA

RFU#144

RFU#230

RFU#227

RFU#205

1/4

280

M_DATA_ B63

DQ63

135

M_DATA_ B62

DQ62

273

M_DATA_ B61

DQ61

128

M_DATA_ B60

DQ60

282

M_DATA_ B59

DQ59

137

M_DATA_ B58

DQ58

275

M_DATA_ B57

DQ57

130

M_DATA_ B56

DQ56

269

M_DATA_ B55

DQ55

124

M_DATA_ B54

DQ54

262

M_DATA_ B53

DQ53

117

M_DATA_ B52

DQ52

271

M_DATA_ B51

DQ51

126

M_DATA_ B50

DQ50

264

M_DATA_ B49

DQ49

119

M_DATA_ B48

DQ48

258

M_DATA_ B47

DQ47

113

M_DATA_ B46

DQ46

251

M_DATA_ B45

DQ45

106

M_DATA_ B44

DQ44

260

M_DATA_ B43

DQ43

115

M_DATA_ B42

DQ42

253

M_DATA_ B41

DQ41

108

M_DATA_ B40

DQ40

247

M_DATA_ B39

DQ39

102

M_DATA_ B38

DQ38

240

M_DATA_ B37

DQ37

95

M_DATA_ B36

DQ36

249

M_DATA_ B35

DQ35

104

M_DATA_ B34

DQ34

242

M_DATA_ B33

DQ33

97

M_DATA_ B32

DQ32

188

M_DATA_ B31

DQ31

43

M_DATA_ B30

DQ30

181

M_DATA_ B29

DQ29

36

M_DATA_ B28

DQ28

190

M_DATA_ B27

DQ27

45

M_DATA_ B26

DQ26

183

M_DATA_ B25

DQ25

38

M_DATA_ B24

DQ24

177

M_DATA_ B23

DQ23

32

M_DATA_ B22

DQ22

170

M_DATA_ B21

DQ21

25

M_DATA_ B20

DQ20

179

M_DATA_ B19

DQ19

34

M_DATA_ B18

DQ18

172

M_DATA_ B17

DQ17

27

M_DATA_ B16

DQ16