1

1

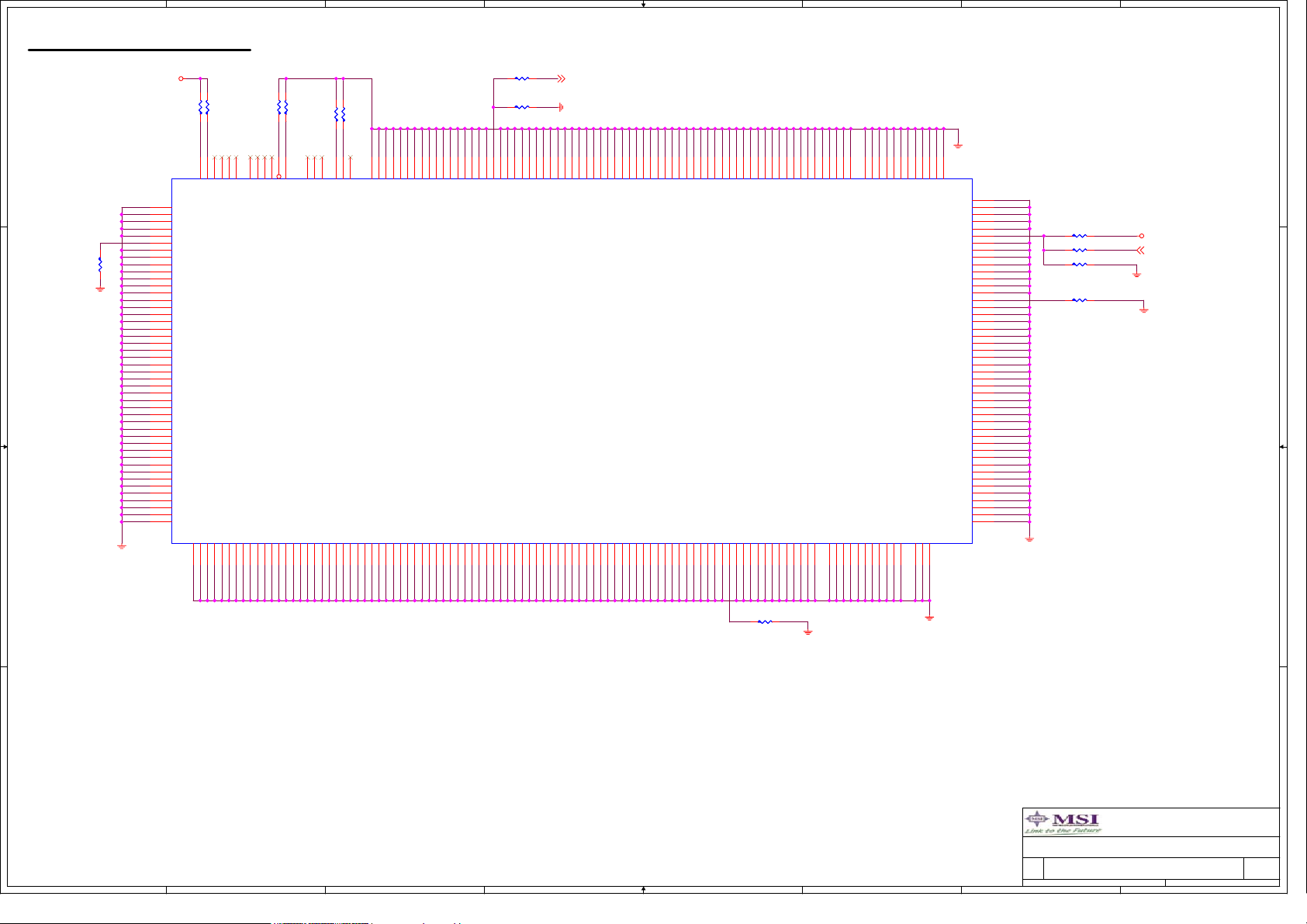

Cover Sheet

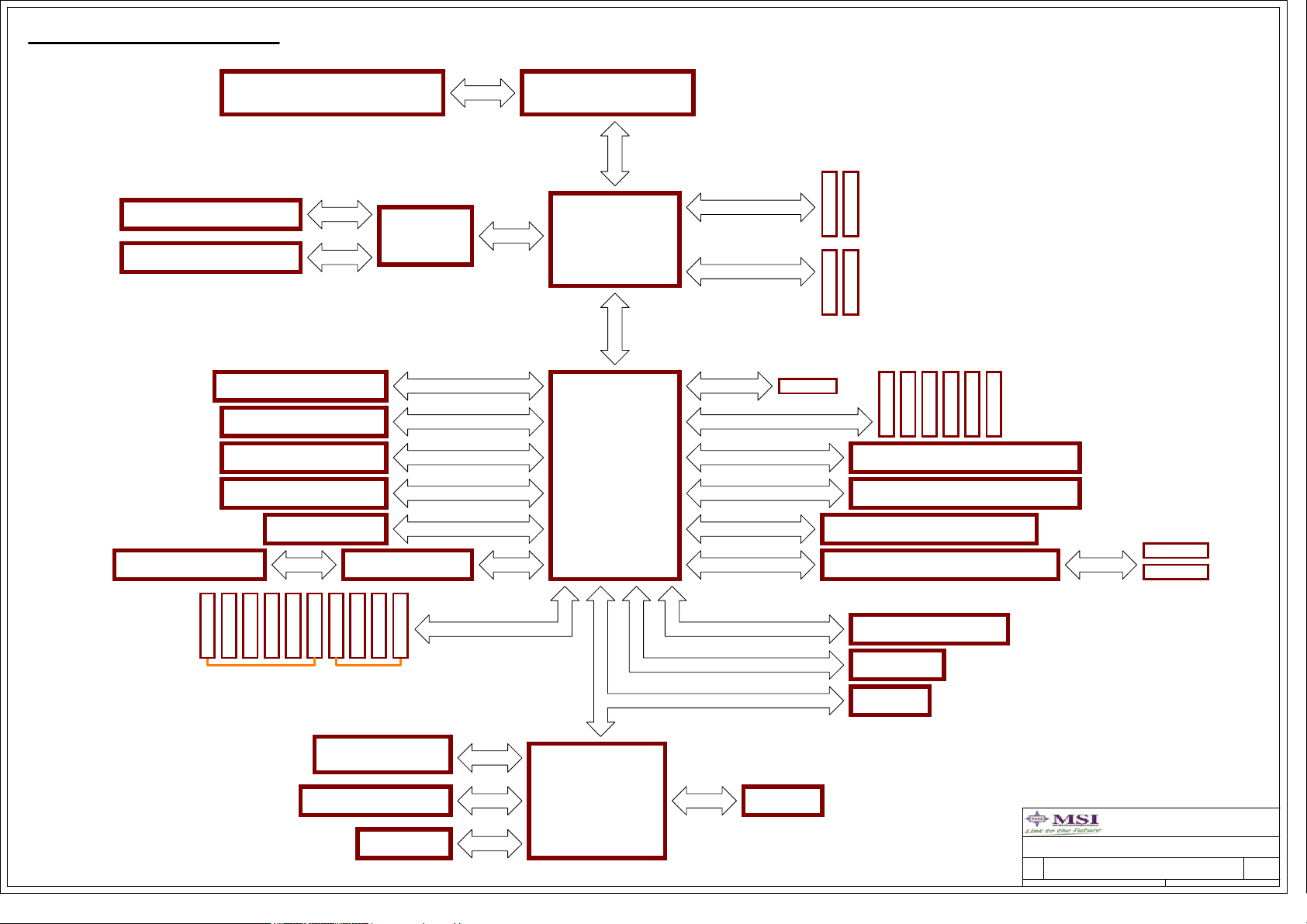

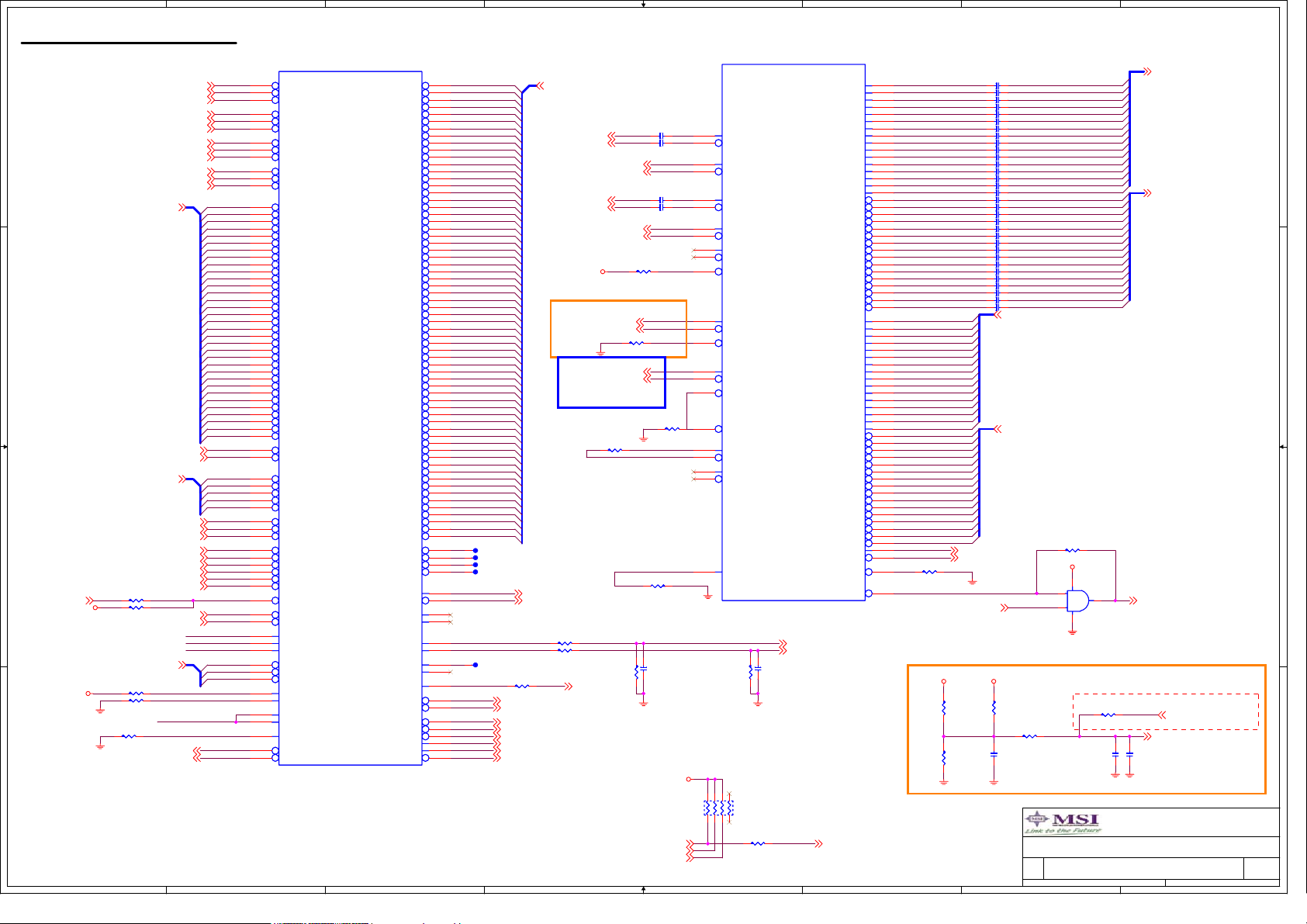

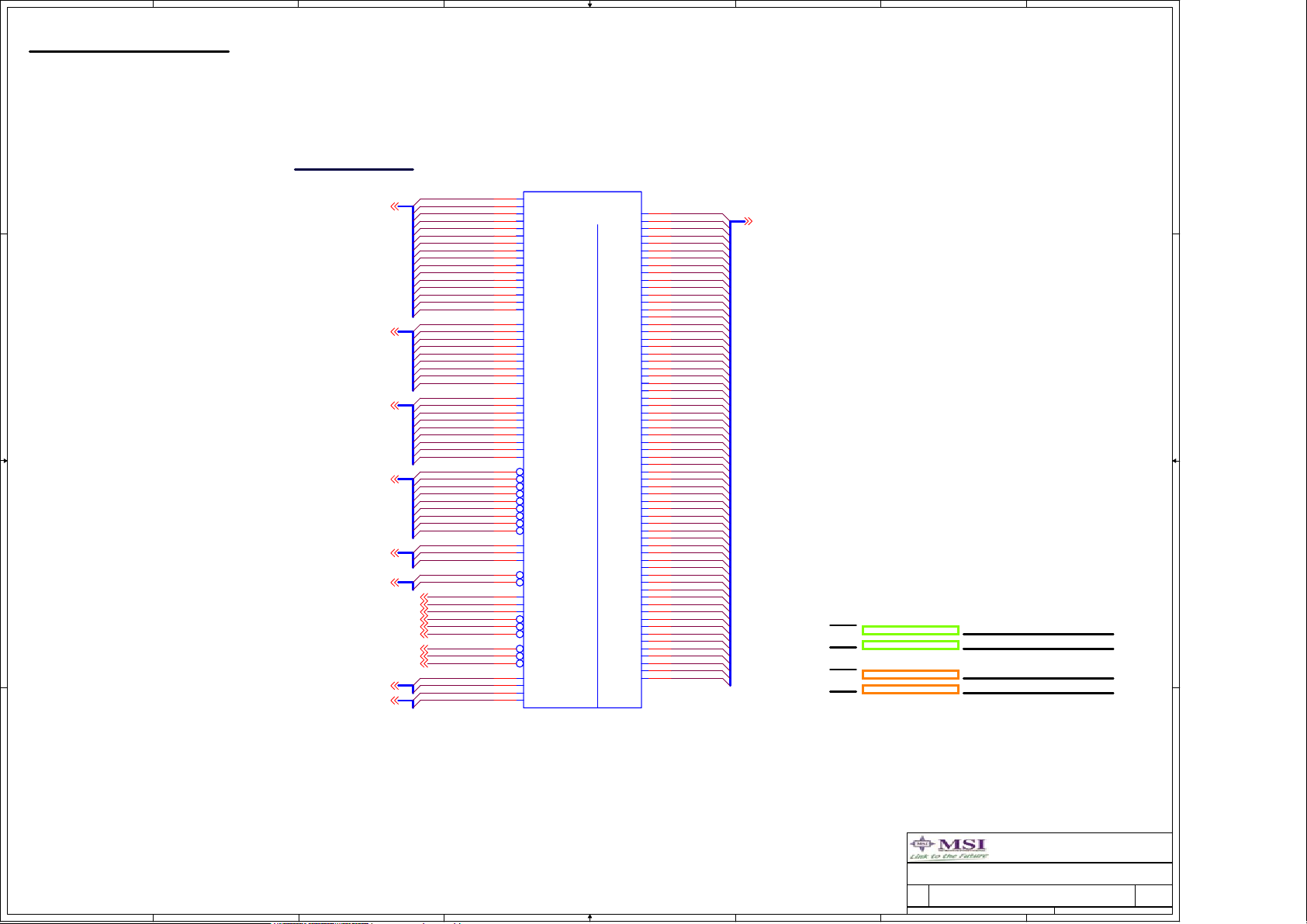

2 System Block Diagram

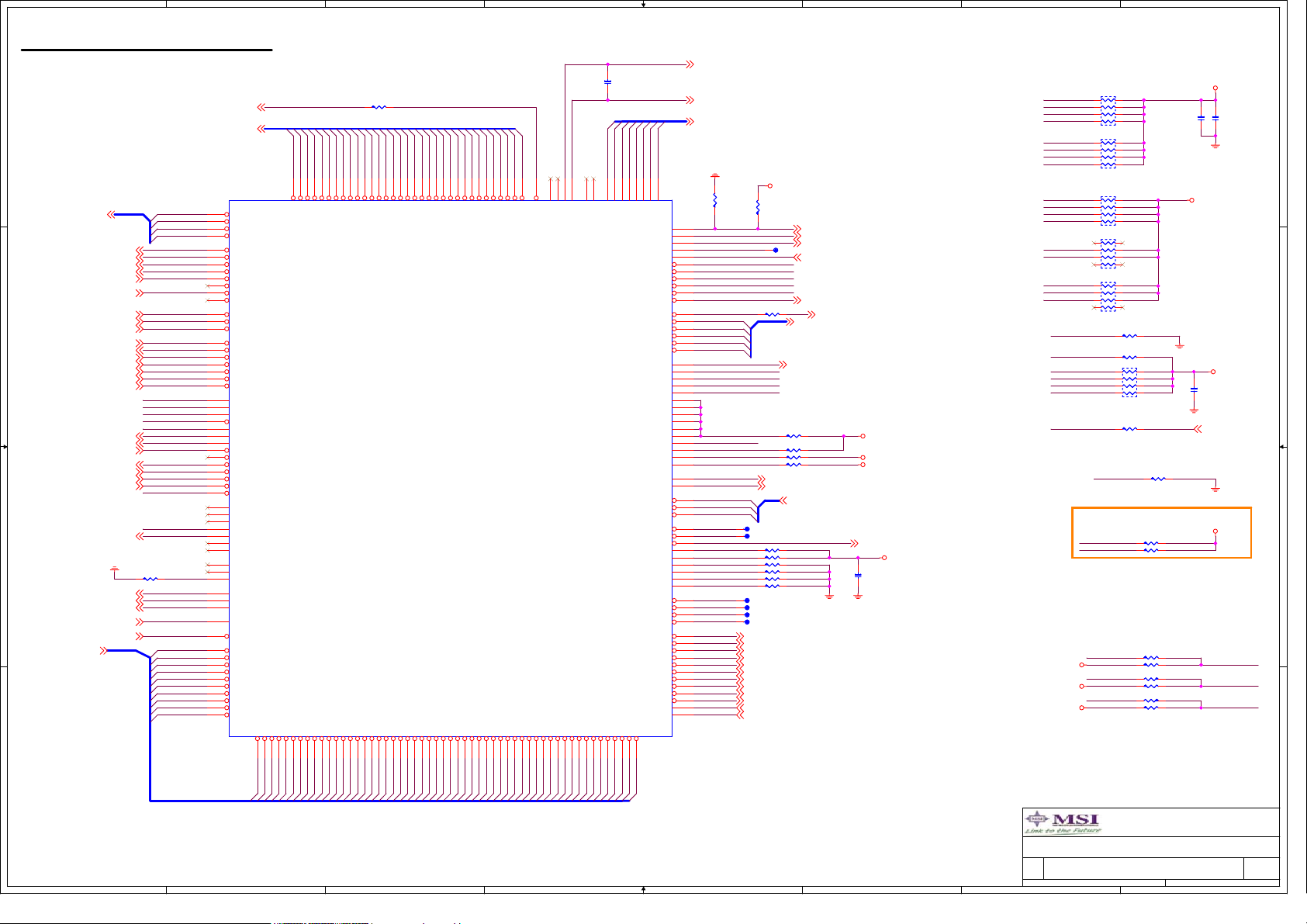

Intel LGA775 CPU - Signals

3

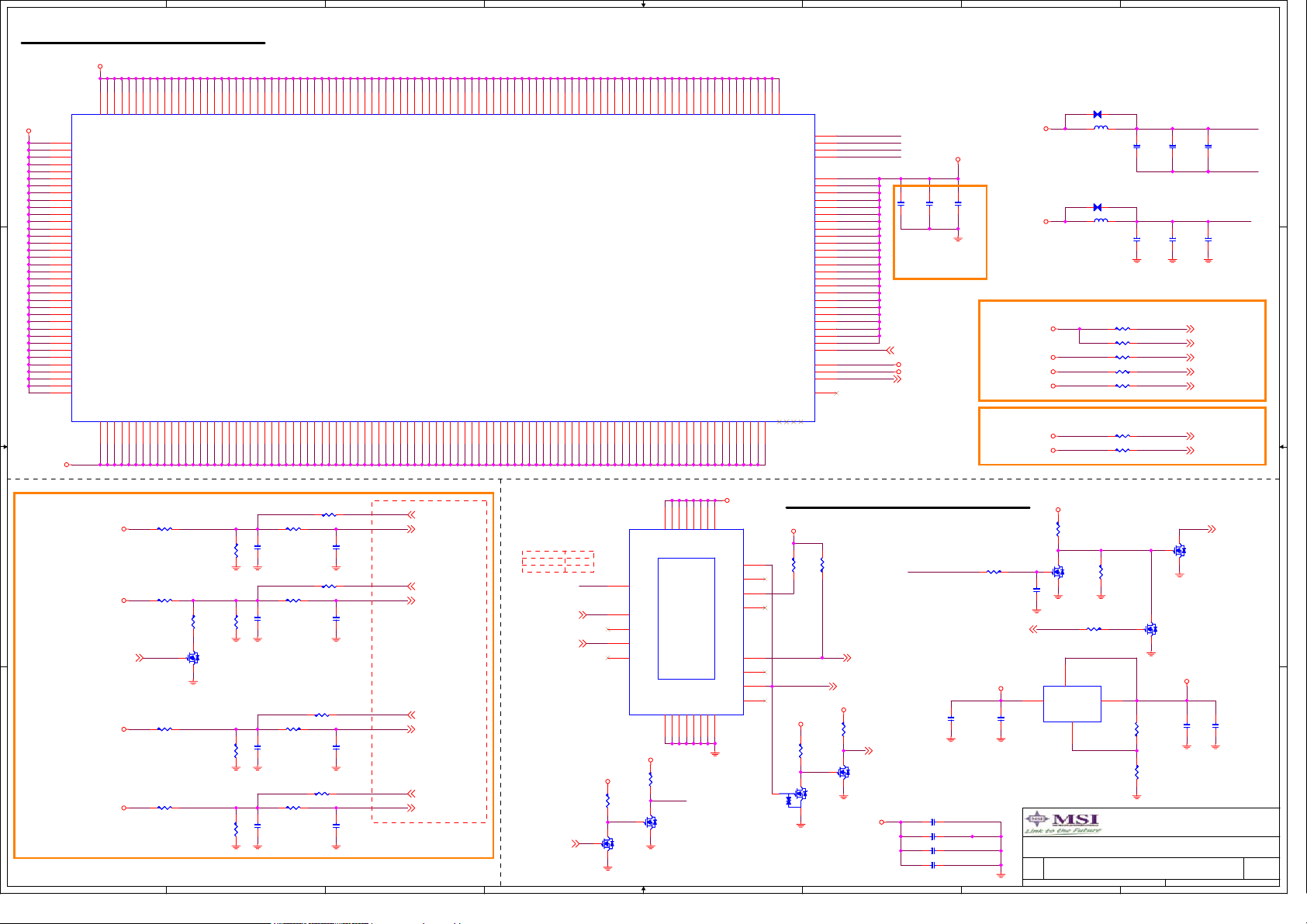

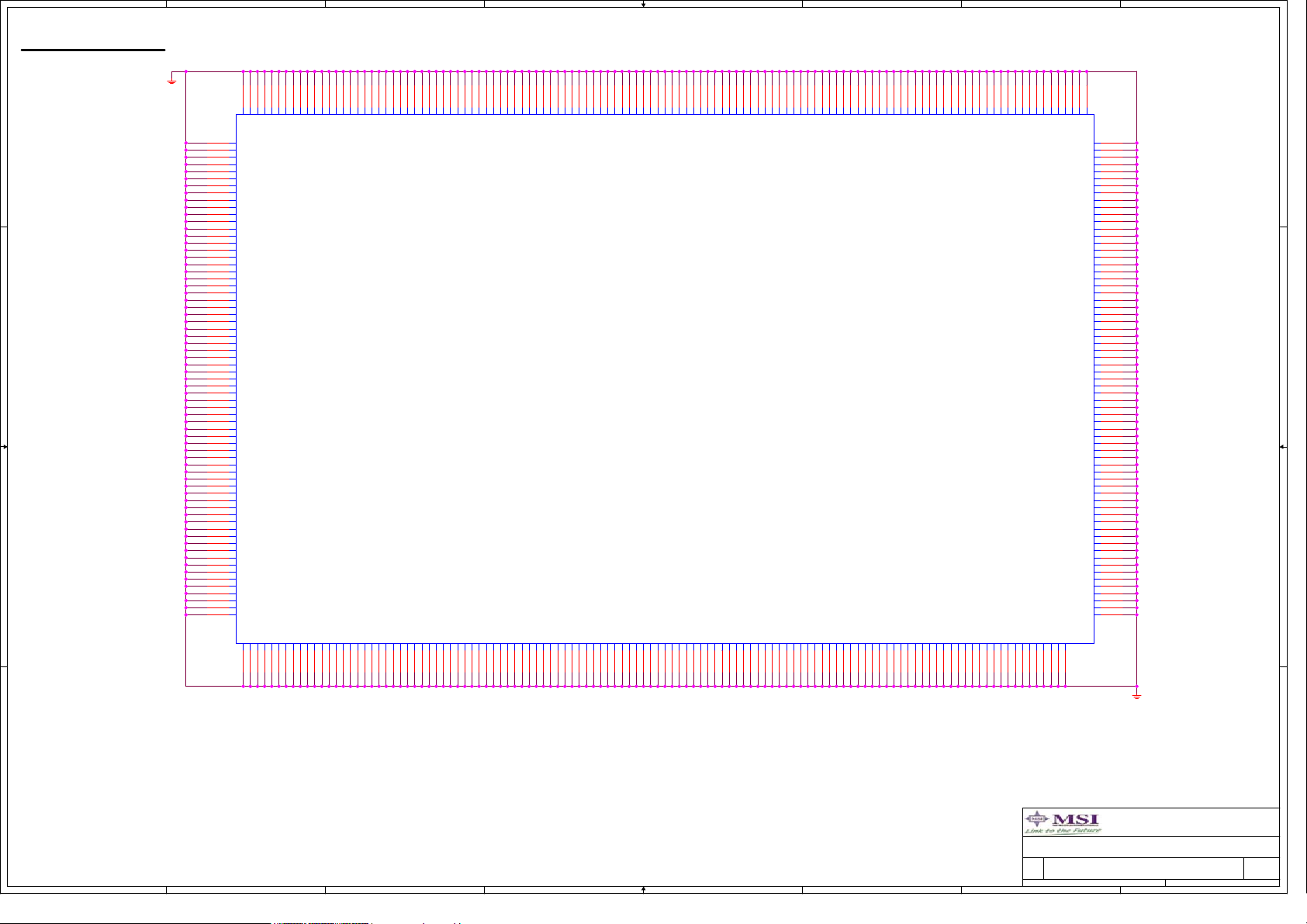

Intel LGA775 CPU - Power

4

5

Intel LGA775 CPU - GND

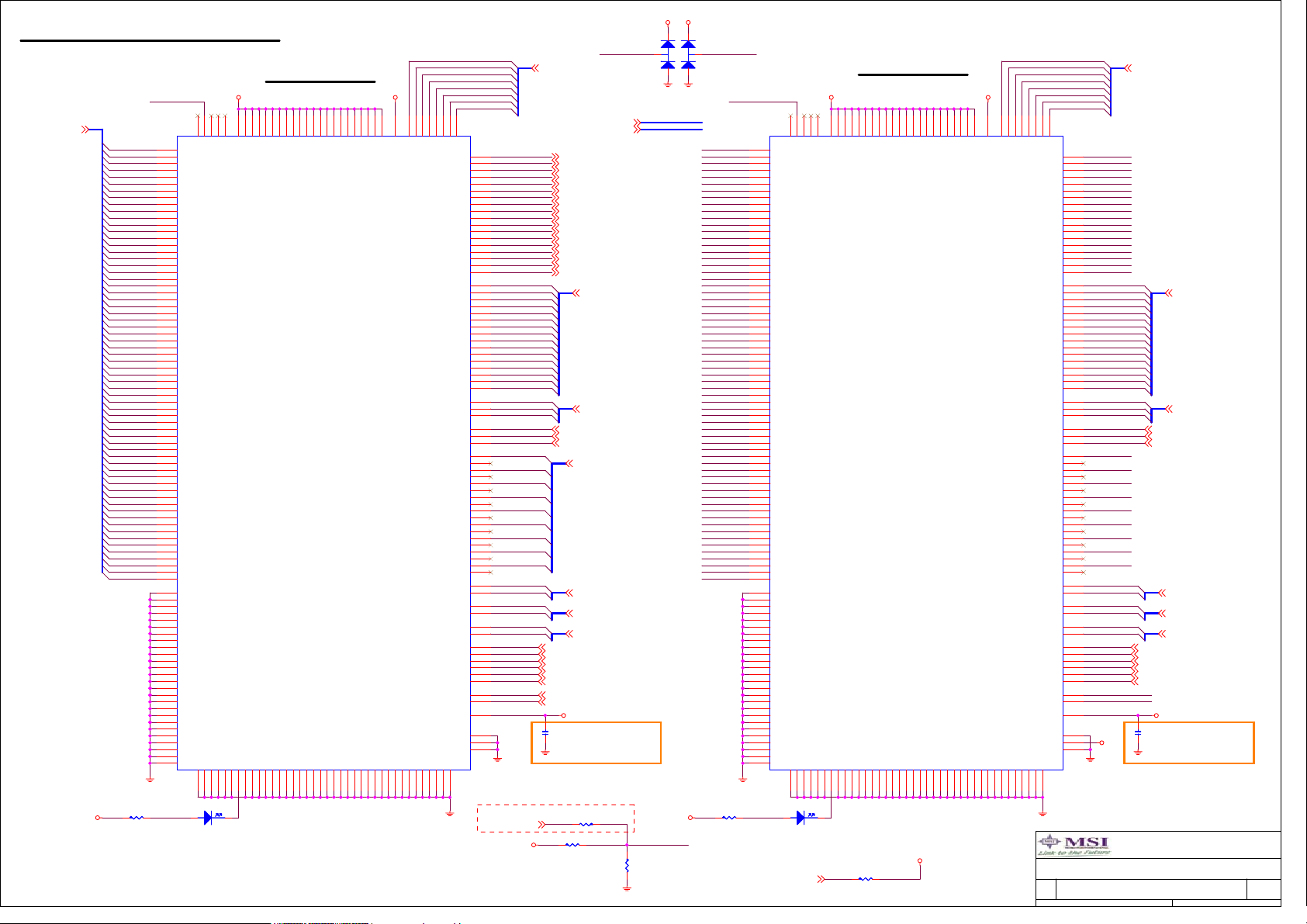

nVidia C55 - CPU / PCI-E

6

7

nVidia C55 - HT Link / Power

8

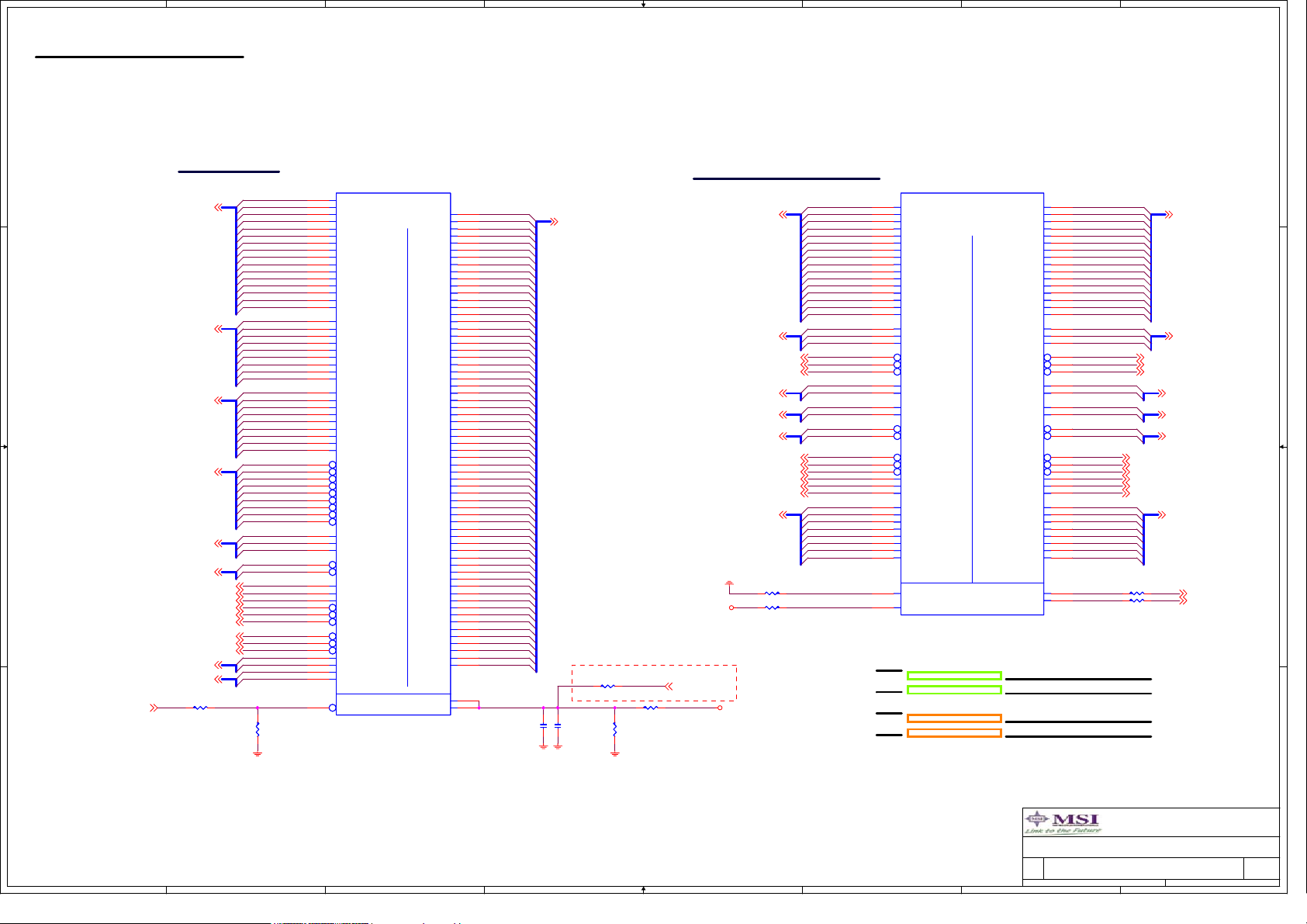

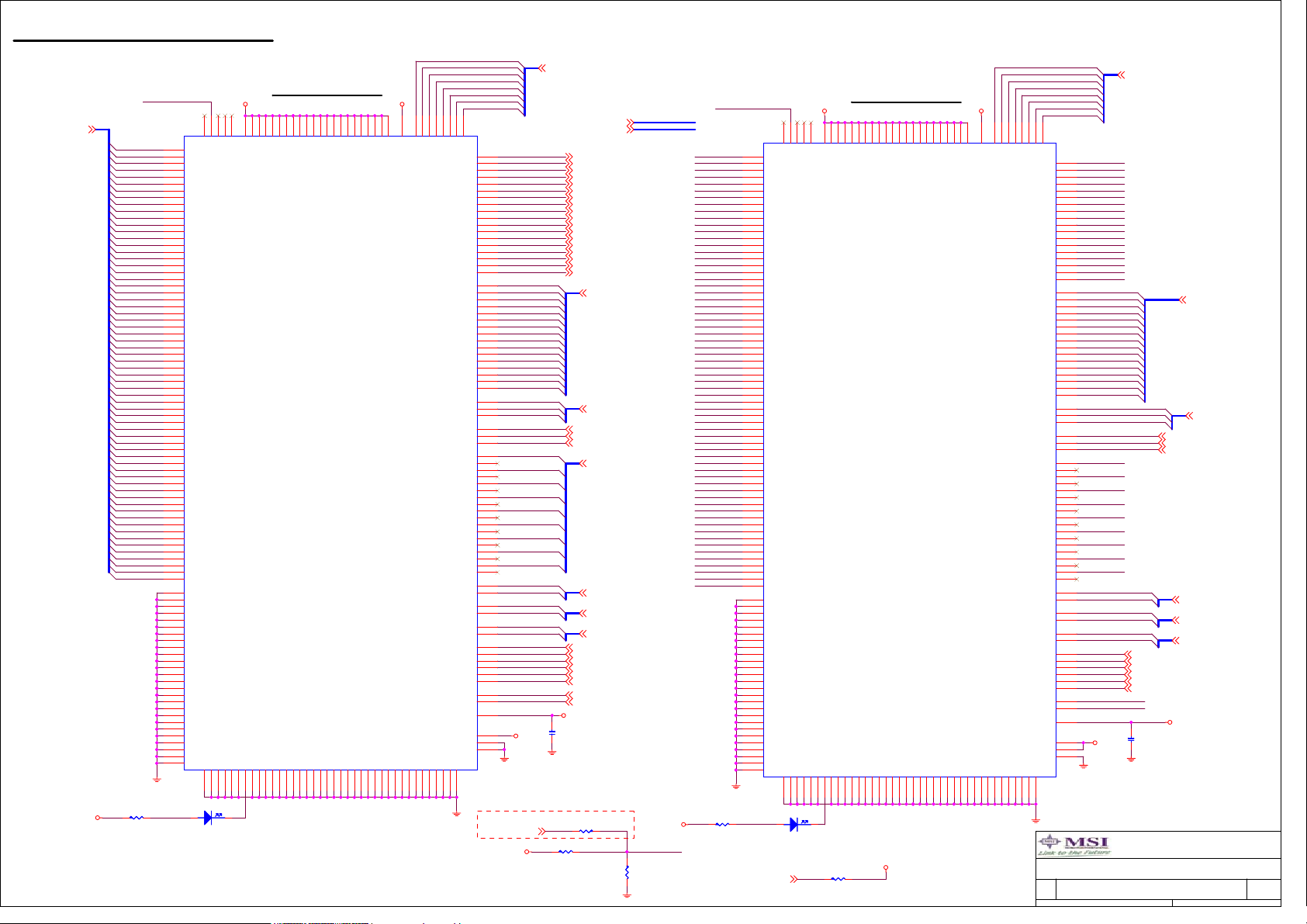

nVidia C55 - Memory A0

9

nVidia C55 - Memory A1

nVidia C55 - Gnd

10

11

DDR II DIMM 1 & 2

12

DDR II DIMM 3 & 4

13

DDR II Termination / EMI

14

nVidia BR04 - C55 Side

15

nVidia BR04 - PCIE x16 Slot

16

nVidia BR04 - Power / Gnd

nVidia MCP55 - HT / PCI / LPC

17

nVidia MCP55 - PCI-E

18

nVidia MCP55 - SATA / IDE / RGMII

19

nVidia MCP55 - Audio / USB / GPIO

20

nVidia MCP55 - PWR & GND

21

22

A A

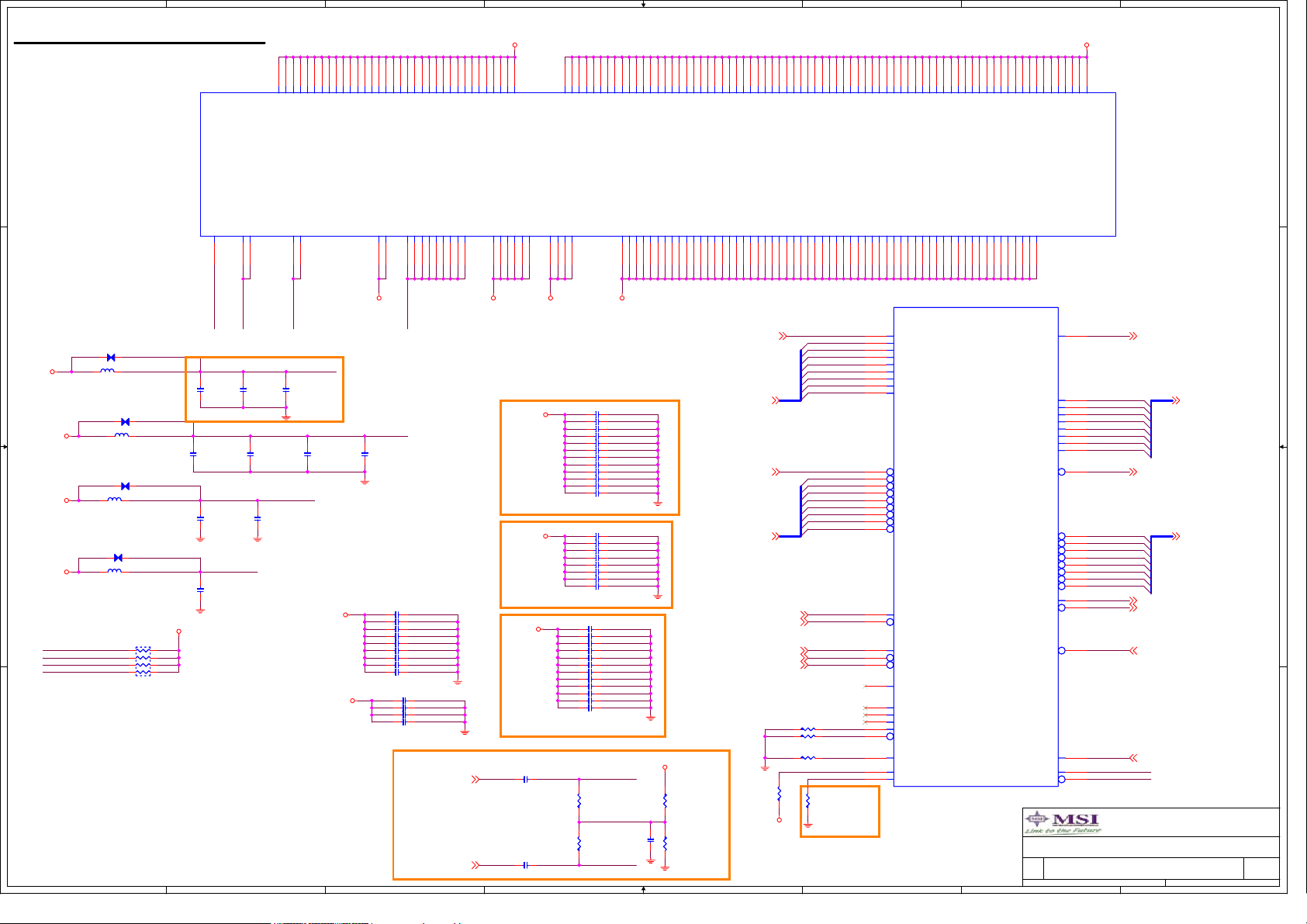

NB PCI-E x16 Pri / Sec Slot

SB PCI-E x16 Pri / Sec Slot

23

SB PCI-E x1 / PCI Slot

24

Gigabit LAN-MARVELL/88E8056

25

26

1394 Controller - JMB381

27

Azalia Codec - ALC888S

28

JMicron JMB363

29

Super I/O - ITE/IT8718F

30

Fan Controller

uPI ACPI Solution

31

32

uPI Power Regulator

33

VRD11- ISL6322 4 Phase 2 Channel

34

Front / Rear USB Connectors

35

ATX / Front Panel / LED

36

Audio De-Pop Circuit

37

Manual Parts

Power On/Off Sequence

38

39

Syatem Power Map

40

GPIO & Jumper Setting

41

System Reset Map

MS-7510

CPU :

Intel Wolfield Family and Yorkfield Family Processor

Intel Conroe Family and Kentsfield Family Processor

Intel Pentium D Processor 900 and 800 Sequence

Intel Pentium 4 Processor 600 and 500 Sequence

System Chipset :

nVidia C72XE [C55 + BR04]

nVidia MCP55P

On Board Chipset :

Azalia Codec -- RealTek ALC888S

GB LAN 1 -- MARVELL/88E8056

GB LAN 2 -- MARVELL/88E8056

VRM 11 -- Intersil ISL6322

ACPI Controller -- uPI Solution

IEEE 1394a Controller -- JMicron JMB381

eSATA Controller -- JMicron JMB363

Super I/O -- ITE/IT8718F

SPI Flash 8Mb

Main Memory :

2 Channel DDR II * 4 (Max 8GB)

Expansion Slot :

PCI Express x16 Slot * 3

PCI Express x8 Slot * 1

PCI Express x1 Slot * 2

PCI Slot * 1

PlatForm or OptionConfig ItemERP No.

C55 + BR04 + MCP55P + ALC888S + MARVELL/88E8056 + JMB381 + JMB363 + ITE/IT8718FCfg-STD7510-01S

Project History42

1

Version : 2.0

Option Select

STD

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

Beetle

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

2.0

2.0

MS-7510

MS-7510

MS-7510

142Thursday, January 10, 2008

142Thursday, January 10, 2008

142Thursday, January 10, 2008

2.0

of

System Block Diagram

1

VRD 11 / 775_VR_Config_05B

Intersil 6322 8 Phase PWM

PCI Express x16 Slot x 1

Gen 2

nVidia BR04

PCI Express x16 Slot x 1

PCI Express x16 Slot x 1

PCI Express x8 Slot x 1

A A

PCI Express x1 Slot x 1

Gen 2

PCI Express Interface

PCI Express Interface

PCI Express Interface

Intel LGA775 Processor

Gen 1

nVidia Crush 55

FSB 800/1066/1333MHz

HT Bus

ATA133

Serial ATA 3Gb/s

RGMII Interface

Channel A

Channel B

IDE1

DDR2DDR2

DDR2DDR2

533/667/800 MHz

533/667/800 MHz

SATA2

SATA3

SATA4

SATA5

SATA6

SATA1

MARVELL 88E8056 Gigabit LAN

nVidia MCP55P

PCI Express x1 Slot x 1

PCI 2.2 Slot x 1

uPI ACPI SolutionuPI Power Regulator

PCI Express Interface

PCI Interface

RGMII Interface

PCIE Interface

PCIE Interface

MARVELL 88E8056 Gigabit LAN

JMB381 IEEE1394a Controller

JMicron JMB363 SATA Controller

SATA

eSATA1

eSATA2

10 port USB 2.0

USB 2.0

USB 2.0

USB 2.0

USB 2.0

Front Rear

USB 2.0

USB 2.0

USB 2.0

USB 2.0

USB 2.0

USB 2.0

PS2

Mouse / KeyBoard

Smart Fan Controller

SPI Flash

LPC Interface

Fintek Super I/O

F71882FG

High DEF Audio Link

SPI

LPC Interface

Azalia Codec ALC888

SPI Flash

TPM 1.2

COM Port

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

System Block Diagram

System Block Diagram

System Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

2.0

2.0

MS-7510

MS-7510

MS-7510

242Friday, January 11, 2008

242Friday, January 11, 2008

242Friday, January 11, 2008

2.0

of

of

of

8

7

6

5

4

3

2

1

CPU LGA775 - Signals

VCC_VRM_SENSE 33

C1

C1

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

VID7

VID6

VID5

AM7

AM5

AL4

AJ3

AK3

AN6

VID6#

VID5#

ITP_CLK1

ITP_CLK0

RSVD#AM7

VSS_MB_REGULATION

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A11

A10

H_D#2

H_D#5

H_D#6

H_D#8

H_D#3

H_D#9

H_D#7

H_D#4

VID2

VID3

VID4

AK4

AL6

AM3

VID4#

VID3#

VID2#

VID_SELECT

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

ZIF-SOCKET775-RH,ZIF-SOCKET775_TH-1

ZIF-SOCKET775-RH,ZIF-SOCKET775_TH-1

B4

H_D#0

H_D#1

H_A#31

H_A#32

AH4

AG5

A32#

D45#

E22

G21

H_D#45

H_D#44

H_A#30

AG4

A31#

A30#

D44#

D43#

F21

H_D#43

H_A#28

H_A#29

AG6

AF4

A29#

D42#

F20

E21

H_D#42

H_D#41

R1 X_0R0402R1 X_0R0402

H_A#22

H_A#27

H_A#23

H_A#24

H_A#25

H_A#26

AF5

AB4

AC5

AB5

AA5

AD6

A28#

A27#

A26#

A25#

A24#

A23#

D41#

D40#

D39#

D38#

D37#

D36#

F18

F17

E19

E18

G17

G18

H_D#38

H_D#36

H_D#37

H_D#39

H_D#35

H_D#40

H_A#21

AA4

A22#

A21#

D35#

D34#

E16

H_D#34

H_A#18

H_A#20

H_A#19

A20#Y4A19#Y6A18#W6A17#

D33#

D32#

D31#

E15

G16

G15

H_D#31

H_D#32

H_D#33

H_A#16

H_A#17

H_A#15

H_A#13

H_A#14

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D30#

D29#

D28#

D27#

F15

F14

E13

G14

G13

H_D#29

H_D#28

H_D#30

H_D#26

H_D#27

H_A#12

D26#

D25#

D13

H_D#25

H_A#11

F12

H_D#24

H_A#8

H_A#10

H_A#7

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D24#

D23#

D22#

D21#

F11

E10

D10

H_D#20

H_D#23

H_D#21

H_D#22

H_A#3

H_A#4

H_A#5

H_A#6

L5

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D11

H_D#14

H_D#15

H_D#17

H_D#18

H_D#19

H_D#16

AC2

DBR#

D14#

C12

B12

H_D#13

AN4

AN3

VSS_SENSE

VCC_SENSE

D13#

D12#D8D11#

C11

H_D#12

H_D#10

H_D#11

AN5

VCC_MB_REGULATION

D10#

B10

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

H_A#[3..35]6

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

FP_RST#20,35

U8A

U8A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

H_D#53

D53#

B15

D52#

C14

C15

H_D#51

H_D#52

D51#

D50#

A14

H_D#50

H_A#35

AJ6

D49#

D17

D20

H_D#48

H_D#49

H_A#34

AJ5

A35#

A34#

D48#

D47#

G22

H_D#47

H_A#33

AH5

A33#

D46#

D22

H_D#46

D D

H_DBI#[0..3]6

CPU_GTLREF24

H_IERR#4

H_MERR#6

H_FERR#4,6

H_STPCLK#6

H_INIT#6

H_DBSY#6

H_DRDY#6

C C

B B

A A

H_TRDY#6

H_ADS#6

H_LOCK#6

H_BNR#6

H_HIT#6

H_HITM#6

H_BPRI#6

H_DEFER#6

THERMDA29

THERMDC29

TRMTRIP#4,6

H_PROCHOT#4,6

H_IGNNE#6

H_SMI#6

H_A20M#4

CPU_GTLREF34

CPU_BSEL06

CPU_BSEL16

CPU_BSEL26

H_PWRGD4,6

H_CPURST#4

H_D#[0..63]6

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_TESTHI13

C9_RESERVED

R19 X_0R0402R19 X_0R0402

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

VID1

AL5

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

VID0

AM2

VID1#

VID0#

AN7

H1

H2

H29

E24

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

VSS_VRM_SENSE 33

VID[0..7] 33

R51

R51

X_0R0402

X_0R0402

GTLREF_SEL

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_SST

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

H_RS#2

H_RS#1

H_RS#0

TEST-U3

TEST-U2

H_COMP5

R14 49.9R1%0402R14 49.9R1%0402

H_COMP4

R15 49.9R1%0402R15 49.9R1%0402

H_COMP3

R17 49.9R1%0402R17 49.9R1%0402

H_COMP2

R18 49.9R1%0402R18 49.9R1%0402

H_COMP1

R20 49.9R1%0402R20 49.9R1%0402

H_COMP0

R21 49.9R1%0402R21 49.9R1%0402

TEST-J17

TEST-H16

TEST-H15

TEST-J16

H_ADSTB#1 6

H_ADSTB#0 6

H_DSTBP#3 6

H_DSTBP#2 6

H_DSTBP#1 6

H_DSTBP#0 6

H_DSTBN#3 6

H_DSTBN#2 6

H_DSTBN#1 6

H_DSTBN#0 6

H_NMI 6

H_INTR 6

VTT_OUT_RIGHT

R3

R3

680R0402-RH

680R0402-RH

VRD_VIDSEL 6,33

CPU_GTLREF0 4

CPU_GTLREF1 4

TP1TP1

C55_GTLREF_CPU 6

R4 0R0402R4 0R0402

TP2TP2

TP3TP3

TP4TP4

TP5TP5

TP6TP6

TP7TP7

H_BPM#0 5

H_REQ#[0..4] 6

H_TESTHI12 5

R8 51R0402R8 51R0402

R9 51R0402R9 51R0402

R10 X_130R1%0402R10 X_130R1%0402

R11 X_51R0402R11 X_51R0402

CK_H_CPU# 6

CK_H_CPU 6

H_RS#[0..2] 6

IO_PECI 29

H_BR#0 4,6

V_FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_LEFT

C5

C5

C0.1u25Y0402-RH

C0.1u25Y0402-RH

VID3

VID2

VID1

VID0

VID7

VID6

VID5

VID4

H_BPM#0

H_BPM#1

H_BPM#5

H_BPM#3

H_BPM#4

H_TDO

H_TDI

H_BPM#2

H_TMS

H_TRST#

H_TESTHI12

H_TESTHI1

H_TESTHI11

H_TESTHI13

H_TESTHI10

H_TESTHI13

VTT_OUT_LEFT

VTT_OUT_LEFT

VTT_OUT_LEFT

1

2

3

4

5

6

7

8

RN18P4R-680R RN18P4R-680R

1

2

3

4

5

6

7

8

RN28P4R-680R RN28P4R-680R

1

2

3

4

5

6

7

8

RN38P4R-51R0402 RN38P4R-51R0402

1

2

3

4

5

6

7

8

RN48P4R-51R0402 RN48P4R-51R0402

1

2

3

4

5

6

7

8

RN58P4R-51R0402 RN58P4R-51R0402

R5 51R0402R5 51R0402

R6 51R0402R6 51R0402

1

2

3

4

5

6

7

RN6 8P4R-51R0402RN6 8P4R-51R0402

NVIDIA suggest

Place at C55 End of Route

H_NMI

H_INTR

H_BPM#1

H_BPM#2

H_BPM#3

8

R7 X_0R0402R7 X_0R0402

H_TCK

R12 49.9R1%0402R12 49.9R1%0402

R13 150R1%0402R13 150R1%0402

R16 150R1%0402R16 150R1%0402

R22 X_0R0402R22 X_0R0402

R23 49.9R1%0402R23 49.9R1%0402

R24 X_0R0402R24 X_0R0402

R25 51R0402R25 51R0402

R26 X_0R0402R26 X_0R0402

R27 51R0402R27 51R0402

VTT_OUT_RIGHT

C3

C2

C0.1u25Y0402-RHC2C0.1u25Y0402-RH

VTT_OUT_RIGHT

VTT_OUT_LEFT

C4

C4

C0.1u25Y0402-RH

C0.1u25Y0402-RH

H_SLP 6

VTT_OUT_RIGHT

C9_RESERVED

H_TESTHI9

H_TESTHI8

C0.1u25Y0402-RHC3C0.1u25Y0402-RH

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

CPU LGA775 - Signals

CPU LGA775 - Signals

CPU LGA775 - Signals

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

2.0

2.0

MS-7510

MS-7510

MS-7510

342Saturday, January 12, 2008

342Saturday, January 12, 2008

342Saturday, January 12, 2008

1

2.0

of

of

of

8

7

6

5

4

3

2

1

CPU LGA775 - Power

VCCP

AJ8

AF9

AF8

AF22

AF21

U8B

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

VCCP

AE9

AD8

AC8

AB8

AA8

U8B

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

VCC#AF22

VCC#AF21

VCC#Y30

VCC#Y8

Y8

Y29

Y30

VCC#AF9

VCC#AF8

VCC#Y28

VCC#Y29

Y28

D D

VCCP

C C

AG14

AG12

AG11

VCC#AG14

VCC#AG12

VCC#AG11

VCC#Y25

VCC#Y26

VCC#Y27

Y25

Y26

Y27

AG19

AG18

AG15

VCC#AG19

VCC#AG18

VCC#AG15

VCC#W8W8VCC#Y23

VCC#Y24

Y23

Y24

AG21

VCC#AG21

VCC#W30

W30

AG26

AG25

AG22

VCC#AG26

VCC#AG25

VCC#AG22

VCC#W27

VCC#W28

VCC#W29

W27

W28

W29

AG29

AG28

AG27

VCC#AG29

VCC#AG28

VCC#AG27

VCC#W24

VCC#W25

VCC#W26

W24

W25

W26

AG30

AG9

AG8

VCC#AG9

VCC#AG8

VCC#AG30

VCC#U8

VCC#V8

VCC#W23

V8

U8

W23

AH14

AH12

AH11

VCC#AH14

VCC#AH12

VCC#AH11

VCC#U28

VCC#U29

VCC#U30

U28

U29

U30

AH19

AH18

AH15

VCC#AH19

VCC#AH18

VCC#AH15

VCC#U25

VCC#U26

VCC#U27

U25

U26

U27

AH22

AH21

VCC#AH22

VCC#AH21

VCC#U23

VCC#U24

U23

U24

AH27

AH26

AH25

VCC#AH27

VCC#AH26

VCC#AH25

VCC#T29

VCC#T30

VCC#T8

T8

T29

T30

AH28

AH29

AH30

VCC#AH28

VCC#AH29

VCC#AH30

VCC#T26

VCC#T27

VCC#T28

T26

T27

T28

AH8

AH9

AJ11

VCC#AH8

VCC#AH9

VCC#T24

VCC#T25

T23

T24

T25

AJ12

AJ14

AJ15

VCC#AJ11

VCC#AJ12

VCC#AJ14

VCC#P8

VCC#R8

VCC#T23

P8

N8

R8

AJ18

VCC#AJ15

VCC#AJ18

VCC#N30

VCC#N8

N30

AJ19

AJ21

AJ22

VCC#AJ19

VCC#AJ21

VCC#N28

VCC#N29

N27

N28

N29

AJ25

AJ26

VCC#AJ22

VCC#AJ25

VCC#AJ26

VCC#N25

VCC#N26

VCC#N27

N24

N25

N26

AJ9

AK11

VCC#AJ8

VCC#AJ9

VCC#AK11

VCC#M8

VCC#N23

VCC#N24

M8

N23

AK12

AK14

AK15

VCC#AK12

VCC#AK14

VCC#AK15

VCC#M28

VCC#M29

VCC#M30

M28

M29

M30

AK18

AK19

VCC#AK18

VCC#M27

M26

M27

AK21

AK22

AK25

VCC#AK19

VCC#AK21

VCC#AK22

VCC#M24

VCC#M25

VCC#M26

M23

M24

M25

AK26

AK8

AK9

VCC#AK8

VCC#AK25

VCC#AK26

VCC#K8

VCC#L8

VCC#M23

L8

K8

K30

AL11

AL12

VCC#AK9

VCC#AL11

VCC#AL12

VCC#K28

VCC#K29

VCC#K30

K28

K29

AL14

AL15

AL18

VCC#AL14

VCC#AL15

VCC#K26

VCC#K27

K25

K26

K27

AL19

AL21

AL22

VCC#AL18

VCC#AL19

VCC#AL21

VCC#K24

VCC#K25

K23

K24

AL25

AL26

AL29

VCC#AL22

VCC#AL25

VCC#AL26

VCC#J30

VCC#J8J8VCC#J9J9VCC#K23

J29

J30

AL30

AL8

AL9

VCC#AL8

VCC#AL29

VCC#AL30

VCC#J27

VCC#J28

VCC#J29

J26

J27

J28

AM11

AM12

VCC#AL9

VCC#AM11

VCC#AM12

VCC#J24

VCC#J25

VCC#J26

J24

J25

AM14

AM15

AM18

VCC#AM14

VCC#AM15

VCC#AM18

VCC#J21

VCC#J22

VCC#J23

J21

J22

J23

AM19

AM21

AM22

VCC#AM19

VCC#AM21

VCC#AM22

VCC#J18

VCC#J19

VCC#J20

J18

J19

J20

AM25

AM26

AM29

VCC#AM25

VCC#AM26

VCC#AM29

VCC#J13

VCC#J14

VCC#J15

J13

J14

J15

AM8

AM9

AM30

VCC#AM8

VCC#AM9

VCC#AM30

VCC#J10

VCC#J11

VCC#J12

J10

J11

J12

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCCA

VCC#AN11

VCC#AN12

VCC#AN14

VCC#AN30

VCC#AN8

VCC#AN9

AN8

AN9

AN30

VSSA

VCC#AN15

VCC#AN18

VCC#AN19

VCC#AN21

VCC#AN22

VCCPLL

VCC-IOPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC#AN25

VCC#AN26

VCC#AN29

1122334

4

AN25

AN26

AN29

ZIF-SOCKET775-RH,ZIF-SOCKET775_TH-1

ZIF-SOCKET775-RH,ZIF-SOCKET775_TH-1

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

H_VCCA

H_VSSA

H_VCCPLL

H_VCCA

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C6

C6

Caps For FSB Generic

VTT_PWG 31

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL 31

*TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MILS

*PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

CP1 X_COPPERCP1 X_COPPER

21

L1

L1

CP2 X_COPPERCP2 X_COPPER

21

L3

L3

C1u6.3Y0402-RH

C1u6.3Y0402-RH

C11

C11

X_C1u6.3Y0402-RH

X_C1u6.3Y0402-RH

C16

C16

V_FSB_VTT

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C7

C7

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C8

C8

V_FSB_VTT

VCC1_5

X_10u100mA_0805-RH

X_10u100mA_0805-RH

X_10u100mA_0805-RH

X_10u100mA_0805-RH

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT

V_FSB_VTT

VTT_OUT_LEFT

VTT_OUT_LEFT

R30 X_130R1%0402R30 X_130R1%0402

R32 62R0402R32 62R0402

R33 X_62R0402R33 X_62R0402

R35 150R1%0402R35 150R1%0402

R36 62R0402R36 62R0402

PLACE AT C55 END OF ROUTE

VTT_OUT_RIGHT

V_FSB_VTT

R40 62R0402R40 62R0402

R41 62R0402R41 62R0402

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C12

C12

C0.01u25X0402

C0.01u25X0402

C17

C17

H_PROCHOT# 3,6

H_IERR# 3

H_CPURST# 3

H_PWRGD 3,6

H_BR#0 3,6

TRMTRIP# 3,6

H_FERR# 3,6

H_VCCA

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C13

C13

H_VSSA

H_VCCPLL

C10u6.3X50805-RH-3

C10u6.3X50805-RH-3

C18

C18

CPU GTLREF Voltage Should be 0.628 x VTT

VTT_OUT_RIGHT

B B

VTT_OUT_RIGHT

CPU_GTLREF1_SET29

CPU_GTLREF1_SET = 0

0.628 * VTT_OUT_RIGHT

CPU_GTLREF1_SET = 1

0.569 * VTT_OUT_RIGHT

VTT_OUT_LEFT

A A

V_FSB_VTT

8

R28 57.6R1%0402-RHR28 57.6R1%0402-RH

100R1%0402

100R1%0402

R37 63.4R1%0402R37 63.4R1%0402

R90

R90

357R1%0402

357R1%0402

137R1%0402

137R1%0402

DS

G

Q62

Q62

2N7002S

2N7002S

R42 57.6R1%0402-RHR42 57.6R1%0402-RH

100R1%0402

100R1%0402

R46 57.6R1%0402-RHR46 57.6R1%0402-RH

100R1%0402

100R1%0402

R31

R31

R39

R39

R44

R44

R50

R50

7

R45 0R0402R45 0R0402

R29 10R0402R29 10R0402

C9

C9

C1u6.3Y0402-RH

C1u6.3Y0402-RH

R48 X_0R0402R48 X_0R0402

R38 10R0402R38 10R0402

C14

C14

C1u6.3Y0402-RH

C1u6.3Y0402-RH

R49 0R0402R49 0R0402

R43 10R0402R43 10R0402

C19

C19

C1u6.3Y0402-RH

C1u6.3Y0402-RH

R149 0R0402R149 0R0402

R47 10R0402R47 10R0402

C21

C21

C1u6.3Y0402-RH

C1u6.3Y0402-RH

C10

C10

C220p50N0402

C220p50N0402

C15

C15

C220p50N0402

C220p50N0402

CPU GTL REF Over voltage

Add R45 , R48 , R49 , R149

C20

C20

C220p50N0402

C220p50N0402

C22

C22

C220p50N0402

C220p50N0402

CPU_GTL_REF 31

CPU_GTLREF0 3

CPU_GTL_REF 31

CPU_GTLREF1 3

CPU_GTL_REF 31

CPU_GTLREF2 3

CPU_GTL_REF 31

CPU_GTLREF3 3

6

Function

AN To NB1

AN To NB2

H_CPURST#3

H_A20M#3

PI2PCIE212ZHE_TQFN28-RH

PI2PCIE212ZHE_TQFN28-RH

SB_GPIO1820

5

28

U51

U51

U51_1.8V

DS

GND

GND

GND

GND

1

10

R570

R570

10KR0402

10KR0402

SEL

Q64

Q64

2N7002S

2N7002S

VDD19VDD26VDD

GND

12

SEL

L

H

SEL

2

SEL

4

A0

5

A1

6

A2

7

A3

VCC3

R555

R555

10KR0402

10KR0402

G

DS

G

Q63

Q63

2N7002S

2N7002S

13

VDD

GND

14

9

11

VDD

GND20GND25GND

U51_1.8V

300mA

3

VDD

VDD8VDD

0B1

1B1

2B1

3B1

0B2

1B2

2B2

3B2

GND

27

29

4

CPU_RST# Work Around

VCC1_2

R288

1KR1%0402

R288

1KR1%0402

R91

62R0402

R91

24

23

22

21

18

17

16

15

G

62R0402

H_CPURST#_C55 6

H_A20M#_C55 6

VCC3

VCC5

DS

Q65

Q65

N-DMN2005K-7_SOT23-3-RH

N-DMN2005K-7_SOT23-3-RH

R536

R536

10KR0402

10KR0402

R542

R542

10KR0402

10KR0402

DS

G

Q66

Q66

2N7002S

2N7002S

U51_1.8V

H_CPURST#

SB_GPIO17 20

C923 C0.1u16X0402-2C923 C0.1u16X0402-2

C924 C0.1u16X0402-2C924 C0.1u16X0402-2

C925 C0.1u16X0402-2C925 C0.1u16X0402-2

C926 C0.1u16X0402-2C926 C0.1u16X0402-2

3

R474 X_0R0402R474 X_0R0402

X_C100p50N0402

X_C100p50N0402

SB_GPIO2020

VCC5

C908

C908

C4.7u6.3X5-1

C4.7u6.3X5-1

C879

C879

C0.1u16X0402-2

C0.1u16X0402-2

VCC5

R547

R547

X_10KR0402

X_10KR0402

G

R435

R435

240R1%0402

240R1%0402

R291

R291

100R1%0402

100R1%0402

G

DS

Q69

Q69

X_2N7002S

X_2N7002S

300mA

DS

G

C23

C23

U15

U15

VIN3VOUT

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

R571

R571

X_15KR1%0402

X_15KR1%0402

Q67

Q67

X_2N7002S

X_2N7002S

R549X_0R0402 R549X_0R0402

4

4

2

ADJ/GND

RC1117S_SOT223

RC1117S_SOT223

1

REG_CTRL

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

CPU LGA775 - Power

CPU LGA775 - Power

CPU LGA775 - Power

MS-7510

MS-7510

MS-7510

DS

Q68

Q68

X_2N7002S

X_2N7002S

U51_1.8V

H_BR#0 3,6

C4.7u6.3X5-1

C4.7u6.3X5-1

C878

C878

442Monday, January 14, 2008

442Monday, January 14, 2008

442Monday, January 14, 2008

1

C0.1u16X0402-2

C0.1u16X0402-2

of

of

of

C927

C927

2.0

2.0

2.0

8

CPU LGA775 - Gnd

7

6

5

4

3

2

1

V26

V25

VSS#V26

VSS#V25

VSS#AH6

VSS#AH7

AH6

AH7

V24

V23

VSS#V24

VSS#V23

VSS#AJ10

VSS#AJ13

AJ10

AJ13

AJ16

VSS#U7U7VSS#U1

VSS#AJ16

R52 0R0402R52 0R0402

R57 X_0R0402R57 X_0R0402

T3

U1

R5

VSS#T7T7VSS#T6T6VSS#T3

VSS#R7R7VSS#R5

VSS#AJ17

VSS#AJ20

VSS#AJ23

VSS#AJ24

VSS#AJ27

VSS#AJ28

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

R30

R29

R28

VSS#R30

VSS#R29

VSS#AJ29

VSS#AJ30

AJ4

AJ29

AJ30

H_TESTHI12 3

R27

R26

R25

R24

VSS#R28

VSS#R27

VSS#R26

VSS#R25

VSS#AJ4

VSS#AJ7

VSS#AK10

VSS#AK13

AJ7

AK10

AK13

AK16

R23

R2

VSS#R2

VSS#R24

VSS#R23

VSS#AK16

VSS#AK17

VSS#AK2

AK2

AK17

AK20

P4

P30

P29

VSS#P7P7VSS#P4

VSS#P30

VSS#AK20

VSS#AK23

VSS#AK24

AK23

AK24

AK27

P28

P27

P26

VSS#P29

VSS#P28

VSS#P27

VSS#AK27

VSS#AK28

VSS#AK29

AK28

AK29

AK30

P25

P24

P23

VSS#P26

VSS#P25

VSS#P24

VSS#AK30

VSS#AK5

VSS#AK7

AK5

AK7

AL10

N3

VSS#N7N7VSS#N6N6VSS#N3

VSS#P23

VSS#AL10

VSS#AL13

VSS#AL16

AL13

AL16

AL17

M1

VSS#M7M7VSS#M1

VSS#AL17

VSS#AL20

VSS#AL23

AL20

AL23

AL24

L30

L6

L3

VSS#L7L7VSS#L6

VSS#L30

VSS#AL24

VSS#AL27

VSS#AL28

AL3

AL27

AL28

L29

L28

VSS#L3

VSS#L29

VSS#L28

VSS#AL3

VSS#AL7

VSS#AM1

AL7

AM1

L27

L26

L25

VSS#L27

VSS#L26

VSS#L25

VSS#AM10

VSS#AM13

VSS#AM16

AM10

AM13

AM16

L24

L23

VSS#K7K7VSS#K5

VSS#L24

VSS#L23

VSS#AM17

VSS#AM20

VSS#AM23

AM17

AM20

AM23

K2

K5

J7

VSS#K2

VSS#AM24

VSS#AM27

VSS#AM28

AM24

AM27

AM28

H9

VSS#J4J4VSS#J7

VSS#H9

VSS#AM4

AM4

H7

H8

VSS#H7

VSS#H8

VSS#AN1

VSS#AN10

AN1

AN10

H3

H6

VSS#H3

VSS#H6

VSS#AN13

VSS#AN16

AN13

AN16

AN17

H26

H27

H28

VSS#H27

VSS#H28

VSS#AN17

VSS#AN2

VSS#AN20

AN2

AN20

AN23

H23

H24

H25

VSS#H24

VSS#H25

VSS#H26

VSS#AN23

VSS#AN24

VSS#AN27

AN24

AN27

AN28

H17

H18

H19

H20

H21

H22

H14

VSS#H14

H13

VSS#H13

VSS#H17

VSS#H18

VSS#H19

VSS#H20

VSS#H21

VSS#H22

VSS#H23

VSS#AN28

VSS#B1B1VSS#B11

B11

B14

H12

VSS#H12

H11

VSS#H11

H10

VSS#H10

G1

VSS#G1

F7

VSS#F7

F4

VSS#F4

F22

VSS#F22

F19

VSS#F19

F16

VSS#F16

F13

VSS#F13

F10

VSS#F10

E8

VSS#E8

E29

VSS#E29

E28

VSS#E28

E27

VSS#E27

E26

VSS#E26

E25

VSS#E25

E20

VSS#E20

E2

VSS#E2

E17

VSS#E17

E14

VSS#E14

E11

VSS#E11

D9

VSS#D9

D6

VSS#D6

D5

VSS#D5

D3

VSS#D3

D24

VSS#D24

D21

VSS#D21

D18

VSS#D18

D15

VSS#D15

D12

VSS#D12

C7

VSS#C7

C4

VSS#C4

C24

VSS#C24

C22

VSS#C22

C19

VSS#C19

C16

VSS#C16

C13

VSS#C13

C10

VSS#C10

B8

VSS#B8

B5

VSS#B5

B24

VSS#B24

B20

VSS#B20

B17

VSS#B17

VSS#B14

ZIF-SOCKET775-RH,ZIF-SOCKET775_TH-1

ZIF-SOCKET775-RH,ZIF-SOCKET775_TH-1

R61 51R0402R61 51R0402

R62 X_0R0402R62 X_0R0402

R63 X_0R0402R63 X_0R0402

R64 X_1KR1%0402R64 X_1KR1%0402

VTT_OUT_LEFT

H_BPM#0 3

VTT_OUT_RIGHT

R5551R0402 R5551R0402

E7

RSVD#E5E5RSVD#E6E6RSVD#E7

VSS#AF17

VSS#AF20

VSS#AF23

VSS#AF24

AF20

AF23

AF24

H_COMP8

B13

F23

F6

IMPSEL#

RSVD#F23

VSS#AF25

VSS#AF26

AF25

AF26

AF27

R5624.9R1%0402 R5624.9R1%0402

J3

RSVD#B13

VSS#AF27

VSS#AF28

VSS#AF29

AF3

AF28

AF29

N4

P5

RSVD#J3

RSVD#P5

RSVD#N4

VSS#AF3

VSS#AF30

VSS#AF6

AF6

AF30

R5851R0402 R5851R0402

MSID[1]V1MSID[0]

VSS#AF7

VSS#AG10

AF7

AG10

R6051R0402 R6051R0402

W1

AC4

RSVD#AC4

VSS#AG13

VSS#AG16

VSS#AG17

AG13

AG16

AG17

VSS#Y7Y7VSS#Y5Y5VSS#Y2

VSS#AG20

VSS#AG23

VSS#AG24

AG20

AG23

AG24

Y2

VSS#W7W7VSS#W4

VSS#AG7

VSS#AH1

AH1

AG7

V6

W4

VSS#V7V7VSS#V6

VSS#AH10

VSS#AH13

AH10

AH13

AH16

V3

V30

V29

VSS#V3

VSS#V30

VSS#AH16

VSS#AH17

VSS#AH20

AH17

AH20

AH23

V28

V27

VSS#V29

VSS#V28

VSS#V27

VSS#AH23

VSS#AH24

VSS#AH3

AH3

AH24

R53

R53

R54

R54

D D

R59

R59

X_1KR1%0402

X_1KR1%0402

C C

B B

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

A12

A15

A18

A21

A24

A2

A6

A9

U8C

U8C

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A24

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

49.9R1%0402

49.9R1%0402

H_COMP6

H_COMP7

AE3

COMP6Y3COMP7

VSS#AE29

VSS#AE30

AE5

AE29

AE30

49.9R1%0402

49.9R1%0402

D1

AE4

RSVD#D1

RSVD#AE4

VSS#AE5

VSS#AE7

VSS#AF10

AE7

AF10

E23

D14

RSVD#E23

RSVD#D14

VSS#AF13

VSS#AF16

AF13

AF16

AF17

R65 X_0R0402R65 X_0R0402

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

CPU LGA775 - Gnd

CPU LGA775 - Gnd

CPU LGA775 - Gnd

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

MICRO-START INT'L CO.,LTD.

2.0

2.0

MS-7510

MS-7510

MS-7510

542Saturday, January 12, 2008

542Saturday, January 12, 2008

542Saturday, January 12, 2008

1

2.0

of

of

of

8

7

6

5

4

3

2

1

C55 - CPU / PCI-E

U11A

U11A

CRUSH55

CRUSH55

SEC

SEC

1 OF 8

1 OF 8

CPU I/F

CPU I/F

?

?

CPU_D0*

CPU_D1*

CPU_D2*

CPU_D3*

CPU_D4*

CPU_D5*

CPU_D6*

CPU_D7*

CPU_D8*

CPU_D9*

CPU_D10*

CPU_D11*

CPU_D12*

CPU_D13*

CPU_D14*

CPU_D15*

CPU_D16*

CPU_D17*

CPU_D18*

CPU_D19*

CPU_D20*

CPU_D21*

CPU_D22*

CPU_D23*

CPU_D24*

CPU_D25*

CPU_D26*

CPU_D27*

CPU_D28*

CPU_D29*

CPU_D30*

CPU_D31*

CPU_D32*

CPU_D33*

CPU_D34*

CPU_D35*

CPU_D36*

CPU_D37*

CPU_D38*

CPU_D39*

CPU_D40*

CPU_D41*

CPU_D42*

CPU_D43*

CPU_D44*

CPU_D45*

CPU_D46*

CPU_D47*

CPU_D48*

CPU_D49*

CPU_D50*

CPU_D51*

CPU_D52*

CPU_D53*

CPU_D54*

CPU_D55*

CPU_D56*

CPU_D57*

CPU_D58*

CPU_D59*

CPU_D60*

CPU_D61*

CPU_D62*

CPU_D63*

CPU_DEP0*

CPU_DEP1*

CPU_DEP2*

CPU_DEP3*

CPU_PWRGOOD

CPU_RESET*

CPU_ITP_CLK_P

CPU_ITP_CLK_N

CPU_CLK_N

CPU_CLK_P

CPU_DPSLP*

CPU_DPWR*

CPU_MCERR*

CPU_BPRI*

CPU_DEFER*

CPU_A20M*

CPU_IGNNE*

CPU_INIT*

CPU_INTR

CPU_NMI

CPU_SMI*

6

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

AH2

AG3

AF4

AD5

AD6

AB8

AM5

AM7

AK8

AN3

AN4

AT2

AA2

AB2

AA3

AA1

AC3

AY5

AW5

AV5

AB4

AB3

7

CPU_DSTBP0*

CPU_DSTBN0*

CPU_DBI0*

CPU_DSTBP1*

CPU_DSTBN1*

CPU_DBI1*

CPU_DSTBP2*

CPU_DSTBN2*

CPU_DBI2*

CPU_DSTBP3*

CPU_DSTBN3*

CPU_DBI3*

U6

CPU_A3*

R6

CPU_A4*

R8

CPU_A5*

U5

CPU_A6*

T9

CPU_A7*

P9

CPU_A8*

P3

CPU_A9*

N3

CPU_A10*

P2

CPU_A11*

N2

CPU_A12*

N1

CPU_A13*

N4

CPU_A14*

N9

CPU_A15*

N7

CPU_A16*

M3

CPU_A17*

N8

CPU_A18*

N6

CPU_A19*

N5

CPU_A20*

M2

CPU_A21*

L7

CPU_A22*

M9

CPU_A23*

L4

CPU_A24*

L9

CPU_A25*

L3

CPU_A26*

L5

CPU_A27*

K9

CPU_A28*

J3

CPU_A29*

K3

CPU_A30*

K2

CPU_A31*

J1

CPU_A32*

J2

CPU_A33*

H2

CPU_A34*

J4

CPU_A35*

R5

CPU_ADSTB0*

L6

CPU_ADSTB1*

U9

CPU_REQ0*

V9

CPU_REQ1*

R7

CPU_REQ2*

U7

CPU_REQ3*

U8

CPU_REQ4*

CPU_ADS*

CPU_BNR*

W3

CPU_BR0*

CPU_DBSY*

CPU_DRDY*

W5

CPU_HIT*

Y3

CPU_HITM*

CPU_LOCK*

Y2

CPU_TRDY*

F2

CPU_PROCHOT*

U1

CPU_THERMTRIP*

R4

CPU_FERR*

CPU_BSEL2

CPU_BSEL1

CPU_BSEL0

CPU_RS0*

W4

CPU_RS1*

CPU_RS2*

F3

CPU_DRV0_VTT

F4

CPU_DRV1_GND

G4

CPU_GTL_VREF

H3

CPU_GTL_VREF

G3

CPU_CLK_COMP

U3

CPU_SLP*

R9

CPU_STPCLK*

H_DSTBP#03

H_DSTBN#03

H_DBI#03

H_A#[3..35]3

H_REQ#[0..4]3

H_RS#[0..2]3

H_DSTBP#13

H_DSTBN#13

H_DBI#13

H_DSTBP#23

H_DSTBN#23

H_DBI#23

H_DSTBP#33

H_DSTBN#33

H_DBI#33

H_ADSTB#03

H_ADSTB#13

H_ADS#3

H_BNR#3

H_BR#03,4

H_DBSY#3

H_DRDY#3

H_HIT#3

H_HITM#3

H_LOCK#3

H_TRDY#3

TRMTRIP#3,4

H_FERR#3,4

C55_GTLREF_CPU

H_SLP3

H_STPCLK#3

H_PROCHOT#_R

CPU_BSEL2

CPU_BSEL1

CPU_BSEL0

CPU_DRV0_VTT

CPU_DRV1_GND

CPU_CLK_COMP

D D

C C

B B

H_PROCHOT#3,4

VTT_OUT_RIGHT

VTT_OUT_RIGHT

A A

R75 0R0402R75 0R0402

R74 X_130R1%0402R74 X_130R1%0402

R81 42.2R1%0402R81 42.2R1%0402

R82 42.2R1%0402R82 42.2R1%0402

R85 2.37KR1%0402R85 2.37KR1%0402

8

AD2

AE1

AD3

AE3

AD4

AE2

AF3

AF2

AH4

AJ2

AJ1

AJ3

AH3

AK3

AK4

AK2

AB5

W9

Y9

AA9

W8

AB6

AB7

AB9

AC9

AD7

AD8

AD9

AE9

AF5

AF7

AF6

AF9

AF8

AG9

AK7

AJ9

AH9

AK6

AK5

AK9

AM6

AN6

AR5

AT4

AT5

AU4

AV3

AU3

AP2

AL3

AM2

AM4

AM3

AR3

AN1

AN2

AP3

AU2

AU1

AT3

AR4

AV1

AV2

AH7

AH5

AH6

AH8

T2

AW2

J6

J5

AY3

AW3

J7

J8

L8

W7

W6

V3

U4

T3

V2

U2

R3

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

CPUCLK#

CPUCLK

H_MERR#_R

TP8TP8

TP9TP9

TP10TP10

TP11TP11

H_PWRGD 3,4

H_CPURST#_C55 4

TP12TP12

R80 X_0R0402R80 X_0R0402

H_BPRI# 3

H_DEFER# 3

H_A20M#_C55 4

H_IGNNE# 3

H_INIT# 3

H_INTR 3

H_NMI 3

H_SMI# 3

H_D#[0..63] 3

PEX_TXP1625

PEX_TXN1625

PEX_TXP1725

PEX_TXN1725

VCC2_5

To Clock Buffer clock in

BF_PE_CLK#14

PE_100M_LAN025

PE_100M_LAN0#25

To LAN1 clock in

R76 33R0402R76 33R0402

R77 33R0402R77 33R0402

H_MERR# 3

5

PEX_RXP1625

PEX_RXN1625

PEX_RXP1725

PEX_RXN1725

R66 10KR0402R66 10KR0402

BF_PE_CLK14

R67 10KR0402R67 10KR0402

R68

R68

10KR0402

R70 X_100R1%0402R70 X_100R1%0402

49.9R1%0402

49.9R1%0402

10KR0402

PE_CTERM_GND

R73 2.37KR1%0402R73 2.37KR1%0402

C56

C56

R78

R78

X_C15p50N0402

X_C15p50N0402

V_FSB_VTT

CPU_BSEL23

CPU_BSEL13

CPU_BSEL03

C531C0.1U16X0402 C531C0.1U16X0402

AU14

C532C0.1U16X0402 C532C0.1U16X0402

AV14

AV15

AU15

C533C0.1U16X0402 C533C0.1U16X0402

AY13

C534C0.1U16X0402 C534C0.1U16X0402

AW13

AV13

AW14

AP13

AR13

AM10

AR11

AT11

AN11

AP11

AM11

AN9

AU11

AV11

AR9

AP9

AV12

AT9

49.9R1%0402

49.9R1%0402

246

135

PE_TX16_P

PE_TX16_N

PE_RX16_P

PE_RX16_N

PE_TX17_P

PE_TX17_N

PE_RX17_P

PE_RX17_N

PE1_REFCLK_P

PE1_REFCLK_N

PE1_PRSNT*

PE2_REFCLK_P

PE2_REFCLK_N

PE2_PRSNT*

PE3_REFCLK_P

PE3_REFCLK_N

PE3_PRSNT*

PE3_CLKREQ*

PE_TSTCLK_P

PE_TSTCLK_N

PE_REFCLKIN_P

PE_REFCLKIN_N

PE_CTERM_GND

4

U11B

U11B

CRUSH55

CRUSH55

PCI EXP I/F

PCI EXP I/F

R79

R79

8

RN7

RN7

8P4R-470R0402

8P4R-470R0402

7

R89 X_0R0402R89 X_0R0402

SEC

SEC

2 OF 8

2 OF 8

<PATH>

<PATH>

CK_H_CPU# 3

CK_H_CPU 3

C57

C57

X_C15p50N0402

X_C15p50N0402

PE_TX15_P

PE_TX14_P

PE_TX13_P

PE_TX12_P

PE_TX11_P

PE_TX10_P

PE_TX9_P

PE_TX8_P

PE_TX7_P

PE_TX6_P

PE_TX5_P

PE_TX4_P

PE_TX3_P

PE_TX2_P

PE_TX1_P

PE_TX0_P

PE_TX15_N

PE_TX14_N

PE_TX13_N

PE_TX12_N

PE_TX11_N

PE_TX10_N

PE_TX9_N

PE_TX8_N

PE_TX7_N

PE_TX6_N

PE_TX5_N

PE_TX4_N

PE_TX3_N

PE_TX2_N

PE_TX1_N

PE_TX0_N

PE_RX15_P

PE_RX14_P

PE_RX13_P

PE_RX12_P

PE_RX11_P

PE_RX10_P

PE_RX9_P

PE_RX8_P

PE_RX7_P

PE_RX6_P

PE_RX5_P

PE_RX4_P

PE_RX3_P

PE_RX2_P

PE_RX1_P

PE_RX0_P

PE_RX15_N

PE_RX14_N

PE_RX13_N

PE_RX12_N

PE_RX11_N

PE_RX10_N

PE_RX9_N

PE_RX8_N

PE_RX7_N

PE_RX6_N

PE_RX5_N

PE_RX4_N

PE_RX3_N

PE_RX2_N

PE_RX1_N

PE_RX0_N

PE0_REFCLK_P

PE0_REFCLK_N

PE0_PRSNT*

PE_RESET*

VRD_VIDSEL 3,33

PEX_TXP15

AV28

PEX_TXP14

AV27

PEX_TXP13

AV26

PEX_TXP12

AV25

PEX_TXP11

AY25

PEX_TXP10

AV24

PEX_TXP9

AV23

PEX_TXP8

AV22

PEX_TXP7

AV21

PEX_TXP6

AY21

PEX_TXP5

AV20

PEX_TXP4

AV19

PEX_TXP3

AV18

PEX_TXP2

AV17

PEX_TXP1

AY17

PEX_TXP0

AV16

PEX_TXN15

AW28

PEX_TXN14

AU28

PEX_TXN13

AU27

PEX_TXN12

AW26

PEX_TXN11

AW25

PEX_TXN10

AW24

PEX_TXN9

AU24

PEX_TXN8

AU23

PEX_TXN7

AW22

PEX_TXN6

AW21

PEX_TXN5

AW20

PEX_TXN4

AU19

PEX_TXN3

AU18

PEX_TXN2

AW18

PEX_TXN1

AW17

PEX_TXN0

AW16

PEX_RXCP15

AR24

PEX_RXCP14

AN24

PEX_RXCP13

AM23

PEX_RXCP12

AT22

PEX_RXCP11

AP22

PEX_RXCP10

AM22

PEX_RXCP9

AR19

PEX_RXCP8

AN19

PEX_RXCP7

AM18

PEX_RXCP6

AT17

PEX_RXCP5

AP17

PEX_RXCP4

AM17

PEX_RXCP3

AR15

PEX_RXCP2

AN15

PEX_RXCP1

AM14

PEX_RXCP0

AT13

PEX_RXCN15

AT24

PEX_RXCN14

AP24

PEX_RXCN13

AM24

PEX_RXCN12

AU22

PEX_RXCN11

AR22

PEX_RXCN10

AN22

PEX_RXCN9

AT19

PEX_RXCN8

AP19

PEX_RXCN7

AM19

PEX_RXCN6

AU17

PEX_RXCN5

AR17

PEX_RXCN4

AN17

PEX_RXCN3

AT15

PEX_RXCN2

AP15

PEX_RXCN1

AM15

PEX_RXCN0

AU13

AM13

AN13

R72 10KR0402R72 10KR0402

AU9

PE_RESET_GATE#

AW12

VTT_OUT_RIGHTVTT_OUT_LEFT

3

C24 C0.1u16Y0402C24 C0.1u16Y0402

C25 C0.1u16Y0402C25 C0.1u16Y0402

C26 C0.1u16Y0402C26 C0.1u16Y0402

C27 C0.1u16Y0402C27 C0.1u16Y0402

C28 C0.1u16Y0402C28 C0.1u16Y0402

C29 C0.1u16Y0402C29 C0.1u16Y0402

C30 C0.1u16Y0402C30 C0.1u16Y0402

C31 C0.1u16Y0402C31 C0.1u16Y0402

C32 C0.1u16Y0402C32 C0.1u16Y0402

C33 C0.1u16Y0402C33 C0.1u16Y0402

C34 C0.1u16Y0402C34 C0.1u16Y0402

C35 C0.1u16Y0402C35 C0.1u16Y0402

C36 C0.1u16Y0402C36 C0.1u16Y0402

C37 C0.1u16Y0402C37 C0.1u16Y0402

C38 C0.1u16Y0402C38 C0.1u16Y0402

C39 C0.1u16Y0402C39 C0.1u16Y0402

C40 C0.1u16Y0402C40 C0.1u16Y0402

C41 C0.1u16Y0402C41 C0.1u16Y0402

C42 C0.1u16Y0402C42 C0.1u16Y0402

C43 C0.1u16Y0402C43 C0.1u16Y0402

C44 C0.1u16Y0402C44 C0.1u16Y0402

C45 C0.1u16Y0402C45 C0.1u16Y0402

C46 C0.1u16Y0402C46 C0.1u16Y0402

C47 C0.1u16Y0402C47 C0.1u16Y0402

C48 C0.1u16Y0402C48 C0.1u16Y0402

C49 C0.1u16Y0402C49 C0.1u16Y0402

C50 C0.1u16Y0402C50 C0.1u16Y0402

C51 C0.1u16Y0402C51 C0.1u16Y0402

C52 C0.1u16Y0402C52 C0.1u16Y0402

C53 C0.1u16Y0402C53 C0.1u16Y0402

C54 C0.1u16Y0402C54 C0.1u16Y0402

C55 C0.1u16Y0402C55 C0.1u16Y0402

PE_BR04_CLK 14

PE_BR04_CLK# 14

ATX_PWR_OK18,20,31,35

R83

R83

100R1%0402

100R1%0402

R87

R87

82.5R1%0402

82.5R1%0402

PEX_TXCP[0..15] 14

PEX_TXCN[0..15] 14

PEX_RESET# 14,25

PEX_RXCP[0..15] 14

PEX_RXCN[0..15] 14

R71 X_0R0402R71 X_0R0402

3VDUAL

1

2

PEX_TXCP15

PEX_TXCP14

PEX_TXCP13

PEX_TXCP12

PEX_TXCP11

PEX_TXCP10

PEX_TXCP9

PEX_TXCP8

PEX_TXCP7

PEX_TXCP6

PEX_TXCP5

PEX_TXCP4

PEX_TXCP3

PEX_TXCP2

PEX_TXCP1

PEX_TXCP0

PEX_TXCN15

PEX_TXCN14

PEX_TXCN13

PEX_TXCN12

PEX_TXCN11

PEX_TXCN10

PEX_TXCN9

PEX_TXCN8

PEX_TXCN7

PEX_TXCN6

PEX_TXCN5

PEX_TXCN4

PEX_TXCN3

PEX_TXCN2

PEX_TXCN1

PEX_TXCN0

53

4

U3

U3

NC7SZ08M5X_SOT23-5

NC7SZ08M5X_SOT23-5

Please cloce to NB

R84

R84

88.7R1%

88.7R1%

R86 35.7R1%R86 35.7R1%

C60

C60

C1u6.3Y0402-RH

C1u6.3Y0402-RH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

R244 0R0402R244 0R0402

C58

C58

C0.1u25Y0402-RH

C0.1u25Y0402-RH

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

C55 - CPU / PCI-E

C55 - CPU / PCI-E

C55 - CPU / PCI-E

MS-7510

MS-7510

MS-7510

2

Over voltage

MCH_GTL_REF 31

C55_GTLREF_CPU 3

C59

C59

C220p50N0402

C220p50N0402

642Saturday, January 12, 2008

642Saturday, January 12, 2008

642Saturday, January 12, 2008

1

2.0

2.0

2.0

of

of

of

8

7

6

5

4

3

2

1

VCC_DDR

D37

F35

D33

E36

F31

C38

M20

R28

M14

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

7 OF 8

7 OF 8

SEC

SEC

VDD_NVCORE

VDD_NVCORE

AD29

AG29

AV30

HTMCP_DWN7

AV31

HTMCP_DWN6

AW32

HTMCP_DWN5

AY33

HTMCP_DWN4

AV33

HTMCP_DWN3

AV35

HTMCP_DWN2

AW36

HTMCP_DWN1

AW37

HTMCP_DWN0

AW38

AU31

HTMCP_DWN#7

AU32

HTMCP_DWN#6

AV32

HTMCP_DWN#5

AW33

HTMCP_DWN#4

AW34

HTMCP_DWN#3

AU35

HTMCP_DWN#2

AY37

HTMCP_DWN#1

AY38

HTMCP_DWN#0

AW39

AV34

AU34

AM26

AW4

C55_200MHZ

AW29

C55_200MHZ#

AY29

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

C55 - HT Link / Power

C55 - HT Link / Power

C55 - HT Link / Power

MS-7510

MS-7510

MS-7510

2

HTMCP_DWNCNTL 17

HTMCP_DWN[7..0] 17

HTMCP_DWNCNTL# 17

HTMCP_DWN#[7..0] 17HTMCP_UP#[7..0]17

HTMCP_DWNCLK0 17

HTMCP_DWNCLK0# 17

HTMCP_REQ# 17

C55_25MHZ 17

742Monday, January 14, 2008

742Monday, January 14, 2008

742Monday, January 14, 2008

1

2.0

2.0

2.0

of

of

of

AM9

VTT_CPU

PEX_AVDD

AG23

AV8

VTT_CPU

PEX_AVDD

AF23

AR8

VTT_CPU

PEX_AVDD

AF22

AU8

V_FSB_VTT

AD12

AW8

AA12

AC12

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

PEX_DVDD

PEX_DVDD

AF24

AH24

VCC1_2

C133 C3900p50XC133 C3900p50X

C135 C3900p50XC135 C3900p50X

P12

AM8

POWER

POWER

VTT_CPU

VTT_CPU

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

VDD_HT_CORE

VDD_HT_CORE

AJ24

VCC_DDR

V_FSB_VTT

AG24

AG25

AH25

AF26

AH26

VCC1_2 VCC1_2VCC2_5

Bottom Side Cap.

VCC1_2

Bottom Side Cap.

R95

R95

49.9R1%0402

49.9R1%0402

R99

R99

49.9R1%0402

49.9R1%0402

M28

N28

N20

N19

N18

N17

F29

H31

M25

P29

N29

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_HT_CORE

VDD_HT_CORE

AJ26

AG26

C100 C10u6.3X50805-RH-3C100 C10u6.3X50805-RH-3

C98 C10u6.3X50805-RH-3C98 C10u6.3X50805-RH-3

C131 C0.1u16XC131 C0.1u16X

C103 C0.1u16XC103 C0.1u16X

C101 C0.1u16XC101 C0.1u16X

C105 C0.1u16XC105 C0.1u16X

C109 C0.1u16XC109 C0.1u16X

C106 C0.1u16XC106 C0.1u16X

C108 C0.1u16XC108 C0.1u16X

C119 C0.1u16XC119 C0.1u16X

C107 C0.1u16XC107 C0.1u16X

C113 C0.1u16XC113 C0.1u16X

VDD_NVCORE

AJ25

AH28

AH27

Bottom Side Cap.

C114 C0.1u16XC114 C0.1u16X

C118 C0.1u16XC118 C0.1u16X

C116 C0.1u16XC116 C0.1u16X

C124 C0.1u16XC124 C0.1u16X

C132 C0.1u16XC132 C0.1u16X

C126 C0.1u16XC126 C0.1u16X

C128 C0.1u16XC128 C0.1u16X

C130 C0.1u16XC130 C0.1u16X

C70 C0.1u16XC70 C0.1u16X

C74 C0.1u16XC74 C0.1u16X

C89 C0.1u16XC89 C0.1u16X

C95 C0.1u16XC95 C0.1u16X

C96 C0.1u16XC96 C0.1u16X

C97 C0.1u16XC97 C0.1u16X

C91 C0.1u16XC91 C0.1u16X

C901 C0.1u16XC901 C0.1u16X

C354 C0.1u16XC354 C0.1u16X

C900 C0.1u16XC900 C0.1u16X

C902 C0.1u16XC902 C0.1u16X

C55_200MHZ#

C134

C134

X_C0.01u16X0402

X_C0.01u16X0402

C55_200MHZ

5

M29

D29

A32

P33

E40

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AJ27

AA29

AA28

AV39

AD27

VCC3

R96

R96

1.54KR1%0402

1.54KR1%0402

R100

R100

511R1%0402

511R1%0402

N16

F27

H29

H27

M33

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AB28

AV37

AV40

AU38

AM32

N15

A28

M27

M37

H35

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AB27

AB26

AA27

AA26

AD26

HTMCP_UPCNTL17

HTMCP_UP[7..0]17

HTMCP_UPCNTL#17

HTMCP_UPCLK017

HTMCP_UPCLK0#17

HTMCP_PWRGD17

HTMCP_RST#17

HTMCP_STOP#17

150R1%0402

150R1%0402

4

P28

N37

N14

J32

J37

D32

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AB29

AE27

AP34

AR36

AU33

AN33

R92 10KR0402R92 10KR0402

R93 10KR0402R93 10KR0402

R94 1KR1%0402R94 1KR1%0402

R97

R97

VCC1_2

K33

J31

F33

M15

K32

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AT37

AT36

AR35

AH29

AU40

HTMCP_UP7

HTMCP_UP6

HTMCP_UP5

HTMCP_UP4

HTMCP_UP3

HTMCP_UP2

HTMCP_UP1

HTMCP_UP0

HTMCP_UP#7

HTMCP_UP#6

HTMCP_UP#5

HTMCP_UP#4

HTMCP_UP#3

HTMCP_UP#2

HTMCP_UP#1

HTMCP_UP#0

HT_CAL_1_2V

HT_CAL_GND

R98

R98

150R1%

150R1%

Bottom Side R

H40

A36

M22

M40

K35

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AJ29

AT34

AY36

AU37

AR34

M21

P35

M19

G34

N27

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AY32

AR33

AC26

AC27

AM33

AR32

HT_MCP_RXCTL_P

AN32

HT_MCP_RXD7_P

AT30

HT_MCP_RXD6_P

AP30

HT_MCP_RXD5_P

AM30

HT_MCP_RXD4_P

AN28

HT_MCP_RXD3_P

AM27

HT_MCP_RXD2_P

AT26

HT_MCP_RXD1_P

AP26

HT_MCP_RXD0_P

AT32

HT_MCP_RXCTL_N

AP32

HT_MCP_RXD7_N

AU30

HT_MCP_RXD6_N

AR30

HT_MCP_RXD5_N

AN30

HT_MCP_RXD4_N

AP28

HT_MCP_RXD3_N

AM28

HT_MCP_RXD2_N

AU26

HT_MCP_RXD1_N

AR26

HT_MCP_RXD0_N

AR28

HT_MCP_RX_CLK0_P

AT28

HT_MCP_RX_CLK0_N

AW30

HT_MCP_PWRGD

AV29

HT_MCP_RESET*

AN26

HT_MCP_STOP*

AU5

FUSE_SRC

AW9

JTAG_TMS

AV9

JTAG_TDI

AU10

JTAG_TDO

AY9

JTAG_TCK

AV10

JTAG_TRST*

AW10

TEST_EN

AM31

HT_CAL_1.2V

AM29

HT_CAL_GND

3

T29

M24

N26

M35

N25

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AV38

AE29

AE28

AC29

AD28

U11C

U11C

R29

M23

M18

M17

H33

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AF28

AF25

AC28

AG27

AG28

<PN>

<PN>

CRUSH55

CRUSH55

SEC 3 OF 8

SEC 3 OF 8

HT I/F

HT I/F

<PATH>

<PATH>

M16

N23

M26

N22

H37

N24

N21

T28

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

AJ28

AF29

AF27

AV36

AE26

AU39

AU36

AU29

HT_MCP_TXCTL_P

HT_MCP_TXD7_P

HT_MCP_TXD6_P

HT_MCP_TXD5_P

HT_MCP_TXD4_P

HT_MCP_TXD3_P

HT_MCP_TXD2_P

HT_MCP_TXD1_P

HT_MCP_TXD0_P

HT_MCP_TXCTL_N

HT_MCP_TXD7_N

HT_MCP_TXD6_N

HT_MCP_TXD5_N

HT_MCP_TXD4_N

HT_MCP_TXD3_N

HT_MCP_TXD2_N

HT_MCP_TXD1_N

HT_MCP_TXD0_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_REQ*

CLKIN_25MHZ

HT_MCP_REFCLK_IN_P

HT_MCP_REFCLK_IN_N

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

C55 - HT Link / Power

CRUSH55

CRUSH55

U11G

U11G

D D

+1.2V_PEX_PLL

AJ15

+1.2V_PE_PLL

C C

VCC1_2

VCC2_5

VCC1_2

B B

VCC1_2

A A

CP4 X_COPPERCP4 X_COPPER

L4 X_30L600mA-100_0805-RHL4 X_30L600mA-100_0805-RH

21

CP5 X_COPPERCP5 X_COPPER

L5 40L3A-25_0805L5 40L3A-25_0805

21

CP6 X_COPPERCP6 X_COPPER

L6 X_30L500mA-200-RHL6 X_30L500mA-200-RH

21

CP7 X_COPPERCP7 X_COPPER

L7 X_30L500mA-200-RHL7 X_30L500mA-200-RH

21

HTMCP_RST#

HTMCP_PWRGD

HTMCP_STOP#

HTMCP_REQ#

1

3

5

7

8

2

4

6

8

RN88P4R-680R RN88P4R-680R

VCC2_5

Bottom Side Cap.

C63

C63

C0.1u16X

C0.1u16X

C77

C77

C0.1u16X0402-2

C0.1u16X0402-2

C88

C88

C0.1u16X0402-2

C0.1u16X0402-2

+1.2V_PE_PLL

C102

C102

C0.1u16X0402-2

C0.1u16X0402-2

+1.2V_HT_PLL

+1.2V_PEX_CORE_PLL

AJ19

AH19

+1.2V_HT_PLL

C66

C66

C0.1u16X

C0.1u16X

C78

C78

C0.1u16X0402-2

C0.1u16X0402-2

7

P13

V13

AV7

AU7

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

+2.5V_PLL

+2.5V_PLL_PE_SS

AH15

AG15

+2.5V_PLL

PXE_AVDD

C67

C67

C0.1u16X

C0.1u16X

+1.2V_HT_PLL

C90

C90

C0.1u16X0402-2

C0.1u16X0402-2

AT7

AR7

AP7

AG12

AH12

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

C79

C79

C0.1u16X0402-2

C0.1u16X0402-2

VCC_DDR

V_FSB_VTT

AJ12

Y12

W12

U12

T12

R12

Y13

T13

AL9

AF12

AE12

AY8

AB12

AN8

V12

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

+2.5V

+2.5V

PEX_AVDD

PEX_AVDD

PEX_AVDD

PEX_AVDD

PEX_AVDD

PEX_AVDD

AJ13

AJ22

AJ23

AH22

PXE_AVDD

MCPOUT_200MHZ#17

AH23

AE23

AG22

AH13

+2.5V_PLL

C80

C80

C0.1u16X0402-2

C0.1u16X0402-2

C104 C0.1u16X0402-2C104 C0.1u16X0402-2

C111 C0.1u16X0402-2C111 C0.1u16X0402-2

C115 C0.1u16X0402-2C115 C0.1u16X0402-2

C117 C0.1u16X0402-2C117 C0.1u16X0402-2

C121 C0.1u16X0402-2C121 C0.1u16X0402-2 C85 C0.1u16XC85 C0.1u16X

C123 C0.1u16X0402-2C123 C0.1u16X0402-2

C125 C0.1u16X0402-2C125 C0.1u16X0402-2

C127 C0.1u16X0402-2C127 C0.1u16X0402-2

C129 C0.1u16X0402-2C129 C0.1u16X0402-2

C112 C10u6.3X50805-RH-3C112 C10u6.3X50805-RH-3

C110 C0.1u16X0402-2C110 C0.1u16X0402-2

C120 C0.1u16X0402-2C120 C0.1u16X0402-2

C122 C0.1u16X0402-2C122 C0.1u16X0402-2

Place Close To C55

MCPOUT_200MHZ17

6

8

7

6

5

4

3

2

1

C55 - Memory A0

D D

DIMM1 0A

U11E

W38

W37

M39

G38

G37

H39

D35

E38

C35

C34

A33

B33

D30

C32

B30

K38

C30

A29

R38

C28

C26

D3

C6

A13

B17

C21

B2

C7

C13

B18

Y38

C22

C2

D6

B13

C17

B22

K37

J39

C27

T38

D7

C8

L37

P39

N40

B25

A25

P37

T39

U11E

MA0A_0

MA0A_1

MA0A_2

MA0A_3

MA0A_4

MA0A_5

MA0A_6

MA0A_7

MA0A_8

MA0A_9

MA0A_10

MA0A_11

MA0A_12

MA0A_13

MA0A_14

MA0A_15

MDQM0_0/DQS0_9

MDQM0_1/DQS0_10

MDQM0_2/DQS0_11

MDQM0_3/DQS0_12

MDQM0_4/DQS0_13

MDQM0_5/DQS0_14

MDQM0_6/DQS0_15

MDQM0_7/DQS0_16

MDQM0_8/DQS0_17

MDQS0_0_P

MDQS0_1_P

MDQS0_2_P

MDQS0_3_P

MDQS0_4_P

MDQS0_5_P

MDQS0_6_P

MDQS0_7_P

MDQS0_8_P

MDQS0_0_N

MDQS0_1_N

MDQS0_2_N

MDQS0_3_N

MDQS0_4_N

MDQS0_5_N

MDQS0_6_N

MDQS0_7_N

MDQS0_8_N

MBA0A_0

MBA0A_1

MBA0A_2

MCS0A_0*

MCS0A_1*

MCLK0A_0_P

MCLK0A_1_P

MCLK0A_2_P

MCLK0A_0_N

MCLK0A_1_N

MCLK0A_2_N

MRAS_0A*

MCAS_0A*

MWE_0A*

MCKE0A_0

MCKE0A_1

MODT0A_0

MODT0A_1

STR_EN*

5 OF 8

5 OF 8

SEC

SEC

DIMM 0

DIMM 0

CRUSH55

CRUSH55

MDQ0_0

MDQ0_1

MDQ0_2

MDQ0_3

MDQ0_4

MDQ0_5

MDQ0_6

MDQ0_7

MDQ0_8

MDQ0_9

MDQ0_10

MDQ0_11

MDQ0_12

MDQ0_13

MDQ0_14

MDQ0_15

MDQ0_16

MDQ0_17

MDQ0_18

MDQ0_19

MDQ0_20

MDQ0_21

MDQ0_22

MDQ0_23

MDQ0_24

MDQ0_25

MDQ0_26

MDQ0_27

MDQ0_28

MDQ0_29

MDQ0_30

MDQ0_31

MDQ0_32

MDQ0_33

MDQ0_34

MDQ0_35

MDQ0_36

MDQ0_37

MDQ0_38

MDQ0_39

MDQ0_40

MDQ0_41

MDQ0_42

MDQ0_43

MDQ0_44

MDQ0_45

MDQ0_46

MDQ0_47

MDQ0_48

MDQ0_49

MDQ0_50

MDQ0_51

MDQ0_52

MDQ0_53

MDQ0_54

MDQ0_55

MDQ0_56

MDQ0_57

MDQ0_58

MDQ0_59

MDQ0_60

MDQ0_61

MDQ0_62

MDQ0_63

MEM_VREF

MEM_VREF2

D1

D2

B4

A4

E2

E3

C3

B3

C5

B6

C10

D10

C4

B5

C9

B10

C12

B12

D14

C15

C11

D11

B14

C14

B16

A17

D18

D19

D15

C16

C18

C19

V39

V37

AA39

AA38

U38

V38

Y39

AA40

AC37

AC38

AE38

AF39

AB39

AB38

AE40

AE39

AG38

AH37

AM38

AM39

AF38

AG37

AL38

AM37

AN38

AP39

AT38

AT40

AN40

AN39

AR37

AT39

F5

E4

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

C55_MEMVREF

C136

C136

X_C10u10Y0805

X_C10u10Y0805

DATA_A[0..63] 11

Over voltage

R350 0R0402R350 0R0402

C137

C137

C0.1u16X0402-2

C0.1u16X0402-2

R108

R108

121R1%0402

121R1%0402

MEM_0A_ADD0

MCLK011

MCLK111

MCLK211

MCLK#011

MCLK#111

MCLK#211

R107

R107

18.7KR1%

18.7KR1%

MEM_0A_ADD1

MEM_0A_ADD2

MEM_0A_ADD3

MEM_0A_ADD4

MEM_0A_ADD5

MEM_0A_ADD6

MEM_0A_ADD7

MEM_0A_ADD8

MEM_0A_ADD9

MEM_0A_ADD10

MEM_0A_ADD11

MEM_0A_ADD12

MEM_0A_ADD13

MEM_0A_ADD14

MEM_0A_ADD15

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

DQM_A8

DQS_A0

DQS_A1

DQS_A2

DQS_A3

DQS_A4

DQS_A5

DQS_A6

DQS_A7

DQS_A8

DQS_A#0

DQS_A#1

DQS_A#2

DQS_A#3

DQS_A#4

DQS_A#5

DQS_A#6

DQS_A#7

DQS_A#8

MEM_0A_BA0

MEM_0A_BA1

MEM_0A_BA2

MEM_0A_CS#0

MEM_0A_CS#1

MCLK0

MCLK1

MCLK2

MCLK#0

MCLK#1

MCLK#2

MEM_0A_RAS#

MEM_0A_CAS#

MEM_0A_WE#

MEM_0A_CKE0

MEM_0A_CKE1

MEM_0A_ODT0

MEM_0A_ODT1

STR_EN*

AD37

AK39

AP38

AD39

AL37

AR38

AD38

AK38

AP37

AH38

AH39

AP36

MEM_0A_ADD[0..15]11,13

C C

B B

C55_PCIRST#17

DQM_A[0..8]11

DQS_A[0..8]11

DQS_A#[0..8]11

MEM_0A_BA[0..2]11,13

MEM_0A_CS#[0..1]11,13

MEM_0A_RAS#11,13

MEM_0A_CAS#11,13

MEM_0A_WE#11,13

MEM_0A_CKE[0..1]11,13

MEM_0A_ODT[0..1]11,13

R105 6.04KR1%0402R105 6.04KR1%0402 R106 121R1%0402R106 121R1%0402

DIMM2 0B / DIMM4 1B

MEM_0B_ADD[0..15]11,13

MEM_0B_BA[0..2]11,13

MEM_0B_RAS#11,13

MEM_0B_CAS#11,13

MEM_0B_WE#11,13

MEM_0B_CKE[0..1]11,13

MEM_0B_ODT[0..1]11,13

MEM_0B_CS#[0..1]11,13

MCLK#311

MCLK#411

MCLK#511

MCLK311

MCLK411

MCLK511

MBC_A[0..7]11

R101 40.2R1%0402R101 40.2R1%0402

VCC_DDR

C55_MEM_VREF 32

R104 40.2R1%0402R104 40.2R1%0402

VCC_DDR

MEM_0B_ADD0

MEM_0B_ADD1

MEM_0B_ADD2

MEM_0B_ADD3

MEM_0B_ADD4

MEM_0B_ADD5

MEM_0B_ADD6

MEM_0B_ADD7

MEM_0B_ADD8

MEM_0B_ADD9

MEM_0B_ADD10

MEM_0B_ADD11

MEM_0B_ADD12

MEM_0B_ADD13

MEM_0B_ADD14

MEM_0B_ADD15

MEM_0B_BA0

MEM_0B_BA1

MEM_0B_BA2

MEM_0B_RAS#

MEM_0B_CAS#

MEM_0B_WE#

MEM_0B_CKE0

MEM_0B_CKE1

MEM_0B_ODT0

MEM_0B_ODT1

MEM_0B_CS#0

MEM_0B_CS#1

MCLK#3

MCLK#4

MCLK#5

MCLK3

MCLK4

MCLK5

MBC_A0

MBC_A1

MBC_A2

MBC_A3

MBC_A4

MBC_A5

MBC_A6

MBC_A7

M_DRV0_1P8V

M_DRV1_GND

H38

C36

F39

D34

B34

C33

B32

C31

D31

B29

J40

C29

B28

R37

D26

B26

K39

J38

D27

L38

N38

M38

C25

B24

P38

U39

N39

U40

F37

AJ39

F38

AJ40

B20

B21

D23

C24

C20

A21

D22

C23

DATA 0

DATA 1

B9

A9

G7

G5

U11F

U11F

MA0B_0

MA0B_1

MA0B_2

MA0B_3

MA0B_4

MA0B_5

MA0B_6

MA0B_7

MA0B_8

MA0B_9

MA0B_10

MA0B_11

MA0B_12

MA0B_13

MA0B_14

MA0B_15

MBA0B_0

MBA0B_1

MBA0B_2

MRAS_0B*

MCAS_0B*

MWE_0B*

MCKE0B_0

MCKE0B_1

MODT0B_0

MODT0B_1

MCS0B_0*

MCS0B_1*

MCLK0B_0_N

MCLK0B_1_N

MCLK0B_2_N

MCLK0B_0

MCLK0B_1

MCLK0B_2

MCB0_0

MCB0_1

MCB0_2

MCB0_3

MCB0_4

MCB0_5

MCB0_6

MCB0_7

MEM_DRV0_1P8V

MEM_DRV1_GND

CRUSH55

CRUSH55

SEC

SEC

6 OF 8

6 OF 8

DIMM 2

DIMM 2

DIMM 3

DIMM 3

MCLK1B_0_N

MCLK1B_1_N

MCLK1B_2_N

MCLK1B_0_P

MCLK1B_1_P

MCLK1B_2_P

MA1B_0

MA1B_1

MA1B_2

MA1B_3

MA1B_4

MA1B_5

MA1B_6

MA1B_7

MA1B_8

MA1B_9

MA1B_10

MA1B_11

MA1B_12

MA1B_13

MA1B_14

MA1B_15

MBA1B_0

MBA1B_1

MBA1B_2

MRAS_1B*

MCAS_1B*

MWE_1B*

MCKE1B_0

MCKE1B_1

MODT1B_0

MODT1B_1

MCS1B_0*

MCS1B_1*

MCB1_0

MCB1_1

MCB1_2

MCB1_3

MCB1_4

MCB1_5

MCB1_6

MCB1_7

MRESET0*

MRESET1*

DIMM 1

DIMM 2

DIMM 3

DIMM 4

MEM_1B_ADD0

J33

MEM_1B_ADD1

D40

MEM_1B_ADD2

C40

MEM_1B_ADD3

E37

MEM_1B_ADD4

B38

MEM_1B_ADD5

A38

MEM_1B_ADD6

D36

MEM_1B_ADD7

H32

MEM_1B_ADD8

F34

MEM_1B_ADD9

J30

MEM_1B_ADD10

J36

MEM_1B_ADD11

E32

MEM_1B_ADD12

H30

MEM_1B_ADD13

R34

MEM_1B_ADD14

E30

MEM_1B_ADD15

G28

MEM_1B_BA0

L34

MEM_1B_BA1

J35

MEM_1B_BA2

J28

MEM_1B_RAS#

L36

MEM_1B_CAS#

P32

MEM_1B_WE#

N33

MEM_1B_CKE0

E28

MEM_1B_CKE1

J27

MEM_1B_ODT0

R32

MEM_1B_ODT1

U33

MEM_1B_CS#0