Page 1

Jan. 11 2002

www.kythuatvitinh.com

Digitally signed by dd

DN: cn=dd, o=dd, ou=dd,

email=dddd@yahoo.com,

c=US

Date: 2009.11.20 21:05:23

+07'00'

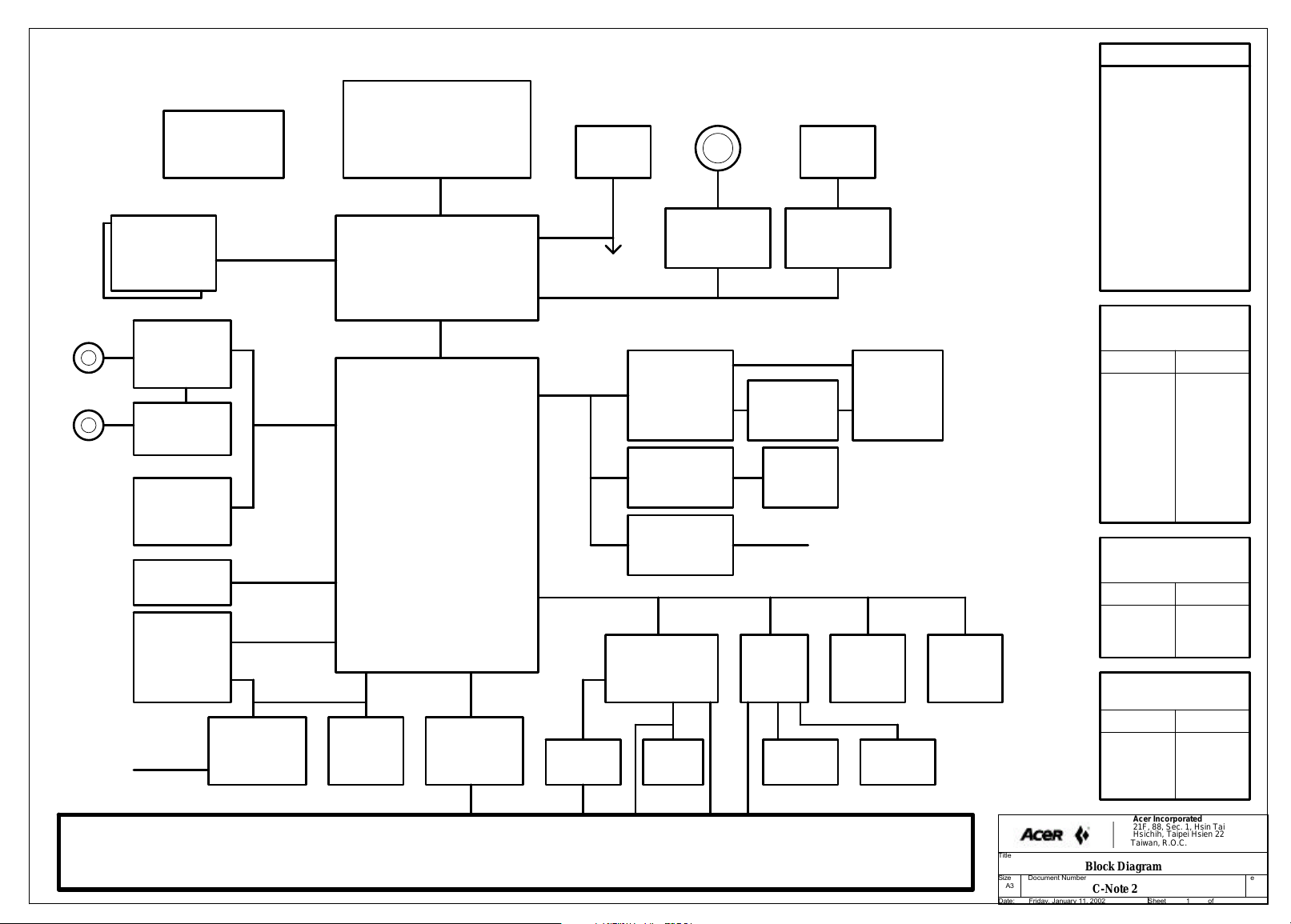

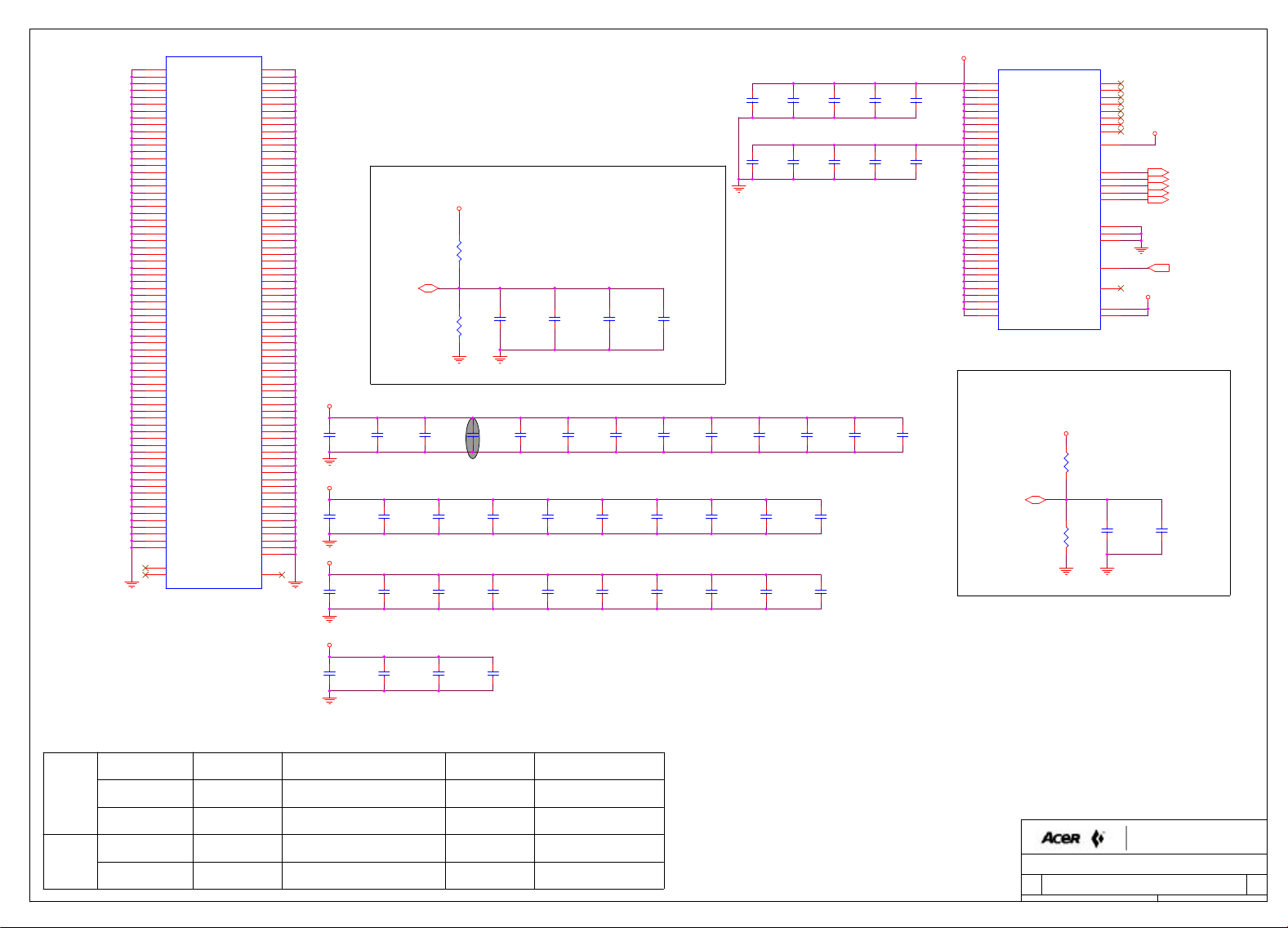

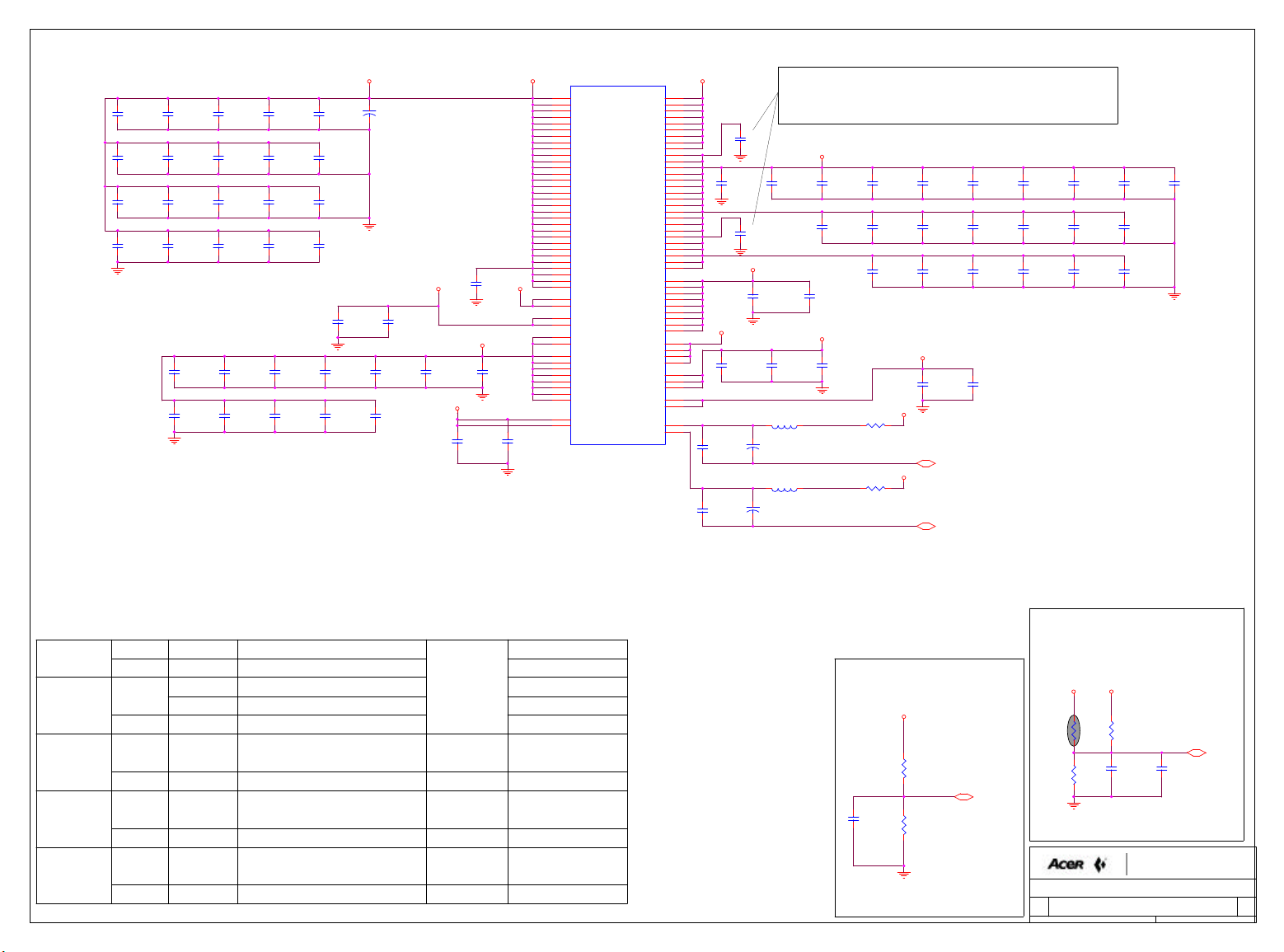

SO-DIMM*2

MIC IN

Line Out

AC'97

CODEC

AD1881A

OP AMP

TPA0202

MODEM

CLK GEN.

ICS 950806

MEM BUS

10

133MHz

24

25

AC-Link

Mobile CPU

Tualatin

Celeron-T

HOST BUS

133MHz

4,53

Almador-M

GMCH

HUB I/F

7,8,9

66MHz

ICH3-M

CRT

CONN

13

RGB

To P.R.

DVO BUS / 66MHz

PCI BUS

CARDBUS

TI 1410A

1394

TSB43AB21

C-Note 2 Block Diagram

TV OUT

CH70011

TV Encoder

12

20

21 21

PWR SW

TPS2211A

20

1394

CONN

LCD

14

LVDS

VCH

11

CARDBUS

ONE SLOT

01204-3

For C2 SOVP

C3 DV

Final version

20

PCB LAYER

L1:

L2:

L3:

L4:

L5:

L6:

L7:

L8:

L9:

L10:

DC/DC&CHARGER

Switching Power

MAX1631/MAX1772

INPUTS

DCBATOUT LAN+3VAUX

AD+

CDC Card

PRIMARY

HDD

UltraBay

CD/DVDROM

CD-RW/FDD

NEST

AC-Link

22

IDE

18

IDE

18

Bluetooth

CDC Card

MiniPCI

802.11b

LPC BUS

15,16,17

NS SIO

PC87392

USB

28

LAN

USB*2

23

23

82562ET

MAX3243

19

29

PRN

Port

29

22

AC-Link

KBC

M38859

27

TRACK

POINT

FWH

82802AB

26

INT KB

2727

LPC

DEBUG

CONN.

CPU DC/DC

Switching Power

MAX1718/MAX1714

INPUTS

DCBATOUT

26

OTHER DC/DC

MAX1644/MAX1792

INPUTS OUTPUTS

+3.3VRUN

+3.3VRUN

Port Replicator(244PIN)

RS232 CRTUSB RJ45RJ11 PS2FDDLine In Line Out DC In

PRN Port

30

Title

Size Document Number Rev

A3

Date: Sheet of

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

Block Diagram

C-Note 2

Signal 1

GND

Signal 2

Signal 3

GND

POWER

Signal 4(weak)

Signal 5

GND

Signal 6

OUTPUTS

UBAY+5V

+3VSUS

+5VSUS

+3VRUN

+5VRUN

BT+

33,36

OUTPUTS

+VCC_CORE

+VCCT

31,32

+1.8VRUN

+1.5VRUN

32

1Friday, January 11, 2002

-3

37

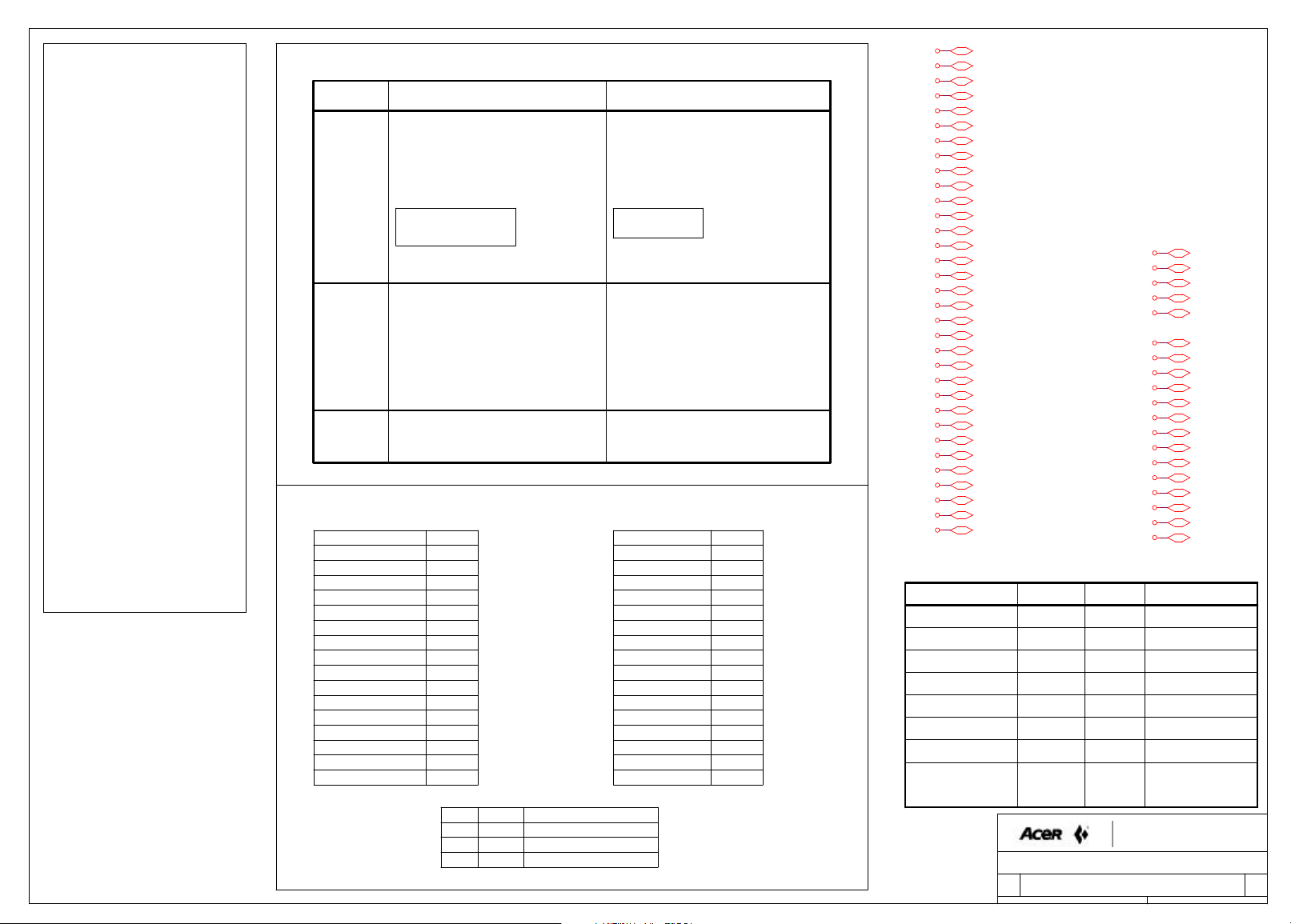

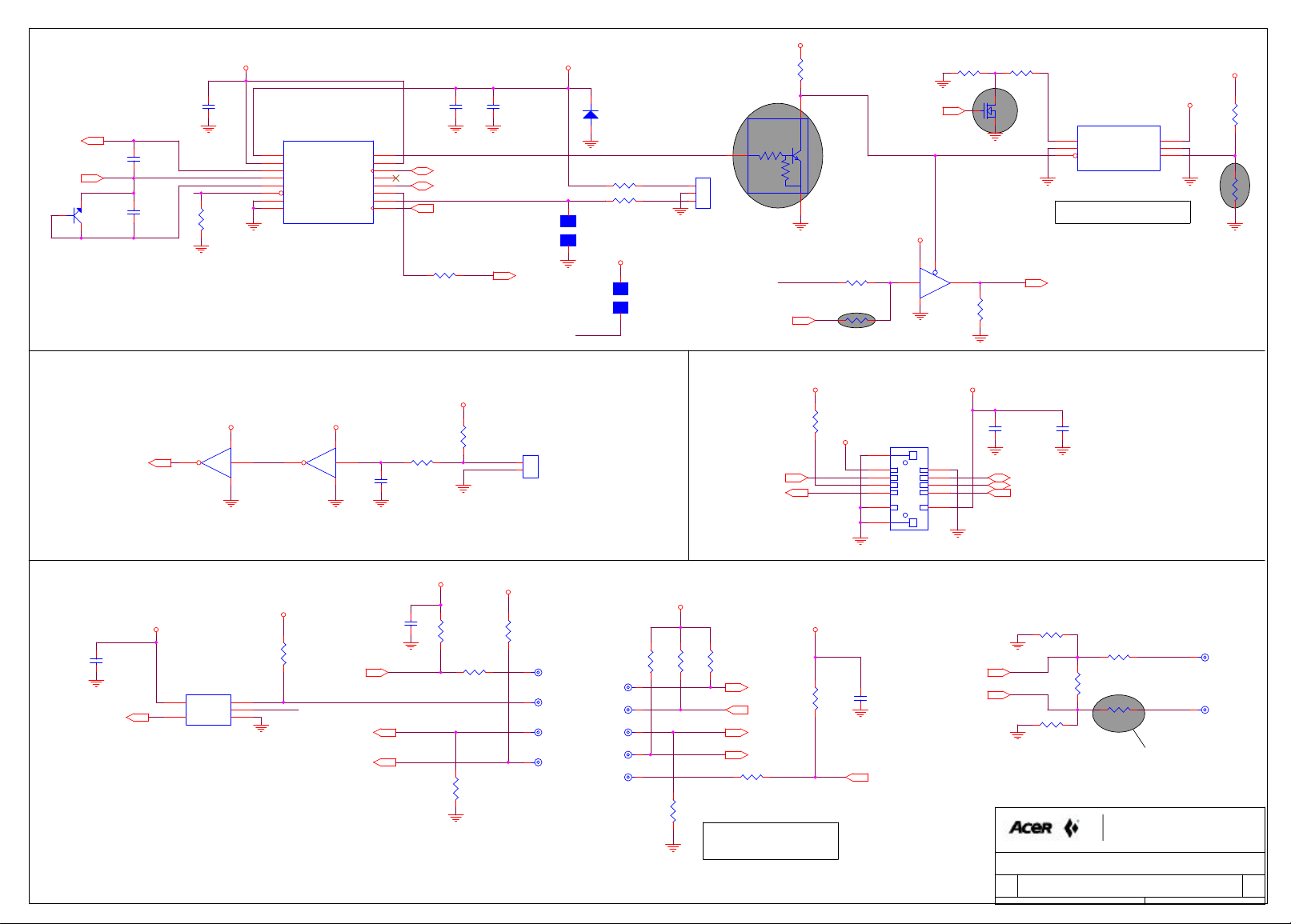

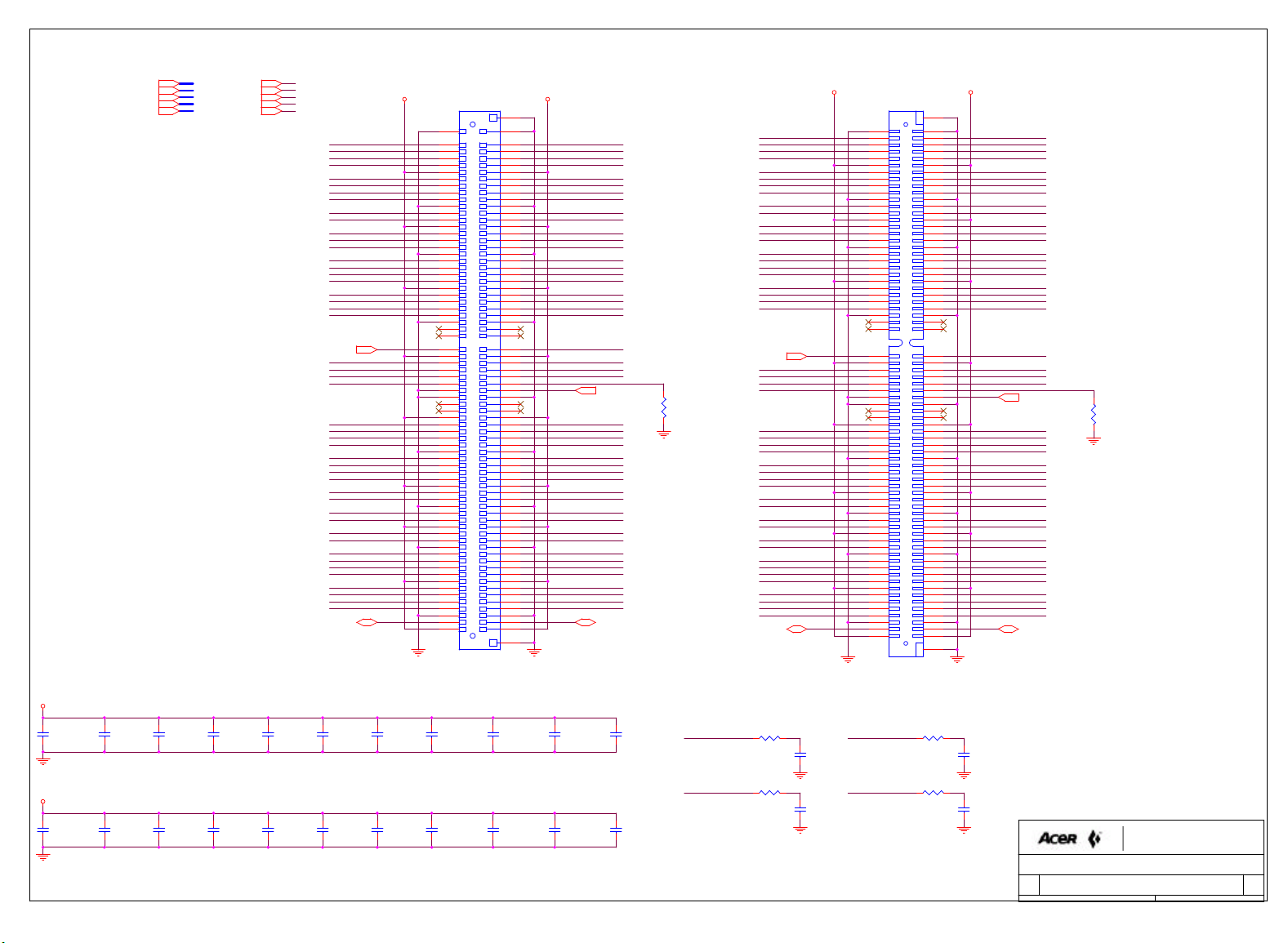

Page 2

01.BLOCK DIAGRAM

www.kythuatvitinh.com

02.TABLE OF CONTENT

03.CLOCK GENERATOR

04.CPU

05.CPU CONFIGURATION

06.ITP/Thermal/Fan Control/RFID

07.GMCH (1/3)

08.GMCH (2/3)

09.GMCH (3/3)

10.SO-DIMM

11.VCH

12.TV Encoder

13.CRT CONN

14.LCD/Inverter CONN

15.ICH3-M (1/3)

16.ICH3-M (2/3)

17.ICH3-M (3/3)

18.HDD & ULTRA BAY

19.LAN

20.PCMCIA Controler OZ6912

21.1394 TSB43AA22

22.Mini PCI SOCKET & MDC

23.USB I/F & BLUETOOTH

24.AC'97 CODEC-ALC200

25.OP AMP & PHONE JACK

26.FIRMWARE HUB

27.KBC-M38859

28.SIO-PC87392

29.Printer Port

30.PORT-REPLICATOR

31.CPU CORE

32.CPUIO/1.5V/1.8V/1.2V

33.3V/5V DC/DC

34.PWR PLANE & RESET LOGIC

35.CHARGER uP-MC68HC908SR

36.CHARGER CONTROLER-MAX1772

37.SPARE Logic/TEST POINT

CG_* : CPU GTL+

CC_* : CPU CMOS

M_* : MEMORY BUS

G_* : AGP BUS

P_* : PCI BUS

HL_* : HUB LINK I/F

LPC_* : LPC I/F

ICH_AC_* : AC'97 LINK I/F

IDE_* : IDE BUS

Tualatin

Cu-T

GMCH

D4 D3 D2

0

0 0

0

0 0 01 1

0 0 1

0

0 001 1

0 01 0

0 1 0

0 1 01

D1 D0

0 0

0 0 1.75

0 1 0

1 10

0 0

0 0 01

1

100 11

1

10 01

0

1 00

1

1 1

1

1 1

110

Cu-T & Tualatin SPEC Summary

Early Samples/ES QS/ Production

VCC = 1.50V (perf mode)/

1.15V (batt mode)

VCCT = 1.3V (min), 1.365V (max)

R143 R142

16K5R3F 49K9R3F

Tj (min) = 10C

VCC = 1.7V (perf Mode)/

1.35V (Batt Mode)

VCCT = 1.2V +/- 5%

Functional at :

VCCT = 1.3V (min), 1.365 (max)

VCC/VTT = 1.2V +/- 5%

Functional at :

VCC/VTT= 1.3V (min), 1.365V (max)

MAX1718 Voltage Setting

Vout (V)

1

0

000

11

Perf for Cu-T

1.700 0 0 0

1.65

1.60

1.55

1.50

1.45

Perf for Tualatin

1.40

Batt for Cu-T

1.35

1.30

1.25

1.20

1.15

Batt for Tualatin

1.10

1.05

1.00

ZMODE SUS Vout Determined by:

GND GND

Logic Level of D0 - D4

GNDVCC

Impedance of D0 - D4

VCCX

Logic Level of S0, S1

VCC = 1.40V (perf mode)/

1.15V (batt mode)

ICC,MAX = 13.71A

VCCDPRSLP=0.85V

ICC,DSLP=2.09A

VCCT = 1.25V +/- 5% (static)

+/- 9%(transient)

R143 R142

2D49KR3 10KR3F

ICC =2.7A

Tj (min) = 0C

VCC = 1.7V (perf Mode)/

1.35V (Batt Mode)

VCCT = 1.25V +/- 5% (static)

+/- 9%(transient)

VCC/ VTT = 1.25V +/- 5%

S0

S1

GND

GND

GND

REF

Float

GND

VCC

GND

GND

REF

REF

REF

FloatREF

REF

VCC

GND

Float

REF

Float

Float

Float

Float

VCC

GND

VCC

REF

VCC

VCC

Float

VCC

VCC

July 3 '01

Vout (V)

0.975

0.950

0.925

0.900

0.875

0.850

0.825

0.800

0.775

0.750

0.725

0.700

0.675

0.650

0.625

0.600

+VCCT

+VCC_CORE

+1.5VRUN

+1.8VRUN

LAN+3VAUX

+3VRUN

+3VSUS

+3VALW

+3.3VRTC

+5VRUN

+1.8VALW

+5VSUS

+5VALW

LAN+1.8VAUX

UBAY+5V

+5VA

BT+

+3VAUX

USB1_VCC

LCDVDD

AC97_3V

CRT_VCC

AD+

AD+IN

DCBATOUT

DCBATOUT+

ICH_VBIAS

VCC_RTC

AD+_IN

MAX1631_VL

BT_VCC

FAN1_VCC

TV_DVDD

+VCCT 3,4,5,6,9,32

+VCC_CORE 4,5,31

+1.5VRUN 4,5,6,7,8,9,11,12,17,26,32

+1.8VRUN 4,8,9,11,15,17,32

LAN+3VAUX 15,17,19,22,30,34

+3VRUN 3,6,8,9,11,12,13,14,15,16,17,18,20,21,22,23,24,26,27,28,31,32,34,35,37

+3VSUS 6,9,10,14,18,20,23,27,31,32,34,35,37

+3VALW 14,15,16,17,23,25,32,33,34,36

+3.3VRTC 16

+5VRUN 6,13,14,15,17,18,22,24,25,26,27,29,30,31,34,35,37

+1.8VALW 17,34

+5VSUS 13,14,20,23,25,27,32,34,37

+5VALW 14,17,18,30,33,34,36

LAN+1.8VAUX 17,34

UBAY+5V 18

+5VA 24,25

BT+ 35,36

+3VAUX 22,23

USB1_VCC 23,30

LCDVDD 14

AC97_3V 23

CRT_VCC 13,30

AD+ 35,36

AD+IN 35,36

DCBATOUT 14,31,32,33,34,35,36

DCBATOUT+ 36

ICH_VBIAS 16

VCC_RTC 6,15,16,17

AD+_IN 30,36

MAX1631_VL 14,33

BT_VCC 23

FAN1_VCC 6

TV_DVDD 12

TV_AVDD

TV_VDD

+1.5VRUN_F

LCD_DCBAT

LIGHT_PWR

SLOTVCC

SLOTVPP

1394_AVDD

1394_PLLVDD

MOD_5VAD

USB0_VCC

AUD_VREF

OP+5V

TP_VCC

1718_+5V

M1772+3V

M1772_LDO

DC+5V

DC+3V

PCI TABLE

DEVICE IDSEL IRQ REQ# / GNT#

TI 1394

MINIPCI SLOT

PCMCIA TI1410

AGP

LAN AD24(Int.) E

USB AD29 A,D,C

Hub-to-PCI AD30

LPC Bridge/

IDE/AC97/

SMBus

AD19

AD21

AD25

B,D REQ1# / GNT1#

A,BAD17(Int.)

AD15

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Title

Size Document Number Rev

A3

Date: Sheet of

Taiwan, R.O.C.

TABLE OF CONTENT

C-Note 2

REQ2# / GNT2#Auto

REQ3# / GNT3#C,E

TV_AVDD 12

TV_VDD 12

+1.5VRUN_F 12

LCD_DCBAT 14

LIGHT_PWR 14

SLOTVCC 20

SLOTVPP 20

1394_AVDD 21

1394_PLLVDD 21

MOD_5VAD 22

USB0_VCC 23

AUD_VREF 25

OP+5V 25

TP_VCC 27

1718_+5V 31

M1772+3V 36

M1772_LDO 36

DC+5V 33

DC+3V 33

2Friday, January 04, 2002

37

-3

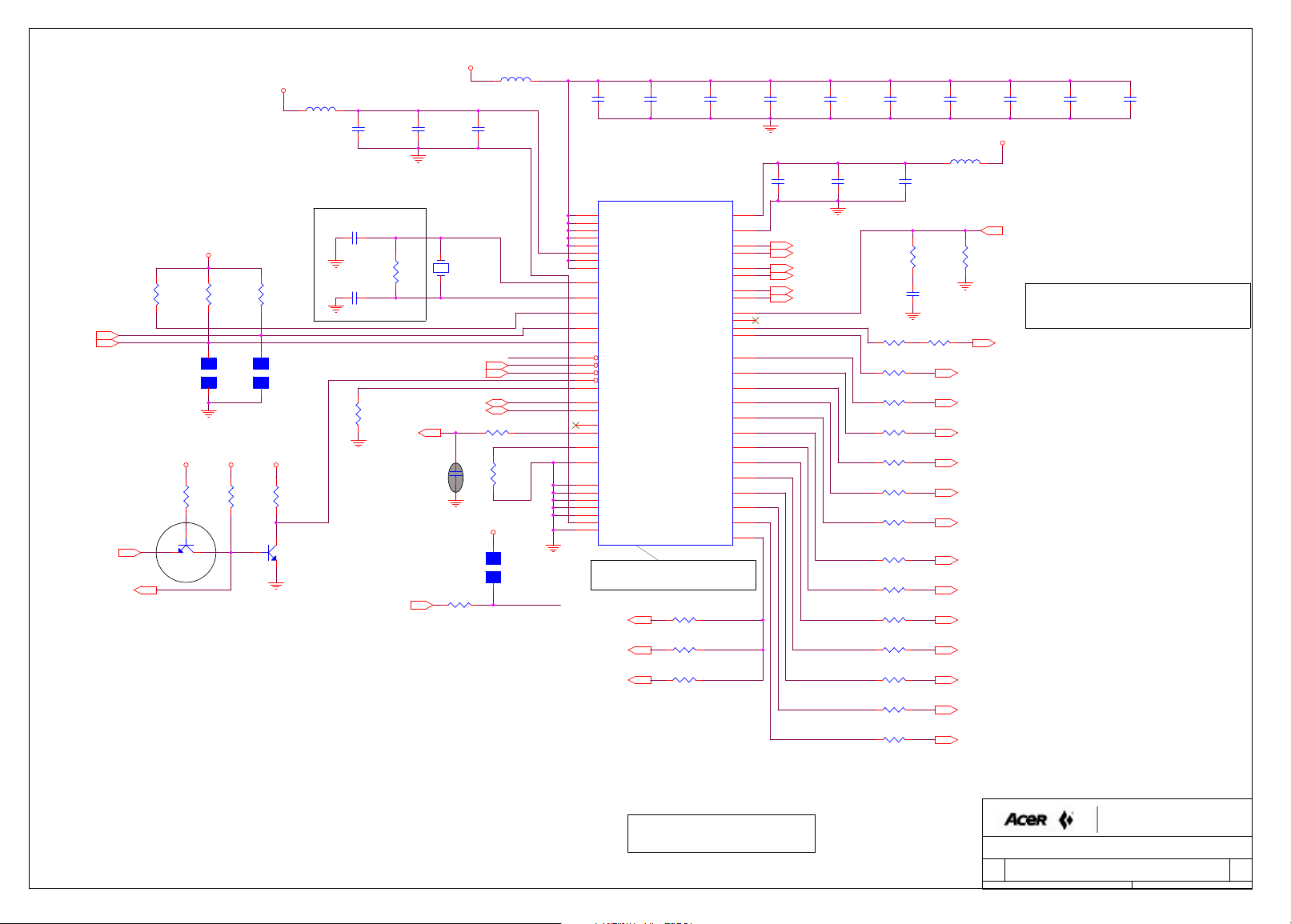

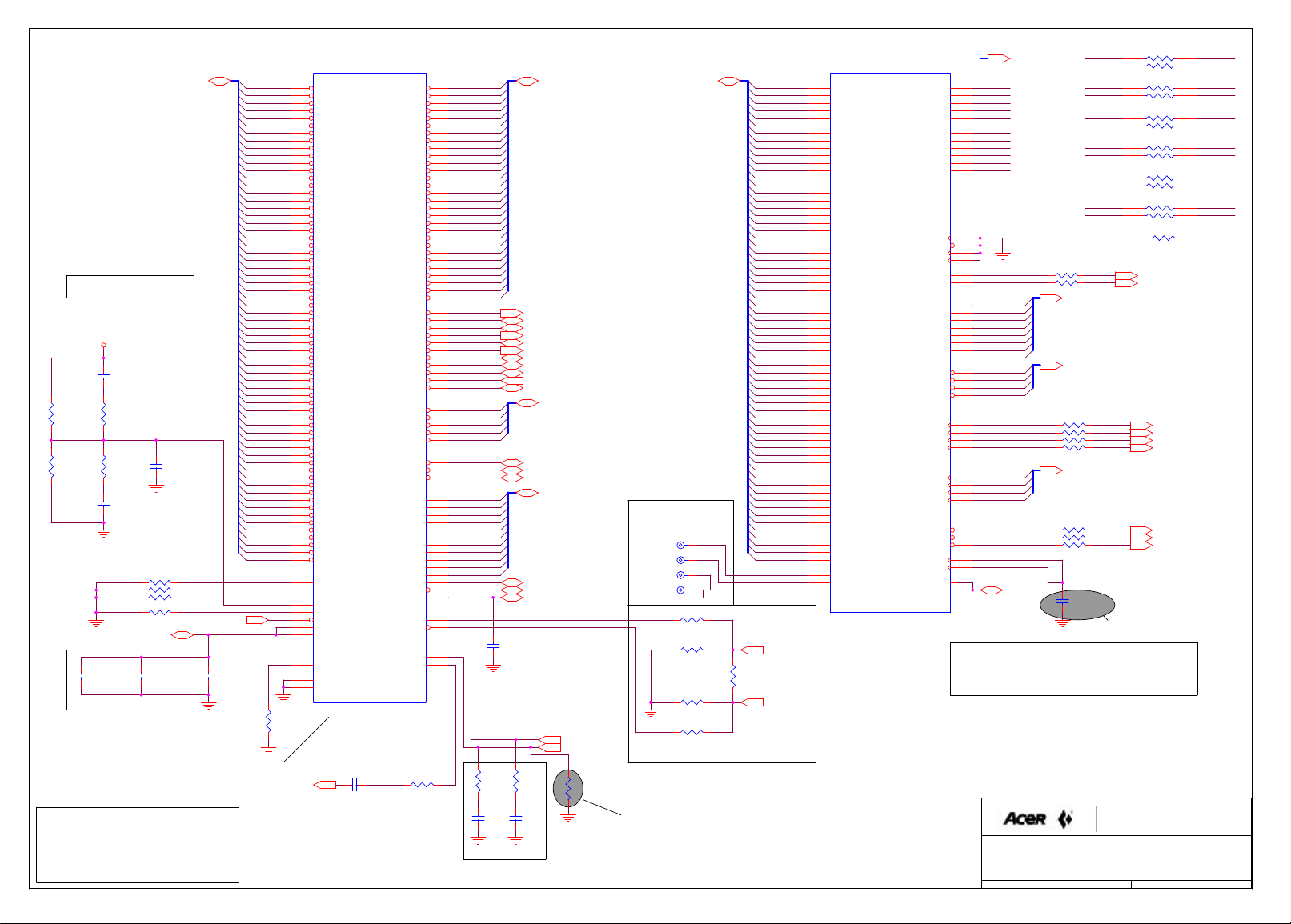

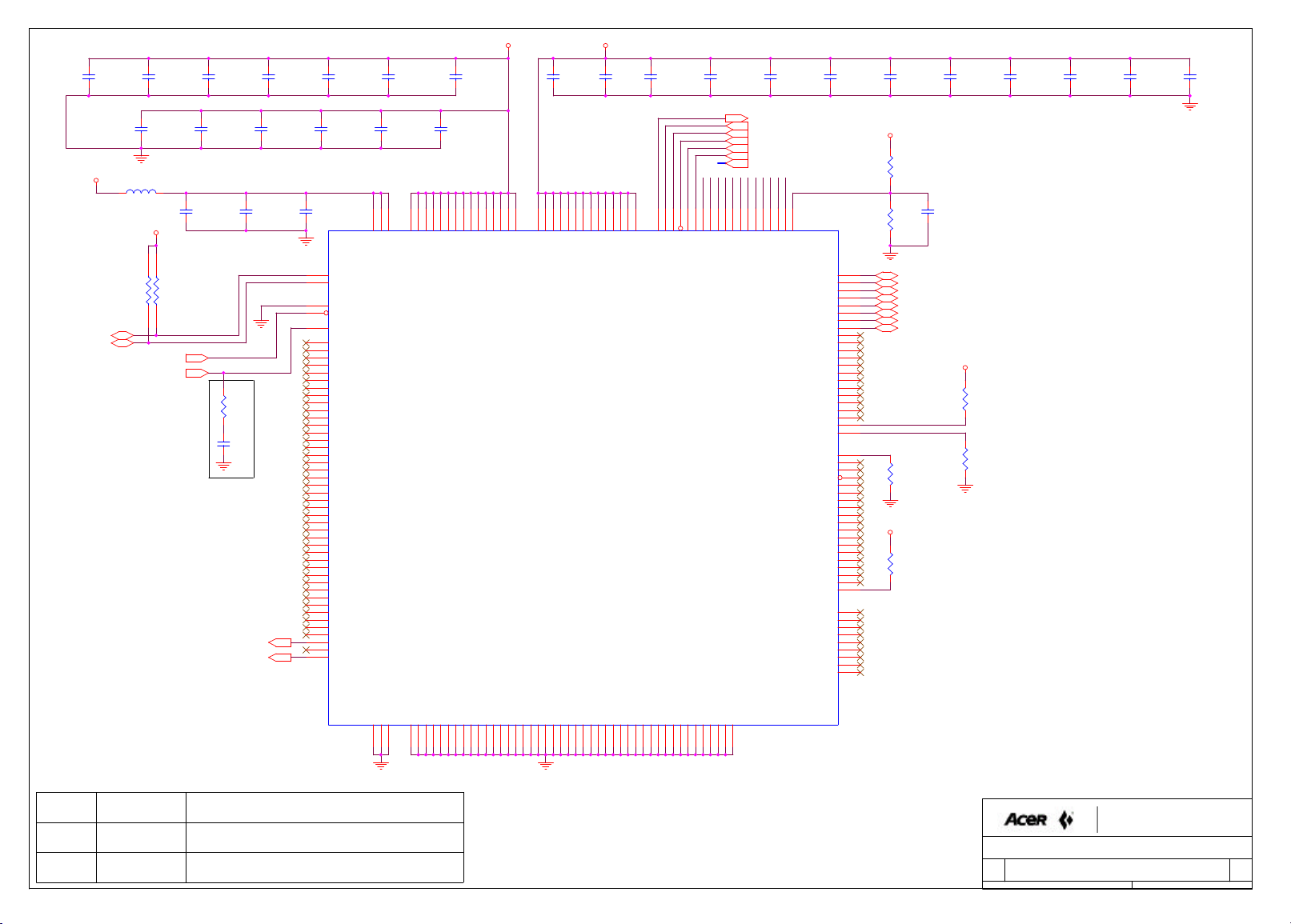

Page 3

+3VRUN

www.kythuatvitinh.com

L17

X3

X-14.318MHZ-1

ICH_SDA15

ICH_SCL15

1 2

BC698

SC22P

+3VRUN

R197

0R3-0-U

1 2

BLM21P221SGPT

BC617

SCD1U10V2MX

CLKGEN_XIN

CLKGEN_XOUT

CLKGEN_PD#

VTT_PWRGD#

R196

CLK66R_VCH

33R3

12

R192

221R3F

12

R198

DUMMY-R3

CLKGEN_PD#

SEL2

+3VRUN

CPU & MEMORY Freq. Selection

+3VRUN

R564

1KR3

R565

DUMMY-R3

+VCCT

12

R147

1KR3

2

12

R562

1KR3

12

R563

DUMMY-R3

12

31

R146

10KR3

Q16

DTC114TK

12

H_BSEL14

H_BSEL04

RUN_ON32

MMBT3904-U

VTTPWRGOOD5

12

R193

10KR3

12

+VCCT +3VRUN

12

R150

10KR3

1

3

2

Q17

MMBT3904

Filtering CKT for

48MHz power plane

L26

12

BLM21A601S

No stuff:

caps are internal to CK-TITAN.

BC616

SC4D7U10V6KX

BC200

SC10P

BC203

SC10P

R191

10KR3

1 2

CLK66_VCH11

CLKGEN_48MPWR

12

R222

2MR3

BC165

SCD01U50V3KX

PM_STPPCI#16

PM_STPCPU#16

NO STUFF

PM_SLP_S1#16

1 2

1 2

CLKGEN_+3VRUN

BC161

SC4D7U10V6KX

U25

1

VDD

8

VDD

14

VDD

19

VDD

32

VDD

37

VDD

46

VDD

50

VDD

2

XIN

3

XOUT

40

S2

55

S1

54

S0

25

PD#/SRESET#

34

PCI_STP#

53

CPU_STP#

28

VTT_PG#

43

MULT0

29

SDATA

30

SCLK

33

3V66_0

35

3V66_1/VCH

42

IREF

41

VSSIREF

4

VSS

9

VSS

15

VSS

20

VSS

31

VSS

36

VSS

47

VSS

ICS950806

C-Note 2 use the symbol of

C9827 to replace that of

ICS950806.

CLK14_ICH16

CLK14_SIO28

CRYPT_14M6

BC163

SCD1U10V2MX

66IN/3V66_5

66B2_3V66_4

66B1/3V66_3

66B0/3V66_2

R190

33R3

R189

33R3

R188

33R3

BC166

SCD1U10V2MX

VDDA

VSSA

CPU2

CPU/2

CPU1

CPU/1

CPU0

CPU/0

PCIF2

PCIF1

PCIF0

PCI6

PCI5

PCI4

PCI3

PCI2

PCI1

PCI0

48MUSB

48MDOT

REF

12

12

CLK_14M PCLKR_DEBUGBD

12

26

27

45

44

49

48

52

51

24

23

22

21

7

6

5

18

17

16

13

12

11

10

39

38

56

BC162

SCD1U10V2MX

BC167

SCD1U10V2MX

CLK_CPU 4

CLK_CPU# 4

CLK_MCH 7

CLK_MCH# 7

CLK_ITP 6

CLK_ITP# 6

CLKGBINR_MCH

CLK66R_ICH

CLKPCIFR_ICH

CLKAPICR_CPU

CLKAPICR_ICH

PCLKR_SIO

PCLKR_PCM

PCLKR_FWH

CLKDREFR_MCH

BC206

SCD1U10V2MX

PCLKR_KBC

PCLKR_MINI

PCLKR_1394

CLK48R_ICH

CLKGEN_APWR

BC618

SCD01U50V3KX

R234

1 2

33R3

R233

1 2

33R3

R225

1 2

33R3

R223

1 2

33R3

R224

1 2

33R3

R232

1 2

33R3

R231

1 2

22R3

R230

1 2

33R3

R229

1 2

33R3

R228

1 2

33R3

R227

1 2

33R3

R226

1 2

33R3

R194

1 2

22R3

R195

1 2

33R3

BC164

SCD1U10V2MX

BC623

SC4D7U10V6KX

12

R235

47R3

BC208

SC5P

BC207

1 2

0R3-0-U

1 2

PLACE NEAR EACH PIN

BC205

SCD1U10V2MX

+3VRUN

L27

BLM21A601S

12

R236

240KR3

CLKGBIN_MCH 7

CLK66_ICH 15

CLKPCIF_ICH 15

CLKAPIC_CPU 4

CLKAPIC_ICH 15

PCLK_SIO 28

PCLK_PCM 20

PCLK_FWH 26

PCLK_KBC 27

PCLK_MINI 22

PCLK_DEBUGBD 26

PCLK_1394 21

CLK48_ICH 16

CLKDREF_MCH 7

BC204

SCD1U10V2MX

CLKGBOUT_MCH 7

BC202

SCD1U10V2MX

New stepping of CK-408 chip has pin22 (66BUF1)

dedicate for GBIN use

BC201

SCD1U10V2MX

Almador checklist v0.93 9/08

CLK GEN. SECOND SOURCE

ICS : ICS950806 71.95806.00W

CYPRESS : W320-04X 71.00320.00W

Title

Size Document Number Rev

A3

Date: Sheet of

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

CLOCK GENERATOR

C-Note 2

3Friday, January 11, 2002

-3

37

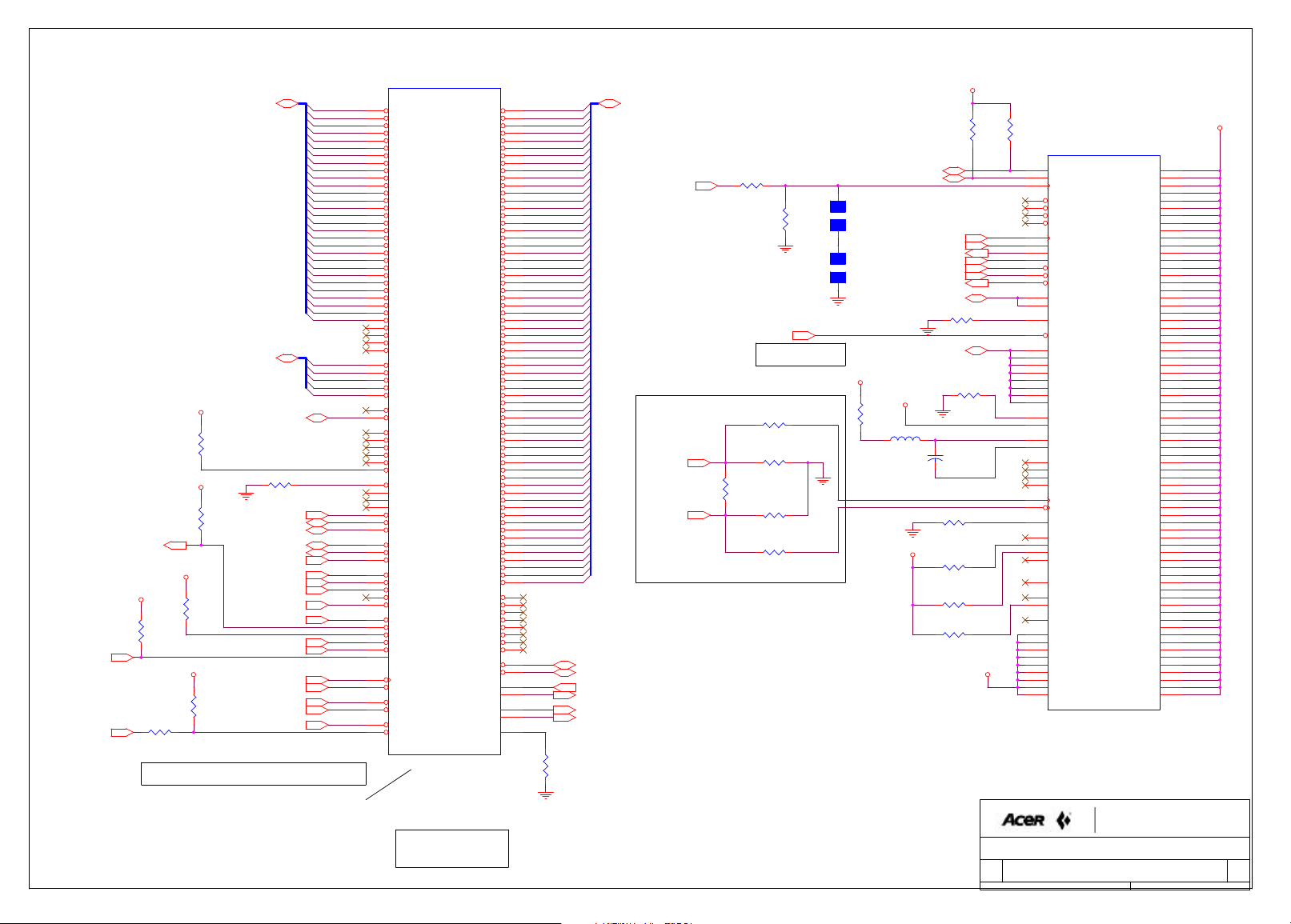

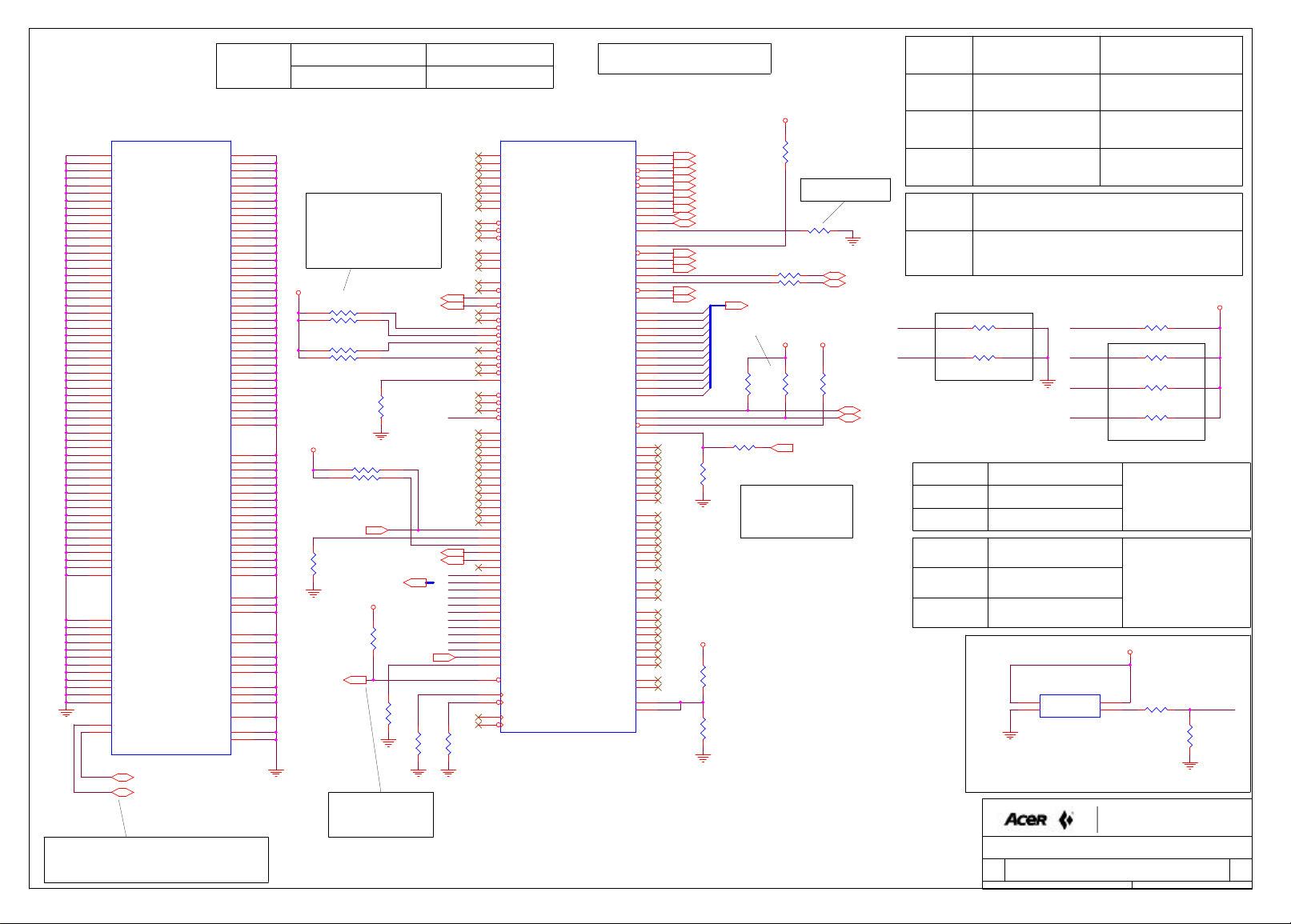

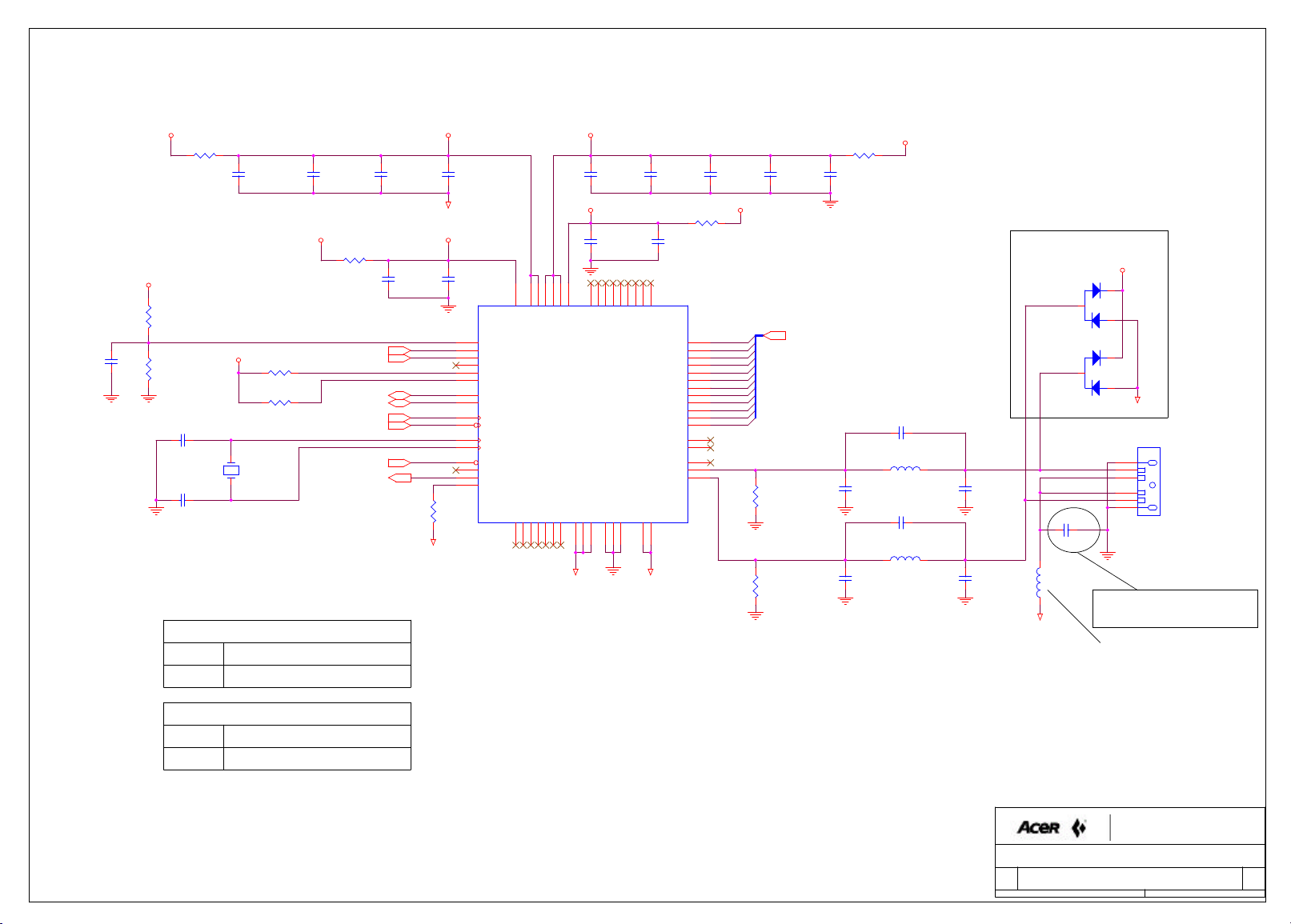

Page 4

U21A

www.kythuatvitinh.com

CG_DBSY# 7

CG_DRDY# 7

THERMDP 6

THERMDN 6

H_BSEL0 3

H_BSEL1 3

CG_HD#[63..0] 7

CLKAPIC_CPU3

Place near CPU

CLK_CPU3

CLK_CPU#3

R131

1 2

26D7R3F

PM_CPUPERF16

12

R515

475R3F

R130

137R3F

1 2

GHI#:internal

pull up to VCCT

R514

1 2

10R3F

R513

12

61D9R3F

R517

1 2

61D9R3F

R516

1 2

10R3F

12

R132

DUMMY-R3

12

BC110

DUMMY-C3

10pF

+VCCT

12

R507

0R3-0-U

CC_PICD015

CC_PICD115

CPU_COMSREF5

+VCC_CORE

L25

1 2

IND-4D7UH

+VCCT

CG_HA#[31..3]7

CG_REQ#[0..4]7

+1.5VRUN

12

+1.5VRUN

12

CC_FERR#15

+1.5VRUN

+1.8VRUN

CC_CPUPWRGD15

CG_CPURST#7

12

R519

12

R512

1K5R3

R487

1 2

0R3-0-U

Layout note:

Place CPU_RST# Resistor < 0.1" from CPU

3KR3

CC_CPUPWRGD

+VCCT

12

R488

56D2R3F

R518

1K5R3

R520

1K5R3

CG_ADS#7

R504

1 2

10R3

CG_BPRI#7

CG_BNR#7

CG_LOCK#7

CG_HIT#7

CG_HITM#7

CG_DEFER#7

CG_RS#07

CG_RS#17

CG_RS#27

CG_TRDY#7

CC_A20M#15

CC_IGNNE#15

CC_SMI#15

CC_STPCLK#15

CC_DPSLP#15

CC_INTR15

CC_NMI15

CC_INIT#15

CG_HA#3

CG_HA#4

CG_HA#5

CG_HA#6

CG_HA#7

CG_HA#8

CG_HA#9

CG_HA#10

CG_HA#11

CG_HA#12

CG_HA#13

CG_HA#14

CG_HA#15

CG_HA#16

CG_HA#17

CG_HA#18

CG_HA#19

CG_HA#20

CG_HA#21

CG_HA#22

CG_HA#23

CG_HA#24

CG_HA#25

CG_HA#26

CG_HA#27

CG_HA#28

CG_HA#29

CG_HA#30

CG_HA#31

CG_REQ#0

CG_REQ#1

CG_REQ#2

CG_REQ#3

CG_REQ#4

CC_IERR#

CG_BREQ0#

CC_FERR#

CC_FLUSH#

CPU_RST#

AF23

AD23

AC3

AF6

AF5

AD9

AD3

AB4

AE4

AF8

AD15

AE14

AE6

K1

J1

G2

K3

J2

H3

G1

A3

J3

H1

D3

F3

G3

C2

B5

B11

C6

B9

B7

C8

A8

A10

B3

A13

A9

C3

C12

C10

A6

A15

A14

B13

A12

R1

L3

T1

U1

L1

T4

AA3

W2

AB3

P3

C14

AF4

A7

C4

C22

R2

L2

V3

AA2

U2

T3

Y3

V1

U3

M5

W1

B15

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

CPU

REQ3#

REQ4#

RP#

1/4

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

NC

NC

NC

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

RS0#

RS1#

RS2#

RSP#

TRDY#

A20M#

FERR#

FLUSH#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

INTR/LINT0

NMI/LINT1

INIT#

RESET#

BGA479-SKT-2-U

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

THERMDA

THERMDC

SELFSB0

SELFSB1

EDGECTRLP

A16

CG_HD#0

D0#

B17

CG_HD#1

D1#

A17

CG_HD#2

D2#

D23

CG_HD#3

D3#

B19

CG_HD#4

D4#

C20

CG_HD#5

D5#

C16

CG_HD#6

D6#

A20

CG_HD#7

D7#

A22

CG_HD#8

D8#

A19

CG_HD#9

D9#

A23

CG_HD#10

A24

CG_HD#11

C18

CG_HD#12

D24

CG_HD#13

B24

CG_HD#14

A18

CG_HD#15

E23

CG_HD#16

B21

CG_HD#17

B23

CG_HD#18

E26

CG_HD#19

C24

CG_HD#20

F24

CG_HD#21

D25

CG_HD#22

E24

CG_HD#23

B25

CG_HD#24

G24

CG_HD#25

H24

CG_HD#26

F26

CG_HD#27

L24

CG_HD#28

H25

CG_HD#29

C26

CG_HD#30

K24

CG_HD#31

G26

CG_HD#32

K25

CG_HD#33

J24

CG_HD#34

K26

CG_HD#35

F25

CG_HD#36

N26

CG_HD#37

J26

CG_HD#38

M24

CG_HD#39

U26

CG_HD#40

P25

CG_HD#41

L26

CG_HD#42

R24

CG_HD#43

R26

CG_HD#44

M25

CG_HD#45

V25

CG_HD#46

T24

CG_HD#47

M26

CG_HD#48

P24

CG_HD#49

AA26

CG_HD#50

T26

CG_HD#51

U24

CG_HD#52

Y25

CG_HD#53

W26

CG_HD#54

V26

CG_HD#55

AB25

CG_HD#56

T25

CG_HD#57

Y24

CG_HD#58

W24

CG_HD#59

Y26

CG_HD#60

AB24

CG_HD#61

AA24

CG_HD#62

V24

CG_HD#63

AE24

AD25

AE25

AC24

AF24

AD26

AC26

AD24

W3

Y1

AF13

AF14

AE12

AF10

AF16

12

R495

110R3F

ITP_TCK6

ITP_TDI6

ITP_TDO6

ITP_TMS6

ITP_TRST#6

ITP_PREQ#6

ITP_PRDY#6

1 2

AGTLREF5,7

12

R506

1KR3

R478

1 2

14R3F

R490

1 2

1KR3

R505

1 2

1KR3

+1.5VRUN

1 2

APICCLK_CPU

R489

56D2R3F

R508

1 2

1KR3

TC16

ST33U8VM

12

+VCC_CORE

R480

150R3

R481

150R3

1 2

CPU_PLL1

CPU_PLL2

CLK_BCLK

CLK_BCLK#

AD19

AD17

AF20

AF22

AE20

AD22

AD21

AD10

AD7

AD11

AF7

AF15

AF19

AE22

AF12

AD5

AE16

AF21

AB26

H26

AF9

AA1

AC1

AD1

AF18

AD16

AF11

AE8

N24

AE10

AB6

AA5

AC5

L5

A21

A4

N1

Y4

R5

N3

N2

P1

P5

E1

F1

M1

E2

P4

M6

P6

W5

Y6

U5

V6

U21B

PICD0

PICD1

PICCLK

BP2#

BP3#

BPM0#

BPM1#

TCK

TDI

TDO

TMS

TRST#

PREQ#

PRDY#

CMOSREF_1

CMOSREF_0

RTTIMPEDP

GHI#

VREF_1

VREF_2

VREF_3

VREF_4

VREF_5

VREF_6

VREF_7

VREF_8

TESTLO

VCC

PLL1

PLL2

CPU

NC

NC

NC

2/4

NC

CLK0

CLK0#

TESTLO

NC

NCHCTRLP

TESTHI

NC

NC

NC

TESTHI

NC

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_75

VCC_74

VCC_73

VCC_72

BGA479-SKT-2-U

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

D22

F22

E21

H22

G21

K22

J21

M22

L21

P22

N21

T22

R21

V22

U21

Y22

W21

AB22

AA21

AC21

D20

F20

E19

AB20

AA19

AC19

D18

F18

E17

AB18

AA17

AC17

D16

F16

E15

AB16

AA15

AC15

D14

F14

E13

AB14

AA13

AC13

D12

F12

E11

AB12

AA11

AC11

D10

F10

E9

AB10

AA9

AC9

D8

F8

E7

AB8

AA7

AC7

D6

F6

E5

H6

G5

K6

J5

N5

T6

+VCC_CORE

P/N update to 62.10053.061 (BGA479-SKT-2-U)

7/12

CPU SOCKET SECOND SOURCE

AMP : 62.10053.061

FOXCONN: 62.10055.011

Title

Size Document Number Rev

A3

Date: Sheet of

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

CPU

C-Note 2

4Friday, January 11, 2002

-3

37

Page 5

AA25

www.kythuatvitinh.com

AC25

AF25

AE26

AB23

AE23

AB21

AA22

AC22

AE21

AB19

AA20

AC20

AE19

AB17

AA18

AC18

AE17

AB15

AA16

AC16

AE15

AF17

U21C

E16

VSS_0

R4

VSS_1

E25

VSS_2

G25

VSS_3

J25

VSS_4

L25

VSS_5

N25

VSS_6

R25

VSS_7

U25

VSS_8

W25

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

C23

VSS_14

F23

VSS_15

H23

VSS_16

K23

VSS_17

M23

VSS_18

P23

VSS_19

T23

VSS_20

V23

VSS_21

Y23

VSS_22

VSS_23

VSS_24

B22

VSS_25

D21

VSS_26

F21

VSS_27

E22

VSS_28

H21

VSS_29

G22

VSS_30

K21

VSS_31

J22

VSS_32

M21

VSS_33

L22

VSS_34

P21

VSS_35

N22

VSS_36

T21

CPU

VSS_37

R22

VSS_38

V21

VSS_39

U22

3/4

VSS_40

Y21

VSS_41

W22

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

B20

VSS_47

D19

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

B18

VSS_53

D17

VSS_54

F17

VSS_55

E18

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

B16

VSS_61

D15

VSS_62

F15

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

B14

VSS_68

D13

VSS_69

F13

VSS_70

C1

NC

NC

VSS_142

VSS_141

VSS_140

VSS_139

VSS_138

VSS_137

VSS_136

VSS_135

VSS_134

VSS_133

VSS_132

VSS_131

VSS_130

VSS_129

VSS_128

VSS_127

VSS_126

VSS_125

VSS_124

VSS_123

VSS_122

VSS_121

VSS_120

VSS_119

VSS_118

VSS_117

VSS_116

VSS_115

VSS_114

VSS_113

VSS_112

VSS_111

VSS_110

VSS_109

VSS_108

VSS_107

VSS_106

VSS_105

VSS_104

VSS_103

VSS_102

VSS_101

VSS_100

VSS_99

VSS_98

VSS_97

VSS_96

VSS_95

VSS_94

VSS_93

VSS_92

VSS_91

VSS_90

VSS_89

VSS_88

VSS_87

VSS_86

VSS_85

VSS_84

VSS_83

VSS_82

VSS_81

VSS_80

VSS_79

VSS_78

VSS_77

VSS_76

VSS_75

VSS_74

VSS_73

VSS_72

VSS_71

NC

BGA479-SKT-2-U

F19

E20

C25

A25

AE1

AD2

AB2

Y2

V2

T2

P2

M2

K2

H2

F2

D2

B2

W4

U4

M3

K4

H4

F4

D4

B4

AE5

AC6

AA6

AB5

W6

Y5

U6

V5

R6

T5

L6

N6

J6

K5

G6

H5

F5

B6

AE7

AC8

AA8

AB7

E8

F7

D7

B8

AE9

AC10

AA10

AB9

E10

F9

D9

B10

AE11

AC12

AA12

AB11

E12

F11

D11

B12

AE13

AC14

AA14

AB13

E14

N4

+VCC_CORE

BC552

SC10U6D3V5MX

+VCC_CORE

BC556

SCD1U10V2MX

+VCC_CORE

BC518

SCD1U10V2MX

AGTLREF4,7

BC549

SC10U6D3V5MX

BC566

SCD1U10V2MX

BC576

SCD1U10V2MX

GTLREF( 2/3 +VCCT)

+VCCT

12

R125

1KR3F

12

R126

BC590

2KR3F

SCD1U10V2MX

Place caps near CPU

BC112

BC554

SC10U6D3V5MX

BC577

SCD1U10V2MX

BC528

SCD1U10V2MX

NO STUFF

SC10U10V-U

BC530

SCD1U10V2MX

BC529

SCD1U10V2MX

BC519

SC10U6D3V5MX

Place resistors

between GMCH

and CPU

BC589

SCD1U10V2MX

BC515

SCD1U10V2MX

BC523

SCD1U10V2MX

BC526

SC10U6D3V5MX

BC107

SCD1U10V2MX

BC551

SC10U6D3V5MX

BC514

SCD1U10V2MX

BC567

SCD1U10V2MX

BC512

SCD1U10V2MX

BC550

SC10U6D3V5MX

BC548

SCD1U10V2MX

BC527

SCD1U10V2MX

BC555

SC10U6D3V5MX

BC520

SCD1U10V2MX

BC516

SCD1U10V2MX

BC547

SCD1U10V2MX

BC513

SCD1U10V2MX

BC553

SC10U6D3V5MX

BC522

SCD1U10V2MX

BC572

SCD1U10V2MX

BC565

SCD1U10V2MX

BC525

SCD1U10V2MX

BC707

SC10U6D3V5MX

BC524

SCD1U10V2MX

BC571

SCD1U10V2MX

BC570

SCD1U10V2MX

BC531

SCD1U10V2MX

BC708

SC10U6D3V5MX

BC574

SCD1U10V2MX

BC521

SCD1U10V2MX

BC517

SCD1U10V2MX

BC578

SCD1U10V2MX

BC709

SC10U6D3V5MX

+VCCT

W23

AA23

AD20

AD18

AD14

AD12

AC23

CPU_COMSREF4

A26

G23

J23

L23

N23

R23

U23

C21

C19

C17

C15

C13

C11

C9

C7

AD8

C5

AD6

AA4

E4

G4

J4

L4

AC4

V4

AE3

AF2

AF1

U21D

VCCT_1

VCCT_2

VCCT_3

VCCT_4

VCCT_5

VCCT_6

VCCT_7

VCCT_8

VCCT_9

VCCT_10

VCCT_11

VCCT_12

VCCT_13

VCCT_14

VCCT_15

VCCT_16

VCCT_17

VCCT_18

VCCT_19

VCCT_20

VCCT_21

VCCT_22

VCCT_23

VCCT_24

VCCT_25

VCCT_26

VCCT_27

VCCT_28

VCCT_29

VCCT_30

VCCT_31

VCCT_32

VCCT_33

VCCT_34

VCCT_35

BGA479-SKT-2-U

CPU

4/4

VTTPWRGOOD

CMOSREF

+1.5VRUN

VCCT_36

VCCT_37

VCCT_38

12

R491

510R3-1

12

R137

1KR3F

AD4

NC_1

A5

NC_2

D1

NC_3

AD13

NC_4

B1

NC_5

P26

NC_6

A11

NC_7

VID0

VID1

VID2

VID3

VID4

VSS

VSS

VSS

NC

NC

+VCCT

A2

AE18

AB1

AC2

AE2

AF3

R3

B26

M4

AF26

E3

D26

D5

E6

Almador checklist v0.93

9/08

BC558

SCD1U10V2MX

+VCCT

CPU_VID0 31

CPU_VID1 31

CPU_VID2 31

CPU_VID3 31

CPU_VID4 31

VTTPWRGOOD 3

BC579

SCD1U10V2MX

Place caps near CPU

+VCC_CORE

BC568

SCD1U10V2MX

BC575

SCD1U10V2MX

Decouping Recommendation

Underneath balls

VCC_CORE

on solder side

On the peripheral

near balls

Bulk Caps

Place close to

processor for all

VCCT

Bulk Caps

0.22uF * 24

10uF / 6.3V * 10

1uF * 10

Use 2-3 vias per pad for reduced

inductance during layout

Placement should be near

processor for all

Use 2 vias per pad for reduced

inductance during layout

Almador-M Checklist Ver. 0.93 9/08

BC573

SCD1U10V2MX

C-Note 2

0.1uF * 24

10uF / 10V * 10

220uF / 2.5V * 7

0.1uF * 10

220uF / 2.5V * 2

BC569

SCD1U10V2MX

Kenora Ver 0.93

10uF / 6.3V * 10 + 6 * NS

150uF / 4V * 12 + 2 * NS

1uF * 10 + 2 * NS

150uF / 4V * 5 + 1 * NS

0.47uF * 24

Title

Size Document Number Rev

Custom

Date: Sheet of

CPU CONFIGURATION

C-Note 2

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

5Friday, January 11, 2002

37

-3

Page 6

THERMDP4

www.kythuatvitinh.com

THERMDN4

1

2

Q41

MMBT3904

3

MMBT3904-U

BC508

SC2K2P

BC509

SC2K2P

BC507

SCD1U

THERMDP

THERMDN

THERMDP2

G768_PWRGD

12

R536

100KR3

+5VRUN

1

2

3

4

5

6

7

8

U20

OUT1

VCC

DXP1

DXN

DXP2

RESET#

GND

GND

G768B

OUT2

VCC

SMBCLK

SMBDATA

ALERT#

FG2

FG1

CLK

*Layout* 15 mil

16

15

14

13

12

11

10

9

1 2

BC489

SCD1U

KBC_SCL 27

KBC_SDA 27

G768_32K 17

R463

0R3-0-U

BC488

SC10U10V6ZY-U

FAN1_FG

THRM# 16

FAN1_VCC

12

1 2

R461 0R3-0-U

R464 0R3-0-U

BC103

DUMMY-C3

FAN1_FG

D27

S1N4148

1 2

1 2

+5VRUN

12

R719

DUMMY-R3

THRM_SHUT

FAN1_VCC_1

CN10

1

2

3

CON3-4

+3VRUN

12

R641

10KR3

31

Q59

DTC124EUA-U

2222K

2

K

NO STUFF

G768_PWRGD

SW_THER_EN#16

1 2

R652 0R3-0-U

1 2

R653 0R3-0-U

NO STUFF

THERMAL SENSOR & FAN CONTROLLER

R721

1 2

20KR3D

D

Q81

1

2N7002

G

S

2 3

12

R389

10KR3

U77

1

SET

2

GND

3

OUT#

MAX6510HAUT-T

HW thermal shutdown

temperature setting = 75 degree

HW_SHUT 16,33

VCC

OUTSET

HYST

6

5

4

+3VRUN

TH_CHANGE27

+3VRUN

2 3

14

7

R720

1 2

10K5R3F

NO STUFF

from SOVP

U33A

1

TSLCX125

R722

0R3-0-U

R723

0R3-0-U

+3VRUN

12

12

Cover Switch Crypto Card CONN

+3VSUS

+VCCT

12

12

R448

56D2R3F

R449

1 2

240R3

12

R492

39R3

R363

10KR3

COVER+COVERUP_3COVERUP#

+1.5VRUN

12

CN5

1

2

CON2-10

R499

39R3

TP10

TPAD30

TP21

TPAD30

TP16

TPAD30

TP19

TPAD30

TP20

TPAD30

TP17

TPAD30

TP18

TPAD30

TP15

TPAD30

TP1

TPAD30

CRYPT_14M3

+1.5VRUN

12

12

R493

150R3

R494

1K5R3

12

R498

200R3

1 2

ITP_TDI 4

ITP_TDO 4

ITP_TRST# 4

ITP_PREQ# 4

R128

240R3

12

R479

200R3

+3VSUS

U1A

147

TSAHC14

COVERUP14,27

+3VSUS

BC604

SCD1U

U73

5

DRUNPWROK14,16,27

4

NC7SZ08

VCC

Y

GND

A

B

12

1

2

3

+3VSUS

G768_PWRGD

U1B

TSAHC14

12

R537

240R3

+3VSUS

147

34

SCD1U

CG_CPURST#7

ITP_DBREST#

ITP_TCK4

ITP_TMS4

BC347

SCD1U

BC443

R364

1 2

10KR3

VCC_RTC

12

R172

22KR3

+VCCT

12

R129

56D2R3F

+3VRUN

CN13

12

9

7

5

3

1

11

HRS-CONN10D-1

BC109

SCD1U

ITP_PRDY# 4

1.5K pull down if ITP/TAP unused

Almador checklist v0.93 9/08

PULLUP RESISTOR<1"FROM ITP PORT PINS

VCC_RTC

BC134

SCD1U

10

8

6

4

2

CLK_ITP3

CLK_ITP#3

DM2_SDATA 10,14,27

DM2_SCLK 10,14,27

PCIRST# 15INTRUDER#15

Title

Size Document Number Rev

A3

Date: Sheet of

BC135

SCD1U

R184

12

61D9R3F

R183

1 2

61D9R3F

R185

1 2

12

33R3F

R187

475R3F

R186

1 2

33R3F

per Intel

NO STUFF

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221.

Taiwan ,R.O.C.

ITP/Thermal/Fan Control/RFID

C-Note 2

TP6

TPAD30

TP7

TPAD30

6 37Friday, January 11, 2002

-3

Page 7

1 2

www.kythuatvitinh.com

1 2

M_DQM[0..7] 10

M_CS#[0..3] 10

1 2

1 2

1 2

1 2

M_CKE[0..3] 10

1 2

1 2

1 2

BC105

SC22P

GMCH(1/3)

M_MA2

M_MA3

M_MA0

M_MA1

M_MA6

M_MA7

M_MA5

M_MA11

M_MA10

M_MA8

M_MA9

M_MA12 M_RMA12

NO STUFF

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

C-Note 2

M_RMA[0..12] 10

M_MA0

M_MA1

M_MA2

M_MA3

M_MA4

M_MA5

M_MA6

M_MA7

M_MA8

M_MA9

M_MA10

M_MA11

M_MA12

R465 10R3

M_BA0

R475 10R3

M_BA1

M_DQM0

M_DQM1

M_DQM2

M_DQM3

M_DQM4

M_DQM5

M_DQM6

M_DQM7

M_CS#0

M_CS#1

M_CS#2

M_CS#3

CLKSDRAM0

CLKSDRAM1

CLKSDRAM2

CLKSDRAM3

M_CKE0

M_CKE1

M_CKE2

M_CKE3

M_SRAS#

M_SCAS#

M_BMWE#

SM_ORCLK

R120 10R3

R123 10R3

R121 10R3

R122 10R3

R118 10R3

R119 10R3

R117 10R3

SMREF 9

Route 0.15"+/-50mil trace

Title

Size Document Number Rev

A3

Date: Sheet of

CG_HD#[0..63]4 CG_HA#[3..31] 4

AGP_REF used as

DVO_REF for DVO device

+1.5VRUN

BC510

SC470P50V3JN

R471

1KR3F

R473

1KR3F

12

R474

82R3F

AGP_REF

12

R472

82R3F

BC511

SC470P50V3JN

R442 54D9R3F

1 2

R453 27D4R3F

1 2

R451 54D9R3F

1 2

R450 54D9R3F

1 2

AGTLREF4,5

BC557

SCD1U10V2MX

BC459

SCD1U10V2MX

BC477

SCD1U10V2MX

12

12

NO STUFF

Part Number Change to 71.0GMCH.M09

SM_RCOMP = 1/2 PCB impedance

DVO_RCOMP = PCB impedance

HUB_RCOMP = PCB impedance

AGP_RCOMP = PCB impedance

PCIRST#_315

BC445

SCD1U10V2MX

CG_HD#0

CG_HD#1

CG_HD#2

CG_HD#3

CG_HD#4

CG_HD#5

CG_HD#6

CG_HD#7

CG_HD#8

CG_HD#9

CG_HD#10

CG_HD#11

CG_HD#12

CG_HD#13

CG_HD#14

CG_HD#15

CG_HD#16

CG_HD#17

CG_HD#18

CG_HD#19

CG_HD#20

CG_HD#21

CG_HD#22

CG_HD#23

CG_HD#24

CG_HD#25

CG_HD#26

CG_HD#27

CG_HD#28

CG_HD#29

CG_HD#30

CG_HD#31

CG_HD#32

CG_HD#33

CG_HD#34

CG_HD#35

CG_HD#36

CG_HD#37

CG_HD#38

CG_HD#39

CG_HD#40

CG_HD#41

CG_HD#42

CG_HD#43

CG_HD#44

CG_HD#45

CG_HD#46

CG_HD#47

CG_HD#48

CG_HD#49

CG_HD#50

CG_HD#51

CG_HD#52

CG_HD#53

CG_HD#54

CG_HD#55

CG_HD#56

CG_HD#57

CG_HD#58

CG_HD#59

CG_HD#60

CG_HD#61

CG_HD#62

CG_HD#63

DVO_RCOMP

SM_RCOMP

HUB_RCOMP

AGP_REF

AGP_RCOMP

12

R124

80D6R3F

CLKGBOUT_MCH3

AC22

AB24

AB23

AC23

AA3

AD3

AB4

AB5

AA4

AA1

AA6

AB1

AC4

AA2

AB3

AD2

AD1

AC2

AB6

AC6

AC1

AF3

AD4

AD6

AC3

AH3

AE5

AE3

AG2

AF4

AF2

AE4

AG1

AE1

AG4

AH4

AG3

AF1

K24

AA7

U4

P1

W6

U2

U6

R1

N3

W5

V4

P3

R3

U1

V6

W4

T3

P2

V3

R2

T1

W3

U3

Y4

W1

V1

Y1

Y6

V2

Y3

Y2

AJ3

F6

J23

J25

J7

C2

U18A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DVOBC_RCOMP

SM_RCOMP

HL_RCOMP

AGPREF

AGP_RCOMP

RESET#

GTL_REFA

GTL_REFB

GTL_RCOMP

VSS

VSS

GRAPH-U1

HOST

BC440

SCD01U50V3KX

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

CPURST#

ADS#

BNR#

BPRI#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HL10

HLSTRB

HLSTRB#

HLREF

HTCLK

HTCLK#

DCLKREF

GBIN

GBOUT

1 2

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

R440

47R3

H2

E3

G3

N4

M6

F1

F2

J3

F3

P6

G1

N5

H1

P4

T4

M2

J2

L2

R4

K1

L3

L1

J1

N1

T5

H3

M3

M1

K3

R6

C1

E1

L4

G5

J4

F4

D3

D1

J6

G4

K6

M4

K5

K4

L6

H6

H4

G6

G26

H28

H29

H27

F29

F27

E29

E28

G25

G27

H26

G29

F28

H24

AJ4

AH5

AC19

AG26

AD24

CG_HA#3

CG_HA#4

CG_HA#5

CG_HA#6

CG_HA#7

CG_HA#8

CG_HA#9

CG_HA#10

CG_HA#11

CG_HA#12

CG_HA#13

CG_HA#14

CG_HA#15

CG_HA#16

CG_HA#17

CG_HA#18

CG_HA#19

CG_HA#20

CG_HA#21

CG_HA#22

CG_HA#23

CG_HA#24

CG_HA#25

CG_HA#26

CG_HA#27

CG_HA#28

CG_HA#29

CG_HA#30

CG_HA#31

CG_CPURST#

CG_ADS#

CG_BNR#

CG_BPRI#

CG_DBSY#

CG_DEFER#

CG_DRDY#

CG_HIT#

CG_HITM#

CG_LOCK#

CG_TRDY#

CG_REQ#0

CG_REQ#1

CG_REQ#2

CG_REQ#3

CG_REQ#4

CG_RS#0

CG_RS#1

CG_RS#2

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HL_STB

HL_STB#

HUBREF

CLK_HT

CLK_HT#

12

NO STUFF

BC469

SCD01U50V3KX

R38

10R3

BC47

SC10P

CG_CPURST# 4,6

CG_ADS# 4

CG_BNR# 4

CG_BPRI# 4

CG_DBSY# 4

CG_DEFER# 4

CG_DRDY# 4

CG_HIT# 4

CG_HITM# 4

CG_LOCK# 4

CG_TRDY# 4

CG_REQ#[0..4] 4

CG_RS#0 4

CG_RS#1 4

CG_RS#2 4

HL_[0..10] 15

HL_STB 15

HL_STB# 15

HUBREF 9,15

12

R445

10R3

BC442

SC10P

CLKDREF_MCH 3

CLKGBIN_MCH 3

12

R37

240KR3

NO STUFF

Almador checklist v0.93 9/08

M_MD[0..63]10

Per Intel Request

01/15

TP14

TPAD30

TP13

TPAD30

TP12

TPAD30

TP11

TPAD30

R44

1 2

33R3F

R46

1 2

61D9R3F

R84

1 2

61D9R3F

R83

1 2

33R3F

M_MD0

M_MD1

M_MD2

M_MD3

M_MD4

M_MD5

M_MD6

M_MD7

M_MD8

M_MD9

M_MD10

M_MD11

M_MD12

M_MD13

M_MD14

M_MD15

M_MD16

M_MD17

M_MD18

M_MD19

M_MD20

M_MD21

M_MD22

M_MD23

M_MD24

M_MD25

M_MD26

M_MD27

M_MD28

M_MD29

M_MD30

M_MD31

M_MD32

M_MD33

M_MD34

M_MD35

M_MD36

M_MD37

M_MD38

M_MD39

M_MD40

M_MD41

M_MD42

M_MD43

M_MD44

M_MD45

M_MD46

M_MD47

M_MD48

M_MD49

M_MD50

M_MD51

M_MD52

M_MD53

M_MD54

M_MD55

M_MD56

M_MD57

M_MD58

M_MD59

M_MD60

M_MD61

M_MD62

M_MD63

GMCH_E11

GMCH_F12

GMCH_E20

GMCH_F20

CLK_MCH 3

12

R45

475R3F

CLK_MCH# 3

Place near GMCH

D29

C29

D27

C27

A27

B26

E24

C25

E23

B25

C23

F22

B23

C22

E21

B22

C12

D10

C11

A10

C10

C8

C7

C5

D6

C4

E27

C28

B28

E26

C26

D25

A26

D24

F23

A25

G22

D22

A23

F21

D21

A22

F11

A11

B11

F10

B10

D9

C6

D7

D4

E11

F12

E20

F20

A7

E9

E8

A5

F8

B4

B8

B7

F9

A6

B5

E6

A4

U18B

SM_MD0

SM_MD1

SM_MD2

SM_MD3

SM_MD4

SM_MD5

SM_MD6

SM_MD7

SM_MD8

SM_MD9

SM_MD10

SM_MD11

SM_MD12

SM_MD13

SM_MD14

SM_MD15

SM_MD16

SM_MD17

SM_MD18

SM_MD19

SM_MD20

SM_MD21

SM_MD22

SM_MD23

SM_MD24

SM_MD25

SM_MD26

SM_MD27

SM_MD28

SM_MD29

SM_MD30

SM_MD31

SM_MD32

SM_MD33

SM_MD34

SM_MD35

SM_MD36

SM_MD37

SM_MD38

SM_MD39

SM_MD40

SM_MD41

SM_MD42

SM_MD43

SM_MD44

SM_MD45

SM_MD46

SM_MD47

SM_MD48

SM_MD49

SM_MD50

SM_MD51

SM_MD52

SM_MD53

SM_MD54

SM_MD55

SM_MD56

SM_MD57

SM_MD58

SM_MD59

SM_MD60

SM_MD61

SM_MD62

SM_MD63

NC

NC

NC

NC

GRAPH-U1

SDRAM SYSTEM MEMORY

A20

SM_MA0

B20

SM_MA1

B19

SM_MA2

C19

SM_MA3

A18

SM_MA4

A19

SM_MA5

C17

SM_MA6

C18

SM_MA7

B17

SM_MA8

A17

SM_MA9

A16

SM_MA10

C15

SM_MA11

C14

SM_MA12

B13

VSS

E14

VSS

C3

VSS

A14

VSS

B16

SM_BA0

C16

SM_BA1

F18

SM_DQM0

D18

SM_DQM1

D13

SM_DQM2

D12

SM_DQM3

E18

SM_DQM4

F17

SM_DQM5

F14

SM_DQM6

F13

SM_DQM7

E17

SM_CS0#

F16

SM_CS1#

D16

SM_CS2#

D15

SM_CS3#

A15

SM_CLK0

B2

SM_CLK1

B14

SM_CLK2

A3

SM_CLK3

A13

SM_CKE0

C9

SM_CKE1

C13

SM_CKE2

A9

SM_CKE3

C20

SM_RAS#

D19

SM_CAS#

A21

SM_WE#

A24

SM_OCLK

C24

SM_RCLK

E5

SM_REFA

F24

SM_REFB

Almador-M A3 stepping Design Guideline Update

Almador checklist

RS2N100J1-U

RN30

2

1 4

RS2N100J1-U

RN6

2

1 4

RS2N100J1-U

RN32

2

1 4

RS2N100J1-U

RN31

2

1 4

RS2N100J1-U

RN34

2

1 4

RS2N100J1-U

RN33

2

1 4

R476

1 2

10R3

M_RBA0 10

M_RBA1 10

CLK_SDRAM0 10

CLK_SDRAM1 10

CLK_SDRAM2 10

CLK_SDRAM3 10

M_RRAS# 10

M_RCAS# 10

M_RBMWE# 10

12/26/00

3

M_RMA2

M_RMA3

3

M_RMA0

M_RMA1

3

M_RMA6

M_RMA4M_MA4

3

M_RMA7

M_RMA5

3

M_RMA11

M_RMA10

3

M_RMA8

M_RMA9

-3

37

7Friday, January 11, 2002

Page 8

AGP_PAR

www.kythuatvitinh.com

Pull-up 8.2K to 1.5VRUN AGP device attached

Pull-down 2.2K to GND

DVO device attached

DVOA_CLK# (AG24) --> DVO_CLKIN1 (N8)

DVOA_CLK (AJ24) --> DVO_CLKIN0 (M8)

Almador EDS Rev 0.9 Apr.7

DVOA_D5

Int. P/D

DVOA_D6

Strapping Option for SW detection of AGP or DVO device

U18D

AD8

VSS

AD9

VSS

AD10

VSS

AJ21

VSS

AE8

VSS

AE9

VSS

AE10

VSS

AE11

VSS

AE12

VSS

AE13

VSS

AE17

VSS

AE19

VSS

AH21

VSS

AF8

VSS

AF9

VSS

AF10

VSS

AF11

VSS

AF12

VSS

AF13

VSS

AF14

VSS

AF15

VSS

AF16

VSS

AF17

VSS

AF18

VSS

AF19

VSS

AF20

VSS

AG7

VSS

AG15

VSS

AG16

VSS

AG21

VSS

AH6

VSS

AH8

VSS

AH9

VSS

AH11

VSS

AH12

VSS

AH14

VSS

AH17

VSS

AH18

VSS

B3

VSS

B6

VSS

B9

VSS

B12

VSS

B15

VSS

B18

VSS

B21

VSS

B24

VSS

B27

VSS

E7

VSS

E10

VSS

E13

VSS

E16

VSS

E19

VSS

E22

VSS

E25

VSS

G9

VSS

G21

VSS

E4

VSS

C21

VSS

F19

VSS

D28

VSS

K28

VSS

N28

VSS

T28

VSS

W28

VSS

AB28

VSS

L25

VSS

P25

VSS

U25

VSS

Y25

VSS

AE20

VSSA_DPLL0

G24

VSSA_DPLL1

GRAPH-U1

VSSA_DPLL1 9

VSSA_DPLL0 9

Connect pin AE20, G24(VSSA_DPLL[0,1]) to

the respective decoupling caps of pin

AC20, F25(VCCA_DPLL[0,1])

VSSA_CPLL

VSSA_HPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSA_DAC

M12

M13

M17

M18

N12

N13

N14

N15

N16

N17

N18

P13

P14

P15

P16

P17

R13

R14

R15

R16

R17

T13

T14

T15

T16

T17

U12

U13

U14

U15

U16

U17

U18

V12

V13

V17

V18

AJ5

D2

AC5

Y5

U5

P5

L5

H5

AH2

AE2

AB2

W2

T2

N2

K2

G2

AC7

AH19

AH20

AF5

G28

H25

AC26

AD22

AE28

AH24

AF25

AF27

AH26

G8

AD7

Add pull-ups to +1.5VRUN on

G_FRAME#, G_IRDY#,

G_TRDY#, G_DEVSEL#

in SVT planar

Almador checklist v0.93 9/08

+1.5VRUN

+1.5VRUN

12

AGP_BUSY#16

2

1 4

2

1 4

TV_POUT12

R439

4K7R3

RN67

RS2N472J1-U

RN68

RS2N472J1-U

RN5

2

1 4

RS2N822J1-U

Pull-up required

for ext. AGP GFX

and int. DVO GFX

3

3

TV_D[0..11]12

+3VRUN

12

AGP_PAR

12

R91

330R3

3

R441

10KR3

AGP_AD3017

12

R90

10KR3

+1.5VRUN

U18C

AA29

SBA0

AA24

SBA1

AA25

SBA2

Y24

SBA3

Y27

SBA4

Y26

SBA5

W24

SBA6

Y28

SBA7

AB26

PIPE#

AB29

WBF#

AB25

RBF#

AC28

ST0

AC29

ST1

AB27

ST2

L29

AD_STB0

L28

AD_STB0#

TV_D5

TV_D0

TV_D1

TV_D2

TV_D3

TV_D4

TV_D7

TV_D6

TV_D9

TV_D8

TV_D11

TV_D10

12

R43

10KR3

AA27

AA28

AC27

AD29

M29

M28

M27

N29

M25

N26

N27

R25

R24

U27

U26

W29

W26

W25

W27

AC24

AH15

AJ15

AJ16

AH16

U29

U28

R29

P26

P27

N25

R28

P28

L27

P29

R27

T25

J29

J28

K26

K25

L26

J27

K29

K27

L24

T29

T27

T26

V27

V28

V29

V25

Y29

AD_STB1

AD_STB1#

SB_STB

SB_STB#

G_FRAME#

G_IRDY#

G_TRDY#

G_STOP#

G_DEVSEL#

G_REQ#

G_GNT#

G_PAR

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

AGP_BUSY#

CTM

CTM#

CFM

CFM#

GRAPH-U1

TV_CLK12

TV_CLK#12

AGP_AD14

AGP_AD15

TV_VSYNC12

TV_HSYNC12

12

R42

10KR3

CRT

DDC1_DATA

DVOA_CLKINT

DVOA_BLANK#

DVOA_VSYNC

DVOA_HSYNC

GMBUS

DVOA_CLK#

DVI

DDC2_DATA

DVOA_INTR#

DVOA_FLD/STL

AGP,GPIO,DISPLAY,LOCAL MEMORY

DVOBC_CLKINT#

DVOB_FLD/STL

DVOBC_INTR#/DPMS_CLK

DVOC_FLD/STL

VSYNC

HSYNC

RED#

GREEN#

BLUE#

RED

GREEN

BLUE

DDC1_CLK

REFSET

I2C_CLK

I2C_DATA

DVOA_CLK

DVOA_D0

DVOA_D1

DVOA_D2

DVOA_D3

DVOA_D4

DVOA_D5

DVOA_D6

DVOA_D7

DVOA_D8

DVOA_D9

DVOA_D10

DVOA_D11

DDC2_CLK

DQ_A0

DQ_A1

DQ_A2

DQ_A3

DQ_A4

DQ_A5

DQ_A6

DQ_A7

DQ_B0

DQ_B1

DQ_B2

DQ_B3

DQ_B4

DQ_B5

DQ_B6

DQ_B7

CMD

SCK

RQ0

RQ1

RQ2

RQ3

RQ4

RQ5

RQ6

RQ7

GM_RCLK

GM_GCLK

RAM_REFA

RAM_REFB

AE29

AD28

AF28

AG28

AH27

AF29

AG29

AH28

AE27

AD27

AJ27

AD20

AD21

AF23

AF22

AD25

AC25

AG24

AJ24

AJ22

AH22

AG22

AJ23

AH23

AG23

AE23

AE24

AJ25

AH25

AG25

AJ26

AD26

AE26

AE21

AE22

AG17

AJ17

AG18

AJ18

AG19

AJ19

AG20

AJ20

AJ11

AH10

AJ10

AG10

AJ9

AG9

AJ8

AG8

AH7

AF7

AJ7

SIO

AG11

AJ12

AG12

AH13

AG13

AJ13

AG14

AJ14

AJ6

AG6

AE14

AD14

DAC_VSYNC 13

DAC_HSYNC 13

DAC_RED# 13

DAC_GREEN# 13

DAC_BLUE# 13

DAC_RED 13,30

DAC_GREEN 13,30

DAC_BLUE 13,30

CLK_DDC1 13

DAT_DDC1 13

DVO_BLANK# 11

DVO_VSYNC 11

DVO_HSYNC 11

DVO_CLK# 11

DVO_CLK 11

DVO_D0

DVO_D1

DVO_D2

DVO_D3

DVO_D4

DVO_D5

DVO_D6

DVO_D7

DVO_D8

DVO_D9

DVO_D10

DVO_D11

DVO_INTR#

+1.8VRUN

4.7K RDDP1.0 P.72

R41

1 2

12

15R3F

R40

75R3F

12

R446

576R3F

12

R447

2KR3F

12

R443

100KR3

Be close to pin

RDDP 1.0

R81

255R3F

R727 0R3-0-U

1 2

1 2

R728 0R3-0-U

DVO_D[0..11] 11

+1.5VRUN

+3VRUN

12

R80

10KR3

DVO_STALL 11

12

12

R82

10KR3

9/13 per Intel

DVO port of GMCH is

+1.5V Power plane

DVO port of VCH is

+1.8V Power plane

12

IO_I2C_CLK 11

IO_I2C_DATA 11

R39

100KR3

TV_I2C_DATA 12

TV_I2C_CLK 12

DVOA_D0

Int. P/U

DVOA_D1

Int. P/U

DVOA_D7

Int. P/D 1 : Invoking the XOR Chain test mode

DVOA_D8

Int. P/D 1 : Tri-stating all GMCH outputs when ICH3-M is

DVO_D0

DVO_D1

DVO_INTR# Pull-up 100K to 1.5VRUN

DVO_FIELD

DVO_CLKIN Pull-up 100K to 1.5VRUN

DDC1CLK

DDC1DAT

DDC2CLK

DDC2DAT

I2CCLK

I2CDATA

0 = DESKTOP

1 = MOBILE

0 = Dual ended term.

1 = Single ended term.Int. P/D

0 = 200MHz

1 = 133MHz

0 : IOQD = 1

1 : IOQD = 8

Pull-up 2.2K to V1.5S

Pull-up 2.2K to V1.5S

Pull-down 2.2K to GND

Pull-down 2.2K to GND

0 : Normal mode

0 : Normal mode

in XOR Chain mode.

R413 2K2R3

1 2

Per Intel GMCH EDS Rev0.7 12/22/2K

DVO_D5

R412 2K2R3

NO STUFF

R414 2K2R3

1 2

DVO_D6

R416 2K2R3

NO STUFF

R415 2K2R3

DVO_D7

R411 2K2R3

DVO_D8

Pull-down 100K to GND

Pull-up/down required

if DVOA not

implemented.

Pull-up 2.2K to +5VRUN

Pull-up 10K to +5VRUN

Non-5V tolerant,

Q-Switch required for

5V support

Pull-up 10K to +3VRUN

+3VRUN

OSC1

1

NC

2

GND

OSC-32.768KHZ-1

KODIAK 0.7b P.9 33MHz OSC

9/13 change to 32K OSC per Intel

Title

Size Document Number Rev

A3

Date: Sheet of

4

VDD

3

OUT

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

GMCH(2/3)

C-Note 2

1 2

1 2

NO STUFF

1 2

NO STUFF

1 2

NO STUFF

R115

1 2

732R3F

+1.5VRUN

AGP_AD30

12

R116

604R3F

8Friday, January 11, 2002

-3

37

Page 9

BC438

www.kythuatvitinh.com

SCD1U10V2MX

BC447

SCD1U10V2MX

BC426

SCD1U10V2MX

BC464

SCD1U10V2MX

BC435

SCD1U10V2MX

BC448

SCD1U10V2MX

BC421

SCD1U10V2MX

BC437

SCD1U10V2MX

BC436

SCD1U10V2MX

BC415

SCD1U10V2MX

BC427

SCD1U10V2MX

BC479

SCD1U10V2MX

BC478

SCD1U10V2MX

BC433

SCD1U10V2MX

BC434

SCD1U10V2MX

BC412

SCD1U10V2MX

BC425

SCD1U10V2MX

BC480

SCD1U10V2MX

BC441

SCD1U10V2MX

BC462

SCD1U10V2MX

BC458

SCD1U10V2MX

BC490

SCD01U50V3KX

BC446

SCD1U10V2MX

BC475

SCD1U10V2MX

BC422

SCD1U10V2MX

BC463

SCD1U10V2MX

BC420

SCD1U10V2MX

BC413

SCD1U10V2MX

BC439

SCD01U50V3KX

+VCCT

12

TC10

ST150U6D3VM-U

BC428

SCD1U10V2MX

BC417

SCD1U10V2MX

BC466

SCD01U50V3KX

+1.8VRUN

BC418

SCD1U10V2MX

+VCCT

Place C near AE16

and AE15 on GMCH

+3VSUS

BC483

SC68P

+1.5VRUN

BC455

SC22U10V-1

BC482

SCD1U10V2MX

+VCCT +VCCT

BC503

SCD1U10V2MX

AE16

AE15

AD15

AD16

AE25

AD23

AA26

AA23

W23

H23

K23

W7

AB7

M24

P24

T24

V24

Y23

M14

M15

M16

P12

R12

T12

P18

R18

T18

V14

V15

V16

J24

F26

N24

J26

M26

R26

V26

L23

U24

AE6

H7

K7

L7

N6

T6

Y7

G7

U18E

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VDD_LM

VCC_GPIO

VCC_GPIO

VCC_HUB

VCC_HUB

VCCQ_AGP

VCCQ_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCCA_HPLL

VCCA_CPLL

GRAPH-U1

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

VCC_SM

POWER

VCC_SM

VCC_SM

VCCQ_SM

VCCQ_SM

VCCQ_SM

VCCQ_SM

VCCQ_SM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_LM

VCC_CMOS

VCC_CMOS

VCC_CMOS

VCC_CMOS

VCC_DVO

VCC_DVO

VCC_DVO

VCCA_DAC

VCCA_DAC

VCCA_DPLL0

VCCA_DPLL1

F5

VTT

J5

VTT

M5

VTT

R5

VTT

V5

VTT

AA5

VTT

AD5

VTT

AG5

VTT

E2

VTT

A12

E12

G10

D5

D8

D11

D14

D17

D20

D23

D26

G11

G23

A8

G20

F7

F15

G19

E15

AC10

AC11

AD11

AD12

AD13

AE18

AD17

AD18

AD19

AF6

AE7

AC9

AC8

AC21

AF21

AF24

AF26

AG27

AC20

F25

Add at topside w/ shortest & widest Vcc trace directly to ball A8 & A12

Route ball A12 and A8 directly to respective decoupling capacitor

without going through a via first.

BC492

SCD1U10V2MX

BC454

SC68P

BC498

SCD1U10V2MX

+1.8VRUN

BC411

SCD1U10V2MX

+1.8VRUN

BC456

SCD1U10V2MX

GMCH_VCCADPLL0 GMCH_VADPLL0

GMCH_VCCADPLL1 GMCH_VADPLL1

BC419

SCD1U10V2MX

BC460

SCD1U10V2MX

12

TC8

ST150U6D3VM-U

12

TC9

ST150U6D3V-1-U

BC504

SC10U10V-U

CHECK

BC431

SCD1U10V2MX

L23

L-D1UH

L24

L-D1UH

+1.5VRUN

12

12

+3VSUS

BC444

SC22U10V-1

BC476

SCD1U10V2MX

BC457

SCD1U10V2MX

BC432

SCD1U10V2MX

BC467

SCD1U10V2MX

BC494

SCD1U10V2MX

BC470

SCD1U10V2MX

R444

1 2

1R3F

R452

1 2

1R3F

Almador-M A3 stepping Design Guideline Update

+VCCT

+VCCT

+1.8VRUN

BC465

SCD1U10V2MX

BC493

SCD1U10V2MX

BC468

SCD1U10V2MX

BC424

SCD1U10V2MX

VSSA_DPLL0 8

VSSA_DPLL1 8

BC474

SCD1U10V2MX

BC497

SCD1U10V2MX

BC491

SCD1U10V2MX

BC423

SCD1U10V2MX

BC473

SCD1U10V2MX

BC500

SCD1U10V2MX

BC414

SCD1U10V2MX

12/26/00

BC472

SCD1U10V2MX

BC501

SCD1U10V2MX

BC416

SCD1U10V2MX

BC496

SCD1U10V2MX

BC502

SCD1U10V2MX

BC471

SCD1U10V2MX

BC495

SCD1U10V2MX

SYSTEM MEMORY

Decouping Recommendation

V1.2S_GMCH

V1.2S_GMCHCORE

Decoupling

Caps

Bulk Caps

Decoupling

Caps

Bulk Caps

Decoupling

V1.5S_GMCH

Caps

Bulk Caps

Decoupling

V1.8S_GMCH

Caps

Bulk Caps

V3_GMCH

Decoupling

Caps

0.1uF * 10

10uF * 1

68pF * 1

0.1uF * 10

10uF * 1

0.1uF * 9

82pF * 4

0.1uF * 4 + 2

82pF * 2

0.1uF * 12 + 2

82pF * 4

Distribute as close as possible

to GMCH-M processor Quadrant

Close to VDD_LM, near pins AE15

and AE16 on Almador

Distribute as close as possible

to GMCH-M AGP/DVO Quadrant

Distribute as close as possible

to GMCH-M Local Memory Quadrant

Additional 4* 0.1uF shall be distributed

as close as possible to VCCPCMOS_LM

Distribute as close as possible to

GMCH-M System Memory Quadrant

Additional 4* 0.1uF shall be distributed

as close as possible to IO Quadrant

Bulk Caps

Almador-M Checklist Ver. 0.93 9/08

C-Note 2

0.1uF * 20

150uF / 6.3V * 2

68pF * 1 68pF * 1

220uF / 2.5V * 2

Kenora Ver 0.93

0.1uF * 20

150uF / 4V * 5 + 1 * NS

0.1uF * 28

150uF / 4V * 6

0.1uF * 11

0.01uF * 3

10uF /10V * 1

22uF /10V * 1

0.1uF * 6

0.1uF * 9

82pF * 4

22uF / 20V * 1

0.1uF * 4 + 2

0.01uF *2

82pF * 2

22uF / 20V * 2

68uF / 10V * 5

0.1uF * 20+2

22uF 10V * 1

10uF 10V * 1

82pF * 1

0.1uF * 12 + 2

82pF * 4

22uF / 20V * 2

HUB INTERFACE REF

1/2*1.8V

+1.8VRUN

12

R466

301R3F

12

BC499

SCD1U10V2MX

Layout Note:

Place divider pair in middle of bus.

Place capacitors near GMCH.

R467

301R3F

HUBREF 7,15

REF 0.55V

+3VRUN

+3VSUS

NO STUFF

12

12

R108

R729

249R3F

249R3F

12

R107

BC481

49D9R3F

SCD1U10V2MX

Place capacitor near GMCH ball E5 & F24.

Title

Size Document Number Rev

Custom

Date: Sheet of

GMCH(3/3)

C-Note 2

SMREF 7

BC461

SCD1U10V2MX

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

37

9Friday, January 11, 2002

-3

Page 10

(Reverse Type)(Normal Type)

www.kythuatvitinh.com

M_RMA[0..12]7

M_MD[0..63]7

M_CS#[0..3]7

M_DQM[0..7]7

M_CKE[0..3]7

M_RCAS#7

M_RRAS#7

M_RBA07

M_RBA17

M_RBMWE#7

M_MD0

M_MD1

M_MD2

M_MD3

M_MD4

M_MD5

M_MD6

M_MD7

M_DQM0

M_DQM1

M_RMA0

M_RMA1

M_RMA2

M_MD8

M_MD9

M_MD10

M_MD11

M_MD12

M_MD13

M_MD14

M_MD15

CLK_SDRAM07

M_RRAS#

M_RBMWE#

M_CS#0

M_CS#1

M_MD16

M_MD17

M_MD18

M_MD19

M_MD20

M_MD21

M_MD22

M_MD23

M_RMA6

M_RMA8

M_RMA9

M_RMA10

M_DQM2

M_DQM3

M_MD24

M_MD25

M_MD26

M_MD27

M_MD28

M_MD29

M_MD30

M_MD31

DM1_SDATA14,27

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

DM2

SDIMM144-13

+3VSUS+3VSUS

146

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

145

M_MD32

M_MD33

M_MD34

M_MD35

M_MD36

M_MD37

M_MD38

M_MD39

M_DQM4

M_DQM5

M_RMA3

M_RMA4

M_RMA5

M_MD40

M_MD41

M_MD42

M_MD43

M_MD44

M_MD45

M_MD46

M_MD47

M_CKE0

M_RCAS#

M_CKE1

M_RMA12

CLK_SDRAM1 7

M_MD48

M_MD49

M_MD50

M_MD51

M_MD52

M_MD53

M_MD54

M_MD55

M_RMA7

M_RBA0

M_RBA1

M_RMA11

M_DQM6

M_DQM7

M_MD56

M_MD57

M_MD58

M_MD59

M_MD60

M_MD61

M_MD62

M_MD63

DM1_SCLK 14,27

12

R531

0R3-0-U

M_MD0

M_MD1

M_MD2

M_MD3

M_MD4

M_MD5

M_MD6

M_MD7

M_DQM0

M_DQM1

M_RMA0

M_RMA1

M_RMA2

M_MD8

M_MD9

M_MD10

M_MD11

M_MD12

M_MD13

M_MD14

M_MD15

CLK_SDRAM27

M_RRAS#

M_RBMWE#

M_CS#2

M_CS#3

M_MD16

M_MD17

M_MD18

M_MD19

M_MD20

M_MD21

M_MD22

M_MD23

M_RMA6

M_RMA8

M_RMA9

M_RMA10

M_DQM2

M_DQM3

M_MD24

M_MD25

M_MD26

M_MD27

M_MD28

M_MD29

M_MD30

M_MD31

DM2_SDATA6,14,27

+3VSUS +3VSUS

DM1

145

1

2

3

4

5

6

7

8

9

SDIMM144-1U

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144143

146

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

M_MD32

M_MD33

M_MD34

M_MD35

M_MD36

M_MD37

M_MD38

M_MD39

M_DQM4

M_DQM5

M_RMA3

M_RMA4

M_RMA5

M_MD40

M_MD41

M_MD42

M_MD43

M_MD44

M_MD45

M_MD46

M_MD47

M_CKE2

M_RCAS#

M_CKE3

M_RMA12

CLK_SDRAM3 7

M_MD48

M_MD49

M_MD50

M_MD51

M_MD52

M_MD53

M_MD54

M_MD55

M_RMA7

M_RBA0

M_RBA1

M_RMA11

M_DQM6

M_DQM7

M_MD56

M_MD57

M_MD58

M_MD59

M_MD60

M_MD61

M_MD62

M_MD63

DM2_SCLK 6,14,27

12

R484

0R3-0-U

+3VSUS

BC583

SC4D7U10V5ZY

+3VSUS

BC586

SC4D7U10V5ZY

BC584

SC4D7U10V5ZY

BC585

SC4D7U10V5ZY

BC587

SC4D7U10V5ZY

BC588

SC4D7U10V5ZY

BC536

SCD1U

BC597

SCD1U

BC537

SCD1U

BC598

SCD1U

BC540

SCD1U

BC599

SCD1U

BC543

SCD1U

BC600

SCD1U

BC544

SC1000P50V3KX

BC602

SC1000P50V3KX

BC545

SC1000P50V3KX

BC603

SC1000P50V3KX

BC546

SC1000P50V3KX

BC605

SC1000P50V3KX

BC535

SC1000P50V3KX

BC606

SC1000P50V3KX

CLK_SDRAM1

R482

1 2

56R3

R485

1 2

56R3

BC538

SC10P

BC541

SC10P

CLK_SDRAM2CLK_SDRAM0

CLK_SDRAM3

SDRAM clock AC terminations change from 33 Ohm 22p to 56 Ohm 10p.

R483

1 2

56R3

R486

1 2

56R3

BC539

SC10P

BC542

SC10P

12/14/00

Title

Size Document Number Rev

Custom

Date: Sheet of

SO-DIMM

C-Note 2

Acer Incorporated

21F, 88, Sec. 1, Hsin Tai Wu Rd.,

Hsichih, Taipei Hsien 221,

Taiwan, R.O.C.

37

10Friday, January 11, 2002

-3

Page 11

+1.8VRUN

www.kythuatvitinh.com

+3VRUN

BC77

SCD1U10V2MX

+1.8VRUN

IO_I2C_CLK8

IO_I2C_DATA8

L13

1 2

BLM11B750S

+3VRUN

14

PCIRST#_315

CLK66_VCH3

BC76

SCD1U10V2MX

BC67

SCD1U10V2MX

2

RN28

SRN4D7KJ

3

BC86

SCD1U10V2MX

BC85

SCD1U10V2MX

+1.8VRUN_VCH

BC71

SCD1U10V2MX

12

R436

10R3

BC429

SC18P

NO STUFF

LCDVDD_ON14

BC65

SCD1U10V2MX

BL_ON14

BC68

SCD1U10V2MX

BC88

SCD1U10V2MX

BC89

SCD1U10V2MX

BC87

SCD1U10V2MX

D12

GMBSCL

D13

GMBSDA

B14

TESTIN

D14

PCIRST#

M12

OSC

E3

P[0]

E2

P[1]

E1