Page 1

A

www.kythuatvitinh.com

Digitally signed by dd

DN: cn=dd, o=dd,

ou=dd,

email=dddd@yahoo.

com, c=US

Date: 2009.11.20

21:04:32 +07'00'

B

C

D

E

CLOCK

GENERATOR

ICS9248-157

SDRAM CLK BUFFER

4 4

ICS9112BM-17

CPU CORE

REGULATOR

MAXIM MAXIM

MAX1717

PAGE:5

BATTERY

CHARGER

3 3

Controler

MAXIM

MAX1772

PAGE:29

1394Controller

PAGE:3

SYSTEM DC/DC

REGULATOR

MAX1631

BATTERY

CHARGER

FirmWare

(Ambit)

MC68HC908SR12

MINIPCI Socket

Actiontec

802.11b/Modem

TSB43AB22

ULTRA 33/66

2 2

PAGE:36 PAGE:19

card

UltraBay

PRIMARY

HDD

IBM(IC25N010/15/30ATDA04)

Hitachi(DK23CA-10/15/30)

CD ROM

TEAC CD-224E-B25

LG CRN-8245B

DVD ROM

Hitachi GD-S250

MKE SR-8175B

CD-RW

SONY CRX700E-10

1 1

DVD/CD-RW

Toshiba SD-R2002

FDD

USB PORT

PAGE:20

Infineon

IRMS6453

PAGE:34

A

USB

2 PORT

FIR

Serial

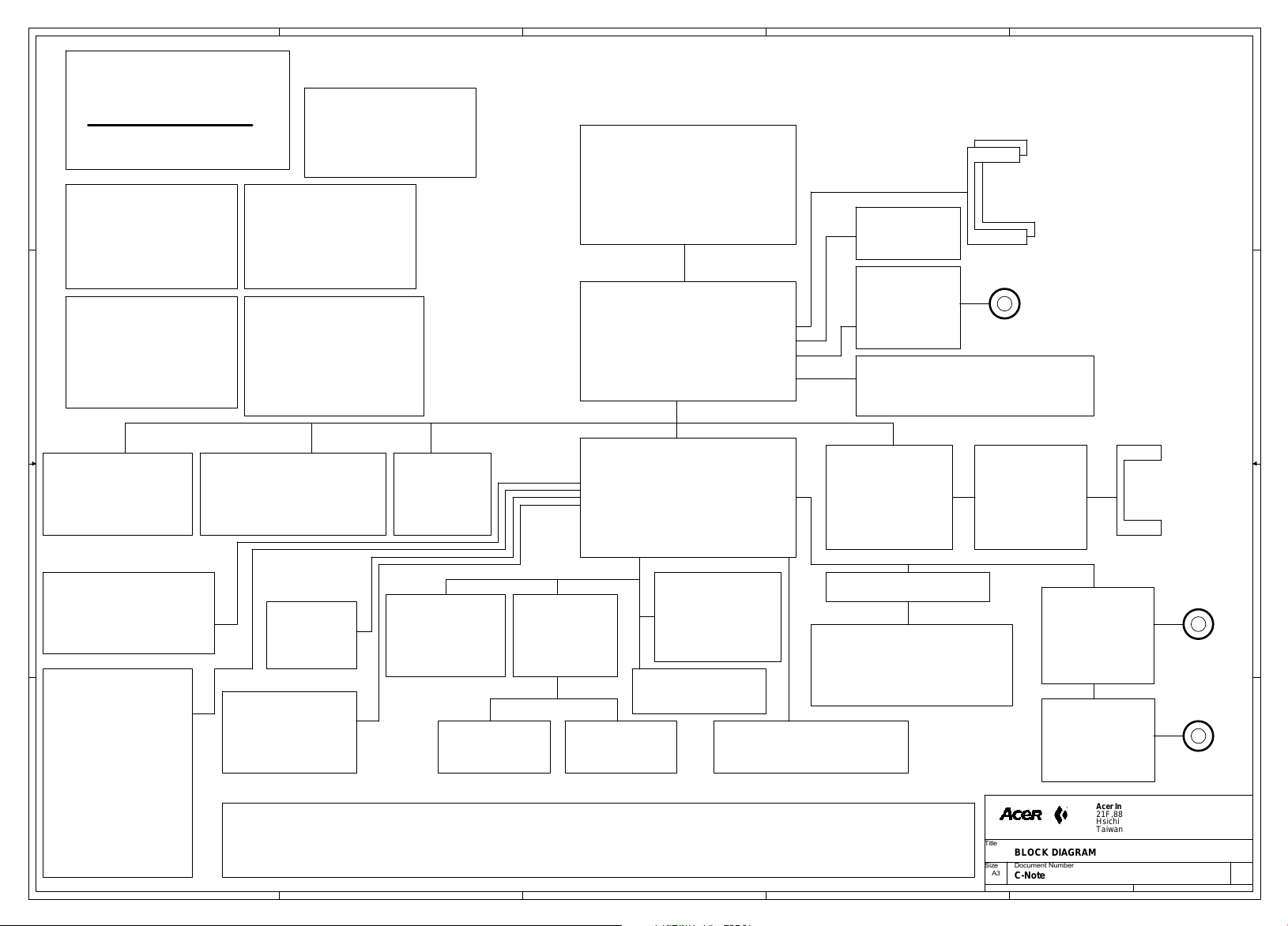

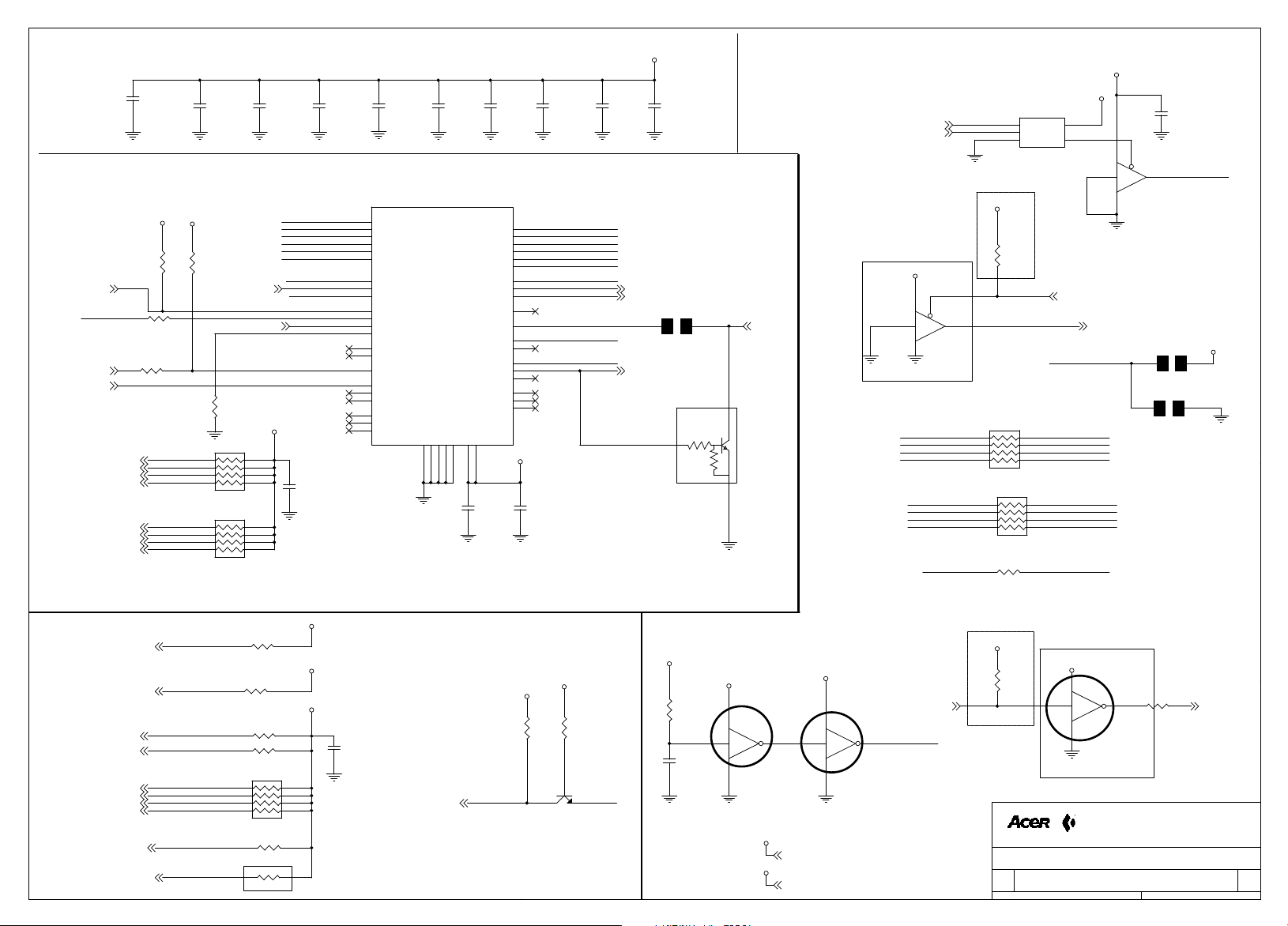

C-NOTE SYSTEM BLOCK DIAGRAM

Thermal&Fan

Controler

GMT

G768B

PAGE:28

PAGE:30

PAGE:22

VCC_CORE : 1.7 V/1.35V VCC_IO : 1.5V

100MHz Host Bus

LAN

Intel

ALI M1535-B1B

82550GY

PAGE:31

ISA BUS

RTC

KBC

Benchmarq Mitsubishi

PAGE:19

PAGE:27

BQ3285LF

PAGE:27 PAGE:23

TRACK

POINT

M38867

INT KB

Port Replicator (244PIN)

Printer RJ45 RJ11USBCRT PS2

B

CPU

Intel Mobile

PIII/CELERON

GEYSERVILIE

NB

ALI M1632-C

WITH VGA

/TRIDENT CYBERBLADE

PCI BUS/33MHz

SB

(With SIO)

BIOS

MXIC

MX29F004

4Mbit

Debug Port

PAGE:27

PAGE:27

Printer

Serial Port

Legency FDD

C

PAGE:4

PAGE:8

PAGE:16

PC100MHz

Trident

TV

EXPRESS

LCD

PAGE:14

PCMCIA

Controler

O2MICROTI

OZ6912

CDC connector

MODEM

CDCPORT

(AMBIT)

PORT

PAGE:24PAGE:21PAGE:21

Line

In

CRT

PAGE:13

PAGE:15

14' Samsung(LTN141X8-L00)

Hyuandai(HT14X14-101)

13' LG(LG/LP133X7-N2AD)

SANYO(TM133XG02L06B)

PAGE:12

Power

Switch

MICREL

PAGE:18

AC LINK

PAGE:35

Line

Out

AC

In

D

MIC2562A

PAGE:19

Title

BLOCK DIAGRAM

Size Document Number Rev

A3

C-Note

Date: Sheet of

2 So-DIMM

64MB Mitsubishi MH8S64AQFP-6L

128MB Samsung M464S1724CT2-L75

128MB Infineon

HYS64V16220GDL-7.5-C2

TV Out

PAGE:18

ONE SLOT

PAGE:18

AUDIO

MIC In

CODEC

Realtec

ALC200

PAGE:25

PAGE:24

OP AMP

TI

TPA0202

PAGE:26

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221,

Taiwan,R.O.C.

E

Line Out

1 36Monday, December 03, 2001

-4

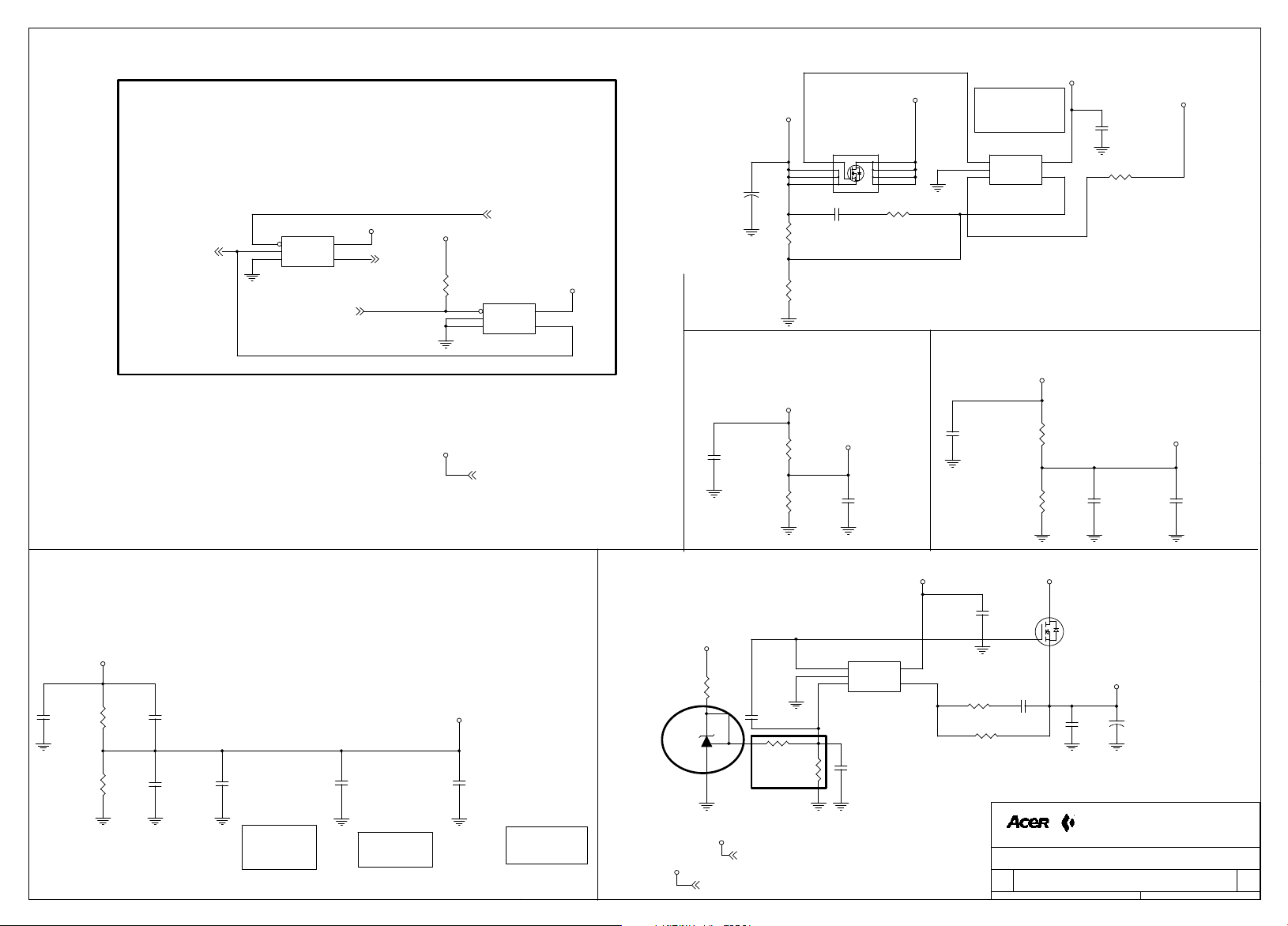

Page 2

A

www.kythuatvitinh.com

SHEET INDEX

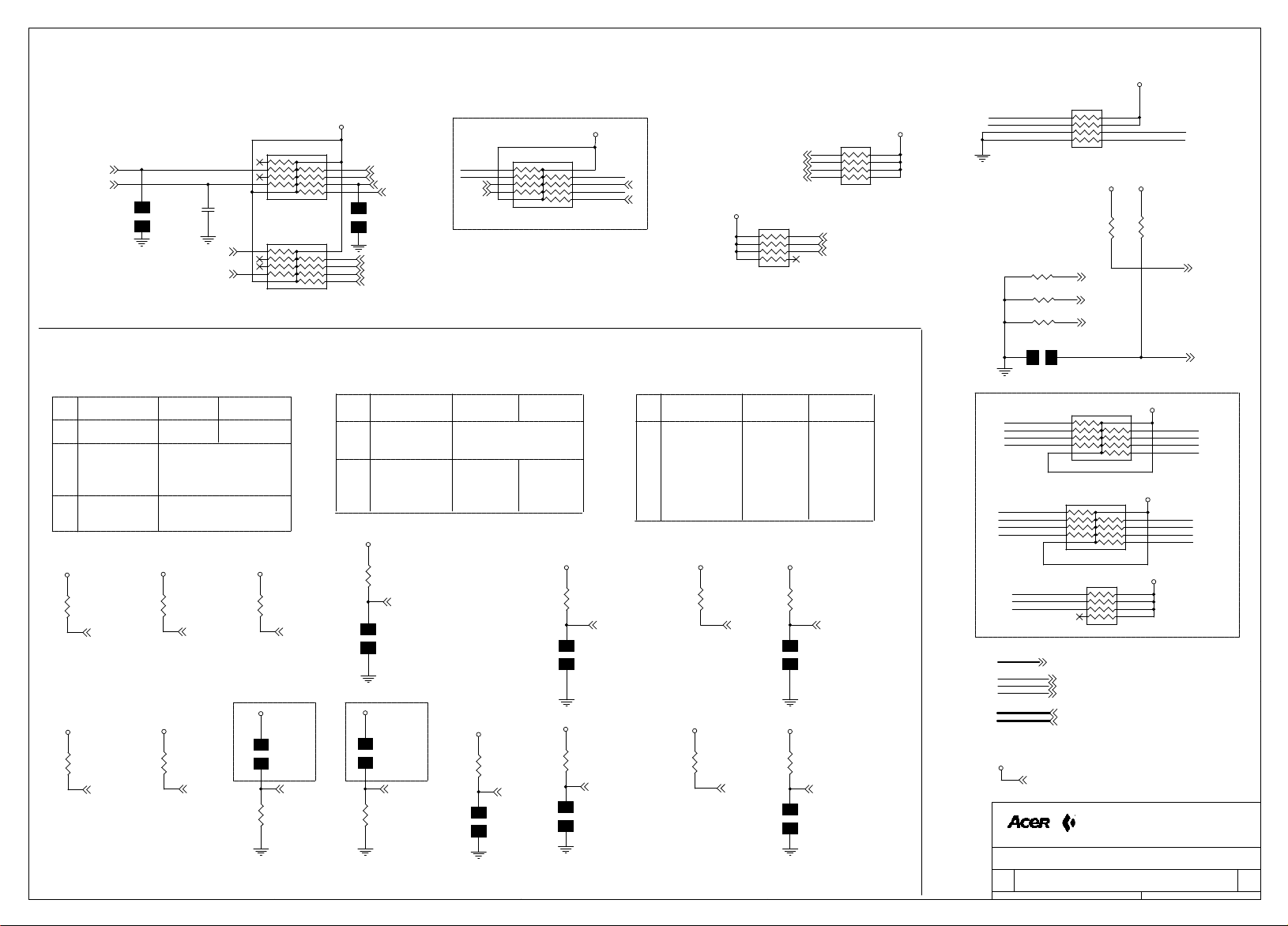

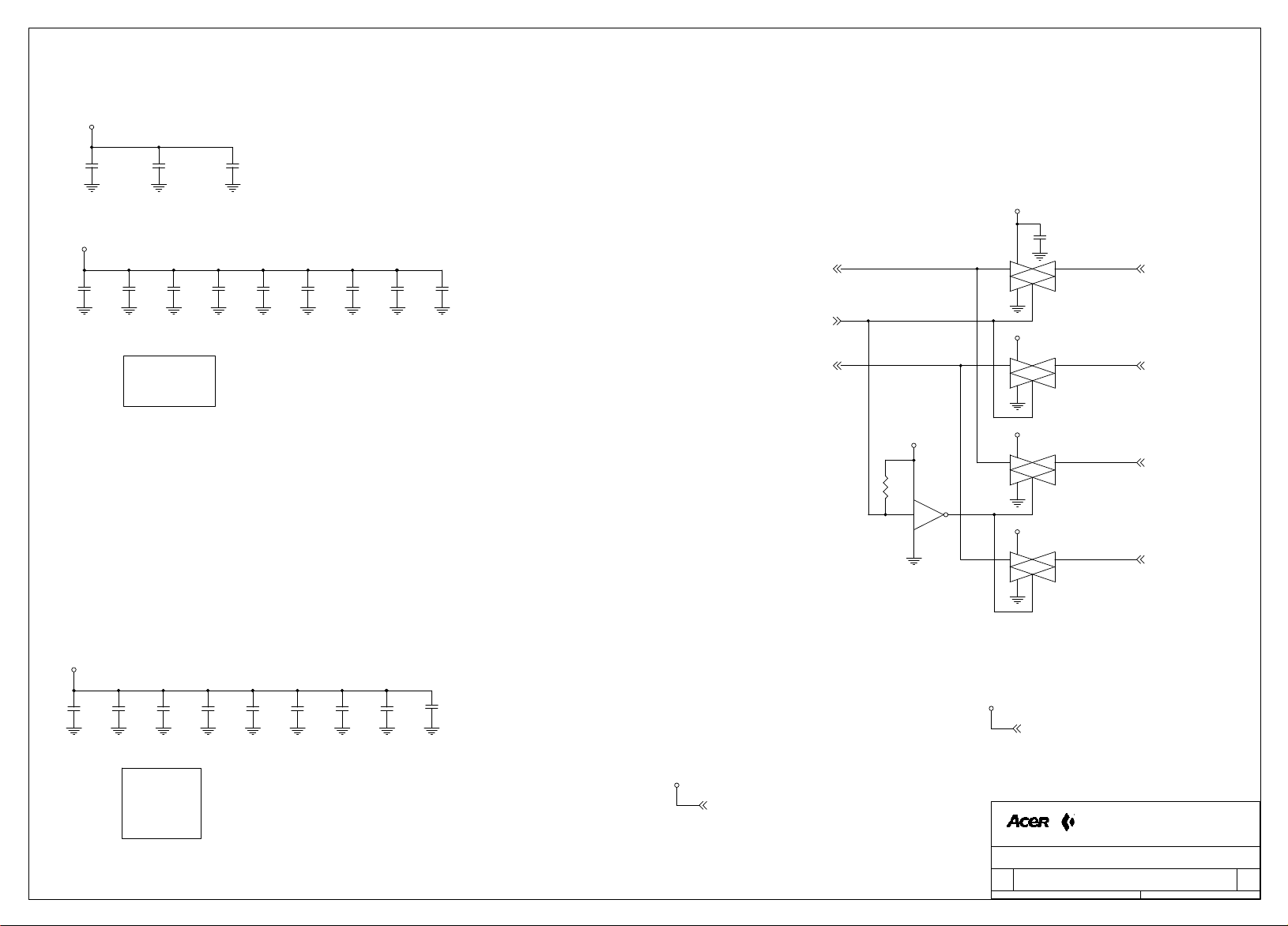

1. Block System Architecture

2. Rev. History Sheet Index & Revision History

3. Clock Gen. CLK GEN. IC9248-157 & CLK Buffer ICS9112A0A

4. CPU1 CPU Mobil pentium!!!/Coppermine

4 4

5. CPU2 CPU CORE/IO Power

6. CPU3 Geyserville & CPU Thermal Sensor

7. Power Power 2.5V & VRM

8. M1632_1 N/B ALi M1632

9. VGA VGA Power & Filter & Damping RES

10. M1632_2 M1632 Hardware Setting

11. SDRAM_1 On Board SDRAM

12. SDRAM_2 SODIMM SOCKET

13. CRT CRT PORT & INVERTER INTERFACE

3 3

14. LCD LCD INTERFACE

15. TV PORT TVEXPRESS

16. M1535_1 S/B ALi M1535

17. M1535_2 S/B HAREWARE SETTING

18. PCMCIA PCMCIA CONTROLLER-OZ6912

19. MINIPCI MINIPCI SOCKET-802.11/IEEE 1394

20. IDE/USB HDD/USB CONECTOR

21. B.T. BLUETOOTH INTERFACE & THERMAL / FAN CONTROLLER

22. THERMAL SENSOR G768B & DS75

2 2

23. KBC/PS2 PORT M38867

24. PORT SERIAL & PARALLEL PORT

25. CODEC AC'97 CODEC -CS4299

26. OP AMP AUDIO OP AMPLIFIER

27. BIOS BIOS & DEBUG PORT & RTC

28. DC/DC SYSTEM DC/DC

29. CHARGER1 CHARGER CONTROLLER-MAX1772

30. CHARGER2 FirmWare-MC68HC908SR

31. LAN INTEL82559

32. NCLOGIC FREE LOGICAL GATES

1 1

33. TEST PAD TEST POINTS

34. ULTRA BAY CD-ROM/FDD/ZIP/USB

35. PORT REPLICATOR

36. 1394 TSB43AA22

B

History

C

Rev:SA

Rev:SB

1.(P.3) PCICLK0 assign for 1394 chip

2.(P.5) R187/492 change from 0 ohm to 4.7 ohm

3.(P.7) Change charger flash circuit,use NC7SZ125 U83/83

4.(P.7) change +1.5V generate circuit (0324)

5.(P.8) 1632 E22/G22 change power to M+3V

6.(P.9) Add +2.5V bypass cap BC544

7.(P.13) Add U85 for 24C02 switch

8.(P.14) Change LCD interface

9.(P.15) Change TV-Port connector SKT2

10.(P.16) Change PCIRST#_3 logic circuit

11.(P.16) SB 32K for NB reserve bypass trace

12.(P.16) Change GPIO assihnment

XFD_INST# / CHKPW /SERIAL_EN / SB_Fn

/ 24C08_WP

13.(P.17) BT_RESET_3 change to PL( SB HW setting)

14.(P.18) PME#_RSM block leakage circuit change

15.(P.19) PME#_RSM block leakage circuit change

16.(P.19)MINIPCI add AC97 interface

17.(P.19)Change MDC interface to CDC interface

18.(P.19)Change modem cable connector

19.(P.20)Change USB connectors

20.(P.21)Combin bluetooth interface to CDC interface

21.(P.22)G768B Thermal Alert add 100K PL to prevent abnormal low signal

22.(P.22)Change FAN/LID connector type

23.(P.22)Change 24C08 to 24RF08

24.(P.22)24RF08 write protect signal change to C02/RF08#

25. (P.23)Remove TP4 PS/2 mouse serial function

26. (P.23)Change KBC GPIO TP4/PS2# / KBID2 / 3_MODE# / BLUEIN#

27. (P.23)KBC SMBus change power to M+5V

28. (P.24)Add printer port FDD support

29. (P.24)1394 connecter add common mode choke

30. (P.26)Change speaker connector

31. (P.28)Change M+3V/+3.3V/+5V power switch on/off circuit

32. (P.29)Change charger current control circuit and

add Li-Ion battery full power charge function

33. (P.30)Change battery LED indicator circuit

34. (P.30)Change AD In logic,R224 to 18K ohm

35. (P.31)Conbine RJ45/RJ11 connector

36. (P.34)Change Ultra Bay power control with TPS2013D

37. (P.35)Change modem connector type

38. (P.36)Add 1394 circuit

39. (P.25/26) SPKR_L/R+1 connec to LINE_OUTL/R

40. (P.16)PNF / VRCHANGE# / XFD_INST# routing together

41. (P.6/14/15/21)U66 change HC14 to LCX14

42. (P.28)UBAY_+5VSB/M+5V/+5V/POWER_ON Logic change

43. (P.19)Modify CDC / MINIPCI interface.

44. (P.22)Add RA48 on FAN1_FG pin

45. (P.23)KBC P44 modify MDMIN#

46. (P.25)Add MDM_BEEP for BUZZER source

47. (P.19)Remove MiniPCI Pin-100 SERIRQ

48. (P.26)Change Audio Jack Type

49. (P.29)Change DC Power Jack Type

50. (P.22)HW_THERM_EN change always PH,not control by GPO

51. (P.16)RA41 mount

52. (P.25)RA43/RA44 mount,BC227/247 un-mount

53. (P.23)KBC port44 change to USB_WAKE_EN

54. (P.28)Add Q44 for Haedward Thermal Shutdown

55. (P.34)Change FDD LEDsignal to DR0/1#_5

56. (P.28)U96 pin connect error

57. (P.28)Remove BC47/49/50 TC6/9

58. (P.5) Add RC termination near D27 for EMI

59. (P.22)Add RA51 for FAN1_VCC

60. (P.15)BC2/10 change to 150P,BC14/15 change to Dummy

03/30

61. (P.36)1394 PCI_REQ/GNT change to REQ#3/GNT#3

62. (P.36)1394_PME# just Pull high to +3.3V

63. (P.34)CD_CSEL pull low change to 470 ohm

64. (P.16/17)Change SBFn connection

04/02

65. (P.15)SKT2 Pin1/Pin3 Swap

66. (P.25)U34 Pin4 to U95 Pin3 net name duplicate(BUZZER)

change to BUZZER_1

04/05

67. (P.3)RA30 and BC577 change circuit from RC filter to termination

68. (P.14)CN9 Pin15 change to BDC_LED

69. (P.16)RA53 mount 0 ohm

70. (P.17)SB_Fn PH(RP13 pin6) change to SBFn

71. (P.17)RA55 change to Dummy

72. (P.19)CN22 Pin31 change name to BDC_LED

73. (P.23)Swap net name KBC_SMBDATA and KBC_SMBSCLK

74. (P.32)Remove G16

75. (P.36)Change DR#_5 and MOT#_5 logic to 2 input DR0/1#_5 and MOT0/1#_5

04/07

76. (P.16)Change DRVRST# logic circuit,add U100(OR gate),not use Smittch trigger

04/08

78. (P.22) Change BC442 from 4.7uF to 10uF for FAN_VCC

79. (P.22) U26/RA6 Dummy, U36 DS75 mount for Hardware Thermal Shutdown

80. (P.22)Hardward Thermal Shutdown enable signal change from GPO to system powergood

1. (P.14) LCD I/F CN18 Pin39/40 SWAP

REV:

2. (P.36) 1394 TSBAB22 Pin 86 PH 3.3V / Pin 96 floating.

SC

Add RB2 for cut signal.

3. (P.24) Remove Printer Port FDD function

4. (P.31) R332 change form 10K to 3.3K for S3 function

5. (P.34) Modify USB_WAKE_EN logic circuit

6. (P.12) Swap CKE1 and CKE3

7. (P.19)Remove MINIPCI/CDC Modem Switch

8. (P.26) Modify HP_IN function

06/02

09. (P.12) Change DM1 type( new location SKT4)

10. (P.15) Add BC578/579 for EMI

11. (P.19) Change MINI-PCI socket type

12. (P.20)Remove BC148,Add TC25 for HDD power

13. (P.20) Add serial resistor on SIRQI_5 for ATA spec

14. (P.25) Add RB4 on VREFOUT path to CODEC

15. (P.29) Modify charger circuit

16. (P.30) R90/92 change to 47K ohm

(P.28) R427 change to 33K,R426 change to 20K

RA8/9/10/11 change to 200K ohm

17. (P.36) R561 change to 390K ohm

06/08

18. (P.23) KBC port60 add AD-IN signal for fresh function

19. (P.15) TV-OUT add composite signal

20. (P.21) ST_SMI signal unconnect

21. (P.22) AT24RF08 WP/PROT pins circuit change

22. (P.25) CP_SPKR# add PL resistor

23. (P.23)KBC_BEEP add voltage division

24. (P.27) Add BC582 for +5V

25. (P.30) Add OFF_PWR1#_5RSM signal to Charger Controll IC

26. (P.18) Cardbus controller Pin34 PH change to +3V power

27. (P.25)Change Buzzer voltage division

28. (P.3) Add RB3 PL for CKG H/W setting

Rev:SD

1. (P.15) Add BC584 for EMI

2. (P.16) R547/R550 change from 1K to 10K

3. (P.20) R314 change to 33 ohm, R552/RB10 change to Dummy

4. (P.22) U78 RFID pin3-PROT change connection.Use U44D to do level shift 5V->3V

5. (P.25) BC227/BC247 change to 47uF 0805,RA43/RA44 dummy for line_out path change

6. (P.27) IrDA circuit change to 3V level.Add U106/U107 for level shift.

R363 change to 33 ohm,BC582 change to 47uF

7. (P.28) BC298/Bc299 change to 10u25VX5R for EMI( The schema is use 4.7uF for

temepary placement before P/N is avaliable)

8. (P.28) Add D32/D33 for undershoot solution

9. (P.28) Reserve RC4/RC5 for undershoot solution

10. (P.28) Change D5/D21/R21/BC575 for power on sequence

11. (P.29) Change RA12/RA15 for total power charge

12. (P.29) Change R53/BC61 for SANYO charge time solution

13. (P.29) Add D31/D30/RC1 ,change net for reserve voltage issue

14. (P.29) Change BC288/BC252/BC272/BC295/BC278 for EMI issue

15. (P.31) Add L20 for EMI

16. (P.34) R140 change to 33 ohm,R137 dummy for IDE signal

17. (P35) CN20 pin168/169 net change.Add RC31/BC583 termination for high port issue

18. (P.36) U87 change to dummy,RA16/RA17 change to dummy,RB5/RB6 change

to 2.7K ohm for 1394 EEPROM remove issue

P.25 RC2 (pull down resister of MDM_BEEP).

PS:

P.27 G26 and RCL# pin

P.28 U7 and U96 parts change to 4466

P.31 PME# _RSM to PWRBTN0#_KB

Rev:-1

1. (P.15) Add RD7,Unmount X1,BC4,BC3,R9,R13,R14,R15 for

TV-Out Issue

2. (P.16) Add RD5 for PCIRST# glitch issue

3. (P.17) Add RP15 for port reloicator ID

4. (P.18) R217 change to 0 ohm

5. (P.21)Remove BlueTooth I/F

6. (P.23) RD8/Q47 unmount(reserve)

7. (P.25) BC227/247 unmount,RA43/RA44 0 ohm

8. (P.26) R331 change 22K,R343 change 5.6K

9. (P.27) R361/358 change to 1.8 ohm

10. (P.28) BC292/19 change to 0.01uF,R21 change to 4.7K

11. (P.29) R379/380 change to 20K/10K,Add RD9,R365/381 change to 3.3K/10K

12. (P.31) TR4/TR3/L20 chabge for EMI

13. (P.32) Add G27 for EMI

14. (P.34) RN5 unmount

Rev:-2

01. (P.17) PRE#_RSM change circuit.Add RE3.RE4,Q48,

(Reserve,not mount)

02. (P.19) Add RE1 PL on AC_SDATA_IN1

03. (P.26) Add RE2 PL on KBC_BEEP

04. (P.29) D30 pin1 connect to AD+IN

05. (P.18) Q19 change to DTC124EKA

06. (P.19) Q18 change to DTC124EKA

07. (P.23) Q36/Q15 change to DTC124EKA

08. (P.20) TC25 change to 150uF

09. (P.25) BC168,BC169 change from 5P to 18P

Rev:-3

01. (P.12) Chnage CKE circuit,add RF1 PL

02. (P.25) Change X6 to 10pF part,BC168/169 change to 9pF

03 (P.17) D19 Un-mount for S3 solution

Rev:-4

01 (P.20) Change TC3/22 to 150uF

D

Title

Size Document Number Rev

A2

Date: Sheet of

Revision History

C-Note

E

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221,

Taiwan,R.O.C.

2 36Wednesday, December 05, 2001

-4

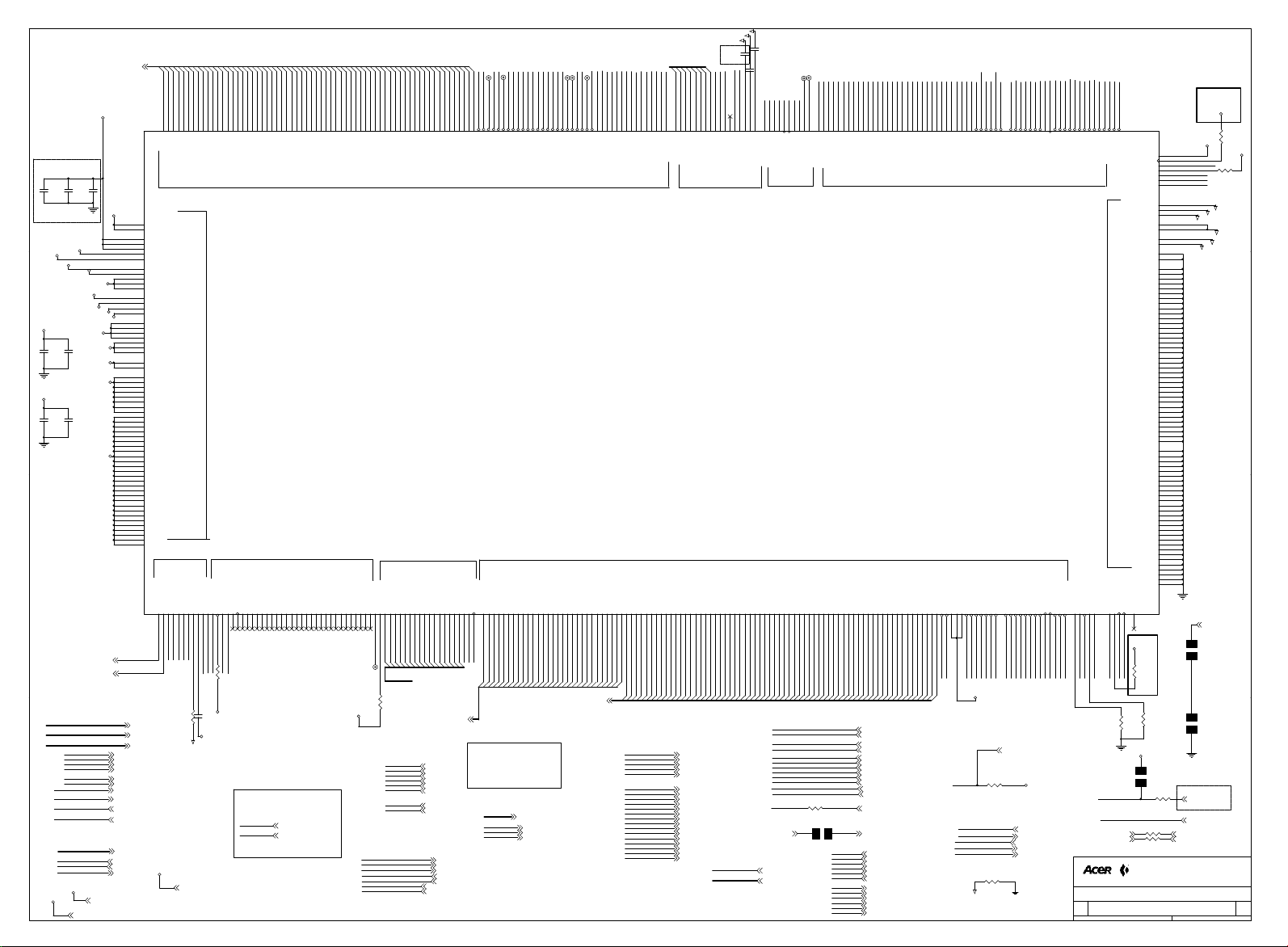

Page 3

R454

www.kythuatvitinh.com

1 2

0R5

63.R0003.161

A

PCLKVCC

BC423

SC10U10V6ZY

BC443

SCD1U16V

BC83

SCD1U16V

SCD1U16V

BC81

+3.3V

(PIN 13) (PIN 19) (PIN 28)

4 4

+3.3V

1 2

R466

DUMMY-R2

PCLKVCC

+3.3V

12

R471

10KR3

12

R473

DUMMY-R3

C-Note 0116 Change

X-14.318MHZ-1

to XTAL-14D318M

BC87

SC10P

BC86

SC10P

12

X3

XTAL-14D318M

3 3

C-Note 1230 change

1632CLK change Freerun

PCLK32_D38

PCLKCARD_D318

PCLKMINIPCI_D319

MCLK8

PCLKLAN_D331

PCLK35_D316

2 2

48M35_D316

R460

1 2

33R3

R458

1 2

33R3

R141

1 2

33R3

R142

1 2

33R3

R143

1 2

33R3

R144

1 2

33R3

R147

1 2

10R3

M1632PCICLK

M1535_CLK

12

R469

DUMMY-R3

R146

DUMMY-R3

14M35D3

XIN

XOUT SPRAD#_3

CARD_CLK

MDLN_CLK

MCLK_PCI3

48M/SEL100/66#

+3.3V

12

10KR3

12

1394_CLK

12

R145

12

B

+2.5V

R150

1 2

0R5

C-Note 0116 Add

R477

1 2

33R3

R476

1 2

33R3

63.33034.151

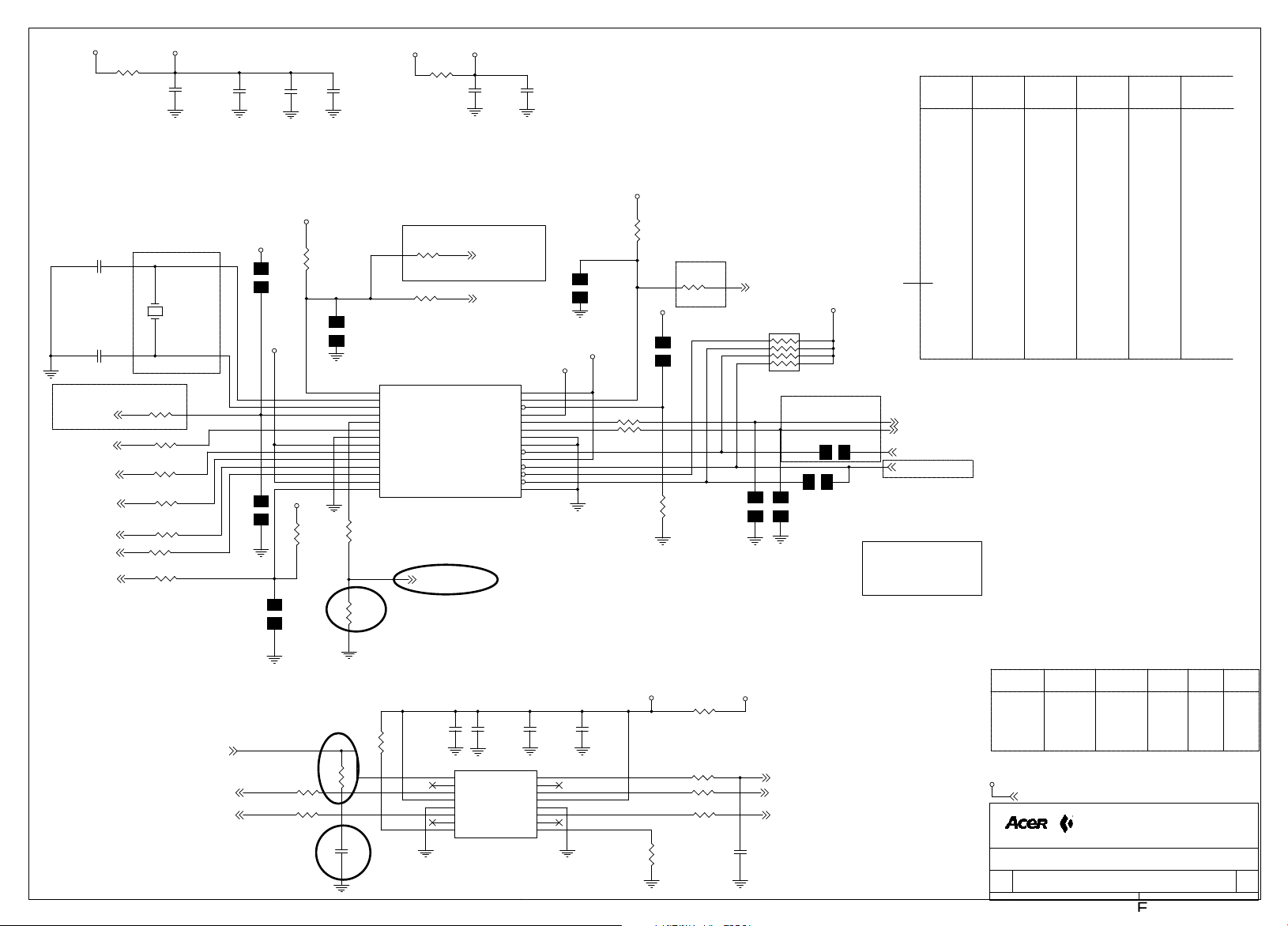

Clock Generator

U12

1

FS1/REF0

2

X1

3

X2

4

FS2/PCICLK_F

5

PCICLK0

6

PCICLK1

7

GND

8

VDD

9

PCICLK2

10

PCICLK3

11

PCICLK4

12

PCICLK_E

13

VDD

14

FS3/48MHZ

ICS9248-157

R463

33R3

PCLK1394_D3 36

RB3

3K3R3

SC 0530

Add PL

SB Add

for

1394

CLK_VCC

BC82

SCD1U16V

14M_GCL_D3 6

14M35_D3 16

REF1/FS0

SPREAD#

CPUCLK1

CPUCLK0

GNDL

PCI_STOP#

CPU_STOP#

DIV/4#

VDD

VDDL

GND

VDD

PD#

GND

BC85

SC10U10V6ZY

28

27

26

25

24

23

CPUCLK0

22

21

20

19

18

17

16

15

CLK_VCC

CPUCLK1

12

R472

DUMMY-R3

PCLKVCC

14MCLK2

1 2

R461

1 2

R456

PCI_STP#

CLK_PWRDWN#

DIV4#

22R3

22R3

+3.3V

12

C

R475

10KR3

+3.3V

DUMMY-R3

12

12

R470

1 2

0R3-0-U

R467

R464

10KR2

63.10334.1D1

C-Note 1230 Change

Flicker Problem

33->0

VGA14M_3 8,15

1

2

3

4 5

12

R459

DUMMY-R3

RN37

8

7

6

SRN4K7

C-Note 1230

Check Clkrun

Function?

DUMMY-R3

R133

12

R457

DUMMY-R3

+3.3V

R134

DUMMY-R3

D

Default

12

PCI_STP#_3 16

12

CKG_CPUSTP#_3 6

C-Note 0116 Change

SB_CPUSTP#_3

to CKG_CPUSTP#_3

C-Note 0129 Change

Delete R561

RN1 has PH

For ICS9248-157 only

FS3

FS2

0 16.66

0

0

0

0

0

0 0

0

1

1

1

1

1

1

1

1

HCLKCPU_D2 4

HCLK1632_D2 8

FS1

0

0

0

0

1

1

1

1

0

0

0

0

1

1 0

1

1

FS0

0

0

1 35.00

1

0

0

1

1

0

0

1

1

0

1

1

Jitter Requirement:

Duty Cycle Requirement:

0

1

0

1

0

1

1

0

1

0

1

0

1

1

Skew Requirement:

CPU_CPU:200ps max.

SDRAM-SDRAM:500ps max.

PCI-PCI:500ps max.

CPU-NB:In Phase

DRAM-NB:In Phase

CPU/NB-PCI:1-4ns,2.5ns typical

NB-SB:1-4ns,2.5ns typical

NB-NBPCI:1-4ns,2.5ns typical

CPU:250ps max.

PCI:500ps max.

45%-55% for all clock

E

CPU

33.33

63.33

69.99

66.66

97.00

96.22

91.50

83.33

50.00

95.25

105.00

100.00

66.66

126.35

139.650

133.33

PCI

31.66

33.33

32.33

32.07

30.50

27.77

16.66

31.75

35.00

33.33

16.66

31.66

35.00

33.33

SB Change

Add RC

SB 0404 change to

RC termination

SDCLKO_D38

1 1

SDRAMCK0_D312

SDRAMCK2_D312

1 2

1 2

R213

10R3

R214

10R3

12

SDRAM Clock Buffer

1KR3

RA30

47R3

BC577

SC10P

12

SDRAMCK2

BC110

SCD1U16V

R215

FS2 FS1

U20

1

REF

2

CLKA1

3

CLKA2

4

VDD

5

GND

6

CLKB1

7

CLKB2

8

FS2

ICS9112BM-17

71.09112.A0A

BC127

SCD1U16V

CLKOUT

CLKA4

CLKA3

VDD

GND

CLKB4

CLKB3

FS1

BC124

SCD1U16V

16

15

14

13

12

11

10

9

SC4D7U10V5ZY

SDCLKID4

SDRAMCK1

SDRAMCK3

BC128

BUF_VCC

12

R197

1KR3

R209

1 2

0R5

R198

1 2

R199

1 2

R196

1 2

22R3

10R3

10R3

+3.3V

BC111

SC15P

SDCLKI_D3 8

SDRAMCK1_D3 12

SDRAMCK3_D3 12

Feedback to N/B

SDCLKI_D3=SDRAMCLK+7000 mils

FS2

+3.3V

Title

Size Document Number Rev

A3

Date: Sheet of

CLKA[1..4]

0

0

1

1

TRISTATE TRISTATE

0

DRIVEN

1

TEST MODE

0

DRIVEN

1

+3.3V 5,6,7,8,9,10,13,14,15,16,17,18,19,21,22,25,27,28,30,32,36

CLOCK GENERATOR

C-Note

CLKB[1..4]

TRISTATE

TEST MODE

DRIVEN

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221.

Taiwan ,R.O.C.

CLKOUTFS1

DRIVEN

DRIVEN

TEST MODE

DRIVEN

OUTPUT

SOURCE

3 36Thursday, January 10, 2002

PLL

SHUTDOWN

PLL

N

N

PLL

REF

Y

PLL

N

-4

Page 4

A

www.kythuatvitinh.com

BC402

BC403

BC404

BC405

BC407

SCD1U16V

SCD1U16V

SCD1U16V

SCD1U16V

BC472

SCD1U16V

BC401

SCD1U16V

78.10491.4F1

BC411

SCD1U16V

78.10491.4F1

BC424

SCD1U16V

78.10491.4F1

BC436

SCD1U16V

78.10491.4F1

BC449

SCD1U16V

78.10491.4F1

4 4

VCC_IO_CPU

R154

IERR#_1

1 2

1K5R3

63.15234.151

R153

1 2

FLUSH#_1

1K5R3

63.15234.151

R157

1 2

SLP#_1

1K5R3

63.15234.151

R127

1 2

CPURST#_1

56D2R3F

64.56R25.651

3 3

HREQ0#_18

HREQ1#_18

HREQ2#_18

HREQ3#_18

HREQ4#_18

ADS#_18

BREQ0#_18

BPRI#_18

BNR#_18

3

HCLKCPU_D2

12

R132

DUMMY-R3

ZZ.DUMMY.XR3

HC_D2

12

BC80

DUMMY-C3

ZZ.DUMMY.XC3

2 2

VCC_IO_CPU

12

R162

1K5R3

63.15234.151

HLOCK#_18

HIT#_18

HITM#_18

DEFER#_18

RS0#_18

RS1#_18

RS2#_18

HTRDY#_18

A20M#_16

FERR#_16

IGNNE#_16

SMI#_16

PWRGOOD_26

STPCLK#_16

INTR_16

NMI_16

INIT#_16

CPURST#_18

HCLKCPU_D23

12

12

R166

R165

1K5R3

56R3

63.15234.151

TESTHI

12

R152

1KR3

TESTLO1

TESTLO2

12

R452

1KR3

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

IERR#_1

FLUSH#_1

SLP#_1

PICD0

PICD1

PICCLK

TCK

TDI

TDO

TMS

TRST#

PREQ#

PRDY#

PLL1

PLL2

L3

A3#

K3

A4#

J2

A5#

L4

A6#

L1

A7#

K5

A8#

K1

A9#

J1

A10#

J3

A11#

K4

A12#

G1

A13#

H1

A14#

E4

A15#

F1

A16#

F4

A17#

F2

A18#

E1

A19#

C4

A20#

D3

A21#

D1

A22#

E2

A23#

D5

A24#

D4

A25#

C3

A26#

C1

A27#

B3

A28#

A3

A29#

B2

A30#

C2

A31#

A4

A32#

A5

A33#

B4

A34#

C5

A35#

T2

REQ0#

V4

REQ1#

V2

REQ2#

W3

REQ3#

W5

REQ4#

W2

RP#

AB2

ADS#

AA1

AERR#

AB1

AP0#

Y2

AP1#

E6

BERR#

V21

BINIT#

AD9

IERR#

C6

BREQ0#

U4

BPRI#

T4

BNR#

R1

LOCK#

V1

HIT#

Y4

HITM#

U3

DEFER#

U1

RS0#

AA2

RS1#

W1

RS2#

Y1

RSP#

U2

TRDY#

AD10

A20M#

AC12

FERR#

AC9

FLUSH#

AC13

IGNNE#

AB10

SMI#

V5

PWRGOOD#

AC11

STPCLK#

AB12

SLP#

AB18

INTR/LINT0

AC19

NMI/LINT1

AA10

INIT#

A6

RESET#

M3

BCLK

AB21

PICD0

Y20

PICD1

AA18

PICCLK

AA21

BP2#

Y21

BP3#

W21

BPM0#

W19

BPM1#

AA11

TCK

AD13

TDI

AC15

TDO

AD14

TMS

AA14

TRST#

AB20

PREQ#

W20

PRDY#

AD17

TESTHI

Y5

TESTLO1

N5

TESTLO2

AD20

TESTP_1

H4

TESTP_2

AA17

TESTP_3

G4

TESTP_4

L2

PLL1

M2

PLL2

VSS_0A2VSS_1A7VSS_2A8VSS_3

A12

A21

VSS_4

VSS_5B1VSS_6B5VSS_7B6VSS_8B7VSS_9

VCC_IO_CPU

VCCT_0G6VCCT_1G7VCCT_2G8VCCT_3G9VCCT_4

VSS_10

VSS_11

VSS_12

B8

B10

B15

B18

G10

G11

VCCT_5

VSS_13C9VSS_14

VSS_15

C11

C15

G12

G13

G14

G15

VCCT_6

VCCT_7

VCCT_8

VSS_16

VSS_17

VSS_18D2VSS_19D6VSS_20D7VSS_21D9VSS_22E3VSS_23E7VSS_24E8VSS_25E9VSS_26

C16

C19

SCD1U16V

G16

VCCT_9

VCCT_10

VCC_IO_CPU

G17

H17

VCCT_11

VCCT_12H6VCCT_13

BC408

SCD1U16V

BC406

SCD1U16V

78.10491.4F1

C-NOTE CHANGE

R138

1 2

DUMMY-R3

J17

K17

L17

VCCT_14J6VCCT_15

VCCT_16K6VCCT_17

VCCT_18L6VCCT_19

VSS_27

VSS_28

E10

E11

E13

E19

M17

VCCT_20M6VCCT_21

VCCT_22N6VCCT_23

BC416

SCD1U16V

78.10491.4F1

N17

VCCT_24P1VCCT_25P6VCCT_26

B

BC409

SCD1U16V

R136

1 2

0R3-0-U

P17

R17

VCCT_27R6VCCT_28

SCD1U16V

78.10491.4F1

VCC_CORE_CPU

T17

U17

VCCT_29T6VCCT_30

VCCT_31U6VCCT_32

VCCT_33V6VCCT_34V7VCCT_35V8VCCT_36V9VCCT_37

BC410

SCD1U16V

BC429

BC412

BC413

BC414

SCD1U16V

SCD1U16V

VCC_IO_CPU

BC441

BC452

SCD1U16V

SCD1U16V

78.10491.4F1

78.10491.4F1

V10

V11

V12

V13

V14

V15

V16

V17

W10

W11

W12

W13

W14

W15

W16

VCCT_38

VCCT_39

VCCT_40

VCCT_41

VCCT_42

VCCT_43

VCCT_44

VCCT_45W6VCCT_46W7VCCT_47W8VCCT_48W9VCCT_49

VCCT_50

VCCT_51

VCCT_52

VCCT_53

VCCT_54

VCCT_55

SCD1U16V

BC474

SCD1U16V

78.10491.4F1

W17

VCCT_56

VCCT_57Y6VCCT_58Y7VCCT_59Y8VCCT_60

BC415

SCD1U16V

12

SE220U2D5VM-1

AA6

AA7

AA8

AB6

AB7

AB8

VCCT_61

VCCT_62

VCCT_63

VCCT_64

VCCT_65

TC16

AC6

AC7

VCCT_66

AC8

AD6

VCCT_67

VCCT_68

BC418

SCD1U16V

12

SE220U2D5VM-1

ZZ.2271V.9P1

AD7

AD8

VCC_0H8VCC_1

VCCT_69

VCCT_70

VCCT_71

TC17

H10

H12

C

H14

VCC_2

H16

VCC_3

VCC_4

C-Note 0129

Remove BC12

12

TC13

SE220U2D5VM-1

J11

J13

J15

K10

VCC_5J7VCC_6J9VCC_7

VCC_8

VCC_9

VCC_10K8VCC_11

12

SE220U2D5VM-1

K12

K14

K16

VCC_12

VCC_13

VCC_14

TC12

L11

L13

VCC_15L7VCC_16L9VCC_17

VCC_18

BC419

SCD1U16V

12

SE220U2D5VM-1

L15

M10

VCC_19

VCC_20M8VCC_21

M12

VCC_22

TC19

M14

VCC_23

M16

BC420

SCD1U16V

VCC_CORE_CPU

2 1

1SMB5913BT3-U

N11

N13

N15

VCC_24

VCC_25N7VCC_26N9VCC_27

VCC_28

BC421

SCD1U16V

C-Note 0106 Change

TC26 Move to CPU_1.3V

12

TC15

D26

SE220U2D5VM-1

C-Note 1230 Add

P10

P12

P14

P16

R11

VCC_29

VCC_30P8VCC_31

VCC_32

VCC_33

VCC_34

VCC_35R7VCC_36R9VCC_37

R13

VCC_38

R15

VCC_39

BC425

SCD1U16V

T10

T12

VCC_40T8VCC_41

VCC_42

T14

T16

VCC_43

VCC_44

MOBILE PENTIUM III

COPPERMINE

VCC_CORE_CPU = 1.35V ~ 1.7V

VCC_IO_CPU = 1.5V

CLK_VCC = 2.5V

CLK_VREF = 1.25V= 2.5V * ( 2K / (2K + 2K) )

CMOS_VREF = 1V = 2.5V * ( 2K / (2K + 3K) )

GTL_VREF_CPU = 1V = VCC_IO_CPU * ( 2K

/ ( 1K + 2K ) )

VSS_29

VSS_30F3VSS_31F6VSS_32F7VSS_33F8VSS_34F9VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43G3VSS_44

VSS_45H2VSS_46H7VSS_47H9VSS_48

VSS_49

VSS_50

VSS_51

VSS_52J4VSS_53J8VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59K2VSS_60K7VSS_61K9VSS_62

VSS_63

VSS_64

VSS_65

VSS_66L5VSS_67L8VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73M7VSS_74M9VSS_75

VSS_76

VSS_77

VSS_78

VSS_79N2VSS_80N3VSS_81N4VSS_82N8VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90P5VSS_91P7VSS_92P9VSS_93

VSS_94

VSS_95

VSS_96

J10

J12

J14

J16

F10

F11

F12

F13

F14

F15

F16

F20

H11

G19

J19

H13

H15

H20

L10

L12

L14

L16

K11

K13

L19

K15

K20

N10

N12

N14

N16

N18

M11

M13

M15

M20

N19

VSS_97R3VSS_98R4VSS_99

P11

P13

P15

P19

N20

VSS_100R8VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106T3VSS_107T5VSS_108T7VSS_109T9VSS_110

VSS_111

VSS_112

VSS_113

R5

R10

R12

R14

R16

R20

VSS_114

T11

T13

T15

T18

T19

CPU VOLTAGE SPEC

CORE : 1.35V +/- 100mV

IO : 1.5V +/- 115mV

CPU CURRENT RATING

CORE :

VSS_115U8VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121V3VSS_122

VSS_123W4VSS_124

VSS_125Y3VSS_126Y9VSS_127

V19

U10

U12

U14

U16

U20

W18

D

BC426

BC427

SCD1U16V

SCD1U16V

BC439

SCD1U16V

78.10491.4F1

VCC_CORE_CPU

U11

U13

U15

A15

A16

A17

C14

D14

D16

NC_1

NC_2

NC_3

NC_4

NC_5D8NC_6

VCC_45U7VCC_46U9VCC_47

IO : 2.5A MAX

VSS_128

VSS_129

Y10

Y11

Y12

NC_7

VCC_48

VCC_49

1.7V +/- 115mV

600MHz ~ 11.2A MAX

650MHz ~ 12.1A MAX

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

Y13

Y14

Y15

Y16

Y19

AA4

AB3

AA13

AA20

E15

NC_8

VSS_139

AB4

G2

NC_9

VSS_140

AB5

AB9

G18

NC_10G5NC_11

VSS_141

AB11

BC428

SCD1U16V

BC440

SCD1U16V

78.10491.4F1

NC_12H3NC_13H5NC_14J5NC_15M4NC_16M5NC_17P3NC_18P4NC_19

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

AC1

AC2

AC4

AC5

AB13

AB14

AB17

BC444

SCD1U16V

78.10491.4F1

AA5

AA19

VSS_149

VSS_150

AC10

AC14

BC432

SCD1U16V

AC3

AC17

NC_20

NC_21

NC_22

VSS_151

VSS_152

VSS_153

AC16

AC18

AC20

NC_23

VSS_154

AC21

AD15

NC_24

VSS_155

AD1

BC433

BC434

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

GHI#

SCD1U16V

U11

D10

D11

C7

C8

B9

A9

C10

B11

C12

B13

A14

B12

E12

B16

A13

D13

D15

D12

B14

E14

C13

A19

B17

A18

C17

D17

C18

B19

D18

B20

A20

B21

D19

C21

E18

C20

F19

D20

D21

H18

F18

J18

F21

E20

H19

E21

J20

H21

L18

G20

P18

G21

K18

K21

M18

L21

R19

K19

T20

J21

L20

M19

U18

R18

V20

T21

U21

R21

V18

P21

P20

U19

AA3

T1

AA15

AB16

AA12

AB15

AA16

P2

AA9

AD18

AD19

R2

E5

E16

E17

F5

F17

U5

Y17

Y18

AB19

COPPERM-1GHz

71.COPRM.E0U

BC446

SCD1U16V

78.10491.4F1

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

BSEL0

BSEL1

RTTIMPEDP

BC435

SCD1U16V

CC_LO/HI# 6

GTL_VREF_CPU

SCD1U16V

BC445

SCD1U16V

78.10491.4F1

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

THERMDA

THERMDC

BSEL0

BSEL1

EDGECTRLP

CLKREF

CMOSREF_1

CMOSREF_2

RTTIMPEDP

VREF_0

VREF_1

VREF_2

VREF_3

VREF_4

VREF_5

VREF_6

VREF_7

RSVD

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

AD2

AD3

AD4

AD5

AD16

AD21

VCC_CORE_CPU

E

BC437

SCD1U16V

BC447

SCD1U16V

78.10491.4F1

Processor system bus speed selection

66MHZ

100MHZ

X

133MHZ

DBSY#_1 8

DRDY#_1 8

THERMDA 22

THERMDC 22

EDGECTRLP

CLK_VREF

CMOS_VREF

12

R163

56D2R3F

BC438

SCD1U16V

BC450

SCD1U16V

78.10491.4F1

BSEL1 BSEL0

0

001

1

1

VCC_IO_CPU

12

R177

10KR3

12

R180

110R3

VCC_CORE_CPU

BC451

SCD1U16V

78.10491.4F1

0

1

VCC_IO_CPU

12

R178

DUMMY-R3

12

R179

110R3

R160

1 2

1 1

VCC_IO_CPU

1 2

R126

1R3F

64.1R005.651

L10

1 2

CORE_VLL PLL1

IND-4D7UH

12

TC14

SE33U8V

79.3361U.9P1

For_SB

PLL2

R176

680R3

63.68134.151

1 2

RN10

8

7

6

SRN1K-1

TRST#

1

PICD0

2

3

PICCLK

45

PICD1

TMS

TDI

TDO

TCK

1KR3

63.10234.151

R159

1 2

1KR3

63.10234.151

R161

1 2

DUMMY-R3

R175

1 2

1KR3

63.10234.151

CMOS_VREF

BC471

SCD1U16V

78.10491.4F1

BC393

SCD1U16V

78.10491.4F1

CMOS_VREF

GTL_VREF_CPUGTL_VREF_CPU

BC475

SCD1U16V

78.10491.4F1

BC448

SCD1U16V

78.10491.4F1

CLK_VREF

BC430

SCD1U16V

78.10491.4F1

VCC_IO_CPU

VCC_IO_CPU 6,7,9

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221.

Title

INTEL Mobile CPU - COPPERMINE

Size Document Number Rev

A2

C-Note

Date: Sheet of

Taiwan ,R.O.C.

HD[0..63] 8

HA[3..31] 8

4 36Thursday, January 10, 2002

-4

Page 5

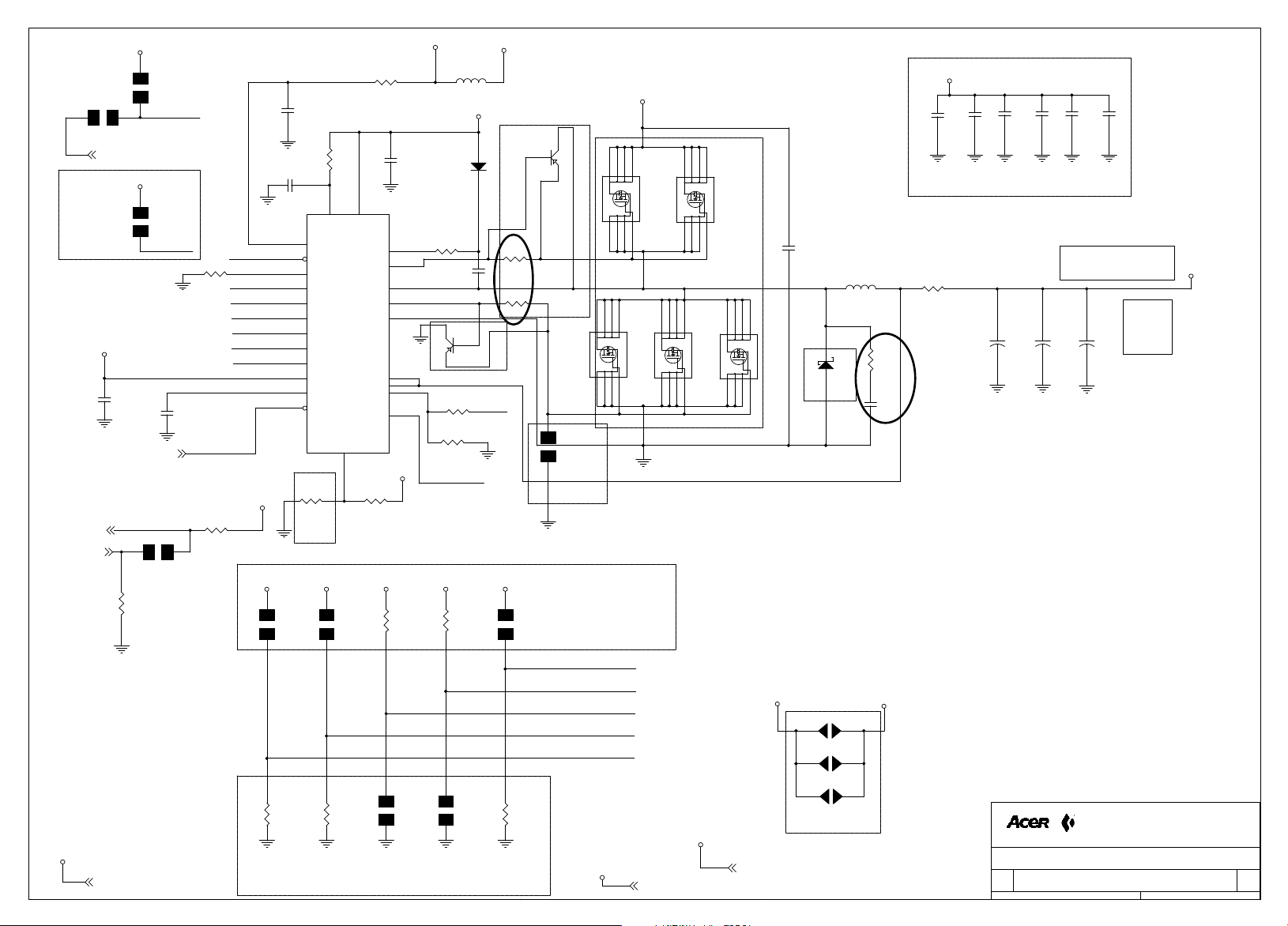

A

www.kythuatvitinh.com

+5V

12

R493

DUMMY-R3

R491

1 2

4 4

DUMMY-R3

POWER_ON 28

TON :

Upper-side

ON Time

GND = 1MHz

Vref = 550KHz

Open = 300KHz

VCC = 200KHz

MAX1717_VREF

+5V

12

MAX1717_TON

R481

DUMMY-R3

MAX1717_SKP/SDN#

R181

1 2

120KR3

3 3

BC485

SC1U25V5ZY

VR_HI/LO#_36

VGATE_36

SB_VGATE_316

2 2

R487

DUMMY-R3

12

R488

10KR3

MAX1717_CC

BC97

SC470P50V3JN

MAX1717_A/B#

R486

12

100KR3

1 1

+5V

+5V 7,8,9,11,13,14,15,16,17,19,20,22,23,24,25,27,28,30,32,34,35

MAX1717_16V

BC490

SCD1U50V5KX

12

R480

SC1U10V3ZY

BC487

MAX1717_SKP/SDN#

MAX1717_TIME

MAX1717_D0

MAX1717_D1

MAX1717_D2

MAX1717_D3

MAX1717_D4

MAX1717_TON

12

21

20

19

18

17

16

MAX1717EEG

1 2

+3.3V

D4

+5V +5V+5V +5V +5V

12

R503

DUMMY-R3

12

R502

1KR3

20R3F

MAX1717_VCC

VCC7VDD

1

V+

2

SKP/SDN#

3

TIME

D0

D1

D2

D3

D4

8

TON

9

REF

6

CC

A/B#

ILIM

10

R483

15KR3F

C-Note 0116

Change

MAX1717_ILIM

D3

12

R500

DUMMY-R3

12

R501

100KR3

For A/B# = High

Set CPU First Voltage 1.70V

D[4..0]=[00110]

R186

1 2

10R3

15

BST

DH

LX

DL

GND

FB

FBS

GNDS

VGATE

MAX1717_VREF

R482

1 2

10KR3

D2

B

V+_MAX1717

1 2

BC489

SC4D7U10V5ZY

U75

R185

0R3-0-U

MAX1717_BST

22

1 2

MAX1717DH MAX1717_DH

24

SCD1U50V5KX

23

14

MAX1717DL

13

4

5

11

12

12

12

MAX1717_GNDS

R499

100KR3

R498

DUMMY-R3

3

2SA1037AK

1

R484

1 2

150KR3

R485

1 2

2KR3

D1

12

12

DCBATOUT

L12

BLM41P600S

+5V

C-NOTE 1225 Change

2SA1037AK

12

D10

BAT54

MAX1717_BST1

R187

1 2

BC100

Q35

VGATE_3

2

MAX1717_VREF

R497

1KR3

R496

DUMMY-R3

4D7R5

SB Change

0-->4.7

R492

1 2

4D7R5

D0

For A/B# = Low

Set CPU First Voltage 1.35V

12

D[4..0]=[01101]

R494

DUMMY-R3

12

R495

100KR3

3

2

Q14

1

MAX1717_DL

12

BC103

DUMMY-C3

C-NOTE 0116 SC100P

Change to DUMMY

MAX1717_D0

MAX1717_D1

MAX1717_D2

MAX1717_D3

MAX1717_D4

+3.3V

C

V+_MAX1717

678

DDD

SSS

G D

123

4 5

678

DDD

U19

IRF7811AV

SSS

G D

123

4 5

+3.3V 3,6,7,8,9,10,13,14,15,16,17,18,19,21,22,25,27,28,30,32,36

C-Note 0116

Change to

IR MOS

678

U16

IRF7807V

DDD

U18

IRF7807V

SSS

G D

123

4 5

MAX1717_LX

678

DDD

U17

DCBATOUT

DDD

SSS

123

DCBATOUT 14,28,29,30

IRF7811AV

SSS

G D

123

4 5

Extend GND

PAD

A/B# Defined Level-Judge Method

If A/B#=High, Set D[4..0] by Voltage-Level in wire

If A/B#=Low, Set D[4..0] by R(resistor)

R=100Kohm, High

R=1Kohm, Low

678

IRF7811AV

G D

4 5

U15

CPU_1.3V

BC503

SCD1U50V5KX

L11

1 2

L1D2UH-4

D27

B540C

2 1

<40V/5A>

SB Add for EMI

MAX1717_FBS

Extend GND

PAD

G7

21

GAP-OPEN

G6

21

GAP-OPEN

G5

21

GAP-OPEN

After MP, Short

D

12

RA50

4D7R3

BC576

SCD01U50V3KX

VCC_CORE_CPU

BC505

SCD1U50V5KX

R183

1 2

D003R7520F

V+_MAX1717

BC106

SC10U35V0ZY

10/16

Delete

0.1U

Bypass

Cap

E

BC502

BC108

SC10U35V0ZY

SC10U35V0ZY

12

12

TC20

SE220U2D5VM-1

SE220U2D5VM-1

While A/B# is High, Vout

SEL Matrix(MAX1717)

4 3 2 1 0 Vout

0 0 0 0 0 2.00

0 0 0 0 1 1.95

0 0 0 1 0 1.90

0 0 0 1 1 1.85

0 0 1 0 0 1.80

0 0 1 0 1 1.75

0 0 1 1 0 1.70

0 0 1 1 1 1.65

0 1 0 0 0 1.60

0 1 0 0 1 1.55

0 1 0 1 0 1.50

0 1 0 1 1 1.45

0 1 1 0 0 1.40

0 1 1 0 1 1.35

0 1 1 1 0 1.30

0 1 1 1 1 No CPU

1 0 0 0 0 1.275

1 0 0 0 1 1.250

1 0 0 1 0 1.225

1 0 0 1 1 1.200

1 0 1 0 0 1.175

1 0 1 0 1 1.150

1 0 1 1 0 1.125

1 0 1 1 1 1.100

1 1 0 0 0 1.075

1 1 0 0 1 1.050

1 1 0 1 0 1.025

1 1 0 1 1 1.000

1 1 1 0 0 0.975

1 1 1 0 1 0.950

1 1 1 1 0 0.925

1 1 1 1 1 No CPU

Title

CPU CORE DC/DC

Size Document Number Rev

A3

C-Note

Date: Sheet of

BC109

BC104

SC10U35V0ZY

SC10U35V0ZY

C-NOTE 1229 CHANGE

REMOVE D3

C-Note

0129

Remove

12

TC21

SE220U2D5VM-1

TC26

TC5

C-Note 0106 Change

Mpve from CPU_CORE_VCC

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221.

Taiwan ,R.O.C.

CPU_1.3V

5 36Thursday, January 10, 2002

-4

Page 6

A

www.kythuatvitinh.com

BC396

SCD1U16V

BC397

SCD1U16V

BC468

SCD1U16V

BC398

SCD1U16V

4 4

+3.3V

+3.3V

12

12

R558

R553

4K7R3

10KR3

SB_LO/HI#_316

3 3

RATIO#_316,17

14M_GCL_D33

ZZ.10334.151

PWRGOOD_3

SB_NMI_316

SB_SMI#_316

SB_INTR_316

SB_CPUSTP#_316

SB_A20M#_316

SB_STPCLK#_316

SB_INIT#_316

SB_IGNNE#_316

1 2

R555

R5590R3-0-U

1 2

ZZ.47234.151

0R3-0-U

ZZ.R0004.151

ZZ.R0004.151

SB_NMI_3

SB_SMI#_3

SB_INTR_3

SB_CPUSTP#_3

SB_A20M#_3

SB_STPCLK#_3

SB_INIT#_3

SB_IGNNE#_3

SB_SUS#_316

SB_LO/HI#_3

G_RATIO#_3

14MGCL_D3

12

R560

10KR3

ZZ.10334.151

RN41

1

2

3

4 5

SRN4K7

ZZ.47236.080

RN42

1

2

3

4 5

SRN4K7

ZZ.47236.080

PWRGD3

SB_NMI_3

SB_INTR_3

SB_INIT#_3

SB_A20M#_3

SB_IGNNE#_3

SB_SMI#_3

SB_STPCLK#_3

+3.3V

VGATE_3

IGN_VGATE#

BC531

SCD1U16V

ZZ.10491.4F1

VGATE_35

8

7

6

8

7

6

2 2

U81

GEYSERVILLE

ZZ.GEYSE.00G

20

NMI

16

INTR

22

INIT#

24

A20M#

21

IGNNE#

17

SMI#

23

STP_CLK#

19

SUSSTAT1#

13

CPU_STP_IN#

14

G_LO_HI#

15

VR_ON

29

VGATE

43

IGN_VGATE#

28

VR100/50#

44

PLL30/60#

41

CRESET#

26

CLK_IN_A

25

CLK_IN_B

45

CLKEN#

38

STB#

37

DIN

36

DOUT

B

BC469

SCD1U16V

BC467

SCD1U16V

G_STPCLK#

G_SUSSTAT1#

CPU_STP_OUT#

A_SUSSTAT1#

CPUPWRGD

LP_TRANS#

GND_16GND_218GND_331GND_442GND_527VCC3_17VCC3_2

G_NMI

G_INTR

G_INIT#

G_A20M#

G_IGNNE#

G_SMI#

LO/HI#

VRPWRGD

VRCHGNG

VR_HI/LO#

RSVD0

RSVD1

RSVD2

30

BC534

SCD1U16V

ZZ.10491.4F1

BC400

SCD1U16V

1

4

8

48

2

5

3

11

47

46

10

9

32

12

33

34

35

39

40

+3.3V

BC399

SCD1U16V

NMI_1

INTR_1

INIT#_1

A20M#_1

IGNNE#_1

SMI#_1

STPCLK#_1

NB_SUS#_3

CKG_CPUSTP#_3SB_CPUSTP#_3

GAS_CC_LO/HI#_3

PWRGOOD_2

VRCHANGE#_3

BC533

SCD1U16V

ZZ.10491.4F1

BC465

SCD1U16V

NB_SUS#_3 8

CKG_CPUSTP#_3 3

VR_HI/LO#_3

C

VCC_IO_CPU

R557 DUMMY-R3

1 2

ZZ.DUMMY.XR3

VR_HI/LO#_3 5

BC466

SCD1U16V

GROUP B

2

2222K

K

CC_LO/HI# 4

CPU internal

pull high

Use Open

Drain

31

Q39

DTC124EUA-U

ZZ.00124.A1K

C-Note Change

D

GROUP A

VGATE_35

PCIRST#_38,15,16,18,19,27,36

+3.3V

U33D

14

13

12 11

TSLCX125

7

Always Mount

SB_INIT#_3

SB_SMI#_3

SB_STPCLK#_3

SB_NMI_3

SB_A20M#_3

SB_CPUSTP#_3

SB_SUS#_3 NB_SUS#_3

1

2

+3.3V

C-NOTE 0116

Add 3.3V PH

12

R251

10KR3

RN22

1

2

3

4 5

SRN0

66.R0036.080

RN24

1

2

3

4 5

SRN0

66.R0036.080

R554

1 2

0R3-0-U

U30

A

VCC

B

GND3Y

NC7SZ32

8

7

6

8

7

6

( Default nonuse )

+3.3V

+3.3V

5

4

14

9 8

7

CPU_LO/HI# 16

CC_LO/HI# 4

VR_HI/LO#_3

INIT#_1

SMI#_1

INTR_1SB_INTR_3

STPCLK#_1

IGNNE#_1SB_IGNNE#_3

NMI_1

A20M#_1

CKG_CPUSTP#_3

E

BC150

SCD1U16V

U33C

10

TSLCX125

PWRGOOD_2

CPU internal

pull high

Use Open

Drain

R95

1 2

DUMMY-R3

R425

1 2

DUMMY-R3

+3.3V

+2.5V

R254

PWRGOOD_24

VRCHANGE#_316

INIT#_14

FERR#_14

INTR_14

1 1

IGNNE#_14

NMI_14

A20M#_14

STPCLK#_14

SMI#_14

INIT#_1

FERR#_1

INTR_1

IGNNE#_1

NMI_1

A20M#_1

STPCLK#_1

SMI#_1

1 2

1K5R3

R295

1K5R3

1 2

R174 10KR3

1 2

1 2

1K5R3

R158

RN11

1

2

3

4 5

SRN1K5

R156

1 2

R155

1 2

270R3

680R3

+3.3V

VCC_IO_CPU

8

7

6

(FERR# FROM CPU TO M1535)

BC94

SCD1U16V

78.10491.4F1

VCC_IO_CPU

+3.3V

12

12

R169

R168

4K7R3

FERR_G

2

3 1

Q13

S2N3904

84.03904.011

4K7R3

63.47234.151

63.47234.151

SB_FERR#_316

SB_FERR#_3 FERR#_1

GCL powergood

+3.3V

12

R434

22KR3

BC361

SCD1U

78.10492.4B1

+3.3V

147

5 6

SB change

HC14->LCX14

U66C

TSLCX14

+3.3V

VCC_IO_CPU

+3.3V

147

9 8

+3.3V 3,5,7,8,9,10,13,14,15,16,17,18,19,21,22,25,27,28,30,32,36

VCC_IO_CPU 4,7,9

U66D

TSLCX14

SB_LO/HI#_316

PWRGOOD_3

C-NOTE 0116

Add 3.3V PH

+3.3V

12

R436

10KR3

+3.3V

147

13 12

SB change

HC14->LCX14

U66F

TSLCX14

C-Note 0116

Add 0R3

R433

1 2

0R3-0-U

Always Mount

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221,

Title

GEYSERILLE&CPU THERMAL SENSOR

Size Document Number Rev

A3

C-Note

Date: Sheet of

Taiwan,R.O.C.

6 36Thursday, January 10, 2002

VR_HI/LO#_3 5

-4

Page 7

A

www.kythuatvitinh.com

SB Change

4 4

Remove R329 Q21

TSAHC125 change to

NC7SZ125

SERIAL_EN use GPO

Check if CHGR_FLASH

is IPH in SR12

CHGR_FLASH30

Charger F/W Flash

Circuit

U83

1

OE#

2

A

GND3Y

NC7SZ125

VCC

SOUT1_516,24

5

4

(From Super IO)

+5V

B

SIN1_5 16,24

C

+2.5V

Layout

60 mil

12

TC4

SERIAL_EN 16

+5V

12

R328

10KR3

U84

1

OE#

2

A

GND3Y

NC7SZ125

VCC

+5V

5

4

ST47U6D3VDM

12

12

R447

1KR3F

BC388

SC20P

R450

4K02R3F

U10

4 5

G D

S

3

2

S

1

S

D

Generate CLK_VCC ( 2.5V )

C-Note 0129

Remove BC550

SI4880DY

D

6

7

D

8

D

2.5V_3

1 2

2.5V_4

R448

1K5R3

+3.3V

Layout

20 mil

1228 Remove

This CAP will

cause VGA flicker

U68

1

OUT

2

VEE

3

IN+

MAX4322EUK-T

VCC

IN-

2.5V_2

E

TO CLOCKGEN

+5V

MAX1717_VREF

Layout

BC392

SCD1U16V

5

4

R445

1 2

1KR3

20 mil

Generate CLK_VREF (1.25V) Generate CMOS_VREF (1V)

3 3

12

12

R131

2KR3D

R130

2KR3D

TO CPU

CLK_VREF

Layout

60 mil

BC79

SC1U10V3ZY

BC476

SC1U10V3ZY

78.10593.4B1

+5V

+5V 5,8,9,11,13,14,15,16,17,19,20,22,23,24,25,27,28,30,32,34,35

BC78

SC1U10V3ZY

78.10593.4B1

+2.5V

+2.5V

12

12

64.20016.651

R474

3KR3D

64.30016.651

R164

2KR3D

TO CPU

SPEC 1V +/- 100mV

CMOS_VREF

Layout

60 mil

BC91

SCD1U

78.10492.4B1

BC90

SCD1U

78.10492.4B1

2 2

Generate VCC_IO_CPU=1.5V

Generate GTL_VREF_CPU (1V)

1.5V_2

R490

3KR3D

12

1.5V_1

U74

1

OUT

2

VEE

3

IN+

MAX4322EUK-T

BC486

SCD1U16V

VCC_IO_CPU

Layout

12

R149

BC88

SCD1U

1KR3F

12

R151

2KR3D

1 1

BC84

SCD1U

BC473

SC1U10V3ZY

BC470

SCD1U16V

C-Note 0129

Remove

BC113

BC394

SCD1U16V

C-Note 0129

Remove

BC114

GTL_VREF_CPU

Layout

60 mil

BC395

SC1000P50V

C-Note 0129

Remove

BC116

20 mil

SB change

Use AT-4 circuit

+5V

12

RA40

2K2R3

3

D29

APL431-U

+3.3V

1

2

VCC_IO_CPU

+3.3V 3,5,6,8,9,10,13,14,15,16,17,18,19,21,22,25,27,28,30,32,36

BC488

SC100P

1 2

R489

2KR3D

VCC_IO_CPU 4,6,9

VCC

+5V

5

4

IN-

1.5V_3

R479

1 2

1K5R3

R478

1 2

1KR3

Title

Size Document Number Rev

Date: Sheet of

+3.3V

D

BC491

SCD1U

1.5V_4

G

BC484

SC20P

Q34

SUD40N03

1

3 2

S

VCC_IO_CPU=1.5V

Layout

60 mil

POWER 2.5V/VRM/CPUIO

A3

C-Note

C-Note 0129

Remove BC551

VCC_IO_CPU

12

TC18

BC480

ST47U6D3VDM

SCD1U

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221,

Taiwan,R.O.C.

7 36Thursday, January 10, 2002

-4

Page 8

GND_V5

www.kythuatvitinh.com

GND_V2

TVD2

TVD3

TVD1

TVD0

TVD4

TVD5

TVD0V1TVD1V2TVD2U5TVD3V3TVD4T5TVD5U4TVD6T6TVD7

HD10

HD11

HD12

HD13

HD14

HD9

B17

A17

A15

E16

D16

D19

HD10

HD15

HD11

HD13

HD14

HD12

HREQ1#_1 4

HREQ2#_1 4

HREQ3#_1 4

HREQ4#_1 4

ADS#_1 4

BNR#_1 4

BPRI#_1 4

DBSY#_1 4

DEFER#_1 4

DRDY#_1 4

HLOCK#_1 4

HITM#_1 4

HIT#_1 4

BREQ0#_1 4

HTRDY#_1 4

CPURST#_1 4

RS0#_1 4

RS1#_1 4

RS2#_1 4

GND_V1

1228

Change

SC3300P50V3KX

TVD7

TVD6

U2

TVHS

TVCLKO

V4

TVCLKO

TV

BC54

SC560P

BC56

SC560P

BC55

TVVS

VGA14M_3

GINTAJ

NB_VLF5

NB_VLF1

NB_VLF2

W3

W4

Y4

W5

AA2

AB1

XTL1

XTLO

VLF1Y3VLF2

VLF5

TVHSV5TVVS

GINTR

TP2

TP3

TA+

TB-

TB+

TCLK-

TCLK+

TA-

TC-

TC+

NB_TD-

NB_TD+

Y5

AA5

AA4

AB4

AC3

AD3

AC2

AD2

AD1

AE1

TA-

TB-

TA+

TB+

TC-

TD-

TC+

TD+

TCLK-

TCLK+

LVDS

CPU

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27E9HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

A14

E18

E17

B14

E14

B11

B15

C15

D14

D13

C13

C12

HD26

HD23

HD28

HD24

HD19

HD16

HD17

HD27

HD22

HD21

HD25

HD18

HD20

HD38

E15

A13

B12

B13

A12

E13

A11

D12

D11

D10

HD38

HD32

HD29

HD36

HD35

HD34

HD33

HD30

HD37

HD31

PCI

R432

1 2

GINTAJ

0R3-0-U

RATIO#/CKRUN#_317 CLKRUN#_3 10,16,18,19,31,36

1 2

DUMMY-R3

C/BE#[0..3] 10,16,18,19,31,36

AD[0..31] 16,18,19,31,36

R118

AD1

AD0

AF14

AE14

AD0

HD39

E10

HD39

HD40

AD2

AE13

AD1

HD40E8HD41C9HD42D9HD43

HD41

AD5

AD6

AD3

AD4

AF13

AC14

AB14

AC13

AD2

AD3

AD4

AD5

HD44

B10

A10

C11

HD43

HD42

HD45

HD44

D

AD8

AD9

AD7

AD10

AD12

AD13

AD14

AD11

AB13

AE12

AD12

AB12

AC12

AF11

AE11

AD11

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

HD45

HD46E7HD47D8HD48B8HD49

HD50B6HD51B9HD52F8HD53D6HD54D7HD55C7HD56E5HD57A7HD58E6HD59B7HD60C6HD61D5HD62A6HD63

C10

HD49

HD47

HD51

HD52

HD46

HD48

HD50

HD53

LOCK#_3 10

PHOLD#_3 16,17

PHLDA#_3 10,16

FRAME#_3 10,16,18,19,31,36

PAR_3 10,16,18,19,31,36

SERR#_3 10,16,18,19,31,36

TRDY#_3 10,16,18,19,31,36

IRDY#_3 10,16,18,19,31,36

STOP#_3 10,16,18,19,31,36

DEVSEL#_3 10,16,18,19,31,36

PCIREQ#_3 10,16

PCIRST#_3 6,15,16,18,19,27,36

INTA#_3 10,16,36

REQ#0 10,18

REQ#1 10,31

REQ#2 10,19

REQ#3 10,36

REQ#4 10

REQ#5 10

GNT#0 10,18

GNT#1 10,31

GNT#2 10,19

GNT#3 10,36

GNT#4 10

GNT#5 10

E

AD15

AD18

AD16

AD17

AD19

AC11

AA8

AC9

AF8

AE8

AD15

AD16

AD17

AD18

HD57

HD55

HD54

HD56

HD58

AD21

AD23

AD20

AD24

AD25

AD22

AD26

AE7

AB8

AF7

AC8

AC7

AB7

AF6

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

CPURSTJ

BNRJ

A8

A19

D26

HD59

HD62

HD63

HD61

HD60

CPURST#_1

BNR#_1

AD29

AD30

AD27

AD28

AD31

GNT#2

REQ#2

REQ#0

GNT#3

REQ#1

GNT#0

GNT#5

GNT#1

GNT#4

AE6

AD6

AC6

AB6

AB5

AF4

AF3

AE3

AE2

AC5

AD5

AE4

AF5

AD27

AD28

AD29

AD30

AD31

PGNTJ5C4PREQJ5

PGNTJ0

PGNTJ1

PGNTJ2

PGNTJ3

PGNTJ4

PREQJ0

PREQJ1

PCI

GTL_REF3

GTL_REF1

GTL_REF2

LOCKJ

HITJ

BPRIJ

HREQJ0

HREQJ1

HREQJ2

HREQJ3

HREQJ4

DEFERJ

F23

E24

HREQ0#_1

HREQ1#_1

NB_VREF

F24

F25

E25

HREQ2#_1

HREQ4#_1

HREQ3#_1

R123

1 2

10KR2

R79

1 2

0R3-0-U

GND_V4

F26

HLOCK#_1

DEFER#_1

MCLK 3

63.R0004.151

G23

G24

HIT#_1

HTRDY#_1

G25

CPUTRDYJ

G26

HITM#_1

SDCLKI_D3 3

SDCLKO_D3 3

VGA14M_3 3,15

PCLK32_D3 3

CLK32K_3 16

F15

E12

E21

E26

BPRI#_1

NB_VREF

ALL TEST POINTS

are at the REAR of

BGA

MCLK

REQ#3

AD4

PREQJ2

PREQJ3

HITMJ

RSJ0

H23

RS0#_1

REQ#4

AF2

REQ#5

C5

PREQJ4

DEVSEL#_3

AB9

DEVSELJ

PAR_3

AB10

PAR

IRDY#_3

PHOLD#_3

PCLK32_D3

AB15

AC10

AC15

IRDYJ

PCICLK

TRDY#_3

AD10

PHOLDJ

PHLDA#_3

AD15

PHLDAJ

PTRDYJ

LOCK#_3

AE5

PLOCKJ

FRAME#_3

AE9

STOP#_3

AE10

FRAMEJ

SERR#_3

PCIRST#_3

RATIO#/CKRUN#_3

AE15

AF10

AF15

STOPJ

SERRJ

RESETJ

RATIOJ/PCK RUN#

C/BE#0

AF12

CBEJ0

C/BE#1

AB11

CBEJ1

C/BE#2

C/BE#3

AD9

AD7

CBEJ2

CBEJ3

HVDDA/PWROK

CKE1/PLLTST

GCLKI/GND

MCLKI/GND

MWEJ3/GND

CKE3/GND

AVSS5

AVSS2

AVSS1

GND/S

GND RGB

LPGND

LAGND

GND

TESTMDA4MFRQ1

MFRQ0B5TEST2EN

DCLKO

DCLKI

ADSJ

BREQJ0

RSJ1

RSJ2

DBSYJ

DRDYJ

J22

J23

J24

J25

K23

K22

H25

H26

ADS#_1

BREQ0#_1

DRDY#_1

DBSY#_1

RS1#_1

RS2#_1

SDCLKI_D3

SDCLKO_D3

+3.3V

NC

CLK32K

CKE0

AREQJ

A5

B3

PCIREQ#_3

NB_TESTMD

MFRQ1/AGPSTP#

Title

Size Document Number Rev

Custom

Date: Sheet of

NC

HCLK

B4

C3

SB Change

E22

R21

AA16

AA11

Power Source

M+3V

CLK32K_3

CKE0

HCLK1632_D2

12

NB_TEST2EN

MFRQ0/AGPBSY#

R444

0R2-0

1632_E22

12

R94

10KR5

+3.3V

12

G_SUSPENDJ

R99 0R3-0-U

1 2

MFRQ1/AGPSTP#10 AGP_STP#_3 16

1 2

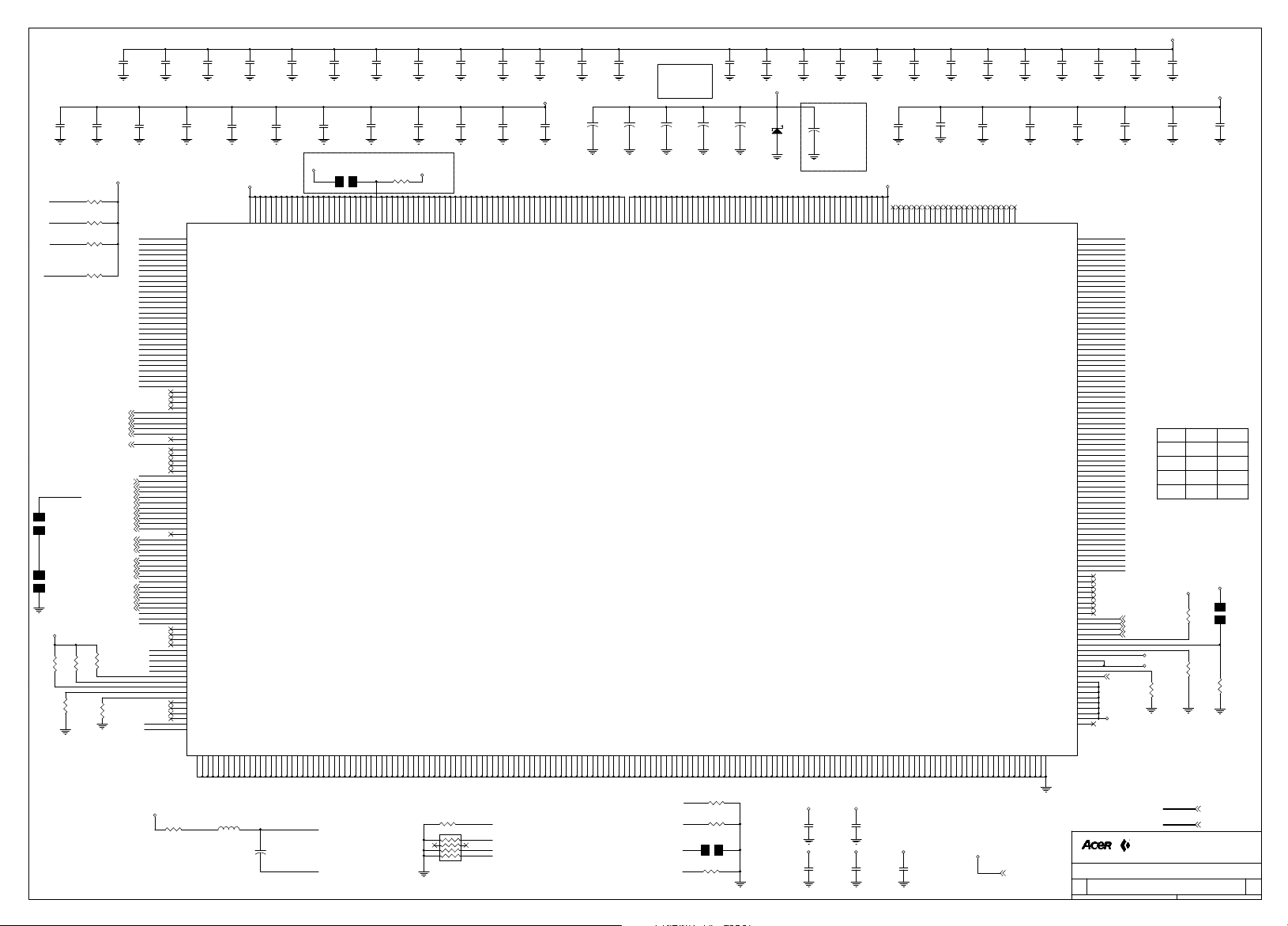

N0rthBridge -ALI M1632

C-Note

U9

M1632M-U2

71.M1632.A0U

AD14

G22

M1632_G22

HCLK

CKE1

K24

AF9

NB_GCLKI_GND

AF18

MCLK

CKE2

P21

AA15

CKE3

AB2

AA1

Y1

L22

GNDA

L21

GNDA

B1

A1

W7

AA3

T16

G/T

T14

G/T

T13

G/T

T11

G/T

R15

G/T

R14

G/T

R13

G/T

R12

G/T

P16

G/T

P15

G/T

P14

G/T

P13

G/T

P12

G/T

P11

G/T

N16

G/T

N15

G/T

N14

G/T

N13

G/T

N12

G/T

N11

G/T

M15

G/T

M14

G/T

M13

G/T

M12

G/T

L16

G/T

L14

G/T

L13

G/T

L11

G/T

AF26

GND

AF1

GND

AD19

GND

AD13

GND

AD8

GND

AC23

GND

AC4

GND

AA21

GND

AA14

GND

AA13

GND

AA6

GND

W24

GND

V26

GND

T21

GND

P6

GND

P1

GND

N21

GND

N6

GND

N3

GND

M21

GND

J26

GND

H24

GND

F21

GND

F16

GND

F14

GND

F13

GND

F6

GND

D23

GND

D4

GND

C19

GND

C14

GND

C8

GND

B2

GND

A26

GND

A18

GND

A9

GND

12

R85

10KR5

C-Note 0116 Change

R125

SB_SUS#_3

DUMMY-R3

tp NB_SUS#_3

R124

1 2

NB_SUS#_3 6

0R3-0-U

VGA_SUSPEND#_3 15,16

AGP_BUSY#_3 16MFRQ0/AGPBSY#10

R431

0R3-0-U

Acer Incorporated

21F,88,Sec. 1,Hsin Tai Wu Rd.

Hsichih,Taipei Hsien 221,

Taiwan,R.O.C.

A

MD[0..63]

MD[0..63]12

MD0

MD5

MD1

MD3

MD4

MD2

+3.3V

For_SB

4 4

BC354

BC367

BC353

SCD1U16V

SCD1U16V

78.10491.4F1

ADVDD_V1

AVDD_V3

AVDDA

M+2.5V

BC377

SCD1U16V

Near M+2.5V

3 3

Power Pin

M+3V

Near M+3V

Power Pin

BC379

SCD1U16V

78.10491.4F1

AVDDA

AVDD_V2

BC378

SC4D7U10V5ZY

BC380

SC4D7U10V5ZY

SCD1U16V

+2.5V

AVDD_V5

AVDD_V1

ADVDD_V2

M+2.5V

+3.3V

78.10491.4F1

+5V

NB_VTT

M+3V

+2.5V

+2.5V

2 2

NB_SMBDATA15

NB_SMCLK15

DRAM

SRAS#0 12 HREQ0#_1 4

SRAS#1 12

SCAS#0 12

SCAS#1 12

MWE#0 12

MWE#1 12

CKE0 10,12

CKE1 10,12

CKE2 12

1 1

+5V

CKE3 12

TV

TVD[0..7]

TVD[0..7] 10,15

TVHS 10,15

TVVS 10,15

TVCLKO 15

+3.3V

+3.3V 3,5,6,7,9,10,13,14,15,16,17,18,19,21,22,25,27,28,30,32,36

+5V 5,7,9,11,13,14,15,16,17,19,20,22,23,24,25,27,28,30,32,34,35

Y8

U6

F19

F11

E11

D1

C1

H22

H21

AA12

Y20

Y19

AC1

Y2

W2

W1

V20

Y18

W20

AA22

AB22

W22

V22

AB3

Y7

AA18

AA9

V21

V6

J21

J6

F18

F9

T15

T12

R16

R11

M16

M11

L15

L12

AA20

AA17

AA10

AA7

Y21

Y6

W6

U21

T4

L4

K21

H6

G21

G6

F20

F17

F12

F10

F7

MA[0..14] 12

CS#[0..3] 12

DQMA[0..7] 12

5VVCC2

5VVCC1

VTT

VTT

VTT

VCC/R

VCC/S

AVDDA

DVDDA

VCCPL3

VCCPL2

VCCPL1

AVDD5

AVDD2

AVDD1

ADVDD2

VSUS2

VSUS2

VSUS2

VSUS2

VSUS3

VSUS3

VSUS3

LAVDD

LPVDD

VCCI

VCCI

VCCI

VCCI

VCCI

VCCI

VCCI

VCCI

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

M+3V

M23

GPIO0A2GPIO1

A3

K25

L26

L25

M26

M24

MD0

MD1

MD2

MD3

MD4

MD5

VSUS2.VSUS3

USE M+POWER

CRT

RED

BLUE

HSYNC

GREEND3VSYNC

E1

E2

C2

D2

B

G

HSYNC_3

R

VSYNC_3

R420

360R5F

M+3V 11,12,16,18,21,22,28,32

ALL TEST POINTS are at the REAR of BGA

MD19

MD13

MD12

MD8

MD7

MD6

MD9

MD10

MD14

MD11

MD15

N26

N24

P23

P25

R23

R25

P22

T23

T25

T22

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD25

MD18

MD20

MD21

MD17

MD16

AD22

AF22

AB21

MD15

MD16

MD17

MD28

MD29

MD31

MD26

MD27

MD30

MD23

MD22

MD24

MD33

MD32

MD37

MD34

MD36

MD35

AE21

AB20

AD20

AE20

AC19

AF19

AC18

AE18

AD17

AF17

AB17

AE16

AC16

K26

L23

M22

L24

M25

N23

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

POWER

LCD

EVDD

I2SCL

SUSPG

FLMG3SFCLK

I2SDA

F1

F2

F3

FPVDD_3

DDC_DATA_5

DDC_CLK_5

AVDD_V3

ETSTJ

ENBLT

F4

F5

G1

ENTESTJ

12

VGA_SUSPEND#_3

BACKLIGHT_ON_3

+3.3V

PD0G2PD1H2PD2H1PD3J2PD4J1PD5H4PD6K6PD7J4PD8J3PD9

G4LPG5

No CMOS Signal

C-Note 1222 Change

LCD

PD10K2PD11J5PD12K1PD13K3PD14L6PD15L2PD16K5PD17L1PD18L3PD19M6PD20K4PD21M4PD22M5PD23M1DE

L5

BACKLIGHT_ON_3 13

FPVDD_3 14

IRSETE3COMP

E4

COMP

IRSET

12

GND_V3

4K7R3

R421

SCD1U

MD38

MD39

MD40

N25

N22

P26

MD37

MD38

MD39

63.47234.151

+3.3V

MD40

4K7R3

MD41

MD43

MD42

MD44

P24

R26

R24

R22

MD41

MD42

MD43

EVEEH5IMIOM2IMIN

H3

M3

IMIO

IMIN

TP4

12

R71

CRT

B

MD53

MD46

MD48

MD54

MD51

MD50

MD49

MD55

MD47

MD52

MD58

MD56

MD45

T26

T24

MD44

MD45

MD46

CAPD0R6CAPD1T2CAPD2T1CAPD3R5CAPD4R2CAPD5R4CAPD6R1CAPD7R3CAPD8P5CAPD9

CAPD0

CAPD1

CAPD[0..15]

C-Note 1222 Change

MD57

U23

AE22

AC21

AD21

AF21

AC20

AF20

AB19

AE19

AB18

AD18

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

DRAM

ZV

CAPD10P3CAPD11P4CAPD12N5CAPD13N2CAPD14N1CAPD15N4CAPHS

P2

CAPD6

CAPD8

CAPD9

CAPD7

CAPD4

CAPD5

CAPD3

CAPD2

CAPD12

CAPD11

CAPD10

Not Support ZV

LVDS

TA- 14

TA+ 14

TB- 14

TB+ 14

TC- 14

TC+ 14

TCLK- 14

TCLK+ 14

R 13,35

G 13,35

B 13,35

HSYNC_3 13

VSYNC_3 13

DDC_DATA_5 13

DDC_CLK_5 13

AA19

MD57

CAPD13

HA[3..31]4

MD58

TP7

TP8

MD59

MD63

MD61

MD62

MD60

AE17

AC17

MD59

CAPD15

CAPD14

DQMA0

MWE#1

MWE#0

SCAS#0

SCAS#1

SCAS#2

MWE#2

AD16

AF16

AB16

U24

U25

U26

U22

V25

V24

V23

MD60

MD61

MD62

MD63

MWEJ0

MWEJ1

MWEJ2

SCASJ0

SCASJ1

SCASJ2

HA3

HA4

HA5

HA6

HA7

CAPVSU1CAPCLK

T3

U3

A25

B25

B26

E23

D24

C26

HA3

HA7

HA5

HA4

HA8

HA6

CAPHS

CAPCLK

CAPVS

SC

ZV

C-Note 1230 Change

Not Support ZV

ZV PULL LOW

DQMA3

DQMA2

DQMA1

W23

AF24

AE23

CASJ0

CASJ1

CASJ2

CASJ3

HA8

HA9

HA10

A23

C24

C25

HA9

HA10

HA11

CAPD[0..15] 10

CAPHS 10

CAPVS 10

CAPCLK 10

HA11

DQMA4

W26

CASJ4

HA12

D22

HA12

DQMA5

W25

B24

HA13

CASJ5

HA13

DQMA6

AD23

CASJ6

HA14

D25

HA14

DQMA7

AF23

CASJ7

HA15

F22

HA15

C

TP6

TP16

TP15

MA4

MA3

MA1

MA2

MA0

CS#2

CS#0

CS#3

CS#1

SRAS#1

SRAS#0

G_SUSPENDJ

PASJ_5

PASJ_4

SRAS#2

Y26

Y25

Y24

Y23

Y22

W21

AA24

AA25

AA26

AC22

AA23

AB23

AB26

AB25

AB24

MA0

MA1

MA2

MA3

RASJ0

RASJ1

RASJ2

RASJ3

RASJ4

HA16

HA17

HA18

HA19

HA20

A20

A21

C23

D21

C22

HA16

HA19

HA20

HA17

HA18

MA4

RASJ5

SRASJ0

SRASJ1

SRASJ2

SUSPENDJ

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

B23

A22

B21

E20

B22

B19

A24

B20

C20

D20

HA26

HA23

HA24

HA22

HA30

HA21

HA27

HA25

HA28

HA29

HD[0..63]4

TVD[0..7]

MA9

MA5

MA7HD1

MA8

MA6

MA10

MA11

MA12

MA13

MA14

AC26

AC25

AC24

AD26

AD25

AE26

AD24

AE24

AE25

AF25

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HA31

E19

B18

B16

A16

C18

C17

D18

D15

D17

C16

C21

HA31

HD0

HD2

HD3

HD8

HD4

HD6

HD9

HD7

HD5

CPU

SB Change

Power Source

M+3V

HVDDA

1 2

GND_V2

GND_V1

GND_V3

GND_V4

HCLK1632_D2 3

12

R437

DUMMY-R2

HCLK_1632D2_SET

12

BC356

DUMMY-C3

8 36Thursday, January 10, 2002

12

R443

0R3-0-U

R108

10KR5

63.10333.161

GND_V5

GNDA

+3.3V

-4

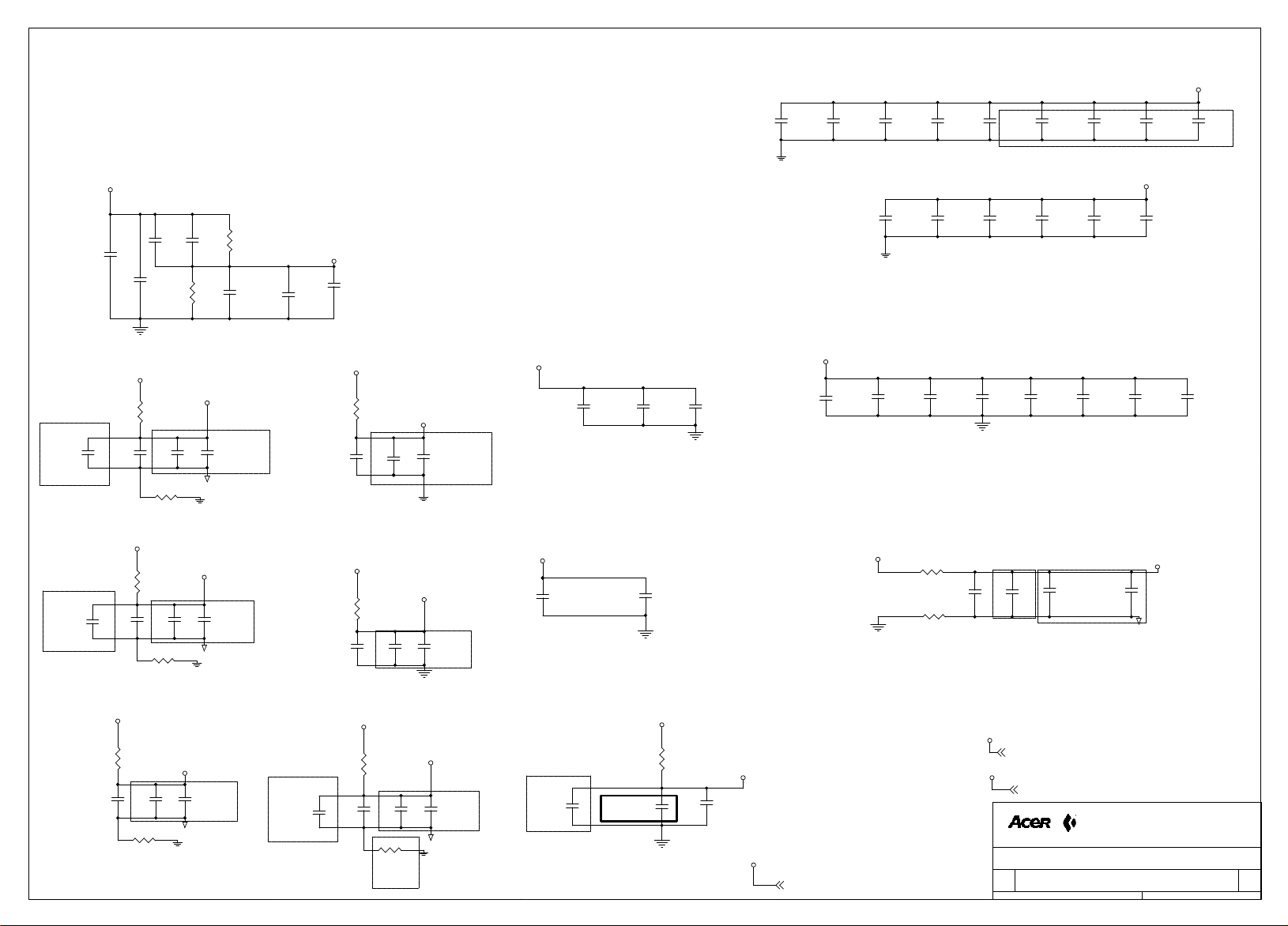

Page 9

A

www.kythuatvitinh.com

B

C

D

E

ALL CAP. are near NB power pins

+3.3V

BC369

SCD1U16V

BC381

SCD1U16V

BC373

SCD1U16V

BC372

SCD1U16V

BC375

SCD1U16V

BC358

SCD1U16V

BC350

SCD1U16V

BC349

SCD1U16V

BC342

SCD1U16V

4 4

VCC_IO_CPU

BC355

SCD1U16V

3 3

BC332

SCD1U16V

78.10491.4F1

BC317

SC1000P50V3KX

2 2

BC331

SCD1U16V

BC319

SC1000P50V3KX

NB V_REF=2/3 VTT R353=2R354

BC364

BC360

SCD1U16V

+2.5V

+2.5V

12

SCD1U16V

12

1 2

R414

0R3-0-U

1 2

R442

150R5F

R413

0R3-0-U

for _SB

BC328

SC1U25V5ZY

78.10592.411

R412

0R3-0-U

for _SB

BC327

SC1U25V5ZY

R416

0R3-0-U

BC366

SCD1U16V

12

AVDD_V1

AVDD_V2

BC320

SC10U16V0ZY

12

R439

75R5F

SC1000P50V3KX

Layout

40 mil

BC318

SC10U16V0ZY

78.10691.431

GND_V1

Layout

40 mil

GND_V2

BC365

Layout

80 mil

NB_VREF

BC362

SC1000P50V3KX

SC1000P50V3KX

BC382

SC1000P50V3KX

+2.5V

12

BC53

+2.5V

BC315

R63

0R3-0-U

for _SB

BC321

SC1U25V5ZY

12

R415

0R3-0-U

BC314

SC1U25V5ZY

for _SB

ADVDD_V1

BC52

SC10U16V0ZY

ADVDD_V2

BC316

SC10U16V0ZY

Layout

40 mil

Layout

40 mil

+5V

+3.3V

BC77

SC10U16V0ZY

78.10691.431

BC344

SCD1U16V

78.10491.4F1

BC281

SCD1U16V

78.10491.4F1

BC72

78.10691.431

SC10U16V0ZY

BC340

SCD1U16V

78.10491.4F1

+2.5V

BC384

SCD1U16V

+2.5V

BC348

SCD1U16V

BC343

SCD1U16V

1 2

BC352

SCD1U16V

BC359

SCD1U16V

R446

0R5

BC391

SC1000P50V3KX

1 2

R449

0R5

BC368

SCD1U16V

BC341

SCD1U16V

for _SB

BC383

SC1U25V5ZY

BC357

SCD1U16V

BC337

SCD1U16V

for _SB

BC390

SC10U16V0ZY

Layout

40 mil

BC345

SCD1U16V

BC376

SCD1U16V

BC386

SCD1U16V

+3.3V

BC385

SCD1U16V

AVDDA

GNDA

BC351

SCD1U16V

BC374

SCD1U16V

+2.5V

12

R75

0R3-0-U

for _SB

BC322

1 1

BC59

SC1000P50V3KX

SC1U25V5ZY

1 2

R72

0R3-0-U

AVDD_V3

BC57

SC10U16V0ZY

Layout

40 mil

GND_V3

SCD1U16V

BC330

+2.5V

12

BC336

SC1000P50V3KX

R422

0R3-0-U

for _SB

BC326

SC1U25V5ZY

1 2

R417

0R3-0-U

AVDD_V5

BC325

SC10U16V0ZY

GND_V5

FOR_SB

Layout

40 mil

BC363

SCD1U16V

78.10491.4F1

C-Note 0129

Remove

BC194/195

SC10U16V0ZY

ZZ.10691.431

SB Add

BC544

+2.5V

12

R121

0R5

Layout

40 mil

BC74

SC1000P50V3KX

HVDDA

+5V

+5V 5,7,8,11,13,14,15,16,17,19,20,22,23,24,25,27,28,30,32,34,35

VCC_IO_CPU

VCC_IO_CPU 4,6,7

+3.3V

+3.3V 3,5,6,7,8,10,13,14,15,16,17,18,19,21,22,25,27,28,30,32,36

Acer Incorporated