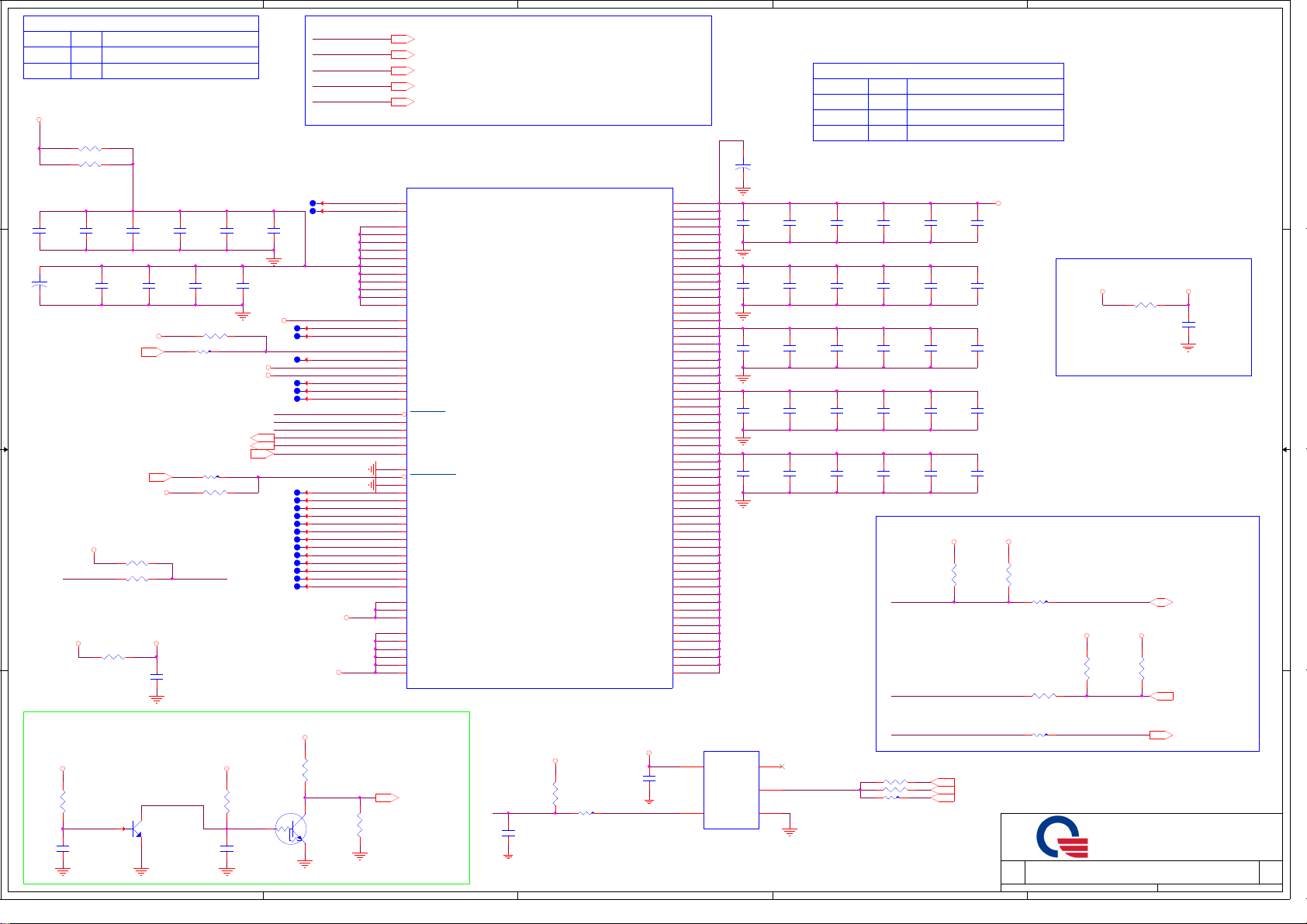

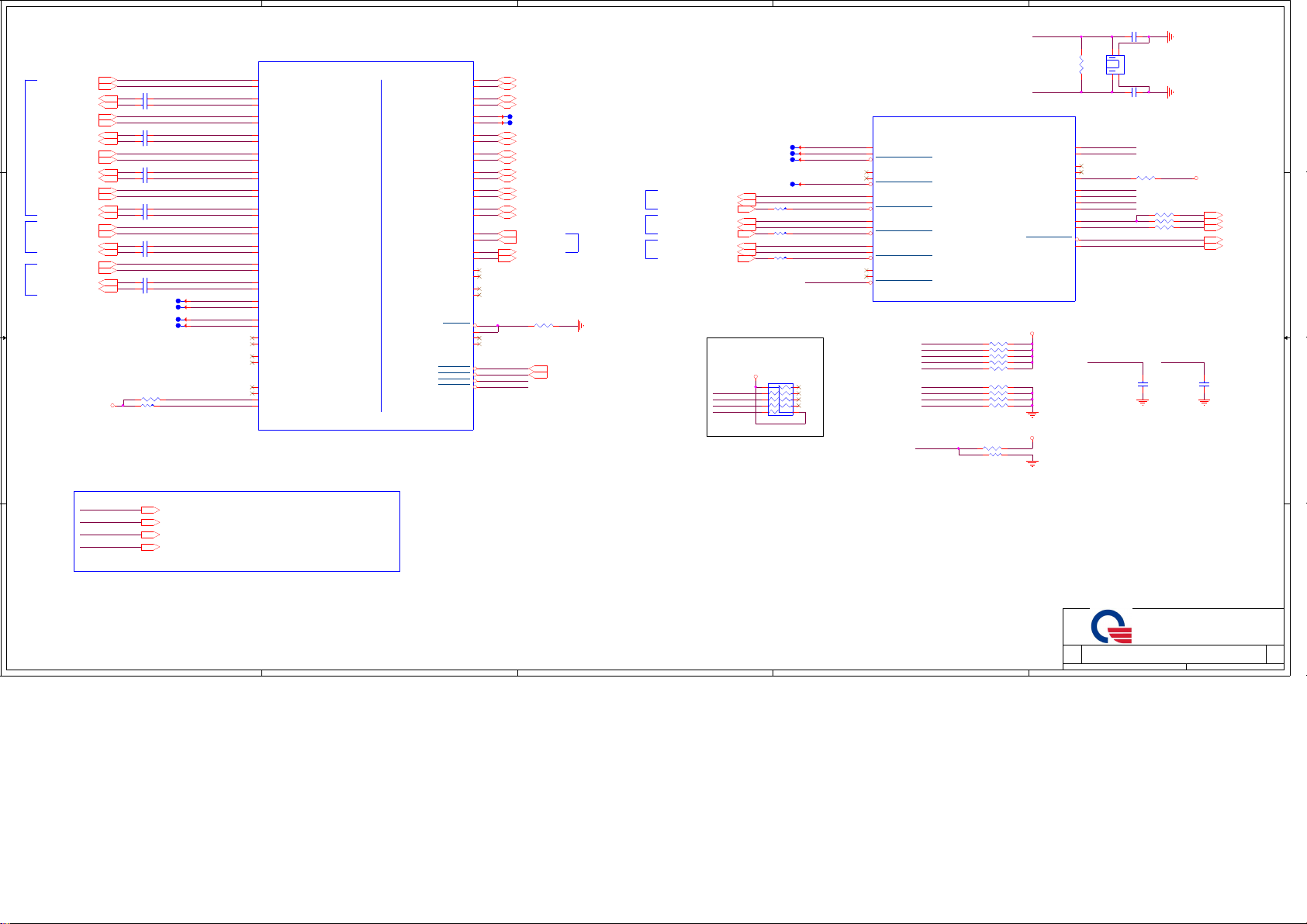

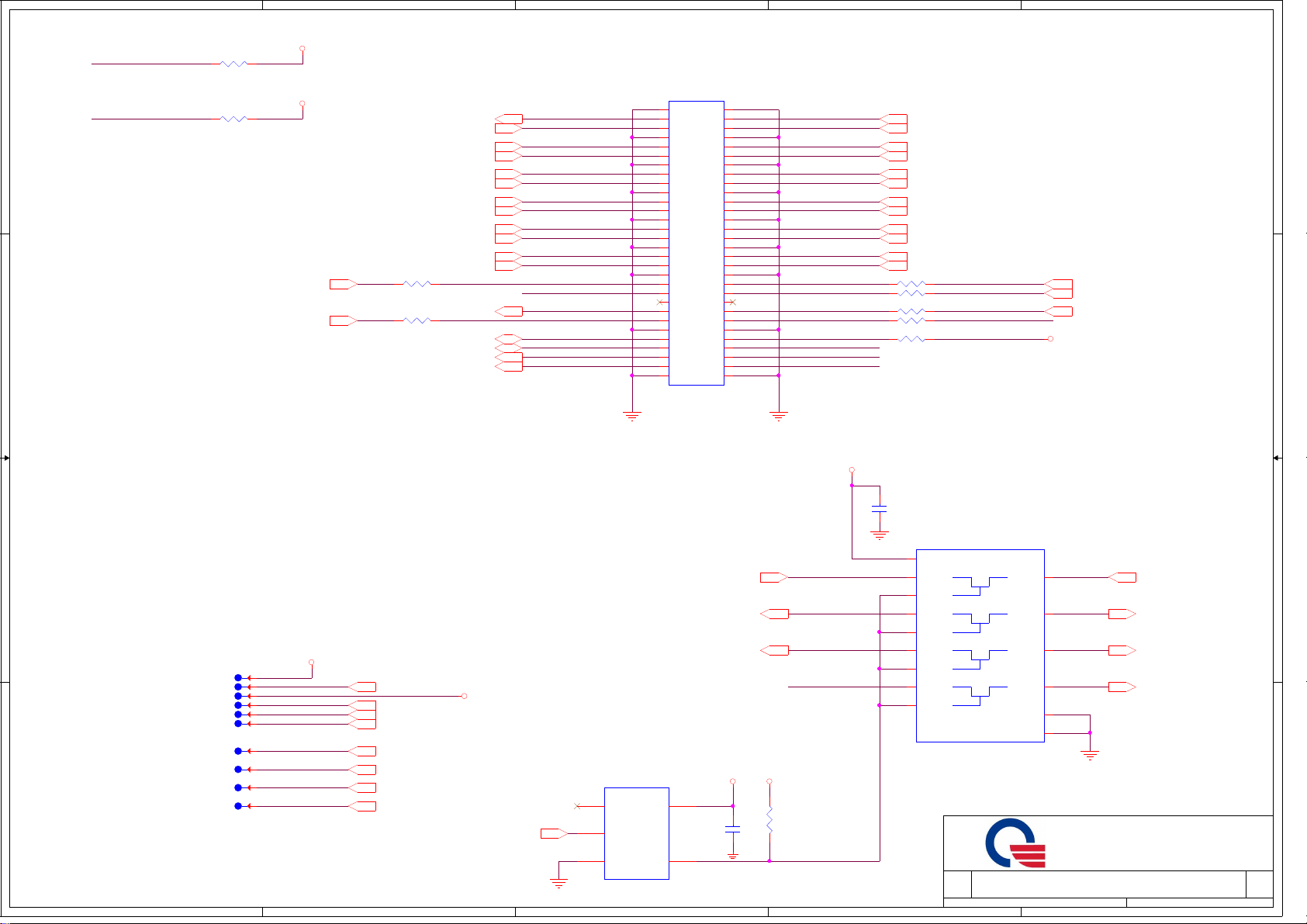

Acer Aspire R3-471 Schematics

5

4

3

2

1

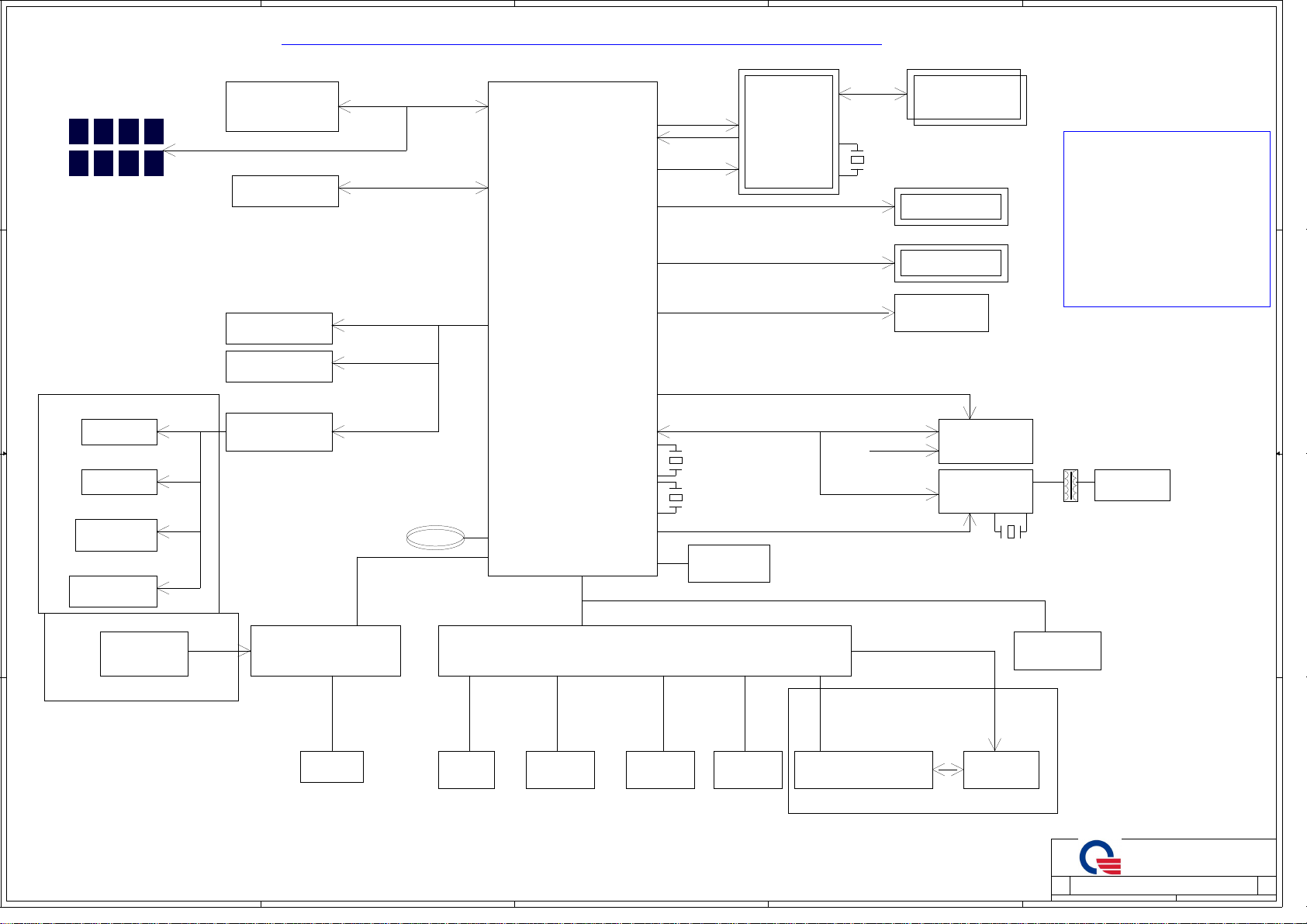

ZQX_DDR3 BDW ULT SYSTEM BLOCK DIAGRAM

Dual Channel DDR III

D D

Memory Down

DDR3L-SODIMM

P15

2Rx16

Max. 4G

P14

SATA - HDD

P26

1066/1333/1600 MHZ

SATA0

Broadwell ULT 15W

MCP 1168pins

IMC

DC+GT3

40 mm X 24 mm

SATA

PCI-E x4

TX/RX

CLK

eDP

PCIE-5

EDP

GPU

N15S-GT

N15V-GM

Display

P16~P21

X'TAL 27MHz

VRAM

DDR3

eDP Conn.

P23

P21

BOM

IV@ : iGPU

EV@ : Optimus

TDI@ : Touch pad I2C

TSU@ : Touch screen USB

TSI@ : Touch screen I2C

SP@ : Special part

TPM@ : TPM

01

TPMS@ : TPM IC OPTION

DDI1

DP

HDMI Conn.

P25

GT@ : N15S-GT

GM@ : N15V-GM

GMS@ : N15V-GM

USB2-0

CCD(Camera)

C C

Touch Screen(option)

P23

P23

USB2-2

USB2-5

Integrated PCH

USB2.0

USB3.0/2.0

CLK

USB3-1

USB board

I/O Board Conn.USB2 IO

P28

USB2-1,2 ,7

PCI-E x1

X'TAL

32.768KHz

USB2 IO

X'TAL 24MHz

P8

Card Reader

BATTERY

Azalia

B B

RTC

IHDA

LPC

P2~P13

CLK

SPI

SPI ROM

P8

Universal jack

PCIE-4

USB2-4

PCIE-3

USB3 Port

MB side

P28

Mini CARD

WLAN+BT

RTL8111GS

10/100/1G

P27

P24

X'TAL 25MHz

RJ45

P24

DMIC Array

Int. MIC

ALC283

AUDIO CODEC

P22

EC

IT8380

P30

TPM(option)

P26

Panel seosor board

Panel seosor board

Speaker*2

P22

A A

5

4

K/B Con.

P29

OCH1691WAD

HALL SENSOR

P23

Image Sensor

3

P32

Fan Driver

(PWM Type)

Gyro/eCompass/(Reserve)

G sensor

P29

Light Sensor

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

Block Diagram

Block Diagram

Block Diagram

ZQX

ZQX

ZQX

1 43Wednesday, September 03, 2014

1 43Wednesday, September 03, 2014

1

1 43Wednesday, September 03, 2014

1B

1B

1B

5

4

3

2

1

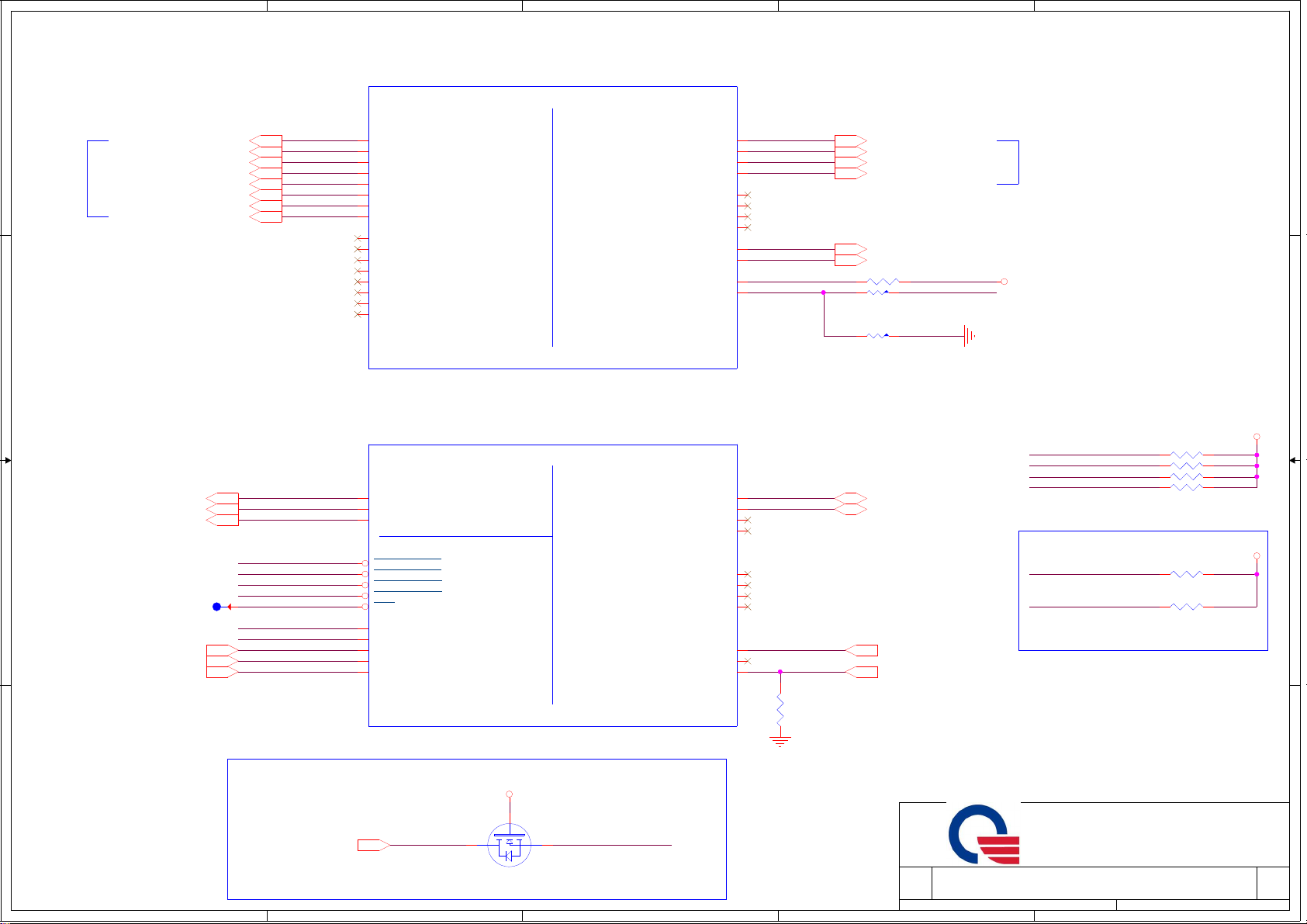

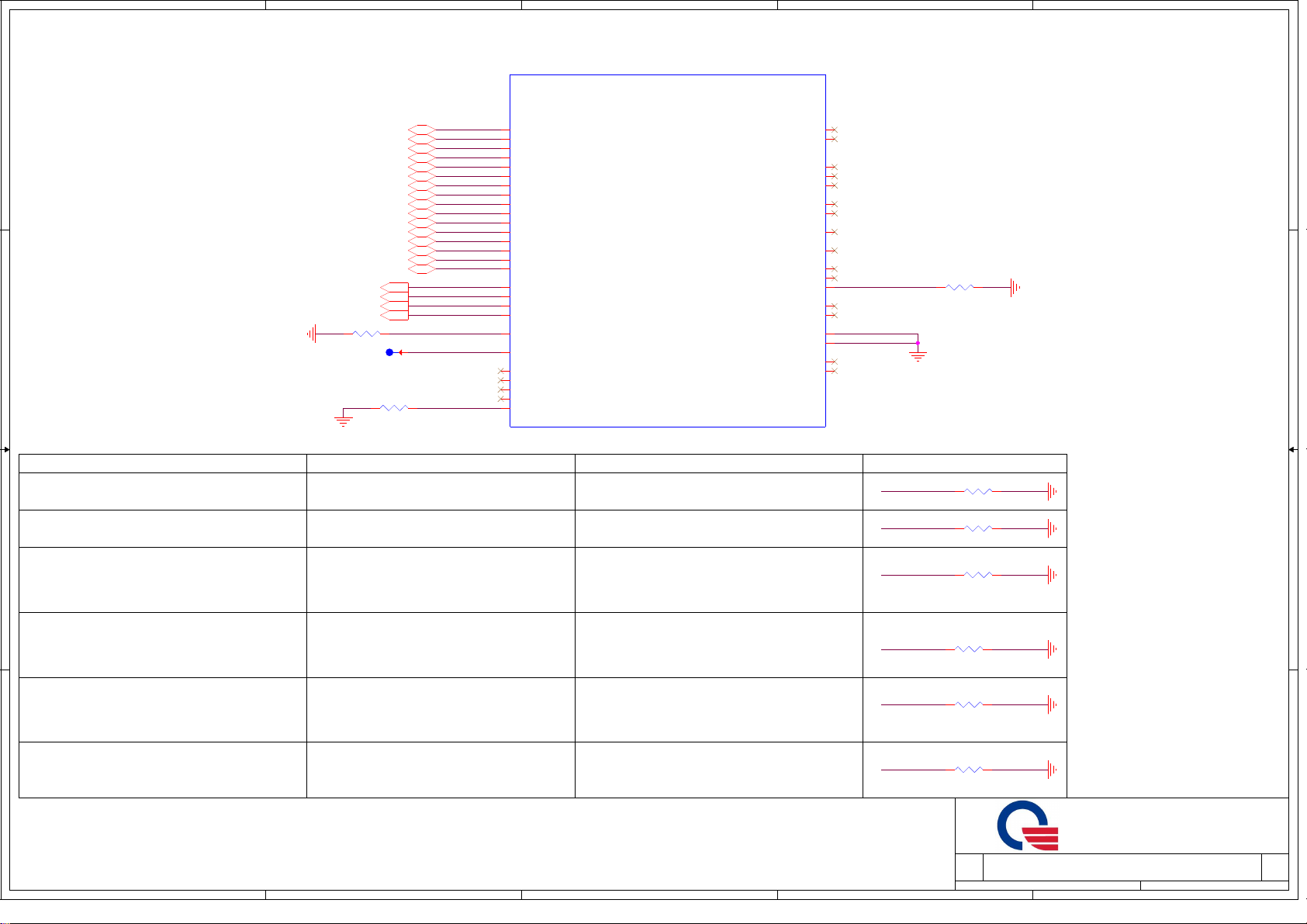

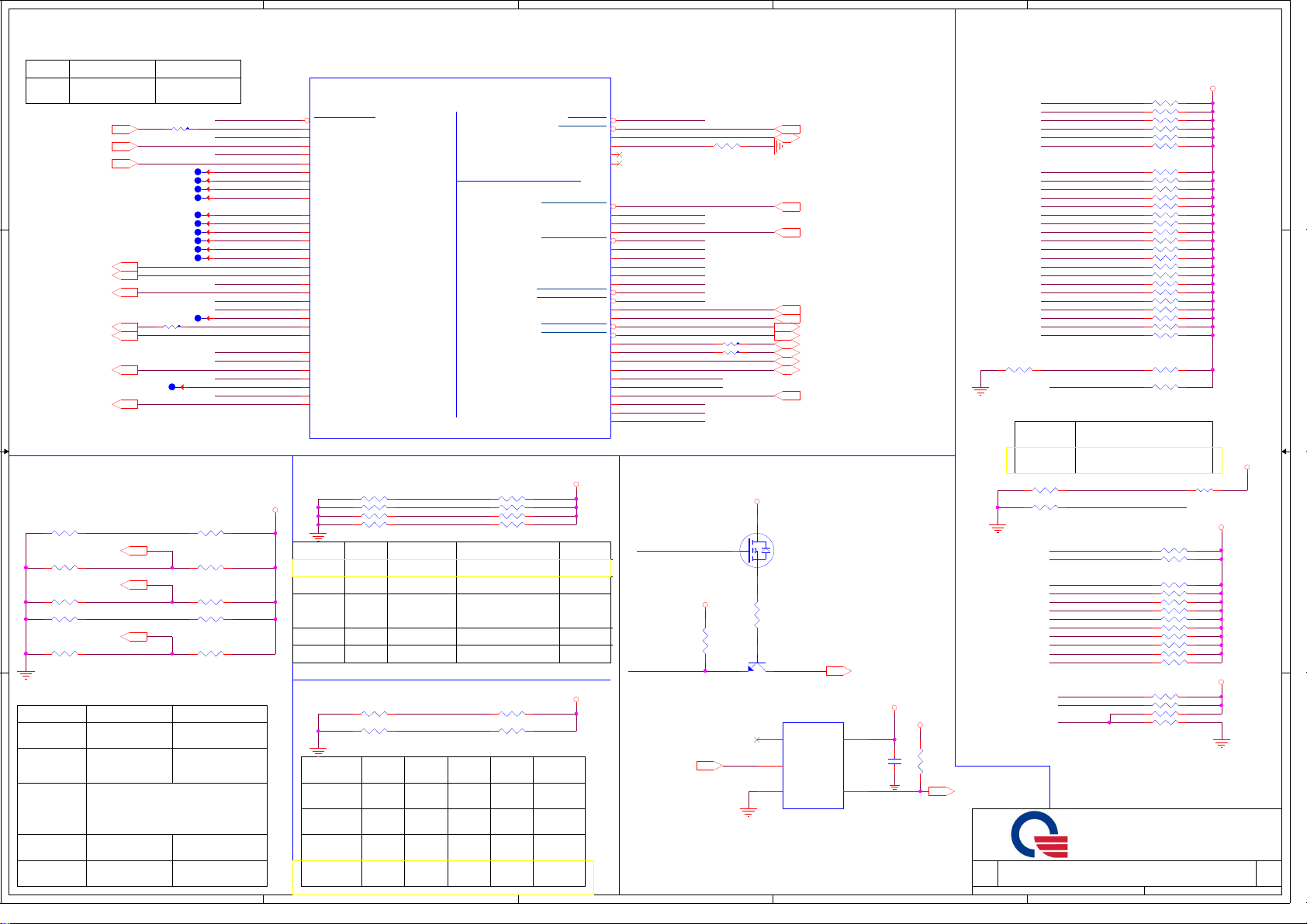

SP@ : i3-4010U i3-4020U i5-4210U

D D

HDMI

C C

B B

INT_HDMITX2N[25]

INT_HDMITX2P[25]

INT_HDMITX1N[25]

INT_HDMITX1P[25]

INT_HDMITX0N[25]

INT_HDMITX0P[25]

INT_HDMICLK-[25]

INT_HDMICLK+[25]

PCH_BRIGHT[23]

PCH_BLON[23]

EDP_VDD_EN[23]

TP94

BOARD_ID4[10]

BOARD_ID1[10]

BOARD_ID2[10]

PCH_BRIGHT

PCH_BLON

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

PCI_PME#

TPD_INT#_D

DGPU_SELECT#

BOARD_ID4

BOARD_ID1

BOARD_ID2

Haswell ULT (DISPLAY,eDP)

HSW_ULT_DDR3L

1 OF 19

HSW_ULT_DDR3L

9 OF 19

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AD4

B8

A9

C6

U6

P4

N4

N2

U7

R5

L1

L3

L4

U28A

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U28I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

+3V

+3V

+3V

+3V

+3V

eDP SIDEBAND

+3V

+3V

+3V

+3V

+3V_S5

PCIE

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_AUXN

EDP_AUXP

EDP_RCOMP

R537

100K_4

EDP_TXN0 [23]

EDP_TXP0 [23]

EDP_TXN1 [23]

EDP_TXP1 [23]

EDP_AUXN [23]

EDP_AUXP [23]

R229 24.9/F_4

R551 *0_4

R552 *0_4

HDMI_DDCCLK_SW [25]

HDMI_DDCDATA_SW [25]

INT_HDMI_HPD [25]

EDP_HPD [23]

02

eDP Panel

PCH_BRIGHTDP_UTIL

+VCCIOA_OUT

eDP_RCOMP

Trace length < 100 mils

Trace width = 20 mils

Trace spacing = 25 mils

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

TPD_INT#_D

DGPU_SELECT#

R184 10K_4

R142 10K_4

R141 10K_4

R491 10K_4

R159 10K_4

R488 10K_4

DGPU_SELECT#,0=defalt,1=iGPU

+3V

+3V

+3V

A A

TPD_INT#[28,29]

Q19

5

4

3

2

2N7002K

1

TPD_INT#_D

Add 10/31

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

2

PROJECT :

Haswell 3/5 (DDI/eDP)

Haswell 3/5 (DDI/eDP)

Haswell 3/5 (DDI/eDP)

ZQX

ZQX

ZQX

2 43

2 43

2 43

1

1B

1B

1B

5

4

3

2

1

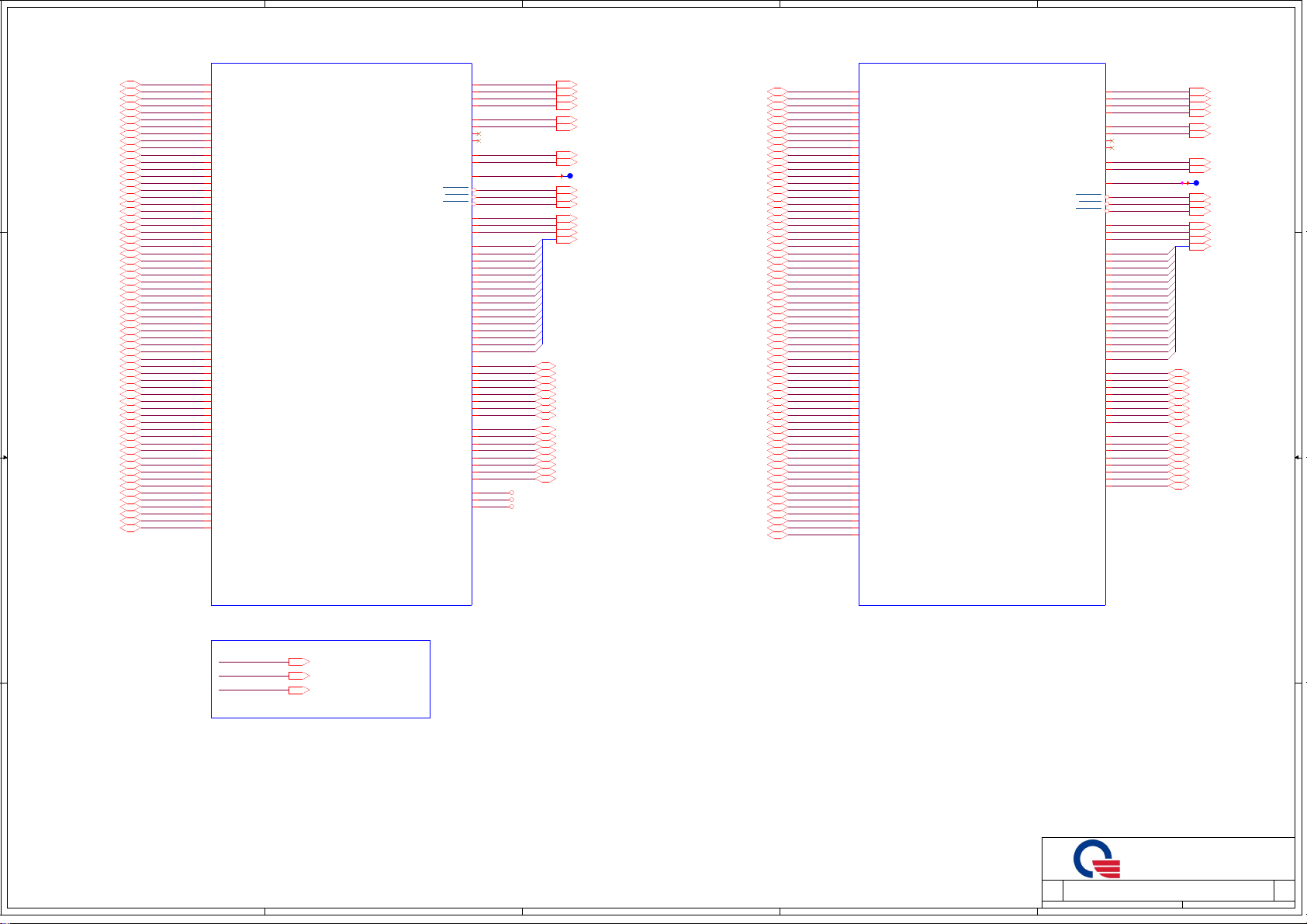

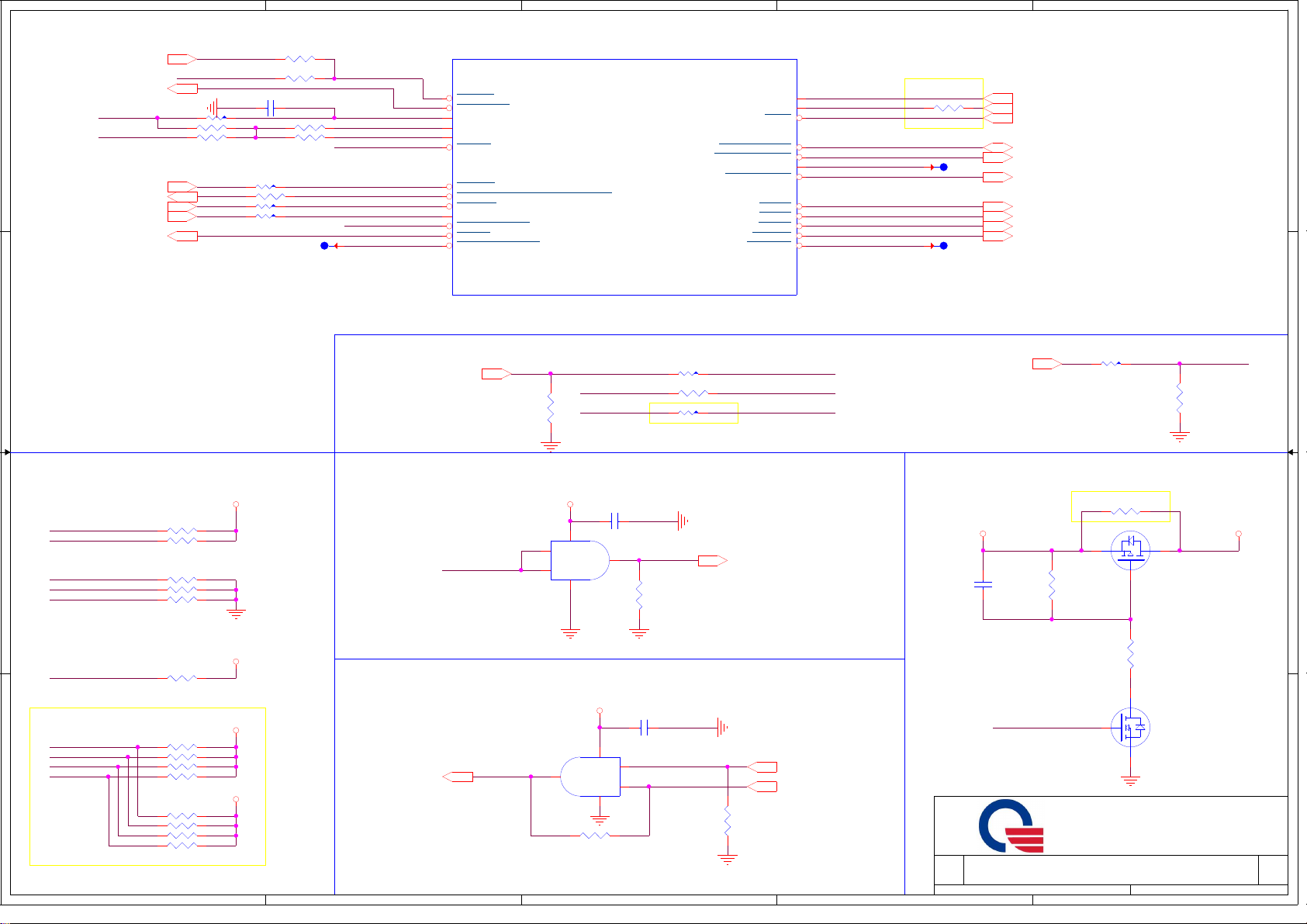

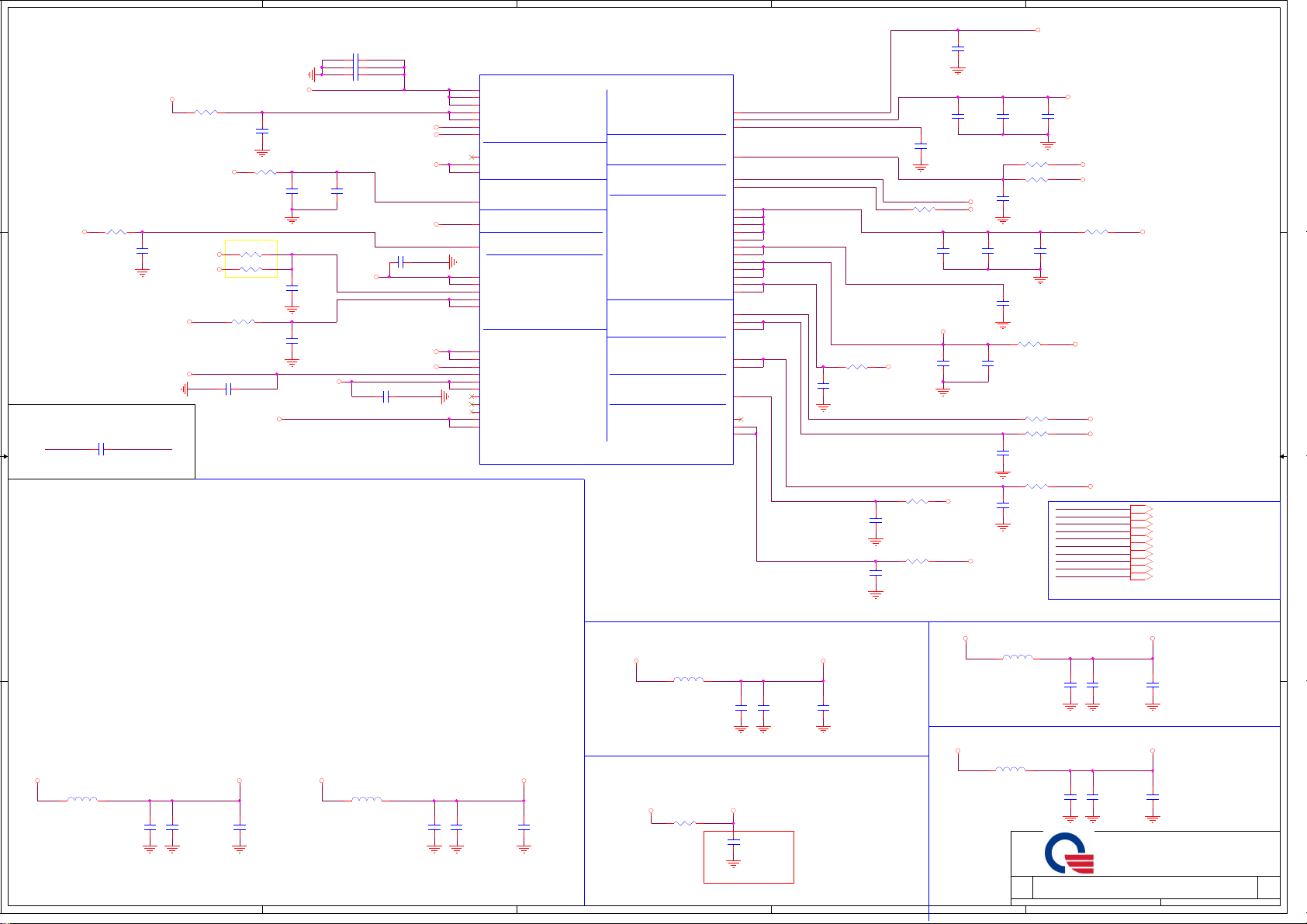

Change Data and DQS to interleave.

Haswell ULT (DDR3L) Haswell Processor (DDR3)

U28C

AH63

M_A_DQ0[14]

M_A_DQ1[14]

M_A_DQ2[14]

M_A_DQ3[14]

M_A_DQ4[14]

D D

C C

M_A_DQ5[14]

M_A_DQ6[14]

M_A_DQ7[14]

M_A_DQ8[14]

M_A_DQ9[14]

M_A_DQ10[14]

M_A_DQ11[14]

M_A_DQ12[14]

M_A_DQ13[14]

M_A_DQ14[14]

M_A_DQ15[14]

M_B_DQ0[15]

M_B_DQ1[15]

M_B_DQ2[15]

M_B_DQ3[15]

M_B_DQ4[15]

M_B_DQ5[15]

M_B_DQ6[15]

M_B_DQ7[15]

M_B_DQ8[15]

M_B_DQ9[15]

M_B_DQ10[15]

M_B_DQ11[15]

M_B_DQ12[15]

M_B_DQ13[15]

M_B_DQ14[15]

M_B_DQ15[15]

M_A_DQ16[14]

M_A_DQ17[14]

M_A_DQ18[14]

M_A_DQ19[14]

M_A_DQ20[14]

M_A_DQ21[14]

M_A_DQ22[14]

M_A_DQ23[14]

M_A_DQ24[14]

M_A_DQ25[14]

M_A_DQ26[14]

M_A_DQ27[14]

M_A_DQ28[14]

M_A_DQ29[14]

M_A_DQ30[14]

M_A_DQ31[14]

M_B_DQ16[15]

M_B_DQ17[15]

M_B_DQ18[15]

M_B_DQ19[15]

M_B_DQ20[15]

M_B_DQ21[15]

M_B_DQ22[15]

M_B_DQ23[15]

M_B_DQ24[15]

M_B_DQ25[15]

M_B_DQ26[15]

M_B_DQ27[15]

M_B_DQ28[15]

M_B_DQ29[15]

M_B_DQ30[15]

M_B_DQ31[15]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_B_DQS#0

M_B_DQS#1

M_A_DQS#2

M_A_DQS#3

M_B_DQS#2

M_B_DQS#3

M_A_DQS0

M_A_DQS1

M_B_DQS0

M_B_DQS1

M_A_DQS2

M_A_DQS3

M_B_DQS2

M_B_DQS3

+VREF_CA_CPU

+VREFDQ_SA_M3

+VREFDQ_SB_M3

M_A_CLK0# [14]

M_A_CLK0 [14]

M_A_CLK1# [14]

M_A_CLK1 [14]

M_A_CKE0 [14]

M_A_CKE1 [14]

M_A_CS#0 [14]

M_A_CS#1 [14]

TP46

M_A_RAS# [14]

M_A_WE# [14]

M_A_CAS# [14]

M_A_BS#0 [14]

M_A_BS#1 [14]

M_A_BS#2 [14]

M_A_A[15:0] [14]

M_A_DQS#0 [14]

M_A_DQS#1 [14]

M_B_DQS#0 [15]

M_B_DQS#1 [15]

M_A_DQS#2 [14]

M_A_DQS#3 [14]

M_B_DQS#2 [15]

M_B_DQS#3 [15]

M_A_DQS0 [14]

M_A_DQS1 [14]

M_B_DQS0 [15]

M_B_DQS1 [15]

M_A_DQS2 [14]

M_A_DQS3 [14]

M_B_DQS2 [15]

M_B_DQS3 [15]

U28D

AY31

M_A_DQ32[14]

M_A_DQ33[14]

M_A_DQ34[14]

M_A_DQ35[14]

M_A_DQ36[14]

M_A_DQ37[14]

M_A_DQ38[14]

M_A_DQ39[14]

M_A_DQ40[14]

M_A_DQ41[14]

M_A_DQ42[14]

M_A_DQ43[14]

M_A_DQ44[14]

M_A_DQ45[14]

M_A_DQ46[14]

M_A_DQ47[14]

M_B_DQ32[15]

M_B_DQ33[15]

M_B_DQ34[15]

M_B_DQ35[15]

M_B_DQ36[15]

M_B_DQ37[15]

M_B_DQ38[15]

M_B_DQ39[15]

M_B_DQ40[15]

M_B_DQ41[15]

M_B_DQ42[15]

M_B_DQ43[15]

M_B_DQ44[15]

M_B_DQ45[15]

M_B_DQ46[15]

M_B_DQ47[15]

M_A_DQ48[14]

M_A_DQ49[14]

M_A_DQ50[14]

M_A_DQ51[14]

M_A_DQ52[14]

M_A_DQ53[14]

M_A_DQ54[14]

M_A_DQ55[14]

M_A_DQ56[14]

M_A_DQ57[14]

M_A_DQ58[14]

M_A_DQ59[14]

M_A_DQ60[14]

M_A_DQ61[14]

M_A_DQ62[14]

M_A_DQ63[14]

M_B_DQ48[15]

M_B_DQ49[15]

M_B_DQ50[15]

M_B_DQ51[15]

M_B_DQ52[15]

M_B_DQ53[15]

M_B_DQ54[15]

M_B_DQ55[15]

M_B_DQ56[15]

M_B_DQ57[15]

M_B_DQ58[15]

M_B_DQ59[15]

M_B_DQ60[15]

M_B_DQ61[15]

M_B_DQ62[15]

M_B_DQ63[15]

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_ODT0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_A_DQS#4

M_A_DQS#5

M_B_DQS#4

M_B_DQS#5

M_A_DQS#6

M_A_DQS#7

M_B_DQS#6

M_B_DQS#7

M_A_DQS4

M_A_DQS5

M_B_DQS4

M_B_DQS5

M_A_DQS6

M_A_DQS7

M_B_DQS6

M_B_DQS7

03

M_B_CLK0# [15]

M_B_CLK0 [15]

M_B_CLK1# [15]

M_B_CLK1 [15]

M_B_CKE0 [15]

M_B_CKE1 [15]

M_B_CS#0 [15]

M_B_CS#1 [15]

TP45

M_B_RAS# [15]

M_B_WE# [15]

M_B_CAS# [15]

M_B_BS#0 [15]

M_B_BS#1 [15]

M_B_BS#2 [15]

M_B_A[15:0] [15]

M_A_DQS#4 [14]

M_A_DQS#5 [14]

M_B_DQS#4 [15]

M_B_DQS#5 [15]

M_A_DQS#6 [14]

M_A_DQS#7 [14]

M_B_DQS#6 [15]

M_B_DQS#7 [15]

M_A_DQS4 [14]

M_A_DQS5 [14]

M_B_DQS4 [15]

M_B_DQS5 [15]

M_A_DQS6 [14]

M_A_DQS7 [14]

M_B_DQS6 [15]

M_B_DQS7 [15]

B B

+VREF_CA_CPU

+VREFDQ_SA_M3

+VREFDQ_SB_M3

3 OF 19

+VREF_CA_CPU [14]

+VREFDQ_SA_M3 [14]

+VREFDQ_SB_M3 [15]

4 OF 19

Power tracking

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

5

4

3

2

Wednesday, September 03, 2014

PROJECT :

Haswell 2/5 (DDR3 I/F)

Haswell 2/5 (DDR3 I/F)

Haswell 2/5 (DDR3 I/F)

ZQX

ZQX

ZQX

1B

1B

3 43

3 43

1

3 43

1B

5

4

3

2

1

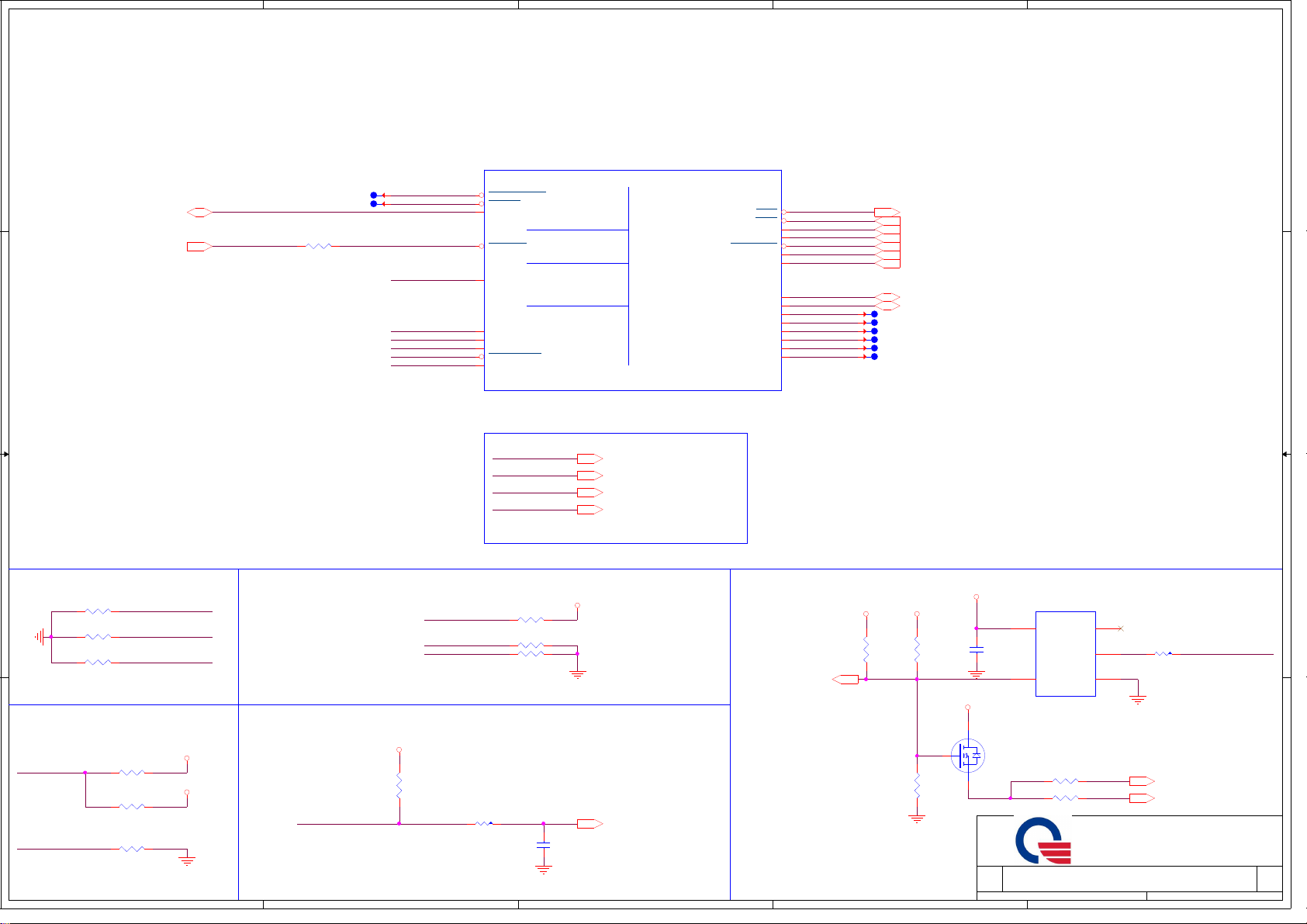

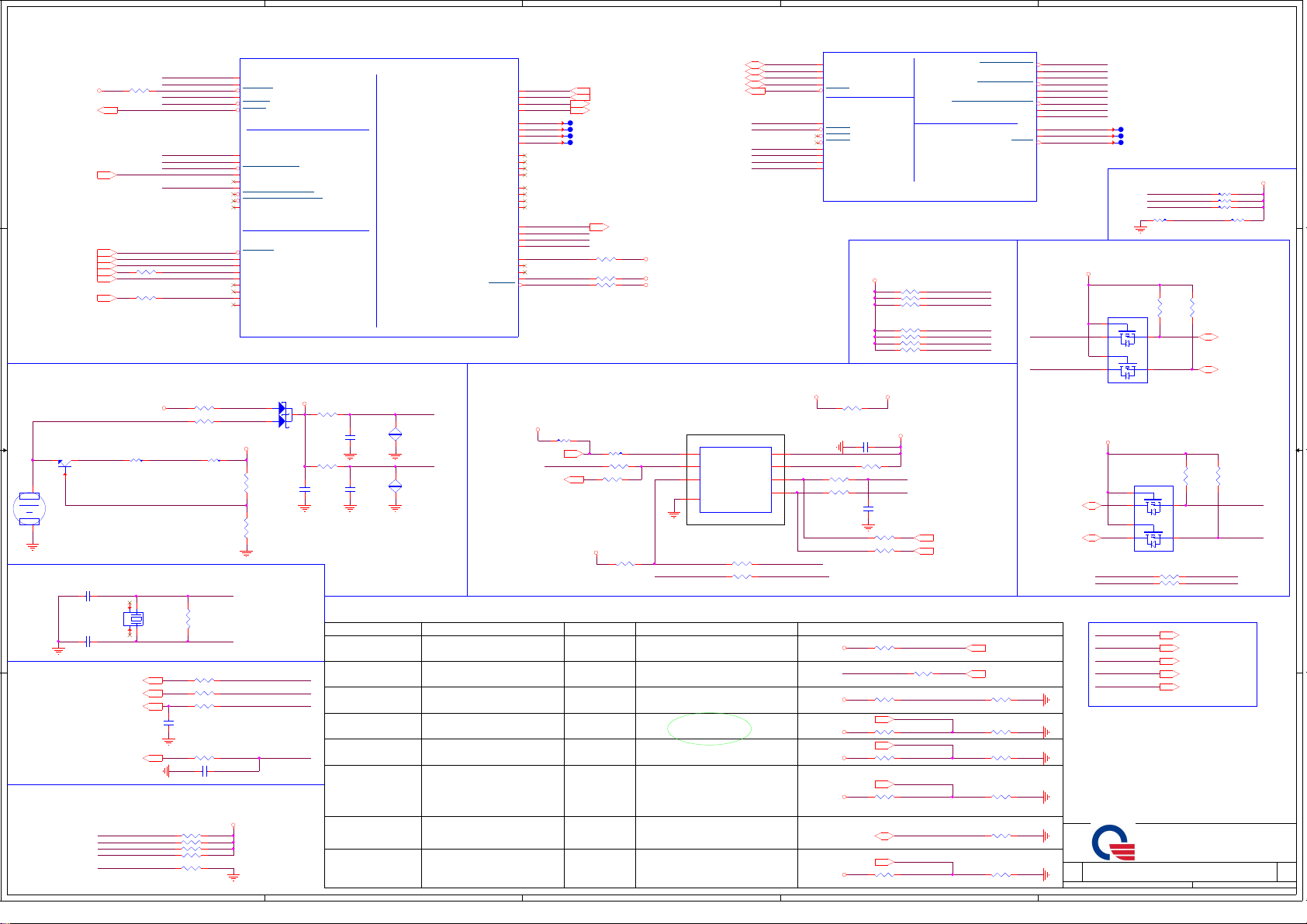

04

H_PECI (50ohm)

Route on microstrip only

D D

C C

Spacing >18 mils

Trace Length: 0.4~6.125 iches

H_PWRGOOD (50ohm)

Trace Length: 1~11.25 inches

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

H_PECI[29] XDP_PRDY# [13]

H_PROCHOT#[29,30,34]

TP116

TP49

R569 56_4

SM_RCOMP[0:2]

Trace length < 500 mils

Trace width = 12~15 mils

Trace spacing = 20 mils

PROC_DETECT

CATERR#

H_PECI

H_PROCHOT#_RH_PROCHOT#

H_PWRGOOD_R

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

DDR_PG_CTRL

Haswell ULT (SIDEBAND)

HSW_ULT_DDR3L

MISC

THERMAL

PWR

DDR3L

DSW

JTAG

2 OF 19

+1.05V_VCCST [5,10]

+1.35V_SUS [5,14,15,32]

+VCCIO_OUT [5]

+5V_S5 [8,27,31,32,34,36]

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

U28B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

+1.05V_VCCST

+1.35V_SUS

+VCCIO_OUT

+5V_S5

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

XDP_PRDY#

K62

XDP_PREQ#

E60

XDP_TCK0

E61

XDP_TMS_CPU

E59

XDP_TRST#

F63

XDP_TDI_CPU

F62

XDP_TDO_CPU

J60

XDP_BPM#0

H60

XDP_BPM#1

H61

XDP_BPM#2

H62

XDP_BPM#3

K59

XDP_BPM#4

H63

XDP_BPM#5

K60

XDP_BPM#6

J61

XDP_BPM#7CPU_DRAMRST#

XDP_PREQ# [13]

XDP_TCK0 [8,13]

XDP_TMS_CPU [13]

XDP_TRST# [8,13]

XDP_TDI_CPU [13]

XDP_TDO_CPU [13]

XDP_BPM#0 [13]

XDP_BPM#1 [13]

TP114

TP113

TP55

TP117

TP58

TP56

TCK,TMS

Trace Length < 9000mils

BPM#[0:7]

Trace Length 1~6 inches

Length match < 300 mils

Power tracking

B B

DRAM COMP

R249 200/F_4 U33

R250 120/F_4

R248 100/F_4

PU/PD of CPU

H_PROCHOT#

A A

H_PWRGOOD_R

R579 *62_4

R578 62_4

R565 10K_4

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

5

+VCCIO_OUT

+1.05V_VCCST

DRAMRST

CPU DRAM

CPU_DRAMRST#

+1.35V_SUS

12

4

XDP_TDO_CPU

XDP_TCK0

XDP_TRST#

R220

470_4

R568 51_4

R269 51_4

R262 *51_4

R217 *short_4

+1.05V_VCCST

12

C154

*0.1u/10V_4

DDR3_DRAMRST# [14,15]

3

DDR3L ODT GENERATIONXDP PU/PD

+3VSUS

12

R645

*220K/F_4

DDR_VTTT_PG_CTRL[32]

2

+5V_S5

12

R573

220K/F_4

+1.35V_SUS

2

R651

*2M/F_4

+1.35V_SUS

5

12

C545

0.1u/10V_4

3

Q41

2N7002K

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

VCC

4

Y

74AUP1G07GW

R544 66.5/F_4

R542 66.5/F_4

Haswell 1/5 (PEG/DMI/FDI)

Haswell 1/5 (PEG/DMI/FDI)

Haswell 1/5 (PEG/DMI/FDI)

Wednesday, September 03, 2014

Wednesday, September 03, 2014

Wednesday, September 03, 2014

1

NC

2

3

R572 *short_4

M_B_ODT0_DIMM [15]

M_B_ODT1_DIMM [15]

ZQX

ZQX

ZQX

4 43

4 43

4 43

1

A

GND

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

DDR_PG_CTRL

1B

1B

1B

5

4

3

2

1

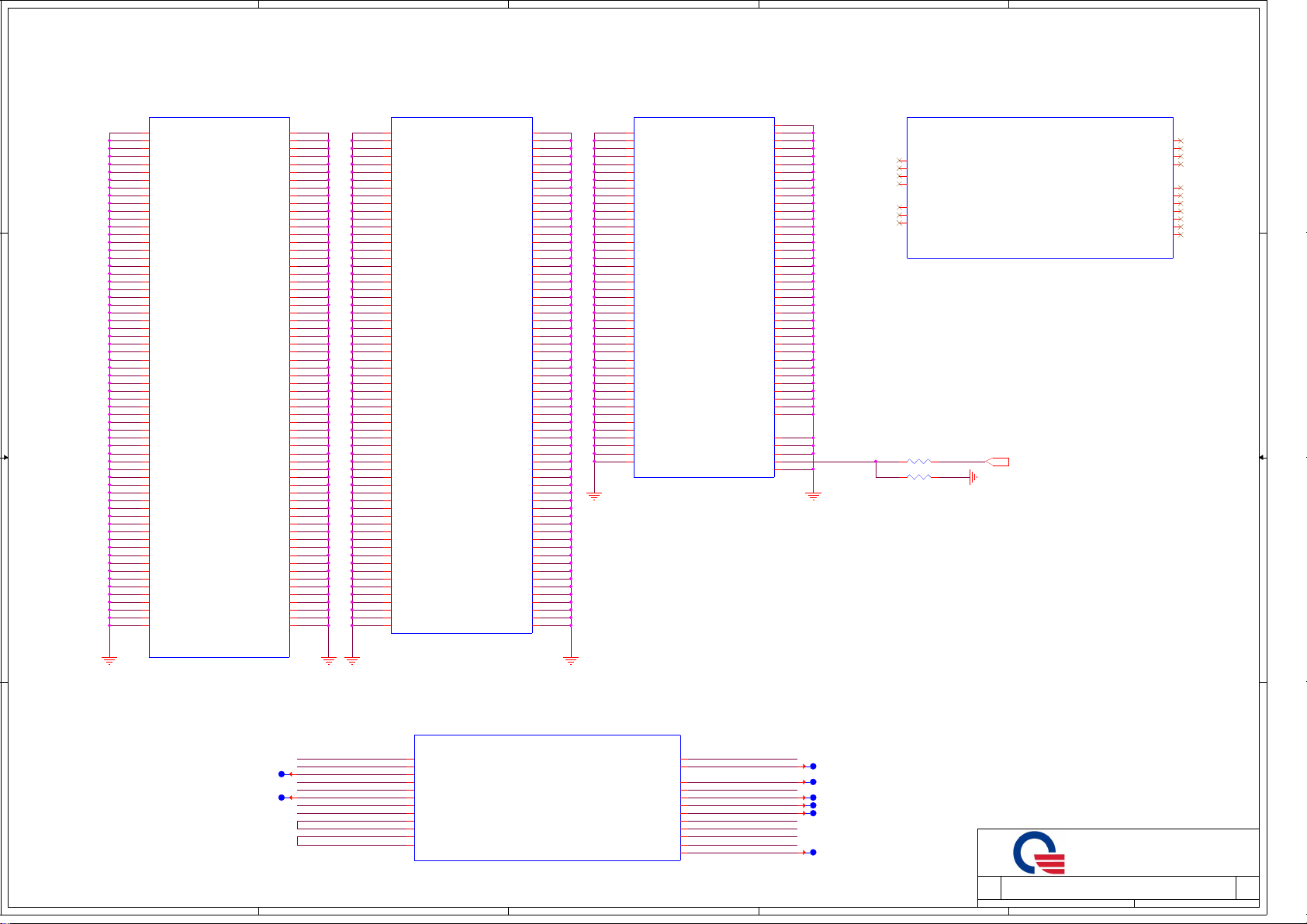

VDDQ Output Decoupling Recommendations

C217

10u/6.3V_6

TP61

TP68

TP47

TP44

TP48

TP64

TP51

TP52

TP50

TP62

TP70

TP69

TP59

TP66

TP65

TP60

TP53

TP63

TP67

+3V

+1.05V

+1.35V_SUS

+1.05V_VCCST

+VCCIN

Power tracking

TP57

TP54

ULT_RVSD_63

ULT_RVSD_64

VCC_SENSE_R

ULT_RVSD_65

ULT_RVSD_66

ULT_RVSD_67

ULT_RVSD_68

H_CPU_SVIDART#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

VCCST_PWRGD

VRON_CPU

IMVP_PWRGD

ULT_RVSD_69

ULT_RVSD_70

ULT_RVSD_71

ULT_RVSD_72

ULT_RVSD_73

ULT_RVSD_74

ULT_RVSD_75

ULT_RVSD_76

ULT_RVSD_77

ULT_RVSD_78

ULT_RVSD_79

ULT_RVSD_80

ULT_RVSD_81

+1.05V_VCCST

+VCCIN

ULT_RVSD_61

ULT_RVSD_62

PWR_DEBUG_R

+3V [2,7,8,9,10,11,13,14,15,16,17,18,21,22,23,24,25,26,27,28,29,31,32,33,34,35,36]

+1.05V [11,13,30,33,34,35]

+1.35V_SUS [4,14,15,32]

+1.05V_VCCST [4,10]

+VCCIN [34]

Haswell ULT (POWER)

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

L59

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

J58

U28L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

+

C521

*330u_2.5V_3528

C236

22u/6.3V_8

C238

22u/6.3V_8

C282

22u/6.3V_8

C237

22u/6.3V_8

C242

*22u/6.3V_8

VCC Output Decoupling Recommendations

470uFx4 7343

22uFx8

22uFx11

10uFx11

C257

22u/6.3V_8

C254

22u/6.3V_8

C260

22u/6.3V_8

C250

22u/6.3V_8

C247

*22u/6.3V_8

C269

22u/6.3V_8

C252

22u/6.3V_8

C262

22u/6.3V_8

C245

22u/6.3V_8

C248

*22u/6.3V_8

TOP socket side

4 on TOP, 4 on BOT near socket edge

0805

0805

TOP, inside socket cavity

0805

BOT, inside socket cavity

C285

22u/6.3V_8

C274

22u/6.3V_8

C264

22u/6.3V_8

C271

22u/6.3V_8

C243

*22u/6.3V_8

SVID

+VCCIO_OUT

H_CPU_SVIDDAT

Place PU resistor

close to CPU

Place PU resistor

close to CPU

H_CPU_SVIDART#

+VCCIN 32A

C267

22u/6.3V_8

C235

22u/6.3V_8

C265

22u/6.3V_8

C253

22u/6.3V_8

C266

*22u/6.3V_8

R260

*130/F_4

+VCCIN

C255

22u/6.3V_8C220

C523

22u/6.3V_8

C259

22u/6.3V_8

C256

22u/6.3V_8

C268

*22u/6.3V_8

+1.05V_VCCST

R259

130/F_4

R258 *short_4

R263 43_4

05

+VCCIO_OUT+1.05V

R555 *0_8

C528

*4.7u/6.3V_6

Layout note: need routing together

and ALERT need between CLK and DATA.

VR_SVID_DATA [34]

R265

75_4

+VCCIO_OUT

R266

*75_4

VR_SVID_ALERT# [34]

+1.05V_VCCST

330uFx2 7343

22uFx11

10uFx10

+1.35V_SUS

D D

R231 0_1206

R239 0_1206

BOT socket side

5 onTOP, 6 on BOT inside socket cavity

0805

5 onTOP, 5 on BOT inside socket cavity

0805

+1.35V_CPU 1.4A

+1.35V_CPU

C219

10u/6.3V_6

C215

2.2u/6.3V_6

R566 100/F_4

R582 *short_4

300mA

300mA

VCCST_PWRGD[13]

R277 *short_4

R570 150_6

C240

*4.7u/6.3V_6

C278

2.2u/6.3V_6

VRON_CPU[34]

IMVP_PWRGD[10,34]

C276

10u/6.3V_6

C218

2.2u/6.3V_6

+VCCIO_OUT

+VCCIOA_OUT

+VCCIN

C494

2.2u/6.3V_6

+VCCIN

VCC_SENSE[34]

PWR_DEBUG[13]

+1.05V_VCCST

R564 *10K_4

R580 10K_4

+1.05V_VCCST+1.05V

C277

10u/6.3V_6

C216

10u/6.3V_6

+

C470

*470u/2V_7343

C C

B B

10u/6.3V_6

+1.05V_VCCST

VRON_CPU IMVP_PWRGD

R235 *short_8

+3V

HWPG_1.05V for DDR=1.5V

+1.05V

A A

R556

*4.7K_4

C535

*1000p/50V_4

2

Q38

1 3

*MMBT3904-7-F

5

+3V

R558

*4.7K_4

C534

*1000p/50V_4

2

10/30 reserve

DDR=1.5V ,This block POP

R559

*4.7K_4

R557

*100K/F_4

Q40

1 3

*DTC144EU

HWPG_1.05V [29]

4

VCCST PWRGD

+1.05V_VCCST

10K_4

VCCST_PWRGD

C558

*0.1u/10V_4

R588 *short_4

+3V_S5

C573

0.1u/10V_4

VCCST_PWRGD_R

3

U37

5

VCC

4

Y

74AUP1G07GW

NC

GND

1

2

A

3

VCCST_PWRGD_EN

H_CPU_SVIDCLK

R612 *0_4

R613 *0_4R587

R604 *short_4

2

R268 *short_4

HWPG_1.05V_S5 [13,29,33]

APWORK [7,29]

PCH_PW ROK [7,29]

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

VR_SVID_CLK [34]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Haswell 4/5 (POWER)

Haswell 4/5 (POWER)

Haswell 4/5 (POWER)

ZQX

ZQX

ZQX

1

5 43

5 43

5 43

1B

1B

1B

5

4

3

2

1

Haswell ULT (CFG,RSVD)

U28S

D D

NOA_STBN_0[13]

NOA_STBN_1[13]

NOA_STBP_0[13]

NOA_STBP_1[13]

C C

R254 49.9/F_4

CFG0[13]

CFG1[13]

CFG2[13]

CFG3[13]

CFG4[8,13]

CFG5[13]

CFG6[13]

CFG7[13]

CFG8[13]

CFG9[13]

CFG10[13]

CFG11[13]

CFG12[13]

CFG13[13]

CFG14[13]

CFG15[13]

TP103

R541 8.2K_4

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

CFG_RCOMP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

J20

H18

B12

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

HSW_ULT_DDR3L

RESERVED

19 OF 19

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

PROC_OPI_RCOMP

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

OPI_COMP1

R224 49.9/F_4

06

Processor Strapping

1 0

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE SELECTION

(DEFAULT) NORMAL OPERATION; NO STALL

(DEFAULT) NORMAL OPERATION

STALL

PCH-LESS MODE

CFG0

CFG1

R270 *1K_4

R264 *1K_4

B B

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

CFG 8

ALLOW THE USE OF NOA ON LOCKED UNITS

CFG9

NO SVID PROTOCOL CAPABLE VR

CONNECTED

CFG10

SAFE MODE BOOT

A A

5

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED

TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE, NOA

WILL BE DISABLED IN LOCKED UNITS AND

ENABLED IN UN-LOCKED UNITS

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

4

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS

CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF THE UNIT

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

3

CFG3

CFG8

CFG9

CFG10

R561 *1K_4

R577 *1K_4

R560 *1K_4

R308 *1K_4

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

PROJECT :

Haswell 5/5 (CFG/GND)

Haswell 5/5 (CFG/GND)

Haswell 5/5 (CFG/GND)

ZQX

ZQX

ZQX

6 43

6 43

6 43

1

1B

1B

1B

5

4

3

2

1

Haswell ULT PCH (PM)

PCH_SUSACK#[29]

SYS_RESET#[13]

D D

SYS_PWROK

EC_PWROK

PCH_SUSPWARN#[29]

PCH_SLP_S0#[13]

RSMRST#[29]

DNBSWON#[29]

ACPRESENT[30]

PCH_SUSPWRACK

R602 *short_4

R598 *0_4

R608 *0_4

R467 *0_4

R468 *0_4

C571 *1u/6.3V_4

R601 *0_4

R605 *0_4

R511 *short_4

R445 *0_4

R128 *short_4

R139 *short_4

TP38

SUSACK#_R

SYS_RESET#

SYS_PWROK_R

EC_PWROK_R

APWROK_R

PCI_PLTRST#

PCH_RSMRST#

PCH_SUSPWRACK

PCH_PWRBTN#

PCH_ACPRESENT

PCH_BATLOW#

PCH_SLP_S0#

PCH_SLP_WLAN#

U28H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

AW6

AV4

AL7

AJ8

AN4

AF3

AM5

+3V_S5

PLTRST

RSMRST

SUSWARN/SUSPWRDNACK/GPIO30

PWRBTN

ACPRESENT/GPIO31

BATLOW/GPIO72

SLP_S0

SLP_WLAN/GPIO29

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

+3V

+3V_S5

+3V_S5

DSW

DSW

DSW

DSW

+3V_S5

DSW

+3V_S5

8 OF 19

DSWVRMEN

DPWROK

DSW

CLKRUN/GPIO32

SUS_STAT/GPIO61

DSW

DSW

DSW

DSW

DSW

WAKE

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

DSWVREN

AV5

DPWROK_R

AJ5

PCIE_LAN_WAKE#

V5

CLKRUN#

AG4

LPCPD#

AE6

PCH_SUSCLK

AP5

PCH_SLP_S5#

AJ6

SUSC#

AT4

SUSB#

AL5

PCH_SLP_A#

AP4

PCH_SLP_SUS#

AJ7

PCH_SLP_LAN#

Deep Sx

R479 *0_4

TP20

TP31

DSWVREN [8]

DPWROK [29]

PCIE_LAN_WAKE# [24,26]

CLKRUN# [21,29]

LPCPD# [21]

PCH_SLP_S5# [13]

SUSC# [13,29]

SUSB# [13,29]

PCH_SLP_A# [13]

PCH_SLP_SUS# [29]

07

C C

Power Sequence

PCH_PWROK[5,29]

R519

100K_4

R518 *short_4

EC_PWROK SYS_PWROK_R

R606 *0_4

EC_PWROK_R

DPWROK_RRSMRST#

APWORK[5,29]

R614 *short_4

Speed up 250ms to boot up

for EC power on 250 ms

APWROK_R

R615

10K_4R482 *short_4

Non Deep Sx

PCH PM PU/PD

+3V

CLKRUN#

SYS_RESET#

B B

A A

PCH_RSMRST#

SYS_PWROK

DPWROK_R

PCH_SUSPWRACK

PCH_ACPRESENT

PCH_BATLOW#

PCIE_LAN_WAKE#

PCH_PWRBTN#

R160 8.2K_4

R499 10K_4

R510 10K_4

R596 *10K_4

R478 100K/F_4

+3V_S5

R453 *10K_4

+3V_S5

R165 10K_4

R505 8.2K_4

R193 1K_4

R137 *10K_4

+3VPCU

R134 *10K_4

R471 *8.2K_4

R169 *1K_4

R145 *10K_4

5

DSW PU

PLTRST# Buffer Deep Sx Circuit

+3V

PCI_PLTRST#

2

1

C127 0.1u/10V_4

4

U9

3 5

TC7SH08FU

R94

100K_4

PLTRST# [13,16,21,24,26,29]

+3V_S5 +3VCC_S5

C157

*0.33u/10V_6

SYSPWOK

+3V_S5

C561 *0.1u/10V_4

2

SYS_PWROK[13]

4

SYS_PWROK

4

U38

TC7SH08FU

R607 *0_4

3 5

EC_PWROK

1

3

EC_PWROK [29]

IMVP_PWRGD_3V [10]

R616

10K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

PCH_SLP_SUS#

Wednesday, September 03, 2014

Wednesday, September 03, 2014

Wednesday, September 03, 2014

Non Deep Sx

R204 *Short_6

2

3

1

Q20

*AO3413

R136

*0_6

Q15

*2N7002K

ZQX

ZQX

ZQX

3

1

1

R151

*100K_4

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 1/6 (DMI/FDI/VGA)

LPT 1/6 (DMI/FDI/VGA)

LPT 1/6 (DMI/FDI/VGA)

7 43

7 43

7 43

1B

1B

1B

5

[2,5,7,9,10,11,13,14,15,16,17,18,21,22,23,24,25,26,27,28,29,31,32,33,34,35,36]

Haswell ULT PCH (RTC/HDA/SATA/SPI)

U28E

RTC_X1

RTC_X2

+3VPCU

20MIL

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BCLK_R

HDA_SYNC_R

HDA_RST#_R

HDA_SDO_R

XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

+3V_RTC_[0:2]

Trace width = 20 mils

R481 1M_4

+3V_RTC

D D

C C

B B

RTC_RST#[13]

PCH_AZ_CODEC_SDIN0[22]

XDP_TRST#[4,13]

XDP_TCK1[13]

XDP_TDI[13]

XDP_TDO[13]

XDP_TMS[13]

XDP_TCK0[4,13]

RTC Circuitry

(RTC)

VCCRTC_2

1 3

VCCRTC_3 VCCRTC_4

Q39

MMBT3904

2

12

BT6

R303 0_4

R571 0_4

R563 4.7K_4

RTC Clock 32.768KHz (RTC)

C437 18p/50V_4

C438 18p/50V_4

HDA

A A

PCH JTAG

JTAG_TCK,JTAG_TMS

Trace Length < 9000mils

PCH_AZ_CODEC_RST#[22]

PCH_AZ_CODEC_SDOUT[22]

PCH_AZ_CODEC_BITCLK[22]

PCH_AZ_CODEC_SYNC[22]

23

XDP_TMS

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

XDP_TCK1

Y7

32.768KHZ

4 1

MP remove(Intel)

R272 51_4

R273 51_4

R271 51_4

R562 *1K_4

R276 *51_4

5

C448

*10p/50V_4

AW5

AW8

AV11

AY10

AU12

AU11

AW10

AV10

AU62

AE62

AD61

AE61

AD62

AL11

AE63

R516 *Short_6

R509 1K_4

R574 4.7K_4

RTC_X1

R508

10M_4

RTC_X2

R530 33_4

R536 33_4

R529 33_4

R532 33_4

C450 *10p/50V_4

+1.05V_S5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

HDA_BCLK/I2S0_SCLK

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_SDO/I2S0_TXD

HDA_DOCK_EN/I2S1_TXD

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

RSVD

AC4

RSVD

JTAGX

AV2

RSVD

+3V_RTC_2

+3V_RTC_1

+5V_S5

R576

68.1K/F_4

R575

150K/F_4

HDA_RST#_R

HDA_SDO_R

HDA_BCLK_R

HDA_SYNC_R

RTC

AUDIO SATA

JTAG

+3V_RTC

Trace width = 30 mils

+3V_RTC

D29

R517

20K/F_4

BAT54C

R524

20K/F_4

C436

1u/6.3V_4

ULT Strapping Table

Pin Name Strap description

GPIO81(SPKR)

HDA_SDO

INTVRMEN

GPIO66

GPIO86

GPIO15

CFG4

DSWVREN

HSW_ULT_DDR3L

5 OF 19

C152

1u/6.3V_4

C161

1u/6.3V_4

4

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

+3V

SATA0GP/GPIO34

+3V

SATA1GP/GPIO35

+3V

SATA2GP/GPIO36

+3V

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

RTC_RST#

12

J6

*JUMP

SRTC_RST#

12

J7

*JUMP

No reboot on TCO Timer

expiration

Flash Descriptor Security

Override / Intel ME Debug Mode

SPI_CS0#_UR_ME[29]

PCH_SPI_SO_EC[29]

Integrated 1.05V VRM enable ALWAYS

Top-Block Swap override

Boot BIOS Strap Bit

TLS(Transport layer security)

DP presence strap

Deep Sx well on die VR enable

4

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

VGPU_EN

U1

SYS_COM_REQ

V6

GPIO36

AC1

GPIO37

A12

SATA_IREF

L11

K10

C12

SATA_RCOMP

U3

SATA_LED#

SATA_RCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

PCH Quad SPI

ROM(8M)

+3V_PCH_ME

R416 10K_4

PCH_SPI_SO

reserve for SPI fast read

SATA_RXN0 [21]

SATA_RXP0 [21]

SATA_TXN0 [21]

SATA_TXP0 [21]

TP35

TP36

TP41

TP40

VGPU_EN [36]

R539 0_4

R538 3.01K/F_4

R455 10K_4

R415 *short_4

R430 15_4

R429 15_4

+3V_PCH_ME

R419 *1K_4

Sampled

PWROK

PWROK

3

Haswell ULT PCH(LPC,SPI,SMBUS,C-LINK,THERMAL)

U28G

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

8

7

6

5

PCH_SPI_IO2

SPI_HOLD_IO3_ME

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

R421 *Short_6

SPI_HOLD_IO3_ME

R425 15_4

R427 15_4

PCH_SPI_CLK_R

PCH_SPI_SI_R

+3V_RTC

+3V_S5

+3V_RTC

LPC_LAD0[21,26,29]

LPC_LAD1[21,26,29]

LPC_LAD2[21,26,29]

LPC_LAD3[21,26,29]

LPC_LFRAME#[21,26,29]

HDD

trace width 12~15mil

+V1.05S_ASATA3PLL

trace width 12~15mil

+V1.05S_ASATA3PLL

+3V

(Default for WIN8)

U24

PCH_SPI_CS0#

PCH_SPI_SO_R

0 = Default enable (iPD 20K)

1 =Disable No-Reboot mode

0 = Default can program ME (iPD 20K)

1 =can't program ME

1=Should be always pull-up

0 = Default disable (iPD 20K)

1 = Enable TBS function

0 = Default SPI (iPD 20K)

1 =LPC

0 = Default enable w/o

confidentiality(iPD 20K)

1 =Default enable with

confidentiality

0 = Enable an external display

port is connected to the eDP

1 =disable

1=Should be always pull-up

1

CS#

2

IO1/DO

3

IO2/WP#

4

GND

W25Q64FVSSIQ -- 8MB

VCC

IO3/HOLD#

CLK

IO0/DI

change PN 11/15

SPI_WP_IO2_ME

PCH_SPI_IO3

R423 15_4

R422 15_4 R98 0_4

Configuration note

3

2

HSW_ULT_DDR3L

+3V_S5

SMBUS

+3V_S5

+3V_S5

+3V_S5

C-LINKSPI

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

SML1ALERT/PCHHOT/GPIO73

LPC

SMBus

+3V_S5

R501 10K_4

R485 10K_4

R470 10K_4

R123 2.2K_4

R124 2.2K_4

R500 2.2K_4

R503 2.2K_4

+3V_PCH_ME+3V_S5

+3V_PCH_ME

C420 0.1u/10V_4

R418 *1K_4

PCH_SPI_CLK

PCH_SPI_SI

C430

*22p/50V_4

reserve for SPI fast read

R426 15_4

R428 15_4

3.3K is original and

for no support fast

read function

R448 *1K_4

+3V

HDA_SDO_R

GPIO66[10]

+3V

GPIO86[10]

+3V

GPIO15[10]

DSWVREN[7]

R535 0_4

R526 330K_4 R525 *330K_4

R520 *1K_4

R202 *1K_4

R161 8.2K_4

CFG4[6,13]

R513 330K_4

PCH_INTVRMEN

GPIO66

GPIO86

GPIO15

CFG4

DSWVREN

2

SMB0ALERT#

SMB1ALERT#

SMBALERT#

SMB_PCH_CLK

SMB_PCH_DAT

SMBDATA0

SMBCLK0

PCH_SPI_CLK_EC [29]

PCH_SPI_SI_EC [29]

SPKR

SMBALERT/GPIO11

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_DATA

7 OF 19

SPKR [10,22]

ME_WR# [29]

R527 *1K_4

R200 *1K_4

R186 *1K_4

R255 1K_4

R514 *330K_4

1

SYS_COM_REQ

GPIO36

GPIO37

08

R495 10K_4

R185 10K_4

R498 10K_4

VGPU_EN

SMBCLK

CL_CLK

CL_RST

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

SMBALERT#

SMB_PCH_CLK

SMB_PCH_DAT

SMB0ALERT#

SMBCLK0

SMBDATA0

SMB1ALERT#

SMB_ME1_CLK

SMB_ME1_DAT

CL_CLKPCH_SPI_CS0#

CL_DAT

CL_RST#

TP98

TP96

TP97

R465 *10K_4

SMBus(PCH)

+3V

R104

4.7K_4

R117

4.7K_4

SMB_PCH_DAT

SMB_PCH_CLK

Q17

5

2

6

2N7002DW

43

1

PCH_XDP_WLAN/S5 DDR_TP/S0

SMBus(EC)

2ND_MBCLK[19,29]

2ND_MBDATA[19,29]

EC/S5 PCH/S5

+3V_S5

Q14

5

2

6

*2N7002DW

2ND_MBCLK

2ND_MBDATA

+3VPCU

+3V_S5

+3V

+1.05V_S5

+V1.05S_ASATA3PLL

Power tracking

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

LPT 2/6 (SATA/HDA/SPI)

LPT 2/6 (SATA/HDA/SPI)

LPT 2/6 (SATA/HDA/SPI)

Wednesday, September 03, 2014

Wednesday, September 03, 2014

Wednesday, September 03, 2014

R97

*2.2K_4

43

1

SMB_ME1_CLK

SMB_ME1_DAT

R92 0_4

+3VPCU [7,11,13,21,22,23,28,29,30,31,35,36,37]

+3V_S5 [5,7,9,10,11,13,21,24,27,28,29,31,34,36]

+3V

+1.05V_S5 [11,13,33,37]

+V1.05S_ASATA3PLL [11]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZQX

ZQX

ZQX

1

+3V

R447 10K_4

CLK_SDATA [13,14,15,26]

CLK_SCLK [13,14,15,26]

R91

*2.2K_4

SMB_ME1_CLK

SMB_ME1_DAT

8 43

8 43

8 43

1B

1B

1B

5

4

3

2

1

Haswell ULT PCH (PCIE,USB3.0,USB2.0)

PCIE USB

+3V_S5

+3V_S5

+3V_S5

+3V_S5

HSW_ULT_DDR3L

11 OF 19

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

DSW

USB2N0

DSW

USB2P0

DSW

USB2N1

DSW

USB2P1

DSW

USB2N2

DSW

USB2P2

DSW

USB2N3

DSW

USB2P3

DSW

USB2N4

DSW

USB2P4

DSW

USB2N5

DSW

USB2P5

DSW

USB2N6

DSW

USB2P6

DSW

USB2N7

DSW

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

RSVD

RSVD

AN8

USBP1- [27]

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

MB USB3.0

USBP1+ [27]

USBP2- [27]

DB USB2.0

USBP2+ [27]

TP37

TP39

USBP3- [27]

DB USB2.0

USBP3+ [27]

USBP4- [26]

BT

USBP4+ [26]

USBP5- [23]

Touch screen

USBP5+ [23]

USBP6- [23]

CCD

USBP6+ [23]

USBP7- [27]

Card reader

USBP7+ [27] PCLK_TPM [21]

USB3_RXN0 [27]

USB3_RXP0 [27]

USB3_TXN0 [27]

USB3_TXP0 [27]

R222 22.6/F_4

USB_OC0# [27]

USB_OC1# [27]

MB USB3.0

USBCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

MB U3

DB U2

WLAN LAN

VGA

CLK_PCIE_LANN[24]

CLK_PCIE_LANP[24]

CLK_PCIE_LAN_REQ#[24]

CLK_PCIE_WLANN[26]

CLK_PCIE_WLANP[26]

PCIE_CLKREQ_WLAN#[26]

CLK_PCIE_VGA#[16]

CLK_PCIE_VGA[16]

CLK_PEGA_REQ#[16]

USB Overcurrent

USB_OC3#

USB_OC1#

USB_OC0#

Swap for layou 11/14

U28K

PEG_RX#0[16]

D D

PEG x4

C C

WLAN LAN

B B

PEG_RX0[16]

PEG_TX#0[16]

PEG_TX0[16]

PEG_RX#1[16]

PEG_RX1[16]

PEG_TX#1[16]

PEG_TX1[16]

PEG_RX#2[16]

PEG_RX2[16]

PEG_TX#2[16]

PEG_TX2[16]

PEG_RX#3[16]

PEG_RX3[16]

PEG_TX#3[16]

PEG_TX3[16]

PCIE_RX3-_LAN[24]

PCIE_RX3+_LAN[24]

PCIE_TX3-_LAN[24]

PCIE_TX3+_LAN[24]

PCIE_RX4-_WLAN[26]

PCIE_RX4+_WLAN[26]

PCIE_TX4-_WLAN[26]

PCIE_TX4+_WLAN[26]

+V1.05S_AUSB3PLL

C478 EV@0.22u/10V_4

C476 EV@0.22u/10V_4

C481 EV@0.22u/10V_4

C480 EV@0.22u/10V_4

C467 EV@0.22u/10V_4

C463 EV@0.22u/10V_4

C474 EV@0.22u/10V_4

C468 EV@0.22u/10V_4

C497 0.1u/10V_4

C506 0.1u/10V_4

C491 0.1u/10V_4

C493 0.1u/10V_4

TP42

TP43

TP105

TP104

R232 3.01K/F_4

R233 *short_4

PCIE_RCOMP

PCIE_IREF

F10

PERN5_L0

E10

PERP5_L0

C23

R_PEG_TX#0

R_PEG_TX0

R_PEG_TX#1

R_PEG_TX1

R_PEG_TX#2

R_PEG_TX2

R_PEG_TX#3

R_PEG_TX3

PCIE_TX3PCIE_TX3+

PCIE_TX4PCIE_TX4+

PCIE_RXN1

PCIE_RXP1

PCIE_TXN1

PCIE_TXP1 USBCOMP

C22

F8

E8

B23

A23

H10

G10

B21

C21

E6

F6

B22

A21

G11

F11

C29

B30

F13

G13

B29

A29

G17

F17

C30

C31

F15

G15

B31

A31

E15

E13

A27

B27

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD

RSVD

PCIE_RCOMP

PCIE_IREF

Haswell ULT PCH (CLOCK)

U28F

TP108

TP106

TP92

TP22

R450 *short_4

R462 *short_4

R125 *short_4

+3V_S5

10

9

8

7 4

RP6

10K_10P8R

CLK_PCIE_N0

CLK_PCIE_P0

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PCIE_REQ5#

1

2

3

56

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ5#

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8USB_OC2#

CLK_PCIE_REQ4#

CLOCK

SIGNALS

6 OF 19

R474 10K_4

R143 10K_4

R451 10K_4

R490 10K_4

R477 10K_4

R550 10K_4

R549 10K_4

R218 10K_4

R219 10K_4

R158 10K_4

R183 *1K_4

XTAL24_IN

XTAL24_OUT

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

+3V

+3V

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

R545

1M_4

C490 12p/50V_4

2 4

1 3

C489 12p/50V_4

XTAL24_IN

XTAL24_OUT

ICLK_BIAS

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLK_PCH_PCI3

CLK_PCH_PCI4

Y8

24MHz

R546 3.01K/F_4

R228 TPM@22_4

R227 22_4

R225 22_4

C205

*18p/50V_4

CLK_PCI_LPCCLK_PCI_EC

09

+V1.05S_AXCK_LCPLL

CLK_PCI_LPC [26]

CLK_PCI_EC [29]

CLK_PCIE_XDPN [13]

CLK_PCIE_XDPP [13]

C210

*18p/50V_4

+V1.05S_AUSB3PLL

+3V_S5

+3V

+V1.05S_AXCK_LCPLL

+V1.05S_AUSB3PLL [11]

+3V_S5 [5,7,8,10,11,13,21,24,27,28,29,31,34,36]

+3V [2,5,7,8,10,11,13,14,15,16,17,18,21,22,23,24,25,26,27,28,29,31,32,33,34,35,36]

+V1.05S_AXCK_LCPLL [11]

Power tracking

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

5

4

3

2

Wednesday, September 03, 2014

PROJECT :

LPT 3/6 (PCIE/USB/CLK)

LPT 3/6 (PCIE/USB/CLK)

LPT 3/6 (PCIE/USB/CLK)

ZQX

ZQX

ZQX

9 43

9 43

1

9 43

1B

1B

1B

5

4

3

2

1

PCH GPIO PU/PD

Haswell ULT PCH (GPIO,CPU/MISC,NCTF)

High Low

GPIO8

D D

C C

DEVSLP0 for HDD

DEVSLP1 for mSATA

touch panel No Touch panel

GPIO8[23]

GPIO15[8]

DGPU_PWROK[17]

DGPU_HOLD_RST#[16]

DGPU_PWR_EN[37]

MODPHY_EN[33]

Sensor_INT[27,29]

G_sen_INT[27,29]

DEVSLP0[21]

TP93

SPKR[8,22]

R484 *short_4

TP21

TP33

TP29

TP95

TP27

TP18

TP19

TP34

TP30

TP26

DGPU_HOLD_RST#

DGPU_PWR_EN

MODPHY_EN

TP25

R138 *short_4

DEVSLP0

SPKR

BOARD_ID0

LAN_DISABLE#

GPIO15

SKU_ID0

DGPU_PWROK

GPIO24

WK_GPIO27

GPIO28

ODD_PRSNT#

GPIO56

GPIO57

GPIO58

GPIO59

GPIO44

GPIO47

DGPU_PW_CTRL#

RAM_ID0

RAM_ID3

GPIO25

GPIO45

RAM_ID1

RAM_ID2

BOARD_ID3

DEVSLP1

SKU_ID1

Board ID

+3V

R492 10K_4

R181 10K_4

B B

R178 10K_4

R534 NTPM@10K_4

R489 10K_4

BOARD_ID0

BOARD_ID1[2]

BOARD_ID1

BOARD_ID2[2]

BOARD_ID2

BOARD_ID3

BOARD_ID4[2]

BOARD_ID4

R463 *10K_4

R156 *10K_4

R154 *10K_4

R533 TPM@10K_4

R461 *10K_4

U28J

P1

BMBUSY/GPIO76

AU2

AM7

AD6

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

AT3

AH4

AM4

AG5

AG3

AM3

AM2

Y1

T3

U4

Y3

P3

Y2

P2

C4

L2

N5

V2

+3V_S5

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

+3V_S5

GPIO15

+3V

GPIO16

+3V

GPIO17

+3V_S5

GPIO24

DSW

GPIO27

+3V_S5

GPIO28

+3V_S5

GPIO26

+3V_S5

GPIO56

+3V_S5

GPIO57

+3V_S5

GPIO58

+3V_S5

GPIO59

+3V_S5

GPIO44

+3V_S5

GPIO47

+3V

GPIO48

+3V

GPIO49

+3V

GPIO50

HSIOPC/GPIO71

+3V_S5

GPIO13

+3V_S5

GPIO14

DSW

GPIO25

+3V_S5

GPIO45

+3V_S5

GPIO46

+3V_S5

GPIO9

+3V_S5

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

RAM ID

R506 SP@10K_4

R191 SP@10K_4

R502 SP@10K_4

R188 10K_4

RAM_IDVender Freq.

Hynix

Elpida 0010 AKD5JGST407 EDJ4216EFBG-GN-LF 1600MHz

MICRON 0100 MT41K256M16HA-125 1600MHzAKD5JGSTL08

Kingston 0101

0000

0001

1234

SKU ID

UMA Only

dGPU Only

Switchable

(Mux)

Optimize

(Muxless)

R497 IV@10K_4

R179 IV@10K_4

Low

BOARD_ID0

BOARD_ID1

A A

BOARD_ID2

BOARD_ID3

BOARD_ID4

Reserved

(Default)

Enable on

board memory

Default(LOW)

No DTPM

Reserved

(Default)

5

High

Reserved

Disable on

board memory

DTPM

Reserved

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

GPIO

+3V

DSW

10 OF 19

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID3

+3V

CPU/

PCH_OPI_RCOMP

MISC

+3V

GSPI0_CS/GPIO83

+3V

GSPI0_CLK/GPIO84

+3V

GSPI0_MISO/GPIO85

+3V

GSPI0_MOSI/GPIO86

+3V

GSPI1_CS/GPIO87

+3V

GSPI1_CLK/GPIO88

+3V

GSPI1_MISO/GPIO89

+3V

GSPI_MOSI/GPIO90

+3V

UART0_RXD/GPIO91

+3V

UART0_TXD/GPIO92

+3V

UART0_RTS/GPIO93

SERIAL IO

+3V

UART0_CTS/GPIO94

+3V

UART1_RXD/GPIO0

+3V

UART1_TXD/GPIO1

+3V

UART1_RST/GPIO2

+3V

UART1_CTS/GPIO3

+3V

I2C0_SDA/GPIO4

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

R472 SP@10K_4

R167 SP@10K_4

R469 SP@10K_4

R163 *10K_4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

Q PN Mfr. PN

AKD5JGETW04 H5TC4G63AFR-PRBA(A) 1600MHz

H5TC4G63MFR-PBA(M) 1600MHzHynix 0011 AKD5PGSTW03

SKU_ID0

SKU_ID1

SKU_ID1 SKU_ID0 VGA H/W

0

0

1

1

0

1

0

1

4

R466 EV@10K_4

R155 EV@10K_4

Setup

Signal

Menu

UMA

Hidden

UMA boot

GPU

Hidden

GPU boot

UMA+GPU dGPU/SG UMA boot

UMA

UMA/SG

UMA boot

THRMTRIP

RCIN/GPIO82

SERIRQ

RSVD

RSVD

+3V_S5

4

3

2

1

+3V

D60

THRMTRIP#

V4

SIO_RCIN#

T4

IRQ_SERIRQ

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

OPI_COMP2

TP_INT_PCH

GPIO84

GPIO85

GPIO86

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

SIO_EXT_SMI#

SIO_EXT_SCI#

DGPU_EVENT#

GC6_FB_EN

GPIO64

GPIO65

GPIO66

GPIO67

GPIO68

GPIO69

R223 49.9/F_4

CPU thermal trip

IMVP_PWRGD_3V

+1.05V_VCCST

THRMTRIP#

IMVP_PWRGD[5,34]

3

I2C0 connect to Sensor HUB,

I2C1 connect touchpanle and

touchpad for Acer request 11/08

R203 *short_4

R210 *short_4

20130926 chnge GPIO port

+1.05V_VCCST

3

2

R627

1K_4

Q43

FDV301N

1

R628

1K_4

2

1 3

Q42 MMBT3904-7-F

U39

NC1VCC

2

A

GND3Y

74AUP1G07GW

SIO_RCIN# [29]

IRQ_SERIRQ [21,29]

TP_INT_PCH [23]

GPIO86 [8]

SIO_EXT_SMI# [29]

SIO_EXT_SCI# [29]

DGPU_EVENT# [19]

GC6_FB_EN [17,19]

Sensor_PCH_DAT [29]

Sensor_PCH_CLK [29]

I2C1_SDA_GPIO6 [23,28]

I2C1_SCL_GPIO7 [23,28]

GPIO66 [8]

SYS_SHDN# [21,31,35]

+1.05V_VCCST

5

C579

0.1u/10V_4

4

IRQ_SERIRQ

DEVSLP0

DEVSLP1

SIO_RCIN#

SIO_EXT_SMI#

SIO_EXT_SCI#

GPIO85

GPIO87

GPIO88

GPIO89

GPIO90

GPIO91

GPIO92

GPIO93

GPIO94

GPIO64

GPIO65

TP_INT_PCH

GPIO84

Sensor_PCH_DAT

Sensor_PCH_CLK

I2C1_SDA_GPIO6

I2C1_SCL_GPIO7

GPIO67

GPIO68

GPIO69

R475 *100K_4

R493 EV@100K_4

R494 *10K_4

+3V

12

R623

10K_4

IMVP_PWRGD_3V [7]

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

2

Wednesday, September 03, 2014

DGPU_PWR_EN

DGPU_HOLD_RST#

high UMA Only

GPU power is control by PCH

low

GPIO (Discrete, SG or Optimize)

ODD_PRSNT#

GPIO8

GPIO24

GPIO28

GPIO56

GPIO57

GPIO58

GPIO59

GPIO44

GPIO47

GPIO45

G_sen_INT

LAN_DISABLE#

GPIO25

WK_GPIO27

GPIO27 : If not used then use

8.2-kΩ to 10-kΩ pull-down to GND.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 4/6 (GPIO/MISC)

LPT 4/6 (GPIO/MISC)

LPT 4/6 (GPIO/MISC)

R182 10K_4

R476 10K_4

R460 10K_4

R412 10K_4

R177 10K_4

R458 10K_4

R180 10K_4

R170 10K_4

R152 10K_4

R140 10K_4

R459 10K_4

R454 10K_4

R153 10K_4

R487 10K_4

R486 10K_4

R201 10K_4

R205 10K_4

R157 10K_4

R176 10K_4

R442 2.2K_4

R444 2.2K_4

R483 2.2K_4

R512 2.2K_4

R206 10K_4

R531 10K_4

R515 10K_4

R449 10K_4

R496 10K_4

DGPU_PW_CTRL#

DGPU_PWROK

R504 10K_4

R473 10K_4

R187 10K_4

R162 10K_4

R189 10K_4

R207 10K_4

R190 10K_4

R211 10K_4

R166 10K_4

R144 10K_4

R164 10K_4

R452 10K_4

R209 10K_4

R147 10K_4

R168 10K_4

R192 *10K_4

1

ZQX

ZQX

ZQX

10

+3V

I2C PULL HIGH

R464 IV@1K_4

+3V_S5

+3V_S5

10 43

10 43

10 43

+3V

1B

1B

1B

5

[2,5,7,8,9,10,13,14,15,16,17,18,21,22,23,24,25,26,27,28,29,31,32,33,34,35,36]

C182 *1u/6.3V_4

C190 1u/6.3V_4

C191 1u/6.3V_4

+1.05V

25mA

C232

1u/6.3V_4

R212 *short_8

Deep Sx

+3VPCU

+3V_S5

D D

R238 *0_6

+1.05V_S5

Non Deep Sx

+3V

C C

+1.05V

WW15 4/10 Intel

VCCDSW3 G3 can't

boot issue.

C181

+PCH_VCCDSW+VCCPDSW

0.47u/25V_6

+1.05V_MODPHY

R208 *0_6

+1.05V_S5

+1.05V_DCPSUS2

R171 *0_6

R194 *Short_6

R523 *short_8

C201 1u/6.3V_4

+3VCC_S5

1.741A

C176

*1u/6.3V_4

C168

10u/6.3V_6

+V1.05S_AIDLE

10mA

C172

1u/6.3V_4

+V3.3DX_1.5DX_1.8DX_AUDIO

0.114A

+3VCC_S5

C163

1u/6.3V_4

41mA

C446

22u/6.3V_8

+1.05V

63mA

PCH VCCHSIO Power

B B

4

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+V1.05S_APLLOPI

+1.05V_DCPSUS3

C202 22u/6.3V_8

+VCCPDSW

+V3.3S_VCCPCORE

+V1.05S_AXCK_DCB

+V1.05S_AXCK_LCPLL

C204 1u/6.3V_4

1.838A

AA21

W21

AH14

AH13

AC9

AA9

AH10

K19

R21

K18

M20

AE20

AE21

K9

L10

M9

N8

P9

B18

B11

Y20

J13

V8

W9

J18

A20

J17

T21

V21

3

Haswell ULT PCH (Power)

HSIO

USB3

HDA

VRM

GPIO/LPC

LPT LP POWER

HSW_ULT_DDR3L

OPI

RTC

SPI

CORE

THERMAL SENSOR

SERIAL IO

SUS OSCILLATOR

USB2

13 OF 19

U28M

VCCHSIO

VCCHSIO

VCCHSIO

VCC1_05

VCC1_05

VCCUSB3PLL

VCCSATA3PLL

RSVD

VCCAPLL

VCCAPLL

DCPSUS3

VCCHDA

DCPSUS2

VCCSUS3_3

VCCSUS3_3

VCCDSW3_3

VCC3_3

VCC3_3

VCCCLK

VCCCLK

VCCACLKPLL

VCCCLK

VCCCLK

VCCCLK

RSVD

RSVD

RSVD

VCCSUS3_3

VCCSUS3_3

VCCSUS3_3

VCCRTC

DCPRTC

VCCSPI

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

DCPSUSBYP

DCPSUSBYP

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCC3_3

VCC3_3

VCCSDIO

VCCSDIO

DCPSUS4

RSVD

VCC1_05

VCC1_05

AH11

AG10

AE7

Y8

AG14

AG13

J11

H11

H15

AE8

AF22

AG19

AG20

AE9

AF9

AG8

AD10

AD8

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

+VCCRTCEXT

+V3.3M_PSPI

+1.05V_DCPSUS1

PCH_VCC_1_1_21

+V1.05S_CORE_PCH

0.109A

R237 *0_6

C231

1u/6.3V_4

+V3.3S_VCCSDIO

+1.05V_DCPSUS4

+V1.05S_VCCUSBCORE

18mA

+PCH_VCCDSW

+V1.05M_VCCASW

2

R221 *Short_6

+V1.05M_VCCASW

+1.05V_S5

3mA

1mA

17mA

R236 *0_6

C230

1u/6.3V_4

R230 *short_8

C229

1u/6.3V_4

C193

0.1u/10V_4

C200

1u/6.3V_4

0.658A

C174

1u/6.3V_4

+V1.5S_VCCATS

+V3.3S_VCCPTS

+1.05V_S5

C203

1u/6.3V_4

C171

0.1u/10V_4

+1.05V

+1.05V

+1.05V

C170

0.1u/10V_4

R521 *Short_6

R522 *0_6

C192

0.1u/10V_4

C186

1u/6.3V_4

C195

1u/6.3V_4

R214 *short_8

C166

22u/6.3V_8

R540 *Short_6

R226 *Short_6

C208

1u/6.3V_4

R175 *Short_6

C160

1u/6.3V_4

+3VCC_S5

+3V_RTC

C447

1u/6.3V_4

R215 *short_8

C185

10u/6.3V_6

+1.05V

+3V_S5

+1.5V

+3V

+1.05V

+3V_RTC

+3VCC_S5

+1.05V_S5

+V1.05S_AUSB3PLL

+V1.05S_ASATA3PLL

+V1.05S_AXCK_LCPLL

Power tracking

+3V_S5

+3V

+1.5V

+3V

+3V

1

11

+1.05V

+3V_S5 [5,7,8,9,10,13,21,24,27,28,29,31,34,36]

+1.5V [22,26,35]

+3V

+1.05V [5,13,30,33,34,35]

+3V_RTC [8,29]

+3VCC_S5 [7,13]

+1.05V_S5 [8,13,33,37]

+V1.05S_AUSB3PLL [9]

+V1.05S_ASATA3PLL [8]

+V1.05S_AXCK_LCPLL [9]

7/2 remove LDO instead of MOS switch

L9 2.2uH/210mA_8

C196

*47u/6.3V_8

+1.05V_MODPHY +V1.05S_AUSB3PLL +1.05V_MODPHY +V1.05S_ASATA3PLL

A A

L11 2.2uH/210mA_8

C197

47u/6.3V_8

5

C198

47u/6.3V_8

C199

1u/6.3V_4

L18 2.2uH/210mA_8

C454

47u/6.3V_8

4

42mA41mA

C455

47u/6.3V_8

C457

1u/6.3V_4

PCH HDA Power

+3V_S5

R216 *Short_6

3

11mA

+V3.3DX_1.5DX_1.8DX_AUDIO

C189

0.1u/10V_4

Place close to ball

57mA

C184

*47u/6.3V_8

+V1.05S_APLLOPI+1.05V

C206

1u/6.3V_4

2

VCCAPLL power

+1.05V +V1.05S_AXCK_DCB

L10 2.2uH/210mA_8

C180

47u/6.3V_8

+1.05V +V1.05S_AXCK_LCPLL

L19 2.2uH/210mA_8

C460

47u/6.3V_8

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

Date: Sheet of

Wednesday, September 03, 2014

0.2A

C179

47u/6.3V_8

C188

1u/6.3V_4

31mA

C461

47u/6.3V_8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

LPT 5/6 (POWER)

LPT 5/6 (POWER)

LPT 5/6 (POWER)

C462

1u/6.3V_4

1

ZQX

ZQX

ZQX

11 43

11 43

11 43

1B

1B

1B

5

4

3

2

1

Haswell ULT (GND)

HSW_ULT_DDR3L

18 OF 19

VSS_SENSE [34]

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U28O

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

G18

G22

H13

HSW_ULT_DDR3L

U28P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

VSS

16 OF 19

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS