Acer Aspire One AO751H Schematics

5

hexainf@hotmail.com

ZA3 PCB STACK UP

LAYER 1 : TOP

D D

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : BOT

4

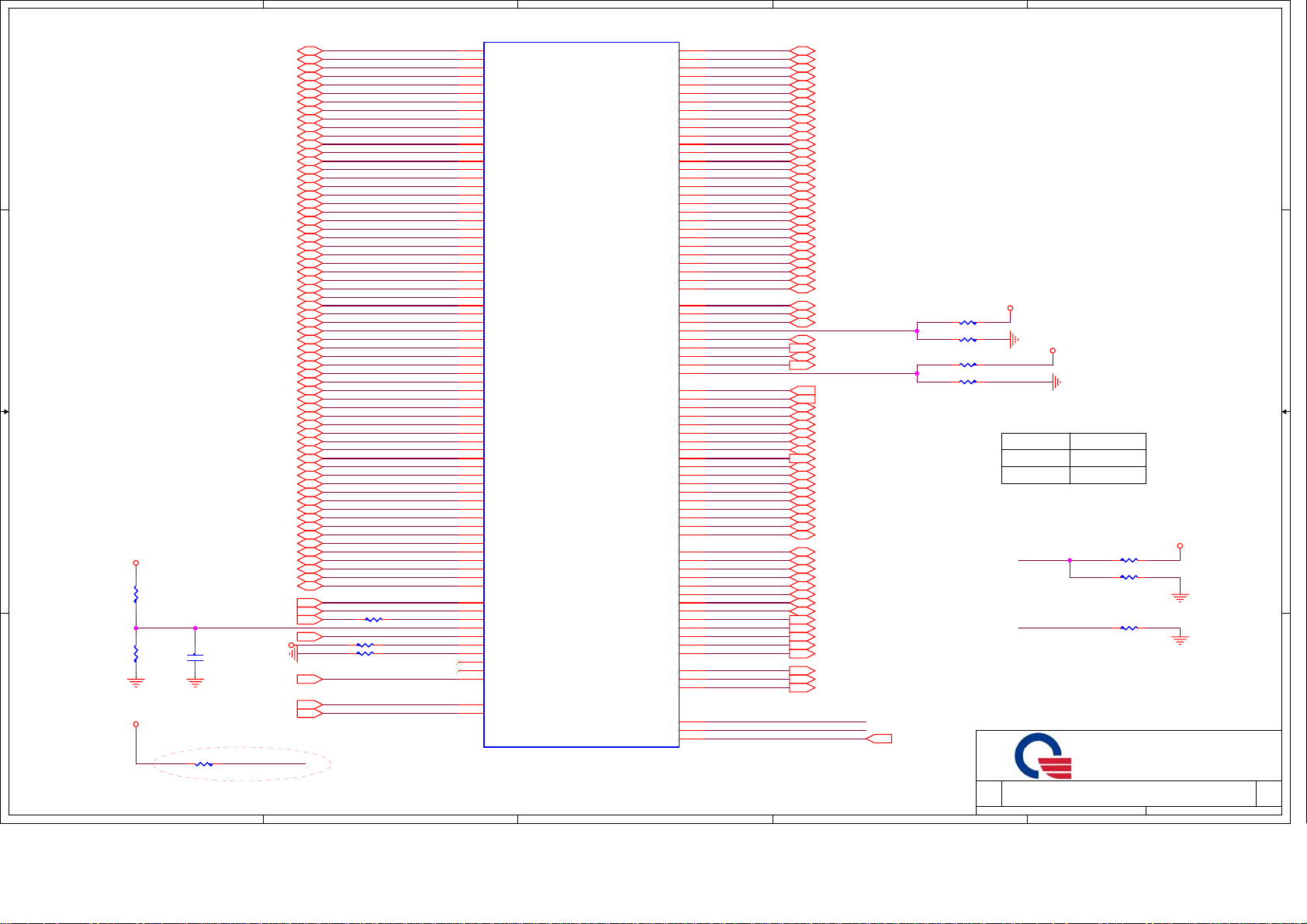

ZA3(11.6") Block Diagram

Intel@Atom(Silverthorne)

14 x 13 mm 441 Balls

3

Z520/Z530

Page 4~6

FSB 400/533MHz

2

CPU FSB (133MHz)

SCH FSB (133MHz)

SCH PCIE (100MHz)

SCH DA (96MHz)

SCH DB (100MHz)

SCH CLK14 (14.31818MHz)

WLAN CLK(100MHz)

LAN CLK(100MHz)

CR CLK(48MHz)

1

CLOCK GEN CK505

(SLG8SP513VTR

,ICS9LPRS365BKLFT)

Page 3

LVDS

11.6" LED Panel

Page 15

C C

CRT PORT CH7317A SDVO to RGB

RGB

Page 14Page 14

(1366 x 768)

SDVO

(1280 x 1024)

Intel@ System Controller Hub

(Poulsbo)

PCIE-1

PCIE-2

USB

10/100 LAN

(RTL8103EL)

Page 17

WLAN/WMAX

MODULE

Page 19

22 x 22 mm FCBGA 1249 Balls

DDR2 SO-DIMM

Page 13

USB X 3

DDR2 400/533MHz 1GB (Max 2GB)

USB 2.0 * (port0~7)

(PORT0,1,2)

B B

Page 20

CCD MODULE

Page 7~12

(PORT3)

Page 15

LPC

BT MODULE

(PORT4)

Page 21

4 IN 1 CardReader

WPCE775C/FLASH

Page 22

(PORT6)

Page 20

IDE/PATA INTERFACE

HD

PATA TO SATA CHIP

(JMH330 OR 8040)

Page 18

AUDIO CODEC

(ALC272)

Page 16

Audio AMP

(G1453L)

Page 16

SATA

2.5"HDD&SSD

Page 18

MIC(PINK)

Page 16

HP(GREEN)

Page 16

Int. MIC

Page 16

Int SPK

Page 16

A A

SIM Card

Page 19

5

3G MODULE

(PORT7)

Page 19

Touch Pad/B Con.

Page 21

4

3

SPI FlashK/B Con.

Page 22Page 21

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet

Date: Sheet

2

Date: Sheet

PROJECT :

ZA3

ZA3

ZA3

1A

1A

1A

134Sunday, March 08, 2009

134Sunday, March 08, 2009

134Sunday, March 08, 2009

of

of

1

of

5

4

3

2

1

ZA3 Power On Sequence

From AC,Battery VIN

D D

From PWM

From Power Button

From EC

From EC

From EC

From PWM

C C

From SCH

From SCH

From SCH

From EC

+5VPCU +3VPCU

SYS_HWPG(PCU)

NBSWON#

S5_ON

+3V_S5

+5V_S5

RSMRST#

SUSON

+3VSUS +1.8VSUS +SMDDR_VREF +SMDDR_VTERM

SUSON

>5ms

HWPG_1.8V (SUS)

RSTRDY#(H Level)

SLPMODE(L Level)

SLPRDY#(H Level)

MAINON

>5ms

MAINON

Items Function Name Description

PATA TO SATA BRIDGE 8040@

1

2

3G Module 3G@

3

4

FAN Module FAN_PWM@ PWM FAN

5

6

+5V +3V +2.5V +1.8V +1.5V +1.05V

From PWM

From EC

From PWM

HWPG_1.5V HWPG_1.05V

VRON

+VCC_CORE

VRON

(SMB_DATA) / (SMB_CLK) (+3V)

Power Plane

MOS CKT

CPU_COREPG

HWPG

B B

A A

From EC

From SCH

From SCH

From SCH

From SCH

From SCH

From SCH

From EC

From EC

From SCH

From SCH

ECPWROK

STPCPU#

STPCLK#

CPUSLP#

DPSLP#

DPRSTP#

DPRSLPVR

RSTWARN

PLTRST#

CPU_PWRGD

CPURST#

>5ms

20us

100us

EC775 SDA1 / SCL1 (+3VPCU)

EC775 SDA2 / SCL2 (+3VPCU)

Power Plane

MOS CKT

2ms

BOM naming rule

330@

Poulsbo SCH SMBUS Table

CLK GEN RAM Mini Card (WLAN/WMAX)

V

+3V +3V

ReserveReserve

VV

+3V

Reserve

EC SMBUS Table

Battery CPU thermal Sensor EC EEPROM

V

+3VPCU +3V +3VPCU

XX

VV

Stuff

Marvell 88SE8040

Jmicron JMH330PATA TO SATA BRIDGE

Mini Card (3G)

V

+3VSUS

Reserve

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Power Sequence/ BOM Rule

Power Sequence/ BOM Rule

Power Sequence/ BOM Rule

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

1

ZA3

ZA3

ZA3

1A

1A

1A

of

of

of

234Sunday, March 08, 2009

234Sunday, March 08, 2009

234Sunday, March 08, 2009

5

hexainf@hotmail.com

Clock Generator(CLK)

PBY160808T-301Y-N/2A/300ohm_6

PBY160808T-301Y-N/2A/300ohm_6

+3V

D D

C C

L2

L2

33p/50V_4C43 33p/50V_4C43

33p/50V_4C42 33p/50V_4C42

To Card Reader CLK

14M_SCH9

To SCH Oscillator CLK

B B

Pin 11

Pin 13

Pin 14

A A

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

C19

C19

0.1u/10V_4

0.1u/10V_4

C38

C38

0.1u/10V_4

0.1u/10V_4

C30

10u/10V_8

10u/10V_8

C37

C37

0.1u/10V_4

0.1u/10V_4

C45

C45

0.1u/10V_4

0.1u/10V_4

C47

C47

0.1u/10V_4

0.1u/10V_4

C41

C41

0.1u/10V_4

0.1u/10V_4

C24

C24

10u/10V_8

10u/10V_8

CG_XIN

21

Y2

Y2

14.318MHZ

14.318MHZ

CG_XOUT

FSC

SLG8SP513VTR

(AL8SP513000)

PCI2/TME

PCI4/

27_Select

PCIF-5/ITP_EN

SEL0SEL1SEL2

5

C26

VDD_CK_VDD_REF

T8T8

T9T9

CG_XIN

CG_XOUT

R40 10K_4R40 10K_4

R38 33_4R38 33_4

C26

10u/10V_8

10u/10V_8C30

+1.05V_VDD

PCI2

PCI4

PCIF5

FSA

FSB

FSC_R

C25

C25

10u/10V_8

10u/10V_8

U2

U2

9

VDD_PCI

16

VDD_48

23

VDD_PLL3

4

VDD_REF

46

VDD_SRC

62

VDD_CPU

19

VDD_96_IO

27

VDD_PLL3_IO

33

VDD_SRC_IO_1

52

VDD_SRC_IO_3

43

VDD_SRC_IO_2

56

VDD_CPU_IO

8

PCI0/CR#_A

10

PCI1/CR#_B

11

PCI2/TME

12

PCI3

13

PCI4/SRC5_EN

14

PCIF5/ITP_EN

3

XTAL_IN

2

XTAL_OUT

17

USB_48/FSA

64

FSB/TEST/MODE

5

REF0/FSC/TESTSEL

65

VSS_BODY

15

VSS_PCI

18

VSS_48

22

VSS_IO

26

VSS_PLL3

59

VSS_CPU

30

VSS_SRC1

36

VSS_SRC2

49

VSS_SRC3

1

VSS_REF

SLG8SP513VTR ,ICS9LPRS365BKLFT

ICS9LPRS365

(ALPRS365000)

PCI2/TME

PCI_4/

SEL_LCDCLK#

PCIF-5/ITP_EN

<MAIN> : SLG8SP513VTR(AL8SP513000)

<SECOND> : ICS9LPRS365BKLFT(ALPRS365000)

PULL HIGH PULL DOWN

NO OVERCLOCKING NORMAL RUN

PIN 24/25 IS 27MHz PIN 24/25

PIN 53/54 IS CPUITP PIN 53/54 IS SRC8

(default)

Frequence select

States

Default

4

C36

C36

0.1u/10V_4

0.1u/10V_4

CK505

CK505

IS SRC/DOT

4

C27

C27

0.1u/10V_4

0.1u/10V_4

IO_VOUT

SCLK

SDA

SRC5/PCI_STOP#

SRC5#/CPU_STOP#

CPU0

CPU0#

CPU1

CPU1#

SRC8/ITP

SRC8#/ITP#

SRC10

SRC10#

SRC11/CR#_H

SRC11#/CR#_G

SRC9

SRC9#

SRC7/CR#_F

SRC7#/CR#_E

SRC6

SRC6#

SRC4

SRC4#

SRC3/CR#_C

SRC3#/CR#_D

SRC2/SATA

SRC2#/SATA#

SRC1/SE1

SRC1#/SE2

SRC0/DOT96

SRC0#/DOT96#

CKPWRGD/PWRDWN#

SLG8SP513VTR

SLG8SP513VTR

(default)

(default)

C20

C20

0.1u/10V_4

0.1u/10V_4

55

SMBCK1

7

SMBDT1

6

PCI_STOP#

45

PM_STPCPU#

44

61

60

58

57

54

53

41

42

NB_CLKREQ0#_R

40

CLKREQ_WLAN#_R

39

37

38

51

50

48

47

34

35

31

CLKREQ_LAN#_R

32

28

29

24

25

20

21

63

+3V

+3V

+3V

C29

C29

0.1u/10V_4

0.1u/10V_4

R34 10K_4R34 10K_4

R33 *10K_4R33 *10K_4

R32 *10K_4R32 *10K_4

R31 10K_4R31 10K_4

R30 *10K_4R30 *10K_4

R29 10K_4R29 10K_4

FSA

FSB

FSC

3

+1.05V_VDD

C39

C39

0.1u/10V_4

0.1u/10V_4

T1T1

T7T7

T6T6

R11 475/F_4R11 475/F_4

R12 475/F_4R12 475/F_4

T4T4

T5T5

T3T3

T2T2

T11T11

R14 475/F_4R14 475/F_4

T13T13

T12T12

VR_PWRGD_CK410

3

L3

L3

PBY160808T-301Y-N/2A/300ohm_6

PBY160808T-301Y-N/2A/300ohm_6

C31

C31

0.1u/10V_4

0.1u/10V_4

PM_STPCPU# 9

HCLK_CPU 4

HCLK_CPU# 4

HCLK_MCH 7

HCLK_MCH# 7

PECLK_MCH 8

PECLK_MCH# 8

NB_CLKREQ0#

CLKREQ_WLAN#

WLAN_PE2CLK+ 19

WLAN_PE2CLK- 19

LAN_PE1CLK+ 17

LAN_PE1CLK- 17

DREFCLK_SS 9

DREFCLK_SS# 9

DREFCLK 9

DREFCLK# 9

PCI2

PCI4

PCIF5

R26 10K_4R26 10K_4

R25 10K_4R25 10K_4

R45 0_4R45 0_4

R44 0_4R44 0_4

R43 *10K_4R43 *10K_4

R46 *10K_4R46 *10K_4

2

Clock Gen I2C

+1.05V

PDAT_SMB9,19 SMBDT1 13

To CPU FSB CLK

To SCH FSB CLK

PCLK_SMB9,19 SMBCK1 13

To SCH PCIE CLK

NB_CLKREQ0# 9

CLKREQ_WLAN# 19

To Mini Card 1 (WLAN/WMAX)

To LAN

CLKREQ_LAN# 17

To SCH Display PLLB CLK

To SCH Display PLLA CLK

+3V

SCH_BSEL2 7

CPU_BSEL2 5

Change R43 P/N

+1.05V

from

CS00002JB38 to

CS31002JB28

rev.c 20090301

SCH PCIE CLKREQ

WLAN PCIE CLKREQ

LAN CLKREQ

NB_CLKREQ0#

PCI_STOP#

PM_STPCPU#

CLKREQ_WLAN#

CLK GEN & PWR

VR_PWRGD_CK410#25

2

1

+3V

R28

Q3

Q3

*2N7002E

*2N7002E

*2N7002E

*2N7002E

2

3

R39 *Short_4R39 *Short_4

Q4

Q4

2

3

R36 *Short_4R36 *Short_4

Modify R39 R36

footprint from

RC0402 to SHORT0402

for 0 ohm cost down

rev.c 20090301

R28

*10K_4

*10K_4

SMBDT1

1

+3V

R35

R35

*10K_4

*10K_4

SMBCK1

1

EMI

FSC_R

FSA

R10 *10K_4R10 *10K_4

R16 10K_4R16 10K_4

R17 10K_4R17 10K_4

R13 10K_4R13 10K_4

2

Q2

Q2

2N7002E

2N7002E

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

3

CLOCK GEN(CK505)

CLOCK GEN(CK505)

CLOCK GEN(CK505)

C46 *33p/50V_4C46 *33p/50V_4

C40 *33p/50V_4C40 *33p/50V_4

+3V

R24 100K_4R24 100K_4

VR_PWRGD_CK410

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

+3V

1

ZA3

ZA3

ZA3

334Sunday, March 08, 2009

334Sunday, March 08, 2009

334Sunday, March 08, 2009

of

of

of

1A

1A

1A

5

4

3

2

1

Silverthorne(CPU)

U14A

U14A

H_IGNNE#

AE16

AF17

AD15

AD17

E22

A22

D21

E24

B17

A18

B23

A16

E18

D15

B19

A20

D17

B15

D19

B25

D23

E20

A24

B21

B5

A12

D5

E12

B9

A6

B13

E14

A10

B7

D13

A8

C4

A14

B11

D11

G30

J28

H27

K1

H31

L28

J26

D9

D7

E8

E10

L30

J30

K29

A[3]#

0

0

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

ADDR GROUP 1

ADDR GROUP 1

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD7

RSVD8

RSVD9

RSVD10

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD13

SILVERTHORNE

SILVERTHORNE

ADDR GROUP

ADDR GROUP

THERM

THERM

THERMTRIP#

NC

NC

HA#37

HA#47

HA#57

HA#67

HA#77

HA#87

D D

C C

H_A20M#22

H_PBE#7

Note : H_FERR# for layout length must be greater

B B

than 150mils 20081128

HA#97

HA#107

HA#117

HA#127

HA#137

HA#147

HA#157

HA#167

HADSTB0#7

HREQ#07

HREQ#17

HREQ#27

HREQ#37

HREQ#47

HA#177

HA#187

HA#197

HA#207

HA#217

HA#227

HA#237

HA#247

HA#257

HA#267

HA#277

HA#287

HA#297

HA#307

HA#317

HADSTB1#7

T59T59

H_STPCLK#7

H_INTR7

H_NMI7

H_SMI#7

+1.05V_C6_OFF

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TDO

TMS

TRST#

RSVD14

XDP/ITP SIGNALSH CLK

XDP/ITP SIGNALSH CLK

PROCHOT#

THRMDA

THRMDC

BCLK[0]

BCLK[1]

VSS0

RSVD11

RSVD6

RSVD15

TEST4

TEST3

CMREF[1]

TCK

TDI

C26

H25

G24

B27

W28

D29

C28

H1

F31

D25

M5

D27

E28

E26

F25

E30

F29

XDP_OBSDATA_A3

F1

XDP_OBSDATA_A2

E2

XDP_OBSDATA_A1

F5

XDP_OBSDATA_A0

D3

XDP_OBSFN_A1

E4

XDP_OBSFN_A0

F7

TCK_CPU

L2

TDI

N2

TDO

M1

TMS

P1

TRST#

J4

G26

H_PROCHOT#

H5

H_THERMDA

T5

H_THERMDC

U4

CPU_THRMTRIP#

T1

P29

R28

K31

A26

E6

G28

U30

V27

AE26

.

.

H_IERR#

HCLK_CPU

HCLK_CPU#

CPU_CMREF

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BREQ#0 7

H_INIT# 7

H_LOCK# 7

T55T55

H_CPURST# 7

H_RS#0 7

H_RS#1 7

H_RS#2 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

T17T17

T19T19

T20T20

T18T18

XDP/ITP Debug

T24T24

T31T31

Test Points

TMS 9

TRST# 9

H_PROCHOT# 25

HCLK_CPU 3

HCLK_CPU# 3

C166

C166

*0.1u/10V_4

*0.1u/10V_4

+1.05V_C6_OFF

R132

R132

1K/F_4

1K/F_4

R135

R135

1K/F_4

1K/F_4

CPU Thermal monitor(THM)

2ND_MBCLK22

2ND_MBDATA22

R68 10K_4R68 10K_4

THERM_ALERT#9

+3V

FAN(THM)

THER_OVERT# THER_OVERT#_B

CPUFAN#22

R315 FAN_PWM@10K_4R315 FAN_PWM@10K_4

R320 FAN_PWM@0_4R320 FAN_PWM@0_4

FAN_PWM_EC FAN_PWM_E

+3V

3

R77 *0_4R77 *0_4

+3V

3

R78 *0_4R78 *0_4

+3V

FAN_PWM@MMBT3904

FAN_PWM@MMBT3904

Q5

2

2N7002EQ52N7002E

1

Q6

2

2N7002EQ62N7002E

1

R67 *0_4R67 *0_4

R69 10K_4R69 10K_4

2

Q25

Q25

1 3

+3V

R66

R66

10K_4

10K_4

THERM_ALERT#_R

+3V +3V

R314

R314

FAN_PWM@10K_4

FAN_PWM@10K_4

Q24

Q24

1 3

FAN_PWM@MMBT3904

FAN_PWM@MMBT3904

<check list>

Layout Note:Routing 10:10 mils and away

from noise source with ground gard

R80

R80

10K_4

10K_4

U6

U6

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

G780P81U

G780P81U

ADDRESS: 4C

FANSIG22

+5V

R321

R321

FAN_PWM@10K_4

FAN_PWM@10K_4

2

R203

R203

FAN_PWM@10K_4

FAN_PWM@10K_4

FAN_PWM_CN

VCC

DXP

DXN

GND

+3V

1

2

3

5

+3V

C104

C104

0.1u/10V_4

0.1u/10V_4

H_THERMDA

C103

C103

2200p/50V_4

2200p/50V_4

H_THERMDCTHER_OVERT#

R202

R202

FAN_PWM@10K_4

FAN_PWM@10K_4

+5V

CN9

CN9

1

2

5

3

6

4

FAN_PWM@CONN(88266-04001-06)

FAN_PWM@CONN(88266-04001-06)

+1.05V_C6_OFF

H_A20M#

H_IGNNE#

H_INIT#

H_PBE#

XDP_OBSFN_A0

For intel suggest R115 connect to

+1.05V_C6_OFF 20081218

TDO

TDI

A A

TCK_CPU

Modify JETC pins for Boundary

Scan rev.b 20090205

TDI

TMS

TCK_CPU

5

R141 1K_4R141 1K_4

R142 1K_4R142 1K_4

R146 1K_4R146 1K_4

R145 120_4R145 120_4

R115 51/F_4R115 51/F_4

R90 0_4R90 0_4

R94 *0_4R94 *0_4

R95 0_4R95 0_4

R96 0_4R96 0_4

R98 56_4R98 56_4

R87 56_4R87 56_4

R97 56_4R97 56_4

XDP_TDO 9

BC_TDI 9

TCK_SCH 9

+1.05V

H_IERR#

H_PROCHOT#

4

TDI

XDP_TDO

BC_TDI

TMS

TCK_CPU

TCK_SCH

TRST#

R102 56_4R102 56_4

R113 68_4R113 68_4

+1.05V

Thermal Trip(CPU)

+1.05V

3

Q8

IMVP_PWRGD22,25

Change R88 P/N from

CS05602JB17 to

T25T25

T22T22

T44T44

T28T28

T21T21

T40T40

T27T27

CS11202JB21 rev.c

20090301

3

CPU_THRMTRIP#

+1.05V

R88

R88

120_4

120_4

2

2N7002EQ82N7002E

1

R103 100K_6R103 100K_6

R93

R93

1K_4

1K_4

2

Q7

Q7

1 3

MMBT3904

MMBT3904

R81 *24_4R81 *24_4

Change R81 P/N from

CS00002JB38 to

CS02402JB11 rev.c

20090301

2

SYS_SHDN# 24,29

H_THRMTRIP# 7

To SCH

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Silverthorne CPU(01_HOST)

Silverthorne CPU(01_HOST)

Silverthorne CPU(01_HOST)

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

ZA3

ZA3

ZA3

of

of

of

434Sunday, March 08, 2009

434Sunday, March 08, 2009

1

434Sunday, March 08, 2009

1A

1A

1A

5

hexainf@hotmail.com

4

3

2

1

Silverthorne(CPU)

U14D

U14D

A4

VSS1

A28

VSS2

AA6

D D

C C

B B

A A

5

AA24

AB3

AB27

AB29

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD3

AD5

AD9

AD11

AD21

AD23

AD25

AD29

AF1

AF31

AG2

AG6

AG8

AG10

AG12

AG14

AG16

AG18

AG20

AG22

AG24

AG26

AG30

AH3

AH29

AJ4

AJ28

B29

C10

C12

C14

C16

C18

C20

C22

C24

C30

D31

F11

F13

F17

F19

F21

F23

F27

G10

G12

G14

G16

G18

G20

G22

H29

B3

C2

C6

C8

D1

F3

F9

G8

H3

J6

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS41

VSS42

VSS45

VSS46

VSS48

VSS49

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

SILVERTHORNE

SILVERTHORNE

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

Y29

Y25

Y23

Y21

Y19

Y17

Y15

Y13

Y11

Y9

Y7

Y3

W6

V29

V25

V23

V21

V19

V17

V15

V13

V11

V9

V7

V5

V3

T29

T27

T25

T23

T21

T19

T17

T15

T13

T11

T9

T7

T3

P27

P25

P23

P21

P19

P17

P15

P13

P11

P9

P7

P3

N28

M29

M25

M23

M21

M19

M17

M15

M13

M11

M9

M7

M3

L6

K25

K23

K21

K19

K17

K15

K13

K11

K9

K7

K3

J24

4

+1.05V_C6_OFF

R133

R133

1K/F_4

1K/F_4

R136

R136

C167

C167

2K/F_4

2K/F_4

*0.1u/10V_4

*0.1u/10V_4

BSEL[2] BSEL[1]

L

HL

HD#07

HD#17

HD#27

HD#37

HD#47

HD#57

HD#67

HD#77

HD#87

HD#97

HD#107

HD#117

HD#127

HD#137

HD#147

HD#157

HDSTBP#07

HDINV#07

HD#167

HD#177

HD#187

HD#197

HD#207

HD#217

HD#227

HD#237

HD#247

HD#257

HD#267

HD#277

HD#287

HD#297

HD#307

HD#317

HDSTBN#17

HDSTBP#17

HDINV#17

CPU_BSEL23

CPU_GTLREF

BSEL[0]

AH27

AC30

AE30

AF29

AA26

AB31

W30

AC28

AD31

AF27

AD27

AG28

AB25

AC26

AA28

AA30

AE28

AE24

AC24

AJ20

AE20

AJ22

AF25

AH25

AH23

AH19

AF23

AE18

AH17

AD19

AJ24

AJ18

AF19

AF21

AH21

AE22

AJ26

M31

U28

Frequency

LH

H

3

U14B

U14B

Y27

D[0]#

D[1]#

Y31

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

P31

TEST1

T31

TEST2

R30

BSEL[0]

BSEL[1]

BSEL[2]

SILVERTHORNE

SILVERTHORNE

133

100

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

MISC

MISC

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

DATA GRP 2

DATA GRP 2

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

DATA GRP 3

DATA GRP 3

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

RSVD12

AE8

AD7

AH15

AF9

AH9

AE10

AJ16

AF13

AF7

AF15

AH13

AJ14

AJ12

AH7

AJ8

AJ10

AH11

AF11

AE12

AH5

AB5

AJ6

Y1

AF5

AG4

AF3

AC6

AE6

AE4

W4

AC2

AE2

AD1

AA2

AC4

AB1

AA4

Y5

AE14

AD13

E16

F15

G2

G6

V31

G4

J2

K27

COMP0

COMP1

COMP2

COMP3

2

HD#32 7

HD#33 7

HD#34 7

HD#35 7

HD#36 7

HD#37 7

HD#38 7

HD#39 7

HD#40 7

HD#41 7

HD#42 7

HD#43 7

HD#44 7

HD#45 7

HD#46 7

HD#47 7

HDSTBN#2 7HDSTBN#07

HDSTBP#2 7

HDINV#2 7

HD#48 7

HD#49 7

HD#50 7

HD#51 7

HD#52 7

HD#53 7

HD#54 7

HD#55 7

HD#56 7

HD#57 7

HD#58 7

HD#59 7

HD#60 7

HD#61 7

HD#62 7

HD#63 7

HDSTBN#3 7

HDSTBP#3 7

HDINV#3 7

R125 27.4/F_4R125 27.4/F_4

R117 54.9/F_4R117 54.9/F_4

R119 27.4/F_4R119 27.4/F_4

R120 54.9/F_4R120 54.9/F_4

H_DPRSTP# 7,25

H_DPSLP# 7

H_DPWR# 7

H_PWRGD 7

H_CPUSLP# 7

T54T54

T56T56

T57T57

T58T58

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Silverthorne CPU(02_HOST)

Silverthorne CPU(02_HOST)

Silverthorne CPU(02_HOST)

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

ZA3

ZA3

ZA3

534Sunday, March 08, 2009

534Sunday, March 08, 2009

534Sunday, March 08, 2009

1

1A

1A

1A

of

of

of

5

Silverthorne(CPU)

4

3

2

1

D D

+1.05V

C C

B B

A A

+1.05V_C6_OFF

C148

C148

1u/10V_4

1u/10V_4

+1.05V_C6_OFF

C113

C113

1u/10V_4

1u/10V_4

5

AA14

AA10

AA12

AA16

AA18

AA20

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AB23

W26

M27

AA8

AB7

AB9

H11

H13

H15

H17

H19

H21

H23

L26

N26

R26

U26

J16

H7

H9

J8

J10

J12

J14

J18

J20

J22

U14C

U14C

VCCP35

VCCP36

VCCP0

VCCPC61

VCCPC62

VCCPC63

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

VCCP28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

SILVERTHORNE

SILVERTHORNE

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

VCC_CORE

L8

L10

L12

L14

L16

L18

L20

L22

L24

N6

N8

N10

N12

N14

N16

N18

N20

N22

N24

R6

R8

R10

R12

R14

R16

R18

R20

R22

R24

U6

U8

U10

U12

U14

U16

U18

U20

U22

U24

W8

W10

W12

W14

W16

W18

W20

W22

W24

N30

P5

R4

N4

K5

L4

R2

U2

W2

V1

For Design Guide VCCSENSE pull up

100ohm to VCC_CORE 20081206

CPU_CORE

C138

C138

0.1u/10V_4

0.1u/10V_4

C156

C156

10u/6.3V_6

10u/6.3V_6

C129

C129

0.1u/10V_4

0.1u/10V_4

C155

C155

10u/6.3V_6

10u/6.3V_6

VCCP(+1.05V_C6_OFF)

C121

C127

C127

0.1u/10V_4

0.1u/10V_4

VID0 25

VID1 25

VID2 25

VID3 25

VID4 25

VID5 25

VID6 25

R101 100_4R101 100_4

R100 100_4R100 100_4

C121

1u/10V_4

1u/10V_4

VCC_CORE

4

C149

C149

1u/10V_4

1u/10V_4

C130

C130

1u/10V_4

1u/10V_4

VCC_CORE

C157

C157

10u/6.3V_6

10u/6.3V_6

+1.05V_C6_OFF

C162

C162

1u/10V_4

1u/10V_4

+1.5V

C174

C174

0.1u/10V_4

0.1u/10V_4

VCC_SENSE 25

VSS_SENSE 25

C140

C140

1u/10V_4

1u/10V_4

C135

C135

10u/6.3V_6

10u/6.3V_6

C165

C165

10u/6.3V_6

10u/6.3V_6

+1.5V

C137

C137

1u/10V_4

1u/10V_4

C185

C185

10u/6.3V_6

10u/6.3V_6

C141

C141

C128

C128

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

Modify +1.05V_C6_OFF

circuit 20090113

Modify R326 from

10K to 100K and

pull up +3V rev.c

20090228

SLPIOVR#9

3

C158

C158

1u/10V_4

1u/10V_4

VCC_CORE

C139

C139

1u/10V_4

1u/10V_4

Modify R168 P/N

from CS31002JB28

to CS41002JB20

rev.c 20090228

R326

R326

100K_4

100K_4

2

Q26

Q26

DTC144EU

DTC144EU

C131

C131

1u/10V_4

1u/10V_4

R168

R168

100K_4

100K_4

1.05_C6_EN1

1 3

+5V+3V

Add and revrse

Q27 R329 for C6

circuit rev.c

20090303

1

Q27

Q27

*AO3409

*AO3409

2

3

R329 *1K_4R329 *1K_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

R148

R148

33K_4

33K_4

1.05_C6_EN2

3

2

Q13

Q13

2N7002E

2N7002E

1

Silverthorne CPU(03_Power)

Silverthorne CPU(03_Power)

Silverthorne CPU(03_Power)

+1.05V

+1.05V

Q9

Q9

65241

SI3456BDV

SI3456BDV

3

C160

C160

*0.047u/25V_4

*0.047u/25V_4

+1.05V_C6_OFF

2.5A

+1.05V_C6_OFF

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZA3

ZA3

ZA3

of

of

of

634Sunday, March 08, 2009

634Sunday, March 08, 2009

634Sunday, March 08, 2009

1

1A

1A

1A

5

hexainf@hotmail.com

Poulsbo(CLG)

D D

C C

B B

+1.05V

15mil/10mil

R137

R137

221/F_4

221/F_4

R140

R140

100/F_4

100/F_4

A A

+1.05V

R89 56_4R89 56_4

5

C172

C172

0.1u/10V_4

0.1u/10V_4

HD#05

HD#15

HD#25

HD#35

HD#45

HD#55

HD#65

HD#75

HD#85

HD#95

HD#105

HD#115

HD#125

HD#135

HD#145

HD#155

HD#165

HD#175

HD#185

HD#195

HD#205

HD#215

HD#225

HD#235

HD#245

HD#255

HD#265

HD#275

HD#285

HD#295

HD#305

HD#315

HD#325

HD#335

HD#345

HD#355

HD#365

HD#375

HD#385

HD#395

HD#405

HD#415

HD#425

HD#435

HD#445

HD#455

HD#465

HD#475

HD#485

HD#495

HD#505

HD#515

HD#525

HD#535

HD#545

HD#555

HD#565

HD#575

HD#585

HD#595

HD#605

HD#615

HD#625

HD#635

H_NMI4

H_SMI#4

H_PBE#4

H_STPCLK#4

+1.05V

H_THRMTRIP#4

H_INIT#4

H_INTR4

H_THRMTRIP#

R150 24_4R150 24_4

R127 *56_4R127 *56_4

R147 24.9/F_4R147 24.9/F_4

4

H_PBE#_R

H_SWING

H_TESTIN#

H_RCOMPO

Modify R150

from CPU side

to SCH side

rev.c

20090301

4

AA1

AC1

AD2

AB2

AB4

AE1

AB8

AH2

AM8

AN1

AK4

AG1

AH8

AK8

AP8

AK2

AR1

AH4

AP4

AP2

AV4

BB6

AV6

AY8

BA1

AU1

AV8

BB4

AY6

AV10

AV2

BC1

BB2

AY2

BD2

BH4

BD10

BK10

BD6

BD4

BE1

BD8

BH10

BK6

BB8

BF10

BH6

AB10

AB6

AH6

AD10

AK6

AT10

AP10

AM6

AF10

AF4

AF2

AF8

AJ1

AT8

AT2

AT6

AT4

BF2

BF4

BF6

T10

AF6

V8

V2

V4

Y2

U1

Y8

V6

U15A

U15A

H_D0#

H_D1#

H_D2#

H_D3#

H_D4#

H_D5#

H_D6#

H_D7#

H_D8#

H_D9#

H_D10#

H_D11#

H_D12#

H_D13#

H_D14#

H_D15#

H_D16#

H_D17#

H_D18#

H_D19#

H_D20#

H_D21#

H_D22#

H_D23#

H_D24#

H_D25#

H_D26#

H_D27#

H_D28#

H_D29#

H_D30#

H_D31#

H_D32#

H_D33#

H_D34#

H_D35#

H_D36#

H_D37#

H_D38#

H_D39#

H_D40#

H_D41#

H_D42#

H_D43#

H_D44#

H_D45#

H_D46#

H_D47#

H_D48#

H_D49#

H_D50#

H_D51#

H_D52#

H_D53#

H_D54#

H_D55#

H_D56#

H_D57#

H_D58#

H_D59#

H_D60#

H_D61#

H_D62#

H_D63#

H_NMI

H_SMI#

H_PBE#

H_SWING

H_STPCLK#

H_TESTIN#

H_RCOMPO

RESERVED5

RESERVED4

H_THRMTRIP#

H_INIT#

H_INTR

POULSBO

POULSBO

HOST

HOST

H_CPUPWRGD

3

H_A3#

H_A4#

H_A5#

H_A6#

H_A7#

H_A8#

H_A9#

H_A10#

H_A11#

H_A12#

H_A13#

H_A14#

H_A15#

H_A16#

H_A17#

H_A18#

H_A19#

H_A20#

H_A21#

H_A22#

H_A23#

H_A24#

H_A25#

H_A26#

H_A27#

H_A28#

H_A29#

H_A30#

H_A31#

H_ADS#

H_ADSTB0#

H_ADSTB1#

H_GVREF

H_BNR#

H_BPRI#

H_BREQ0#

H_CPURST#

H_CGVREF

H_CLKINN

H_CLKINP

H_DBSY#

H_DEFER#

H_DINV0#

H_DINV1#

H_DINV2#

H_DINV3#

H_DPWR#

H_DRDY#

H_DSTBN0#

H_DSTBN1#

H_DSTBN2#

H_DSTBN3#

H_DSTBP0#

H_DSTBP1#

H_DSTBP2#

H_DSTBP3#

H_HIT#

H_HITM#

H_LOCK#

H_REQ0#

H_REQ1#

H_REQ2#

H_REQ3#

H_REQ4#

H_RS0#

H_RS1#

H_RS2#

H_CPUSLP#

H_TRDY#

H_DPSLP#

H_DPRSTP#

CFG0

CFG1

BSEL2

3

M2

M8

K4

P2

F4

G1

M4

F6

H6

D2

H2

J1

F2

D4

D12

H12

G11

A7

A9

A11

B6

H8

F10

B10

D6

D10

B12

B4

D8

K6

H4

B8

Y10

R1

P10

L1

M6

AD4

K10

M10

H10

AD6

AD8

AM2

AY10

BK8

P6

J9

Y4

AL1

AW1

BH8

W1

AM4

AY4

BF8

V10

T6

Y6

P4

N1

K8

P8

K2

T4

T2

T8

AH10

F12

AP6

F8

AK10

J27

B34

F28

H_GVREF

H_CGVREF

HCLK_MCH#

HCLK_MCH

CFG0

CFG1

SCH_BSEL2

HA#3 4

HA#4 4

HA#5 4

HA#6 4

HA#7 4

HA#8 4

HA#9 4

HA#10 4

HA#11 4

HA#12 4

HA#13 4

HA#14 4

HA#15 4

HA#16 4

HA#17 4

HA#18 4

HA#19 4

HA#20 4

HA#21 4

HA#22 4

HA#23 4

HA#24 4

HA#25 4

HA#26 4

HA#27 4

HA#28 4

HA#29 4

HA#30 4

HA#31 4

H_ADS# 4

HADSTB0# 4

HADSTB1# 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_CPURST# 4

HCLK_MCH# 3

HCLK_MCH 3

H_DBSY# 4

H_DEFER# 4

HDINV#0 5

HDINV#1 5

HDINV#2 5

HDINV#3 5

H_DPWR# 5

H_DRDY# 4

HDSTBN#0 5

HDSTBN#1 5

HDSTBN#2 5

HDSTBN#3 5

HDSTBP#0 5

HDSTBP#1 5

HDSTBP#2 5

HDSTBP#3 5

H_HIT# 4

H_HITM# 4

H_LOCK# 4

HREQ#0 4

HREQ#1 4

HREQ#2 4

HREQ#3 4

HREQ#4 4

H_RS#0 4

H_RS#1 4

H_RS#2 4

H_CPUSLP# 5

H_TRDY# 4

H_PWRGD 5

H_DPSLP# 5

H_DPRSTP# 5,25

2

R130 1K/F_4R130 1K/F_4

R134 2K/F_4R134 2K/F_4

R131 1K/F_4R131 1K/F_4

R129 1K/F_4R129 1K/F_4

SCH_BSEL2 3

2

1

+1.05V

+1.05V

FSB Clock

FSB/DDR

H

CFG0

CFG0

CFG1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Poulsbo(01_HOST)

Poulsbo(01_HOST)

Poulsbo(01_HOST)

Date: Sheet

Date: Sheet

Date: Sheet

133

L

100CFG0

+1.05V

R154 10K_4R154 10K_4

R155 *10K_4R155 *10K_4

R299 10K_4R299 10K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZA3

ZA3

ZA3

1

734Sunday, March 08, 2009

734Sunday, March 08, 2009

734Sunday, March 08, 2009

of

of

of

1A

1A

1A

5

4

3

2

1

Poulsbo(CLG)

Stuff R312 for Keyboard

and TP issues rev.c

20090228

D D

+3V

R311 10K_4R311 10K_4

R312 10K_4R312 10K_4

R294 10K_4R294 10K_4

R293 10K_4R293 10K_4

R333 20K_4R333 20K_4

R334 20K_4R334 20K_4

R335 20K_4R335 20K_4

R336 20K_4R336 20K_4

Add R333 R334

R335 R336 for

LPC AD0~AD3

rev.c 20090301

CLKRUN#

SERIRQ

PHL_CLK

PHL_DATA

LPCAD0

LPCAD1

LPCAD2

LPCAD3

EMI

C192 *22p/50V_4C192 *22p/50V_4

C C

RTC Battery

SANYO: AHL03001502 ; ML1220-CM11

MATSUSHITA: AHL03001405 ; ML1220/USTC/TSB1

MAXELL: AHL03001404 ; ML1220-ZR1S

B B

LCLK_EC

LPCAD019,22

LPCAD119,22

LPCAD219,22

LPCAD319,22

LCLK_EC22

PCLK_DEBUG19

CLKRUN#22

SERIRQ22

LPCFRAME#19,22

INT_LVDS_PWM15

INT_LVDS_BLON15

PHL_CLK15

PHL_DATA15

INT_LVDS_DIGON15

TXLCLKOUT+15

TXLCLKOUT-15

TXLOUT0-15

TXLOUT1-15

TXLOUT2-15

TXLOUT0+15

TXLOUT1+15

TXLOUT2+15

R157 22_4R157 22_4

R300 22_4R300 22_4

+3V

Add T60 T61 T62 T63

test point for

Boundary Scan rev.b

20090205

R189 10K_4R189 10K_4

R182 10K_4R182 10K_4

T60T60

T61T61

T62T62

T63T63

LPCAD0

LPCAD1

LPCAD2

LPCAD3

LCLK_EC_R

PCLK_DEBUG_R

SERIRQ

SD_CD#

SD_CMD

RTC(RTC)

VCCRTC

C208

+3VPCU

R280

R280

1K_4

1K_4

D12

D12

CH500H-40

CH500H-40

D13

D13

CH500H-40

CH500H-40

C208

1u/10V_6

1u/10V_6

R205

R205

20K/F_6

20K/F_6

C207

C207

1u/10V_6

1u/10V_6

RTCRST#VCCRTC_3

12

G2

G2

*SHORT_PAD

*SHORT_PAD

AF48

AF50

AJ43

AK48

AH48

AG45

AJ45

AK50

AH50

AG43

K38

A35

F38

B36

D38

D36

B38

K40

A33

A31

D28

K26

A27

H28

D30

B18

D18

H18

F18

H16

A17

K18

F16

K16

B16

D16

K20

B22

H22

F20

A21

B20

F22

K22

D22

G21

H20

D20

A19

K24

D26

B24

D24

B26

A25

F26

A23

F24

H24

H26

E25

J39

L39

J15

J19

J23

U15B

U15B

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_CLKOUT0

LPC_CLKOUT1

LPC_CLKOUT2

LPC_CLKRUN#

LPC_SERIRQ

LPC_FRAME#

L_BKLTCTL

L_BKLTEN

L_CTLA_CLK

L_CTLB_DATA

L_DDCCLK

L_DDCDATA

L_VDDEN

LA_CLKP

LA_CLKN

LA_DATAN0

LA_DATAN1

LA_DATAN2

LA_DATAN3

LA_DATAP0

LA_DATAP1

LA_DATAP2

LA_DATAP3

SD0_CD#

SD0_CLK

SD0_CMD

SD0_LED

SD0_WP

SD0_DATA0

SD0_DATA1

SD0_DATA2

SD0_DATA3

SD0_DATA4

SD0_DATA5

SD0_DATA6

SD0_DATA7

SD1_CD#

SD1_CLK

SD1_CMD

SD1_LED

SD1_WP

SD1_DATA0

SD1_DATA1

SD1_DATA2

SD1_DATA3

RESERVED18

SD0_PWR#

SD1_PWR#

SD2_PWR#

SD2_CD#

SD2_CLK

SD2_CMD

SD2_LED

SD2_WP

SD2_DATA0

SD2_DATA1

SD2_DATA2

SD2_DATA3

SD2_DATA4

SD2_DATA5

SD2_DATA6

SD2_DATA7

LPC BUS

LPC BUS

LVDS

LVDS

MISC SIGNALSSYSTEM MGMTSDVOPCIE

MISC SIGNALSSYSTEM MGMTSDVOPCIE

RTC

RTC

SDIO / MMC

SDIO / MMC

SDVOB_TVCLKIN#

POULSBO

POULSBO

RESERVED8

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RTC_X1

RTC_X2

INTVRMEN

RTCRST#

EXTTS

PWROK

SLPRDY#

DPRSLPVR

SLPMODE

RSMRST#

SDVO_CTRLCLK

SDVO_CTRLDATA

SDVOB_CLK

SDVOB_CLK#

SDVOB_INT

SDVOB_INT#

SDVOB_STALL

SDVOB_STALL#

SDVOB_TVCLKIN

SDVOB_RED

SDVOB_RED#

SDVOB_GREEN

SDVOB_GREEN#

SDVOB_BLUE

SDVOB_BLUE#

PCIE_PERn1

PCIE_PERp1

PCIE_PETn1

PCIE_PETp1

PCIE_PERn2

PCIE_PERp2

PCIE_PETn2

PCIE_PETp2

PCIE_CLKINN

PCIE_CLKINP

PCIE_ICOMPI

PCIE_ICOMPO

BK50

SCH_RSV1 : (LPC_CLKOUT0 buffer strength)

0 = 1 Load driver strength

1 = 2 Load driver strength

*** intel has integrated 300K puii-up

+3V

E49

B32

BE15

BA21

F48

F50

F46

H48

D32

C49

J49

D34

L45

L43

F30

A29

AV48

AV50

AU47

AU49

AN45

AN43

AP48

AP50

AM50

AM48

AT50

AT48

AR45

AR43

AW45

AW43

BB48

BB50

BA43

BA45

BE49

BD50

AY48

AY50

BA47

BA49

SDVO_CLK+

SDVO_CLK-

SDVO_R+

SDVO_RSDVO_G+

SDVO_GSDVO_B+

SDVO_B-

PE1TX-R

PE1TX+R

PE2TX-R

PE2TX+R

R298 *10K_4R298 *10K_4

RSVD1

R310 10K_4R310 10K_4

RTC_X1

RTC_X2

INTVRMEN

RTCRST#

R302 10K_4R302 10K_4

R122 10K_4R122 10K_4

C233 0.1u/10V_4C233 0.1u/10V_4

C231 0.1u/10V_4C231 0.1u/10V_4

SDVO to CRT

C243 0.1u/10V_4C243 0.1u/10V_4

C240 0.1u/10V_4C240 0.1u/10V_4

C239 0.1u/10V_4C239 0.1u/10V_4

C238 0.1u/10V_4C238 0.1u/10V_4

C237 0.1u/10V_4C237 0.1u/10V_4

C235 0.1u/10V_4C235 0.1u/10V_4

C109 0.1u/10V_4C109 0.1u/10V_4

C111 0.1u/10V_4C111 0.1u/10V_4

C257 0.1u/10V_4C257 0.1u/10V_4

C258 0.1u/10V_4C258 0.1u/10V_4

PCIE_ICOMPO

R118 24.9/F_4R118 24.9/F_4

VCCRTC

+3V

PM_EXTTS#0 13

ECPWROK 22

PM_SLPRDY# 22

PM_DPRSLPVR 25

PM_SLPMODE 22

EC_RSMRST# 22

SDVO_CTRLCLK 14

SDVO_CTRLDAT 14

SDVO_CLK+_R 14

SDVO_CLK-_R 14

SDVO_R+_R 14

SDVO_R-_R 14

SDVO_G+_R 14

SDVO_G-_R 14

SDVO_B+_R 14

SDVO_B-_R 14

PE1RX- 17

PE1RX+ 17

PE1TX- 17

PE1TX+ 17

PE2RX- 19

PE2RX+ 19

PE2TX- 19

PE2TX+ 19

PECLK_MCH# 3

PECLK_MCH 3

+1.5V

ECPWROK

R303 10K_4R303 10K_4

R287

R287

10M_4

10M_4

Change C233 C231 C243

C240 C239 C238 C237

C235 from SDVO chip

side to SCH side rev.c

20090301

PCIE TO LAN

PCIE TO WLAN/WMAX

C281 18p/50V_4C281 18p/50V_4

Y6

Y6

32.768KHz

32.768KHz

C279 18p/50V_4C279 18p/50V_4R185 10K_4R185 10K_4

CN16

A A

CN16

1

3

1

3

2

4

2

4

ACS_85204-0200L

ACS_85204-0200L

5

VCCRTC_4

Q23

Q23

MMBT3904

MMBT3904

1 3

2

R281 2K/F_4R281 2K/F_4

4

R282 2K/F_4R282 2K/F_4

R285

R285

6.8K_4

6.8K_4

R289 15K_4R289 15K_4

+5V_S5

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Poulsbo(02_LPC/LVDS/SDIO)

Poulsbo(02_LPC/LVDS/SDIO)

Poulsbo(02_LPC/LVDS/SDIO)

Date: Sheet

Date: Sheet

2

Date: Sheet

PROJECT :

ZA3

ZA3

ZA3

1A

1A

1A

of

of

of

834Sunday, March 08, 2009

834Sunday, March 08, 2009

834Sunday, March 08, 2009

1

5

hexainf@hotmail.com

Poulsbo(CLG)

0--MB USB PORT1

1--MB USB PORT2

2--DB USB PORT3

3--CCD Module

4--BT Module

D D

5--MINI WLAN/WMAX

6--CARD READER

7--MINI 3G Module

+3V_S5

R240 10K_4R240 10K_4

R124 10K_4R124 10K_4

C C

+3V

B B

A A

R301 4.7K_4R301 4.7K_4

R279 10K_4R279 10K_4

5

USBP0-20

USBP0+20

USBP1-20

USBP1+20

USBP2-20

USBP2+20

USBP3-15

USBP3+15

USBP4-21

USBP4+21

USBP5-19

USBP5+19

USBP6-20

USBP6+20

USBP7-19

USBP7+19

USBOC#0_120

USBOC#220

R128 22.6/F_4R128 22.6/F_4

PDDREQ18

PIORDY18

IRQ1418

PDDACK#18

PDIOW#18

PDIOR#18

PDCS3#18

PDCS1#18

PDA218

PDA118

PDA018

PDD1518

PDD1418

PDD1318

PDD1218

PDD1118

PDD1018

PDD918

PDD818

PDD718

PDD618

PDD518

PDD418

PDD318

PDD218

PDD118

PDD018

PIORDY

IRQ14

USB_RBIAS_P/N

PIORDY

IRQ14

AE47

AE49

AD48

AD50

AB50

AB48

AA49

AA47

Y48

Y50

V50

V48

U47

U49

T50

T48

R43

W45

R45

U43

AA45

AA43

W43

U45

AC45

AC43

D46

G45

B46

A37

F44

C47

E47

K42

H40

B40

E43

H42

D42

F40

A43

A41

A39

B42

F42

D44

B44

G43

D40

4

J43

J45

J41

L41

4

U15C

U15C

USB_DN0

USB_DP0

USB_DN1

USB_DP1

USB_DN2

USB_DP2

USB_DN3

USB_DP3

USB_DN4

USB_DP4

USB_DN5

USB_DP5

USB_DN6

USB_DP6

USB_DN7

USB_DP7

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

USB_OC5#

USB_OC6#

USB_OC7#

USB_RBIASN

USB_RBIASP

PATA_DDREQ

PATA_IORDY

PATA_IDEIRQ

PATA_DDACK#

PATA_DIOW#

PATA_DIOR#

PATA_DCS3#

PATA_DCS1#

PATA_DA2

PATA_DA1

PATA_DA0

PATA_DD15

PATA_DD14

PATA_DD13

PATA_DD12

PATA_DD11

PATA_DD10

PATA_DD9

PATA_DD8

PATA_DD7

PATA_DD6

PATA_DD5

PATA_DD4

PATA_DD3

PATA_DD2

PATA_DD1

PATA_DD0

USB I/F PATA/IDE

USB I/F PATA/IDE

JTAG

JTAG

STPCPU#

RSTRDY#

RSTWARN

GPIOSUS0

GPIOSUS1

GPIOSUS2

GPIOSUS3

SYSTEM GPIOsHD AUDIOCLOCK I/F

SYSTEM GPIOsHD AUDIOCLOCK I/F

No-Connect

No-Connect

HDA_CLK

HDA_SYNC

HDA_RST#

HDA_SDI0

HDA_SDI1

HDA_SDO

HDA_DOCKEN#

HDA_DOCKRST#

RESERVED6

RESERVED7

DA_REFCLKINN

DA_REFCLKINP

DB_REFCLKINNSSC

DB_REFCLKINPSSC

CLKREQ#

USB_CLK48

SMB_ALERT#

SMB_DATA

SMB_CLK

SMB Termination Voltage

SMB Termination Voltage

POULSBO

POULSBO

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_16

TRST#

TMS

TDO

TCK

RESET#

WAKE#

SMI#

THRMB

GPE#

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

SPKR

CLK14

SUSCLK

AW13

AV12

AU13

AT12

AR13

AP12

AN13

AM12

AL13

AK12

AJ13

AH12

AG13

AF12

AE13

AC13

AB12

AA13

Y12

W13

V12

U13

T12

R13

P12

N13

M14

M12

AD12

N49

M50

K48

TDI

M48

N47

H30

H50

BA41

K50

U41

N43

N45

R41

N41

B30

F32

P50

G29

K30

F34

G33

K36

H36

F36

J31

H34

K28

J35

K14

E13

A13

F14

B14

D14

E15

H14

AU43

AU45

AL45

AL43

AE45

AE43

B28

H32

W41

J47

K32

G37

H38

3

C124

C124

C143

C143

1u/10V_4

1u/10V_4

*1u/10V_4

+1.05V

+3V

R316 *10K_4R316 *10K_4

R319 *10K_4R319 *10K_4

*1u/10V_4

BOARD_ID0

BOARD_ID1

ID1 ID0

0

0

0

1

1

0

11

* : Default

XDP/ITP Debug Test Points

TRST#

TMS

BC_TDI

XDP_TDO

TCK_SCH

T45T45

SWI#

DNBSWON#

T50T50

PCIE_WAKE#_R

EC_SMI#

EC_SCI#

SCH_GPIO0

SCH_GPIO3

BOARD_ID0

BOARD_ID1

ACZ_BITCLK_AUDIO_R

ACZ_SYNC_AUDIO_R

ACZ_RESET#_AUDIO_R

ACZ_SDOUT_AUDIO_R

14M_SCH

SMB_ALERT#

PDAT_SMB

PCLK_SMB

3

R116 *0_4R116 *0_4

T51T51

T48T48

T52T52

T41T41

T53T53

T49T49

R277 33_4R277 33_4

R283 33_4R283 33_4

R284 33_4R284 33_4

R264 33_4R264 33_4

T47T47

T46T46

R308 10K_4R308 10K_4

R337 10K_4R337 10K_4

R338 10K_4R338 10K_4

Del RN8 and Add R337 R338 to SCH

SMBUS rev.c 20090301

2

+1.05V

C153

C153

*1u/10V_4

*1u/10V_4

R317 *10K_4R317 *10K_4

R318 *10K_4R318 *10K_4

Functions

TRST# 4

TMS 4

BC_TDI 4

XDP_TDO 4

TCK_SCH 4

PM_STPCPU# 3

PM_RSTRDY# 22

PLTRST# 14,17,18,19,20,22

PM_RSTWARN 22

DNBSWON# 22

PCIE_WAKE# 17,19

EC_SMI# 22

THERM_ALERT# 4

EC_SCI# 22

SLPIOVR# 6

SB_BEEP 16

ACZ_BITCLK_AUDIO 16

ACZ_SYNC_AUDIO 16

ACZ_RESET#_AUDIO 16

ACZ_SDIN0 16

ACZ_SDOUT_AUDIO 16

DREFCLK# 3

DREFCLK 3

DREFCLK_SS# 3

DREFCLK_SS 3

NB_CLKREQ0# 3

14M_SCH 3

+3V

PDAT_SMB 3,19

PCLK_SMB 3,19

+3V

2

1

C145

C145

10u/6.3V_6

10u/6.3V_6

Change R186 R184 R309 R296

P/N from CS31002JB28 to

CS21002JB34 rev.c 20090301

+3V

SCH_GPIO3

R186 *1K_4R186 *1K_4

R309 *1K_4R309 *1K_4

GPIO3 GPIO0

0

0

1

R184 *1K_4R184 *1K_4

SCH_GPIO0

R296 *1K_4R296 *1K_4

CMC Base Add.

0 FFFB000h

FFFC000h

1

FFFD000h(*)

0

FFFE000h

11

* : Default

Modify JETC pins for Boundary

Scan rev.b 20090205

BC_TDI

XDP_TDO

TMS

TRST#

TCK_SCH

ACZ_SDOUT_AUDIO

EC_SMI#

DNBSWON#

PCIE_WAKE#_R

EC_SCI#

SWI#

NB_CLKREQ0#

R265 56_4R265 56_4

R260 200_4R260 200_4

R259 56_4R259 56_4

R244 1K_4R244 1K_4

R257 *56_4R257 *56_4

R256 56_4R256 56_4

Change R297 from

+3V_S5 to +3V

for SMI# rev.c

20090304

R263 *1K_4R263 *1K_4

R297 10K_4R297 10K_4

R236 10K_4R236 10K_4

R238 1K_4R238 1K_4

R245 *10K_4R245 *10K_4

R239 *10K_4R239 *10K_4

R295 10K_4R295 10K_4

For intel suggest add R295 pull

down 20081218

SCH GFX Clock

SCH GFX SS Clock

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Poulsbo(03_USB/PATA/HD)

Poulsbo(03_USB/PATA/HD)

Poulsbo(03_USB/PATA/HD)

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

1

ZA3

ZA3

ZA3

+1.05V

+3V

+3V_S5

1A

1A

934Sunday, March 08, 2009

934Sunday, March 08, 2009

934Sunday, March 08, 2009

1A

of

of

of

5

Poulsbo(CLG)

4

3

2

1

D D

SMA_DQ[63..0]13 SMA_BS0 13

C C

B B

SMA_DQ0

SMA_DQ1

SMA_DQ2

SMA_DQ3

SMA_DQ4

SMA_DQ5

SMA_DQ6

SMA_DQ7

SMA_DQ8

SMA_DQ9

SMA_DQ10

SMA_DQ11

SMA_DQ12

SMA_DQ13

SMA_DQ14

SMA_DQ15

SMA_DQ16

SMA_DQ17

SMA_DQ18

SMA_DQ19

SMA_DQ20

SMA_DQ21

SMA_DQ22

SMA_DQ23

SMA_DQ24

SMA_DQ25

SMA_DQ26

SMA_DQ27

SMA_DQ28

SMA_DQ29

SMA_DQ30

SMA_DQ31

SMA_DQ32

SMA_DQ33

SMA_DQ34

SMA_DQ35

SMA_DQ36

SMA_DQ37

SMA_DQ38

SMA_DQ39

SMA_DQ40

SMA_DQ41

SMA_DQ42

SMA_DQ43

SMA_DQ44

SMA_DQ45

SMA_DQ46

SMA_DQ47

SMA_DQ48

SMA_DQ49

SMA_DQ50

SMA_DQ51

SMA_DQ52

SMA_DQ53

SMA_DQ54

SMA_DQ55

SMA_DQ56

SMA_DQ57

SMA_DQ58

SMA_DQ59

SMA_DQ60

SMA_DQ61

SMA_DQ62

SMA_DQ63

BG49

BG47

BE45

BC43

BE47

BC47

BC45

BK44

BK42

BG41

BK40

BC41

BG43

BJ43

BJ39

BG39

BC39

BK38

BG37

BK36

BJ37

BG35

BJ35

BC35

BK34

BG31

BG33

BK30

BC33

BJ33

BJ31

BC31

BJ29

BG29

BK28

BC29

BE27

BK26

BG25

BJ25

BC25

BG23

BK22

BJ21

BK24

BJ23

BG21

BC21

BK20

BJ19

BG17

BJ17

BG19

BC19

BC17

BK16

BG15

BC15

BJ13

BK12

BK14

BJ15

BC13

BC11

U15D

U15D

SM_DQ0

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

POULSBO

POULSBO

BC27

SM_BS0

BE25

SM_BS1

BA35

SM_BS2

BG45

SM_CK0

BE11

SM_CK1

BJ45

SM_CK0#

BG11

SM_CK1#

BE39

SM_CKE0

BE37

SM_CKE1

BJ47

SM_DQS0

BJ41

SM_DQS1

BC37

SM_DQS2

BK32

SM_DQS3

BG27

SM_DQS4

BE23

SM_DQS5

BK18

SM_DQS6

BG13

SM_DQS7

BJ27

SM_MA0

BA19

SM_MA1

BA27

SM_MA2

BA25

SM_MA3

BE29

SM_MA4

BC23

SM_MA5

BE31

SM_MA6

BA31

SM_MA7

BA33

SM_MA8

BA29

SM_MA9

BE17

SM_MA10

BE35

SM_MA11

BE33

SM_MA12

BE19

SM_MA13

BA37

SM_MA14

SM_VREF

SM_RAS#

SM_CAS#

SM_WE#

SM_CS0#

SM_CS1#

DDR SYSTEM MEMORY

DDR SYSTEM MEMORY

SM_RCOMPO

SM_RCVENIN

SM_RCVENOUT

BE43

BE21

BA13

BA17

BA23

BA15

SM_RCOMPO

BE13

SM_REVENIN

BA39

SM_RCVENOUT

BE41

SM_VREF_MCH

R107 30.1/F_4R107 30.1/F_4

R111 *Short_4R111 *Short_4

Modify R111

footprint from

RC0402 to SHORT0402

for 0 ohm cost down

rev.c 20090301

SMA_BS1 13

SMA_BS2 13

SMA_CK0 13

SMA_CK1 13

SMA_CK#0 13

SMA_CK#1 13

SMA_CKE0 13

SMA_CKE1 13

SMA_DQS0 13

SMA_DQS1 13

SMA_DQS2 13

SMA_DQS3 13

SMA_DQS4 13

SMA_DQS5 13

SMA_DQS6 13

SMA_DQS7 13

SMA_MA0 13

SMA_MA1 13

SMA_MA2 13

SMA_MA3 13

SMA_MA4 13

SMA_MA5 13

SMA_MA6 13

SMA_MA7 13

SMA_MA8 13

SMA_MA9 13

SMA_MA10 13

SMA_MA11 13

SMA_MA12 13

SMA_MA13 13

SMA_MA14 13

SMA_RAS# 13

SMA_CAS# 13

SMA_WE# 13

SMA_CS#0 13

SMA_CS#1 13

VTERM

+1.8VSUS

R114

R114

10K/F_4

10K/F_4

R105

R105

10K/F_4

10K/F_4

15mils/10mils

C110

C110

0.1u/10V_4

0.1u/10V_4

DDR_VREF

R106 *0_6R106 *0_6

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Poulsbo(04_MEM)

Poulsbo(04_MEM)

Poulsbo(04_MEM)

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

PROJECT :

ZA3

ZA3

ZA3

1A

1A

1A

10 34Sunday, March 08, 2009

10 34Sunday, March 08, 2009

10 34Sunday, March 08, 2009

of

of

1

of

5

hexainf@hotmail.com

Poulsbo(CLG)

+1.05V

C142

C142

0.1u/10V_4

0.1u/10V_4

4

C144

C144

0.1u/10V_4

0.1u/10V_4

C154

C154

0.1u/10V_4

0.1u/10V_4

C132

C132

2.2u/6.3V_6

2.2u/6.3V_6

3

2

1

D D

+1.5V

C169

C169

C170

C170

C171

1u/10V_4

1u/10V_4

D9

D9

D11

D11

C171

1u/10V_4

1u/10V_4

VCC5REFSUS

C150 1u/10V_4C150 1u/10V_4

VCC5REF

C187 1u/10V_4C187 1u/10V_4

5

1u/10V_4

1u/10V_4

C C

+1.5V

C164

C164

1u/10V_4

1u/10V_4

+3V

C117

C117

0.1u/10V_4

0.1u/10V_4

R123 10_4R123 10_4

R177 10_4R177 10_4

+1.5V

Modify R126

footprint from

RC0603 to

SHORT0603 for 0

ohm cost down

rev.c 20090301

2 1

*BZX584C5V6

*BZX584C5V6

2 1

*BZX584C5V6

*BZX584C5V6

R126 *Short_6R126 *Short_6

+3V_S5

B B

+5V_S5

+3V

+5V

A A

C168

C168

1u/10V_4

1u/10V_4

+1.5V

+1.5V

+3V

VCC5REFSUS

VCC5REF

VCCADPLLB

C146 1u/10V_4C146 1u/10V_4

C147 1u/10V_4C147 1u/10V_4

C133 1u/10V_4C133 1u/10V_4

+1.05V

AD34

AD32

AB34

AB32

AB38

AA37

AW41

AY42

R33

R31

R29

R27

R25

R23

R21

R19

R17

R15

P34

P32

N33

N31

M38

M36

M34

M32

P38

P36

Y34

Y32

W37

Y20

U15E

U15E

VCC_70

VCC15_1

VCC15_2

VCC15_3

VCC15_4

VCC15_5

VCC15_6

VCC15_7

VCC15_8

VCC15_9

VCC15_10

VCC15_11

VCC15_12

VCC15_13

VCC15_14

VCC15_15

VCC15_16

VCC15_17

VCC15_18

RESERVED10

RESERVED9

VCC15USB_1

VCC15USB_2

VCC15USB_3

VCC15USB_4

VCC15USB_5

VCC15USB_6

RESERVED12

RESERVED11

RESERVED13

VCCAPCIEBG

VSSAPCIEBG

VCC5REFSUS

AA41

V26

V24

VCC_78

K34

V32

V30

V28

VCC_75

VCC_76

VCC_77

VCCAPCIEPLL

VCCADPLLB

VCC5REF_1

AE39

AN49

AG39

Y18

Y16

V34

VCC_71

VCC_72

VCC_73

VCC_74

VCCAUSBBGSUS

VCCADPLLA

AE41

AK32

AK30

AK28

AK26

AK24

V16

VCC_61

VCC_62

VCC_82

VCC_120

VCC_121

VCCAUSBPLL

VCCDHPLL

VCCAHPLL

VSSAUSBBGSUS

J11

BB10

BA11

AC39

AC41

4

AM24

AM22

AM20

AM18

AM16

AK34

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC33_1

VCC33_2

VCC33_3

VCC33RTC

VCCHDA_1

VCCHDA_2

VCC33_16

A45

K12

N29

N27

N25

M16

VCCRTC

VCC_HDA

VCCAUSBPLL

VCCAHPLL

C179 1u/10V_4C179 1u/10V_4

C152 0.1u/10V_4C152 0.1u/10V_4

C115 1u/10V_4C115 1u/10V_4

AM34

AM32

AM30

AM28

AM26

N23

VCC_53

VCC33_4

VCC_52

VCC33_5

N21

AB26

AB24

AB22

AB20

VCC_49

VCC_50

VCC_51

VCC33_7

N17

L18 BLM18PG121SN1/2A/120ohm_6L18 BLM18PG121SN1/2A/120ohm_6

L17 BLM18PG121SN1/2A/120ohm_6L17 BLM18PG121SN1/2A/120ohm_6

VCC_45

VCC_46

VCC_47

VCC_48

VCC33_6

VCC33_8

VCC33_9

VCC33_10

VCC33_11

VCC33_12

N19

N15

M30

M28

M26

M24

L14 BLM18PG121SN1/2A/120ohm_6L14 BLM18PG121SN1/2A/120ohm_6

AB28

VCC_44

VCC33_13

M22

AB30

M20

+3V

AD16

VCC_43

VCC33_14

M18

AD20

AD18

VCC_41

VCC_42

VCC33_15

R39

C175

C175

1u/10V_4

1u/10V_4

AD24

AD22

VCC_38

VCC_39

VCC_40

VCC33SUS_1

VCC33SUS_2

VCC33SUS_3

T38

U37

+3V

AF22

AF20

AF18

AF16

AD30

AD28

AD26

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC

VCC

VCCP33USBSUS_1

VCCP33USBSUS_2

RESERVED16

RESERVED17

RESERVED15

VCCP33USBSUS_3

Y38

N37

N35

W39

AA39

AB36

AC37

SCH_VCCSUS3

C176

C176

1u/10V_4

1u/10V_4

3

AF30

AF28

AF26

AF24

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCCSM_40

VCCSM_41

VCCSM_42

RESERVED14

AP22

AP20

AP18

+3V

+1.5V

+1.5V

C177

C177

1u/10V_4

1u/10V_4

AK22

AK20

AK18

AK16

AH34

AH32

AH30

AH28

AH26

AH24

AH22

AH20

AH18

AH16

AF34

AF32

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCCSM_25

VCCSM_26

VCCSM_27

VCCSM_28

VCCSM_29

VCCSM_30

VCCSM_31

VCCSM_32

VCCSM_33

VCCSM_34

VCCSM_35

VCCSM_36

VCCSM_37

VCCSM_38

VCCSM_39

AT30

AT28

AT26

AT24

AT22

AT20

AT18

AT16

AP34

AP32

AP30

AP28

AP26

AP24

L16 BLM18PG121SN1/2A/120ohm_6L16 BLM18PG121SN1/2A/120ohm_6

AV18

AV16

C163

C163

0.1u/10V_4

0.1u/10V_4

Change C163 C136

connect

SCH_VCCSUS3 power

net 20090223

AB18

AB16

Y30

Y28

Y26

Y24

Y22

T34

T32

T30

T28

T26

T24

T22

T20

T18

T16

VCC_9

VCC_8

VCC_7

VCC_6

VCC_5

VCC_4

VCC_3

VCC_2

VCC_1

VCC_11

VCCSM_5

VCCSM_6

VCCSM_7

VCCSM_21

VCCSM_22

VCCSM_23

VCCSM_24

AV32

AV30

AV28

AV26

AV24

AV22

AV20

C136

C136

1u/10V_4

1u/10V_4

VCCSM_4

VCCSM_3

AV34

VCC_10

VCCSM_1

VCCSM_2

AV36

AW17

+3V_S5

2

VCC_69

VCCSM_10

AW37

VCC_68

VCCSM_108

AW19

VCC_67

VCCSM_107

AW21

V22

V20

V18

VCC_63

VCC_64

VCC_65

VCC_66

VCC_79

VCC_80

VCC_81

VCCLVDS_101

VCCLVDS_100

VCCLVDS_1

VCCLVDS_2

VCCLVDS_3

VCCPCIE_4

VCCPCIE_5

VCCPCIE_6

VCCPCIE_7

VCCPCIE_8

VCCPCIE_9

VCCPCIE_1

VCCPCIE_2

VCCPCIE_3

VCCPCIE_100

VCCPCIE_101

VCCSDVO_110

VCCSDVO_100

VCCSDVO_101

VCCSDVO_103

VCCSDVO_106

VCCSDVO_105

VCCSM_100

VCCSM_101

VCCSM_102

VCCSM_103

VCCSM_104

VCCSM_105

VCCSM_106

AP16

AW35

AW33

AW31

AW29

AW27

AW25

AW23

+1.8VSUS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

+1.5V

C134

C134

1u/10V_4

1u/10V_4

+1.5V

AG37

AF38

AF36

AE37

AD36

AT34

AT32

AR37

AP38

AP36

AN37

AU37

AT38

AT36

AM36

AV38

AK36

AJ37

AH38

AH36

AK38

AL37

VCCSM_43

POULSBO

POULSBO

+1.8VSUS

C126

C126

10u/6.3V_6

10u/6.3V_6

Poulsbo(05_Power)

Poulsbo(05_Power)

Poulsbo(05_Power)

C118

C118

1u/10V_4

1u/10V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

C123

C123

1u/10V_4

1u/10V_4

C125

C125

1u/10V_4

1u/10V_4

C122

C122

C151

C151

1u/10V_4

1u/10V_4

1u/10V_4

1u/10V_4

C116

C116

1u/10V_4

1u/10V_4

ZA3

ZA3

ZA3

1A

1A

11 34Sunday, March 08, 2009

11 34Sunday, March 08, 2009

11 34Sunday, March 08, 2009

1

1A

of

of

of

Loading...

Loading...