5

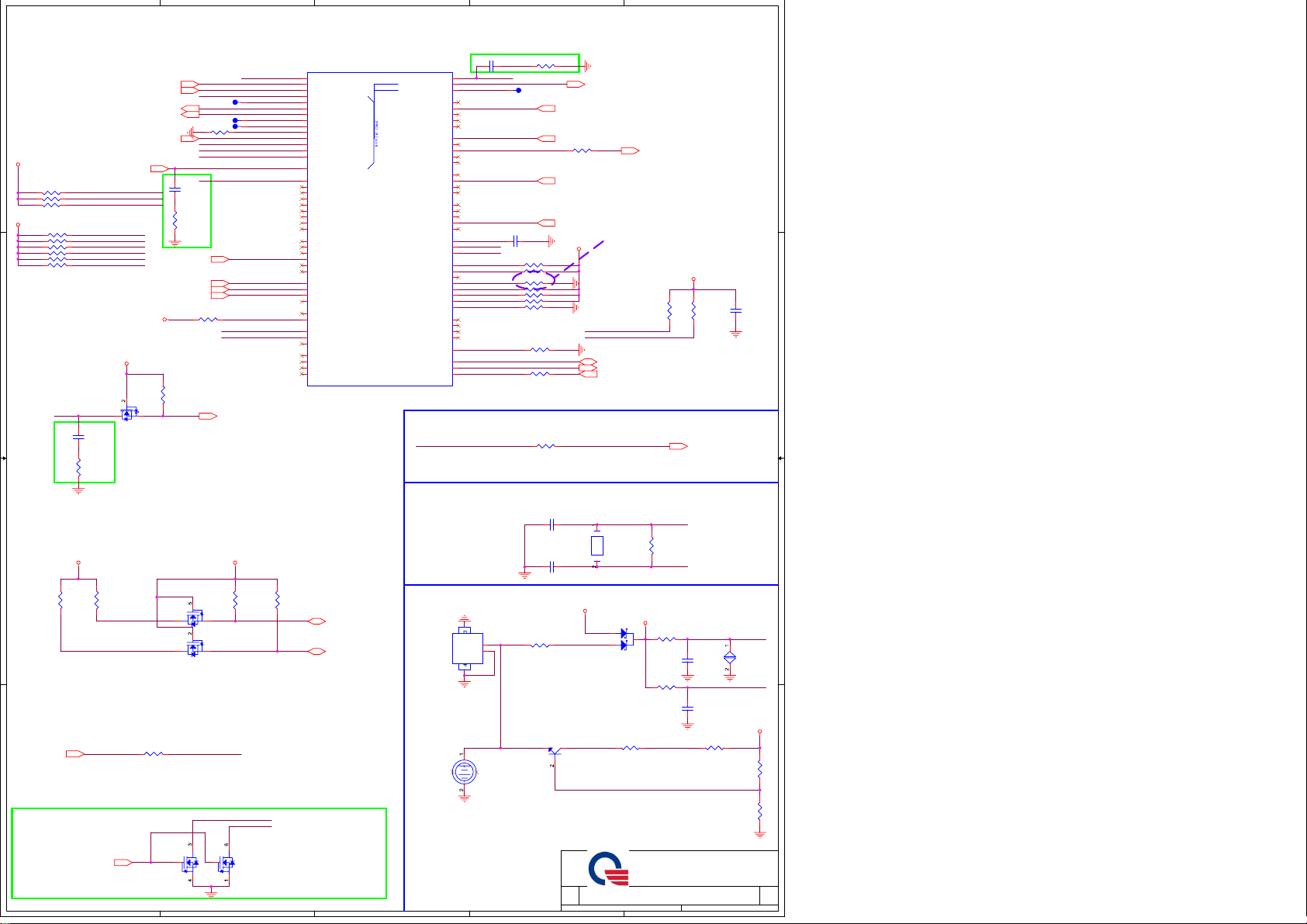

TPM@ : TPM

GS@ : G-SENSOR

CB@ : Cloud book SKU

EJ@ : EJ sereies SKU

KBL@ : keyboard backlight

NVL@ : none LED panel boost

VL@ : LED panel boost

EC@ : EMMC

TPC@ : Type C function

w/o GS@: stuff with none GS sku

SSD@ : SATA interface SSD

PSD@ : PCIE interfance SSD

ODD@ : ODD function

P19

P20

D

C

B

A

D

C

B

A

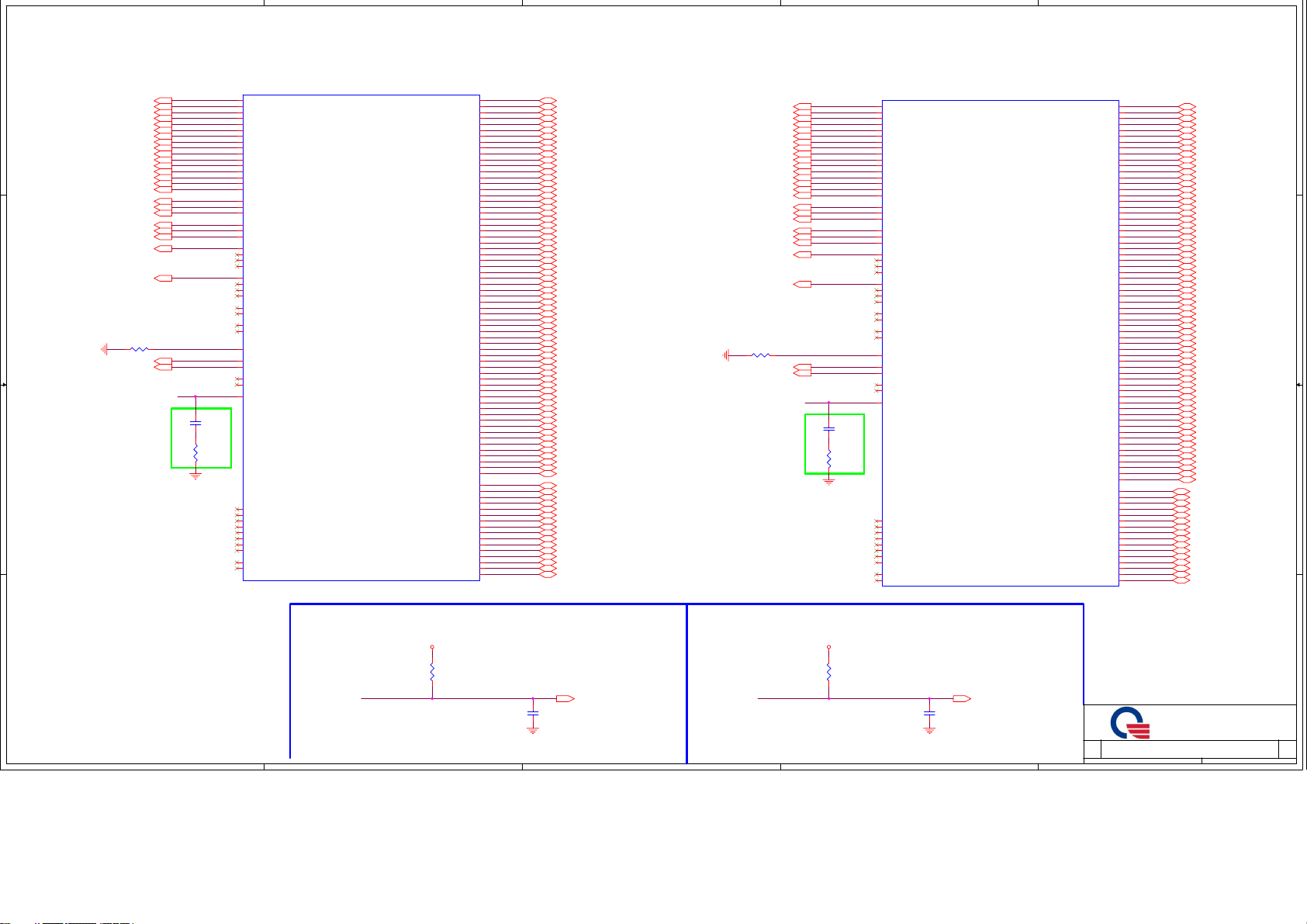

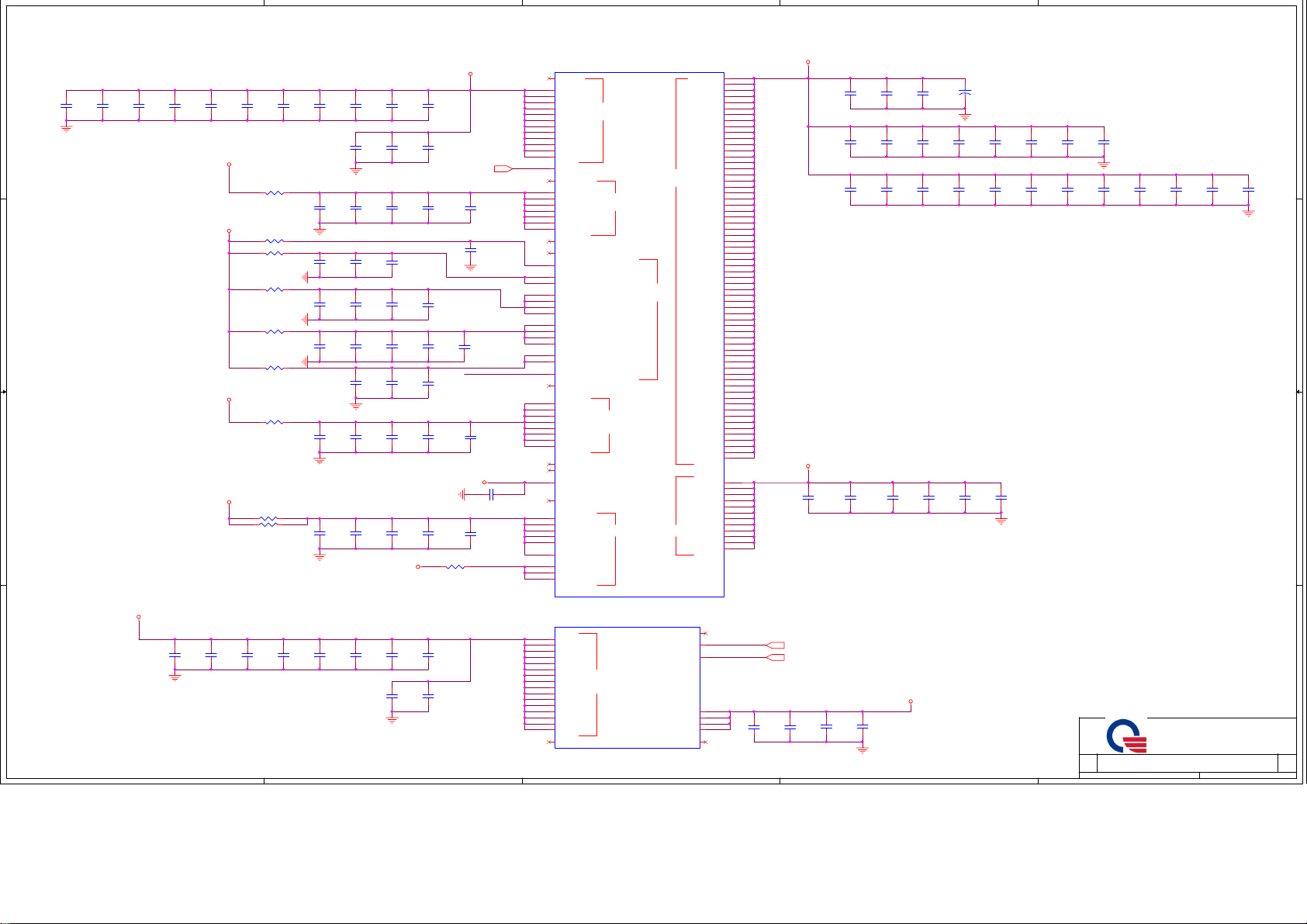

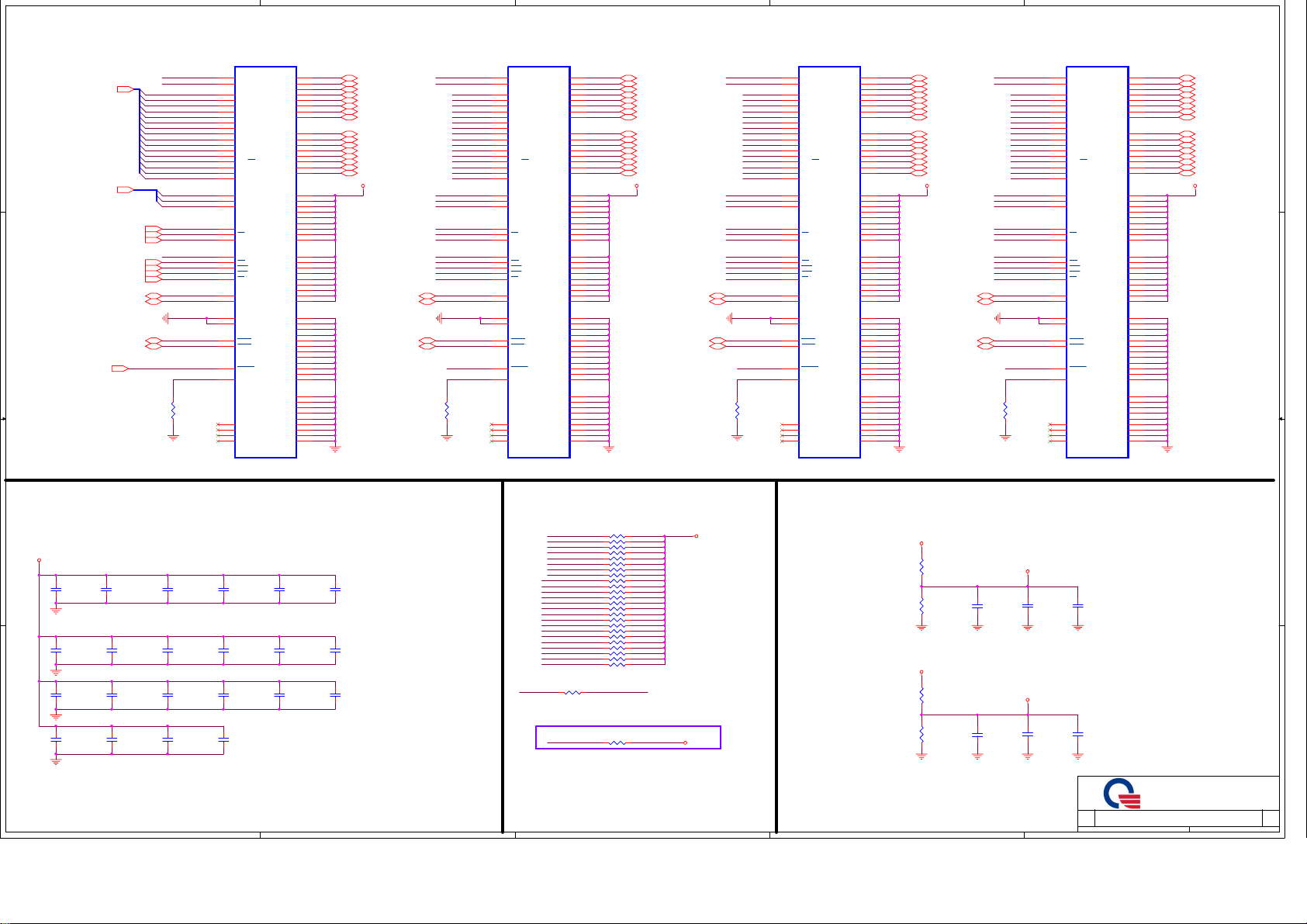

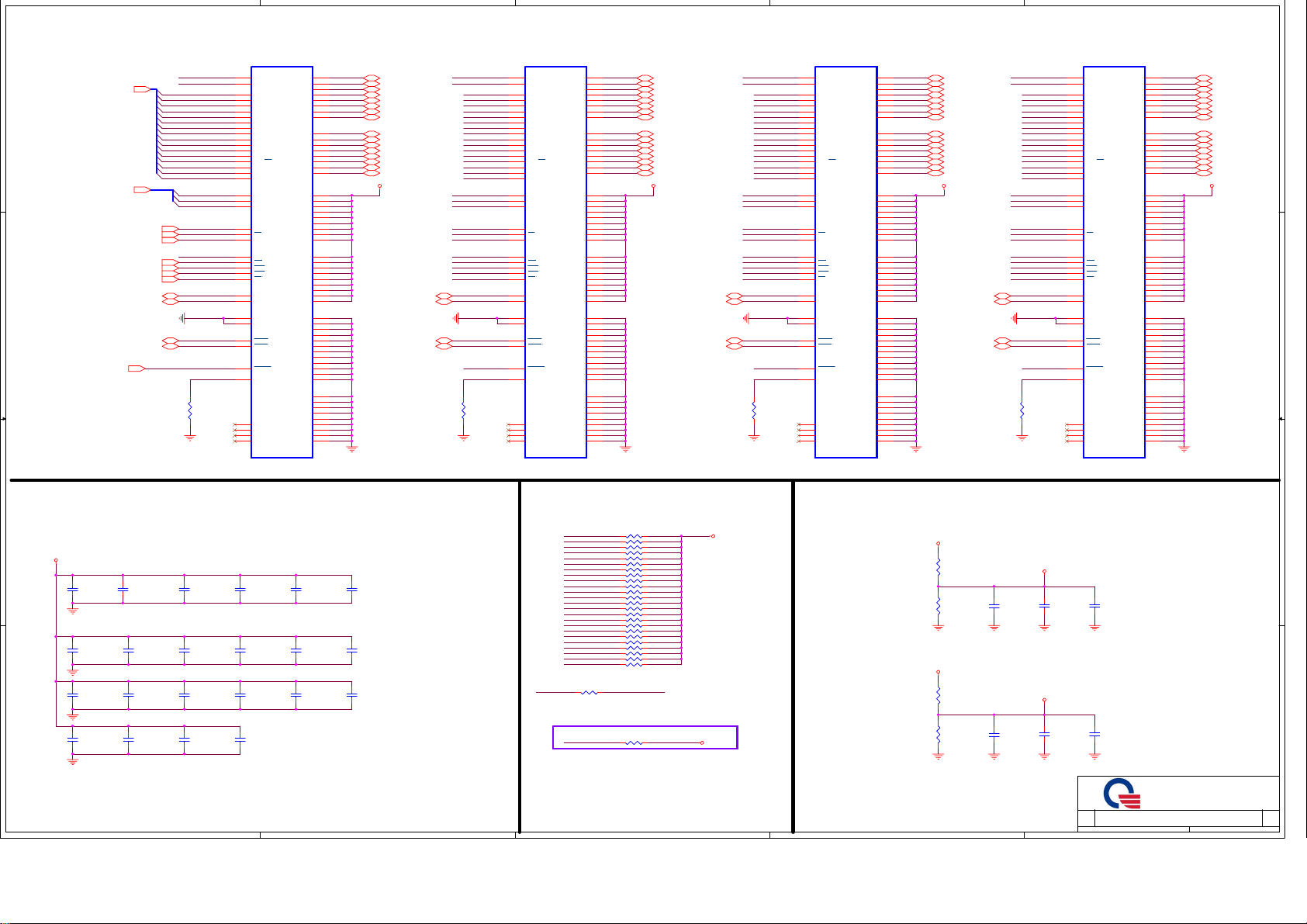

Dual Channel DDR3L

1867 MHz MAX

SATA0

SATA1

EMMC

USB2-2

USB2-3

USB2-4

USB2-5

USB2-6

USB2-7

DDR3L-2GB

Memory down CHA

P10

DDR3L-2GB

Memory down CHB

P11

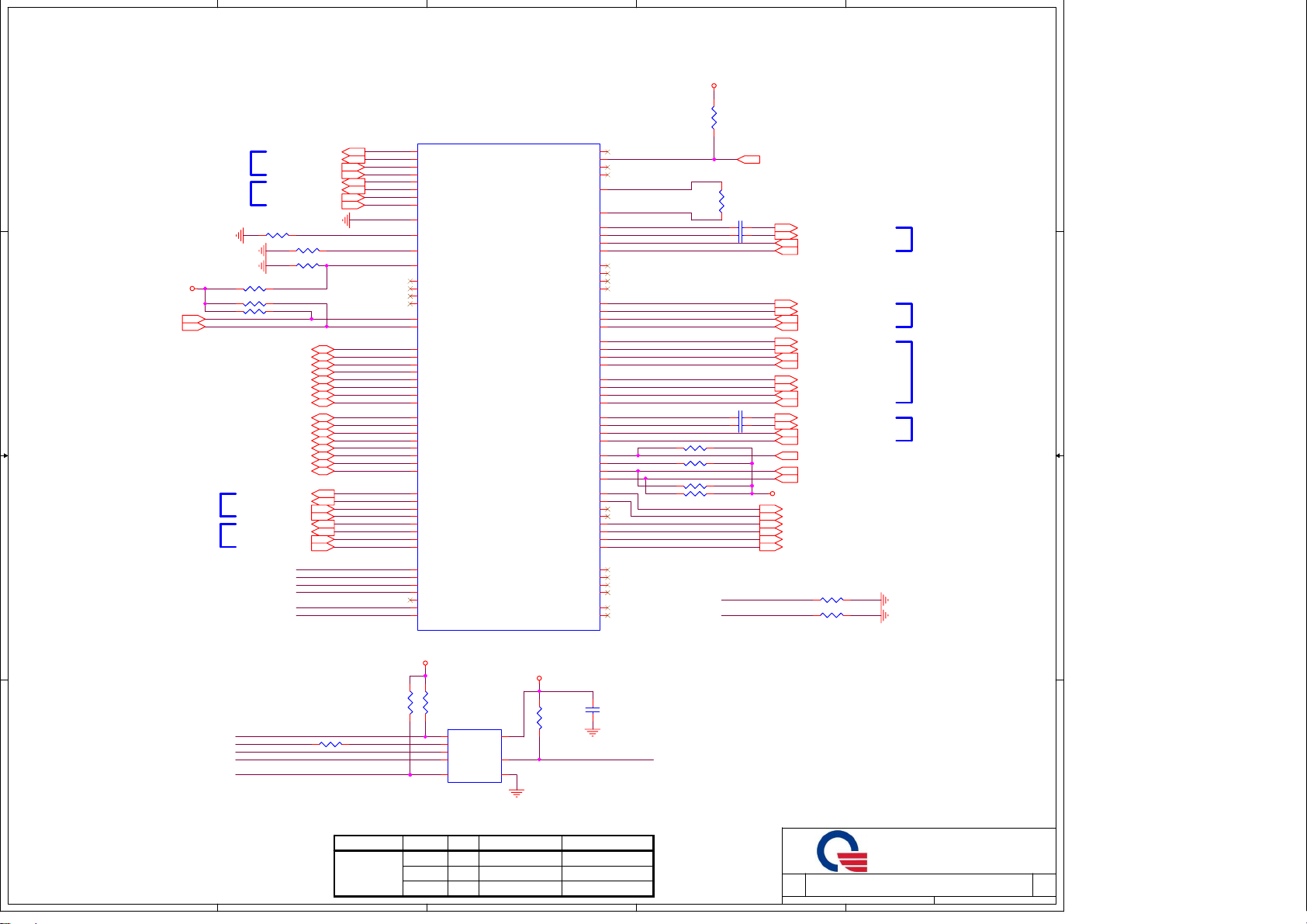

Apollo Lake - 6W

(BROXTON-P)

MCP 1296 pins

EDP

eDP

DDI0

DP

SMB

eDP Conn.

HDMI Conn.

P12

P13

USB3.0 Port

Type C port

SATA - HDD

SATA SSD M.2

32GB/64GB

USB2.0 Port 1

USB2.0 Port 2

Blue Tooth

Touch Screen

CCD(Camera)

P16

P16

P12

P19

P19

P17

P12

P12

SATA

EMMC5.0

USB2.0

PCIE-0/1

USB3-0 + USB2-0

USB3.0/2.0 USB3-1 + USB3-2

USB2-1

PCI-E

PCIE-3

PCIE-2

M.2 NGFF

WLAN+BT

P17

RJ45

P15

Cardreader

RTL8411B-CG

10/100/1G

P15

X'TAL 25MHz

X'TAL

32.768KHz

X'TAL 19.2MHz

I2C_0

SPI

SPI ROM 8M

P3

P20

Integrated PCH

RTC

P2~P8

IHDA

LPC

EC

IT8987

ODD bridge

ASM1153

P16

P6

Azalia

D-MIC AUDIO CODEC

P14

ALC255

P15

P22

BATTERY

P14

TPM(NPCT650)

P16

+1.8V_S5 / +1.24VSUS/+1.5V

P28

Quanta Computer Inc.

Date: Tuesday, March 21, 2017 Sheet

3

2b

1

P28

G-sensor

BQ24737RGRR

Batery Charger

RT8231BGQW

+1.35VSUS

G5719CTB1U

G5719CTB1U

G9661MF11U

P25

SY8286 & SY8288

+3VPCU/+5VPCU

M5671RE1U

+1.05V

P23

P24

ISL95859HRTZ-T Thermal Protection

+VCCGI / +VNN

HP JACK Speaker K/B Con. SPI ROM 1M Touch PAD Fan module

(PWM signal)

P14

P14

P18

P20

P18

P18

P26~27

P29

Discharger

PROJECT :

Size Document Number

Block Diagram

ZAJ

Rev

3A

4

3

2

1

01

ZAJ/Z8P/Z8PA SYSTEM BLOCK DIAGRAM

BOM

5 4 3 2 1

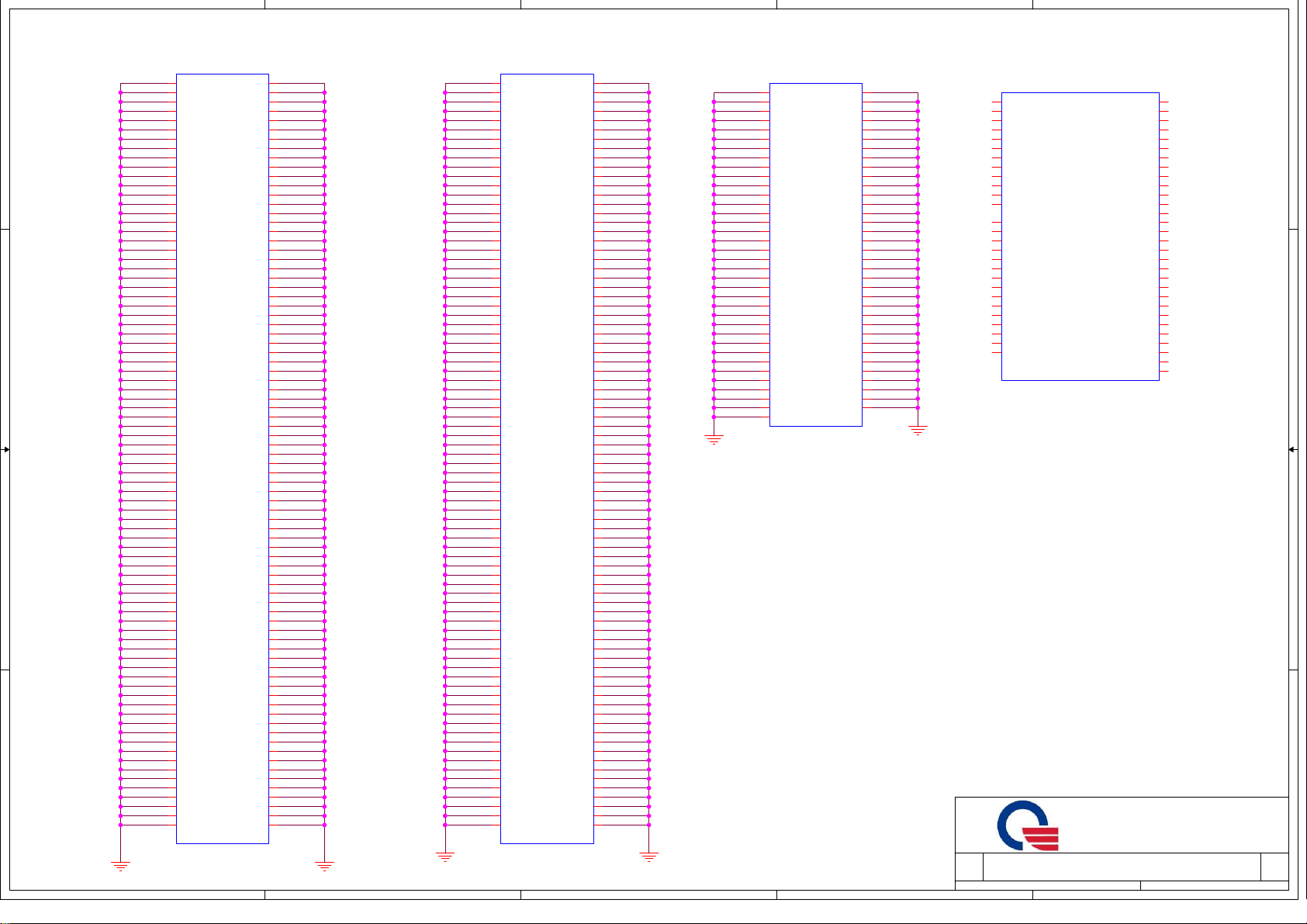

Section 2 of 12

DDR3L_ CH1_CB0_LPD DR3_NC

DDR3L_ CH1_CB1_LPD DR3_NC

DDR3L_ CH1_CB2_LPD DR3_NC

DDR3L_ CH1_CB3_LPD DR3_NC

DDR3L_ CH1_CB4_LPD DR3_NC

DDR3L_ CH1_CB5_LPD DR3_NC

DDR3L_ CH1_CB6_LPD DR3_NC

DDR3L_ CH1_CB7_LPD DR3_NC

DDR3L_CH1_DQSP8_LPDDR 3_NC

DDR3L_ CH1_DQSN8_LP DDR3_N C

Section 1 of 12

DDR3L_CH0_CB0_ LPDDR3 _NC

DDR3L_CH0_CB1_ LPDDR3 _NC

DDR3L_CH0_CB2_ LPDDR3 _NC

DDR3L_CH0_CB3_ LPDDR3 _NC

DDR3L_CH0_CB4_ LPDDR3 _NC

DDR3L_CH0_CB5_ LPDDR3 _NC

DDR3L_CH0_CB6_ LPDDR3 _NC

DDR3L_CH0_CB7_ LPDDR3 _NC

DDR3L_ CH0_DQ SP8_LPDDR3_NC

DDR3L_ CH0_DQSN 8_LPDDR 3_NC

DDR3L_C H 1_DQSP0_LPDDR3 _CH1_DQS PA0

DDR3L_ CH1_D QSN0_L PDDR3_ CH1_DQS NA0

DDR3L_C H 1_DQSP1_LPDDR3 _CH1_DQS PA1

DDR3L_ CH1_D QSN1_L PDDR3_ CH1_DQS NA1

DDR3L_C H 1_DQSP2_LPDDR3 _CH1_DQS PA2

DDR3L_ CH1_D QSN2_L PDDR3_ CH1_DQS NA2

DDR3L_C H 1_DQSP3_LPDDR3 _CH1_DQS PA3

DDR3L_ CH1_D QSN3_L PDDR3_ CH1_DQS NA3

DDR3L_C H 1_DQSP4_LPDDR3 _CH1_DQS PB0

DDR3L_ CH1_D QSN4_L PDDR3_ CH1_DQS NB0

DDR3L_C H 1_DQSP5_LPDDR3 _CH1_DQS PB1

DDR3L_ CH1_D QSN5_L PDDR3_ CH1_DQS NB1

DDR3L_C H 1_DQSP6_LPDDR3 _CH1_DQS PB2

DDR3L_ CH1_D QSN6_L PDDR3_ CH1_DQS NB2

DDR3L_C H 1_DQSP7_LPDDR3 _CH1_DQS PB3

DDR3L_ CH1_D QSN7_L PDDR3_ CH1_DQS NB3

MB_DRAMRST# [1 1]

DDR3L_ CH0_DQSP0_L PD DR3_CH0 _DQSPA0

DDR3L_ CH0_DQSN 0_LPDD R3_CH 0_DQSNA0

DDR3L_ CH0_DQSP1_L PD DR3_CH0 _DQSPA1

DDR3L_ CH0_DQSN 1_LPDD R3_CH 0_DQSNA1

DDR3L_ CH0_DQSP2_L PD DR3_CH0 _DQSPA2

DDR3L_ CH0_DQSN 2_LPDD R3_CH 0_DQSNA2

DDR3L_ CH0_DQSP3_L PD DR3_CH0 _DQSPA3

DDR3L_ CH0_DQSN 3_LPDD R3_CH 0_DQSNA3

DDR3L_ CH0_DQSP4_L PD DR3_CH0 _DQSPB0

DDR3L_ CH0_DQSN 4_LPDD R3_CH 0_DQSNB0

DDR3L_ CH0_DQSP5_ L PDDR3_CH 0_DQSPB1

DDR3L_ CH0_DQSN 5_LPDD R3_CH 0_DQSNB1

DDR3L_ CH0_DQSP6_L PD DR3_CH0 _DQSPB2

DDR3L_ CH0_DQSN 6_LPDD R3_CH 0_DQSNB2

DDR3L_ CH0_DQSP7_L PD DR3_CH0 _DQSPB3

DDR3L_ CH0_DQSN 7_LPDD R3_CH 0_DQSNB3

Rev

3A

Size Document Num ber

BXTP (MEMORY)

Date: Tuesday, March 21, 201 7 Sheet 2 of 34

5 4 3 2 1

Quanta Computer Inc.

PROJECT : ZAJ

C103 C101

0.1u/1 6V _4 0.1u/1 6V _4

MB_DRAMRST#

MA_ DRAMRST#

MA_DRAMRST# [ 10 ]

DRAMRST-MA DRAMRST-MB

+1.3 5VSUS +1.35VSU S

R106 R105

CPU

CPU

1K_1 %_ 4 1K_1 %_ 4

02

M_B _DQ0 [11]

M_B _DQ1 [11]

M_B _DQ2 [11]

M_B _DQ3 [11]

M_B _DQ4 [11]

M_B _DQ5 [11]

M_B _DQ6 [11]

M_B _DQ7 [11]

M_B _DQ8 [11]

M_B _DQ9 [11]

M_B _DQ10 [11 ]

M_B _DQ11 [11 ]

M_B _DQ12 [11 ]

M_B _DQ13 [11 ]

M_B _DQ14 [11 ]

M_B _DQ15 [11 ]

M_B _DQ16 [11 ]

M_B _DQ17 [11 ]

M_B _DQ18 [11 ]

M_B _DQ19 [11 ]

M_B _DQ20 [11 ]

M_B _DQ2 1 [11]

M_B _DQ22 [11 ]

M_B _DQ23 [11 ]

M_B _DQ24 [11 ]

M_B _DQ25 [11 ]

M_B _DQ26 [11 ]

M_B _DQ27 [11 ]

M_B _DQ28 [11 ]

M_B _DQ29 [11 ]

M_B _DQ30 [11 ]

M_B _DQ31 [11 ]

M_B _DQ32 [11 ]

M_B _DQ33 [11 ]

M_B _DQ34 [11 ]

M_B _DQ35 [11 ]

M_B _DQ36 [11 ]

M_B _DQ37 [11 ]

M_B _DQ38 [11 ]

M_B _DQ39 [11 ]

M_B _DQ40 [11 ]

M_B _DQ41 [11 ]

M_B _DQ42 [11 ]

M_B _DQ43 [11 ]

M_B _DQ44 [11 ]

M_B _DQ45 [11 ]

M_B _DQ46 [11 ]

M_B _DQ47 [11 ]

M_B _DQ48 [11 ]

M_B _DQ49 [11 ]

M_B _DQ50 [11 ]

M_B _DQ51 [11 ]

M_B _DQ52 [11 ]

M_B _DQ53 [11 ]

M_B _DQ54 [11 ]

M_B _DQ55 [11 ]

M_B _DQ56 [11 ]

M_B _DQ57 [11 ]

M_B _DQ58 [11 ]

M_B _DQ59 [11 ]

M_B _DQ60 [11 ]

M_B _DQ61 [11 ]

M_B _DQ62 [11 ]

M_B _DQ63 [11 ]

M_B_ DQS0 [11 ]

M_B_ DQS #0 [11]

M_B_ DQS1 [11 ]

M_B_ DQS #1 [11]

M_B_ DQS2 [11 ]

M_B_ DQS #2 [11]

M_B_ DQS3 [11 ]

M_B_ DQS #3 [11]

M_B_ DQS4 [11 ]

M_B_ DQS #4 [11]

M_B_ DQS5 [11 ]

M_B_ DQS #5 [11]

M_B_ DQS6 [11 ]

M_B_ DQS #6 [11]

M_B_ DQS7 [11 ]

M_B_ DQS #7 [11]

M A A 0 BG50

M_A_A1 BG51

M_A_A2 BH51

M_A_A3 BD41

M_A_A4 BE41

M A A5 BJ 52

M A A 6 BG53

M_A_A7 BG55

M_A_A8 BH53

M_A_A9 BG52

M A A 10 BH49

M A A 11 BH55

M_A_A12 BG54

M_A_A13 BG46

M_A_A14 BG56

M_A_A15 BG57

BJ48

BG49

BH57

BH47

BG47

BG48

AR43

AT43

BB41

BA41

BH61

BH60

BH58

BJ58

AW43

AW41

AT34

AR35

MEM CH0 RCO MP

AV34

BD45

BE45

BB48

BD48

MA_ DRAMRST#

AR34

C102

0.1 u/1 6V_ 4

R102

10_5 %_ 4

AW48

AW47

BB43

AW45

AV48

AV47

BD43

BA45

BD47

BB47

AY62 M A DQ0

AY61 M_A_DQ1

BE62 M_A_DQ2

BG62 M_A_DQ3

BD63 M_A_DQ4

AW62

M A

DQ5

AW63

M A

DQ6

BD62 M_A_DQ7

AV59 M_A_DQ8

AU63 M_A_DQ9

AU62 M A DQ10

AV58 M A DQ11

AV57 M_A_DQ12

AT55 M_A_DQ13

AT54 M_A_DQ14

AY59 M_A_DQ15

AY57 M A DQ16

BB57 M_A_DQ17

BD59 M_A_DQ18

BF59 M_A_D Q19

AV54 M_A_DQ20

AY55 M A D Q21

AV52 M_A_DQ22

BD58 M_A_DQ23

BE56 M_A_DQ24

BD54 M_A_DQ25

BF58 M_A_D Q26

BE50 M A DQ27

BD50 M_A_DQ28

BB50 M_A_DQ29

BA50 M_A_DQ30

BB54 M_A_DQ31

AR39 M A DQ32

AV37 M_A_DQ33

AW37

M_A_DQ34

AR37 M_A_DQ35

AT37 M_A_DQ36

AT41 M A DQ37

AR41 M A DQ38

AW35

M_A_DQ39

BJ44 M_ A_DQ40

BG39 M_A_DQ41

BG40 M A DQ42

BJ40 M A DQ43

BG43 M_A_DQ44

BG44 M_A_DQ45

BH45 M_A_DQ46

BH41 M_A_DQ47

BA34 M A DQ48

BE34 M A DQ49

BD34 M_A_DQ50

BD37 M_A_DQ51

BB37 M_A_DQ52

BE39 M A DQ53

BD39 M A DQ54

BB34 M_A_DQ55

BJ38 M_ A_DQ56

BG34 M_A_DQ57

BG33 M_A_DQ58

BH33 M A DQ59

BG38 M A DQ60

BH37 M_A_DQ61

BG37 M_A_DQ62

BJ34 M_ A_DQ63

BB63

M A DQ S0

BC62 M _A_DQS #0

AT59

M_A _D QS1

AT58 M_A _DQS#1

BB59

M_A _DQ S2

BB58 M A DQS #2

BD52

M A DQS 3

BB52 M_A_DQ S#3

AV39

M_A _DQ S4

AW39 M_A _DQS#4

BJ42

M A DQS5

BG42 M A DQS#5

BB35

M_A _DQ S6

BD35 M _A_DQS #6

BG36

M _A_ DQS 7

BH35 M _A_DQS #7

U21B APL B GA 1296P

DDR3L_C H 1_MA0_LPDDR3_CH 1_CAB7 DDR3L _CH1_DQ0_L PDDR3 _CH1_DQ A0

DDR3L_C H 1_MA1_LPDDR3_CH 1_CAB9 DDR3L _CH1_DQ1_L PDDR3 _CH1_DQ A1

DDR3L_C H 1_MA2_LPDDR3_CH 1_CAB5 DDR3L _CH1_DQ2_L PDDR3 _CH1_DQA2

DDR3L_CH1_MA3_LPDDR3 _NC

DDR3L_ CH1_DQ3_L PDDR3_C H1_DQA3

DDR3L_CH1_MA4_LPDDR3 _NC

DDR3L_ CH1_DQ4_L PDDR3_C H1_DQA4

DDR3L_C H 1_MA5_LPDDR3_CH 1_CAA2 DDR3L _CH1_DQ5_L PDDR3 _CH1_DQ A5

DDR3L_C H 1_MA6_LPDDR3_CH 1_CAA0 DDR3L _CH1_DQ6_L PDDR3 _CH1_DQ A6

DDR3L_C H 1_MA7_LPDDR3_CH 1_CAA3 DDR3L _CH1_DQ7_L PDDR3 _CH1_DQ A7

DDR3L_C H 1_MA8_LPDDR3_CH 1_CAA1 DDR3L _CH1_DQ8_L PDDR3 _CH1_DQ A8

DDR3L_C H 1_MA9_LPDDR3_CH 1_CAA4 DDR3L _CH1_DQ9_L PDDR3 _CH1_DQ A9

DDR3L_ CH1_MA10_LPDD R3_CH1 _CAB6 DDR3L _CH1_DQ10_LPD D R3_CH 1_DQA10

DDR3L_ CH1_MA11_LPDD R3_CH1 _CAA6 DDR3L_CH1_D Q 11_LPDDR3_CH 1_DQA11

DDR3L_ CH1_MA12_LPDD R3_CH1 _CAA5 DDR3L _CH1_DQ12_LPD D R3_CH 1_DQA12

DDR3L_ CH1_MA13_LPDD R3_CH1 _CAB0 DDR3L _CH1_DQ13_LPD D R3_CH 1_DQA13

DDR3L_ CH1_MA14_LPDD R3_CH1 _CAA8 DDR3L _CH1_DQ14_LPD D R3_CH 1_DQA14

DDR3L_ CH1_MA15_LPDD R3_CH1 _CAA9 DDR3L _CH1_DQ15_LPD D R3_CH 1_DQA15

DDR3L_ CH1_DQ16_LPD D R3_CH1_DQA16

DDR3L_C H 1_BA0_LPDDR3_CH 1_CAB2 DDR3L_ CH1_DQ17_LPD D R3_CH1_DQA17

DDR3L_C H 1_BA1_LPDDR3_CH 1_CAB8 DDR3L_ CH1_DQ18_LPD D R3_CH1_DQA18

DDR3L_C H 1_BA2_LPDDR3_CH 1_CAA7 DDR3L_ CH1_DQ19_LPD D R3_CH1_DQA19

DDR3L_ CH1_DQ20_LPD D R3_CH1_DQA20

DDR3L_ CH1_C AS_N_LPDD R3_CH 1_CAB1 DDR3L_ CH1_DQ21_LPD D R3_CH1_DQA21

DDR3L_ CH1_R AS_N_LPDD R3_CH 1_CAB3 DDR3L_ CH1_DQ22_LPD D R3_CH1_DQA22

DDR3L_ CH1_W E_N_ LPDDR3 _CH1_C AB4 DDR3L_ CH1_DQ23_LPD D R3_CH1_DQA23

DDR3L_ CH1_DQ24_LPD D R3_CH1_DQA24

DDR3L_ CH1_CS0_N_LPDD R3_CH1_ CS0A_N DDR3L_ CH1_DQ25_LPD D R3_CH1_DQA25

DDR3L_NC_LPDDR3_CH1 _CS1A_ N

DDR3L_ CH1_DQ26_LPD D R3_CH1_DQA26

DDR3L_NC_LPDDR3_CH1 _CS0B_ N

DDR3L_ CH1_DQ27_LPD D R3_CH1_DQA27

DDR3L_ CH1_CS1_N_LPDD R3_CH1_ CS1B_N DDR3L_ CH1_DQ28_LPD D R3_CH1_DQA28

DDR3L_ CH1_DQ29_LPD D R3_CH1_DQA29

DDR3L_ CH1_CKE0_LPDD R3_CH1_C KE0A DDR3L_ CH1_DQ30_LPD D R3_CH1_DQA30

DDR3L_ CH1_CKE1_LPDD R3_CH1_C KE1A DDR3L_ CH1_DQ31_LPD D R3_CH1_DQA31

DDR3L_NC_LPDDR3_CH1 _CKE0B

DDR3L_ CH1_DQ32_L PDDR3_ CH1_DQB 0

DDR3L_NC_LPDDR3_CH1 _CKE1B

DDR3L_ CH1_DQ33_L PDDR3_ CH1_DQB 1

DDR3L_CH1 _DQ34_LPDDR 3_CH1_D QB2

DDR3L_ CH1_ ODT0_L PDDR3_C H1_ODT A DDR3L_ CH1_DQ35_L PDDR3_ CH1_DQB 3

DDR3L_ CH1_ ODT1_L PDDR3_C H1_ODT B DDR3L_ CH1_DQ36_L PDDR3_ CH1_DQB 4

DDR3L_ CH1_DQ37_L PDDR3_ CH1_DQB 5

MEM_CH1_VRE FDQ

DDR3L _CH1_DQ38_LPD DR3_CH 1_DQB6

MEM_CH1_VRE FCA

DDR3L_ CH1_DQ39_L PDDR3_ CH1_DQB 7

DDR3L_ CH1_DQ40_L PDDR3_ CH1_DQB 8

DDR3L_ CH1_DQ41_L PDDR3_ CH1_DQB 9

MEM_CH1_RCOM P

DDR3L _CH1_DQ42_LPD D R3_CH 1_DQB10

DDR3L_ CH1_DQ43_LPD D R3_CH1_DQB11

DDR3L_ CH1_C LKP0_LPDDR3 _CH1_C LKP_B DDR3L_ CH1_DQ44_LPD D R3_CH1_DQB12

DDR3L_ CH1_CLKN0_LPDD R3_CH1_ CLKN_B DDR3L_ CH1_DQ45_LPD D R3_CH1_DQB13

DDR3L_ CH1_DQ46_LPD D R3_CH1_DQB14

DDR3L_ CH1_C LKP1_LPDDR3 _CH1_C LKP_A DDR3L_ CH1_DQ47_LPD D R3_CH1_DQB15

DDR3L_ CH1_CLKN1_LPDD R3_CH1_ CLKN_A DDR3L_ CH1_DQ48_LPD D R3_CH1_DQB16

DDR3L_ CH1_DQ49_LPD D R3_CH1_DQB17

DDR3L_ CH1_R ESET_N_LPDD R3_NC DDR3L _CH1_DQ50_LPD D R3_CH 1_DQB18

DDR3L_ CH1_DQ51_LPD D R3_CH1_DQB19

DDR3L_ CH1_DQ52_LPD D R3_CH1_DQB20

DDR3L_ CH1_DQ53_LPD D R3_CH1_DQB21

DDR3L_ CH1_DQ54_LPD D R3_CH1_DQB22

DDR3L_ CH1_DQ55_LPD D R3_CH1_DQB23

DDR3L_ CH1_DQ56_LPD D R3_CH1_DQB24

DDR3L_ CH1_DQ57_LPD D R3_CH1_DQB2 5

DDR3L_ CH1_DQ58_LPD D R3_CH1_DQB26

DDR3L_ CH1_DQ59_LPD D R3_CH1_DQB27

DDR3L_ CH1_DQ60_LPD D R3_CH1_DQB28

DDR3L_ CH1_DQ61_LPD D R3_CH1_DQB29

DDR3L_ CH1_DQ62_LPD D R3_CH1_DQB30

DDR3L_ CH1_DQ63_LPD D R3_CH1_DQB31

[10 ] M_ A_A 0

[10 ] M_ A_A 1

[10 ] M_ A_A 2

[10 ] M_ A_A 3

[10 ] M_ A_A 4

[10 ] M_ A_A 5

[10 ] M_ A_A 6

[10 ] M_ A_A 7

[10 ] M_ A_A 8

[10 ] M_ A_A 9

[10 ] M_A_A 10

[10 ] M_A_A 11

[10 ] M_A_A 12

[10 ] M_A_A 13

[10 ] M_A_A 14

[10 ] M_A_A 15

[10] M _A_ BS#0

[10] M _A_ BS#1

[10] M _A_ BS#2

[10] M_ A_C AS#

[10] M_ A_R AS#

[10] M_A_W E#

[10] M _A_ CS#0

[10] M_ A_C KE0

R89 105 1% 4

[10 ] M_A_ CLK 0

[10] M _A_ CLK0 #

colsed to CPU pin within 100 mils

M_A_ DQ0 [10]

M_A_ DQ1 [10]

M_A_ DQ2 [10]

M_A_ DQ3 [10]

M_A_ DQ4 [10]

M_A_ DQ5 [10]

M_A_ DQ6 [10]

M_A_ DQ7 [10]

M_A_ DQ8 [10]

M_A_ DQ9 [10]

M_A _DQ1 0 [10]

M_A _DQ1 1 [10]

M_A _DQ1 2 [10]

M_A _DQ1 3 [10]

M_A _DQ1 4 [10]

M_A _DQ1 5 [10]

M_A _DQ1 6 [10]

M_A _DQ1 7 [10]

M_A _DQ1 8 [10]

M_A _DQ1 9 [10]

M_A _DQ2 0 [10]

M_A _DQ2 1 [10]

M_A _DQ2 2 [10]

M_A _DQ2 3 [10]

M_A _DQ2 4 [10]

M_A _DQ2 5 [10]

M_A _DQ2 6 [10]

M_A _DQ2 7 [10]

M_A _DQ2 8 [10]

M_A _DQ2 9 [10]

M_A _DQ3 0 [10]

M_A _DQ3 1 [10]

M_A _DQ3 2 [10]

M_A _DQ3 3 [10]

M_A _DQ3 4 [10]

M_A _DQ3 5 [10]

M_A _DQ3 6 [10]

M_A _DQ3 7 [10]

M_A _DQ3 8 [10]

M_A _DQ3 9 [10]

M_A _DQ4 0 [10]

M_A _DQ4 1 [10]

M_A _DQ4 2 [10]

M_A _DQ4 3 [10]

M_A _DQ4 4 [10]

M_A _DQ4 5 [10]

M_A _DQ4 6 [10]

M_A _DQ4 7 [10]

M_A _DQ4 8 [10]

M_A _DQ4 9 [10]

M_A _DQ5 0 [10]

M_A _DQ5 1 [10]

M_A _DQ5 2 [10]

M_A _DQ5 3 [10]

M_A _DQ5 4 [10]

M_A _DQ5 5 [10]

M_A _DQ5 6 [10]

M_A _DQ5 7 [10]

M_A _DQ5 8 [10]

M_A _DQ5 9 [10]

M_A _DQ6 0 [10]

M_A _DQ6 1 [10]

M_A _DQ6 2 [10]

M_A _DQ6 3 [10]

M_A _DQS0 [10]

M_A _DQS #0 [10]

M_A _DQS1 [10]

M_A _DQS #1 [10]

M_A _DQS2 [10]

M_A _DQS #2 [10]

M_A _DQS3 [10]

M_A _DQS #3 [10]

M_A _DQS4 [10]

M_A _DQS #4 [10]

M_A _DQS5 [10]

M_A _DQS #5 [10]

M_A _DQS6 [10]

M_A _DQS #6 [10]

M_A _DQS7 [10]

M_A _DQS #7 [10]

DDR3L_ CH0_MA0_LPDD R3_CH0_ CAB7 DDR3L_ CH0_DQ0_LPD DR3_CH 0_DQA0

DDR3L_ CH0_MA1_LPDD R3_CH0_ CAB9 DDR3L_ CH0_DQ1_LPD DR3_CH 0_DQA1

DDR3L_ CH0_MA2_LPDD R3_CH0_ CAB5 DDR3L_ CH0_DQ2_LPD DR3_CH 0_DQA2

DDR3L_ CH0_MA3_LPDD R3_NC

DDR3L_ CH0_DQ3_LPD DR3_CH 0_DQA3

DDR3L_ CH0_MA4_LPDD R3_NC

DDR3L_ CH0_DQ4_LPD DR3_CH 0_DQA4

DDR3L_ CH0_MA5_LPDD R3_CH0_ CAA2 DDR3L_ CH0_DQ5_LPD DR3_CH 0_DQA5

DDR3L_ CH0_MA6_LPDD R3_CH0_ CAA0 DDR3L_ CH0_DQ6_LPD DR3_CH 0_DQA6

DDR3L_ CH0_MA7_LPDD R3_CH0_ CAA3 DDR3L_ CH0_DQ7_LPD DR3_CH 0_DQA7

DDR3L_ CH0_MA8_LPDD R3_CH0_ CAA1 DDR3L_ CH0_DQ8_LPD DR3_CH 0_DQA8

DDR3L_ CH0_MA9_LPDD R3_CH0_ CAA4 DDR3L_ CH0_DQ9_LPD DR3_CH 0_DQA9

DDR3L_ CH0_MA10_LPDDR 3_CH0_CAB6 DDR3L_ CH0_D Q10_LPDD R3_CH0 _DQA10

DDR3L_ CH0_MA11_LPDDR 3_CH0_CAA6 DDR3L_ CH0_D Q11_LPDD R3_CH0 _DQA11

DDR3L_ CH0_MA12_LPDDR 3_CH0_CAA5 DDR3L_ CH0_D Q12_LPDD R3_CH0 _DQA12

DDR3L_ CH0_MA13_LPDDR 3_CH0_CAB0 DDR3L_ CH0_D Q13_LPDD R3_CH0 _DQA13

DDR3L_ CH0_MA14_LPDDR 3_CH0_CAA8 DDR3L_ CH0_D Q14_LPDD R3_CH0 _DQA14

DDR3L_ CH0_MA15_LPDDR 3_CH0_CAA9 DDR3L_ CH0_D Q15_LPDD R3_CH0 _DQA15

DDR3L_ CH0_D Q16_LPDDR 3_CH0 _DQA16

DDR3L_ CH0_BA0_LPDD R3_CH0_C AB2 DDR3L_ CH0_D Q17_LPDD R3_CH0 _DQA17

DDR3L_ CH0_BA1_LPDD R3_CH0_C AB8 DDR3L_ CH0_D Q18_LPDD R3_CH0_DQA18

DDR3L_ CH0_BA2_LPDD R3_CH0_C AA7 DDR3L_ CH0_D Q19_LPDD R3_CH0 _DQA19

DDR3L_ CH0_D Q20_LPDDR 3_CH0 _DQA20

DDR3L_ CH0_CA S_N_LPDDR 3_CH0_ CAB1 DDR3L_ CH0_D Q21_LPDD R3_CH0 _DQA21

DDR3L_ CH0_RA S_N_LPDDR 3_CH0_ CAB3 DDR3L_ CH0_D Q22_LPDD R3_CH0 _DQA22

DDR3L_ CH0_W E_N_L PDDR3_ CH0_CAB 4 DDR3L_ CH0_D Q23_LPDD R3_CH0 _DQA23

DDR3L_ CH0_D Q24_LPDDR 3_CH0 _DQA24

DDR3L_ CH0_CS 0_N_LPD DR3_CH0 _CS0A_N DDR3L_ CH0_D Q25_LPDD R3_CH0 _DQA25

DDR3L_NC_LPDD R3_CH0_C S1A_N

DDR3L_ CH0_D Q26_LPDD R3_CH0 _DQA26

DDR3L_NC_LPDD R3_CH0_C S0B_N

DDR3L_ CH0_D Q27_LPDD R3_CH0 _DQA27

DDR3L_CH0_CS1_ N_LPDDR 3_CH0_C S1B_N DDR3L_ CH0_D Q28_LPDD R3_CH0 _DQA28

DDR3L_ CH0_D Q29_LPDDR 3_CH0 _DQA29

DDR3L_ CH0_CKE0_L PDDR3_C H0_CKE0A DDR3L_ CH0_D Q30_LPDD R3_CH0 _DQA30

DDR3L_ CH0_CKE1_L PDDR3_C H0_CKE1A DDR3L_ CH0_D Q31_LPDD R3_CH0 _DQA31

DDR3L_NC_LPDD R3_CH0_C KE0B

DDR3L_ CH0_DQ 32_LPDDR 3_CH0_DQB0

DDR3L_NC_LPDD R3_CH0_C KE1B

DDR3L_ CH0_DQ 33_LPDDR 3_CH0_DQB1

DDR3L_ CH0_DQ 34_LPDDR 3_CH0_DQB2

DDR3L_ CH0_ ODT0_L PDDR3 _CH0_OD TA DDR3L_ CH0_DQ 35_LPDDR 3_CH0_DQB3

DDR3L_ CH0_ ODT1_L PDDR3 _CH0_OD TB DDR3L_ CH0_DQ 36_LPDDR 3_CH0_DQB4

DDR3L_ CH0_DQ 37_LPDDR 3_CH0_DQB5

MEM_CH0_ VREFDQ

DDR3L _CH0_DQ 38_LPDD R3_CH0_ DQB6

MEM_CH0_ VREFCA

DDR3L_ CH0_DQ 39_LPDDR 3_CH0_DQB7

DDR3L_ CH0_DQ 40_LPDDR 3_CH0_DQB8

DDR3L_ CH0_DQ 41_LPDDR 3_CH0_DQB9

MEM_CH0_R COMP

DDR3L_ CH0_D Q42_LPDD R3_CH0 _DQB10

DDR3L_ CH0_D Q43_LPDDR 3_CH0 _DQB11

DDR3L_ CH0_CL KP0_LPDD R3_CH 0_CLKP_B DDR3L_ CH0_D Q44_LPDD R3_CH0 _DQB12

DDR3L_ CH0_CLKN 0_LPDDR3_CH 0_CLKN_ B DDR3L_ CH0_D Q45_LPDD R3_CH0 _DQB13

DDR3L_ CH0_D Q46_LPDDR 3_CH0 _DQB14

DDR3L_ CH0_CL KP1_LPDDR 3_CH0_ CLKP_A DDR3L_ CH0_D Q47_LPDD R3_CH0 _DQB15

DDR3L_ CH0_CLKN 1_LPDDR3_CH 0_CLKN_ A DDR3L_ CH0_D Q48_LPDD R3_CH0 _DQB16

DDR3L_ CH0_D Q49_LPDDR 3_CH0 _DQB17

DDR3L_ CH0_R ESET_N _LPDDR3 _NC DDR3L_ CH0_D Q50_LPDD R3_CH0 _DQB18

DDR3L_ CH0_D Q51_LPDDR 3_CH0 _DQB19

DDR3L_ CH0_D Q52_LPDDR 3_CH0 _DQB20

DDR3L_ CH0_D Q53_LPDDR 3_CH0 _DQB21

DDR3L_ CH0_D Q54_LPDDR 3_CH0 _DQB22

DDR3L_ CH0_DQ55_LPD DR3_CH 0_DQB23

DDR3L_ CH0_D Q56_LPDDR 3_CH0 _DQB24

DDR3L_ CH0_D Q57_LPDDR 3_CH0 _DQB25

DDR3L_ CH0_D Q58_LPDDR 3_CH0 _DQB26

DDR3L_ CH0_D Q59_LPDDR 3_CH0 _DQB27

DDR3L_ CH0_D Q60_LPDDR 3_CH0 _DQB28

DDR3L_ CH0_D Q61_LPDDR 3_CH0 _DQB29

DDR3L_ CH0_D Q62_LPDDR 3_CH0 _DQB30

DDR3L_ CH0_DQ63_LPD DR3_CH 0_DQB31

M_B_ A0 BG9

M_B_A1 BG10

M_B _A 2

BH9

M_B_A3 BD1 6

M B A4 BB16

M B A 5 BG11

M_B_A6 BJ12

M_B_A7 BG14

M_B_A8 BG12

M B A 9 BH11

M B A10 BG7

M_B_A11 BH13

M_B_A12 BG13

M_B_ A13

BH3

M_B_A14 BG15

M B A 15 BG16

BH6

BG8

BH15

BH4

BJ6

BH7

BD17

BB17

AV17

AW17

BG18

BG17

BH17

BJ16

AW16

AV16

AT30

AR29

MEM CH1 RCO MP

AV30

BD19

BE19

BB21

BD21

MB_ DRAMRST#

AR30

C97

0.1u/1 6V _4

R101

10_5% _4

AR21

AT21

AW23

AW21

BA19

AW19

BA23

BB23

BD23

BE23

BJ26 M_B_DQ0

BG30 M_B_DQ1

BH31 M_B_DQ2

BG31 M_B_DQ3

BH27 M B DQ4

BG27 M B DQ5

BG26 M_B_DQ6

BJ30 M_B_DQ7

BA30 M_B_DQ8

BB30 M B DQ9

BE30 M B DQ10

BD30 M_B_DQ11

BE25 M_B_DQ12

BB27 M_B_DQ13

BD25 M_B_DQ14

BD27 M B DQ15

BG24 M_B_DQ16

BJ20 M_B_DQ17

BH23 M_B_DQ18

BJ24 M_B_DQ19

BG20 M B DQ20

BG21 M_B_DQ21

BH19 M_B_DQ22

BG25 M_B_DQ23

AT27 M_B_DQ24

AW29

M_B_DQ25

AR27 M B DQ26

AT23 M_B_DQ27

AV27 M_B_DQ28

AR25 M_B_DQ29

AR23 M_B_DQ30

AW27

M B

DQ31

BF6

M_B _D Q32

BD10 M_B_DQ33

BE14 M_B_DQ34

BB10 M_B_DQ35

BA14 M B DQ36

BB14 M B DQ37

BD14 M_B_DQ38

BE8

M_B _DQ3 9

AV12 M_B_DQ40

BD6

M B DQ41

BD5

M B DQ42

BB7

M_B _DQ4 3

AV10 M_B_DQ44

AY9

M_B _DQ4 5

AY7

M_B _DQ4 6

BF5

M B D Q47

AU2

M B DQ48

AT10 M_B_DQ49

AT9

M_B _DQ5 0

AU1

M _B_ DQ51

AY5

M B DQ52

AV5

M B DQ53

AV6

M_B _DQ5 4

AV7

M_B _DQ5 5

AY2

M_B _DQ5 6

BD2

M _B_ DQ57

BD1

M B DQ58

BE2

M B DQ59

AW1 M_B_ DQ60

AW2 M_B_ DQ61

AY3

M_B _DQ6 2

BG2 M B DQ63

BG28

M_B_ DQS 0

BH29 M_B_DQS#0

BD29

M_B _DQ S1

BB29 M_B_ DQS#1

BJ22

M B DQS 2

BG22 M B DQS#2

AV25

M_ B_D QS3

AW25 M_B_ DQS#3

BB12

M_ B_D QS4

BD12 M B DQS# 4

BB5

M B DQ S5

BB6

M_B_ DQS #5

AT5

M_B _D QS6

AT6

M_B_ DQS #6

BC2

M_B_ DQS 7

BB1

M B DQS #7

D

C

B

A

D

C

B

A

[11] M _B_ A0

[11] M _B_ A1

[11] M _B_ A2

[11] M _B_ A3

[11] M _B_ A4

[11] M _B_ A5

[11] M _B_ A6

[11] M _B_ A7

[11] M _B_ A8

[11] M _B_ A9

[11] M_B _A1 0

[11] M_B _A1 1

[11] M_B _A1 2

[11] M_B _A1 3

[11] M_B _A1 4

[11] M_B _A1 5

[11] M _B_ BS#0

[11] M _B_ BS#1

[11] M _B_ BS#2

[11] M _B_ CAS#

[11] M _B_ RAS#

[11] M_ B_WE #

[11] M_ B_CS #0

[11] M _B_ CKE0

R91 105 1% 4

[11 ] M _B_ CLK 0

[11] M_B_ CLK 0#

colsed to CPU pin within 100 mils

_ _

_ _ _ _

_ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _ _ _

_ _ _ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _ _ _

_ _

_ _ _ _ _ _

_ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _

_ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _ _ _

_ _

APL ULT (DDR3L)

U21A APL BGA 1296P

J1

J2

K9

K10

K3

K2

F2

G2

AC16

WND

GGD

5

4

3

2

1

8M

8M

Quanta Computer Inc.

PROJECT :ZAJ

Vender

Size

Quanta P/N Vender P/N

SPI ROM

1.8V

SP@ socket P/N: DFHS08FS023 only for A-TEST

Rev

3A

Size Document Number

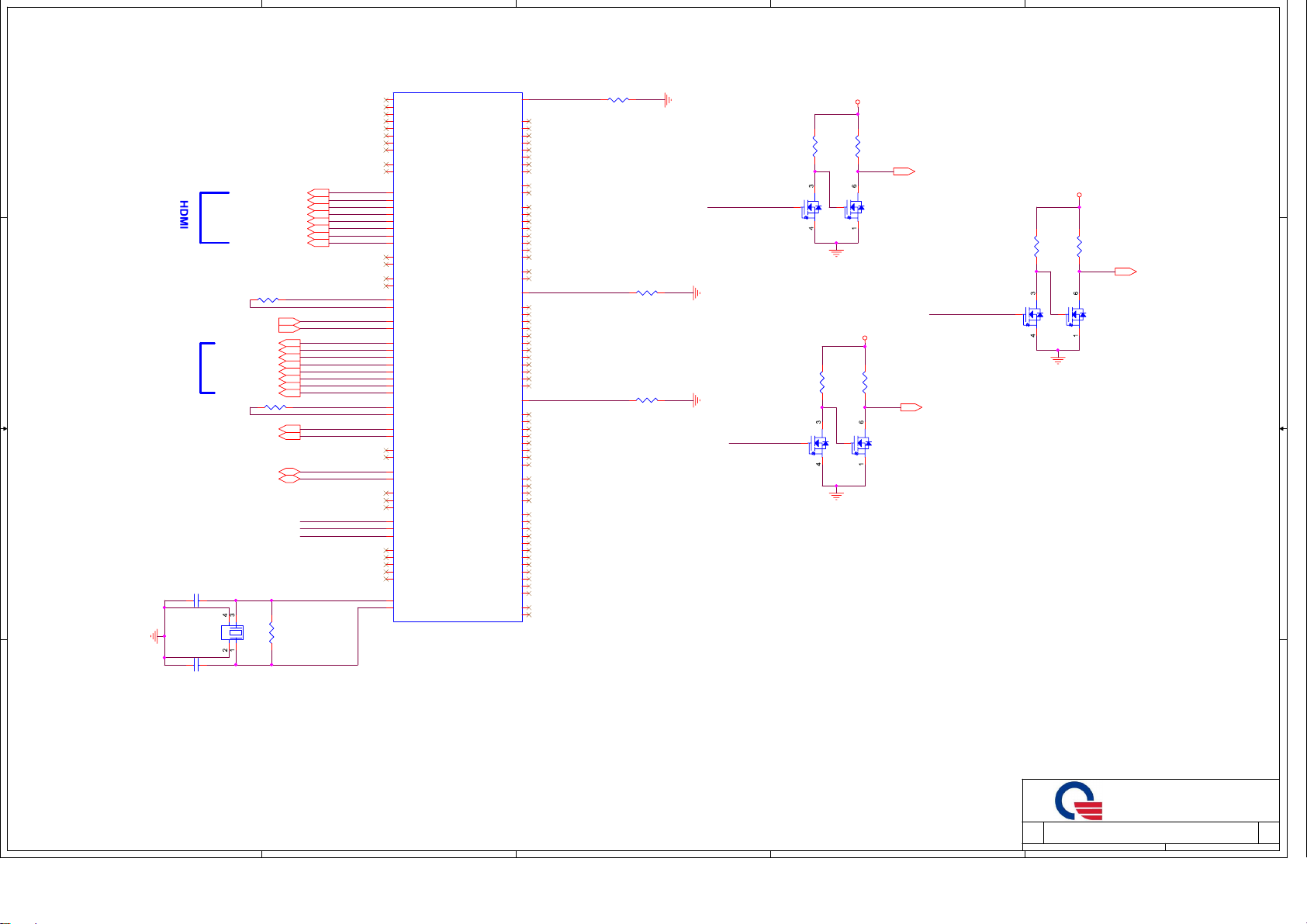

BXTP (PCIE/USB/SATA/SPI)

Date: Tuesday, March 21, 2017

Sheet

3 of 34

AKE5EG-0Q01 GD25LB64CSIGR

03

D

C

B

A

D

C

B

A

[19] USB3_0_TXP

[19] USB3_0_TXN

[19] USB3_0_RXP

[19] USB3_0_RXN

[20] USB3_1_TXP

[20] USB3_1_TXN

[20] USB3_1_RXP

[20] USB3_1_RXN

USB_SSIC_RCOMP

N62

P61

PCIE_LAN_WAKE#

PCIE_LAN_WAKE# [15]

PCIE_TX3+_WLAN [17]

PCIE_TX3-_WLAN

[17]

PCIE_RX3+_WLAN [17]

PCIE_RX3-_WLAN

[17]

USB3_2_TXP [20]

USB3_2_TXN [20]

USB3_2_RXP [20]

USB3_2_RXN [20]

PCIE_TX0+_SSD [16]

PCIE_TX0-_SSD [16]

PCIE_RX0+_SSD [16]

PCIE_RX0-_SSD [16]

PCIE_TX1+_SSD [16]

PCIE_TX1-_SSD [16]

PCIE_RX1+_SSD [16]

PCIE_RX1-_SSD [16]

PCIE_TX2+_LAN [15]

PCIE_TX2-_LAN [15]

PCIE_RX2+_LAN

[15]

PCIE_RX2-_LAN

[15]

CLK_PCIE_SSD_REQ#

[16]

CLK_PCIE_LAN_REQ#

[15]

PCIE_CLKREQ_WLAN#

[17]

+1.8V_S5

MB USB3.0

MB TYPE C

USB2COMP:4-8mils trace width with <1000 mils

P62

R62

F6

PCIE_RCOMPP

F5

PCIE RCOMPN

R37

402_1%_4

0.1u/16V 4 C332

0.1u/16V 4 C333

0.1u/16V_4 C335

0.1u/16V 4 C334

10K 5% 4

10K 5% 4

10K 5% 4

*10K_5%_4

USB3_P0_TXP

PCIE_WAKE3_N

USB3_P0_TXN

PCIE_WAKE2_N

USB3_P0_RXP

PCIE_WAKE1_N

USB3_P0_RXN

PCIE_WAKE0_N

USB3_P1_TXP

USB3_P1_TXN PCIE2_USB3_SATA3_RCOMP_P

USB3_P1_RXP

USB3_P1_RXN

PCIE2_USB3_SATA3_RCOMP_N

USB2_VBUS_SNS

PCIE_P3_USB3_P4_TXP

USB_SSIC_RCOMP PCIE_P3_USB3_P4_TXN

PCIE_P3_USB3_P4_RXP

USB2_RCOMP

PCIE_P3_USB3_P4_RXN

P3

P2

P12

P10

N2

M2

H5

H6

L2

L1

K7

M7

V3

V2

P7

P6

R1

R2

T10

T12

T2

T3

M5

M6

AK62

AH62

AH61

AJ62

C11

B11

C10

A10

A7

B8

B7

B5

C1

F1

B4

A4

A18

C19

PCIE_TX3+

PCIE_TX3-

PCIE_TX2+

PCIE TX2-

R398

R391

R397

R392

R64 137 1% 4

AB15

WIFI

MB TYPE C

M.2 SSD

LAN

R75

R382

*10K 5% 4

10K 5% 4

10K 5% 4

113 1% 4

USBCOMP Y15

*0 5% 4

AC15

AH13

AH12

AG16

AG15

B55

C55

V12

V10

V16

V15

Y13

V13

V9

V7

Y9

Y10

AB6

AB7

AC12

AC10

V5

V6

W 1

W 2

T5

T6

Y3

Y2

T9

T7

USB2_OTG_ID

USB_SSIC_0_TX_P

USB_SSIC_0_TX_N

USB_SSIC_0_RX_P

USB_SSIC_0_RX_N

USB2_OC0_N

USB2_OC1_N

USB2_DP0

USB2_DN0

USB2_DP1

USB2_DN1

USB2_DP2

USB2_DN2

USB2_DP3

USB2_DN3

USB2_DP4

USB2_DN4

USB2_DP5

USB2_DN5

USB2_DP6

USB2_DN6

USB2_DP7

USB2_DN7

PCIE_P4_USB3_P3_TXP

PCIE_P4_USB3_P3_TXN

PCIE_P4_USB3_P3_RXP

PCIE_P4_USB3_P3_RXN

PCIE_P5_USB3_P2_TXP

PCIE_P5_USB3_P2_TXN

PCIE_P5_USB3_P2_RXP

PCIE_P5_USB3_P2_RXN

PCIE_P0_TXP

PCIE_P0_TXN

PCIE_P0_RXP

PCIE_P0_RXN

PCIE_P1_TXP

PCIE_P1_TXN

PCIE_P1_RXP

PCIE_P1_RXN

PCIE_P2_TXP

PCIE_P2_TXN

PCIE_P2_RXP

PCIE_P2_RXN

PCIE_CLKREQ0_N

PCIE_CLKREQ1_N

PCIE_CLKREQ2_N

PCIE_CLKREQ3_N

+1.8V_S5

[20] USB_OC0#

[19] USB_OC1#

R377

R328

R327

[19]

USBP0+

MB USB3.0 CONN

[19]

USBP0-

[20]

USBP1+

MB TYPE C

[20]

USBP1-

[19]

USBP2+

USB 2.0

[19]

USBP2-

[19]

USBP3+

USB 2.0

[19]

USBP3-

BT

[17]

USBP4-

Touch Screen

[12]

USBP5-

CCD

ODD bridge

[16]

USBP7-

AKE5EZN0N01

W25Q64FWSSIQ

SATA_P1_USB3_P5_TXP

PCIE_CLKOUT0P

SATA_P1_USB3_P5_TXN

PCIE_CLKOUT0N

SATA_P1_USB3_P5_RXP

PCIE_CLKOUT1P

SATA_P1_USB3_P5_RXN

PCIE_CLKOUT1N

SATA_P0_TXP

PCIE_CLKOUT2P

SATA_P0_TXN

PCIE_CLKOUT2N

SATA_P0_RXP

PCIE_CLKOUT3P

SATA_P0_RXN

PCIE_CLKOUT3N

M.2 SATA

HDD

PCH SPI SI

PCH SPI SO

PCH SPI IO3

PCH SPI IO2

PCH_SPI_CS0#

PCH_SPI_CLK

R302 33 5% 4

A58

B58

B61

B60

C57

B57

C56

RSVD_C1

RSVD_F1

RSVD_B4

RSVD_A4

RSVD_A18

RSVD_C19

VSTBY_FSPI

R352 R326

3.3K_5%_4 *3.3K_5%_4

U1

C5

R354

0.1u/16V_4

3.3K_5%_4

PCH_SPI_IO3

PCH SPI CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

1

6

5

2

3

8

7

4

CE# VCC

SCLK

SI

SO

IO3

IO2 VSS

GD25LB64CSIGR

_ _ _ _

_ _ _

_ _

_ _

_ _

_ _

_ _ _ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

USB_OTG_ID

[17]

USBP4+

[12]

USBP5+

[12]

USBP6+

[12]

USBP6-

[16]

USBP7+

[16]

SATA_TXP1

[16] SATA_TXN1

[16]

SATA_RXP1

[16]

SATA_RXN1

[16]

SATA_TXP0

[16] SATA_TXN0

[16]

SATA_RXP0

[16]

SATA_RXN0

CLK_PCIE_SSDP

[16]

CLK_PCIE_SSDN [16]

CLK_PCIE_LANP

[15]

CLK_PCIE_LANN [15]

CLK_PCIE_WLANP

[17]

CLK_PCIE_WLANN

[17]

M.2 SSD

LAN

WIFI

FST_SPI_MOSI_IO0

FST_SPI_MISO_IO1

FST_SPI_IO3

FST_SPI_IO2

FST_SPI_CS1_N

FST_SPI_CS0_N

FST_SPI_CLK

Section 3 of 12

VSTBY_FSPI

CLK_PCIE_LAN_REQ#

PCIE_CLKREQ_WLAN#

R485

*0 5% 4

R486

*0 5% 4

SPI_CLK_A

5

4

3

2

1

Apollo lake (SATA , ODD, CLK ,USB,PCIE)

+1.8V_S5

R366

U21C

APL BGA 1296P

10K_5%_4

Q27A Q27B

+3V

R298 R337

10K_5%_4 10K_5%_4

5

2

SSM6N43FU

Q28A Q28B

Rev

3A

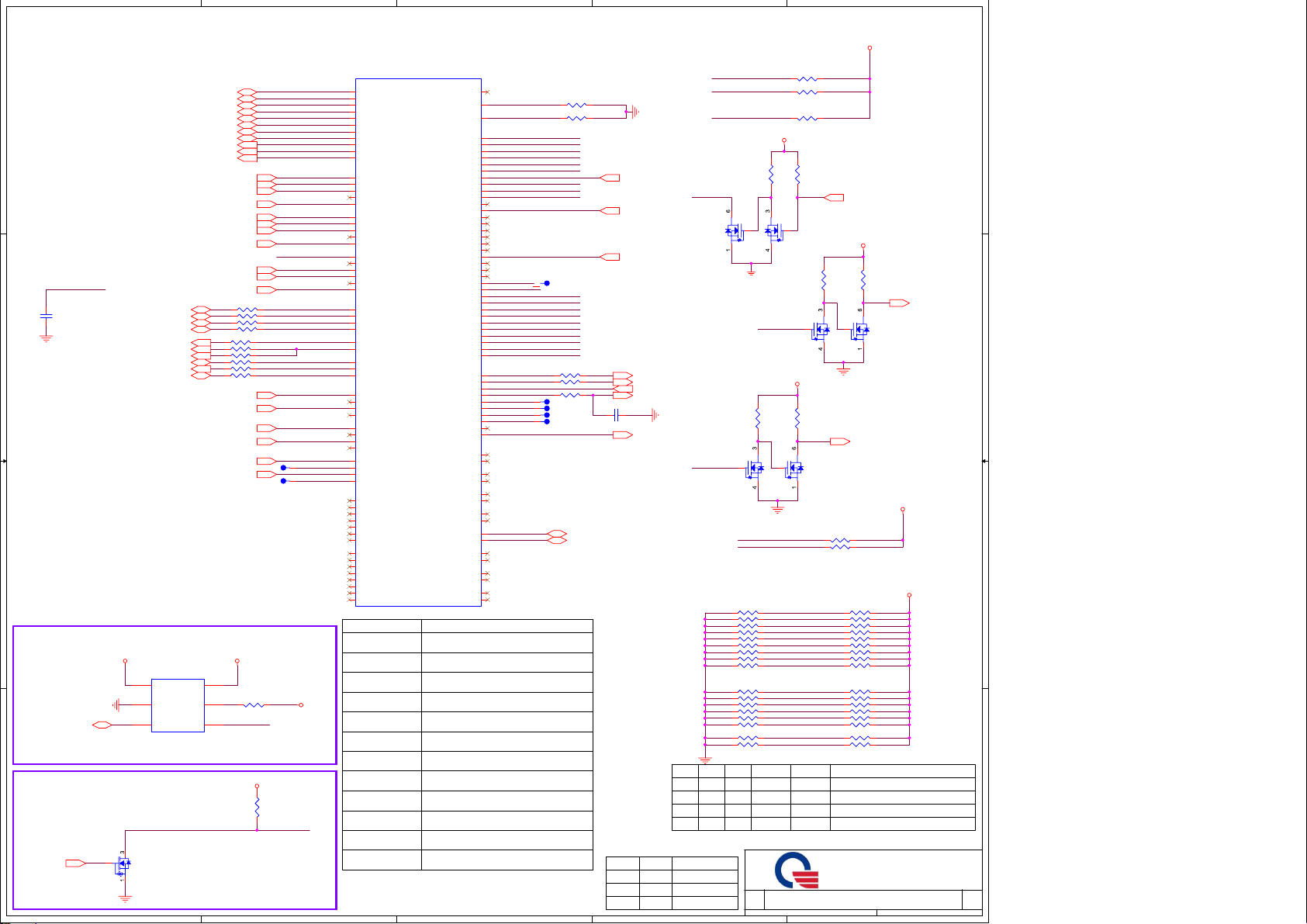

Size Document Number

BXTP (HDMI/eDP)

Date: Tuesday, March 21, 2017 Sheet 4 of 34

5 4 3 2 1

C310 15p/50V 4

XTAL192_IN

19.2MHZ/20ppm 200K_1%_4

5 4 3 2 1

Apollolake (DISPLAY,eDP)

04

D

C

B

U21D

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

DDI1_AUXP

DDI1_AUXN

APL BGA 1296P

MDSI_RCOMP

MDSI_C_DP_0

MDSI_C_DN_ 0

MDSI_C_DP_1

MDSI_C_DN_ 1

MDSI_C_DP_2

MDSI_C_DN_ 2

MDSI_C_DP_3

MDSI_C_DN_ 3

MDSI_C_C LKP

+3V

R297

10K_5%_4

5

2

AF2

AF3

AD3

AD2

AC1

AC2

AB3

AB2

AK16

AK15

AK3

AK2

AM3

AM2

AH3

AH2

AL2

AL1

AM16

AM15

B51

C51

DDI0_RCOMP_P

DDI0 RCOMP N AG2

D

C

B

R336

10K_5%_4

SSM6N43FU

EDP_VDD_EN [12]

PCH_BKLTEN

PCH_BRIGHT [12]

+3V

R299

10K_5%_4

5

2

[13] INT_HDMITX2P

[13] INT_HDMITX2N

[13] INT_HDMITX1P

[13] INT_HDMITX1N

[13] INT_HDMITX0P

[13] INT_HDMITX0N

[13] INT_HDMICLK+

[13] INT_HDMICLK-

PCH_VDDEN

150 1% 4

150 1% 4

PCH_BKLTCTL

PCH_VDDEN

PCH_BKLTEN

PCH_BKLTCTL

XTAL192 OUT

C52

B53

C53

C47

B47

C46

AG62

AF61

AG63

AE60

AF62

P29

R27

R332

10K_5%_4

PCH_BLON [12]

SSM6N43FU

F27

MCSI_DPHY1 .2_RCOM P

R40

M23

P23

L23

J23

J21

H21

M25

L25

F25

E25

H25

J25

H27

MCSI

DPHY1.1 RCOM P

R44

P17

M17

P21

R21

L17

J17

F17

E17

M19

L19

H19

F19

L37

P34

J34

H30

M37

F30

R35

L34

M34

M35

R34

E30

M45

M43

R385 402 1% 4 AG1

INT_HDMI_HPD#

C50

A50

[13] INT_HDMI_HPD#

[20] TypeC_HPD#

EDP_TXP0 AG7

EDP_TXN0 AG9

EDP_TXP1 AG12

EDP TXN1 AG10

EDP_TXP2 AC6

EDP_TXN2 AC5

EDP_TXP3 AC7

EDP_TXN3 AC9

EDP_RCOMP_P AG6

EDP_RCOMP_N AG5

EDP_AUXP AH10

EDP AUXN AH9

C54

A54

Q26A Q26B

[12] EDP_TXP0

[12] EDP_TXN0

[12] EDP_TXP1

[12] EDP_TXN1

[12] EDP_TXP2

[12] EDP_TXN2

[12] EDP_TXP3

[12] EDP_TXN3

R74 402 1% 4

[12] EDP_AUXP

[12] EDP_AUXN

eDP Panel

HDMI DDCDATA SW C49

HDMI_DDCCLK_SW B49

[13] HDMI_DDCDATA_SW

[13] HDMI_DDCCLK_SW

C309 15p/50V 4

Y3 R301

_ _ _

_ _ _ _ _ _ _

_

_ _ _ _ _ _ _ _ _ _ _ _

AP7 MDSI_RCOM P

AK7

AK6

AM5

AM6

AM12

AM10

AK13

AM13

AM9

AM7

AP12

AP10

AR2

AR1

AP15

AP13

AP6

AP5

AP2

AP3

R87 150 1% 4

DDI0_TXP_0 MDSI_C_CLKN

DDI0_TXN_0

DDI0_TXP_1 MDSI_A_DP_0

DDI0_TXN_1 MDSI_A_DN_0

DDI0_TXP_2 MDSI_A_DP_1

DDI0_TXN_2 MDSI_A_DN_1

DDI0_TXP_3 MDSI_A_DP_2

DDI0_TXN_3 MDSI_A_DN_2

MDSI_A_DP_3

DDI0_AUXP MDSI_A_DN_3

DDI0_AUXN

MDSI_A_CLKP

MIPI_I2C_SDA MDSI_A_CLKN

MIPI_I2C_SCL

MCSI_DPHY1.2_RCOMP

DDI0_RCOMP_P

DDI0_RCOMP_N MCSI_RX_DATA0_P

MCSI_RX_DATA0_N

GPIO_200 MCSI_RX_CLK0_P

GPIO_199 MCSI_RX_CLK0_N

MCSI_RX_DATA1_P

EDP_TXP_0 MCSI_RX_DAT A1_N

EDP_TXN_0 MCSI_RX_DATA2_P

EDP_TXP_1 MCSI_RX_DAT A2_N

EDP_TXN_1 MCSI_RX_CLK1_P

EDP_TXP_2 MCSI_RX_CLK1_N

EDP_TXN_2 MCSI_RX_DATA3_P

EDP_TXP_3 MCSI_RX_DAT A3_N

EDP_TXN_3

MCSI_DPHY1.1_RCOMP

EDP_RCOMP_P

EDP_RCOMP_N MCSI_DP_0

MCSI_DN_0

EDP_AUXP MCSI_DP_1

EDP_AUXN MCSI_DN_1

MCSI_DP_2

DDI1_DDC_SDA MCSI_DN_2

DDI1_DDC_SCL MCSI_DP_3

MCSI_DN_3

DDI0_DDC_SDA

DDI0_DDC_SCL MCSI_CLKP_0

MCSI_CLKN_0

PNL1_VDDEN MCSI_CLKP_2

PNL1_BKLTEN MCSI_CLKN_2

PNL1_BKLTCTL

GP_CAMERAS B0

PNL0_VDDEN GP_CAMERASB1

PNL0_BKLTEN GP_CAMERASB2

PNL0_BKLTCTL GP_CAMERASB3

GP_CAMERAS B4

OSC_CLK_OUT_0 GP_CAMERASB5

OSC_CLK_OUT_1 GP_CAMERASB6

OSC_CLK_OUT_2 GP_CAMERASB7

OSC_CLK_OUT_3 GP_CAMERASB8

OSC_CLK_OUT_4 GP_CAMERASB9

GP_CAMERAS B10

GP_CAMERAS B11

OSCOUT

OSCIN MDSI_A_TE

MDSI_C_TE

Section 4 of 12

A

Quanta Computer Inc.

PROJECT :ZAJ

R488 R300

0

1

0

1

0

0

1

1

0

0

0

0

Quanta PN

Description

AKD5JGSTL08 IC SDRAM (96P)MT 41K256M 16HA-125:E STNBSQ

AKD59GSTL12 IC SDRAM (96P)MT 41K256M 16TW-107:P STNBSQ

AKD5PGSTW29 IC SDRAM(9 6P)H5TC 4G63EFR -PBA(F BGA)STN BSQ

AKD5JG0T504 IC SDRAM(9 6P)K4B4 G1646E -BYK0(F BGA)STNB SQ

Quanta Computer Inc.

PROJECT :ZAJ

Vender

Miron-2GB

Miron-2GB

Hynix-2GB

Samsung-2GB

5

4

3

2

1

Rev

3A

Size

Document Number

BXTP (EMMC/LPC/SMB/ISH)

Date: Tuesday, March 21, 2017

Sheet

5 of 34

2N7002K

Samsung 32/64GB

Hynix 32/64GB

Kingston 32/64GB

0

1

0

0

0

1

eMMC_ID1 eMMC_ID0

Vender

[21]

IRQ_SERIRQ

[21]

ME_WR#

2

SOC_OVRIDE

Flash Descriptor Override (SOC_OVRIDE)

0 = Normal Override(Normal operation)

1 = Override

R390 10K_5%_4

SOC_SERIRQ

+1.8V_S5

R381

2.2K_5%_4

*10K_5%_4

*10K 5% 4

*10K 5% 4

R293

5

4

3

2

1

05

SATA_DEVS LP0 [16]

Apollolake (EMMC/LPC/I2C)

U21E APL BGA 1296P

+1.8V_S5

R321 *GS@10K 5% 4

R308 *10K 5% 4

V58

T58

T59

V51

V52

Y49

V55

V57

V54

Y51

Y58

F54

F52

H52

H54

J52

F58

K55

F61

H57

H58

F62

D61

E56

D59

C62

E62

Y61

Y62

W62

W63

[12] EMMC_DAT A_0

[12] EMMC_DAT A_1

[12] EMMC_DAT A_2

[12] EMMC_DAT A_3

[12] EMMC_DAT A_4

[12] EMMC_DAT A_5

[12] EMMC_DAT A_6

[12] EMMC_DAT A_7

[12]

EMMC_RCLK

[12] EMMC_CMD

[12]

EMMC_CLK

[9]

GPIO_104

[9]

GPIO_105

[9]

GPIO_106

[9]

GPIO_110

[9]

GPIO_111

[9]

GPIO_112

[9]

GPIO_113

[9]

GPIO_117

[9]

GPIO_120

[9]

GPIO_121

[9]

GPIO_123

V49

E34

GPIO RCOMP

200 1% 4

200 1% 4

33 5% 4

33_5%_4

33 5% 4

V59

EMMC_RCOMP R58

PCH_TPD_ INT# R25

+3V

R22 R21

10K 5% 4

D

C

B

A

D

C

B

A

A38

B33

C39

B39

B35

A34

B31

H39

B29

A30

L39

C34

E39

C30

C38

F39

C36

C35

J39

C33

B27

C26

A26

B25

C25

C27

C31

C29

B37

H35

C37

H34

F35

F34

Board_ID0

Board_ID1

Board_ID2

Board_ID3

Board_ID4

Board_ID5

Board ID6

Board ID8

Board_ID7

GPIO_23

GPIO_2 4

GPIO_2 5

RAM_ID0

RAM_ID1

RAM ID2

RAM_ID3

RAM_ID4

eMMC_ID0

eMMC ID1

RAM_ID5

HDA BCLK R

HDA_SYNC_R

HDA_SDO_R

GPIO_104

GPIO 105

GPIO 106

GPIO_110

GPIO_111

GPIO_112

GPIO_113

GPIO 117

SOC_OVRIDE

GPIO 120

GPIO_121

GPIO_123

LPC_LAD0_R

ACCEL_INTA

[18]

SIO_EXT_SCI#

[21]

PCH_TPD_INT#

[18]

HDA

10K_5%_4

10K_5%_4

GPIO_23

2 5

Q4B Q4 A

2N7002KDW

NGFF_ SATA_DET # [16]

+3V

EMI

LPC_CLKOUT1

C336

*10p/50V_4

R487 R289

*10K_5%_4

*10K_5%_4

5 2

Q25A

Q25B

*SSM6N43FU

+3V

TP32

[16,17,21] LPC_LA D0

[16,17,21] LPC_LA D1

[16,17,21] LPC_LA D2

[16,17,21] LPC_LA D3

[21] CLK_PCI_E C

[16]

PCLK_TPM

[17] CLK_P CI_LP C

[16,21] CLKRUN#

[16,17,21]

LPC_LFRAME#

[16] SOC_SERIRQ

R374

R375

R370

R372

R379

R376

R380

R371

R369

R386

20 1% 4 LPC_LAD1_R

GPIO_2 4

20_1%_4 LPC_LAD3_R

LPC_CLKOUT0

LPC CLKOUT 1

AZ_CODEC_BITCLK

[14]

AZ_CODEC_ SY NC [14]

AZ_CO DEC_ SDIN0 [14]

AZ_CO DEC_ SDOU T [14]

EMI

B45

C45

A46

C44

B43

C43

A42

C42

H41

J41

L41

M41

P51

T52

P57

T54

T55

T57

P58

AB55

AC49

AC48

AC51

AB51

AC52

AB58

AB54

AM51

AM49

AM57

AM55

AM52

AK57

AR62

AR63

AN62

AM61

AP59

AP58

AM62

AL62

AP52 I2C4 SDA

AP54

I2C4_SCL

AP49

TP9

TP7

TP8

TP10

C245

*10p/50V_4

SPKR [14]

GPIO_25

*10K_5%_4

5 2

Q24A

I2C4_S DA

I2C4_S CL

*10K_5%_4

Q24B

*SSM6N43FU

SATA_DEVSLP1

[16]

+1.8V_S5

LPSS_I2C2_SDA

LPSS_I2C2_SCL

LPSS_I2C3_SDA

LPSS_I2C3_SCL

LPSS_I2C4_SDA

LPSS_I2C4_SCL

LPSS_I2C5_SDA

LPSS_I2C5_SCL

LPSS_I2C6_SDA

LPSS_I2C6_SCL

LPSS_I2C7_SDA

LPSS_I2C7_SCL

SDIO_PWR_DW N_N

SDIO_D0

SDIO_D1

SDIO_D2

SDIO_D3

SDIO_CMD

SDIO_CLK

SDCARD_LVL_WP

SDCARD_D0

SDCARD_D1

SDCARD_D2

SDCARD_D3

SDCARD_CMD

SDCARD_CLK

SDCARD_CD_N

HW strap ID

Board_ID0

Board_ID1

Board_ID2

Board_ID3

Board_ID4

Board_ID5

Board_ID6

Board_ID7

Board_ID8

RAM_ID0

RAM_ID1

RAM_ID2

I2C4_S DA [18]

I2C4_S CL [18]

R90

2K_1%_4

R92 2K 1% 4

+1.8V_S5

Touch PAD

R339

R341

R348

R347

R349

R342

R288

R282

R491

R350

R285

R340

R284

R338

R286

R287

R283

RAM_ID5 RAM _ID4 RAM_ ID3

Strap pin Descrip tion

0 = w/o type C

1 = w/ type C

0 = with EMMC

1 = without EMMC <HDD only>

0 = SATA SSD

1 = PCIE SSD

0 = none G sensor

1 = G sensor

0 = none TPM

1 = TPM

0 = EJ HDD

1 = Cloud book SSD

0 = EJ SSD

1 = Cloud book N/A

0 = EJ se ries

1 = Clo ud book

0 = UMA

1 = GPU

0 = Si ngle cha nnel (A o nly)

1 = Dual cha nnel (A & B)

0 = Cha nnel A 2GB

1 = Cha nnel A 4GB

0 = Cha nnel B 2GB

1 = Cha nnel B 4GB

Board ID

RAM ID

eMMC ID

1

2

3

Q30

6

VCCA VCCB

5

GND EO

4

A B

G2129TL1U

_ _ _ _

_ _

_

_ _

_ _ _ _

_ _

_ _

_

_

_ _

_ _

_ _ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _ _ _

_ _ _ _

_ _

_

_

_ _

_ _

_

_ _

_ _ _ _

_ _ _ _

_

_ _ _ _

_ _ _ _

_ _ _ _

_

_ _ _ _

_ _

_

_ _

_ _ _ _

_ _ _ _

_

_ _ _ _

_ _ _ _

_ _ _ _ _

EMMC _D0

RSVD_V49

EMMC _D1

EMMC _D2

GPIO_RCOMP

EMMC _D3

EMMC _D4

EMMC_RCOMP

EMMC _D5

EMMC _D6

EMMC _D7 GPIO _0

EMMC_RCLK

GPIO_1

EMMC _CMD GP IO_2

EMMC_CLK

GPIO_3

GPIO _4

GPIO _5

SIO_SPI_0_CLK

GPIO _6

SIO_SPI_0_FS0

G PIO_7

SIO_SPI_0_FS1

G PIO_8

SIO_SPI_0_RXD

GPIO_9

SIO_SPI_0_TXD

GPIO _10

GPIO _11

SIO_SPI_1_CLK

GPIO _12

SIO_SPI_1_FS0

GPIO_13

SIO_SPI_1_FS1

GPIO_14

SIO_SPI_1_RXD

GPIO_15

SIO_SPI_1_TXD

GPIO _16

GPIO _17

SIO_SPI_2_CLK

GPIO _18

SIO_SPI_2_FS0

GPIO_19

SIO_SPI_2_FS1

GPIO_20

SIO_SPI_2_FS2

GPIO_21

SIO_SPI_2_RXD

GPIO_22

SIO_SPI_2_TXD

GPIO _23

GPIO _24

GPIO _25

LPC_AD 0 GPIO_ 26

LPC_AD 1 GPIO_ 27

LPC_AD 2 GPIO_ 28

LPC_AD 3 GPIO_ 29

GPIO _30

LPC_CLKOUT0

GPIO_31

LPC_CLKOUT1

GPIO_32

GPIO _33

LPC_C LKRUN_N

LPC_FRAME_N

LPC_SERIRQ

ISH_G PIO _0

ISH_GPIO _1

ISH_GPIO _2

Section 5 of 12

LPSS_UART0_TXD

ISH_GPIO _3

LPSS_UART0_RXD

ISH_GPIO_4

LPSS_UART0_RTS_N

ISH_GPIO_5

LPSS_UART0_CTS_N

ISH_GPIO_6

ISH_GPIO _7

LPSS_UART1_TXD

ISH_GPIO _8

LPSS_UART1_RXD

ISH_GPIO_9

LPSS_UART1_RTS_N

LPSS_UART1_CTS_N

LPSS_I2C0_SDA

LPSS_UART2_TXD LPSS_I2C0_SCL

LPSS_UART2_RXD

LPSS_UART2_RTS_N

LPSS_I2C1_SD A

LPSS_UART2_CTS_N LPSS_I2C1_SCL

AM48 R98

AK58 R399

AK51

AM54 R95

20 1% 4

*10K 5% 4 R318 10K 5% 4

10K_5%_4 R294

*10K_5%_4

*10K 5% 4 R295 10K 5% 4

10K 5% 4 R291 *10K 5% 4

+1.8V_S5

10K 5% 4 R317

10K 5% 4 R292

10K_5%_4

ACCEL_INTA

SIO_E XT_S CI#

R34

LPC LAD2 R

20 1% 4

20 1% 4 AB61

TPM@20 1% 4 AA62

*DBG@20 1% 4

20 1% 4

CLKRUN#_R

V62

20 1% 4 V61

20 1% 4 AB62

LPC_LFRAME #_R

SOC SERIRQ R

GPIO_39

GPIO_40

GPIO 43

GPIO_44

GPIO_47

GPIO_48

AP51

AL63

AK61

AP62

AP61

I2C st andard/fast mode:

I2C tot al lengh t is about 45 00 mils = 4. 5inchs

Cb = 4.5*5pF +7pF = 29.5pF

PU resis tor = 2K ohm

Board ID0

Board_ID1

Board_ID2

Board_ID3

Board ID4

Board_ID5

Board_ID6

Board_ID7

Board ID8

RAM ID0

RAM_ID1

RAM_ID2

RAM_ID3

RAM ID4

RAM_ID5

eMMC_ID0

eMMC ID1

10K 5% 4 R316 *10K 5% 4

10K_5%_4 R320

*10K_5%_4

10K 5% 4 R315 *10K 5% 4

10K 5% 4 R314 *10K 5% 4

10K 5% 4 R319 *10K 5% 4

10K_5%_4 R309

*10K_5%_4

10K 5% 4 R296 *10K 5% 4

10K 5% 4 R290 *10K 5% 4

10K 5% 4 R492 *10K 5% 4

*10K 5% 4 R330 10K 5% 4

[9]

GPIO_39

[9]

GPIO_40

[9]

GPIO_43

[9]

GPIO_44

[9]

SERIRQ IS 1.8V_S5 AT EC SIDE BUT

3V_S5 AT CPU/TPM SIDE

+1.8V_S5 +3V_S5

GPIO_47

GPIO_48

TP1

TP2

[9]

U22

TRST_N PIN

ML1220 Coin type

AHL03001031 [VDE] 17mAH

AHL03001057 [DBV] 17mAH

A A

R469

EJ@150K_ 1%_4

Quanta Computer Inc.

PROJECT :ZAJ

EC reset RTC

[21] CLR_ CMOS

R88 *S 4 ACP RESENT R475

CN13 Q34 E J@PMS T3904

3

4

EJ@530 14-00201-V 09

3

V CCRTC 3

VCCRTC 2

1

RTC_TES T#

RTC_RS T#

5

2

Q11A Q1 1B

2N7002KDW

20K_1 %_4

C253

BAT54CW

R463 1K 1% 4

1

Trace width = 20 mils

Q29A

3

4

Q29B

6

1

2N7002KDW

+3VPC U

+3V RTC 1

RTC Circuitry (RTC)

CN7

1

2

R45 R38

4.7K_5 %_4 4.7K _5%_4

CLK_S DATA [18]

CLK_S CLK [18]

DDR_GS/S0

R365

1K_1%_4

PCH_MB DAT0_R

PCH MBC LK0 R

APL S5

R368

1K_1%_4

[21,22] SB _ACDC

B B

Size Docum ent Number

BXTP (PMU/PMIC/HDA/RTC)

Date: Tuesday March 21 2017 Sheet 6 of 34

5 4 3 2 1

Rev

3A

+3V_S5 +3V

CB@cabl e RTC 1u/6.3V _4

R246

20K_1 %_4

C254

1u/6.3V _4

20MIL

J1

*JUMP

RTC TEST#

+5V_S5

RTC Clock 32.768KHz (CPU)

C47 15p/50V 4

Trace length < 1000 mils

C34 15p/50V 4

5 4 3 2 1

Apollolake (PMU/PMIC/HDA)

colsed to CPU pin within 100 mils

C50 0.1u/16V 4 R61 10 5% 4

06

U21F APL BGA 1296P

RTC_TEST#

PMU_WA KE#

AH49

AC57

E47

AG55

RTC_RS T_N

SUSPWR DNACK

SUS_ST AT_N

AVS_I2S1_ WS_SYNC

AVS_I2S1_SDO

AVS_I2S1_SDI

AVS_I2S1_MCLK

AVS_I2S1_BCL K

AVS_I2S2_SDO

AVS_I2S2_SDI

AVS_I2S2_MCLK

AVS_I2S2_BCL K

AVS_I2S2_ WS_SYNC

AVS_I2S3_ WS_SYNC

AVS_I2S3_SDO

AVS_I2S3_SDI

AVS_I2S3_BCL K

AVS_DMIC_DAT A_2

AVS_DMIC_DAT A_1

AVS_DMIC_CL K_B1

AVS_DMIC_ CLK_AB2

AVS_DMIC_CL K_A1

VCC_RT C_EXT PAD

RTC_X2

RTC_X1

JTAG_PR EQ_N

JTAG_PR DY_N

JTAG_P MODE

JTAG_T RST_N

JTAG_TMS

JTAG_T DO

JTAG_TDI

JTAG_ TCK

GPIO_219

GPIO_218

GPIO_217

GPIO_216

PCIE_REF_CLK_RCO MP

SVID0_DATA

SVID0_CLK

SVID0_AL ERT_N

AC55

AC63

AG58

J62

K62

K61

G62

H63

M58

K59

K58

H59

M57

M61

L63

L62

M62

M52

M54

P52

M55

P54

_

PCH_S USPWR DNA CK

TP6

GPIO 78

GPIO_88

HDA_RST#_ R

GPIO_92

GPIO_82

RTC_TE ST_N

RSM_RST_N

PROCH OT_N

PMU_WA KE_N

PMU_SUSCLK

PMU_SLP_S4_N

PMU_SLP_S3_N

PMU_SLP_S0_N

PMU_RS TBTN_N

PMU_RCOMP

PMU_PW RBTN_ N

PMU_PLT RST_N

PMU_BATL OW_N

PMU_AC_PR ESENT

SOC_P WROK

PMIC_TH ERMTRIP_N

PMIC_STDBY

PMIC_SD WN_B_G PIO_213

PMIC_RESET_ N

PMIC_PW RGOO D

PMIC_I2C_SD A

PMIC_I2C_SCL

GPIO_214

GPIO_215

PMC_SPI_TXD

PMC_SPI_RXD

PMC_SPI_FS 2

PMC_SPI_FS 1

PMC_SPI_FS 0

PMC_SPI_CLK

PWM0

PWM1

PWM2

PWM3

JTAGX

INTRUDER

SMB_DATA

SMB_CLK

SMB_ALERT_N

RSVD_H43

RSVD_AG52

RSVD_J4 3

RSVD_AG54

[21] RSMRST#

[21,22,26] H _PROCHO T#

[21] SUSC#

[21] SUSB#

[21] DNBSW ON#

[21] EC_PWROK

PCH_S USPWR DNA CK

H_PRO CHOT#

THERM TRIP# SOC

PCH_SUSPW RDNA CK [21]

GPIO_ 78 [9]

PMU SUS CLK

AE62

AK54

AC62

PMU_S LP_S0 #

AD61

PMU_RSTBTN# AD62

PMU_RCOM P

AK55

TP37

TP38

TP36

D C D

C

GPIO_ 88 [9]

R52 33_5%_4

PCI_PLTRS T#

PCH_BAT LOW#

ACPRESEN T

THER MTRI P#_S OC

C79

0.1u/16 V_4

R83

10_5%_4

colsed to PU pin within 100 mils

AG57

AH51

AK49

AG49

J47

J45

M47

F48

H48

F47

H45

L47

P47

H50

J50

M48

P48

L48

E52

B41

C41

F41

E41

AZ_CO DEC_ RST # [14]

+1.8V_ S5

R384

R17

R23

+3V_S5

R82

R71

R85

R389

R67

R81

GPIO_ 92 [9]

GPIO_ 82 [9]

FOLLLOW AP L MOW31:

UN-STUFF 51 OHM PULL DOWN RESISTOR ON

*10K 5% 4

1K 1% 4

*10K 5% 4

*100K 5% 4

AG51

AC58

RTC_X2

AC59

RTC_X1

C58 0.1u/16V 4

INT_ED P_HPD#

GPIO_ 34

GPIO_ 35

GPIO_ 36

[12] INT_EDP_HPD #

[9] GPI O_34

[9] GPI O_35

[9] GPI O_36

100 1% 4

100 1% 4

*51 5% 4

51 5% 4

100 1% 4

51 5% 4

51 5% 4

60.4 1% 4

220 5% 4

B21

R62 330K 5% 4 INTRUDER #

AC54

+3V_R TC

PCH MBD AT0 R

PCH_MB CLK0_ R

PLTRST# [12,15,16,17,21]

T61

T62

R63

H43

AG52

J43

AG54

PLTRST# Buffer

PCI_PLTRS T#

Section 6 of 12

THERMALTRIP#

THER MTRI P#_S OC

R66

Q5 10K_5 %_4

3 1

2N7002K

colsed to CPU pin within 100 mils

C70

0.1u/16 V_4

R72

10_5%_4

SMBus(PCH)

R24 *S 4

_ _ _

_ _

RTC RST# _ _

_ _

_ _

_ _

_

_ _

_ _

_ _ _

C

_ _

_ _ _ _ _ _ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _

_ _ _ _

_ _

_ _

_

_ _ _ _ _ _

_ _

_ _

_

_ _

. _ _4

_

, ,

VCCR TC_4

EJ@4. 7K_5% _4

R474 EJ@4 7K 5%

R468

EJ@68. 1K_1% _4

+3V_RTC

Trace width = 20 mils

+3V_RTC

D26

2

R245

3

RTC R ST#

1K 1% 4

10K 5% 4 ACPRESE N T

10K 5% 4

*100K _5%_4 RS MRST#

20K 1% 4

R73 200 1% 4

AG59

PCH_BAT LOW#

PMU_WAKE#

PMU_RS TBTN#

EC PWROK

+3V

+1.8V_S 5

XDP_P REQ#

XDP_P RDY#

XDP_ TRST#

XDP_ TMS

XDP_ TDO

XDP_ TDI

XDP_ TCK

CLKDR V_RCOMP

C20

R307

C21

R306

B19

C24

R322

C23

R303

A22

R30 4

C22

R305

B23

R33 5

L30

M30

M29

P30

E21

R42

C18

C17

B17

SVID_ALERT#_R

R329

+1.05V

R323 R324 C313

169_1%_ 4 68_1%_4 1000p /50V_4

H CPU SVIDDAT

VR_SV ID_AL ERT#_VC ORE

H_CPU_SVIDDAT [26]

H_CPU_SVIDCLK [26]

VR_SV ID_ALE RT#_VCORE [26]

THERM TRIP# [21]

CH01006JB08 -> 10p

CH01506JB06 -> 15p

CH-6806TB01 -> 6.8p

RTC X1

Y1 R60

32.768KHZ/20 ppm

10M_5%_4

RTC_X2

Quanta Computer Inc.

PROJECT :ZAJ

Rev

3A

Size Docum ent Num ber

BXTP (POWER)

Date: Tuesday , March 21, 2017 Sheet 7 of 34

5 4 3 2 1

5 4 3 2 1

Apollolake (POWER)

+VCC_VCCGI

07

+VNN

C304 C302 C29 3 C297 C3 01 C292 C298

47u/6.3 V_8 47u/6.3V _8 47u/6.3V _8 47 u/6.3V _8 4 7u/6.3 V_8 47u/6. 3V_8 47u/ 6.3V_8

U21H APL BGA 1296P

RSVD_AJ 44

VCC_VCGI_1

VCC_VCGI_2

VNN_SVID_1

VCC_VCGI_3

VNN_SVID_2

VCC_VCGI_4

VNN_SVID_3

VCC_VCGI_5

VNN_SVID_4

VCC_VCGI_6

VNN_SVID_6

VCC_VCGI_8

VNN_SVID_7

VCC_VCGI_9

VNN_SVID_8

VCC_VCG I_10

VNN_SVID_9

VCC_VCG I_11

VNN_SVID_10

VCC_VCG I_12

VNN_SVID_11

VCC_VCG I_13

VNN_SVID_12

VCC_VCG I_14

VCC_VCG I_15

VNN_SEN SE

VCC_VCG I_16

AJ44

AJ37

AJ39

AJ41

AJ42

AJ46

AK37

AK39

AK41

AK42

AK44

AK46

AM44

AG48

BG63

AC41

AA42

Y44

V44

V46

AJ25

AK25

AC22

AC20

AG20

AJ20

AJ22

AE18

AE20

AE22

AG22

AM20

AM28

AM37

AK20

AA18

AA20

AA36

AA37

AA39

AC36

AC37

AE36

AE37

AG36

E43

E45

E48

E50

R45

R47

U36

U37

U39

U41

U42

U44

U46

U47

U48

V36

V37

V39

V41

Y36

Y37

Y39

Y41

AA28

AA30

AA32

AC28

AC30

AC32

AE28

AE30

AE32

AG28

AG30

AG32

AJ28

AJ30

AJ32

AK28

AK30

AK32

AK34

AM30

E29

E35

E37

F29

U28

U30

U32

V28

V30

V32

Y28

Y30

Y32

AA25

AC25

AE25

U22

U23

V22

V23

V25

Y23

Y25

U25

U20

C4 C296 C 300

47u/6.3 V_8 47u/6.3 V_8 4 7u/6.3V _8

C8 C33 C41

22u/6.3 V_6 22u/6.3 V_6 2 2u/6.3V _6

C24 C14 C13

1u/6.3V _4 1u/6 .3V_ 4 1u/6.3V_ 4

+

C3

330u/2V _7343 H1.9

C66 C81 C46 C7 C6

22u/6.3 V_6 22u/6.3V_6 22u/6 .3V_6 22u/6 .3V_6 22u/6.3 V_6

C27 C23 C12 C39 C 31 C16 C 15 C11 C2 9

1u/6.3V_ 4 1u/6.3 V_4 1u/6.3 V_4 1u/6. 3V_4 1u/6.3V_4 1u/6.3 V_4 1u/6 .3V_4 1u/6 .3V_4 1u/6.3V_4

D

C

B

A

D

C

B

A

C65 C87 C85

22u/6.3V_6 22u/6. 3V_6 22u/6.3 V_6

+1.35VS US

C64

22u/6.3V_ 6

C84

22u/6.3V_ 6

C73

1u/6.3V_ 4

C77

1u/6.3V_ 4

C78 C76

1u/6.3V_4 1u/6. 3V_4

[26] VNN_SE NSE

+VCC_3.3V

+3V_S5

R84 *S 6

C38

1u/6.3V_ 4

+1.24V _S5

R395 *S 4

R394 *S 6

C72

1u/6.3V_ 4

R387 *S 6

C56

1u/6.3V_ 4

R396 *S 6

C86

1u/6.3V_ 4

R388 *0 5% 6

+1.8V_S 5

R86 *S 6

C62

1u/6.3V_ 4

+1.05V

R373 *S 8

R378 *S 8

C21

1u/6.3V_ 4

C37 C48

1u/6.3V_4 1u/6. 3V_4

C92

22u/6.3 V_6

C67

1u/6.3V_ 4

+VCC_ 1.24V _USB2

+VCC_ 1.24V _AUD_ ISH_ PLL

C74 C3 48

1u/6.3V_ 4 22u/6.3V_6

C71 C49

1u/6.3V_ 4 1u/6.3 V_4

C82 C83

1u/6.3V_ 4 1u/6.3 V_4

C57 C60

*1u/6. 3V_4 *1u /6.3V _4

+VCC 1.8V

C59 C63

1u/6.3V_ 4 1u/6.3 V_4

C17 C44

1u/6.3V_ 4 1u/6.3 V_4

+1.05V

+VCC_1.24V_ MPH Y

C68

22u/6.3V_ 6

+VCC 1.24V GLM

C80 C351

1u/6.3V_ 4 22u/6.3V_ 6

RSVD_AM32

+VCC 1.24V D SI CSI

+VCC 1.24V AU D ISH PLL

AK22

V48

AA46

AC46

AE44

AE42

AC42

AC44

C69

*22u/6 .3V_6

C61 C91

1u/6.3V_ 4 22u/6.3 V_6

+3V_RTC

C45 1u/6.3V 4

+VCC_1.05V_ IO

C20 C40

1u/6.3V_ 4 22u/6.3 V_6

+VCC_ 1.05V _INT

R383 *S_6

AE46

AG25

BJ3

BJ61

AA44

D1

AA22

AC23

V18

Y18

Y20

AA23

P16

T15

T13

AN18

AN20

AN22

AN23

AN41

AN42

AN44

AN46

AR17

AR47

AT13

AT17

AT47

AT51

AV14

AV50

AM32

VCCRTC _3P3V

RSVD_D1

VCC_1P05V_IO_ 1

VCC_1P05V_IO_ 2

VCC_1P05V_IO_ 3

VCC_1P05V_IO_ 4

VCC_1P05V_IO_ 5

VCC_1P05V_3PH ASEI

VCC_1P05V_FUSE

VCC_1P05V_FHV1

VCC_1P05V_FHV0

2.7A

Section 8 of 12

VCC_1P05V_1

VCC_1P05V_2

VCC_1P05V_3

VCC_1P05V_4

VCC_1P05V_5

VCC_1P05V_6

VCC_1P05V_7

VCC_1P05V_8

VCC_1P05V_9

VCC_1P05V_10

VCC_1P05V_11

VCC_1P05V_12

U21I APL BGA 1296P

RSVD_BJ62

BJ62

R41

R43

AM23

AM25

AM41

AM42

AN32

VCC_VCGI_SE NSE_P

VCC_VCGI_SENSE_N

2.8A

VCCIOA_1

VCCIOA_2

VCCIOA_3

VCCIOA_4

C99 C88 C94 C 95 C 89 C98 C100

22u/6.3 V_6 22u/6.3V _6 22u/6.3V _6 22 u/6.3V _6 2 2u/6.3 V_6 22u/6. 3V_6 22u/ 6.3V_6

C104 C96

1u/6.3V_4 1u/6. 3V_4

_ _

_ _ _ _ _ _ _ _ _ _

_ _

_ _ _ _

_ _ _

_ _ O

_ _

VNN_SVID_5

4.8A

VCC_VCGI_7

_17

21A

VCC_VCGI

RSVD_BG63

VCC_VC GI_18

VCC_VCG I_19

VCC_3P3V_A _1

VCC_VCG I_20

VCC_3P3V_A _2

VCC_VCG I_21

VCC_3P3V_A _4

VCC_VCG I_23

VCC_3P3V_A _5

VCC_VCG I_24

VCC_3P3V_A_USB_1

VCC_VCG I_25

VCC_3P3V_A_USB_2

VCC_VCG I_26

VCC_VCG I_27

RSVD_AC 22

VCC_VC GI_28

VCC_VCG I_29

RSVD_AC 20

VCC_VC GI_30

VCC_VCG I_31

VCC_1P24V_1P35V_A_ USB2

VCC_VC GI_32

VCC_VCG I_33

VCC_1P24V_1P35V_ A_PLL_1

VCC_VCG I_34

VCC_1P24V_1P35V_ A_PLL_2

VCC_VCG I_35

VCC_VCG I_36

VCC_1P24V_1P35V_A _MPHY_1

VCC_VC GI_37

VCC_1P24V_1P35V_A _MPHY_2

VCC_VC GI_38

VCC_1P24V_1P35V_A _MPHY_3

VCC_VCGI_39

VCC_1P24V_1P35V_A _MPHY_4

VCC_VC GI_40

VCC_VCG I_41

VCC_1P24V_1P35V_ A_GLML2LDO_1

VCC_VC GI_42

VCC_1P24V_1P35V_ A_GLML2LDO_2

VCC_VC GI_43

VCC_1P24V_1P35V_ A_GLML2LDO_3

VCC_VC GI_44

VCC_1P24V_1P35V_A _GLML2

VCC_VC GI_45

VCC_VCG I_46

VDD2_1P24_DSI_CSI# 1

VCC_VC GI_47

VDD2_1P24_DSI_CSI# 2

VCC_VC GI_48

VCC_VCG I_49

VCC_1P24V_1P35V_ A_AUD_ISH

VCC_VCG I_50

VCC_VCG I_51

RSVD_V48

VCC_VCG I_52

VCC_VCG I_53

VCC_VCG I_54

VCC_1P8V_A _1

VCC_VCG I_55

VCC_1P8V_A _2

VCC_VCG I_56

VCC_1P8V_A _3

VCC_VCG I_57

VCC_1P8V_A _4

VCC_VCG I_58

VCC_1P8V_A _5

VCC_VCG I_59

VCC_1P8V_A _6

VCC_VCG I_60

VCC_1P8V_A _7

VCC_VCG I_61

VCC_1P8V_A _8

VCC_VCG I_62

VCC_VCG I_63

VCC_VCG I_64

RSVD_BJ3

RSVD_BJ 61

VCC_3P3V_A _3

0.15A

VCC_VCG I_22

1.3A

0.4A

RSVD_AN3 2

Section 9 of 12

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

+VCC_ 1.05V _IO

C35 C32 C 25 C19 C 30 C26

22u/6.3 V_6 22u/6. 3V_6 1u/6.3V _4 1u/6.3V _4 1u/6.3V_ 4 1u/6.3V _4

VCCGI_SE NSE [26]

VCCGI SS_SE NSE [26]

C305 C303 C93 C90

22u/6.3V_ 6 22u/6 .3V_6 1u/6 .3V_4 1 u/6.3V _4

+VNN

5

R29

A12

A16

A20

A24

A28

A32

A36

A40

A44

A48

A5

A52

A56

A62

A9

AA1

AA2

AA27

AA34

AA41

AA63

AB10

AB12

AB16

AB48

AB5

AB52

AB57

AB59

AB9

AC18

AC27

AC34

AC39

AE1

AE10

AE11

AE13

AE14

AE16

AE17

AE2

AE23

AE27

AE34

AE39

AE4

AE41

AE47

AE48

AE5

AE50

AE51

AE53

AE54

AE56

AE57

AE59

AE63

AE7

AE8

AG13

AG18

AG23

AG27

AG34

AG37

AG39

AG41

AG42

AG44

AG46

AH15

AH16

AH48

AH5

AH52

AH54

AH55

AH57

5

4

Apollolake ULT (GND)

U21J APL_BGA_1296P U21K APL_BGA_1296P

3

L43

L45

L50

M14

M21

M27

M3

M32

M50

M59

M9

N1

N32

N63

P13

P19

P35

P37

P41

P43

P45

P5

P55

P59

P9

R23

R32

T49

U1

U10

U11

U13

U14

U16

U17

U18

3 2 2

1

08

M12

C15

F16

J16

D8

E8

H16

C9

F8

E10

E16

F14

F12

H10

H14

H12

A14

C14

M39

P39

R39

R37

C2

J29

P25

R30

C63

E63

D2

AP57

VSS_163 VSS_244

VSS_164 VSS_245

VSS_165 VSS_246

VSS_166 VSS_247

VSS_167 VSS_248

VSS_168 VSS_249

VSS_169 VSS_250

VSS_170 VSS_251

VSS_171 VSS_252

VSS_172 VSS_253

VSS_173 VSS_254

VSS_174 VSS_255

VSS_175 VSS_256

VSS_176 VSS_257

VSS_177 VSS_258

VSS_178 VSS_259

VSS_179 VSS_260

VSS_180 VSS_261

VSS_181 VSS_262

VSS_182 VSS_263

VSS_183 VSS_264

VSS_184 VSS_265

VSS_185 VSS_266

VSS_186 VSS_267

VSS_187 VSS_268

VSS_188 VSS_269

VSS_189 VSS_270

VSS_190 VSS_271

VSS_191 VSS_272

VSS_192 VSS_273

VSS_193 VSS_274

VSS_194 VSS_275

VSS_195 VSS_276

VSS_196 VSS_277

VSS_197 VSS_278

VSS_198 VSS_279

VSS_199 VSS_280

VSS_200 VSS_281

VSS_201 VSS_282

VSS_202 VSS_283

VSS_203 VSS_284

VSS_204 VSS_285

VSS_205 VSS_286

VSS_206 VSS_287

VSS_207 VSS_288

VSS_208 VSS_289

VSS_209 VSS_290

VSS_210 VSS_291

VSS_211 VSS_292

VSS_212 VSS_293

VSS_213 VSS_294

VSS_214 VSS_295

VSS_215 VSS_296

VSS_216 VSS_297

VSS_217 VSS_298

VSS_218 VSS_299

VSS_219 VSS_300

VSS_220 VSS_301

VSS_221 VSS_302

VSS_222 VSS_303

VSS_223 VSS_304

VSS_224 VSS_305

VSS_225 VSS_306

VSS_226 VSS_307

VSS_227 VSS_308

VSS_228 VSS_309

VSS_229 VSS_310

VSS_230 VSS_311

VSS_231 VSS_312

VSS_232 VSS_313

VSS_233 VSS_314

VSS_234 VSS_315

VSS_235 VSS_316

VSS_236 VSS_317

VSS_237 VSS_318

VSS_238 VSS_319

VSS_239 VSS_320

VSS_240 VSS_321

VSS_241 VSS_322

VSS_242 VSS_323

VSS_243 VSS_324

Section 11 of 12

U21G APL BGA 1296P

SPARE_9

NOCONNECT_16

SPARE_8

NOCONNECT_17

SPARE_7

NOCONNECT_18

SPARE_6

NOCONNECT_19

SPARE_5

NOCONNECT_20

SPARE_4

NOCONNECT_21

SPARE_3

NOCONNECT_22

SPARE_2

NOCONNECT_23

SPARE_11

NOCONNECT_24

SPARE_10

NOCONNECT_25

SPARE_1

NOCONNECT_26

SPARE_0

NOCONNECT_27

NOCONNECT_28

NOCONNECT_1 NOCONNECT_29

NOCONNECT_2 NOCONNECT_30

NOCONNECT_3 NOCONNECT_31

NOCONNECT_4 NOCONNECT_32

NOCONNECT_5 NOCONNECT_33

NOCONNECT_6 NOCONNECT_34

NOCONNECT_7 NOCONNECT_35

NOCONNECT_8 NOCONNECT_36

NOCONNECT_9 NOCONNECT_37

NOCONNECT_10 NOCONNECT_38

NOCONNECT_11 NOCONNECT_39

NOCONNECT_12 NOCONNECT_40

NOCONNECT_13 NOCONNECT_41

NOCONNECT_14 NOCONNECT_42

NOCONNECT_15 NOCONNECT_43

B13

C13

L16

M16

E23

F23

R25

AB49

AC13

AB13

AM59

AM58

T51

L14

R19

E6

R17

E3

D4

A60

A61

BJ2

BG1

P27

A3

M10

B15

D

C

B

A

D

C

B

A

Rev

3A

Quanta Computer Inc.

PROJECT :ZAJ

Size Document Number

BXTP (GND)

Date: Tuesday, March 21, 2017 Sheet 8 of 34

1

_ _

VSS_1 VSS_82

VSS_2 VSS_83

VSS_3 VSS_84

VSS_4 VSS_85

VSS_5 VSS_86

VSS_6 VSS_87

VSS_7 VSS_88

VSS_8 VSS_89

VSS_9 VSS_90

VSS_10 VSS_91

VSS_11 VSS_92

VSS_12 VSS_93

VSS_13 VSS_94

VSS_14 VSS_95

VSS_15 VSS_96

VSS_16 VSS_97

VSS_17 VSS_98

VSS_18 VSS_99

VSS_19 VSS_100

VSS_20 VSS_101

VSS_21 VSS_102

VSS_22 VSS_103

VSS_23 VSS_104

VSS_24 VSS_105

VSS_25 VSS_106

VSS_26 VSS_107

VSS_27 VSS_108

VSS_28 VSS_109

VSS_29 VSS_110

VSS_30 VSS_111

VSS_31 VSS_112

VSS_32 VSS_113

VSS_33 VSS_114

VSS_34 VSS_115

VSS_35 VSS_116

VSS_36 VSS_117

VSS_37 VSS_118

VSS_38 VSS_119

VSS_39 VSS_120

VSS_40 VSS_121

VSS_41 VSS_122

VSS_42 VSS_123

VSS_43 VSS_124

VSS_44 VSS_125

VSS_45 VSS_126

VSS_46 VSS_127

VSS_47 VSS_128

VSS_48 VSS_129

VSS_49 VSS_130

VSS_50 VSS_131

VSS_51 VSS_132

VSS_52 VSS_133

VSS_53 VSS_134

VSS_54 VSS_135

VSS_55 VSS_136

VSS_56 VSS_137

VSS_57 VSS_138

VSS_58 VSS_139

VSS_59 VSS_140

VSS_60 VSS_141

VSS_61 VSS_142

VSS_62 VSS_143

VSS_63 VSS_144

VSS_64 VSS_145

VSS_65 VSS_146

VSS_66 VSS_147

VSS_67 VSS_148

VSS_68 VSS_149

VSS_69 VSS_150

VSS_70 VSS_151

VSS_71 VSS_152

VSS_72 VSS_153

VSS_73 VSS_154

VSS_74 VSS_155

VSS_75 VSS_156

VSS_76 VSS_157

VSS_77 VSS_158

VSS_78 VSS_159

VSS_79 VSS_160

VSS_80 VSS_161

VSS_81 VSS_162

Section 10 of 12

BG29

BG32

BG35

BG41

BG45

BH1

BH2

BH21

BH25

BH39

BH43

BH62

BH63

BJ10

BJ14

BJ18

BJ28

BJ32

BJ36

BJ4

BJ46

BJ50

BJ54

BJ56

BJ60

BJ8

C12

C16

C28

C32

C40

C48

D32

D58

D6

E12

E14

E19

E27

E4

E54

F10

F21

F3

F32

F37

F43

F45

F50

F56

F59

F63

G1

G32

H17

H23

H29

H3

H37

H47

H61

H7

J12

J14

J19

J27

J30

J32

J35

J37

J48

J63

K32

K5

K54

K57

K6

L21

L27

L29

L35

U21L APL_BGA_1296P

U2

U27

U34

U5

U50

U51

U53

U54

U56

U57

U59

U62

U63

U7

U8

V20

V27

V34

V42

Y12

Y16

Y22

Y27

Y34

Y42

Y46

Y48

Y5

Y52

Y54

Y55

Y57

Y59

Y6

Y7

VSS_325 VSS_361

VSS_326 VSS_362

VSS_327 VSS_363

VSS_328 VSS_364

VSS_329 VSS_365

VSS_330 VSS_366

VSS_331 VSS_367

VSS_332 VSS_368

VSS_333 VSS_369

VSS_334 VSS_370

VSS_335 VSS_371

VSS_336 VSS_372

VSS_337 VSS_373

VSS_338 VSS_374

VSS_339 VSS_375

VSS_340 VSS_376

VSS_341 VSS_377

VSS_342 VSS_378

VSS_343 VSS_379

VSS_344 VSS_380

VSS_345 VSS_381

VSS_346 VSS_382

VSS_347 VSS_383

VSS_348 VSS_384

VSS_349 VSS_385

VSS_350 VSS_386

VSS_351 VSS_387

VSS_352 VSS_388

VSS_353 VSS_389

VSS_354 VSS_390

VSS_355 VSS_391

VSS_356 VSS_392

VSS_357 VSS_393

VSS_358 VSS_394

VSS_359 VSS_395

VSS_360

Sect 12/12

NOCONNECT_44

NOCONNECT_45

Section 7 of 12

AH58

AH59

AH6

AH7

AJ1

AJ18

AJ2

AJ23

AJ27

AJ34

AJ36

AJ63

AK10

AK12

AK18

AK23

AK27

AK36

AK48

AK5

AK52

AK59

AK9

AM18

AM22

AM27

AM34

AM36

AM39

AM46

AN1

AN10

AN11

AN13

AN14

AN16

AN17

AN2

AN25

AN27

AN28

AN30

AN34

AN36

AN37

AN39

AN47

AN48

AN5

AN50

AN51

AN53

AN54

AN56

AN57

AN59

AN63

AN7

AN8

AP55

AP9

AR19

AR32

AR45

AT12

AT16

AT19

AT2

AT25

AT29

AT3

AT35

AT39

AT45

AT48

AT52

AT57

AT61

AT62

AT7

AU32

4

AV19

AV2

AV21

AV23

AV29

AV3

AV32

AV35

AV41

AV43

AV45

AV55

AV61

AV62

AV9

AW14

AW30

AW34

AW50

AY10

AY32

AY54

AY58

AY6

B2

B3

B62

B63

B9

BA1

BA12

BA16

BA17

BA2

BA21

BA25

BA27

BA29

BA32

BA35

BA37

BA39

BA43

BA47

BA48

BA52

BA62

BA63

BB19

BB25

BB3

BB39

BB45

BB61

BC32

BD3

BD32

BD56

BD61

BD8

BE1

BE10

BE12

BE16

BE17

BE21

BE27

BE29

BE35

BE37

BE43

BE47

BE48

BE52

BE54

BE63

BF3

BF32

BF61

BG19

BG23

GPIO_36

Rev

3A

Size Document Number

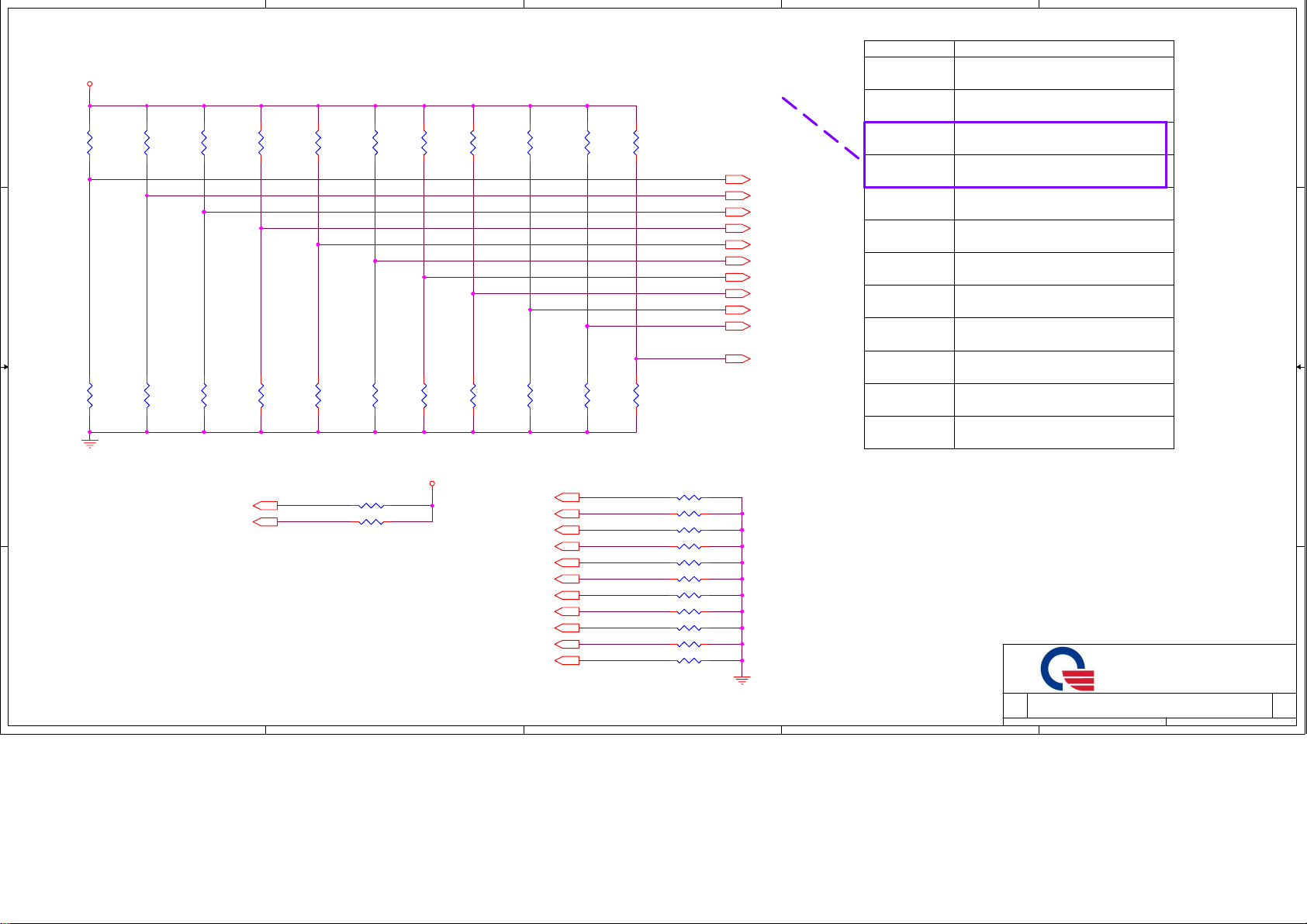

HARDWARE STRAPS

Date: Tuesday, March 21, 2017 Sheet 9 of 34

5 4 3 2 1

5 4 3 2 1

HARDWARE STRAPS

09

D

C

Hardware Strap Strap Descr iption

VCC_1P24V_1P35V_A voltage select

GPIO_36 0 = 1.24V

1 = 1.35V

Enable CSE(TXE3.0) ROM Bypass

GPIO_39 0 = Disable bypass

1 = Enable Bypass

Allow eMMC as a boot source

GPIO_43 0 = Disable

1 = Enable

Allow SPI as a boot source

GPIO_44 0 = Disable

1 = Enable

Force DNX FW Load

GPIO_47 0 = Do not force

1 = Force

SMBus 1.8V/3.3V mode select

GPIO_78 0=buffers set to 3.3V

1=buffers set to 1.8V

PMU 1.8V/3.3V mode select

GPIO_88 0=buffers set to 3.3V mod e

1=buffers set to 1.8V mod e

SMBus No Re-Boot

GPIO_92 0 = Disable (default)

1 = Enable

LPC 1.8V/3.3V mode select

GPIO_110 0=buffers set to 3.3V mod e

1=buffers set to 1.8V mod e

Boot BIOS Strap

GPIO_111 0 = Boot from SPI

1 = Do not boot from SPI

Top swap override

GPIO_120 0 = Disable

1 = Enable

FOLLLOW APL WOW36:

ENABLE BOOT FROM SPI

GPIO_43=0;GPIO_44=1

+1.8V_S5

R27 R310 R311 R312 R28 R360 R19 R363 R16 R26 R18

*4.7K_5%_4 *4.7K_5%_4 *4.7K_5%_4 4.7K_5%_4 *4.7K_5%_4 *10K_5%_4 *10K_5%_4 *4.7K_5%_4 *4.7K_5%_4 *10K_5%_4 *4.7K_5%_4

D

C

GPIO_36 [6]

GPIO_39 [5]

GPIO_43 [5]

GPIO_44 [5]

GPIO_47 [5]

GPIO_78 [6]

GPIO_88 [6]

GPIO_92 [6]

GPIO_110 [5]

GPIO_111 [5]

GPIO_120 [5]

A

Quanta Computer Inc.

PROJECT : ZAJ

B B

+1.8V_S5

GPIO_34

GPIO 35

GPIO_40

GPIO 48

GPIO_82

GPIO 104

GPIO_105

GPIO 117

GPIO_112

GPIO 113

GPIO_121

[6] GPIO_34

[6] GPIO_35

[5] GPIO_40

[5] GPIO_48

[6] GPIO_82

[5] GPIO_104

[5] GPIO_105

[5] GPIO_117

[5] GPIO_112

[5] GPIO_113

[5] GPIO_121

R346 10K 5% 4

R313 10K 5% 4

R334 4.7K 5% 4

R54 10K 5% 4

R59 10K 5% 4

R41 10K 5% 4

R43 10K 5% 4

R55 10K 5% 4

R57 4.7K 5% 4

R39 4.7K 5% 4

R35 10K 5% 4

R20 4.7K 5% 4

R356 10K 5% 4

[5] GPIO_106

[5] GPIO_123

A

_ _ _ _ _ _ _

_ _ _ _ _ _ _ _ _ _ _ _

_ _ _ _ _

_ _ _ _ _ _ _

_

GPIO 39

GPIO_43

GPIO_44

GPIO_47

GPIO_78

GPIO_88

GPIO_92

GPIO_110

GPIO_111

GPIO_120

R33 R343 R344 R345 R32 R364 R31 R367 R36 R29 R30

10K_5%_4 10K_5%_4 10K_5%_4 *10K_5%_4 10K_5%_4 10K_5%_4 10K_5%_4 10K_5%_4 4.7K_5%_4 4.7K_5%_4 10K_5%_4

[2] M_A_ A[15:0]

+1.35VS US

Distributed around all DRAM devices (CHA)

C362 C160 C16 2 C134 C12 0 C133

10u/6.3V _4 10u/6.3V _4 1 0u/6.3V _4 10u/6.3V_4 10u/6.3V_4 10 u/6.3V_ 4

Place these Caps near each X16 Memory Down

C148 C 366 C37 7 C157 C143 C153

1u/6.3V _4 1u/6. 3V_4 1u/6.3V_ 4 1u/6. 3V_4 1u /6.3V_4 1u/6.3 V_4

C365 C 361 C35 6 C357 C354 C369

Rev

3A

ize Documen t Num ber

DDR3L SODIMM-STD CHA

Date: Tuesday, Mar ch 21, 2017 hee t 10 of 34

5

4

3

2 1

FOLLLOW APL WOW37:MEMORY DOWN

ODT SINGLE ON DRAM SIDE IS PULLED UP TO VDDQ

+1.35VSUS

C140 C142 C147

3.65K_ 1%_4 470p/5 0V_4 0.1u/16V _4 2. 2u/10V _4

Quanta Computer Inc.

PROJECT :ZAJ

C367 C 373 C36 0 C379

M_A_ ODT0

1u/6.3V _4 1u/6. 3V_4 1u/6.3V_ 4 1u/6. 3V_4

A

1u/6.3V _4 1u/6. 3V_4 1u/6.3V_ 4 1u/6. 3V_4 1u /6.3V_4 1u/6.3 V_4 3.65K_ 1%_4

R147

M_A_C LK0#

VREF_DQ trace at least 20mils wide and space

+SMDD R_VRE F_D Q_A

A

+1.35VS US

R145

5

4

3

2 1

DDR3L MEMORY CHANNEL A

10

BYTE4_32-39

BYTE6_48-55

M_A_D Q38 [ 2]

M_A_D Q35 [ 2]

M_A_D Q37 [ 2]

M_A_D Q32 [ 2]

M_A_D Q39 [ 2]

M_A_D Q33 [ 2]

M_A_D Q36 [ 2]

M_A_D Q34 [ 2]

M_A_D Q55 [ 2]

M_A_D Q51 [ 2]

M_A_D Q50 [ 2]

M_A_D Q52 [ 2]

M_A_D Q48 [ 2]

M_A_D Q54 [ 2]

M_A_D Q49 [ 2]

M_A_D Q53 [ 2]

+1.35VS US

On board memory(OBM)

+SMDDR_VREF _CA_A M8

+SMDDR VREF DQ A H1

BYTE0_0-7

BYTE1_8-15

U24 U8

BYTE2_16-23

BYTE3_24-31

M_A_D Q19 [ 2]

M_A_D Q18 [ 2]

M_A_D Q23 [ 2]

M_A_D Q17 [ 2]

M_A_D Q21 [ 2]

M_A_D Q20 [ 2]

M_A_D Q22 [ 2]

M_A_D Q16 [ 2]

M_A_D Q28 [ 2]

M_A_D Q31 [ 2]

M_A_D Q30 [ 2]

M_A_D Q24 [ 2]

M_A_D Q27 [ 2]

M_A_D Q26 [ 2]

M_A_D Q29 [ 2]

M_A_D Q25 [ 2]

+1.35VS US

[2] M_A_DQ S7

[2] M_A_DQ S5

[2] M_A _DQS# 7

[2] M_A_ DQS#5

BYTE7_56-63

BYTE5_40-47

M_A_D Q62 [ 2]

M_A_D Q60 [ 2]

M_A_D Q56 [ 2]

M_A_D Q61 [ 2]

M_A_D Q57 [ 2]

M_A_D Q59 [ 2]

M_A_D Q58 [ 2]

M_A_D Q63 [ 2]

M_A_D Q40 [ 2]

M_A_D Q43 [ 2]

M_A_D Q46 [ 2]

M_A_D Q41 [ 2]

M_A_D Q44 [ 2]

M_A_D Q47 [ 2]

M_A_D Q45 [ 2]

M_A_D Q42 [ 2]

+1.35VS US

[2] M_A_DQS4

[2] M_A_DQ S6

[2] M_A _DQS# 4

[2] M_A _DQS# 6

U25