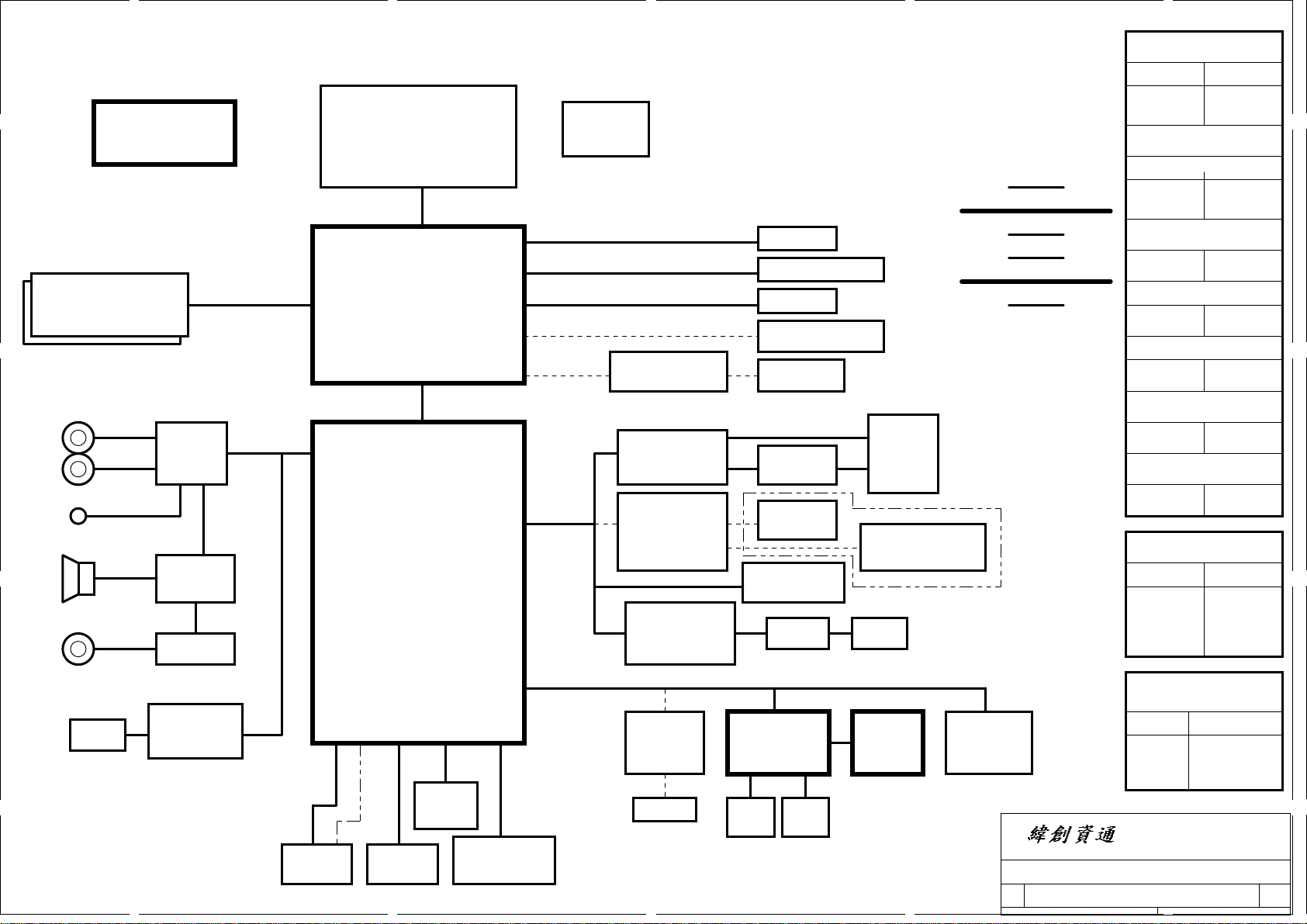

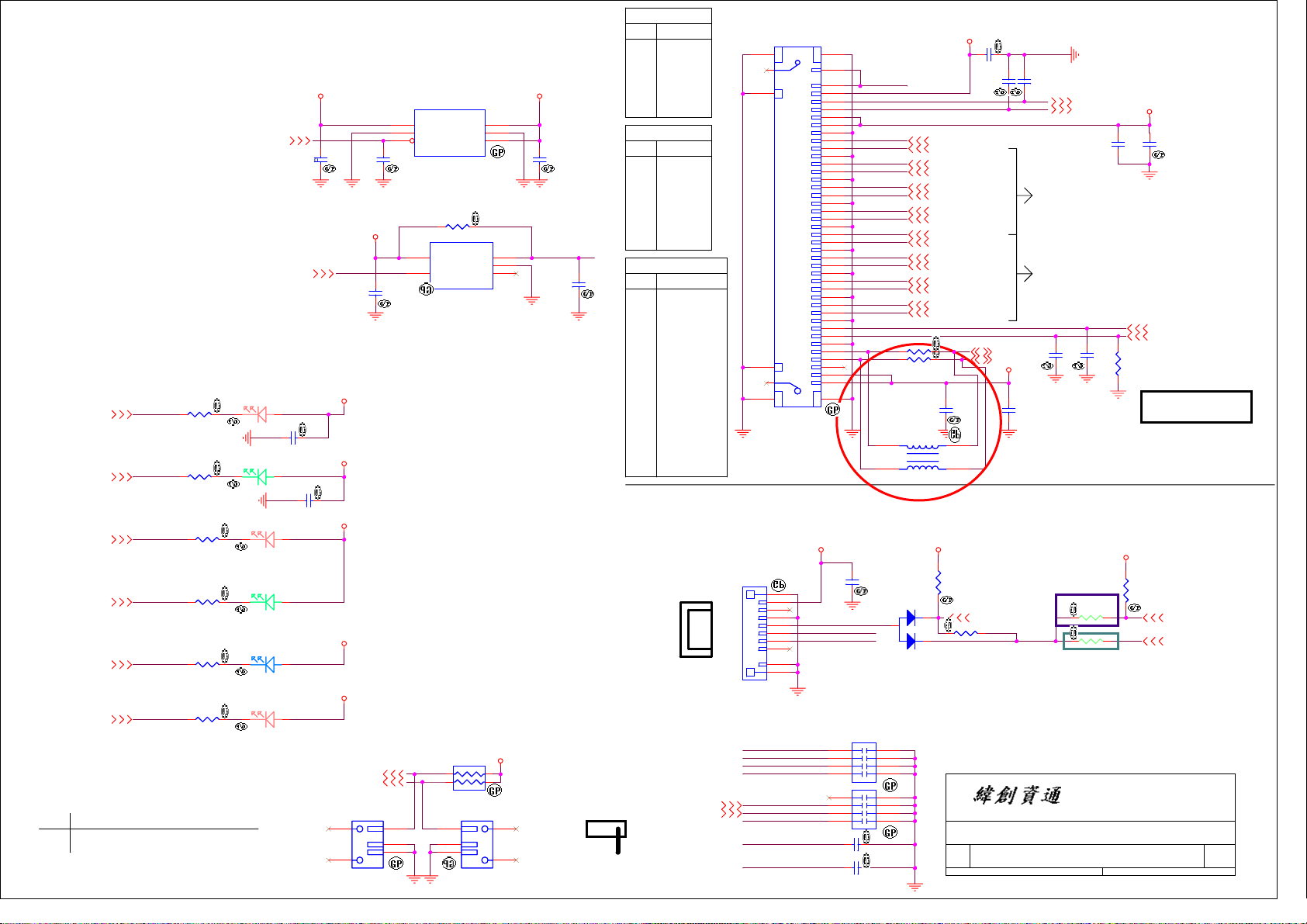

Acer Aspire 3640, Aspire 5590 TravelMate 2440 Schematics

A

B

C

D

E

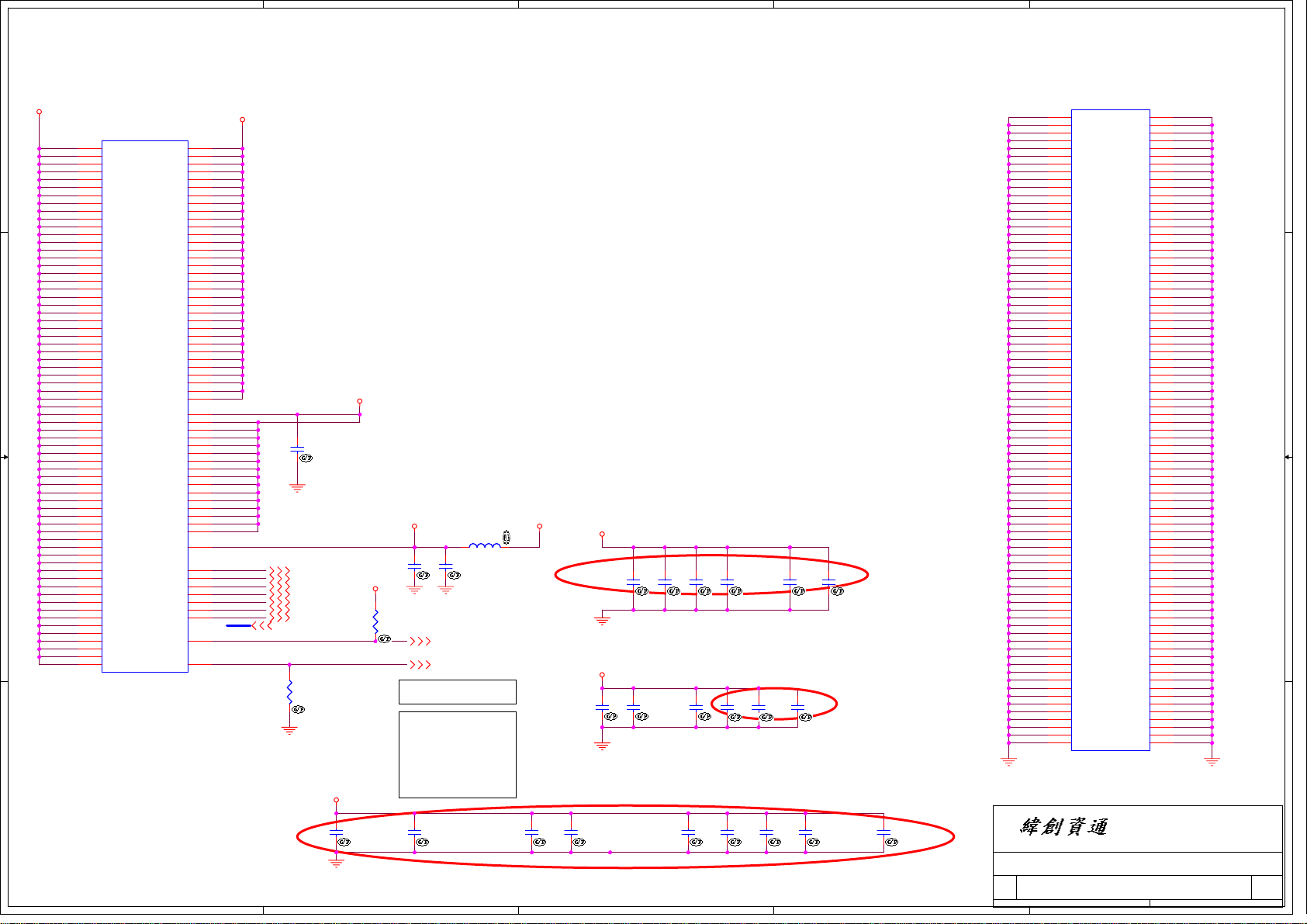

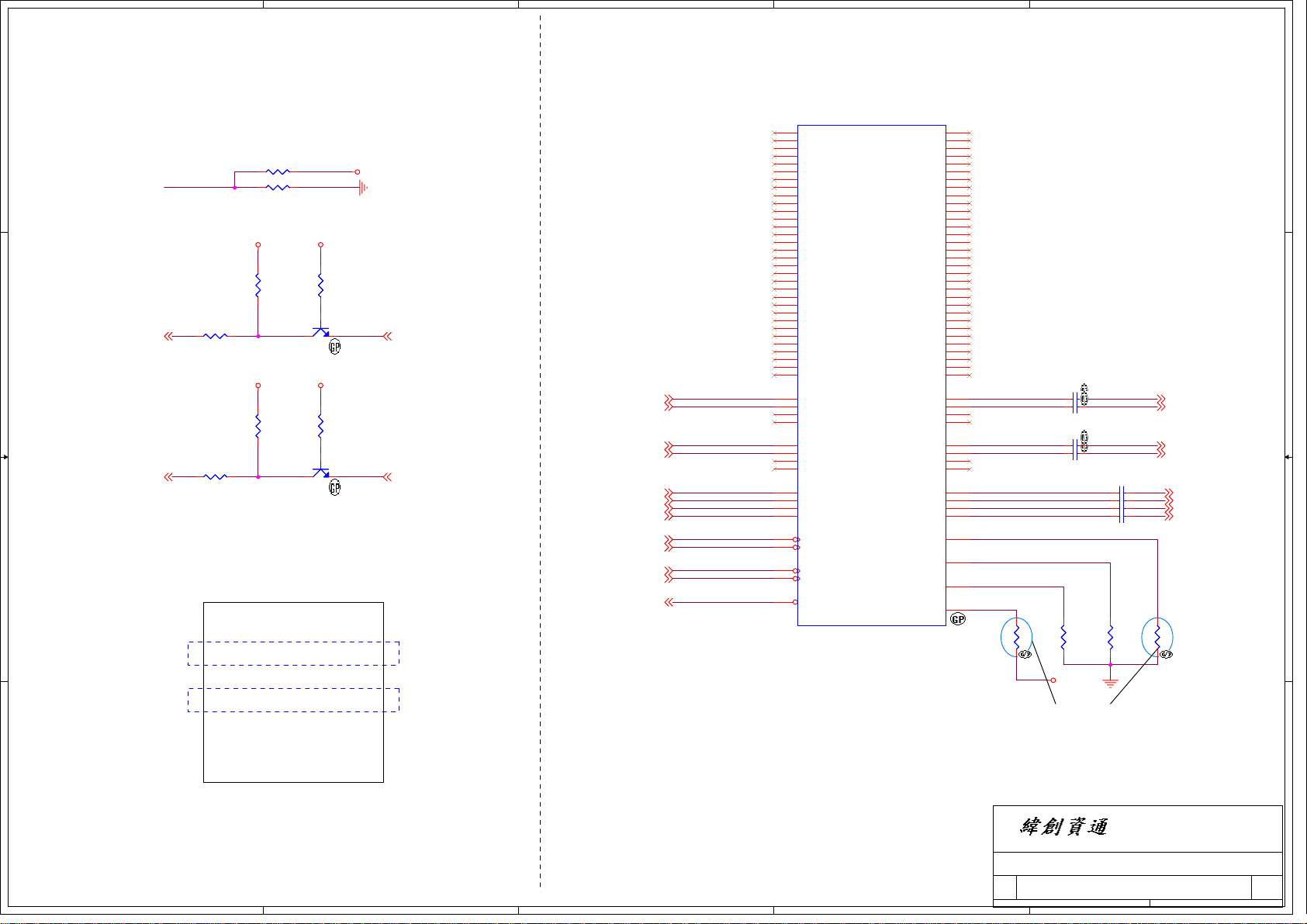

Garda-5 Block Diagram

PCB P/N : 55.4Q201.XXX

REVISION : 06206-SA

Project code: 91.4Q201.001

4 4

CLK GEN.

ICS951413

(RTM865T-300/CY28RS400)

DDR2 x 2

11,12

3 3

3

533/667MHz

Mobile CPU

Yonah 478

AGTL+

133/166MHz

ATI RC410ME

AGTL+ CPU I/F

SINGAL DDR2 CHANNEL

INTEGRATED GRAPHICS

LVDS/TVOUT/CRT

1 X4 PCIE SB I/F

6 X1 PCIE GPP I/F

Ver.:A13, 71.RC410.D0U

4, 5

6,7,8,9,10

G792

PCIE x 1

PCIE x 1

20

SVIDEO/COMP

LVDS

RGB CRT

New card

-1-0426

32

A-Link Express

Line In

31

31

Codec

ALC883

AZALIA

30

MIC In

INT.MIC

31

2 2

OP AMP

G1432Q

31

INT.SPKR

31

MAX4411

Line Out

(SPDIF)

MODEM

RJ11

1 1

MDC Card

22

HDD

X4

ATI SB460

USB2.0 8Ports

SATA II (4 PORTS)

AZALIA HD AUDIO 1.0

AC97 2.3

ATA 66/100/133

LPC I/F

ACPI 1.2

INT RTC

PCI/PCI BDGE

Lab Ver. :A11, 71.SB460.A0U

Eng Ver. :A12, 71.SB460.B0U

PATA

SATA

USB

3 PORT

CDROM

21

21

15,16,17,18,19

22

MINI USB

Blue-tooth

PCI BUS

LPC BUS

22

CARDBUS

ENE

CB1410

25

RICOH

R5C832

1394

CardReader

28,29

LAN

Reltek10/100

RTL8100CL

SIO

NS87381

FIR

35

35

23

Touch

Pad

(Hannstar, GCE)

PCB STACKUP

TOP

VCC

36

26

S

S

GND

BOTTOM

LPC

DEBUG

CONN.

29

36

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

TVOUT

14"WXGA+ LCD

CRT

Mini Card*1

14

14

802.11A/B/G

PWR SW

TPS2231

PCMCIA I/F

32

PWR SW

TPS2211

26

1394

CONN

29

Mini-PCI

802.11A/B/G

TXFM RJ45

KBC

ENE

3910

34 34

32

24

33

INT.

KB

13

27

PCMCIA

SLOT

Support

TypeII

MS/MS Pro/xD/

MMC/SD/SDIO

6 in 1

24

BIOS

MX29LV800

Garda-5 -1

Garda-5 -1

Garda-5 -1

SYSTEM DC/DC

TPS51120

INPUTS

DCBATOUT

41

OUTPUTS

5V_S5

3D3V_S5

SYSTEM DC/DC

1D8V_S3

1D2V_S0

120mA

1A

3A

1A

300mA

39,40

of

of

of

42

43

43

43

44

TPS51124RGER

INPUTS OUTPUTS

DCBATOUT

APL5312

3D3V_S0 1D5V_CPU_S0

APL5332

3D3V_S0 1D5V_NEW_

APL5912

1D2V_S0 1D05V_S0

TPS51100

1D8V_S3

APL5308

3D3V_S5 1D8V_S5

MAXIM CHARGER

DCBATOUT

CPU DC/DC

INPUTS

DCBATOUT

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

MINI_S0

DDR_VREF_S3

DDR_VREF_S0

MAX8725

OUTPUTSINPUTS

CHG_PWR

18V 4.0A

UP+5V

5V 100mA

ISL6262

OUTPUTS

VCC_CORE_S0

0~1.3V 48A

146Wednesday, April 26, 2006

146Wednesday, April 26, 2006

146Wednesday, April 26, 2006

43

43

A

USB

Pair

Device

USB1

0

BT

1

USB2

4 4

2

NEW C

3

4 USB3

5

CCD

MINIC1

6

NC

7

PCI_CLK0 PCM

PCI_CLK1 IEEE1394

PCI_CLK2 LAN

PCI_CLK3 MINI

PCI_CLK4 KBC

PCI_CLK5 FWH

PCI_CLK6 SIO

PCI_CLK7 SPDIFOUT

3 3

DEVICE

MiniPCI

R5C832

LAN(RTL8100CL)

CARDBUS CB1410

USB UHCI

USB 2.0 EHCI

DMI-to-PCI

AC97 Modem

AC97 Audio

LPC Bridge

IDE

SATA

SMBus

PCI Express

Azalia Controller AD27 A

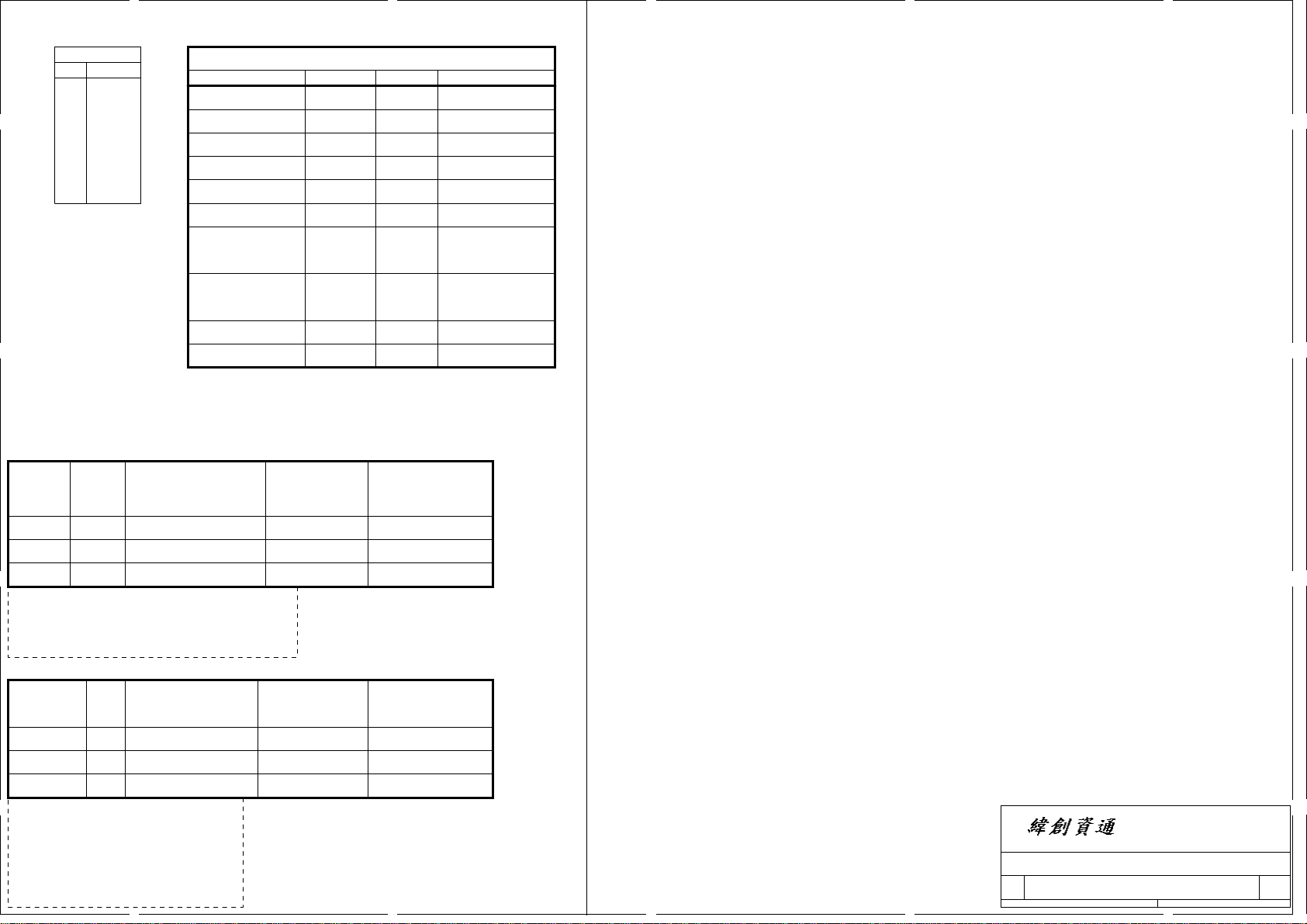

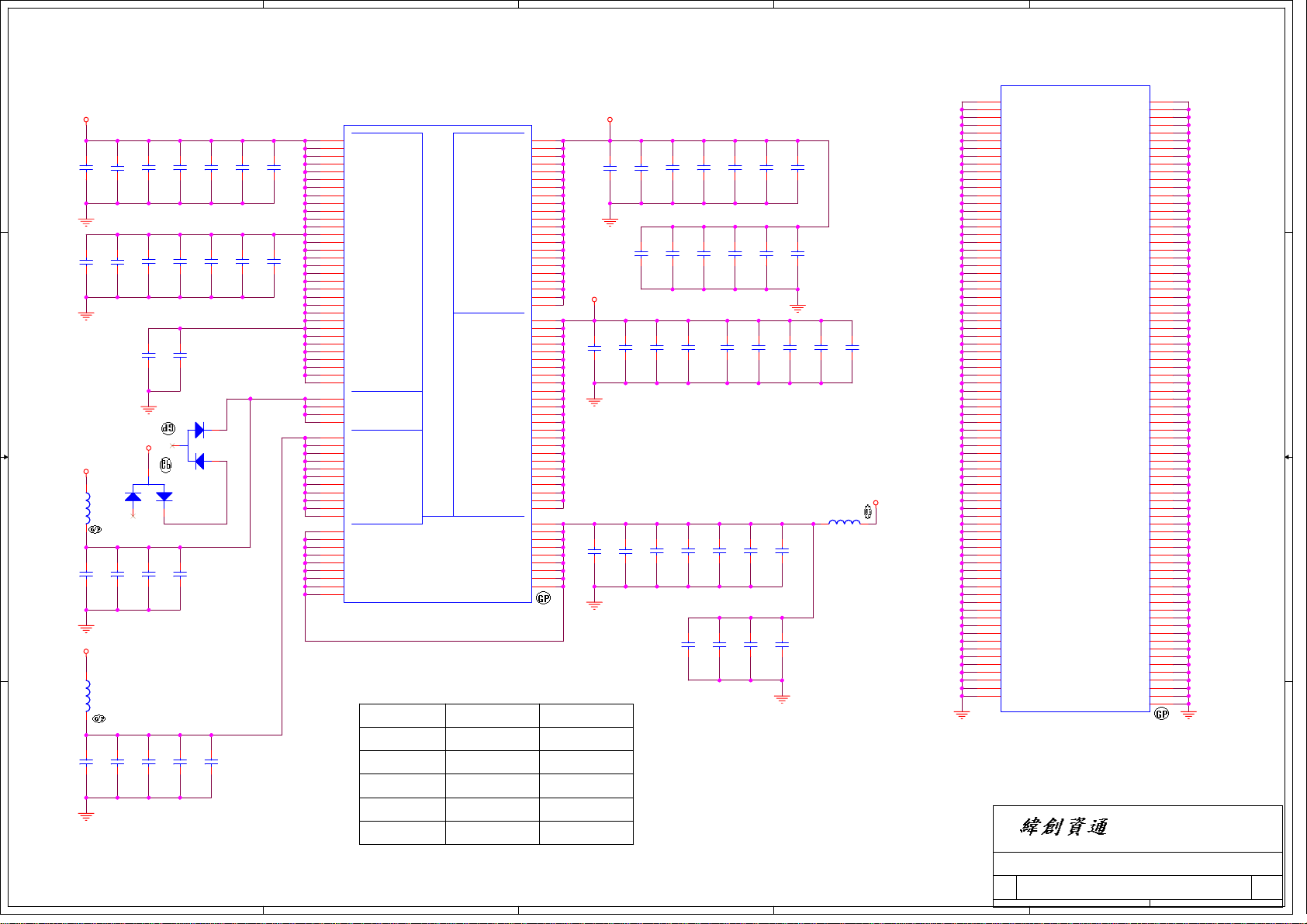

RESISTOR

Symbol name

10KR3

33D3R5

1KR3F

2 2

The naming rule is value + R + size + tolerance

For the value, it can be read by the number before R. (R means resistor)

For the tolerance, it can be read from the last letter.

For the rating, we don't show on the symbol name.

For the size, R2=>0402, R3=>0603, R5=>0805,....

Value

10K Ohm

33.3 Ohm

1K Ohm

Tolerance

(J: 5%, F: 1%, D: 0.5%, B: 0.1 %)

If no letter, it means J: 5%

If no letter, it means J: 5% 0805

F: 1%

CAPACITOR

Symbol name

SCD1U10V2MX-1

SC10U6D3V5MX

SC2D2U16V5ZY

The naming rule is

1 1

Capacitor type + value + rating + size + tolerance + material

SCD1U10V2MX-1

SC=> SMT Ceremic, TC=> POS cap or SP cap

D1U => 0.1uF

10V => the voltage rating is 10V

2=> 0402, 3=>0603, 5=>0805

M=>tolerance J, K, M, Z

X=> X7R/X5R, Y=> Y5V

-1 => symbol version, nonsense to EE characteristic

Value

0.1uF

10uF

2.2uF

Tolerance

(J: +/-5, K: +/-10,

M: +/-20, Z: +80/-20)

M/X5R

M/X5R

Z/Y5V

PCI ROUTING TABLE

IDSEL

AD22 H REQ#1/ GNT#1

AD20

AD16

AD29

AD29

AD30

AD31

AD28

Rating

0402=> 1/16W, 25V

0603 => 1/16W, 75V

0805 => 1/10W, 100V

1/16W, 75V

1/10W, 100V

1/16W, 75V

Rating

( X5R / X7R < 80%,

Y5V/Y5U/Z5U < 1/3 )

10V

6.3V

16V

B

IRQ(Default)

F : 1394

H : 6 in 1

E

G

A, B, C, D

A

B

A

A

B

B

A, B, C, D

Size

2=>0402, 3=>0603, 5=>0805,

6=>1206, 0=>1210

0603

0603

Size

2=>0402, 3=>0603, 5=>0805,

6=>1206, 0=>1210

0402

0805

0805

REQ# / GNT#

REQ#3/ GNT#3

REQ#2/ GNT#2AD17

REQ#0 / GNT#0

REQ#1 / GNT#1

C

History

===========================================================

2006/04/26 (-1 Modify)

1. page 27, change R8/R226 to 100 ohm due to power/email to dark.

2. page 15, change C286/C287 from 18pf to 15pf due to frequence shift(from -6.7 to 4ppm).

3. page 23, change C295/C294 from 15p to 12p due to frequence shift(from -23.3 to 7.9ppm).

4. EMI Solution for USB/MDC

a. Change L23, L24, L31, L32 to "69.10084.071".

b. del R353,R354,R356,R360,R445,R446.

c. Change L1, L2 to "68.00331.011".

5. Page 44, change C12/C14 to 78.10699.43L due to 78.10699.42L Obsoleted.

===========================================================

2006/04/13 (-1 Modify)

1. Page 31, R447/R448 tp 33ohm.

2. Page 45, Add D4:83.P4SSM.0AM.

3. Page 44, Change C321 from 78.10492.4BL to 78.10224.2BL(1000P, 50V, K0603).

4. Page 23, change R209 from 5.6K to 5.37K.

5. Page 24, change XF1 from 68.68161.30A to 68.01201.30A.

6. Page 46, Mini card stand-off(

7. change 84.27002.L04 to 84.27002.F31.

===========================================================

2006/04/10 (-1 Modify)

1. Page 8, add "LVDS_DIGON" solution from ATI PA note.

2. Page 31, Add R to GND and serial R for U60 pin13/15.

===========================================================

2006/04/03 (SB Modify)

1. Page 40, Dummy C593.

2. Page 44, Del C32.

3. Page 41, DCBATOUT_51120 change to DCBATOUT (Del G4,G5,G6,G7,G8)

4. Page 4/5, updae CPU symbol.

5. Page 15, Change X5 to same as X1 due to ME high limit issue, Cap. the same as X1 but should fine-tune.

6. Page 39/41/42, change "GAP-CLOSE-PWR" to 0 ohm PAD due to layout concern.

===========================================================

2006/03/31 (SB Modify)

1. Page 3, change R139 to bead and C211 to 2.2u for CRT Jitter.

2. Page 6, change R105 from 1.8K to 4.7K.

3. Page 8, change C165 to 2.2u for ATI recommend.

4. Page 8, SIV EDID_CLK/DAT issue, change RN53 to 4.7K.

5. Page 14, SIV RBG fail:

6. Page 15,

a. PCIRST1#(1394) shoulder: Add 33 ohm @ SB.

b. PLT_RST1# overshot : change R144 to 33ohm & R141 to 100P.

c. Add 0ohm for RTC power for ATI recommend.

7. Page 40 , add 10U Cap.

8. Page 13/27, change Green LED4/LED5/LED1 to 83.00190.L70.

(manual change yellow LED6/LED3/LED8/LED2 to 83.00190.S70).

9. EMI request:

a. Page 13, USB_PP5,USB_PN5 add COMMON CHOKE.

b. EC28,EC34,C208 add O.1μCap.

c. CLK48_ICH( near CLK GEN.),SB_CLK33_FWH(near R177) add 20p Cap..

===========================================================

2006/03/28 (SB Modify)

1. Page 14, change Q15/Q14 to 2N7002 for SIV CRT SMBus bug.

2. Page 15, Change C248/C261/C264/C263/C252 from 78.10491.4FL to 78.10523.5F1,

and C262 from 78.10693.41L to 78.10623.51L.

3. Page 8, Add "LCDVDD_ON" PL 100K.

4. Page 41, change U7 to AO4406(84.04406.A37).

5. Page 33, KBC GPIO09 for 1394.

6. Page 33, add 1u Cap. for ENE ECRST# spec. 2ms.

7. Page 31, add audio popo noise solution.

8. Page 25, change C520 to 1U for "GBRST#".

9. Page 28, change "GBUS_GRST#_1" timing.

===========================================================

銅柱

) need to be changed from 34.4P401.001 to 34.4A907.001.

D

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet

Reference

Reference

Reference

Garda-5 -1

Garda-5 -1

Garda-5 -1

E

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

of

246Wednesday, April 26, 2006

246Wednesday, April 26, 2006

246Wednesday, April 26, 2006

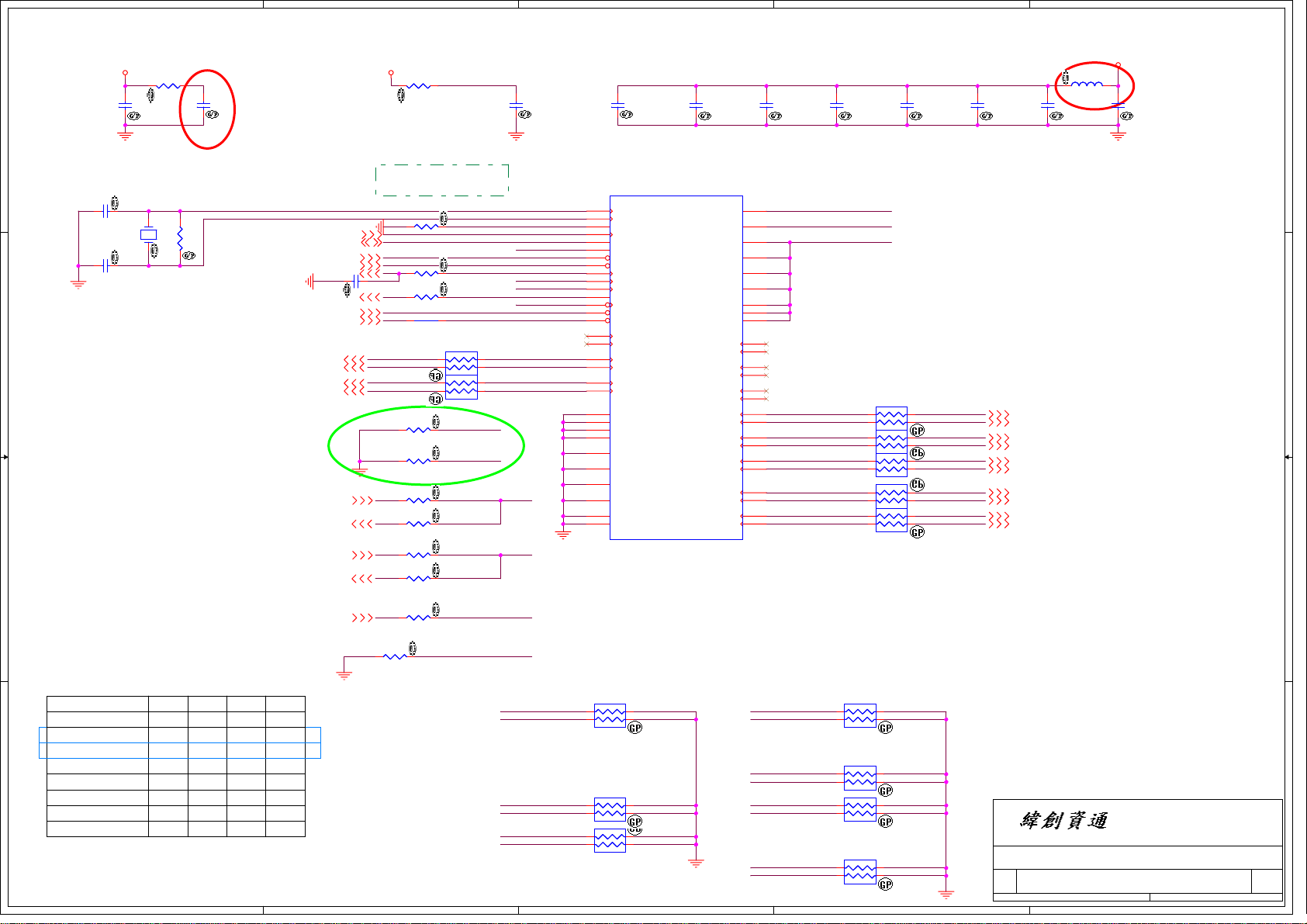

A

B

C

D

E

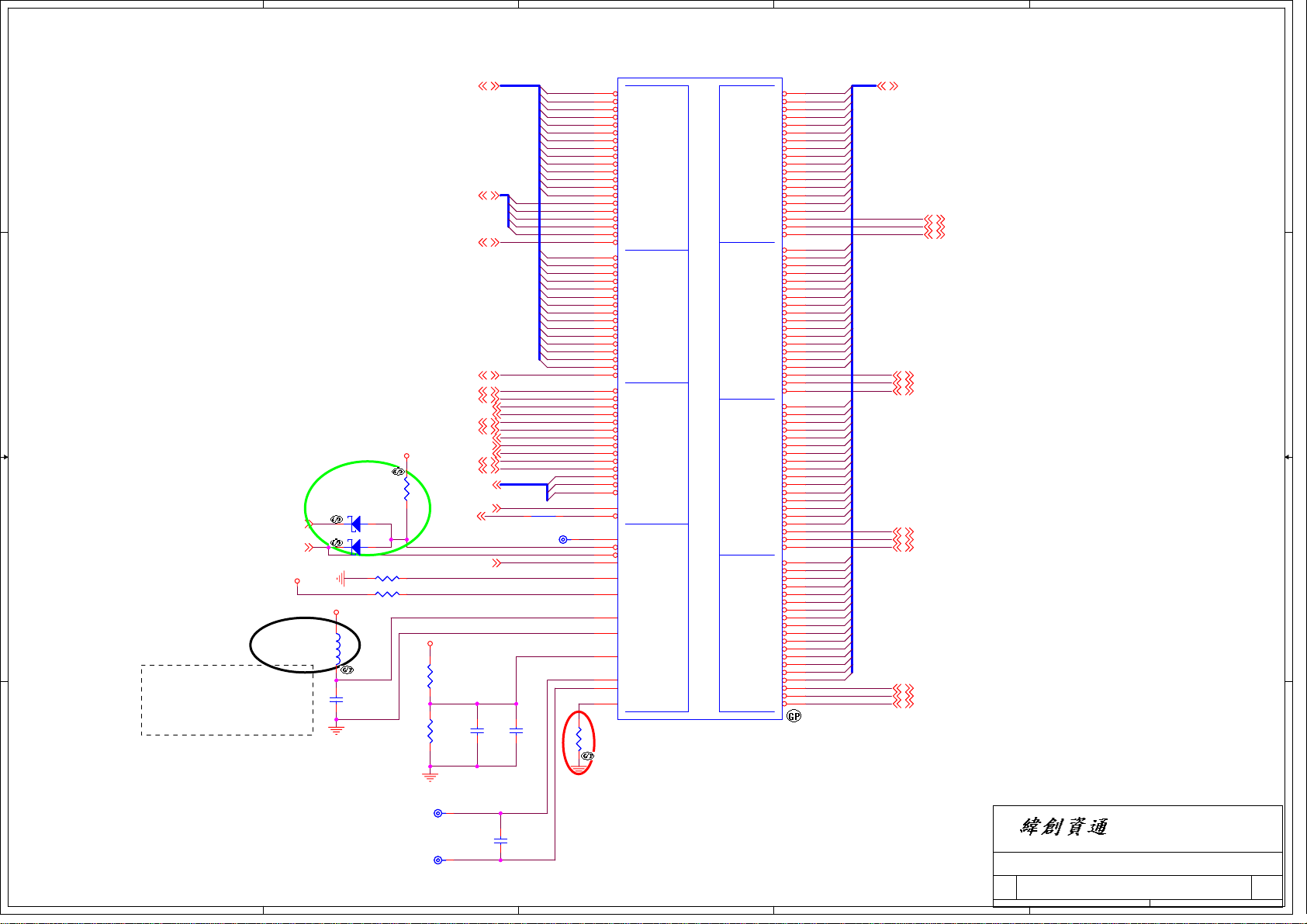

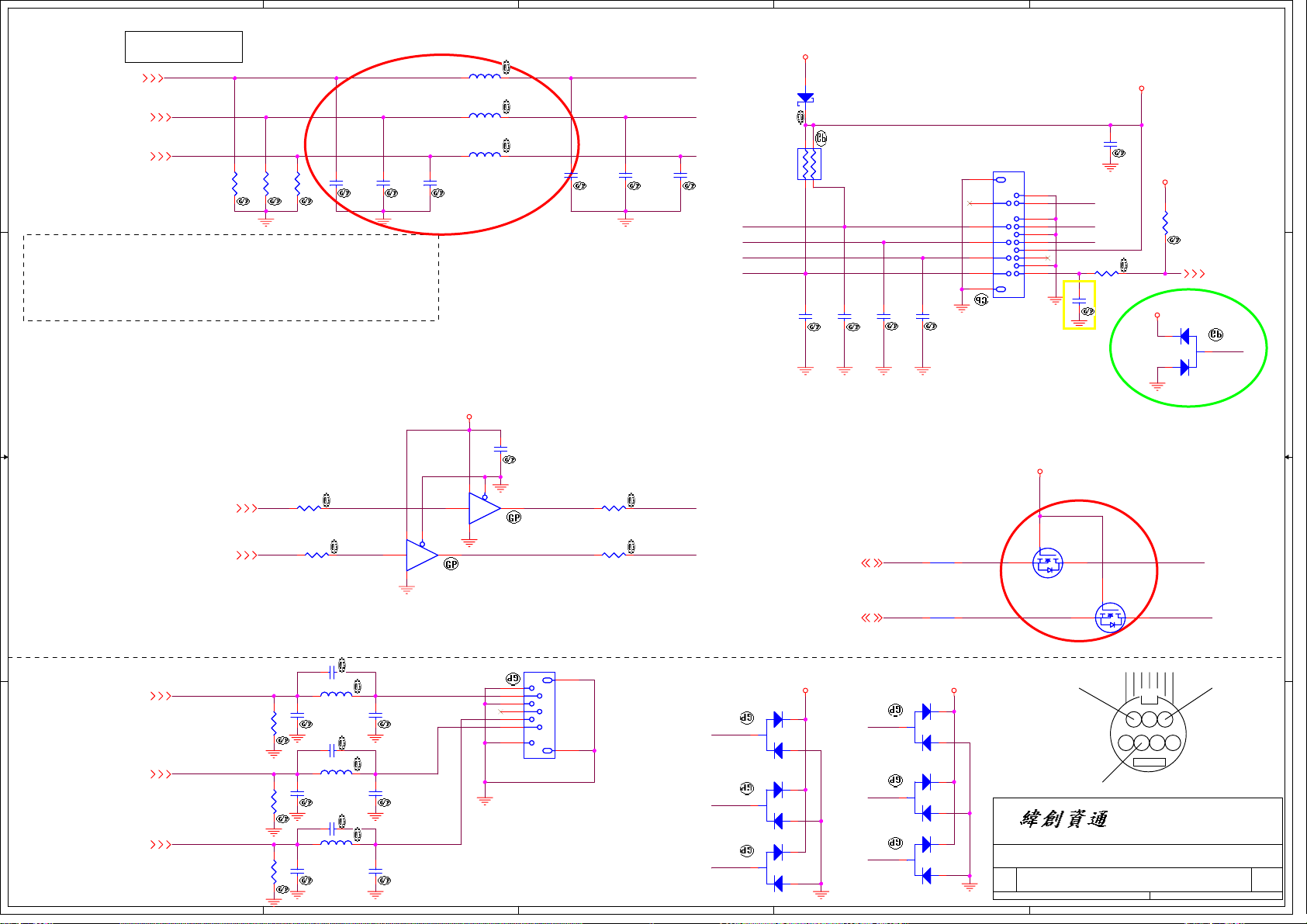

Bead:

200ohm, 200mA.

3D3V_S0 3D3V_S0

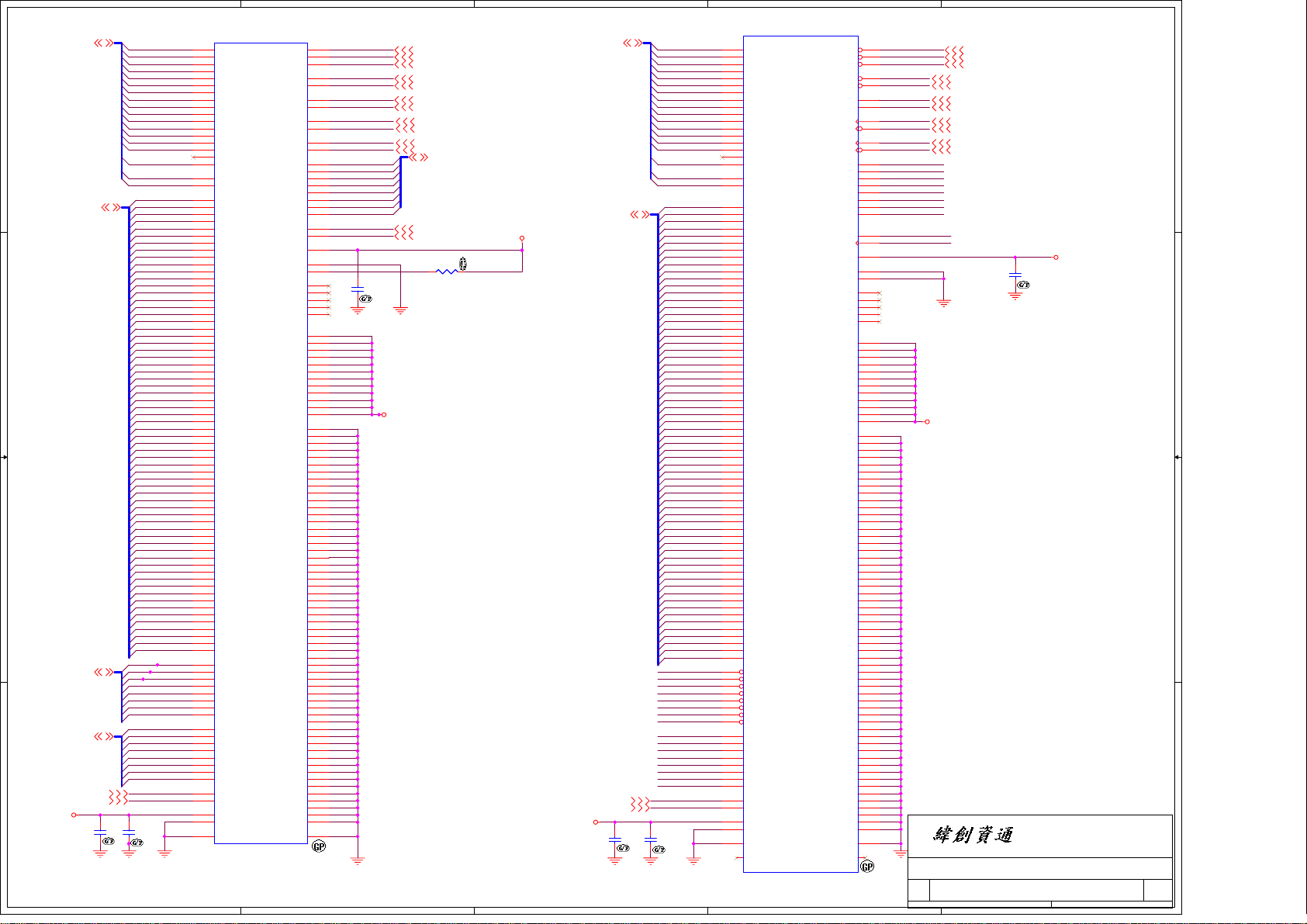

R377

R377

12

0R3-0-U-GP

0R3-0-U-GP

12

C483

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

4 4

SMbus Table:

Byte4 bit 4, CLKREQA#.

Byte2 bit 3, CLKREQB#.

"0": not controlled, "1": controlled.

PL: always output

3 3

NB free-running:

Byte5 bit5 =0.

2 2

C483

DY

DY

C200

C200

1 2

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

X-14D31818M-31GP

X-14D31818M-31GP

82.30005.831

82.30005.831

C199

C199

1 2

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

12

X2

X2

12

C211

C211

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

At least

22u*1, 0.1U*1

12

GEN_XTAL_OUT_R

R127

R127

1MR2J-1-GP

1MR2J-1-GP

GEN_XTAL_IN

CLKREQ_NEW#32

CLKREQ_MINI#27

CLK_MCH_BCLK8

CLK_MCH_BCLK#8

CLK_CPU_BCLK4

CLK_CPU_BCLK#4

CPU_SEL04,9

SB_OSCIN18

CPU_SEL14,9

CLK14_SIO35

Ioh = 6 * Iref (2.32mA)

Voh = 0.7V @ 50 ohm

SMB_CLK11,18,27,32

SMB_DATA11,18,27,32

CLK48_ICH18

OSC14M8

12

C594 SC20P50V2JN-1GP

C594 SC20P50V2JN-1GP

DY

DY

CLK_EN#39

CPU_STP#15

Bead:

200ohm, 200mA.

R128

R128

3D3V_48MPWR_S03D3V_CLKPLL_S0 3D3V_CLKGEN_S0

12

0R3-0-U-GP

0R3-0-U-GP

50mA50mA

At least 2.2u*1

CLK_IREF

R140

R140

1 2

475R2F-L1-GP

475R2F-L1-GP

1 2

R134 33R2J-2-GPR134 33R2J-2-GP

R132 33R2J-2-GPR132 33R2J-2-GP

1 2

1 2

R133 0R0402-PADR133 0R0402-PAD

CPU_STP# CLK GEN Internal PH 120K

RN9SRN33J-5-GP-U RN9SRN33J-5-GP-U

4

4

R137

R137

1 2

1KR2J-1-GP

1KR2J-1-GP

R138

R138

1 2

1KR2J-1-GP

1KR2J-1-GP

1 2

R129 4K7R2J-2-GPR129 4K7R2J-2-GP

1 2

R126 33R2J-2-GPR126 33R2J-2-GP

1 2

R131 4K7R2J-2-GPR131 4K7R2J-2-GP

1 2

R130 33R2J-2-GPR130 33R2J-2-GP

1

23

1

23

CLKREQ_NEW#

CLKREQ_MINI#

RN7SRN33J-5-GP-U RN7SRN33J-5-GP-U

12

C202

C202

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

FS_C

CLK48

FS_B

FS_A

OSC14M_R

SEL_CK410#

CLK_EN#

CPU_STP#_R

CLK_MCH_BCLK_1

CLK_MCH_BCLK_1#

CLK_CPU_BCLK_1

CLK_CPU_BCLK_1#

FS_A

FS_B

12

C210

C210

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

2

X2

1

X1

37

IREF

7

SCLK

8

SDATA

9

FS_C

10

CLKREQA#

11

CLKREQB#

4

USB_48MHZ

53

FS_B/REF1

54

FS_A/REF0

52

TEST_SEL/REF2

50

CK410#/PCICLK0

6

VTT_PWRGD#/PD

48

CPU_STOP#

41

CPUCLKT2_ITP

40

CPUCLKC2_ITP

43

CPUCLKT1

42

CPUCLKC1

47

CPUCLKT0

46

CPUCLKC0

36

GNDSRC

26

GNDSRC

20

GNDSRC

15

GNDSRC

49

GNDPCI

44

GNDCPU

31

GNDATI

38

GNDA

55

GND

5

GND

ICS951413CGLF 71.95143.A0W

ICS951413CGLF 71.95143.A0W

ICS951413 Ver C /CY28RS400 Ver.B /CV136

2nd source: 71.00865.A0W

12

C212

C212

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

VDD48

VDDATI

VDDCPU

VDDPCI

VDDREF

VDDSRC

VDDSRC

VDDSRC

SRCCLKC7

SRCCLKT7

SRCCLKC6

SRCCLKT6

SRCCLKC5

SRCCLKT5

SRCCLKC4

SRCCLKT4

SRCCLKC3

SRCCLKT3

SRCCLKC0

SRCCLKT0

ATIGCLKT1

ATIGCLKC1

ATIGCLKT0

ATIGCLKC0

VDDA

U29

U29

12

39

3

32

45

51

56

35

21

14

13

12

17

16

19

18

CLK_PCIE_NEW_1#

23

CLK_PCIE_NEW_1

22

CLK_PCIE_MINI1_1#

25

CLK_PCIE_MINI1_1

24

CLK_PCIE_ICH_1#

33

CLK_PCIE_ICH_1

34

CLK_NB_ALINK_1

27

CLK_NB_ALINK_1#

28

CLK_NB_GFX_1

30

CLK_NB_GFX_1#

29

C216

C216

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

500mA

12

C209

C209

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_CLKPLL_S0

3D3V_48MPWR_S0

3D3V_CLKGEN_S0

RN12 SRN33J-5-GP-U

RN12 SRN33J-5-GP-U

1

2 3

NEW

NEW

RN19 SRN33J-5-GP-U

RN19 SRN33J-5-GP-U

1

2 3

MINIC

MINIC

RN15 SRN33J-5-GP-URN15 SRN33J-5-GP-U

2 3

1

RN22 SRN33J-5-GP-URN22 SRN33J-5-GP-U

2 3

1

RN23 SRN33J-5-GP-URN23 SRN33J-5-GP-U

1

2 3

Bead:

26ohm, 600mA.

HCB1608K-300T10GP

12

C201

C201

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

4

4

4

4

4

12

C203

C203

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

HCB1608K-300T10GP

12

C207

C207

CLK_PCIE_NEW# 32

CLK_PCIE_NEW 32

CLK_PCIE_MINI1# 27

CLK_PCIE_MINI1 27

CLK_PCIE_ICH# 15

CLK_PCIE_ICH 15

CLK_NB_ALINK 9

CLK_NB_ALINK# 9

CLK_NB_GFX 9

CLK_NB_GFX# 9

3D3V_S0

R139

R139

12

68.00214.111

68.00214.111

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

At least

22u*1, 0.1u*7.

SB Modify

C208

C208

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

FS_C

SEL_CK410#

CK410# = 0, CK410 MODE

CK410# = 1, CK409 MODE

CPU_SEL24

1 2

R136 4K7R2J-2-GPR136 4K7R2J-2-GP

DY

DY

33R2J-2-GP

1 2

33R2J-2-GP

R135

R135

CK410# CLK GEN Internal PL 120K

CLOCK FREQUENCY SELECT TABLE (MHz)

RN18

CPUFSC FSB

FSA

1 0 1

0 0 1

0 1 1

0 1 0

0 0 0

1 1

1 0 0

1 1 0

1 1 1

100 100 33 14.31

133 100 33 14.31

166 100 33 14.31

200 100 33 14.31

266 100 33 14.31

333 100 33 14.31

400 100 33 14.31

RESV 100 33 14.31

A

REFPCISRC

CLK_PCIE_MINI1#

CLK_PCIE_MINI1

SRN49D9F-GP

SRN49D9F-GP

For Yonah Cerlon-M

For Yonah

CLK_PCIE_ICH

CLK_PCIE_ICH#

SRN49D9F-GP

SRN49D9F-GP

CLK_PCIE_NEW

CLK_PCIE_NEW#

SRN49D9F-GP

SRN49D9F-GP

B

RN18

1

2 3

MINIC

MINIC

RN16

RN16

1

2 3

RN11

RN11

2 3

NEW

NEW

1

4

4

4

C

CLK_NB_ALINK#

CLK_NB_ALINK

SRN49D9F-GP

SRN49D9F-GP

CLK_CPU_BCLK

CLK_CPU_BCLK#

SRN49D9F-GP

SRN49D9F-GP

CLK_MCH_BCLK

CLK_MCH_BCLK#

SRN49D9F-GP

SRN49D9F-GP

CLK_NB_GFX

CLK_NB_GFX#

SRN49D9F-GP

SRN49D9F-GP

RN21

RN21

1

2 3

RN8

RN8

1

2 3

RN10

RN10

1

2 3

RN24

RN24

1

2 3

4

4

<Variant Name>

<Variant Name>

4

4

D

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Clock Generator -ICS951413

Clock Generator -ICS951413

Clock Generator -ICS951413

Garda-5 SB

Garda-5 SB

Garda-5 SB

E

of

346Wednesday, April 26, 2006

of

346Wednesday, April 26, 2006

of

346Wednesday, April 26, 2006

A

U53A

4 4

3 3

2 2

H_A#[31..3]6

H_ADSTB#06

H_REQ#[4..0]6

H_ADSTB#16

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

H_NMI15

H_SMI#15

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP41TPAD30 TP41TPAD30

TP39TPAD30 TP39TPAD30

TP43TPAD30 TP43TPAD30

TP40TPAD30 TP40TPAD30

TP32TPAD30 TP32TPAD30

TP31TPAD30 TP31TPAD30

TP35TPAD30 TP35TPAD30

TP36TPAD30 TP36TPAD30

TP22TPAD30 TP22TPAD30

TP21TPAD30 TP21TPAD30

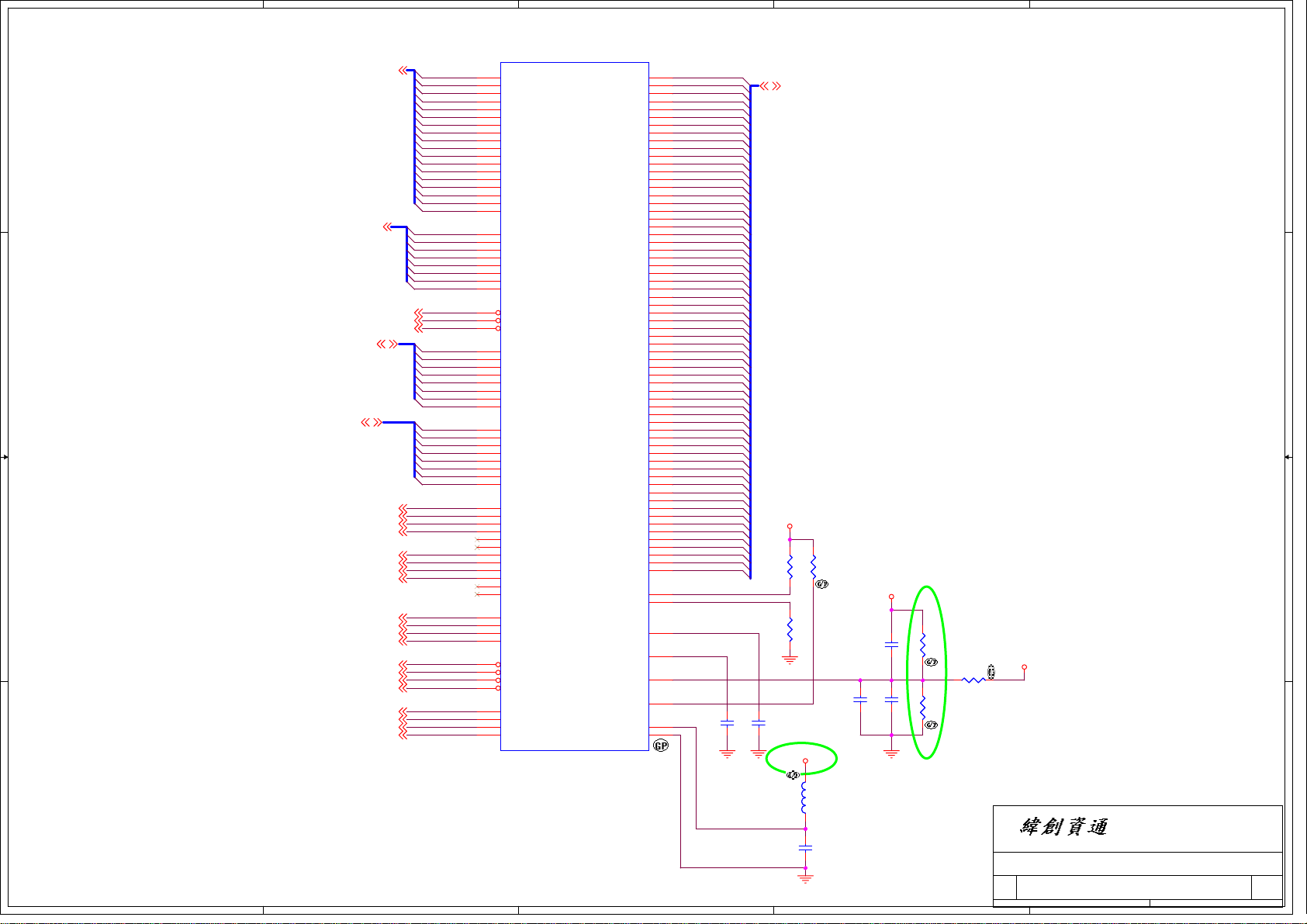

CPU on die PH 55 ohm

1 1

U53A

J4

A[3]#

L4

A[4]#

M3

A[5]#

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

2nd source: 62.10053.401

ADDR GROUP 0

ADDR GROUP 0

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

ADDR GROUP 1

ADDR GROUP 1

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

RSVD[10]

RSVD[11]

BGA479-SKT6-GPU2

BGA479-SKT6-GPU2

62.10079.001

62.10079.001

XDP/ITP SIGNALSH CLK

XDP/ITP SIGNALSH CLK

PROCHOT#

THERMDA

THERMDC

THERM

THERM

THERMTRIP#

RESERVED

RESERVED

XDP_TDI

XDP_TMS

XDP_TDO

H_CPURST#

XDP_DBRESET#

XDP_TCK

XDP_TRST#

All place within 2" to CPU

A

B

H1

ADS#

E2

BNR#

G5

BPRI#

H5

DEFER#

F21

DRDY#

E1

DBSY#

F1

BR0#

D20

IERR#

B3

INIT#

H4

LOCK#

CONTROL

CONTROL

B1

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

BCLK[0]

BCLK[1]

RSVD[12]

RSVD[13]

RSVD[14]

RSVD[15]

RSVD[16]

RSVD[17]

RSVD[18]

RSVD[19]

RSVD[20]

TDI

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

XDP_BPM#0

AD4

XDP_BPM#1

AD3

XDP_BPM#2

AD1

XDP_BPM#3

AC4

XDP_BPM#4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

XDP_TDO

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

XDP_DBRESET#

C20

D21

A24

A25

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

1 2

R107 150R2F-1-GPR107 150R2F-1-GP

1 2

R110 39D2R3F-2-GPR110 39D2R3F-2-GP

1 2

DY

DY

R112 54D9R2F-L1-GP

R112 54D9R2F-L1-GP

1 2

DY

DY

R325 220R2J-L2-GP

R325 220R2J-L2-GP

1 2

150R2F-1-GP

150R2F-1-GP

DY

DY

R79

R79

1 2

R116 27D4R2F-L1-GPR116 27D4R2F-L1-GP

1 2

R115 680R3F-GPR115 680R3F-GP

B

TP28 TPAD30TP28 TPAD30

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_HIT# 6

H_HITM# 6

TP34 TPAD30TP34 TPAD30

TP26 TPAD30TP26 TPAD30

TP27 TPAD30TP27 TPAD30

TP52 TPAD30TP52 TPAD30

TP25 TPAD30TP25 TPAD30

TP24 TPAD30TP24 TPAD30

TP23 TPAD30TP23 TPAD30

1D05V_S0

3D3V_S0

H_IERR#

H_INIT# 15

H_LOCK# 6

H_CPURST# 6

H_TRDY# 6

H_THERMDA 20

H_THERMDC 20

PM_THRMTRIP-I# 37

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

TP47 TPAD30TP47 TPAD30

TP49 TPAD30TP49 TPAD30

TP50 TPAD30TP50 TPAD30

TP48 TPAD30TP48 TPAD30

TP46 TPAD30TP46 TPAD30

TP51 TPAD30TP51 TPAD30

TP44 TPAD30TP44 TPAD30

TP37 TPAD30TP37 TPAD30

TP42 TPAD30TP42 TPAD30

TP38 TPAD30TP38 TPAD30

TP45 TPAD30TP45 TPAD30

TP20 TPAD30TP20 TPAD30

H_RS#[2..0] 6

Layout Note:

0.5" max length.

1D05V_S0

12

R78

R78

56R2J-4-GP

56R2J-4-GP

Place testpoint on

H_IERR# with a GND

0.1" away

1D05V_S0

1 2

2KR2F-3-GP

2KR2F-3-GP

H_THERMDA

H_THERMDC

R77

R77

56R2J-4-GP

56R2J-4-GP

R76

R76

1 2

DY

DY

0R2J-2-GP

0R2J-2-GP

1D05V_S0

R124

R124

H_DPRSLP#

12

12

C

12

PM_THRMTRIP#

should connect to

ICH7 and Calistoga

without T-ing

R125

R125

1KR2F-3-GP

1KR2F-3-GP

12

DY

DY

1D05V_S0

1 2

C

E

CH3904PT-GP

CH3904PT-GP

C

C84

C84

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

H_DSTBN#06

H_DSTBP#06

H_DINV#06

CPU_PROCHOT# 39

( No stub)

H_DSTBN#16

H_DSTBP#16

H_DINV#16

CPU_GTLREF0

C197

C197

SC1KP16V2KX-GP

SC1KP16V2KX-GP

CPU_SEL03,9

CPU_SEL13,9

CPU_SEL23

R328

R328

470R2J-2-GP

470R2J-2-GP

Q8

Q8

B

1 2

R80 1KR2J-1-GP

R80 1KR2J-1-GP

DY

DY

1 2

1 2

R83 51R2F-2-GPR83 51R2F-2-GP

3D3V_S0

R71

R71

470R2J-2-GP

470R2J-2-GP

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST2

12

H_D#[63..0] 6

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

H23

G22

J26

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

R378

R378

10KR2J-3-GP

10KR2J-3-GP

D

U53B

U53B

D[0]#

D[1]#

D[2]#

D[3]#

DATA GRP 0 DATA GRP 1

DATA GRP 0 DATA GRP 1

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

MISC

MISC

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

BGA479-SKT6-GPU2

BGA479-SKT6-GPU2

PM_DPRSLPVR 15,39

D

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

DATA GRP 3

DATA GRP 3

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

E

SB460 contains 400ohm inernal pull-up on

CPU sideband signals.

A20M#

IGNNE#

INIT#

INTR/LIN0

NMI/LIN1

SMI#

STPCLK#

H_D#32

AA23

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

W25

H_D#37

U23

H_D#38

U25

H_D#39

U22

H_D#40

AB25

H_D#41

W22

H_D#42

Y23

H_D#43

AA26

H_D#44

Y26

H_D#45

Y22

H_D#46

AC26

H_D#47

AA24

W24

Y25

V23

H_D#48

AC22

H_D#49

AC23

H_D#50

AB22

H_D#51

AA21

H_D#52

AB21

H_D#53

AC25

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AD24

H_D#58

AE21

H_D#59

AD21

H_D#60

AE25

H_D#61

AF25

H_D#62

AF22

H_D#63

AF26

AD23

AE24

AC20

COMP0

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

R99 27D4R2F-L1-GPR99 27D4R2F-L1-GP

COMP1

COMP2

COMP3TEST1

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

1 2

R102 54D9R2F-L1-GPR102 54D9R2F-L1-GP

1 2

R103 27D4R2F-L1-GPR103 27D4R2F-L1-GP

1 2

R104 54D9R2F-L1-GPR104 54D9R2F-L1-GP

1 2

H_DPRSLP# 39

H_DPSLP# 15

H_DPWR# 6

H_PWRGD 15,37

H_CPUSLP# 18

PSI# 39

CPU (1 of 2)

CPU (1 of 2)

CPU (1 of 2)

H_FERR#

H_PWRGD

H_BREQ#0

H_DPSLP#

H_CPUSLP#

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

Garda-5 SA

Garda-5 SA

Garda-5 SA

1 2

R327 56R2J-4-GPR327 56R2J-4-GP

1 2

R330 330R2J-3-GPR330 330R2J-3-GP

1 2

R329 200R2J-L1-GPR329 200R2J-L1-GP

1 2

R326 200R2J-L1-GPR326 200R2J-L1-GP

1 2

R331 200R2J-L1-GPR331 200R2J-L1-GP

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

446Wednesday, April 26, 2006

446Wednesday, April 26, 2006

446Wednesday, April 26, 2006

E

1D05V_S0

of

of

of

A

B

C

D

E

VCC_CORE_S0

4 4

3 3

2 2

1 1

U53C

U53C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

BGA479-SKT6-GPU2

BGA479-SKT6-GPU2

VCCSENSE

VSSSENSE

A

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

VCC_CORE_S0

12

C171

C171

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

H_VID0 39

H_VID1 39

H_VID2 39

H_VID3 39

H_VID4 39

H_VID5 39

H_VID6 39

H_VID[0..6] 39

12

R121

R121

100R2F-L1-GP-U

100R2F-L1-GP-U

VCC_CORE_S0

1D05V_S0

1D5V_VCCA_S0

C78

VCC_CORE_S0

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C78

R122

R122

100R2F-L1-GP-U

100R2F-L1-GP-U

B

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

12

C449

C449

L4

L4

1 2

HCB1608KF121T30-GP

HCB1608KF121T30-GP

12

12

Layout Note:

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

12

C418

C418

68.00230.041

68.00230.041

C77

C77

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

VCC_SENSE 39

VSS_SENSE 39

SC10U10V5KX-2GP

SC10U10V5KX-2GP

1D5V_CPU_S0

12

C421

C421

SC10U10V5KX-2GP

SC10U10V5KX-2GP

1D05V_S0

VCC_CORE_S0

12

C115

C115

12

C416

C416

SC10U10V5KX-2GP

SC10U10V5KX-2GP

12

12

C143

C143

C159

C159

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C112

C112

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C

12

12

C116

C116

C141

C141

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C113

C113

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C456

C456

C420

C420

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SA Modify

12

C454

C454

SC10U10V5KX-2GP

SC10U10V5KX-2GP

12

C423

C423

12

C448

C448

SC10U10V5KX-2GP

SC10U10V5KX-2GP

12

12

SC10U10V5KX-2GP

SC10U10V5KX-2GP

C167

C167

DY

DY

12

C440

C440

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

C441

C441

C189

C189

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

<Variant Name>

<Variant Name>

<Variant Name>

12

C455

C455

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

SC10U10V5KX-2GP

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

D

Date: Sheet

U53D

U53D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

A26

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

BGA479-SKT6-GPU2

BGA479-SKT6-GPU2

CPU (2 of 2)

CPU (2 of 2)

CPU (2 of 2)

Garda-5 SA

Garda-5 SA

Garda-5 SA

P6

VSS[082]

P21

VSS[083]

P24

VSS[084]

R2

VSS[085]

R5

VSS[086]

R22

VSS[087]

R25

VSS[088]

T1

VSS[089]

T4

VSS[090]

T23

VSS[091]

T26

VSS[092]

U3

VSS[093]

U6

VSS[094]

U21

VSS[095]

U24

VSS[096]

V2

VSS[097]

V5

VSS[098]

V22

VSS[099]

V25

VSS[100]

W1

VSS[101]

W4

VSS[102]

W23

VSS[103]

W26

VSS[104]

Y3

VSS[105]

Y6

VSS[106]

Y21

VSS[107]

Y24

VSS[108]

AA2

VSS[109]

AA5

VSS[110]

AA8

VSS[111]

AA11

VSS[112]

AA14

VSS[113]

AA16

VSS[114]

AA19

VSS[115]

AA22

VSS[116]

AA25

VSS[117]

AB1

VSS[118]

AB4

VSS[119]

AB8

VSS[120]

AB11

VSS[121]

AB13

VSS[122]

AB16

VSS[123]

AB19

VSS[124]

AB23

VSS[125]

AB26

VSS[126]

AC3

VSS[127]

AC6

VSS[128]

AC8

VSS[129]

AC11

VSS[130]

AC14

VSS[131]

AC16

VSS[132]

AC19

VSS[133]

AC21

VSS[134]

AC24

VSS[135]

AD2

VSS[136]

AD5

VSS[137]

AD8

VSS[138]

AD11

VSS[139]

AD13

VSS[140]

AD16

VSS[141]

AD19

VSS[142]

AD22

VSS[143]

AD25

VSS[144]

AE1

VSS[145]

AE4

VSS[146]

AE8

VSS[147]

AE11

VSS[148]

AE14

VSS[149]

AE16

VSS[150]

AE19

VSS[151]

AE23

VSS[152]

AE26

VSS[153]

AF3

VSS[154]

AF6

VSS[155]

AF8

VSS[156]

AF11

VSS[157]

AF13

VSS[158]

AF16

VSS[159]

AF19

VSS[160]

AF21

VSS[161]

AF24

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

of

546Wednesday, April 26, 2006

of

546Wednesday, April 26, 2006

of

546Wednesday, April 26, 2006

E

A

4 4

3 3

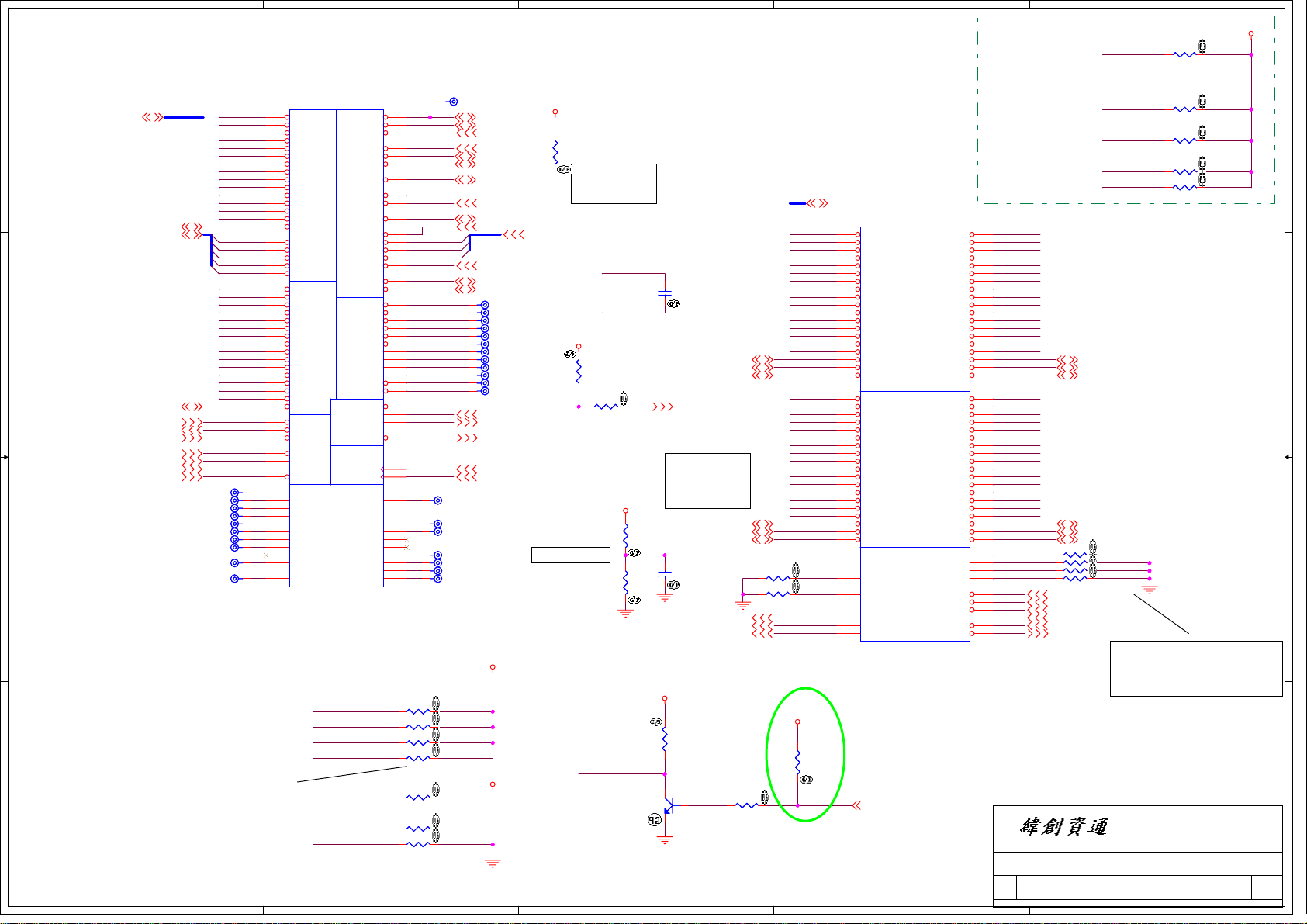

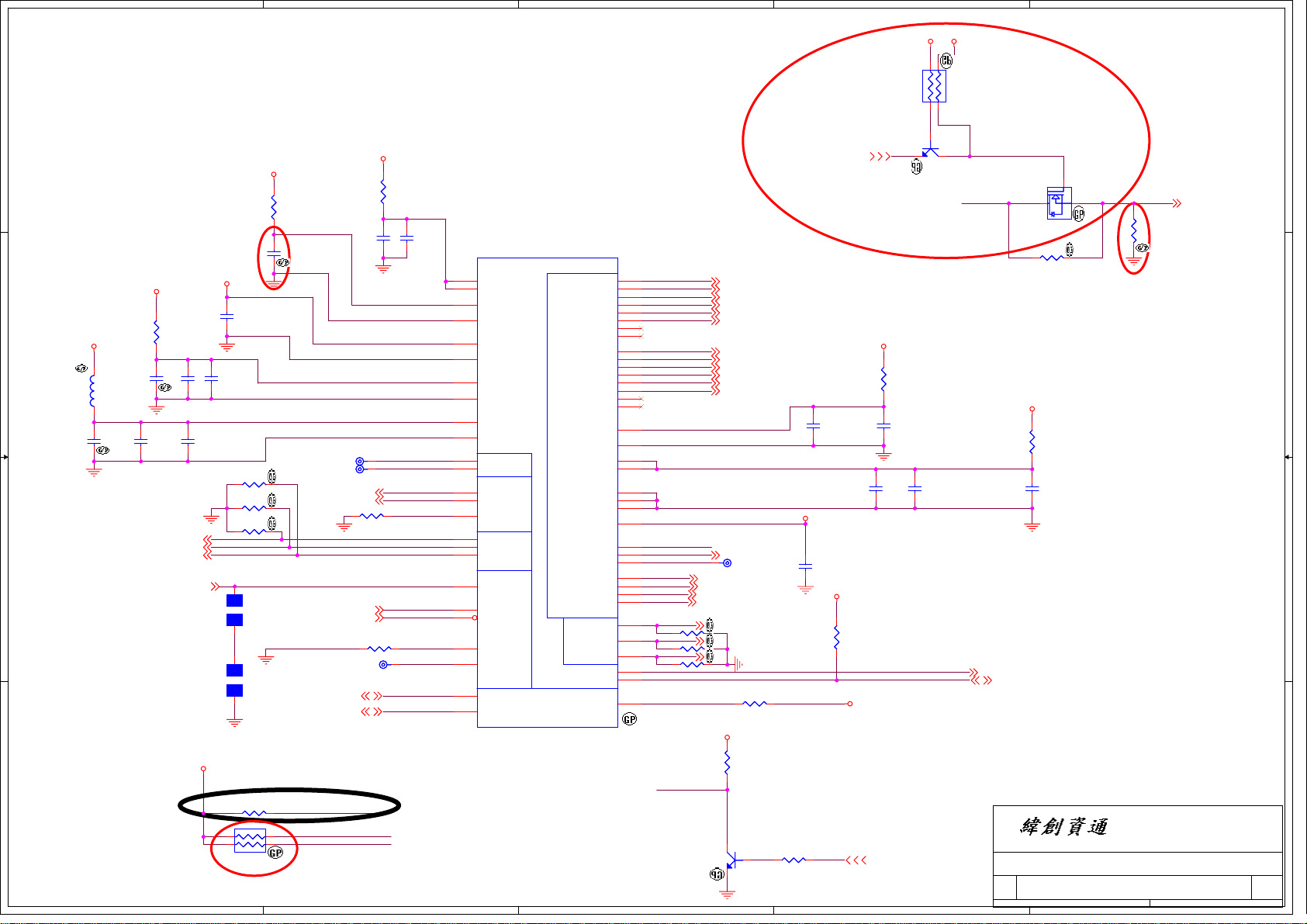

Buffer Implemented:27K

Buffer not Implemented:220K

D9

D9

1D8V_S0

L5

L5

K A

D8

D8

K A

CH751H-40PT-1GP

CH751H-40PT-1GP

12

12

PM_SUS_STAT#18,33,35

NB_RST#15

2 2

Critical Bead

200ohm

200mA

1D05V_S0

BLM18BD152SN-GP

BLM18BD152SN-GP

68.00143.081

68.00143.081

LAYOUT NOTE

CPVSS need to connect to GND

immediately through a

dedicated VIA

1 1

A

B

1D8V_S0

R89

R89

220KR2J-L2-GP

220KR2J-L2-GP

CH751H-40PT-1GP

CH751H-40PT-1GP

R87 49D9R2F-GPR87 49D9R2F-GP

1 2

R86 24D9R2F-L-GPR86 24D9R2F-L-GP

1 2

C111

C111

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

TP33 TPAD30TP33 TPAD30

TP29 TPAD30TP29 TPAD30

B

1 2

1D05V_S0

C

U51A

H_A#[31..3]4

H_REQ#[4..0]4

H_ADSTB#04

H_ADSTB#14

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#4

H_DBSY#4

H_DPWR#4

H_LOCK#4

H_TRDY#4

H_HITM#4

H_HIT#4

H_RS#[2..0]4

H_BREQ#04

H_CPURST#4

NB_RST#

NB_PWRGD8,37

R81

R81

1 2

49D9R2F-GP

49D9R2F-GP

12

R84

R84

100R2F-L1-GP-U

100R2F-L1-GP-U

1989_DXP3

1989_DXN3

R85 0R0402-PADR85 0R0402-PAD

NB_CPU_COMP_P

NB_CPU_COMP_N

NB_CPVDD

12

12

C104

C104

SC220P50V2JN-3GP

SC220P50V2JN-3GP

DY

DY

C137

C137

SC470P50V2KX-3GP

SC470P50V2KX-3GP

1 2

1 2

TP30 TPAD30TP30 TPAD30

NB_GTLVREF

C92

C92

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_RS#0

H_RS#1

H_RS#2

U51A

G28

CPU_A3#

H26

CPU_A4#

G27

CPU_A5#

G30

CPU_A6#

G29

CPU_A7#

G26

CPU_A8#

H28

CPU_A9#

J28

CPU_A10#

H25

CPU_A11#

K28

CPU_A12#

H29

CPU_A13#

J29

CPU_A14#

K24

CPU_A15#

K25

CPU_A16#

F29

CPU_REQ0#

G25

CPU_REQ1#

F26

CPU_REQ2#

F28

CPU_REQ3#

E29

CPU_REQ4#

H27

CPU_ADSTB0#

M28

CPU_A17#

K29

CPU_A18#

K30

CPU_A19#

J26

CPU_A20#

L28

CPU_A21#

L29

CPU_A22#

M30

CPU_A23#

K27

CPU_A24#

M29

CPU_A25#

K26

CPU_A26#

N28

CPU_A27#

L26

CPU_A28#

N25

CPU_A29#

L25

CPU_A30#

N24

CPU_A31#

L27

CPU_ADSTB1#

F25

CPU_ADS#

F24

CPU_BNR#

E23

CPU_BPRI#

E25

CPU_DEFER#

G24

CPU_DRDY#

F23

CPU_DBSY#

G22

CPU_DPWR#

E27

CPU_LOCK#

F22

CPU_TRDY#

E24

CPU_HITM#

D26

CPU_HIT#

E26

CPU_RS0#

G23

CPU_RS1#

D23

CPU_RS2#

D25

RESERVED0

C11

CPU_CPURST#

E11

RESERVED1

AH14

SUS_STAT#

A3

SYSRESET#

E3

POWERGOOD

B11

CPU_COMP_P

D11

CPU_COMP_N

H21

CPVDD

H20

CPVSS

H22

CPU_VREF

AH13

THERMALDIODE_P

AJ13

THERMALDIODE_N

C4

TESTMODE

12

RC410ME-GP

RC410ME-GP

R105

R105

4K7R2J-2-GP

4K7R2J-2-GP

P.L.:Normal Mode.

ATI Modify

50mA

C

PART 1 OF 6

PART 1 OF 6

ADDR. GROUP 0ADDR. GROUP 1CONTROLMISC.

ADDR. GROUP 0ADDR. GROUP 1CONTROLMISC.

AGTL+I/F

AGTL+I/F

71.RC410.D0U

71.RC410.D0U

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

DATA GROUP 0DATA GROUP 1DATA GROUP 2DATA GROUP 3

CPU_D12#

CPU_D13#

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTB0N#

CPU_DSTB0P#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_DSTB1N#

CPU_DSTB1P#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

CPU_DBI2#

CPU_DSTB2N#

CPU_DSTB2P#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

CPU_DBI3#

CPU_DSTB3N#

CPU_DSTB3P#

E28

D28

D29

C29

D30

C30

B29

C28

C26

B25

B27

C25

A27

C24

A24

B26

C27

A28

B28

C19

C23

C20

C22

B22

B23

C21

B24

E21

B21

B20

G19

F21

B19

E20

D21

A21

D22

E22

C18

F19

E19

A18

D19

B18

C17

B17

E17

B16

C15

A15

B15

F16

G18

F18

C16

D18

E18

E16

D16

C14

B14

E15

D15

C13

E14

F13

B13

A12

C12

E12

D13

D12

B12

E13

F15

G15

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DINV#1

H_DSTBN#1

H_DSTBP#1

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DINV#2

H_DSTBN#2

H_DSTBP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DINV#3

H_DSTBN#3

H_DSTBP#3

H_DINV#0

H_DSTBN#0

H_DSTBP#0

D

H_D#[63..0] 4

H_DINV#1 4

H_DSTBN#1 4

H_DSTBP#1 4

H_DINV#2 4

H_DSTBN#2 4

H_DSTBP#2 4

H_DINV#3 4

H_DSTBN#3 4

H_DSTBP#3 4

D

H_DINV#0 4

H_DSTBN#0 4

H_DSTBP#0 4

E

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

RC410ME (1 of 5) Host I/F

RC410ME (1 of 5) Host I/F

RC410ME (1 of 5) Host I/F

Garda-5 SB

Garda-5 SB

Garda-5 SB

646Wednesday, April 26, 2006

646Wednesday, April 26, 2006

646Wednesday, April 26, 2006

E

of

of

of

A

4 4

M_B_DM[7..0]11

3 3

2 2

1 1

A

M_B_DQS[7..0]11

M_B_DQS#[7..0]11

M_CLK_DDR#011

M_CLK_DDR011

M_CLK_DDR#111

M_CLK_DDR111

M_CLK_DDR#311

M_CLK_DDR311

M_CLK_DDR#411

M_CLK_DDR411

B

U51C

M_B_A[17..0]11,12

M_B_RAS#11,12

M_B_CAS#11,12

M_B_WE#11,12

M_CKE011,12

M_CKE111,12

M_CKE211,12

M_CKE311,12

M_CS0#11,12

M_CS1#11,12

M_CS2#11,12

M_CS3#11,12

M_ODT011,12

M_ODT111,12

M_ODT211,12

M_ODT311,12

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_A16

M_B_A17

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_CS0#

M_CS1#

M_CS2#

M_CS3#

B

AK27

AJ27

AH26

AJ26

AH25

AJ25

AH24

AH23

AJ24

AJ23

AH27

AH22

AJ22

AF28

AJ21

AG27

AJ28

AH21

AJ17

AG15

AE20

AF25

Y27

AB28

R26

R28

AJ29

AG28

AH30

AJ18

AE14

AF22

AE25

W27

AB29

P25

R29

AH17

AF15

AE22

AF26

W26

AB30

R25

R30

AC26

AC25

AF16

AE16

V29

V30

AC24

AC23

AG17

AF17

W29

W28

AH20

AJ20

AE24

AE21

AH29

AG29

AH28

AF29

AG30

AE28

AC30

Y30

U51C

MEM_A0

MEM_A1

MEM_A2

MEM_A3

MEM_A4

MEM_A5

MEM_A6

MEM_A7

MEM_A8

MEM_A9

MEM_A10

MEM_A11

MEM_A12

MEM_A13

MEM_A14

MEM_A15

MEM_A16

MEM_A17

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEMB_RAS#

MEMB_CAS#

MEMB_WE#

MEM_DQS0P

MEM_DQS1P

MEM_DQS2P

MEM_DQS3P

MEM_DQS4P

MEM_DQS5P

MEM_DQS6P

MEM_DQS7P

MEM_DQS0N

MEM_DQS1N

MEM_DQS2N

MEM_DQS3N

MEM_DQS4N

MEM_DQS5N

MEM_DQS6N

MEM_DQS7N

MEM_CK0N

MEM_CK0P

MEM_CK1N

MEM_CK1P

MEM_CK2N

MEM_CK2P

MEM_CK3N

MEM_CK3P

MEM_CK4N

MEM_CK4P

MEM_CK5N

MEM_CK5P

MEM_CKE0

MEM_CKE1

MEM_CKE2

MEM_CKE3

MEM_CS0#

MEM_CS1#

MEM_CS2#

MEM_CS3#

MEM_ODT0

MEM_ODT1

MEM_RSRV2

MEM_RSRV3

RC410ME-GP

RC410ME-GP

71.RC410.D0U

71.RC410.D0U

PART 3 OF 6

PART 3 OF 6

MEM_B I/F

MEM_B I/F

MEM_COMPN

MEM_COMPP

MEM_VMODE

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_CAP2

MEM_CAP1

MEM_VREF

MPVDD

MPVSS

C

M_B_DQ0

AJ16

M_B_DQ1

AH16

M_B_DQ2

AJ19

M_B_DQ3

AH19

M_B_DQ4

AH15

M_B_DQ5

AK16

M_B_DQ6

AH18

M_B_DQ7

AK19

M_B_DQ8

AF13

M_B_DQ9

AF14

M_B_DQ10

AE19

M_B_DQ11

AF19

M_B_DQ12

AE13

M_B_DQ13

AG13

M_B_DQ14

AF18

M_B_DQ15

AE17

M_B_DQ16

AF20

M_B_DQ17

AF21

M_B_DQ18

AG23

M_B_DQ19

AF24

M_B_DQ20

AG19

M_B_DQ21

AG20

M_B_DQ22

AG22

M_B_DQ23

AF23

M_B_DQ24

AD25

M_B_DQ25

AG25

M_B_DQ26

AE27

M_B_DQ27

AD27

M_B_DQ28

AE23

M_B_DQ29

AD24

M_B_DQ30

AE26

M_B_DQ31

AD26

M_B_DQ32

AA25

M_B_DQ33

Y26

M_B_DQ34

W24

M_B_DQ35

U25

M_B_DQ36

AA26

M_B_DQ37

Y25

M_B_DQ38

V26

M_B_DQ39

W25

M_B_DQ40

AC28

M_B_DQ41

AC29

M_B_DQ42

AA29

M_B_DQ43

Y29

M_B_DQ44

AD30

M_B_DQ45

AD29

M_B_DQ46

AA30

M_B_DQ47

Y28

M_B_DQ48

U27

M_B_DQ49

T27

M_B_DQ50

N26

M_B_DQ51

M27

M_B_DQ52

U26

M_B_DQ53

T26

M_B_DQ54

P27

M_B_DQ55

P26

M_B_DQ56

U29

M_B_DQ57

T29

M_B_DQ58

P29

M_B_DQ59

N29

M_B_DQ60

U28

M_B_DQ61

T28

M_B_DQ62

P28

M_B_DQ63

N27

MEM_COMPN

AE29

MEM_COMPP

AJ15

MEM_CAP2

N30

MEM_CAP1

AJ14

MEM_VREF

AB27

AD28

AB26

AA27

C

12

C127SCD47U10V3KX-3GPDYC127SCD47U10V3KX-3GP

DY

NB_MPVDD

R336

R336

61D9R2F-GP

61D9R2F-GP

R346

R346

61D9R2F-GP

61D9R2F-GP

12

C413SCD47U10V3KX-3GPDYC413SCD47U10V3KX-3GP

DY

M_B_DQ[63..0] 11

1D8V_S3

12

12

1D8V_S0

1 2

12

L=> 2.0V DDR

12

H=> 1.8V DDRII

R75

R75

1KR2J-1-GP

1KR2J-1-GP

C72

C72

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

L3

L3

HCB1608KF-181-GP

HCB1608KF-181-GP

68.00214.051

68.00214.051

Bead:

200ohm, 200mA.

C82

C82

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

12

1D8V_S3

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C73

C73

C74

C74

D

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

D

12

R69

R69

1KR2J-1-GP

1KR2J-1-GP

DY

DY

12

R70

R70

1KR2J-1-GP

1KR2J-1-GP

DY

DY

E

DDR_VREF_S3

R68

R68

1 2

0R2J-2-GP

0R2J-2-GP

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

RC410ME (2 of 5) Memory I/F

RC410ME (2 of 5) Memory I/F

RC410ME (2 of 5) Memory I/F

Garda-5 SA

Garda-5 SA

Garda-5 SA

E

of

746Wednesday, April 26, 2006

of

746Wednesday, April 26, 2006

of

746Wednesday, April 26, 2006

A

4 4

3D3V_S0

Bead:

26ohm,

600mA.

ATI Modify

R98

R98

0R3-0-U-GP

0R3-0-U-GP

C165

C165

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

OSC14M3

1D8V_S0

12

C170

C170

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

12

12

C164

C164

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C142

C142

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1 2

150R2F-1-GP

150R2F-1-GP

1 2

150R2F-1-GP

150R2F-1-GP

1 2

150R2F-1-GP

150R2F-1-GP

12

DY

DY

12

DY

DY

3D3V_S0

R362 4K7R2J-2-GPR362 4K7R2J-2-GP

1 2

1

2 3

RN53

RN53

SRN4K7J-8-GP

SRN4K7J-8-GP

1D8V_S0

Bead:

200ohm,

200mA.

1D8V_S0 1D8V_S0

SC2D2U10V3ZY-1GP

3 3

Bead:

200ohm,

200mA.

HCB1608KF-181-GP

HCB1608KF-181-GP

68.00214.051

68.00214.051

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

C467

C467

2 2

1 1

SC2D2U10V3ZY-1GP

1 2

12

C166

L27

L27

C166

1 2

12

12

C193

C193

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

RED14

GREEN14

BLUE14

A

R92

R92

R91

R91

R90

R90

R359

R359

DUMMY-R2

DUMMY-R2

C466

C466

DUMMY-C2

DUMMY-C2

R95

R95

0R3-0-U-GP

0R3-0-U-GP

1 2

12

C156

C156

SC2D2U10V3ZY-1GP

SC2D2U10V3ZY-1GP

CLK_MCH_BCLK3

CLK_MCH_BCLK#3

4

SIV Modify

TP70TPAD30 TP70TPAD30

TP72TPAD30 TP72TPAD30

DAC_VSYNC9,14

DAC_HSYNC9,14

EDID_CLK13

EDID_DAT13

3D3V_S0

1 2

12

C188

C188

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

3D3V_S0_AVDD_S

1D8V_S0_AVDDQ

1D8V_S0_PLLVDD

TMDS_HPD

DDC_DATA

R93

R93

1 2

R358 10KR2J-3-GPR358 10KR2J-3-GP

1 2

TP71TPAD30 TP71TPAD30

DDC_DATA

EDID_CLK

EDID_DAT

B

Bead:

200ohm, 200mA.

R117

R117

0R3-0-U-GP

0R3-0-U-GP

3D3V_S0_VDDR3

12

C185

C185

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

715R3-GP

715R3-GP

NB_REST

TVCLKIN

SB_OSCIN_1

EDID_CLK

EDID_DAT

B

C10

H10

B10

E10

D10

G5

G4

C9

D8

C8

B8

B9

H9

J2

H3

B3

C3

F10

G1

J1

K1

G2

F1

D2

C1

U51D

U51D

100mA

VDDR3_1

VDDR3_2

AVDD

250mA

AVSSN

AVDDDI

AVSSDI

AVDDQ

100mA

AVSSQ

PLLVDD

PLLVSS

TMDS_HPD

DDC_DATA

DACVSYNC

DACHSYNC

RSET

RED

GREEN

BLUE

OSCIN

CPU_CLKP

CPU_CLKN

TVCLKIN

OSCOUT

I2C_CLK

I2C_DATA

RC410ME-GP

RC410ME-GP

71.RC410.D0U

71.RC410.D0U

C

PART 4 OF 6

PART 4 OF 6

LPVDD

LPVSS

LVSSR_1

LVSSR_2

LVSSR_3

LVDDR18D

TXCLK_UP

TXCLK_UN

TXCLK_LP

TXCLK_LN

COMP

DACSCL

DACSDA

B4

A4

B5

C6

B6

A6

B7

A7

E5

F5

D5

C5

E6

D6

E7

E8

J8

J7

H8

H7

G9

G8

G7

C7

LVDS_DIGON

E2

G3

LVDS_BLEN

F2

F8

F7

F6

G6

D9

C

F9

Y

E9

B2

C2

D1

1 2

TV

TV

150R2F-1-GP

150R2F-1-GP

1 2

TV

TV

150R2F-1-GP

150R2F-1-GP

1 2

TV

TV

150R2F-1-GP

150R2F-1-GP

GMCH_DDCCLK

C

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

20mA

LVDDR18A_1

100mA

LVDDR18A_2

300mA

LVDS_DIGON

LVDS_BLON

CRT

CRT

"DACSCL"

This strap select the CPU I/O voltage level.

0: mobile CPU Interface(1.4V or below)

1: reserved(Desktop)

LVDS_BLEN

CLK. GEN.

CLK. GEN.

SVID

SVID

STRP_DATA

1D8V_S0_LPVDD

1D8V_S0_LVDDR18A

TXBCLK+ 13

TXBCLK- 13

TXACLK+ 13

TXACLK- 13

R97

R97

R101

R101

R100

R100

STRP_DATA

3D3V_S0

TXBOUT0- 13

TXBOUT0+ 13

TXBOUT1- 13

TXBOUT1+ 13

TXBOUT2- 13

TXBOUT2+ 13

TXAOUT0- 13

TXAOUT0+ 13

TXAOUT1- 13

TXAOUT1+ 13

TXAOUT2- 13

TXAOUT2+ 13

BL_ON 33

TP69 TPAD30TP69 TPAD30

TV_CRMA 14

TV_LUMA 14

TV_COMP 14

R357 4K7R2J-2-GPR357 4K7R2J-2-GP

1 2

R119

R119

4K7R2J-2-GP

4K7R2J-2-GP

1 2

Q12

Q12

C

B

E

CH3904PT-GP

CH3904PT-GP

NB_PWRGD level-shifted to 5V

NB_PWRGD6,37

1 2

C175

C175

R118

R118

3D3V_S0

SB_PWRGD# 37

12

C168

C168

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

12

1D8V_S0

4K7R2J-2-GP

4K7R2J-2-GP

R123

R123

1 2

2KR2F-3-GP

2KR2F-3-GP

12

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C169

C169

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C174

C174

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

3D3V_S0

1 2

STRP_DATA:Debug strap

DEFAULT:0

High, E2PROM STRAPING

Low, Memory Channel STRAPING

D

4

1

B

E

Q30

Q30

CH3904PT-GP

CH3904PT-GP

ATI Modify

R96

R96

0R3-0-U-GP

0R3-0-U-GP

12

C162

C162

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

D

5V_S03D3V_S0

RN68

RN68

SRN10KJ-5-GP

SRN10KJ-5-GP

2 3

C

E

NB_PWRGD_5V

G

Q31

Q31

LVDS_DIGON

FDN337N-1-GP

FDN337N-1-GP

R492

R492

1 2

DY

DY

SD

0R2J-2-GP

0R2J-2-GP

12

R480

R480

100KR2J-1-GP

100KR2J-1-GP

LCDVDD_ON 13

SB Modify

1D8V_S0

R120

R120

0R3-0-U-GP

0R3-0-U-GP

1 2

12

C194

C194

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

GMCH_DDCCLK 14

GMCH_DDCDATA 14

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

RC410ME (3 of 5) Vedio I/F

RC410ME (3 of 5) Vedio I/F

RC410ME (3 of 5) Vedio I/F

Garda-5 -1

Garda-5 -1

Garda-5 -1

846Wednesday, April 26, 2006

846Wednesday, April 26, 2006

846Wednesday, April 26, 2006

E

of

of

A

B

C

D

E

All pull-up and pull-down resistors are 4.7kohm.

NB Strap pins

U51B

AA5

AA4

AB4

AB3

AC6

AC5

AD5

AD4

AF8

AG8

AG6

AG7

AK7

AG4

AH4

AG9

AG10

AE9

AF10

M5

M4

W4

W3

AJ7

M2

M1

U51B

J5

GFX_RX0P

J4

GFX_RX0N

K4

GFX_RX1P

L4

GFX_RX1N

L6

GFX_RX2P

L5

GFX_RX2N

GFX_RX3P

GFX_RX3N

N4

GFX_RX4P

P4

GFX_RX4N

P6

GFX_RX5P

P5

GFX_RX5N

R5

GFX_RX6P

R4

GFX_RX6N

T4

GFX_RX7P

T3

GFX_RX7N

U6

GFX_RX8P

U5

GFX_RX8N

V5

GFX_RX9P

V4

GFX_RX9N

GFX_RX10P

GFX_RX10N

Y6

GFX_RX11P

Y5

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

K2

SB_CLKP

L2

SB_CLKN

GFX_CLKP

GFX_CLKN

H2

BMREQ#

RC410ME-GP

RC410ME-GP

PART 2 OF 6

PART 2 OF 6

71.RC410.D0U

71.RC410.D0U

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCE_TXSET

PCE_ISET

PCE_PCAL

PCE_NCAL

N1

N2

P2

R2

R1

T1

T2

U2

V2

V1

W1

W2

Y2

AA2

AA1

AB1

AB2

AC2

AD2

AD1

AE1

AE2

AF2

AG2

AG1

AH1

AH2

AJ2

AJ3

AJ4

AK4

AJ5

PCIE_LAN_TXP0_1

AJ8

PCIE_LAN_TXN0_1

AJ9

AE6

AF6

PCIE_MC_TXP_2_1

AJ6

PCIE_MC_TXN_2_1

AK6

AE4

AF4

AJ10

AJ11

AK9

AK10

AK13

AJ12

AH12

PCE_NCAL

AG12

82D5R2F-1-GP

82D5R2F-1-GP

C460 SCD1U10V2KX-4GPC460 SCD1U10V2KX-4GP

PCIE_TX0P_NB

PCIE_TX0N_NB

PCIE_TX1P_NB

PCIE_TX1N_NB

PCE_TXSET

PCE_ISET

PCE_PCAL

12

R88

R88

1 2

C459 SCD1U10V2KX-4GPC459 SCD1U10V2KX-4GP

1 2

C462 SCD1U10V2KX-4GPC462 SCD1U10V2KX-4GP

1 2

C461 SCD1U10V2KX-4GPC461 SCD1U10V2KX-4GP

1 2

1 2

1 2

1 2

1 2

12

R94

R94

150R2F-1-GP

150R2F-1-GP

1D2V_S0

12

R349

R349

10KR2F-2-GP

10KR2F-2-GP

PCIE_TXP0 32

PCIE_TXN0 32

C451SCD1U10V2KX-4GP C451SCD1U10V2KX-4GP

C450SCD1U10V2KX-4GP C450SCD1U10V2KX-4GP

C457SCD1U10V2KX-4GP C457SCD1U10V2KX-4GP

C453SCD1U10V2KX-4GP C453SCD1U10V2KX-4GP

12

PCIE_TXP2 27

PCIE_TXN2 27

Adjust PCI-E Amp. R->Small then Amp->Large

<Variant Name>

<Variant Name>

<Variant Name>

PCIE_TX0P_SB 15

PCIE_TX0N_SB 15

PCIE_TX1P_SB 15

PCIE_TX1N_SB 15

R347

R347

8K25R2F-1-GP

8K25R2F-1-GP

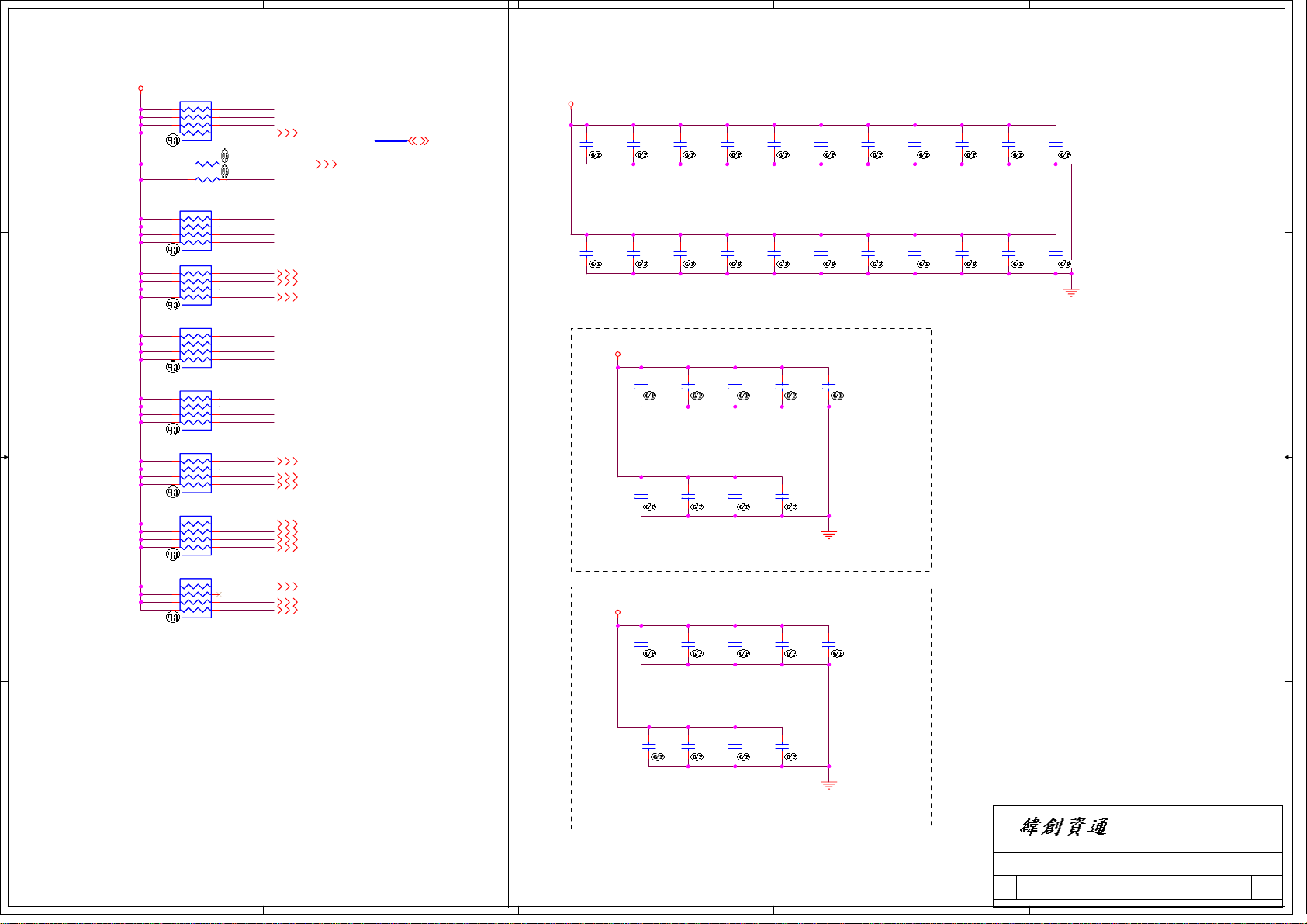

4 4

DY

DY

R363 4K7R2J-2-GP

R363 4K7R2J-2-GP

BMREQ#

1 2

R361 4K7R2J-2-GPR361 4K7R2J-2-GP

1 2

3D3V_S0

BMREQ# pulled down if CPU doesn't support BSEL2.

3D3V_S0

1 2

R111

R111

3 3

2 2

DAC_HSYNC8,14

DAC_VSYNC8,14

1 2

4K7R2J-2-GP

4K7R2J-2-GP

R108

R108

1 2

4K7R2J-2-GP

4K7R2J-2-GP

3D3V_S0

1 2

Select the FSB SPEED

BMREQ# HSYNC VSYNC

000

001

011

0

0

1

1

1

1

1

1 1

R113

R113

4K7R2J-2-GP

4K7R2J-2-GP

CH3904PT-GP

CH3904PT-GP

R114

R114

4K7R2J-2-GP

4K7R2J-2-GP

CH3904PT-GP

CH3904PT-GP

100

0

1

0

1

1D05V_S0

1 2

CBE

Q11

Q11

1D05V_S0

1 2

DY

DY

CBE

Q10

Q10

R109

R109

4K7R2J-2-GP

4K7R2J-2-GP

R106

R106

4K7R2J-2-GP

4K7R2J-2-GP

DY

DY

Freq.

100MHZ

133MHZ

------

166MHZ

100MHZ1

100MHZ

------

------

CPU_SEL1 3,4

CPU_SEL0 3,4

PCIE_RXP032

PCIE_RXN032

PCIE_RXP227

PCIE_RXN227

PCIE_RX0P_SB15

PCIE_RX0N_SB15

PCIE_RX1P_SB15

PCIE_RX1N_SB15

CLK_NB_ALINK3

CLK_NB_ALINK#3

CLK_NB_GFX3

CLK_NB_GFX#3

BMREQ#15

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

A

B

C

D

Date: Sheet

RC410ME (4 of 5) PCI-E & Strap

RC410ME (4 of 5) PCI-E & Strap

RC410ME (4 of 5) PCI-E & Strap

Garda-5 SA

Garda-5 SA

Garda-5 SA

E

of

946Wednesday, April 26, 2006

of

946Wednesday, April 26, 2006

of

946Wednesday, April 26, 2006

A

1D2V_S0 1D8V_S3

4 4

3 3

Bead:

26ohm, 600mA.

L26

68.00214.111

68.00214.111

L26

HCB1608K-300T10GP

HCB1608K-300T10GP

2 2

1 1

At least

22u*1, 0.1u*7.

C148

C123

C123

12

SC1U10V2KX-GP

SC1U10V2KX-GP

C129

C129

1 2

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

1D8V_S0

12

C102

C102

12

SC1U10V2KX-GP

SC1U10V2KX-GP

1D8V_S0

12

L25

L25

HCB1608KF-300-GP

HCB1608KF-300-GP

68.00214.081

68.00214.081

C151

C151

12

SC1U10V2KX-GP

SC1U10V2KX-GP

C148

C144

C144

12

1 2

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C128

C128

C108

C108

12

1 2

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

C110

C110

12

DY

DY

SC1U10V2KX-GP

SC1U10V2KX-GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

3D3V_S0

3

3

D25

D25

BAV99PT-GP-U

BAV99PT-GP-U

1

2

C103

C103

C154

C154

12

12

SC1U10V2KX-GP

SC1U10V2KX-GP

Bead:

50ohm, 3A.

At least

100u*1(ESR<=250), 1u*6.

C155

C155

12

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

C153

C153

12

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

A

C146

C146

C147

C147

12

12

DY

DY

SC1U10V2KX-GP

SC1U10V2KX-GP

C122

C122

C145

C145

12

12

SC1U10V2KX-GP

SC1U10V2KX-GP

C139

C139

12

D26

D26

2

1

BAV99PT-GP-U

BAV99PT-GP-U

3D3V_S0_D

1D8V_S0_VDD18_A

1D8V_S0_VDD18_A

C149

C149

At least 1u*4.

12

1D8V_S0_VDD18_B

C177

C177

C179

C179

12

12

SC1U10V2KX-GP

SC1U10V2KX-GP

C133

C133

C109

C109

12

12

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

C135

C135

C132

C132

12

12

DY

DY

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

SC1U10V2KX-GP

U16

M13

M15

M17

R16

V15

N12

T15

N14

N16

N18

M19

R12

P13

P15

P17

P19

U12

T13

U14

T17

U18

T19

V13

R14

V17

R18

V19

W12

W14

W16

W18

AB22

AB9

AB8

AE11

AC9

AD10

AC10

AG11

AF11

AC7

AB7

J9

J22