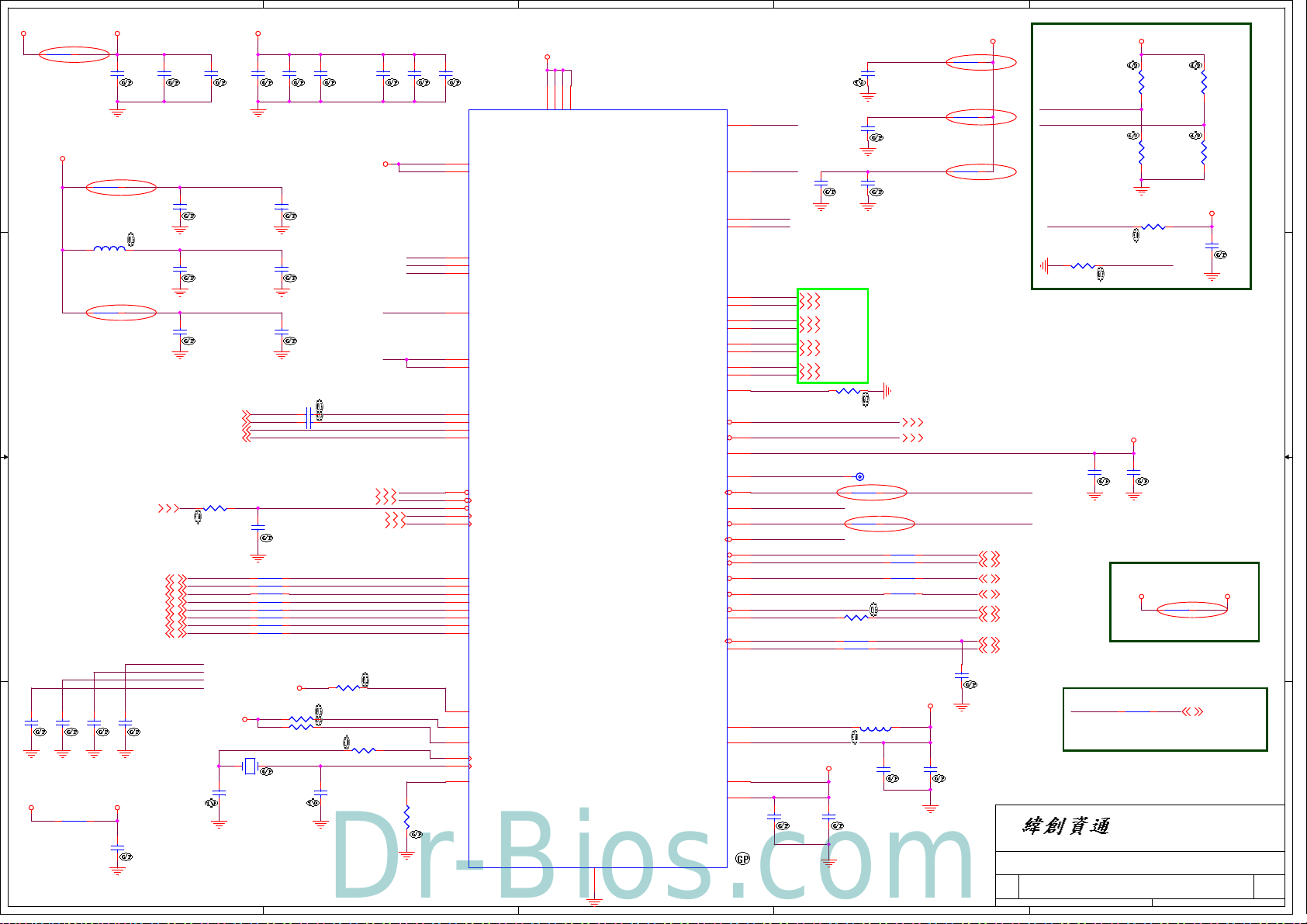

Acer Aspire 5560 Schematic

5

Dr-Bios.com

D D

4

3

2

1

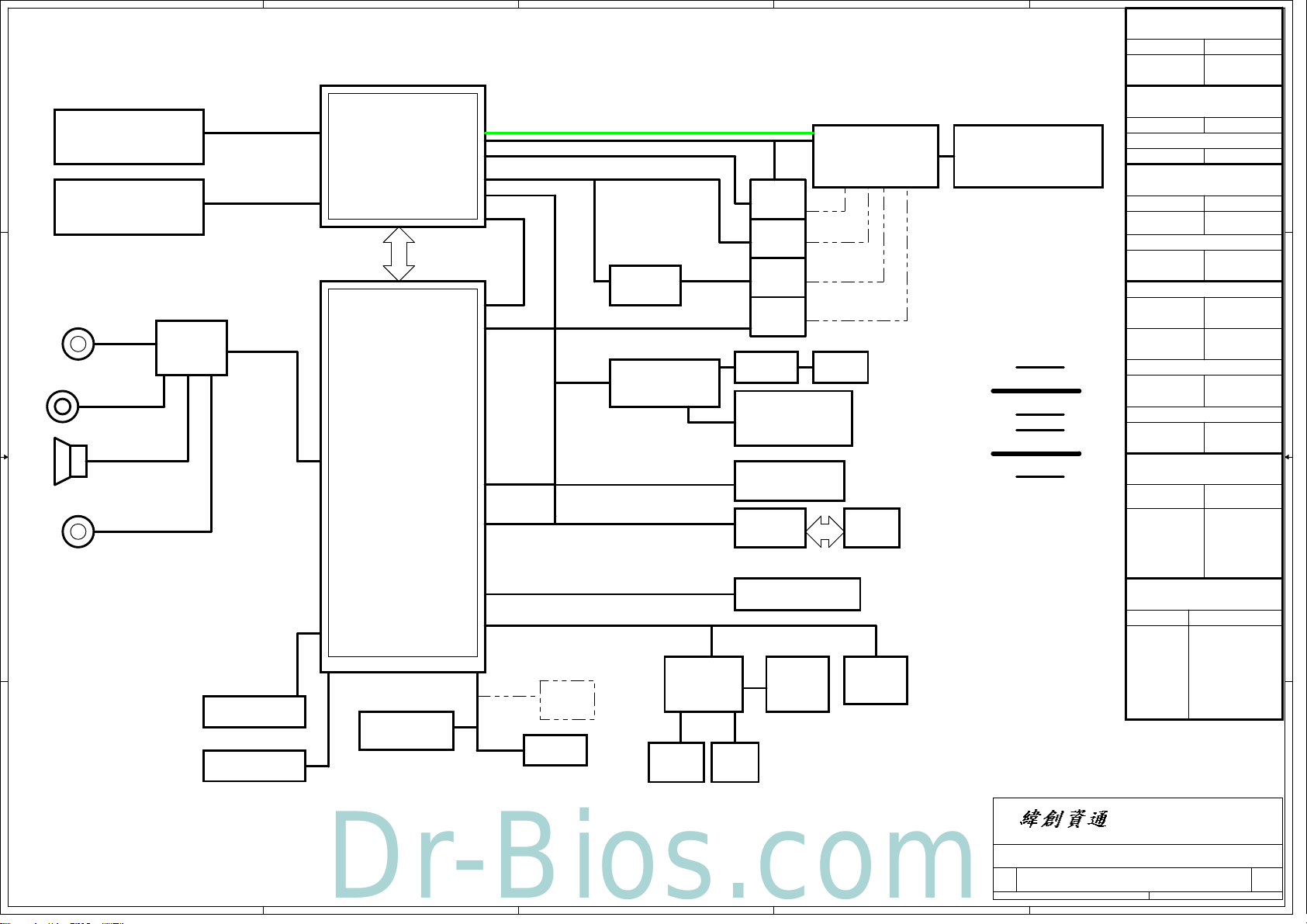

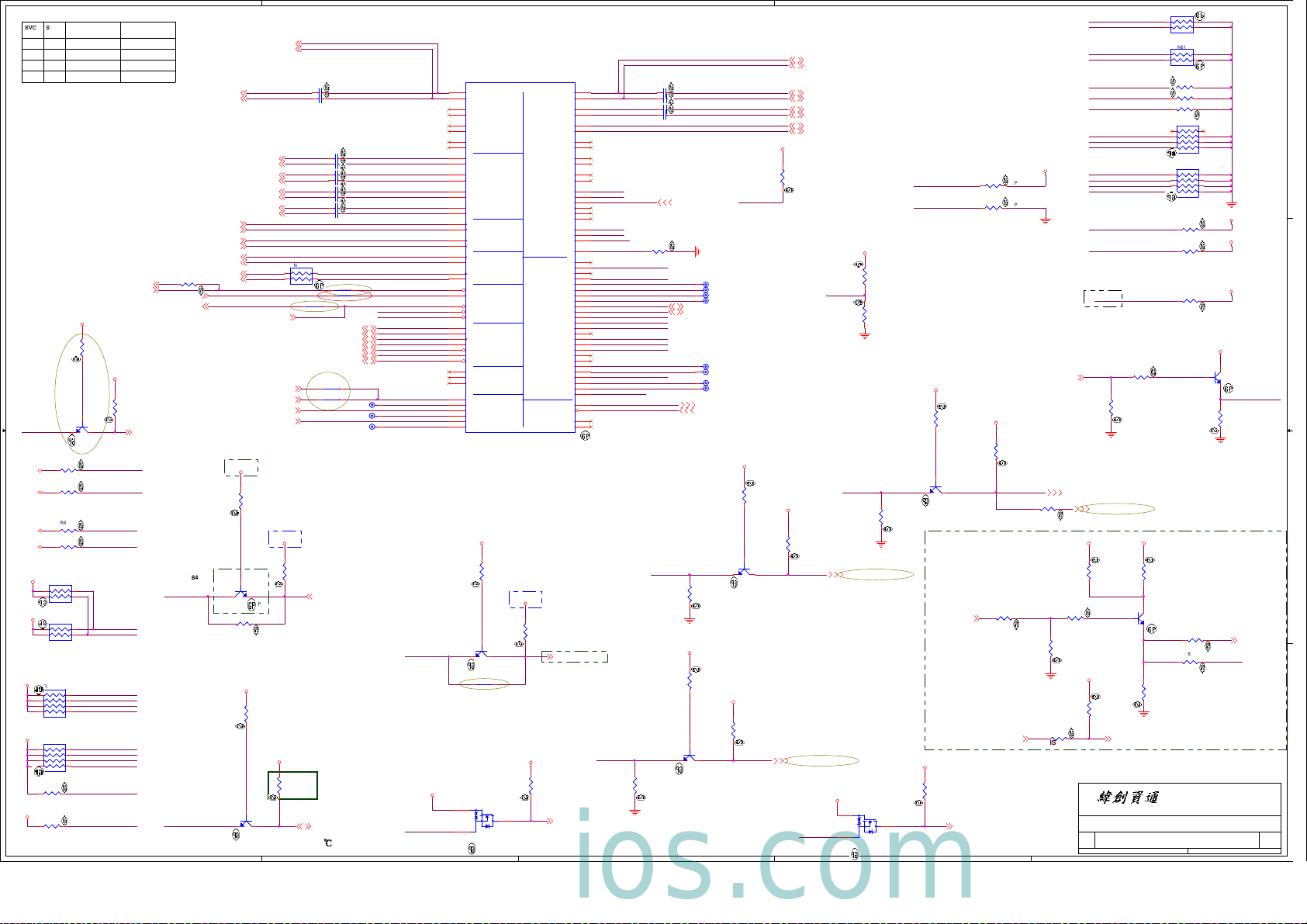

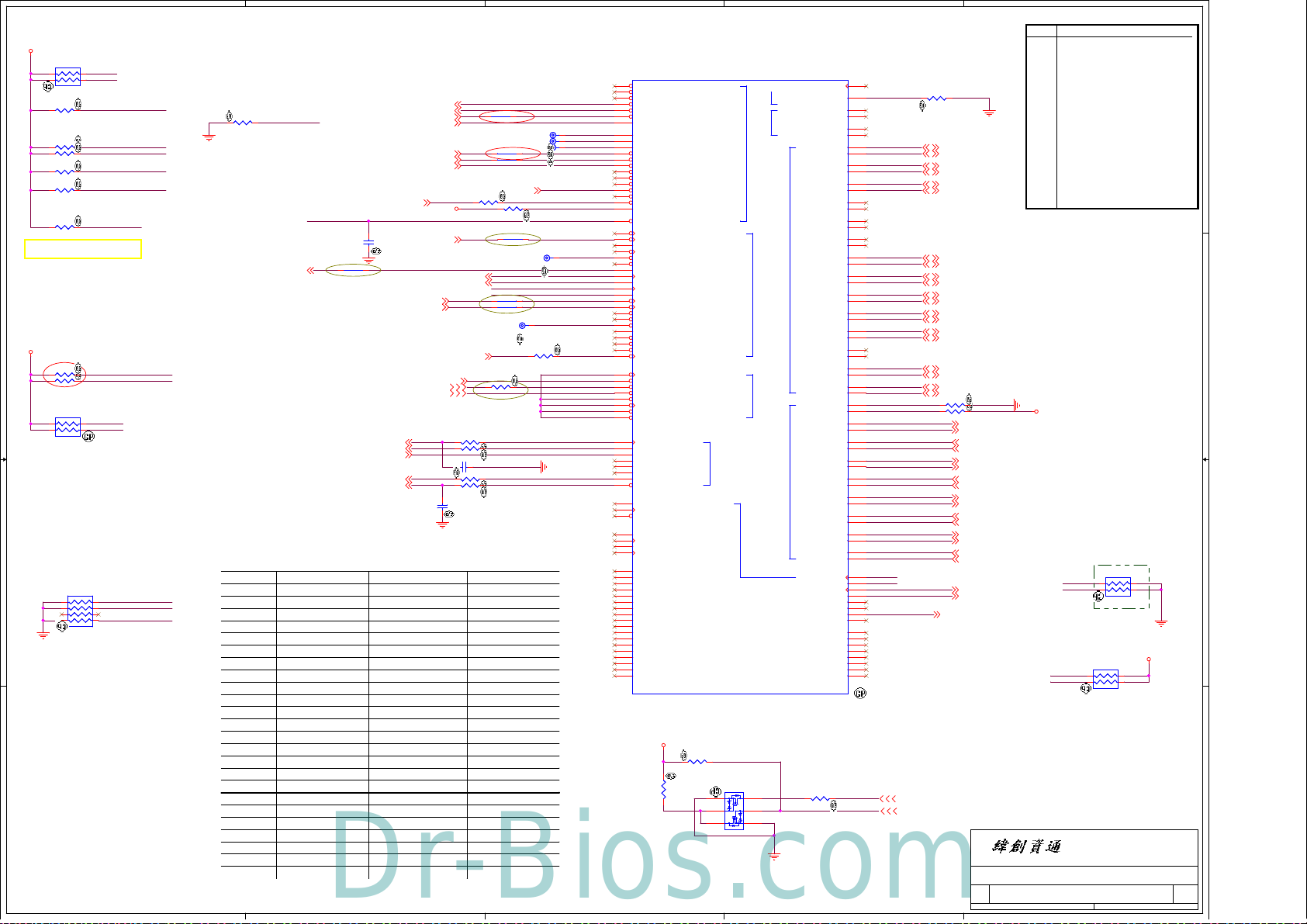

Discrete/UMA /Muxless Schematics Document

AMD LIANO CPU FS1

C C

AMD GPU Manhattan(Park/Madison M2)

and Vancouver(Seymour/Whistler M2)

B B

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

A A

Title

Title

Title

Cover Page

Cover Page

Cover Page

JE50_SB

JE50_SB

JE50_SB

5

4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

3

2

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

1 102

1 102

1 102

1

SB

SB

SB

5

Dr-Bios.com

4

3

2

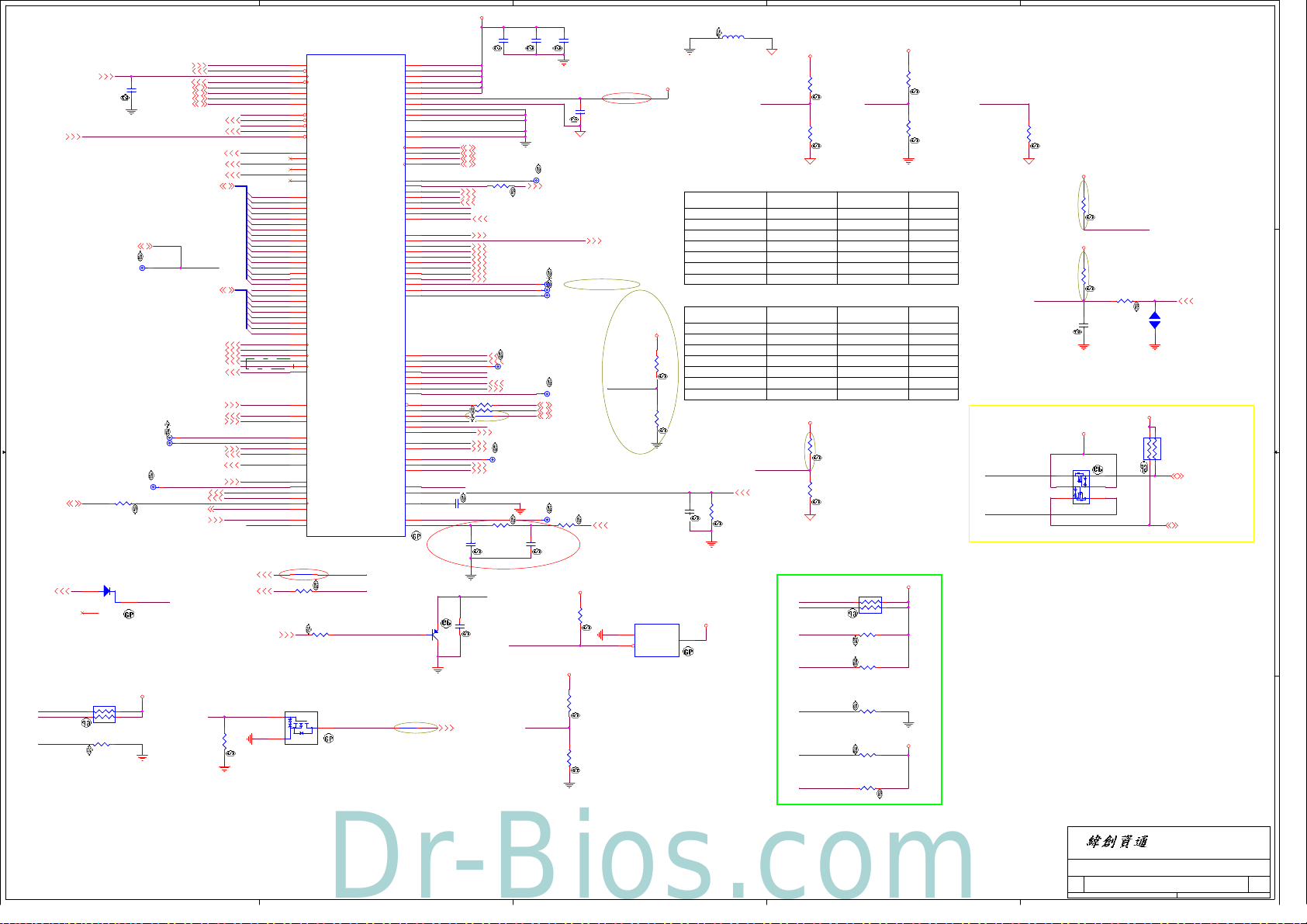

JE50-SB Project code:91.4M701.001

JE50-SB Block Diagram

PCI EXPRESS GRAPHIC(Muxless Lan8 ~Lan15)

D D

DDR3

1066/1333 MHz

14,15,16

AMD Liano APU

( FS1 socket 45W )

722-Pin uFCPGA722

GPP X4 port

DP X6 Port

DDR3

1066/1333 MHz

14,15,16

INT MIC

49

C C

MIC In

58

INT.SPKR

58

Line Out

58

B B

Codec

ALC271X

29

AZALIA

HUDSON-M3

Integrated Display DAC

USB 3.0 (4parts)

USB 2.0

(10 parts or 14 port

if USB 3.0 do not used)

GPP X4 port

USB 1.1 (2 parts)

SATA (6 parts)

INT RTC

INT CLK GEN

HW MONITOR

ACPI 1.1

4,5,6,7,8

UMI-Link

4X4

FCH

17,18,19,20,21,22

X8

X16

PCI EXPRESS GRAPHIC(Diserete only Lan0 ~Lan15)

DP2(PCI EXPRESS Lan0~Lan3)

DP0

DP1

TRAVIS

PS8612

PCIE x 1

9

LAN

Giga LAN

BCM57785

PCIE x 1,USB x 1

PCIE x 1,USB x 1

USB 3.0 x3,USB x 3

LPC BUS

HDMI

EDP

Panel

LCD

CRT

TXFM RJ45

31

MS/MS Pro/xD

/MMC/SD

5 in 1

Mini Card

Mini-Card

WWAN

USB3.0 3 PORT

Madison/Park

Whistler/Seymour

51

49

(Diserete only)

49

50

74

WLAN

65

66 66

61 82

5959

ATI

SIM

DDR3

VRAM

1.Park/Seymour (64Mx16b*4)=>512MB

2.Park/Seymour(128MX16b *4) =>1GB

3.Madison/Whistler(64Mx16b*8)=>1GB

4.Madison/Whistler(128Mx16b*8)=>2GB

512MB/1GB/2GB

88,89,90,9183,84,85,86,87

PCB STACKUP

TOP

VCC

S

S

GND

BOTTOM

1

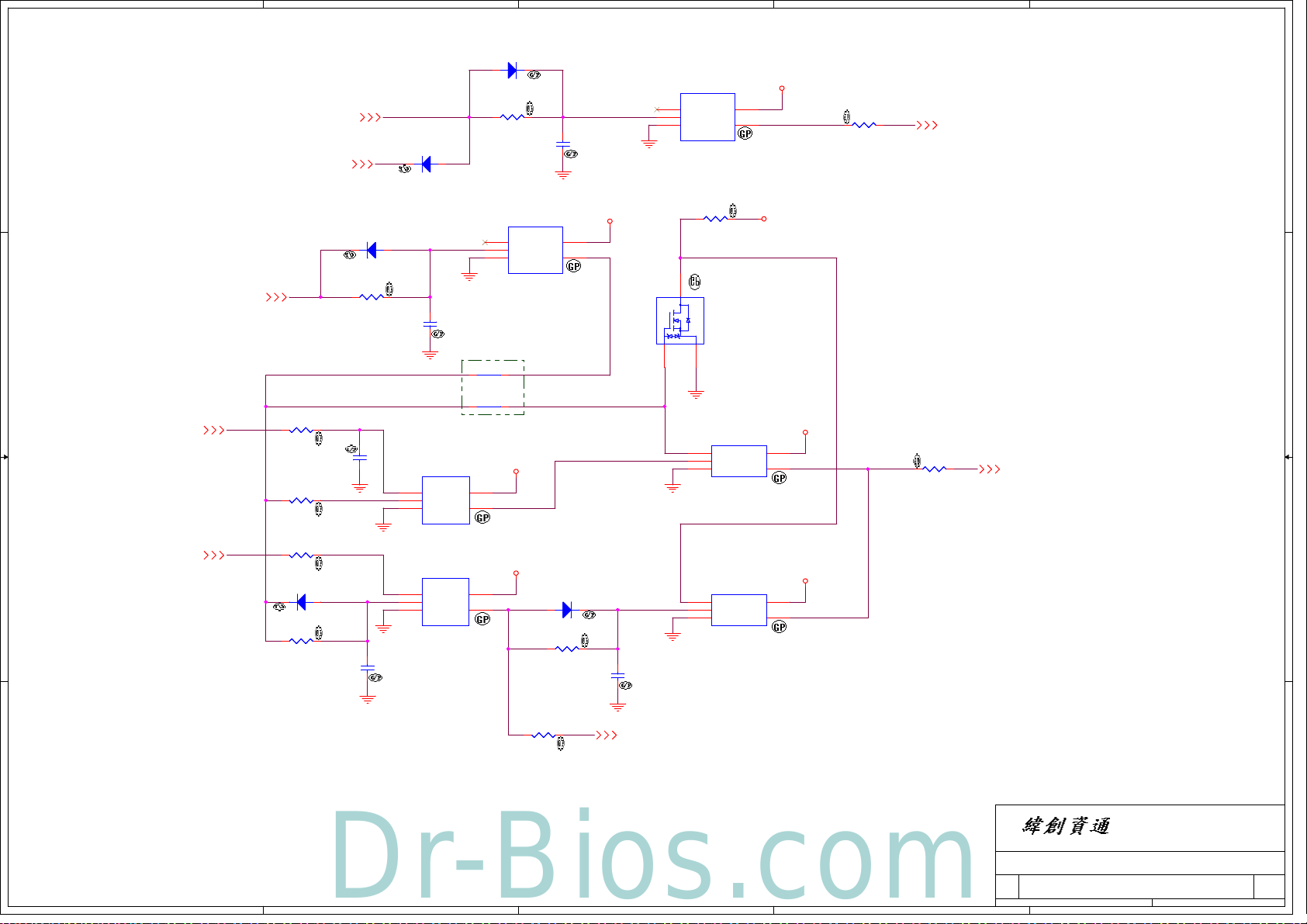

SYSTEM DC/DC

RT8239

INPUTS

DCBATOUT

SYSTEM DC/DC

RT8207

5V_S5

OUTPUTS

5V_S5(5.5A)

3D3V_S5(5A)

1D5V_S3(15A)

RT8207

5V_S5 0D75_S0(1.2A)

SYSTEM DC/DC

RT8238

INPUTS

5V_S5 1D1V_S5(1.4A)

OUTPUTS

RT8238

5V_S5

1D2V_S0(5.2A)

RT9025

3D3V_S5 1D8V_VGA_S0

1D5V_S3

1V_VGA_S0

RT9025

3D3V_S0

2D5V_S0

(200mA)

RT8208

5V_S5

CHARGER

BQ24745

VGA_CORE

OUTPUTSINPUTS

CHG_PWR

DCBATOUT

CPU DC/DC

ISL6267

INPUTS

18V 6.0A

UP+5V

5V 100mA

OUTPUTS

41

44

44

46

45

93

48

92

40

42,43

VCC_CORE_S0

SATA

USB 3.0 x1

USB

HDD SATA

ODD SATA

A A

56

56

Mini USB

Blue Tooth

63

CCD3.0

Camera

35

49

KBC

ENE

KB3936

Touch

Pad

27

INT.

KB

6969

BIOS

MXIC

MX25L1605

5

4

3

LPC

DEBUG

CONN.

60

71

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

JE50_SB

JE50_SB

JE50_SB

DCBATOUT

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

0~1.55V 18A

0~1.55V 4A

2 102

2 102

2 102

1

VDDNB

SB

SB

SB

5

Dr-Bios.com

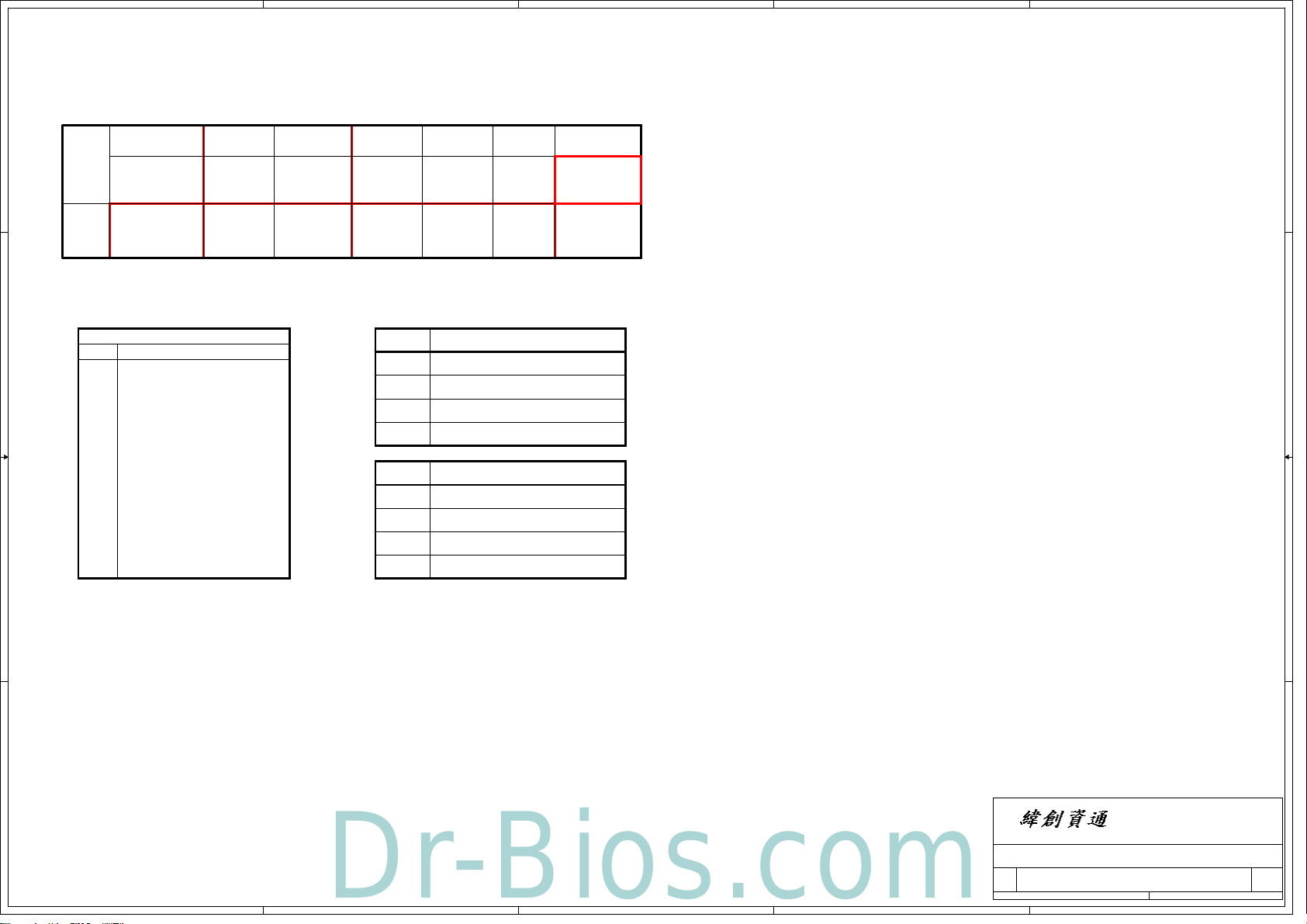

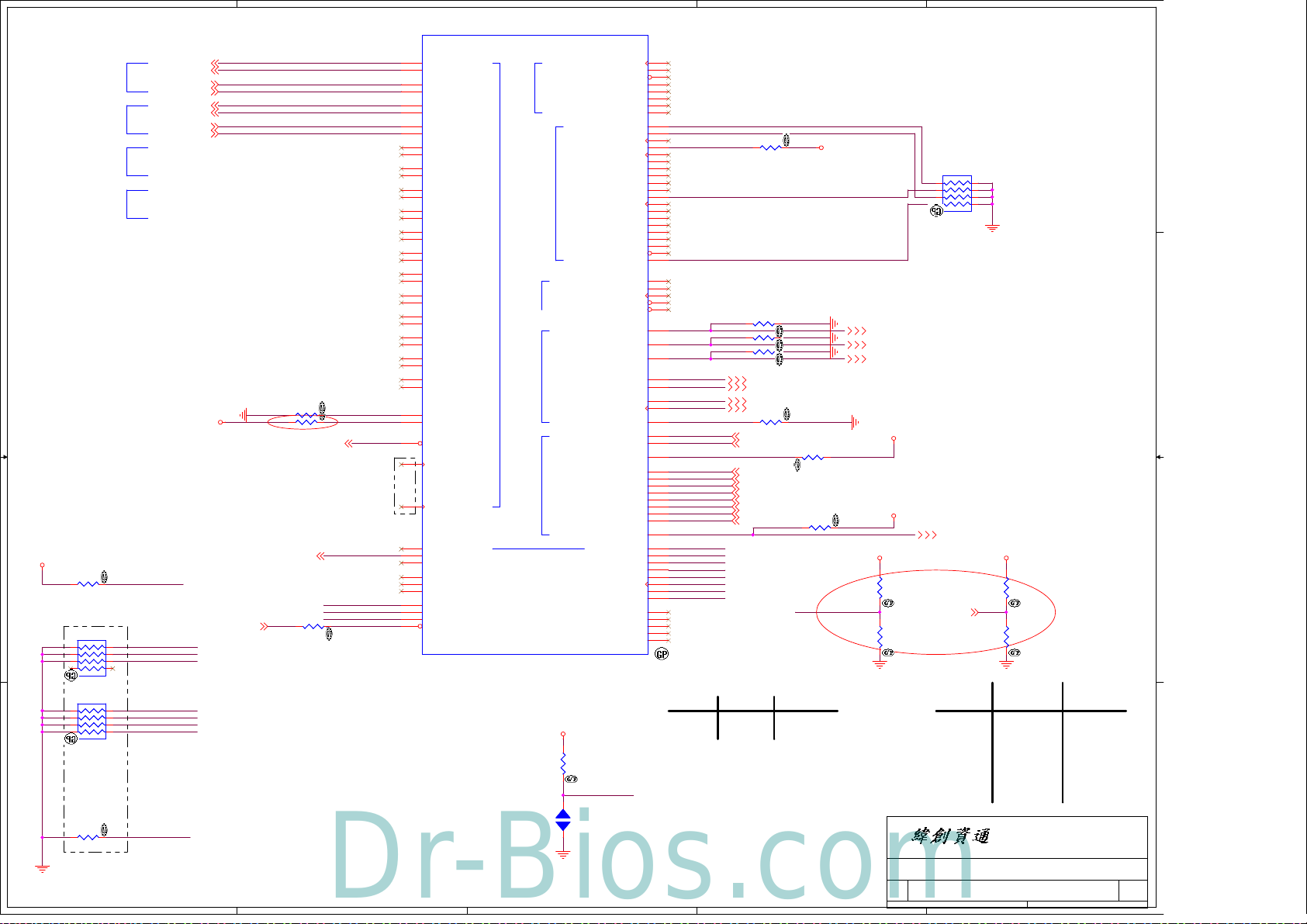

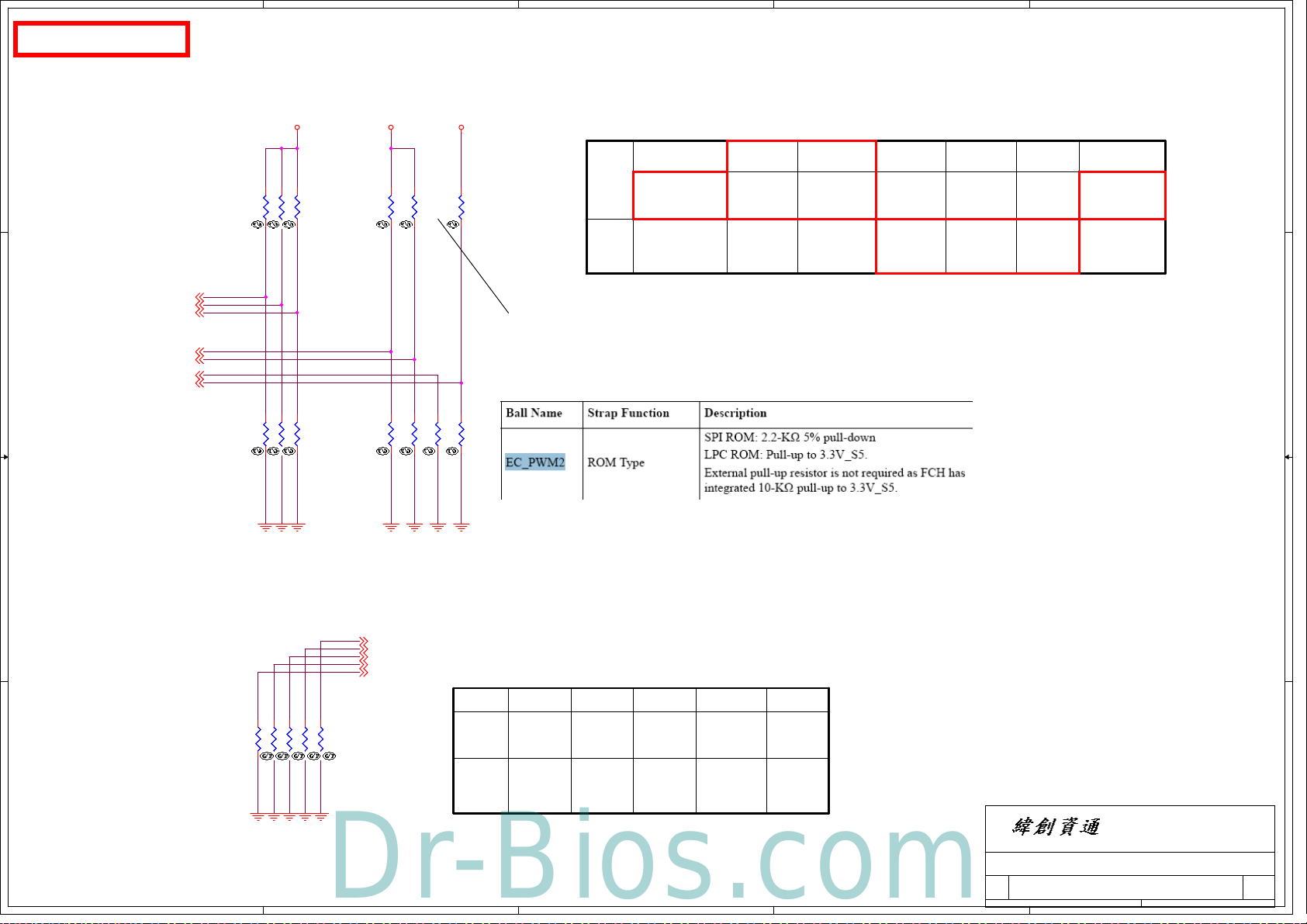

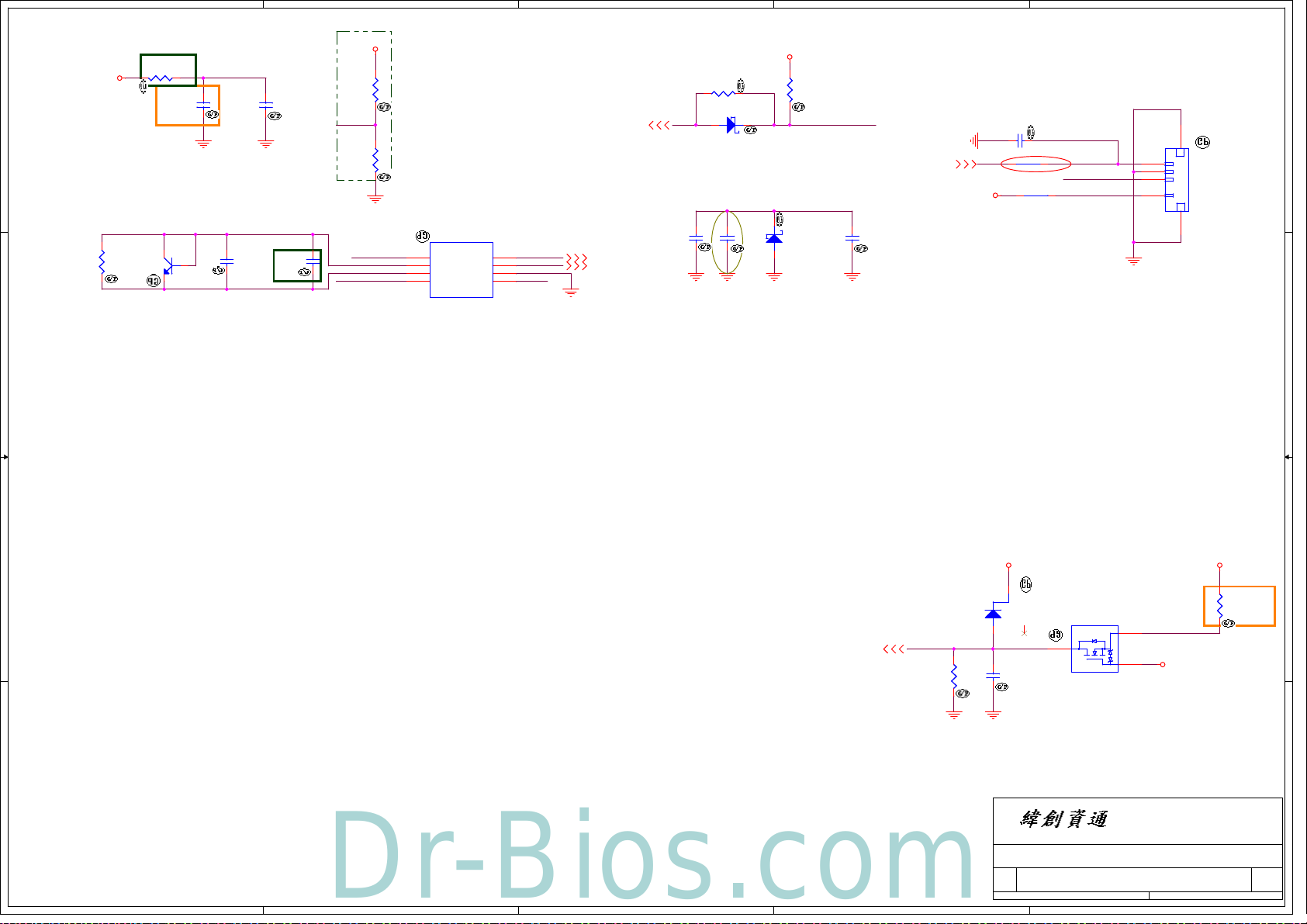

Strapping

4

3

2

1

D D

REQUIRED SYSTEM STRAPS

PULL

HIGH

PULL

LOW

EC_PWM2

PCH GPO199

LPC ROM

DEFAULT

SPI ROM

PCI_CLK1

Allow

PCIE GEN2

DEFAULT

Force

PCIE GEN1

RTC_CLK

S5_PLUS Mode

DISABLE

DEFAULT

S5_PLUS Mode

ENABLE

USE

DEBUG

STRAPS

IGNORE

DEBUG

STRAPS

DEFAULT

PCI_CLK4CLK_PCI_LPC

non_Fusion

CLOCK mode

Fusion

CLOCK mode

DEFAULT

USE this pin to determine INT/EXT CLK

LPC_CLK0

ENABLE EC

DISABLE EC

DEFAULT

LPC_CLK1

CLKGEN

ENABLED

(Use Internal)

DEFAULT

CLKGEN

DISABLED

(Use External)

USB Table PCIE Routing

C C

B B

Pair

0

1

2

3

4

5

6

7

8

9

10

11

12

13

USB

Device

USB 2.0 EXT2(For SW Debug)

WLAN

NC

WWAN

BT

3G SIM Card

NC

CCD

NC

Card Reader

USB 3.0 port 1

USB 2.0 EXT2

USB 2.0 EXT3

NC

LANE1

LANE2

LANE3

LANE0

LANE1

LANE2

LANE3

APU

LANLANE0

WWAN

LAN

FCH

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

Table of Content

Table of Content

Table of Content

JE50_SB

JE50_SB

JE50_SB

Taipei Hsien 221, Taiwan, R.O.C.

3 102

3 102

3 102

1

SB

SB

SB

5

Dr-Bios.com

4

3

2

1

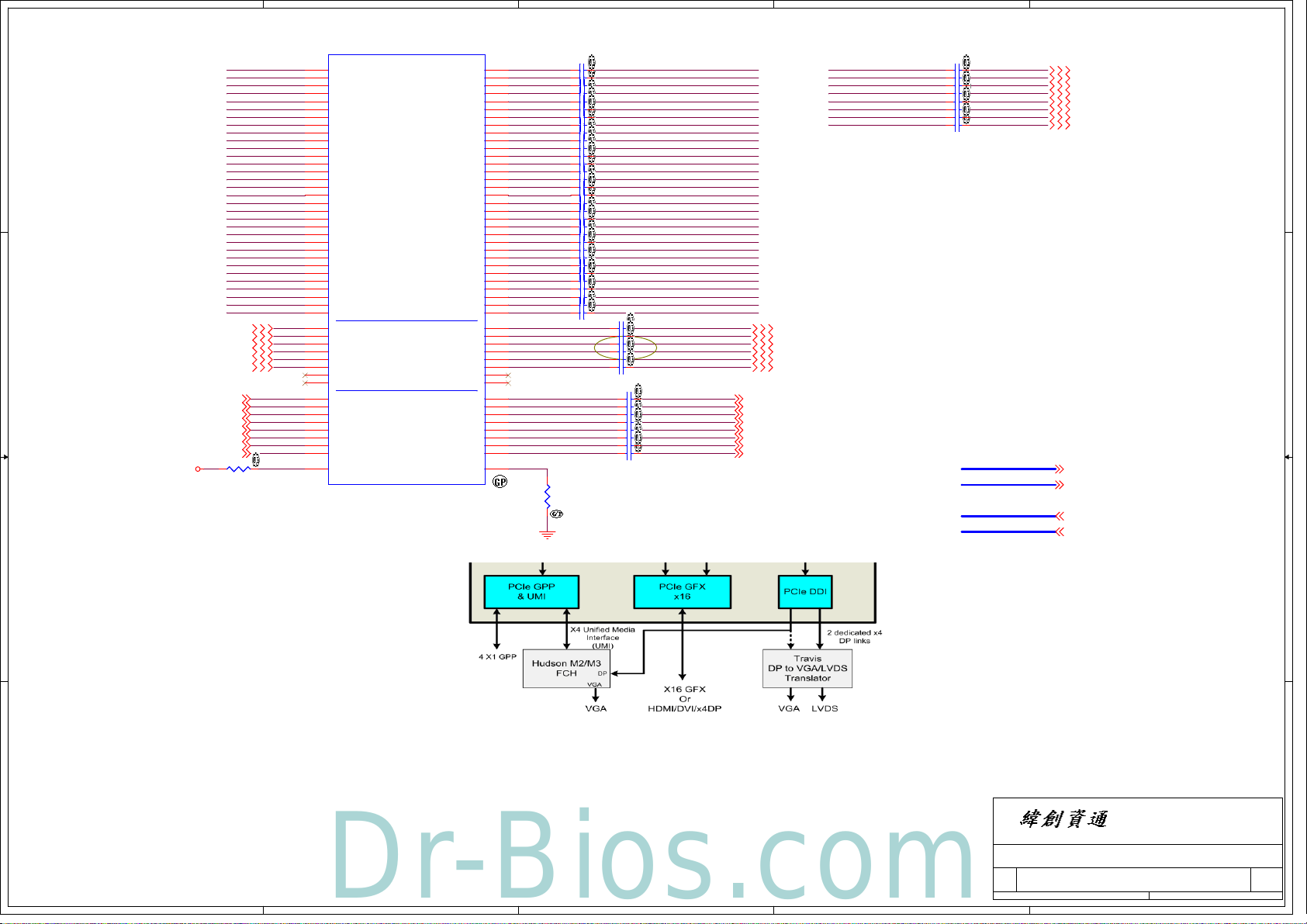

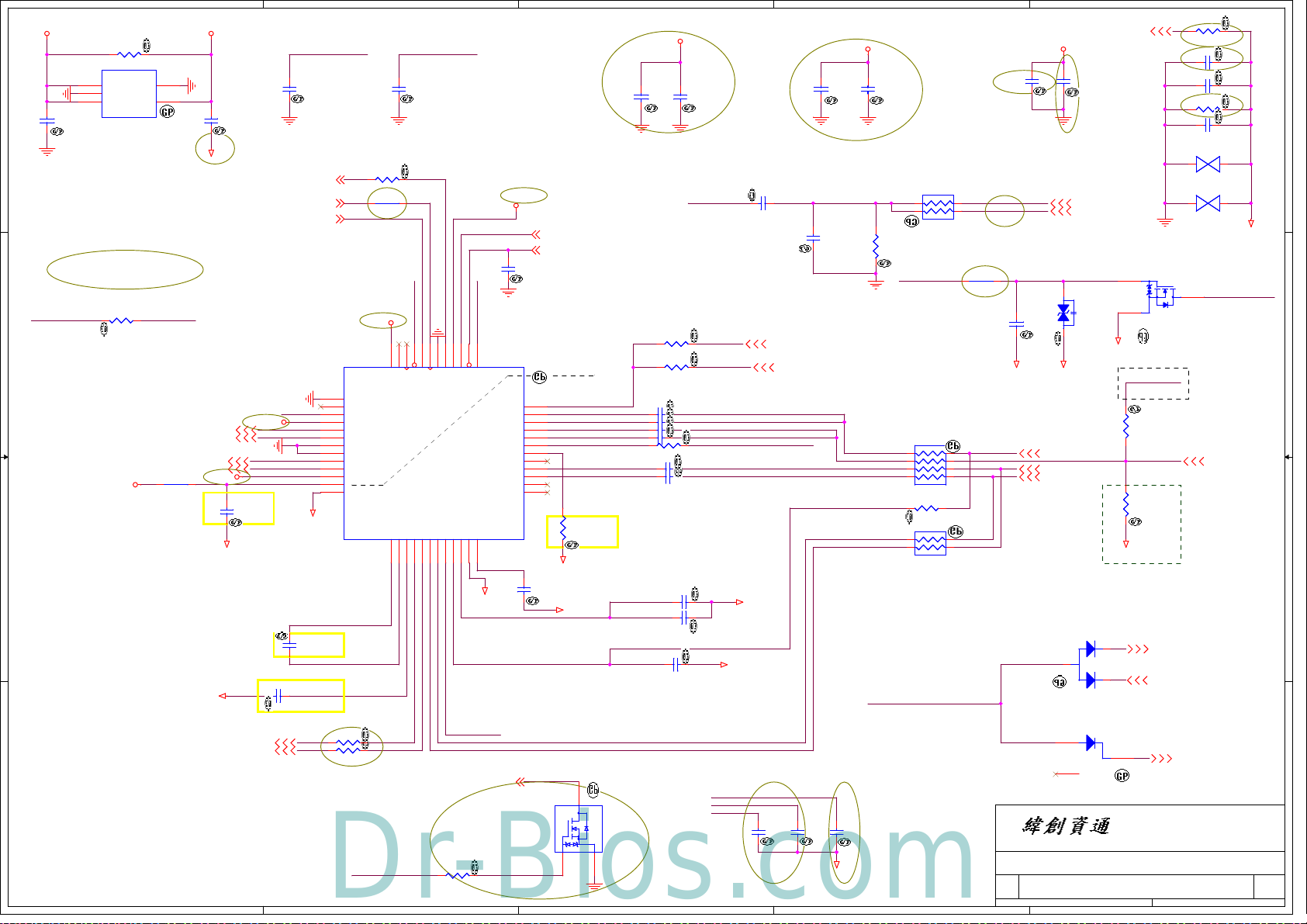

APU1F

APU1F

PEG_RXP 0

PEG_RXN 0

PEG_RXP 1

PEG_RXN 1

PEG_RXP 2

PEG_RXN 2

PEG_RXP 3

PCIE_RXP031

PCIE_RXN031

PCIE_RXP166

PCIE_RXN166

PCIE_RXP265

PCIE_RXN265

1 2

R402

R402

196R2F-G P

196R2F-G P

PEG_RXN 3

PEG_RXP 4

PEG_RXN 4

PEG_RXP 5

PEG_RXN 5

PEG_RXP 6

PEG_RXN 6

PEG_RXP 7

PEG_RXN 7

PEG_RXP 8

PEG_RXN 8

PEG_RXP 9

PEG_RXN 9

PEG_RXP 10

PEG_RXN 10

PEG_RXP 11

PEG_RXN 11

PEG_RXP 12

PEG_RXN 12

PEG_RXP 13

PEG_RXN 13

PEG_RXP 14

PEG_RXN 14

PEG_RXP 15

PEG_RXN 15

D D

LAN

C C

WLAN

UMI_FCH_A PU_RX0P17

UMI_FCH_A PU_RX0N17

UMI_FCH_A PU_RX1P17

UMI_FCH_A PU_RX1N17

UMI_FCH_A PU_RX2P17

UMI_FCH_A PU_RX2N17

UMI_FCH_A PU_RX3P17

UMI_FCH_A PU_RX3N17

1D2V_S0

AA8

P_GFX_RXP0

AA9

P_GFX_RXN0

Y7

P_GFX_RXP1

Y8

P_GFX_RXN1

W5

P_GFX_RXP2

W6

P_GFX_RXN2

W8

P_GFX_RXP3

W9

P_GFX_RXN3

V7

P_GFX_RXP4

V8

P_GFX_RXN4

U5

P_GFX_RXP5

U6

P_GFX_RXN5

U8

P_GFX_RXP6

U9

P_GFX_RXN6

T7

P_GFX_RXP7

T8

P_GFX_RXN7

R5

P_GFX_RXP8

R6

P_GFX_RXN8

R8

P_GFX_RXP9

R9

P_GFX_RXN9

P7

P_GFX_RXP10

P8

P_GFX_RXN10

N5

P_GFX_RXP11

N6

P_GFX_RXN11

N8

P_GFX_RXP12

N9

P_GFX_RXN12

M7

P_GFX_RXP13

M8

P_GFX_RXN13

L5

P_GFX_RXP14

L6

P_GFX_RXN14

L8

P_GFX_RXP15

L9

P_GFX_RXN15

AC5

P_GPP_RXP0

AC6

P_GPP_RXN0

AC8

P_GPP_RXP1

AC9

P_GPP_RXN1

AB7

P_GPP_RXP2

AB8

P_GPP_RXN2

AA5

P_GPP_RXP3

AA6

P_GPP_RXN3

AF8

P_UMI_RXP0

AF7

P_UMI_RXN0

AE6

P_UMI_RXP1

AE5

P_UMI_RXN1

AE9

P_UMI_RXP2

AE8

P_UMI_RXN2

AD8

P_UMI_RXP3

AD7

K5

P_UMI_RXN3

P_ZVDDP

SAINE

SAINE

P_ZVDDP P_ZVSS

PCI EXPRESS

PCI EXPRESS

SAINE

SAINE

GPP GRAPHICS

GPP GRAPHICS

UMI-LINK

UMI-LINK

62.10055.481

62.10055.481

6 OF 6

6 OF 6

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

AA2

AA3

Y2

Y1

Y4

Y5

W2

W3

V2

V1

V4

V5

U2

U3

T2

T1

T4

T5

R2

R3

P2

P1

P4

P5

N2

N3

M2

M1

M4

M5

L2

L3

AD4

AD5

AC2

AC3

AB2

AB1

AB4

AB5

AF1

AF2

AF5

AF4

AE3

AE2

AD1

AD2

K4

GTXP0

DIS

DIS

GTXN0

DIS

DIS

GTXP1

DIS

DIS

GTXN1

DIS

DIS

GTXP2

DIS

DIS

GTXN2

DIS

DIS

GTXP3

DIS

DIS

GTXN3

DIS

DIS

GTXP4

DIS

DIS

GTXN4

DIS

DIS

GTXP5

DIS

DIS

GTXN5

DIS

DIS

GTXP6

DIS

DIS

GTXN6

DIS

DIS

GTXP7

DIS

DIS

GTXN7

DIS

DIS

GTXP8

DIS_PX

DIS_PX

GTXN8

DIS_PX

DIS_PX

GTXP9

DIS_PX

DIS_PX

GTXN9

DIS_PX

DIS_PX

GTXP10

DIS_PX

DIS_PX

GTXN10

DIS_PX

DIS_PX

GTXP11

DIS_PX

DIS_PX

GTXN11

DIS_PX

DIS_PX

GTXP12

DIS_PX

DIS_PX

GTXN12

DIS_PX

DIS_PX

GTXP13

DIS_PX

DIS_PX

GTXN13

DIS_PX

DIS_PX

GTXP14

DIS_PX

DIS_PX

GTXN14

DIS_PX

DIS_PX

GTXP15

DIS_PX

DIS_PX

GTXN15

DIS_PX

DIS_PX

PCIE_TXP0 _C

PCIE_TXN0 _C

PCIE_TXP1 _C

PCIE_TXN1 _C

PCIE_TXP2 _C

PCIE_TXN2 _C

UMI_TX0P_ C

UMI_TX0N_ C

UMI_TX1P_ C

UMI_TX1N_ C

UMI_TX2P_ C

UMI_TX2N_ C

UMI_TX3P_ C

UMI_TX3N_ C

C401 SCD1U16 V2KX-3GP

C401 SCD1U16 V2KX-3GP

1 2

C402 SCD1U16 V2KX-3GP

C402 SCD1U16 V2KX-3GP

1 2

C403 SCD1U16 V2KX-3GP

C403 SCD1U16 V2KX-3GP

1 2

C404 SCD1U16 V2KX-3GP

C404 SCD1U16 V2KX-3GP

1 2

C405 SCD1U16 V2KX-3GP

C405 SCD1U16 V2KX-3GP

1 2

C406 SCD1U16 V2KX-3GP

C406 SCD1U16 V2KX-3GP

1 2

C407 SCD1U16 V2KX-3GP

C407 SCD1U16 V2KX-3GP

1 2

C408 SCD1U16 V2KX-3GP

C408 SCD1U16 V2KX-3GP

1 2

C409 SCD1U16 V2KX-3GP

C409 SCD1U16 V2KX-3GP

1 2

C410 SCD1U16 V2KX-3GP

C410 SCD1U16 V2KX-3GP

1 2

C411 SCD1U16 V2KX-3GP

C411 SCD1U16 V2KX-3GP

1 2

C412 SCD1U16 V2KX-3GP

C412 SCD1U16 V2KX-3GP

1 2

C413 SCD1U16 V2KX-3GP

C413 SCD1U16 V2KX-3GP

1 2

C414 SCD1U16 V2KX-3GP

C414 SCD1U16 V2KX-3GP

1 2

C415 SCD1U16 V2KX-3GP

C415 SCD1U16 V2KX-3GP

1 2

C416 SCD1U16 V2KX-3GP

C416 SCD1U16 V2KX-3GP

1 2

C417 SCD1U16 V2KX-3GP

C417 SCD1U16 V2KX-3GP

1 2

C418 SCD1U16 V2KX-3GP

C418 SCD1U16 V2KX-3GP

1 2

C419 SCD1U16 V2KX-3GP

C419 SCD1U16 V2KX-3GP

1 2

C420 SCD1U16 V2KX-3GP

C420 SCD1U16 V2KX-3GP

1 2

C421 SCD1U16 V2KX-3GP

C421 SCD1U16 V2KX-3GP

1 2

C422 SCD1U16 V2KX-3GP

C422 SCD1U16 V2KX-3GP

1 2

C423 SCD1U16 V2KX-3GP

C423 SCD1U16 V2KX-3GP

1 2

C424 SCD1U16 V2KX-3GP

C424 SCD1U16 V2KX-3GP

1 2

C425 SCD1U16 V2KX-3GP

C425 SCD1U16 V2KX-3GP

1 2

C426 SCD1U16 V2KX-3GP

C426 SCD1U16 V2KX-3GP

1 2

C427 SCD1U16 V2KX-3GP

C427 SCD1U16 V2KX-3GP

1 2

C428 SCD1U16 V2KX-3GP

C428 SCD1U16 V2KX-3GP

1 2

C429 SCD1U16 V2KX-3GP

C429 SCD1U16 V2KX-3GP

1 2

C430 SCD1U16 V2KX-3GP

C430 SCD1U16 V2KX-3GP

1 2

C431 SCD1U16 V2KX-3GP

C431 SCD1U16 V2KX-3GP

1 2

C432 SCD1U16 V2KX-3GP

C432 SCD1U16 V2KX-3GP

1 2

C441 SCD1U16 V2KX-3GPC441 SCD1U16 V2KX-3GP

1 2

C442 SCD1U16 V2KX-3GPC442 SCD1U16 V2KX-3GP

1 2

C443 SCD1U16 V2KX-3GP

C443 SCD1U16 V2KX-3GP

1 2

C444 SCD1U16 V2KX-3GP

C444 SCD1U16 V2KX-3GP

1 2

C457 SCD1U16 V2KX-3GPC457 SCD1U16 V2KX-3GP

1 2

C460 SCD1U16 V2KX-3GPC460 SCD1U16 V2KX-3GP

1 2

C445 SCD1U16 V2KX-3GPC445 SCD1U16 V2KX-3GP

C446 SCD1U16 V2KX-3GPC446 SCD1U16 V2KX-3GP

C447 SCD1U16 V2KX-3GPC447 SCD1U16 V2KX-3GP

C448 SCD1U16 V2KX-3GPC448 SCD1U16 V2KX-3GP

C449 SCD1U16 V2KX-3GPC449 SCD1U16 V2KX-3GP

C450 SCD1U16 V2KX-3GPC450 SCD1U16 V2KX-3GP

C451 SCD1U16 V2KX-3GPC451 SCD1U16 V2KX-3GP

C452 SCD1U16 V2KX-3GPC452 SCD1U16 V2KX-3GP

12

R401

R401

196R2F-G P

196R2F-G P

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PEG_TXP 0

PEG_TXN 0

PEG_TXP 1

PEG_TXN 1

PEG_TXP 2

PEG_TXN 2

PEG_TXP 3

PEG_TXN 3

PEG_TXP 4

PEG_TXN 4

PEG_TXP 5

PEG_TXN 5

PEG_TXP 6

PEG_TXN 6

PEG_TXP 7

PEG_TXN 7

PEG_TXP 8

PEG_TXN 8

PEG_TXP 9

PEG_TXN 9

PEG_TXP 10

PEG_TXN 10

PEG_TXP 11

PEG_TXN 11

PEG_TXP 12

PEG_TXN 12

PEG_TXP 13

PEG_TXN 13

PEG_TXP 14

PEG_TXN 14

PEG_TXP 15

PEG_TXN 15

3G

3G

3G

3G

UMI_APU_F CH_TX0P 17

UMI_APU_F CH_TX0N 17

UMI_APU_F CH_TX1P 17

UMI_APU_F CH_TX1N 17

UMI_APU_F CH_TX2P 17

UMI_APU_F CH_TX2N 17

UMI_APU_F CH_TX3P 17

UMI_APU_F CH_TX3N 17

PCIE_TXP0 31

PCIE_TXN0 31

PCIE_TXP1 66

PCIE_TXN1 66

PCIE_TXP2 65

PCIE_TXN2 65

GTXP0

GTXN0

GTXP1

GTXN1

GTXP2

GTXN2

GTXP3

GTXN3

LAN

WWANWWAN

WLAN

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

110325 -1

C433 SCD1U16 V2KX-3GP

C433 SCD1U16 V2KX-3GP

1 2

C434 SCD1U16 V2KX-3GP

C434 SCD1U16 V2KX-3GP

1 2

C435 SCD1U16 V2KX-3GP

C435 SCD1U16 V2KX-3GP

1 2

C436 SCD1U16 V2KX-3GP

C436 SCD1U16 V2KX-3GP

1 2

C437 SCD1U16 V2KX-3GP

C437 SCD1U16 V2KX-3GP

1 2

C438 SCD1U16 V2KX-3GP

C438 SCD1U16 V2KX-3GP

1 2

C439 SCD1U16 V2KX-3GP

C439 SCD1U16 V2KX-3GP

1 2

C440 SCD1U16 V2KX-3GP

C440 SCD1U16 V2KX-3GP

1 2

PEG_TXP [0..15]

PEG_TXN [0..15]

PEG_RXP [0..15]

PEG_RXN [0..15]

APU_HDM I_DATA2 51

APU_HDM I_DATA2# 51

APU_HDM I_DATA1 51

APU_HDM I_DATA1# 51

APU_HDM I_DATA0 51

APU_HDM I_DATA0# 51

APU_HDM I_CLK 51

APU_HDM I_CLK# 51

PEG_TXP [0..15] 83

PEG_TXN [0..15] 83

PEG_RXP [0..15] 83

PEG_RXN [0..15] 83

B B

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

APU_PCIE(1/5)

APU_PCIE(1/5)

APU_PCIE(1/5)

JE50_SB

JE50_SB

JE50_SB

Taipei Hsien 221, Taiwan, R.O.C.

4 102

4 102

4 102

1

SB

SB

SB

5

Dr-Bios.com

4

3

2

1

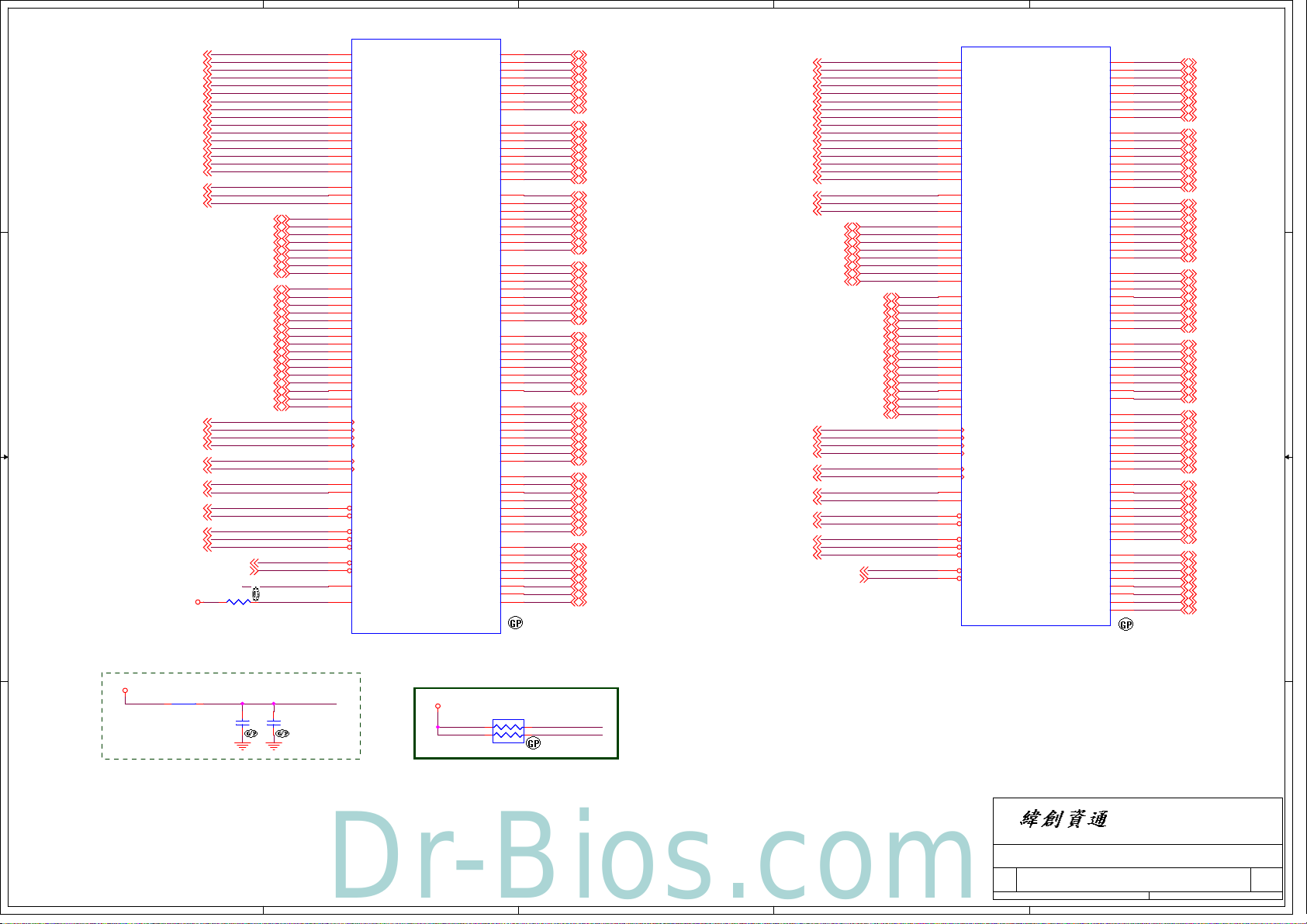

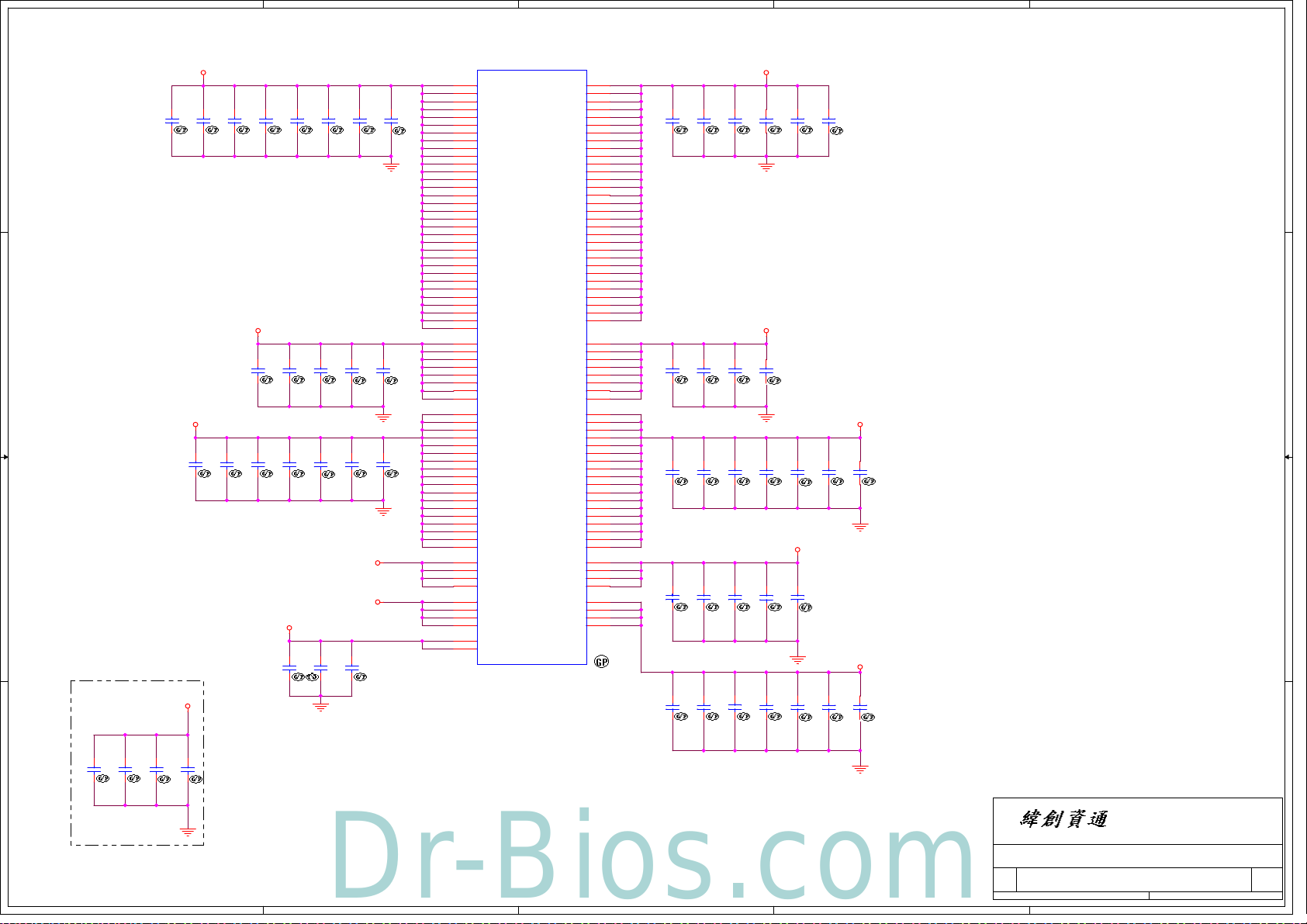

APU1A

APU1A

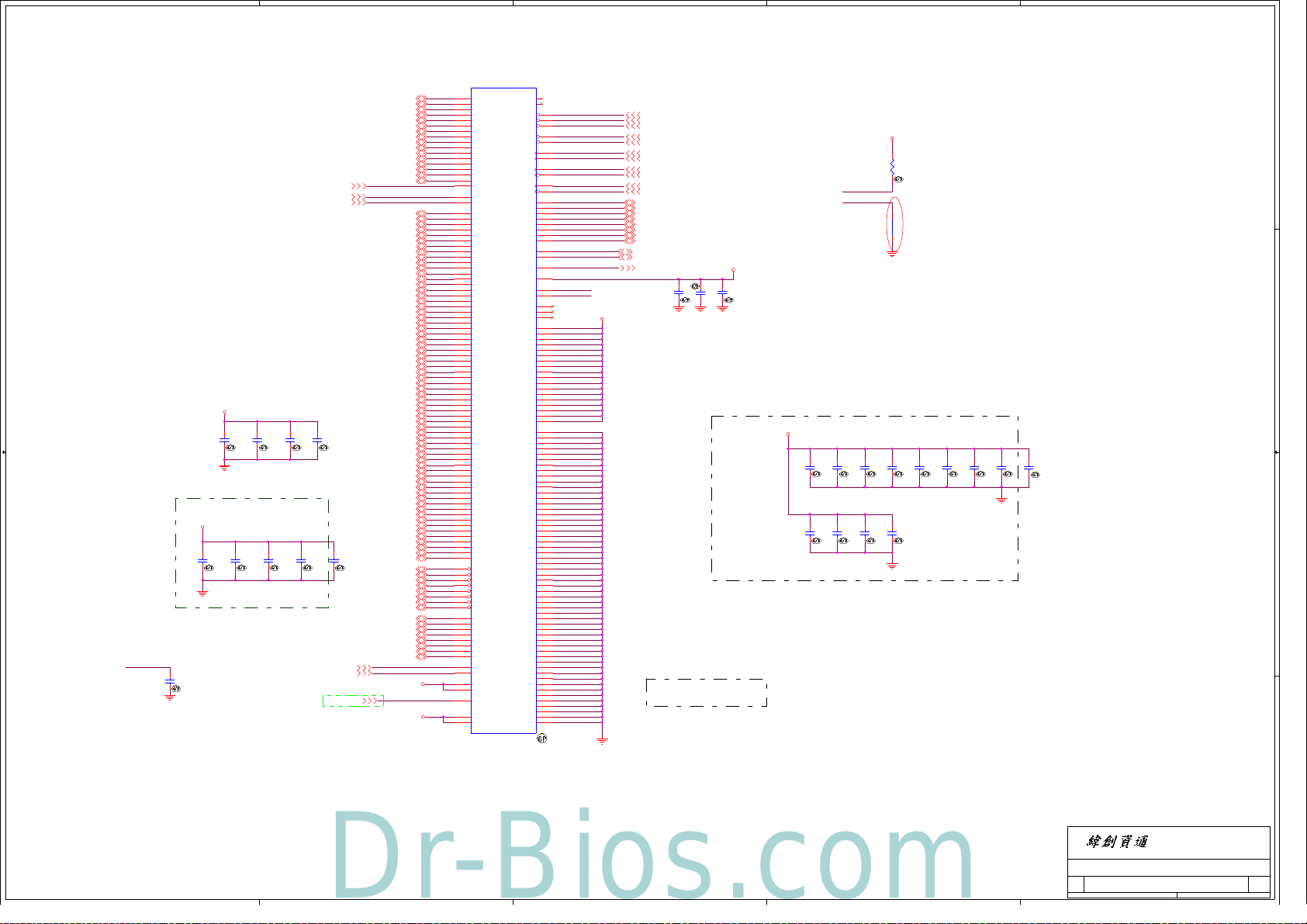

MEMORY CHANNEL

MEMORY CHANNEL

A

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

MA_BANK2

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

MA_CLK_H0

MA_CLK_L0

MA_CLK_H1

MA_CLK_L1

MA_CKE0

MA_CKE1

MA_ODT0

MA_ODT1

MA_CS#0

MA_CS#1

MA_RAS#

MA_CAS#

MA_WE#

MA_RESET#

MA_EVENT#

M_VREF

M_ZVDDIO

SAINE

SAINE

A

SAINE

SAINE

62.10055.481

62.10055.481

M21

M22

AA25

AD27

AC23

AD19

AC15

G14

G18

AE26

AD26

AB22

AA22

AB18

AA18

AA14

AA15

AA27

AA26

W24

W23

W20

W21

U20

R20

R21

P22

P21

N24

N23

N20

N21

U23

L24

L21

L20

U24

U21

L23

E14

J17

E21

F25

H14

H18

J21

H21

E27

E26

T21

T22

R23

R24

H28

H27

Y25

V22

V21

H25

T24

M_A_A014

M_A_A114

M_A_A214

M_A_A314

M_A_A414

M_A_A514

M_A_A614

M_A_A714

D D

C C

B B

M_A_A814

M_A_A914

M_A_A1014

M_A_A1114

M_A_A1214

M_A_A1314

M_A_A1414

M_A_A1514

M_A_BS014

M_A_BS114

M_A_BS214

M_A_DM014

M_A_DM114

M_A_DM214

M_A_DM314

M_A_DM414

M_A_DM514

M_A_DM614

M_A_DM714

M_A_DQS 014

M_A_DQS #014

M_A_DQS 114

M_A_DQS #114

M_A_DQS 214

M_A_DQS #214

M_A_DQS 314

M_A_DQS #314

M_A_DQS 414

M_A_DQS #414

M_A_DQS 514

M_A_DQS #514

M_A_DQS 614

M_A_DQS #614

M_A_DQS 714

M_A_DQS #714

M_A_DIM0_ CLK_DDR014

M_A_DIM0_ CLK_DDR#014

M_A_DIM0_ CLK_DDR114

M_A_DIM0_ CLK_DDR#114

M_A_DIM0_ CKE014

M_A_DIM0_ CKE114

M_A_DIM0_ ODT014

M_A_DIM0_ ODT114

M_A_DIM0_ CS#01 4

M_A_DIM0_ CS#11 4

M_A_RAS #14

M_A_CAS #14

M_A_W E#1 4

M_A_RST #14

M_A_EVE NT#14

M_VREF_ DQ_APU

1D5V_S3

1 2

R501

R501

39R2F-GP

39R2F-GP

M_ZVDDIO

1 OF 6

1 OF 6

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

E13

J13

H15

J15

H13

F13

F15

E15

H17

F17

E19

J19

G16

H16

H19

F19

H20

F21

J23

H23

G20

E20

G22

H22

G24

E25

G27

G26

F23

H24

E28

F27

AB28

AC27

AD25

AA24

AE28

AD28

AB26

AC25

Y23

AA23

Y21

AA20

AB24

AD24

AA21

AC21

AA19

AC19

AC17

AA17

AB20

Y19

AD18

AD17

AA16

Y15

AA13

AC13

Y17

AB16

AB14

Y13

M_A_DQ0 14

M_A_DQ1 14

M_A_DQ2 14

M_A_DQ3 14

M_A_DQ4 14

M_A_DQ5 14

M_A_DQ6 14

M_A_DQ7 14

M_A_DQ8 14

M_A_DQ9 14

M_A_DQ1 0 14

M_A_DQ1 1 14

M_A_DQ1 2 14

M_A_DQ1 3 14

M_A_DQ1 4 14

M_A_DQ1 5 14

M_A_DQ1 6 14

M_A_DQ1 7 14

M_A_DQ1 8 14

M_A_DQ1 9 14

M_A_DQ2 0 14

M_A_DQ2 1 14

M_A_DQ2 2 14

M_A_DQ2 3 14

M_A_DQ2 4 14

M_A_DQ2 5 14

M_A_DQ2 6 14

M_A_DQ2 7 14

M_A_DQ2 8 14

M_A_DQ2 9 14

M_A_DQ3 0 14

M_A_DQ3 1 14

M_A_DQ3 2 14

M_A_DQ3 3 14

M_A_DQ3 4 14

M_A_DQ3 5 14

M_A_DQ3 6 14

M_A_DQ3 7 14

M_A_DQ3 8 14

M_A_DQ3 9 14

M_A_DQ4 0 14

M_A_DQ4 1 14

M_A_DQ4 2 14

M_A_DQ4 3 14

M_A_DQ4 4 14

M_A_DQ4 5 14

M_A_DQ4 6 14

M_A_DQ4 7 14

M_A_DQ4 8 14

M_A_DQ4 9 14

M_A_DQ5 0 14

M_A_DQ5 1 14

M_A_DQ5 2 14

M_A_DQ5 3 14

M_A_DQ5 4 14

M_A_DQ5 5 14

M_A_DQ5 6 14

M_A_DQ5 7 14

M_A_DQ5 8 14

M_A_DQ5 9 14

M_A_DQ6 0 14

M_A_DQ6 1 14

M_A_DQ6 2 14

M_A_DQ6 3 14

APU1B

APU1B

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CKE0

MB_CKE1

MB_ODT0

MB_ODT1

MB_CS#0

MB_CS#1

MB_RAS#

MB_CAS#

MB_WE#

MB_RESET#

MB_EVENT#

SAINE

SAINE

MEMORY CHANNEL B

SAINE

SAINE

62.10055.481

62.10055.481

M_B_A015

M_B_A115

M_B_A215

M_B_A315

M_B_A415

M_B_A515

M_B_A615

M_B_A715

M_B_A815

M_B_A915

M_B_A1015

M_B_A1115

M_B_A1215

M_B_A1315

M_B_A1415

M_B_A1515

M_B_BS015

M_B_BS115

M_B_BS215

M_B_DM01 5

M_B_DM11 5

M_B_DM21 5

M_B_DM31 5

M_B_DM41 5

M_B_DM51 5

M_B_DM61 5

M_B_DM71 5

M_B_DQS 015

M_B_DQS #015

M_B_DQS 115

M_B_DQS #115

M_B_DQS 215

M_B_DQS #215

M_B_DQS 315

M_B_DQS #315

M_B_DQS 415

M_B_DQS #415

M_B_DQS 515

M_B_DQS #515

M_B_DQS 615

M_B_DQS #615

M_B_DQS 715

M_B_DQS #715

M_B_DIM0_ CLK_DDR015

M_B_DIM0_ CLK_DDR#015

M_B_DIM0_ CLK_DDR115

M_B_DIM0_ CLK_DDR#115

M_B_DIM0_ CKE015

M_B_DIM0_ CKE115

M_B_DIM0_ ODT015

M_B_DIM0_ ODT115

M_B_DIM0_ CS#01 5

M_B_DIM0_ CS#11 5

M_B_RAS #15

M_B_CAS #15

M_B_W E#15

M_B_RST #15

M_B_EVE NT#15

T27

P24

P25

N27

N26

M28

M27

M24

M25

U26

K27

W26

K25

K24

U27

T28

K28

D14

A18

A22

C25

AF25

AG22

AH18

AD14

C15

B15

E18

D18

E22

D22

B26

A26

AG24

AG25

AG21

AF21

AG17

AG18

AH14

AG14

R26

R27

W27

V28

L26

L27

P27

P28

J26

J27

Y28

V25

Y27

V24

V27

J25

T25

2 OF 6

2 OF 6

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

A14

B14

D16

E16

B13

C13

B16

A16

C17

B18

B20

A20

E17

B17

B19

C19

C21

B22

C23

A24

D20

B21

E23

B23

E24

B25

B27

D28

B24

D24

D26

C27

AG26

AH26

AF23

AG23

AG27

AF27

AH24

AE24

AE22

AH22

AE20

AH20

AD23

AD22

AD21

AD20

AF19

AE18

AE16

AH16

AG20

AG19

AF17

AD16

AG15

AD15

AG13

AD13

AG16

AF15

AE14

AF13

M_B_DQ0 15

M_B_DQ1 15

M_B_DQ2 15

M_B_DQ3 15

M_B_DQ4 15

M_B_DQ5 15

M_B_DQ6 15

M_B_DQ7 15

M_B_DQ8 15

M_B_DQ9 15

M_B_DQ1 0 15

M_B_DQ1 1 15

M_B_DQ1 2 15

M_B_DQ1 3 15

M_B_DQ1 4 15

M_B_DQ1 5 15

M_B_DQ1 6 15

M_B_DQ1 7 15

M_B_DQ1 8 15

M_B_DQ1 9 15

M_B_DQ2 0 15

M_B_DQ2 1 15

M_B_DQ2 2 15

M_B_DQ2 3 15

M_B_DQ2 4 15

M_B_DQ2 5 15

M_B_DQ2 6 15

M_B_DQ2 7 15

M_B_DQ2 8 15

M_B_DQ2 9 15

M_B_DQ3 0 15

M_B_DQ3 1 15

M_B_DQ3 2 15

M_B_DQ3 3 15

M_B_DQ3 4 15

M_B_DQ3 5 15

M_B_DQ3 6 15

M_B_DQ3 7 15

M_B_DQ3 8 15

M_B_DQ3 9 15

M_B_DQ4 0 15

M_B_DQ4 1 15

M_B_DQ4 2 15

M_B_DQ4 3 15

M_B_DQ4 4 15

M_B_DQ4 5 15

M_B_DQ4 6 15

M_B_DQ4 7 15

M_B_DQ4 8 15

M_B_DQ4 9 15

M_B_DQ5 0 15

M_B_DQ5 1 15

M_B_DQ5 2 15

M_B_DQ5 3 15

M_B_DQ5 4 15

M_B_DQ5 5 15

M_B_DQ5 6 15

M_B_DQ5 7 15

M_B_DQ5 8 15

M_B_DQ5 9 15

M_B_DQ6 0 15

M_B_DQ6 1 15

M_B_DQ6 2 15

M_B_DQ6 3 15

APU_VREF_DQ

DDR_VRE F_S3

LAYOUT: place them close to APU

A A

5

R5020R0603-PADR5020R0603-P AD

1 2

SCD1U10 V2KX-5GP

SCD1U10 V2KX-5GP

C501

C501

12

M_VREF_ DQ_APU

12

C502

C502

SC1KP50 V2KX-1GP

SC1KP50 V2KX-1GP

4

1D5V_S3

0920-SA

RN501

RN501

1

2

SRN1KJ-7 -GP

SRN1KJ-7 -GP

4

3

M_A_EVE NT#

M_B_EVE NT#

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet

APU_DDR(2/5)

APU_DDR(2/5)

APU_DDR(2/5)

JE50_SB

JE50_SB

JE50_SB

Taipei Hsien 221, Taiwan, R.O.C.

5 102

5 102

5 102

1

of

SB

SB

SB

1

Dr-Bios.com

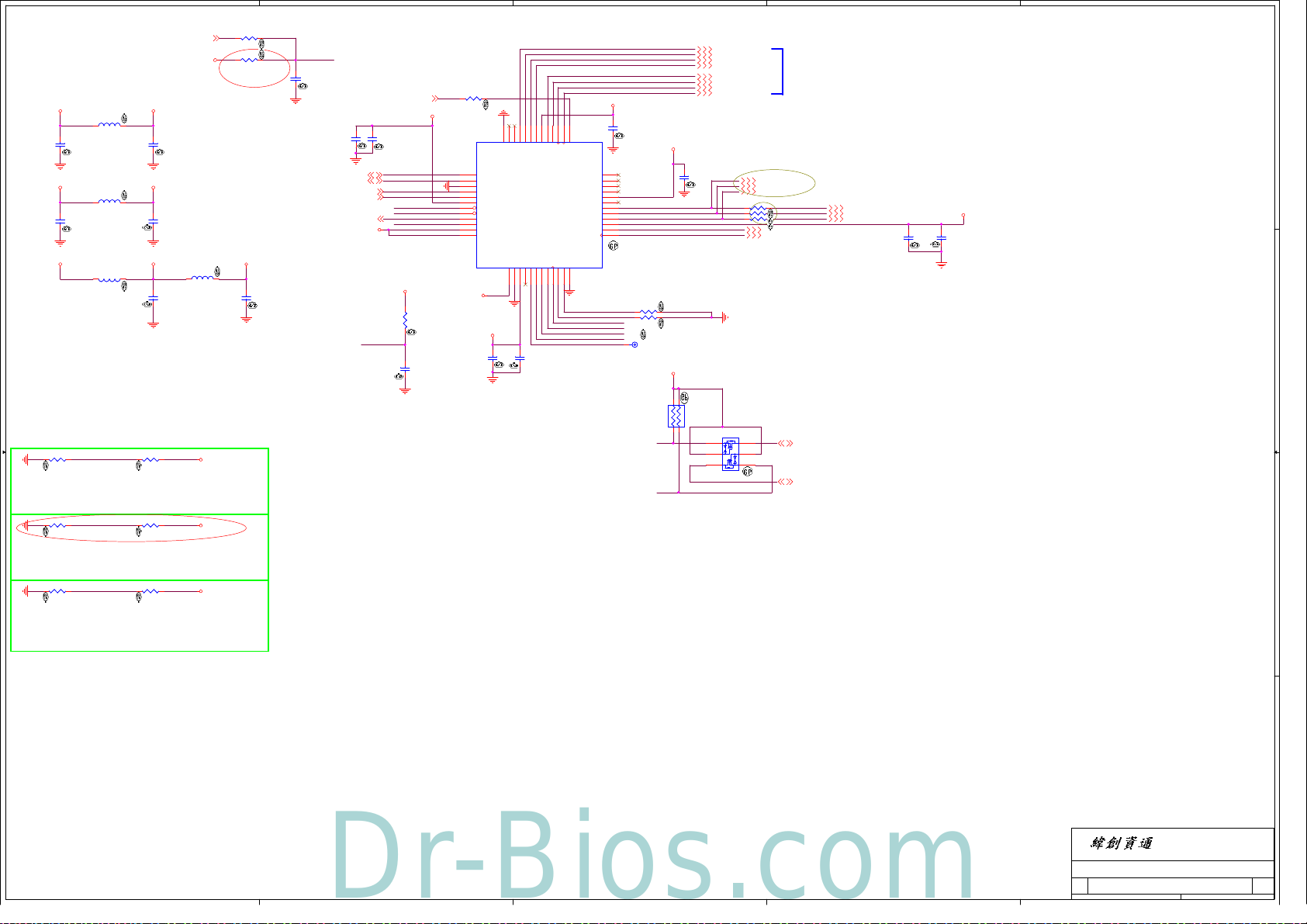

RN609

RN609

3

2

4

1

SRN1K8J-GP

SRN1K8J-GP

RN610

RN610

4

1

3

2

SRN1K8J-GP

SRN1K8J-GP

R611

R611

12

510R2J-1-GP

510R2J-1-GP

R608 39R2F- GPR608 39R2F- GP

12

R602

R602

1 2

0R2J-2-GP

0R2J-2-GP

DY

DY

RN603

RN603

8

1

7

2

6

3

5

4

SRN1KJ-4-G P

SRN1KJ-4-G P

RN602

RN602

8

1

7

2

6

3

5

4

SRN1KJ-4-G P

SRN1KJ-4-G P

1D2V_S0

R613

R613

1 2

510R2J-1-GP

510R2J-1-GP

1D5V_S3

R643

R643

1 2

1KR2J-1-GP

1KR2J-1-GP

3D3V_AUX_S5

R615

R615

10KR2J-3-GP

10KR2J-3-GP

1 2

DY

DY

1D5V_S3

84.03904.L06

84.03904.L06

3

1

2

12

R639

R639

1 2

150KR2J-L1-GP

150KR2J-L1-GP

R644

R644

100KR2J-1-GP

100KR2J-1-GP

DP_HPD1_C_ B

2ND = 84.03904.P11

2ND = 84.03904.P11

110324 -1

1D5V_S33D3V_VGA_S0

R694

R694

0R2J-2-GP

0R2J-2-GP

UMA_PX

UMA_PX

1 2

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

3

UMA_PX

UMA_PX

Q605

Q605

1

PMBS3904-1-GP

PMBS3904-1-GP

2

R690

R690

EDP_HPD

0R2J-2-GP

0R2J-2-GP

1 2

DY

DY

R689

R689

DP0_HPD

0R2J-2-GP

0R2J-2-GP

1 2

UMA_PX

UMA_PX

12

R642

R642

10KR2J-3-GP

10KR2J-3-GP

UMA_PX

UMA_PX

EDP_HPD_D ET 85DP_HPD0_C9,49

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

APU_Control&Debug(3/5)

APU_Control&Debug(3/5)

APU_Control&Debug(3/5)

JE50_SB

JE50_SB

JE50_SB

1

6 102

6 102

6 102

Q604

Q604

PMBS3904-1-GP

PMBS3904-1-GP

R640

R640

10KR2J-3-GP

10KR2J-3-GP

EDP_HPD_D ET 85

DP1_HPD

SB

SB

SB

eDP

LVDS

HDMI

R612

R612

300R2J-4-GP

300R2J-4-GP

1 2

R617

R617

300R2J-4-GP

300R2J-4-GP

1 2

DY

DY

12

R655

R655

4K7R2J-2-GP

4K7R2J-2-GP

D

2

LVDS_CHN_T RAVIS

LVDS_CHP_T RAVIS

UMA_PX

UMA_PX

110324 -1

3D3V_S5

2

1D5V_S3

R656

R656

2K2R2J-2-GP

2K2R2J-2-GP

1 2

APU_BLPWM_Q

1

UMA_PX

UMA_PX

2

3

Q608

Q608

PMBS3904-1-GP

PMBS3904-1-GP

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

DP_HPD0_C9,49

12

R652

R652

10KR2J-3-GP

10KR2J-3-GP

SML1_DATA 9,27,85

APU_DP_AUXP _CPU

APU_DP_AUXN _CPU

DP_AUX1P

DP_AUX1N

APU_TEST25_H _BYPASSCLK_H

M_TEST

APU_TEST9_AN ALOGIN

APU_TEST12_SC ANSHIFTEND

APU_TEST22_SC ANSHIFTEN

APU_TEST19_PLL TEST0

DY

DY

12

R658

R658

4K7R2J-2-GP

4K7R2J-2-GP

UMA_PX

UMA_PX

R687

R687

0R2J-2-GP

0R2J-2-GP

1 2

UMA_PX_EDP

UMA_PX_EDP

3D3V_S0

R622

R622

0R2J-2-GP

0R2J-2-GP

1 2

HPD_C HPD_C_B

DY

DY

R674

R674

100KR2J-1-GP

100KR2J-1-GP

1 2

R675

R675

100KR2J-1-GP

100KR2J-1-GP

1 2

[AMD FAE Frank]:

this is electrical key

do not allow power to turn on if this pin is still "L"

FS1 package is open pin

in the furtur,FS1r2 will have this pin tied to VSS

if the wrong processor is plug ged the socket

This is more of a problem on desktop platforms

(changing CPUs)

3D3V_S0

UMA_PX

UMA_PX

APU_TEST18_PLL TEST1

APU_TEST21_SC ANEN

APU_TEST20_SC ANCLK2

APU_TEST24_SC ANCLK1

APU_TEST25_L_B YPASSCLK_L

ALLOW_STO P

FS1R1

DP_HPD1_R19

12

DY

DY

APU_BLPWM _TRAVIS 9,27

L_BKLT_CTRL_R 9 ,10

R695

R695

0R2J-2-GP

0R2J-2-GP

DY

DY

1 2

EDP_HPD_PW R

R641

R641

1 2

150KR2J-L1-GP

150KR2J-L1-GP

UMA_PX

UMA_PX

12

R646

R646

100KR2J-1-GP

100KR2J-1-GP

UMA_PX

UMA_PX

3D3V_VGA_S0

R693

R693

0R2J-2-GP

0R2J-2-GP

DY

DY

1 2

R691

R691

33R2J-2-GP

33R2J-2-GP

1 2

DIS_EDP

DIS_EDP

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size D ocument Numbe r Rev

Size D ocument Numbe r Rev

Size D ocument Numbe r Rev

Custom

Custom

Custom

Friday, Apri l 01, 2011

Friday, Apri l 01, 2011

Friday, Apri l 01, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

3

APU_DP_AUXP _CPU

APU_DP_AUXN _CPU

C603 SCD1U16V2KX- 3GP

C603 SCD1U16V2KX- 3GP

1 2

C601 SCD1U16V2KX- 3GP

C601 SCD1U16V2KX- 3GP

1 2

C626 SCD1U16V2KX- 3GP

C626 SCD1U16V2KX- 3GP

1 2

C627 SCD1U16V2KX- 3GP

C627 SCD1U16V2KX- 3GP

1 2

DP2_HPD 51

R623

R623

1 2

150R2F-1-GP

150R2F-1-GP

APU_DIGON

UMA_PX_EDP

UMA_PX_EDP

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

12

R661

R661

100KR2J-1-GP

100KR2J-1-GP

3

2

TP611TP611

TP610TP610

TP612TP612

TP613TP613

APU_TEST18_PLL TEST1 71

APU_TEST19_PLL TEST0 71

TP601TP601

TP617TP617

TP618TP618

TP619TP619

FS1R1 36

ALLOW_STO P 17

UMA_PX_EDP

UMA_PX_EDP

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

12

R662

R662

100KR2J-1-GP

100KR2J-1-GP

UMA_PX_EDP

UMA_PX_EDP

1D5V_S3

R660

R660

2K2R2J-2-GP

2K2R2J-2-GP

1 2

3D3V_S0

APU_BLEN_Q

1

3

Q609

Q609

PMBS3904-1-GP

PMBS3904-1-GP

UMA_PX_EDP

UMA_PX_EDP

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX

UMA_PX

UMA_PX

UMA_PX

100KR2J-1-GP

100KR2J-1-GP

DP0_HPD

1D5V_S3

R664

R664

2K2R2J-2-GP

2K2R2J-2-GP

1 2

APU_DIGON_Q

1

2

3

Q610

Q610

PMBS3904-1-GP

PMBS3904-1-GP

UMA_PX_EDP

UMA_PX_EDP

12

R659

R659

4K7R2J-2-GP

4K7R2J-2-GP

UMA_PX_EDP

UMA_PX_EDP

R653

R653

1D5V_S0

DY

DY

APU_DP_AUXP _CPU 94

APU_DP_AUXN _CPU 94

LVDS_CHP_T RAVIS 9

LVDS_CHN_T RAVIS 9

DP1_AUXP_R 19

DP1_AUXN_R 19

PCH_HDMI_CLK _R 51

PCH_HDMI_DA TA_R 51

12

TEST35

[AMD HDMI desing guidance]

Strap define PU :Enable HDMI

PD:Disable HDMI

3D3V_S0

12

R663

R663

4K7R2J-2-GP

4K7R2J-2-GP

UMA_PX_EDP

UMA_PX_EDP

L_BKLT_EN_R 9,10

1D5V_S3

APU_SID

CRT

1D5V_S3

DY

DY

APU_BLPWM

LVDS_VDD_EN _R 9 ,10

110324 -1

BSS138-8-GP

BSS138-8-GP

G

S

Q607

Q607

TP620TP620

TP622TP622

TP623TP623

4

TRAVIS

LVDS Panel

DP1_TX0P

DP1_TX0N

DP1_TX1P

DP1_TX1N

DP1_TX2P

DP1_TX2N

DP1_TX3P

DP1_TX3N

APU_SIC

APU_SID

APU_RST#_R

APU_PWR GD_R

APU_THERM TRIP#_VDDIO

APU_ALERT#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

APU_RUN_F B_L

APU_VDDP_F B_H

1

APU_VDDIO_SU S_FB_H

1

APU_VDDR_ FB_H

1

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

H_CPUPW RGD_E

1D5V_S3

APU_SIC

4

D2

D1

C2

C3

H2

H1

G2

G3

AH7

AH6

AH4

AH3

AH11

AG11

AF10

AE10

AD10

AG12

AH12

C12

A12

A11

D12

B12

B11

C11

K21

AC11

C8

B10

C9

A10

110328 -1

APU1C

APU1C

F2

DP0_TXP0

F1

DP0_TXN0

E3

DP0_TXP1

E2

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

K2

DP1_TXP0

K1

DP1_TXN0

J3

DP1_TXP1

J2

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

B8

SVC

A8

SVD

SIC

SID

RESET#

PWROK

PROCHOT#

THERMTRIP#

ALERT#

TDI

TDO

TCK

TMS

TRST#

DBRDY

DBREQ#

E8

RSVD#E8

RSVD#K21

RSVD#AC11

B9

VSS_SENSE

VDDP_SENSE

A9

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

VDDR_SENSE

SAINE

SAINE

G

S

1D5V_S0

DY

DY

2

1 2

Q606

Q606

BSS138-8-GP

BSS138-8-GP

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT 1

DISPLAY PORT 1

JTAG CTRL SER. CLK

JTAG CTRL SER. CLK

RSVD

RSVD

SENSE

SENSE

12

R667

R667

10KR2J-3-GP

10KR2J-3-GP

H_CPUPWRGD_B

1

DY

DY

3

Q611

Q611

PMBS3904-1-GP

PMBS3904-1-GP

R633 0R0402-PADR633 0R0402- PAD

D

3D3V_S0

3D3V_S5

12

R668

R668

10KR2J-3-GP

10KR2J-3-GP

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

SAINE

SAINE

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

TEST6

TEST9

TEST10

TEST12

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST21

TEST22

TEST

TEST

TEST23

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FS1R1

DMAACTIVE#

THERMDA

THERMDC

62.10055.481

62.10055.481

DY

DY

H_CPUPW RGD 42

12

R650

R650

10KR2J-3-GP

10KR2J-3-GP

SML1_CLK 9,27,85

3 OF 6

3 OF 6

D4

D5

E5

E6

J5

J6

H4

H5

G5

G6

F4

F5

D7

E7

J7

H7

G7

F7

C6

C5

C7

D8

AA10

G10

H10

H12

D9

E9

G9

H9

H11

G11

F12

E11

D11

F10

G12

AH10

AH9

K7

K8

AA12

AB12

K22

AB11

AA11

D10

Y11

AB10

AE12

AD12

DP_AUX1P

DP_AUX1N

DP0_HPD

DP1_HPD

APU_BLEN

APU_DIGON

APU_BLPWM

DP_AUX_ZVSS

APU_TEST9_AN ALOGIN

APU_TEST12_SC ANSHIFTEND

APU_TEST14_BP 0

APU_TEST15_BP 1

APU_TEST16_BP 2

APU_TEST17_BP 3

APU_TEST18_PLL TEST1

APU_TEST19_PLL TEST0

APU_TEST20_SC ANCLK2

APU_TEST21_SC ANEN

APU_TEST22_SC ANSHIFTEN

APU_TEST24_SC ANCLK1

APU_TEST25_H _BYPASSCLK_H

APU_TEST25_L_B YPASSCLK_L

ANATSTIN_H

ANATSTIN_L

M_TEST

ANATSTOUT _H

ANATSTOUT _L

TEST35

APU_BLEN

UMA_PX_EDP

UMA_PX_EDP

5

1.1

1.0

0.9

0.8

12

R636

R636

2K2R2J-2-GP

2K2R2J-2-GP

DY

DY

3D3V_S5

APU_ALERT#_Q

1

3

Q603

Q603

PMBS3904-1-GP

PMBS3904-1-GP

H_CPUPW RGD_E

H_CPUPW RGD_E

APU_SVC_R

APU_SVD_R

APU_PROCH OT#

Boot Voltage

(open)

1.1

1.2

1.1

0.9

APU_RST_L_BU F71

APU_RST#17

110328 -1

12

R673

R673

10KR2J-3-GP

10KR2J-3-GP

DY

DY

PCH_TEMP_ALE RT# 19,27

APU_RST#

APU_RST#

5

LVDS_L0P_TRAV IS9

LVDS_L0N_TRA VIS9

VGA output

from FCH

100MHz

100MHz

H_CPUPW RGD_E17,36,71,97

APU_PROCH OT#17

APU_PROCH OT#

APU_THERM TRIP#_VDDIO

APU_CLKP17

APU_CLKN17

DISP_CLKP17

DISP_CLKN17

APU_SVC_R42

APU_SVD_R42

DY

DY

R631

R631

1 2

0R2J-2-GP

0R2J-2-GP

110218 SB change to short pad

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

APU_DP_TXP0_C PU94

EDP

APU_DP_TXN 0_CPU94

DP1_TX0P_R19

DP1_TX0N_R19

DP1_TX1P_R19

DP1_TX1N_R19

DP1_TX2P_R19

DP1_TX2N_R19

DP1_TX3P_R19

DP1_TX3N_R19

SCLK31 8

SDATA318

110328 -1

H_PROCHO T#27

110328 -1

APU_VDDNB _RUN_FB_L42

APU_VDD_R UN_FB_L42

APU_VDDNB _RUN_FB_H42

APU_VDD_R UN_FB_H42

3D3V_S0

12

R670

R670

10KR2J-3-GP

10KR2J-3-GP

APU_PROCHOT#_B

1

2

3

Q612

Q612

PMBS3904-1-GP

PMBS3904-1-GP

R651

R651

0R2J-2-GP

0R2J-2-GP

1 2

DY

DY

1D5V_S3

12

R635

R635

10KR2J-3-GP

10KR2J-3-GP

APU_THERMTRIP#_VDDIO_Q

1

2

3

Q601

Q601

PMBS3904-1-GP

PMBS3904-1-GP

CPU exceeds to 125

UMA_PX

UMA_PX

UMA_PX

UMA_PX

1

2

3D3V_S0

3D3V_S5

12

0924-SA

1 2

1 2

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

UMA_PX

RN606

RN606

DY

DY

SRN0J-6-GP

SRN0J-6-GP

R632 0R0402-PADR632 0R0402- PAD

1 2

12

R669

R669

10KR2J-3-GP

10KR2J-3-GP

APU_PROCH OT#_VDDIO 42

R638

R638

10KR2J-3-GP

10KR2J-3-GP

C602 SCD1U16V2KX- 3GP

C602 SCD1U16V2KX- 3GP

C606 SCD1U16V2KX- 3GP

C606 SCD1U16V2KX- 3GP

C618 SCD1U16V2KX- 3GP

C618 SCD1U16V2KX- 3GP

1 2

C619 SCD1U16V2KX- 3GP

C619 SCD1U16V2KX- 3GP

1 2

C620 SCD1U16V2KX- 3GP

C620 SCD1U16V2KX- 3GP

1 2

C621 SCD1U16V2KX- 3GP

C621 SCD1U16V2KX- 3GP

1 2

C622 SCD1U16V2KX- 3GP

C622 SCD1U16V2KX- 3GP

1 2

C623 SCD1U16V2KX- 3GP

C623 SCD1U16V2KX- 3GP

1 2

C624 SCD1U16V2KX- 3GP

C624 SCD1U16V2KX- 3GP

1 2

C625 SCD1U16V2KX- 3GP

C625 SCD1U16V2KX- 3GP

1 2

4

3

R629 0R0402-PADR629 0R0402- PAD

1 2

R630

R630

1 2

0R0402-PAD

0R0402-PAD

APU_TDI71

APU_TDO71

APU_TCK71

APU_TMS71

APU_TRST#7 1

APU_DBRDY71

APU_DBREQ#71

R648 0R0402-PADR648 0R0402- PAD

1 2

R649 0R0402-PADR649 0R0402- PAD

1 2

H_THERMT RIP# 18,36,85

℃℃℃℃

Boot Voltage

SVC SVD

0

0

1 0

1

D D

C C

84.03904.L06

84.03904.L06

2ND = 84.03904.P11

2ND = 84.03904.P11

APU_ALERT#

1D5V_S0

1D5V_S3

1D5V_S0

B B

1D5V_S3

1D5V_S0

1D5V_S3

1D5V_S3

1D5V_S3

A A

1D5V_S3

S3 Power

0

1

1

1 2

1 2

1 2

1 2

RN611

RN611

4

3

SRN1K8J-GP

SRN1K8J-GP

RN607

RN607

3

4

SRN1K8J-GP

SRN1K8J-GP

RN601

RN601

5

6

7

8

SRN1KJ-4-G P

SRN1KJ-4-G P

RN604

RN604

8

7

6

5

SRN1KJ-4-G P

SRN1KJ-4-G P

R634

R634

1 2

300R2J-4-GP

300R2J-4-GP

R616

R616

1 2

1KR2J-1-GP

1KR2J-1-GP

0920-SA

(VCC/GND)

1D5V_S3

2

DY

DY

R666

R666

300R2J-4-GP

300R2J-4-GP

DY

DY

R665

R665

300R2J-4-GP

300R2J-4-GP

R654

R654

300R2J-4-GP

300R2J-4-GP

DY

DY

R637

R637

300R2J-4-GP

300R2J-4-GP

1

2

DY

DY

2

1

APU_SID

4

APU_SIC

3

APU_THERM TRIP#_VDDIO

2

APU_ALERT#

1

APU_TRST#

1

APU_TDI

2

APU_TMS

3

APU_TCK

4

APU_DBREQ#

5

Dr-Bios.com

4

3

2

1

12

DY

DY

12

12

12

12

C712

C712

C721

C721

C735

C735

C748

C748

C759

C759

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

APU_VDD

12

C711

C711

APU_VDD NB

C720

C720

12

DY

DY

12

C734

C734

DY

DY

12

C747

C747

12

C758

C758

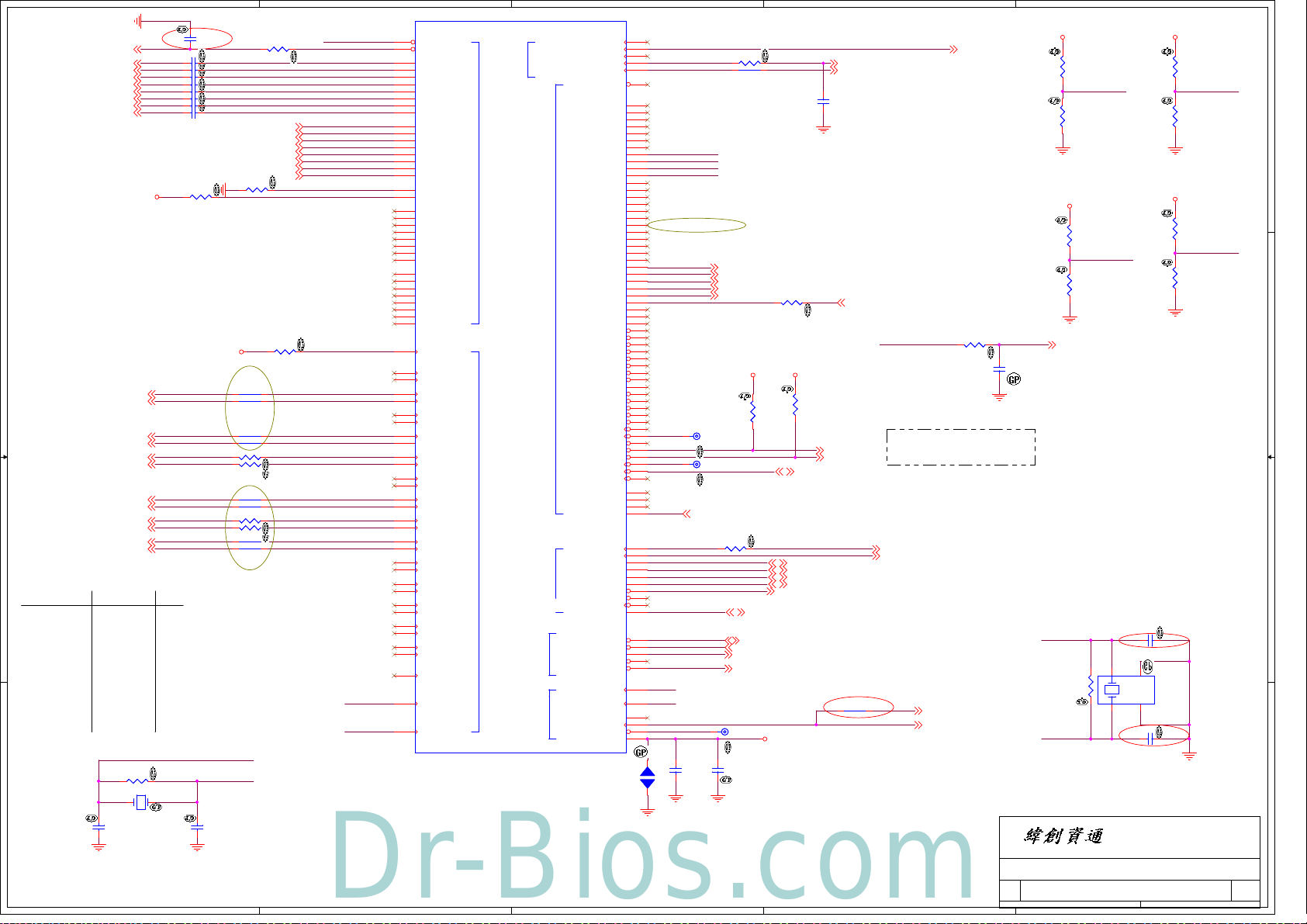

36A for VDD(35W CPU)

45A for VDD(45W CPU)

12

12

C710

C710

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

12

C709

C709

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

DY

DY

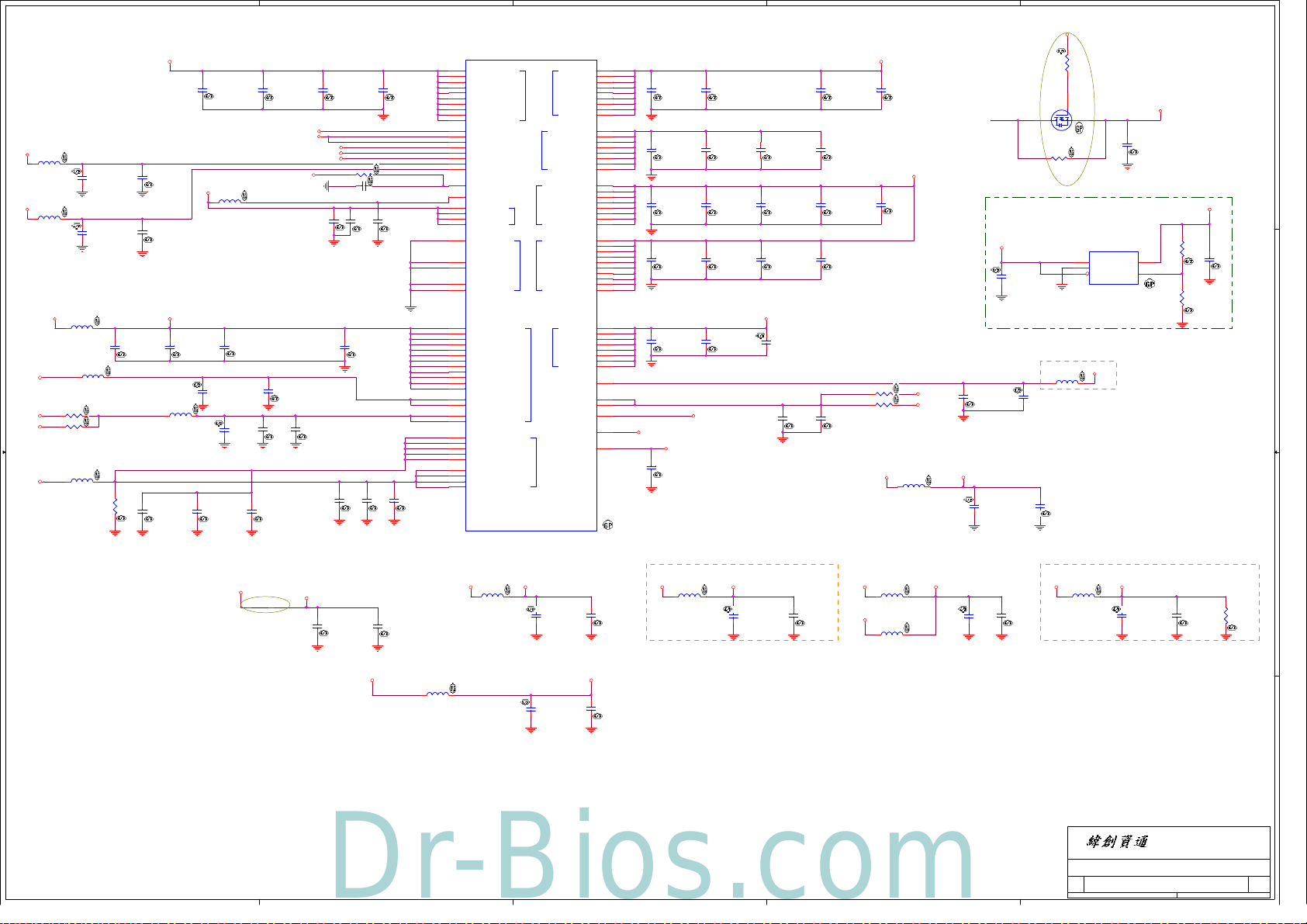

VDD:

10UF X7

180pF Cap for EMI requirment

18A for VDDNB(35W CPU)

22A for VDDNB(45W CPU)

VDDNB:

10UF X4

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

180pF Cap for EMI requirment

0.22UF X2

4A for VDDIO(35W CPU)

4.6A for VDDIO(45W CPU)

1D5V_S3

12

12

C733

C733

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

12

C731

C731

C732

C732

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

VDDIO:

10UF X2

180pF Cap for EMI requirment

3.5A for VDDP(35W/45W)

1D2V_S0

VDDP:

12

12

C745

C745

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

DY

DY

1D2V_S0

12

12

C762

C762

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

C760

C760

C761

C761

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

DY

DY

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

DY

DY

10UF X2 0.22uF X2

180pF Cap for EMI requirment

12

DY

DY

0.22UF X2

10nF X3

0.22UF X6

3A for VDDR(35W)

3.5A for VDDR(45W)

4.7uFUF X4

APU_VDD

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

APU_VDD NB

C719

C719

12

C728

C728

C705

C705

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

12

12

C704

C704

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C718

C718

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C727

C727

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

2D5V_S0

12

C703

C703

C702

DY

DY

C717

C717

C726

C726

C702

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

DY

DY

C716

C716

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

12

12

C725

C725

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

DY

DY

1D2V_S0

1D2V_S0

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

12

DY

DY

12

DY

DY

12

12

C701

C701

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

DY

DY

DY

DY

C715

C715

SC180P50V2JN-1GP

SC180P50V2JN-1GP

12

12

DY

DY

12

12

C724

C724

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

DY

DY

12

12

C707

C707

C706

C708

D D

C C

B B

C708

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C706

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D 3V5KX-1GP

SC10U6D 3V5KX-1GP

1D5V_S3

12

C729

C729

C730

C730

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

0.75A for VDDA(35W/45W)

12

12

C738

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

C738

SC3300P 50V2KX-1GP

SC3300P 50V2KX-1GP

1D5V_S3

C740

C740

12

C739

C739

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

DY

DY

M10

M18

G28

M20

M23

M26

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

AE11

AF11

L11

L19

N11

N19

P10

P18

R11

R19

J10

J11

J12

J14

J16

K10

H26

J28

K20

K23

K26

L22

L25

L28

N22

N25

N28

P20

P23

P26

C1

D3

D6

E1

F3

F6

F8

G1

H3

H6

H8

J1

K3

K6

L1

M3

M6

N1

P3

P6

R1

T3

J9

K9

APU1D

APU1D

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDP_A

VDDP_A

VDDP_A

VDDP_A

VDDR

VDDR

VDDR

VDDR

VDDA

VDDA

SAINE

SAINE

62.10055.481

62.10055.481

4 OF 6

4 OF 6

T6

VDD

T10

VDD

T18

VDD

U1

VDD

U11

VDD

U19

VDD

SAINE

SAINE

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDP_B

VDDP_B

VDDP_B

VDDP_B

VDDR

VDDR

VDDR

VDDR

V3

V6

V10

V18

W1

W11

W13

W15

W17

W19

Y3

Y6

Y10

Y12

Y14

Y16

Y18

Y20

AA1

AB3

AB6

AC1

AD3

AD6

AE1

K11

K12

K13

K14

K16

K17

K18

L18

R22

R25

R28

T20

T23

T26

U22

U25

U28

V20

V23

V26

W22

W25

W28

Y24

Y26

AA28

A3

A4

B3

B4

A5

A6

B5

B6

C714

C714

C723

C723

C737

C737

C751

C751

C767

C767

12

C713

C713

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C722

C722

12

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C736

C736

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C750

C750

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C766

C766

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

12

12

12

C742

C742

C743

C743

C744

C744

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

SCD22U10V2KX-1GP

A A

0624

5

12

C741

C741

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

SC180P50V2JN-1GP

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet

APU_Power(4/5)

APU_Power(4/5)

APU_Power(4/5)

JE50_SB

JE50_SB

JE50_SB

Taipei Hsien 221, Taiwan, R.O.C.

7 102

7 102

7 102

1

of

SB

SB

SB

Decoupling between processor and DIMMs

across VDDIO and VSS Split

4

VDDR:

4.7UF X2 0.22uF X2

180pF Cap for EMI requirment

3

2

5

Dr-Bios.com

4

3

2

1

D D

C C

B B

A13

A15

A17

A19

A21

A23

A25

C10

C14

C16

C18

C20

C22

C24

C26

C28

D13

D15

D17

D19

D21

D23

D25

D27

E10

E12

F11

F14

F16

F18

F20

F22

F24

F26

F28

G13

G15

G17

G19

G21

G23

G25

K19

M11

M19

N10

N18

P11

P19

R10

R18

APU1E

APU1E

A7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B7

VSS

C4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E4

VSS

VSS

VSS

F9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G4

VSS

G8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J4

VSS

J8

VSS

J18

VSS

J20

VSS

J22

VSS

J24

VSS

VSS

L4

VSS

L7

VSS

L10

VSS

M9

VSS

VSS

VSS

N4

VSS

N7

VSS

VSS

VSS

P9

VSS

VSS

VSS

R4

VSS

R7

VSS

VSS

VSS

T9

VSS

SAINE

SAINE

5 OF 6

5 OF 6

SAINE

SAINE

62.10055.481

62.10055.481

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T11

T19

U4

U7

U10

U18

V9

V11

V19

W4

W7

W10

W12

W14

W16

W18

Y9

Y22

AA4

AA7

AB9

AB13

AB15

AB17

AB19

AB21

AB23

AB25

AB27

AC4

AC7

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AC26

AC28

AD9

AD11

AE4

AE7

AE13

AE15

AE17

AE19

AE21

AE23

AE25

AE27

AF3

AF6

AF9

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AH5

AH8

AH13

AH15

AH17

AH19

AH21

AH23

AH25

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Friday, April 01, 2011

Friday, April 01, 2011

Friday, April 01, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

APU_VSS(5/5)

APU_VSS(5/5)

APU_VSS(5/5)

JE50_SB

JE50_SB

JE50_SB

Taipei Hsien 221, Taiwan, R.O.C.

8 102

8 102

8 102

1

SB

SB

SB

2

Dr-Bios.com

PS8615_VDD12

12

12

C947

C947

C946

C946

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD01U16V2KX- 3GP

DY

DY

SCD01U16V2KX- 3GP

UMA_PX_LVDS

UMA_PX_LVDS

12

DP_HPD0_C6,49

PS8615_PD#

SC1U6D3V2KX- GP

SC1U6D3V2KX- GP

4

APU_BLPWM _TRAVIS6,27

12

C937

C937

SCD1U10V2KX- 5GP

SCD1U10V2KX- 5GP

UMA_PX_LVDS

UMA_PX_LVDS

PS8615_VDDIO

R909

R909

10KR2J-3-GP

10KR2J-3-GP

C945

C945

PWMI: 0~100KHz,

0~100% duty cycle

PS8615_VDDRX

PS8615_RST#

PS8615_PD#

PS8615_I2C_CFG

12

UMA_PX_LVDS

UMA_PX_LVDS

12

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX_LVDS

R918

R918

1 2

0R2J-2-GP

0R2J-2-GP

1

2

3

4

5

6

7

8

9

10

11

12

PS8615_SW_OU T

PS8615_VDD12

SCD01U16V2KX- 3GP

SCD01U16V2KX- 3GP

UMA_PX_LVDS

UMA_PX_LVDS

APU_BLPWM _TRAVIS_R

U901

U901

DAUXN

DAUXP

GND

DRX0P

DRX0N

VDDRX

RST#

PD#

HPD

I2C_CFG

VDDIOX

VDDIOX

12

C941

C941

49

48

47

46

GND

NC#48

NC#47

71.08612.A03

71.08612.A03

UMA_PX_LVDS

UMA_PX_LVDS

GNDX

SW_OUT

15

14

13

12

45

44

43

42

41

TA0P

TB0P

TA0N

TB0N

TC0N

VDDIO

ENPVCC/I2C_ADDR

CSDA/MSDA

RLV_SSC

RLV_CFG

GPIO0

TESTMODE

VDD12

20

19

18

17

16

C940

C940

SCD1U10V2KX- 5GP

SCD1U10V2KX- 5GP

DY

DY

40

39

38

37

TC0P

PWMI

TCK0P

TCK0N

DDC_SDA

DDC_SCL

GND

RLV_AMP

REXT

CSCL/MSCL

PS8612QFN48GT R-A0-GP

PS8612QFN48GT R-A0-GP

24

23

22

21

PS8615_RLV_AMP

PS8615_REXT

CSCL/MSCL

CSDA/MSDA

PS8615_RLV_SSC

PS8615_RLV_CFG

PS8615_RLV_LNK

PS8615_VDDIO

TD0N

TD0P

NC#34

NC#33

VDDIO

NC#31

PWMO

ENBLT

VDD12

5

R922

R922

0R2J-2-GP

0R2J-2-GP

PS8612_RST#27

PS8615_VDDIO

110216 SB Bom change By edwin

3D3V_S0

D D

12

C932

C932

DY

DY

SC1U6D3V2KX- GP

SC1U6D3V2KX- GP

3D3V_S0

12

C933

C933

DY

DY

SC1U6D3V2KX- GP

SC1U6D3V2KX- GP

PS8615_SW_OU T PS8615_VDD12

68.4R750.20C

68.4R750.20C

2nd = 68.4R71D.10E

2nd = 68.4R71D.10E

C C

UMA_PX_LVDS

UMA_PX_LVDS

L902

L902

1 2

GBK160808T-601Y-GP

GBK160808T-601Y-GP

68.00248.011

68.00248.011

2nd = 68.00217.241

2nd = 68.00217.241

UMA_PX_LVDS

UMA_PX_LVDS

L906

L906

1 2

GBK160808T-601Y-GP

GBK160808T-601Y-GP

68.00248.011

68.00248.011

2nd = 68.00217.241

2nd = 68.00217.241

UMA_PX_LVDS

UMA_PX_LVDS

L905

L905

1 2

IND-4D7UH- 192-GP

IND-4D7UH- 192-GP

UMA_PX_LVDS

UMA_PX_LVDS

PS8615_VDDIO

12

PS8615_VDDIOX

12

SC4D7U6D3V 3KX-GP

SC4D7U6D3V 3KX-GP

12

C942

C942

SC1U6D3V2KX- GP

SC1U6D3V2KX- GP

UMA_PX_LVDS

UMA_PX_LVDS

C944

C944

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX_LVDS

UMA_PX_LVDS

1 2

GBK160808T-601Y-GP

GBK160808T-601Y-GP

68.00248.011

68.00248.011

2nd = 68.00217.241

2nd = 68.00217.241

C934

C934

SC4D7U6D3V 3KX-GP

SC4D7U6D3V 3KX-GP

1 2

UMA_PX_LVDS

UMA_PX_LVDS

R908

R908

1 2

10KR2J-3-GP

10KR2J-3-GP

UMA_PX_LVDS

UMA_PX_LVDS

PS8615_VDDRX

L904

L904

12

C936

C936

SC1U6D3V2KX- GP

SC1U6D3V2KX- GP

DY

DY

UMA_PX_LVDS

UMA_PX_LVDS

PS8615_RST#

12

C943

C943

SC2D2U6D3V 2MX-GP

SC2D2U6D3V 2MX-GP

SCD01U16V2KX- 3GP

SCD01U16V2KX- 3GP

DY

DY

LVDS_CHN_T RAVIS6

LVDS_CHP_T RAVIS6

C938

C938

LVDS_L0P_TRAV IS6

LVDS_L0N_TRA VIS6

PS8615_VDDIOX

12

C939

C939

SCD1U10V2KX- 5GP

SCD1U10V2KX- 5GP

UMA_PX_LVDS

UMA_PX_LVDS

36

35

34

33

32

31

LVDS_VDD_EN _R

30

L_BKLT_CTRL_R

29

L_BKLT_EN_R

28

27

26

25

1

3

LVDSA_DATA0# 4 9,94

LVDSA_DATA0 49,94

LVDSA_DATA1# 4 9,94

LVDSA_DATA1 49,94

LVDSA_DATA2# 4 9,94

LVDSA_DATA2 49,94

LVDSA_CLK# 49 ,94

LVDSA_CLK 49,94

PS8615_VDDIO

UMA_PX_LVDS

UMA_PX_LVDS

12

C935

C935

SCD1U10V2KX- 5GP

SCD1U10V2KX- 5GP

PH 4.7K 3D3V_S0_TRAVIS on page:94

R902: LVDS output swing control

4.99K for default swing, change the value for swing adjust

UMA_PX_LVDS

UMA_PX_LVDS

R906 4K99R2F-L-GP

R906 4K99R2F-L-GP

1 2

R907 4K99R2F-L-GP

R907 4K99R2F-L-GP

1 2

UMA_PX_LVDS

UMA_PX_LVDS

TP901TP901

3D3V_S0

Single Link LVDS

110317 -1

LVDS_VDD_EN _R 6 ,10

L_BKLT_CTRL_R 6 ,10

L_BKLT_EN_R 6,10

R9190R2J-2-GP

R9190R2J-2-GP

1 2

R9200R2J-2-GP

R9200R2J-2-GP

1 2

R9210R2J-2-GP

R9210R2J-2-GP

1 2

LVDS_DDC_D ATA_R 94

LVDS_DDC_C LK_R 94

Single Link LVDS

110324 -1

DY

DY

DY

DY

DY

DY

LVDS_VDD_EN 10,27,49,94

L_BKLT_CTRL 10,49,94

L_BKLT_EN 10,27,49,94

1

101123

UMA_PX_LVDS

UMA_PX_LVDS

PS8615_I2C_CFG

R915

R915

12

4K7R2J-2-GP

4K7R2J-2-GP

I2C_CFG: Initial code loading selection, internal pull-down ~80K

L: Hardware self configuration

M: No initial code loading, external I2C control is expected

H: Load initial code from external EEPROM through MSCL/MSDA

DY

DY

PS8615_RLV_SSC

R916

R916

12

4K7R2J-2-GP

4K7R2J-2-GP

RLV_SSC: LVDS SSC selection, internal pull-down ~80K

L: SSC off

M: +/- 0.5% central spreading

B B

H: +/- 1% central spreading

DY

DY

PS8615_RLV_CFG

R917

R917

12

4K7R2J-2-GP

4K7R2J-2-GP

RLV_CFG: LVDS color depth and data mapping selection,

internal pull-down ~80K

L: 8-bit LVDS, VESA mapping

M: 8-bit LVDS, JEIDA mapping

H: 6-bit LVDS, both VESA and JEIDA mapping

A A

5

R910

R910

4K7R2J-2-GP

4K7R2J-2-GP

R911

R911

4K7R2J-2-GP

4K7R2J-2-GP

R912

R912

4K7R2J-2-GP

4K7R2J-2-GP

UMA_PX_LVDS

UMA_PX_LVDS

12

UMA_PX_LVDS

UMA_PX_LVDS

12

UMA_PX_LVDS

UMA_PX_LVDS

12

PS8615_VDDIO

PS8615_VDDIO

PS8615_VDDIO

default setting

L: Hardware self configuration

110221 SB Bom change By EMI

L: SSC off

H: 6-bit LVDS, both VESA and JEIDA mapping

4

4

3

RN901

RN901

SRN4K7J-8-G P

SRN4K7J-8-G P

UMA_PX_LVDS

UMA_PX_LVDS

2

1

CSCL/MSCL

CSDA/MSDA

3

Q901

Q901

6

1

5

2

UMA_PX_LVDS

UMA_PX_LVDS

3 4

2N7002KDW -GP

2N7002KDW -GP

84.2N702.A3F

84.2N702.A3F

2nd = 84.DM601.03F

2nd = 84.DM601.03F

SML1_CLK 6,27,85

SML1_DATA 6,27,85

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

Size D ocument Numbe r Rev

Size D ocument Numbe r Rev

Size D ocument Numbe r Rev

A2

A2

A2

Friday, Apri l 01, 2011

Friday, Apri l 01, 2011

Friday, Apri l 01, 2011

Date: Sheet o f

Date: Sheet o f

2

Date: Sheet

TRAVIS

TRAVIS

TRAVIS

JE50_SB

JE50_SB

JE50_SB

1

Taipei Hsie n 221, Taiwan, R.O.C.

9 102

9 102

9 102

SB

SB

SB

of

3

Dr-Bios.com

LCD_CTR L_U

12

C1007

C1007

SCD47U1 0V2KX-GP

SCD47U1 0V2KX-GP

UMA_PX

UMA_PX

U1005

U1005

1

NC#1

2

A

3

GND

NC7SV17 P5X-GP

NC7SV17 P5X-GP

73.7SV17.00H

73.7SV17.00H

UMA_PX

UMA_PX

D

G

5

VCC

4

Y

R1013

R1013

10KR2J-3 -GP

10KR2J-3 -GP

1 2

UMA_PX

UMA_PX

Q1007

Q1007

2N7002K -2-GP

2N7002K -2-GP

84.2N702.J31

84.2N702.J31

2ND = 84.2N702.031

2ND = 84.2N702.031

UMA_PX

UMA_PX

S

U1003

U1003

1

VCC

OE

2

A

3

UMA_PX

UMA_PX

GND

74AHC1G 126GW-GP

74AHC1G 126GW-GP

73.1G126.0AH

73.1G126.0AH

LCD_CTR L_OE

U1004

U1004

1

VCC

OE

2

A

3

UMA_PX

UMA_PX

GND

74AHC1G 126GW-GP

74AHC1G 126GW-GP

73.1G126.0AH

73.1G126.0AH

3D3V_S0

LVDS_VD D_EN_Y

3D3V_S0

3D3V_S0

5

4

Y

3D3V_S0

5

4

Y

R1019

R1019

0R2J-2-GP

0R2J-2-GP

UMA_PX

UMA_PX

D1007

D1007

CH751H-4 0-1-GP

CH751H-4 0-1-GP

UMA_PX

UMA_PX

R1016

R1016

100KR2F -L1-GP

100KR2F -L1-GP

1 2

UMA_PX

UMA_PX

SCD47U1 0V2KX-GP

SCD47U1 0V2KX-GP

UMA_PX

UMA_PX

1 2

LVDS_CT RL_B

LCD_CTR L_D

12

C1006

C1006

SCD47U1 0V2KX-GP

SCD47U1 0V2KX-GP

UMA_PX

UMA_PX

4

AK

UMA_PX

UMA_PX

C1009

C1009

D1005

D1005

CH751H-4 0-1-GP

CH751H-4 0-1-GP

AK

L_BKLT_ EN_A

12

U1001

U1001

UMA_PX

UMA_PX

1

VCC

A

2

B

3

1

2

3

Y

GND

NC7SZ08 M5X-NL-GP

NC7SZ08 M5X-NL-GP

73.7SZ08.AAG

73.7SZ08.AAG

U1002

U1002

VCC

A

UMA_PX

UMA_PX

B

Y

GND

NC7SZ08 M5X-NL-GP

NC7SZ08 M5X-NL-GP

73.7SZ08.AAG

73.7SZ08.AAG

A K

UMA_PX

UMA_PX

1 2

UMA_PX

UMA_PX

R1012

R1012

0R0402-P AD

0R0402-P AD

1 2

R1017

R1017

0R0402-P AD

0R0402-P AD

1 2

110323-1

5

4

5

4

D1006

D1006

CH751H-4 0-1-GP

CH751H-4 0-1-GP

R1015

R1015

220KR2F -GP

220KR2F -GP

U1006

U1006

1

NC#1

2

A

3

GND

NC7SV17 P5X-GP

NC7SV17 P5X-GP

73.7SV17.00H

73.7SV17.00H

UMA_PX

UMA_PX

3D3V_S0

3D3V_S0

LCD_CTR L_R

LVDS_VD D_EN_A

12

C1008

C1008

SCD47U1 0V2KX-GP

SCD47U1 0V2KX-GP

5

VCC

4

Y

LVDS_SE Q_CTRLLVDS_SE Q_CTRL_R

LVDS_CT RL_OE

D1004

D1004

CH751H-4 0-1-GP

CH751H-4 0-1-GP

A K

UMA_PX

UMA_PX

R1006

R1006

100KR2J -1-GP

100KR2J -1-GP

1 2

UMA_PX

UMA_PX

UMA_PX

UMA_PX

3D3V_S0

LCD_CTR L_Q

5

D D

L_BKLT_ EN_R6,9

C C

L_BKLT_ CTRL_R6,9

L_BKLT_ EN_R6,9

B B

LVDS_VD D_EN_R6,9

R1001

R1001

470R2J-2 -GP

470R2J-2 -GP

1 2

UMA_PX

UMA_PX

SCD1U50 V3KX-GP

SCD1U50 V3KX-GP

UMA_PX

UMA_PX

R1018

R1018

0R2J-2-GP

0R2J-2-GP

1 2

UMA_PX