Acer Aspire 5515, eMachines E620 Schematics

A

1 1

B

C

D

E

2 2

Compal Confidential

KAW60 Schematics Document

AMD AM2 / RS690MC / SB600

2008 / 08 / 08 FOR Pre-MP

3 3

4 4

Rev:1.0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/05/09 2006/03/08

2005/05/09 2006/03/08

2005/05/09 2006/03/08

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

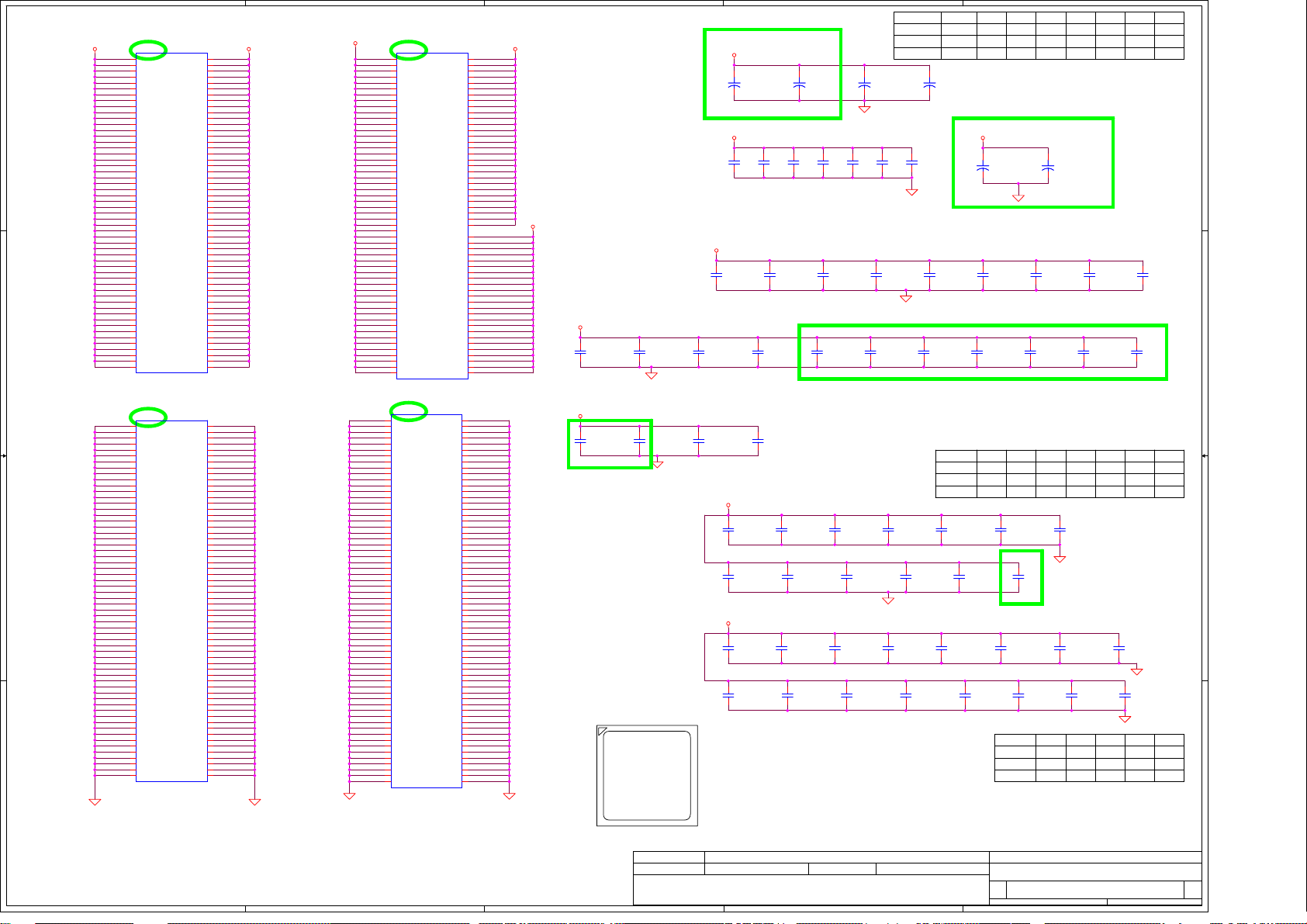

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

Date: Sheet

Date: Sheet

D

Date: Sheet

150Friday, August 08, 2008

150Friday, August 08, 2008

150Friday, August 08, 2008

of

of

E

of

2.0

2.0

2.0

5

4

3

2

1

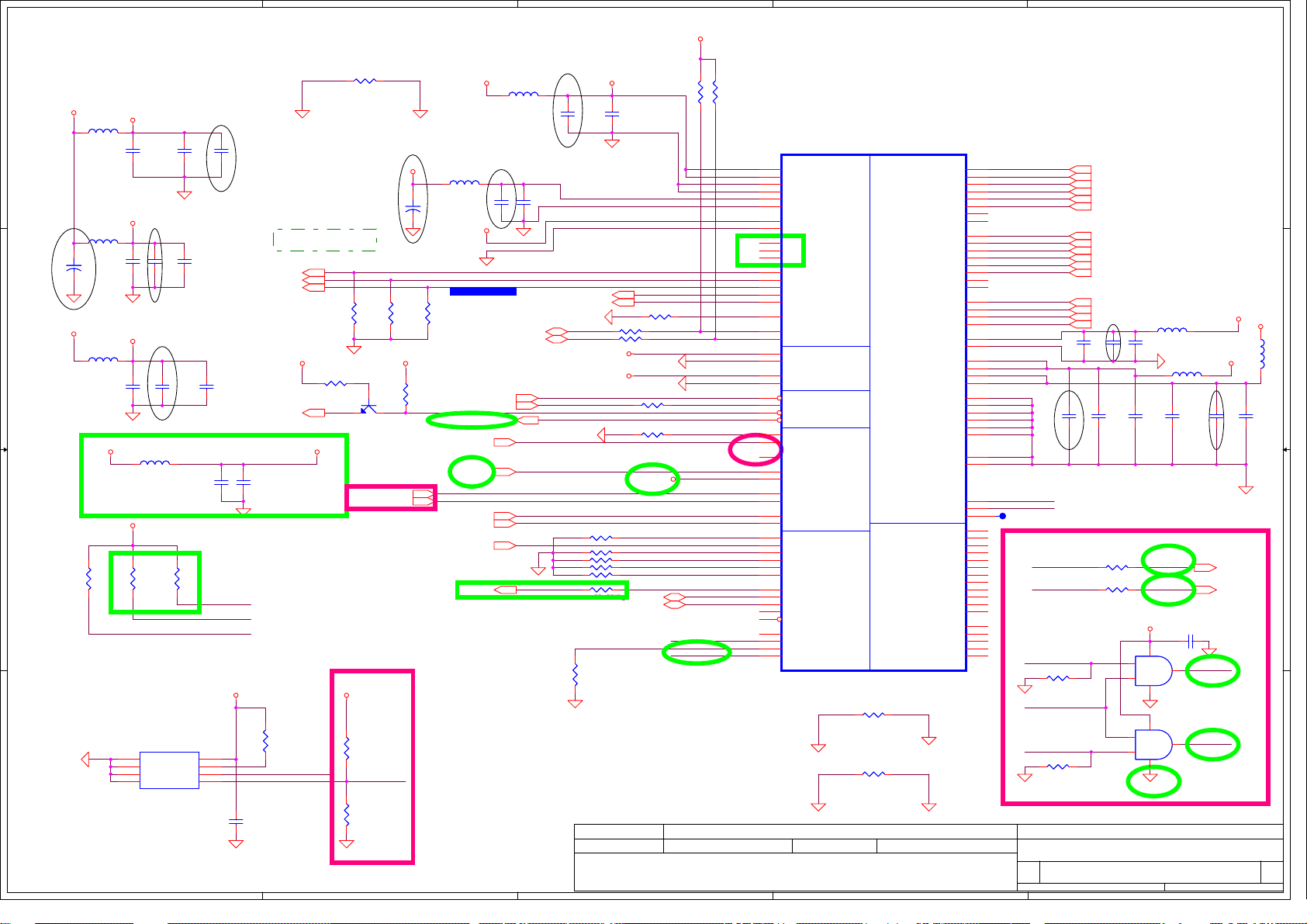

Compal confidential

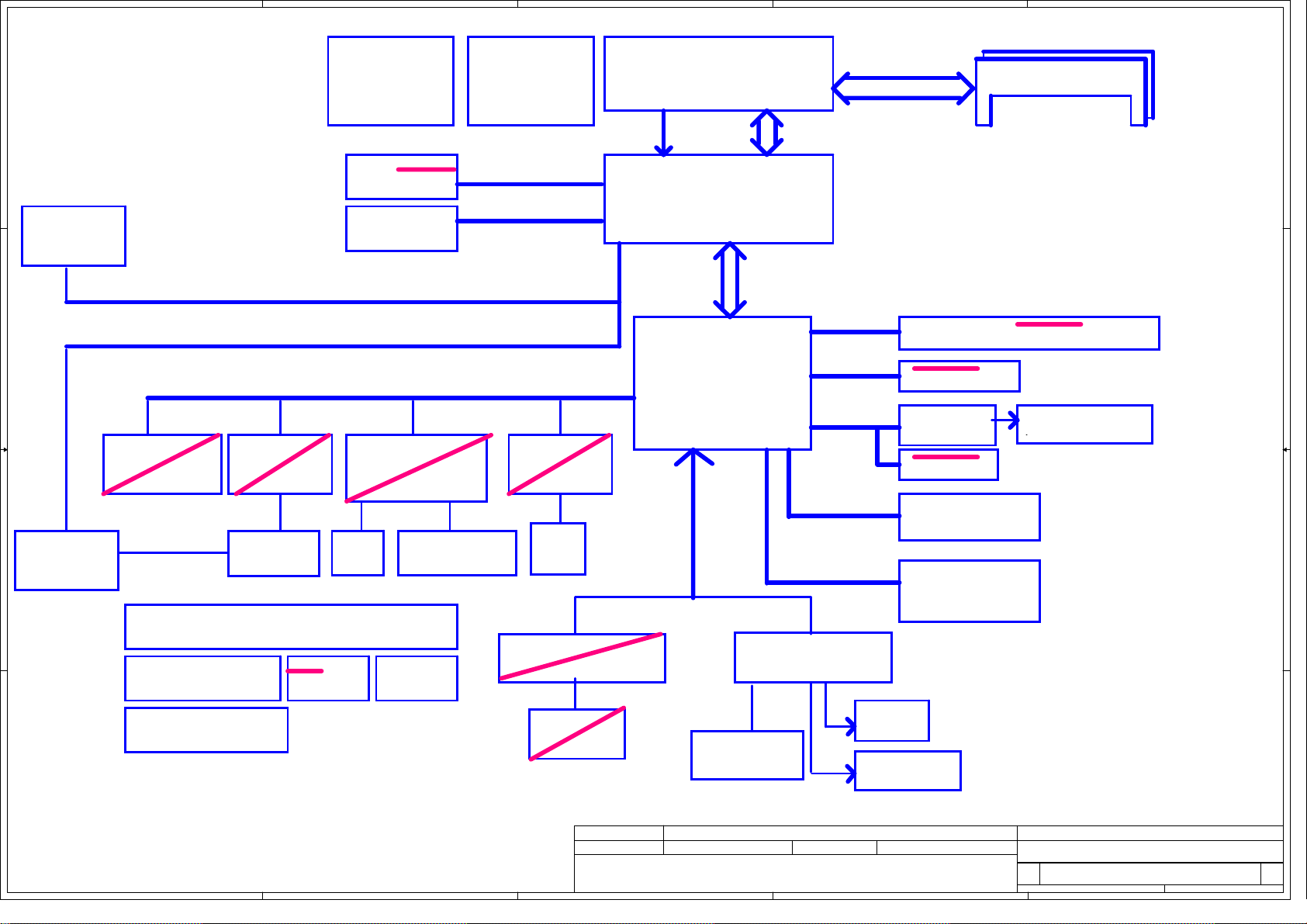

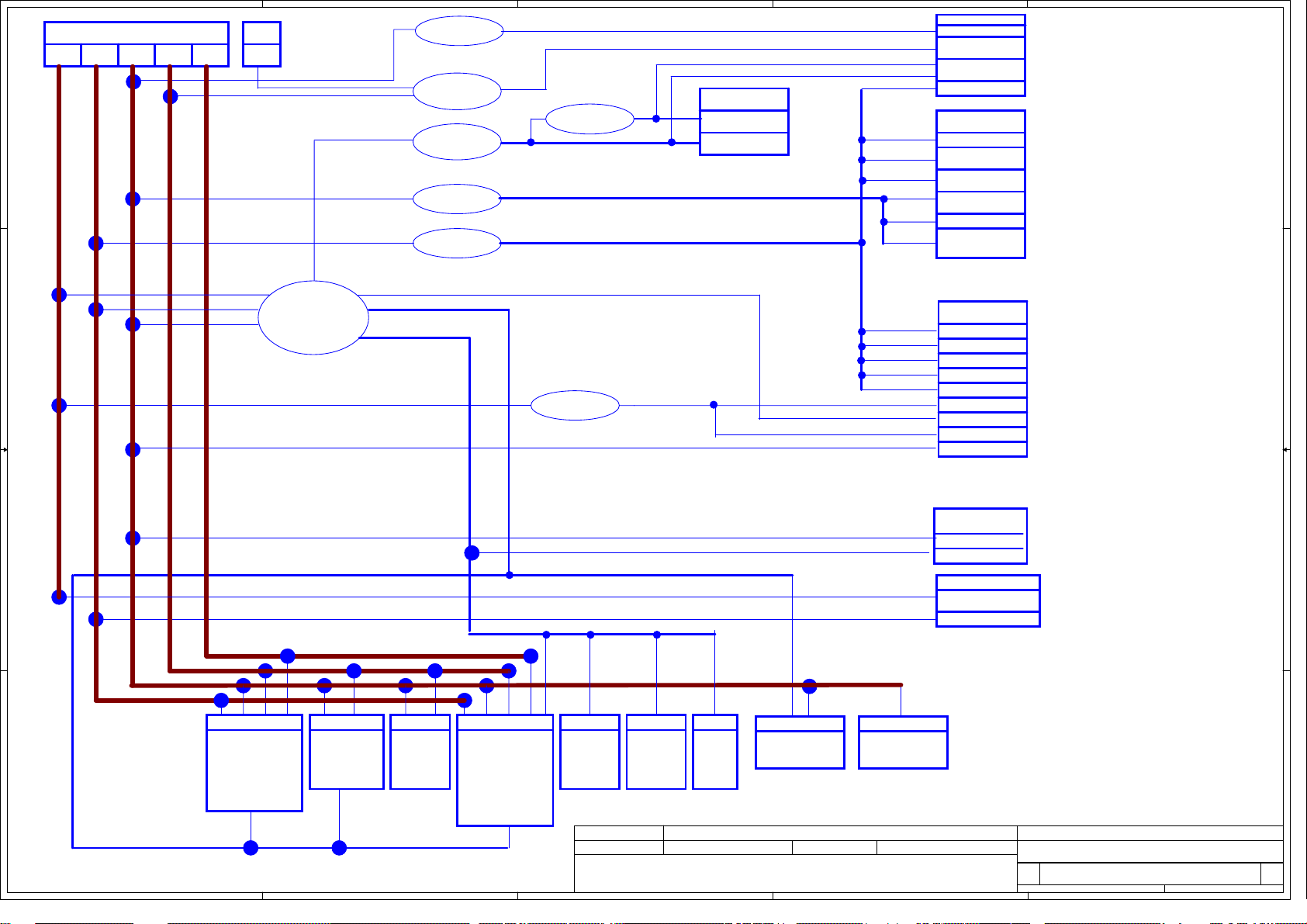

Project Code: KAW60

File Name : LA-4661P

D D

Thermal Sensor

ADM1032ARM

page 8 page 17

Clock Generator

ICS951462

CRT & TV-OUT

page 24

Mini card

page 31

LCD CONN

page 25

PCIE X1

AMD AM2 CPU

940P PGA

H_A#(3..31)

ATI-RS690MC

465 BGA

page 12,13,14,15,16

page 6,7,8,9

H_D#(0..63)

HT 16x16 1000MHZ

A-Link Express

4 x PCIE

DDRII DDRII-SO-DIMM X2

533/667

page 10,11

Dual Channel

SIG1 : 35mm x 35mm x (2.20mm+2.11mm) 638pin

AM2 : 40mm x 40mm x (4.56mm+2.11mm) 940pin

RS485 : 21mm x 21mm (19.2mm x 19.2mm) x2.33mm 465pin

RS690 : 21mm x 21mm (19.2mm x 19.2mm) x2.33mm 465pin

SB460 : 27mm x 27mm (21.6mm x 21.6mm) x2.33mm 549pin

SB600 : 23mm x 23mm (21.6mm x 21.6mm) x2.33mm 549pin

C C

PCIE X1

ATI-SB600

PCI BUS

549 BGA

USB 2.0

USB 2.0

HD Audio

Mini PCI Socket

Mini card RTL8110SCL

page 31

Realtek

RTL8100CL

page 26

ENE Controller

CB714

page 32

1394 Controller

VT6311S

page 35

page 18,19,20,21,22

SATA

Realtek

B B

RTL8102EL

page 26

RJ45 CONN

page 27

Slot 0

page 33

6in1 CardReader

Slot

page 33

1394

Conn.

page 35

LPC BUS

SATA

USB conn x 2 / New card / Camera

page 34

BT Conn

page 38

HDA Codec

ALC268

page 39

MDC Conn.

page 41

AMP & Audio Jack

APA2057

page 31

page 40

HDD Conn.

page 23

CDROM Conn.

page 23

Power On/Off CKT / LID switch / Power OK CKT

page 37

DC/DC Interface CKT.

page 41

CIR/LED

page 38

RTC CKT.

page 18

Power Circuit DC/DC

page 42~48

A A

SMsC LPC47N207

page 36

FIR module

page 36

ENE KB926

Touch Pad

CONN.

page 29

page 28

Int. KBD

page 29

SPI BIOS

page 30

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/03/08 2006/03/08

2005/03/08 2006/03/08

2005/03/08 2006/03/08

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

Date: Sheet

Date: Sheet

2

Date: Sheet

250Sunday, July 20, 2008

250Sunday, July 20, 2008

250Sunday, July 20, 2008

1

2.0

2.0

2.0

of

of

of

5

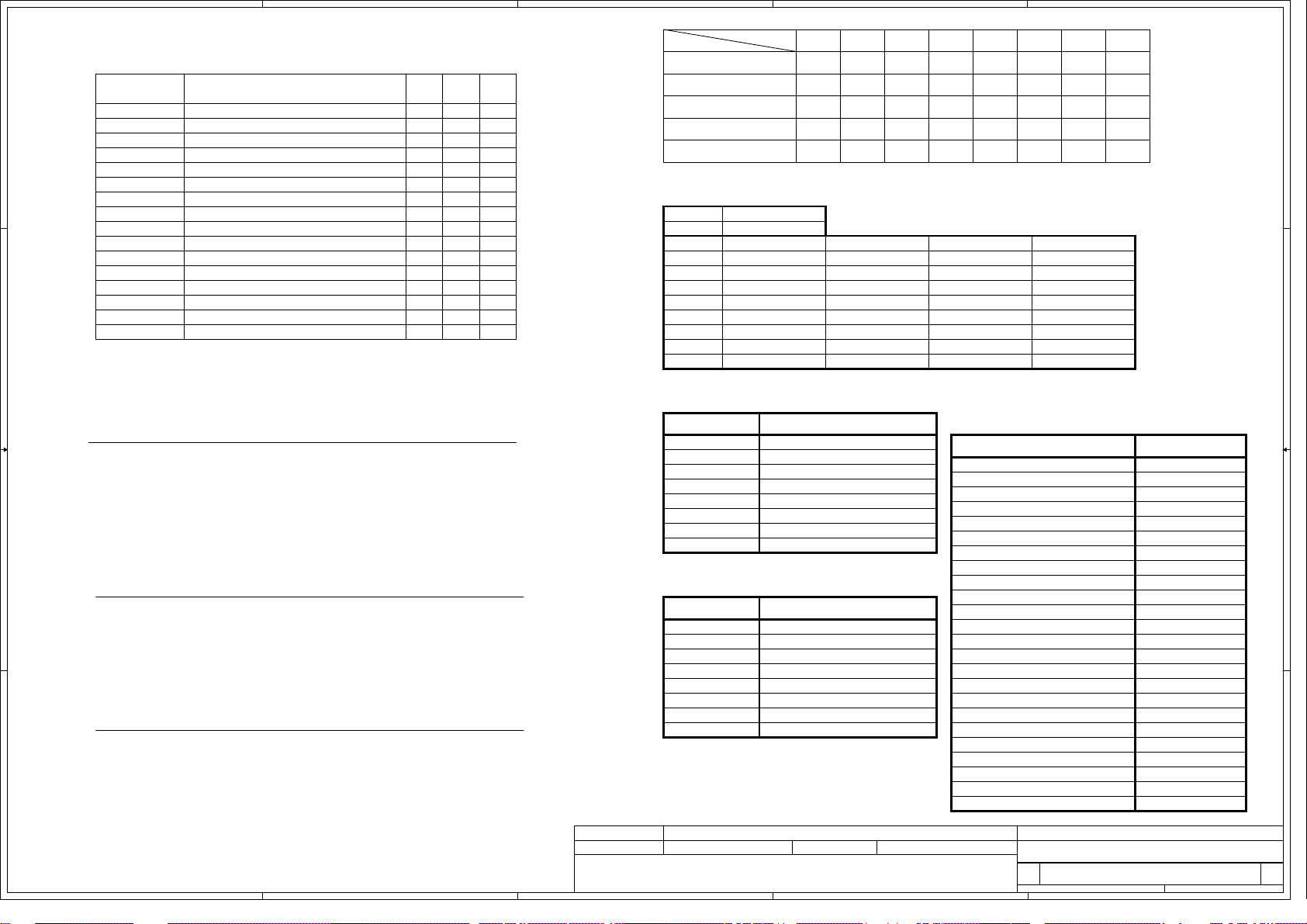

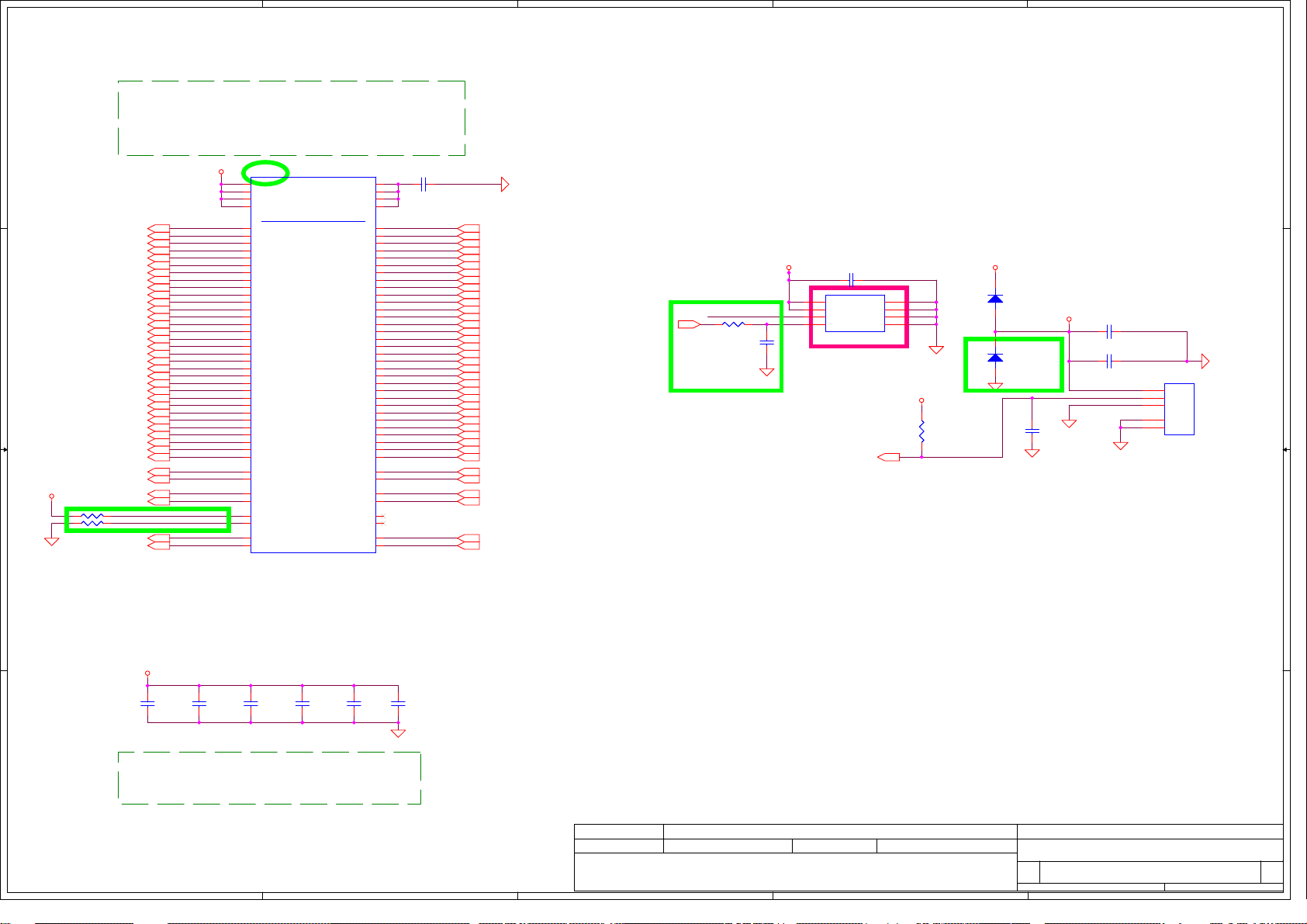

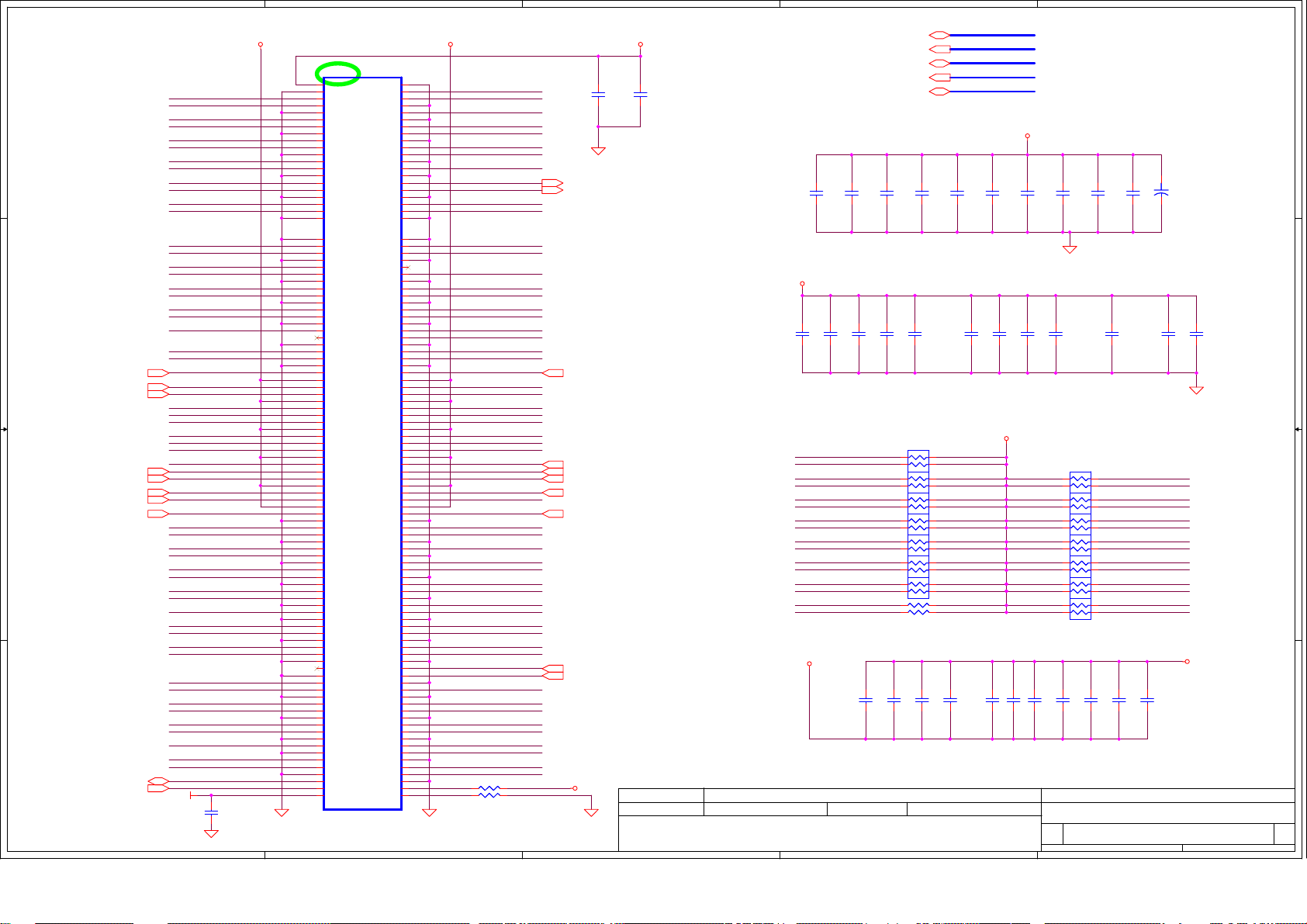

Voltage Rails

Power Plane

D D

C C

VIN

B+

+CPU_CORE

+0.9V

+1.2V_HT

+1.5VS

+1.8VALW

+1.8V

+1.8VS

+2.5VS

+3VALW

+3VS

+5VALW

+5VS

+VSB

+RTCVCC

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

0.9V switched power rail for DDR terminator

1.2V switched power rail

1.5V switched power rail

1.8V always on power rail

1.8V power rail for DDR

1.8V switched power rail

2.5V switched power rail

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

RTC power

4

S1 S3 S5

N/A N/A N/A

ON

ON ON

ON

ON

ON ON ON*

ON

ON

ON

ON

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFF OFF

OFF OFF

OFF

ON

OFF

OFF

OFF

OFF

ON*

ON

OFF

OFF

ON

ON*

OFF

OFF

ON*ON

ON

ON

3

SIGNAL

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

SLP_S1# SLP_S3#

SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

HIGH

LOW

S4 (Suspend to Disk)

S5 (Soft OFF)

LOW LOW LOW LOW

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2

LOWLOWLOW

ON

ON

HIGHHIGHHIGH

HIGH

HIGH

V typ

AD_BID

ON

ON

ON

ON

OFF

ON

OFF

ON

V

0 V 0 V

0.503 V

0.819 V

1.185 V 1.264 V

2.200 V

3.300 V

ON ON

ON

OFF

OFF

OFF

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

1

LOW

OFF

OFF

OFF

max

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

Device

B B

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

IDSEL#

REQ#/GNT#

Interrupts

EC SM Bus2 address

Address Address

1010 000X b

1011 000X b

Device

ADM1032

1001 100X b0001 011X b

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

SKU ID Table

SKU ID

0

1

2

PCB Revision

SKU

BTO Option Table

BTO Item BOM Structure

WITH AMD HDT Debug port HDT@

WITH USBx2 USB2@

USBX1 WITH CHOKE

USBX1 WITHOUT CHOKE

USBx2 WITH CHOKE

USBx2 WITHOUT CHOKE

SPI ROM under SB600 SB600SPI@

EMI@

WOEMI@

USB2EMI@

USB2WOEMI@

MDC@WITH MODEM

3

4

5

SB600 SM Bus address

Device

Clock Generator

A A

(ICS951462)

DDR DIMM0

DDR DIMM2

5

Address

1101 001Xb

1001 000Xb

1001 010Xb

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

6

7

Compal Secret Data

Compal Secret Data

2005/03/08 2006/03/08

2005/03/08 2006/03/08

2005/03/08 2006/03/08

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

HCW51 LA-3121P

HCW51 LA-3121P

HCW51 LA-3121P

Date: Sheet

Date: Sheet

Date: Sheet

350Thursday, July 24, 2008

350Thursday, July 24, 2008

350Thursday, July 24, 2008

of

of

1

of

2.0

2.0

2.0

5

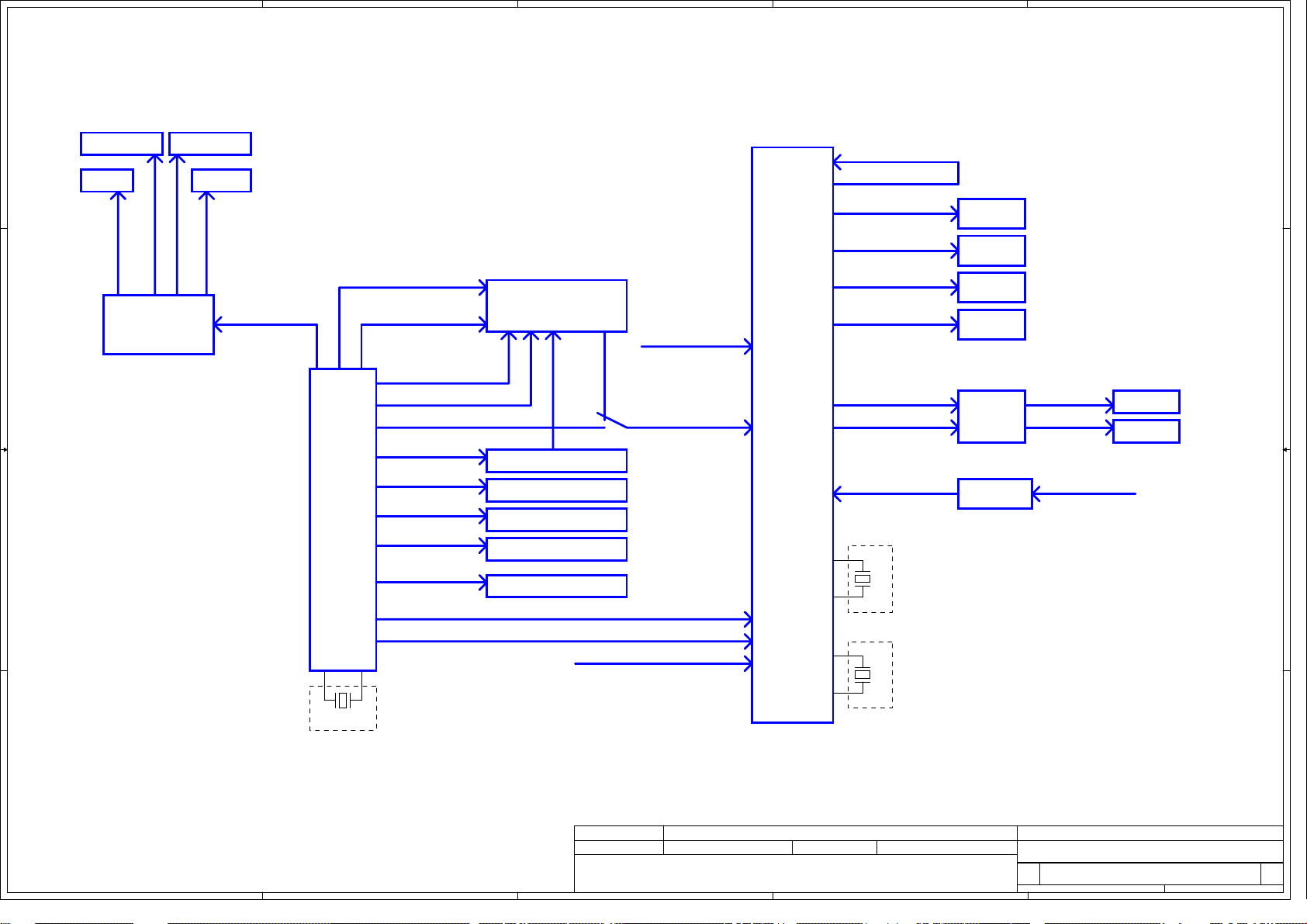

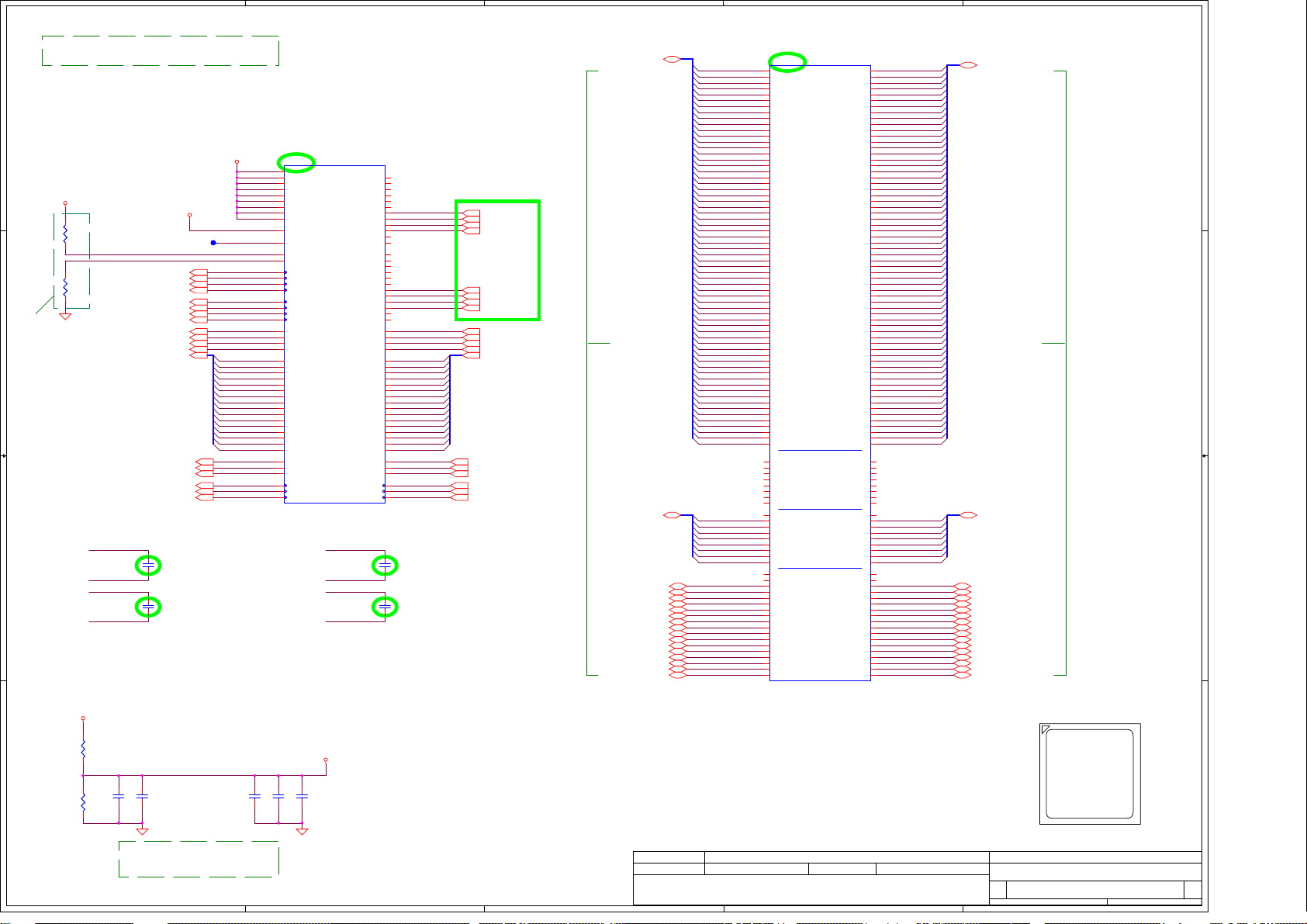

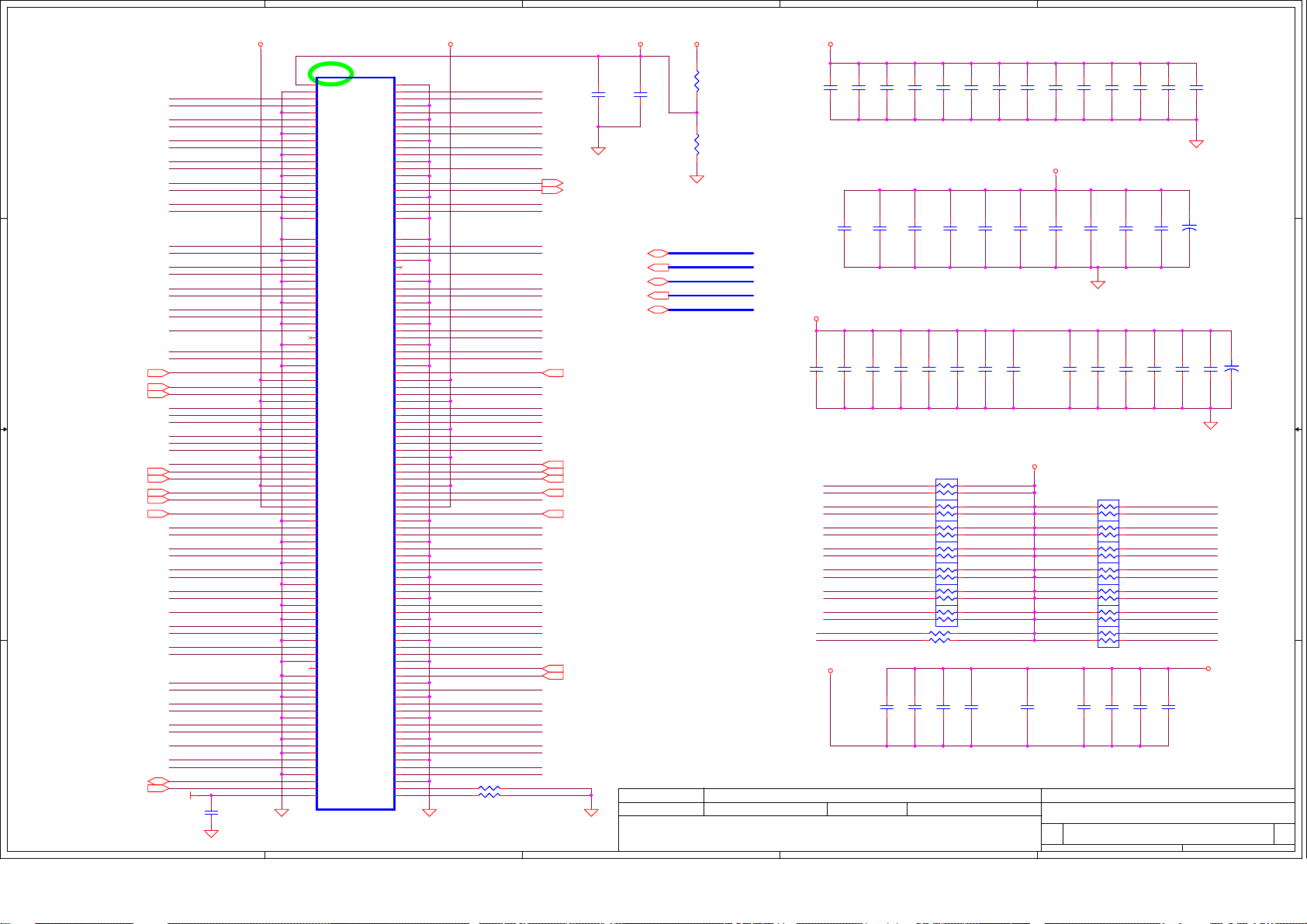

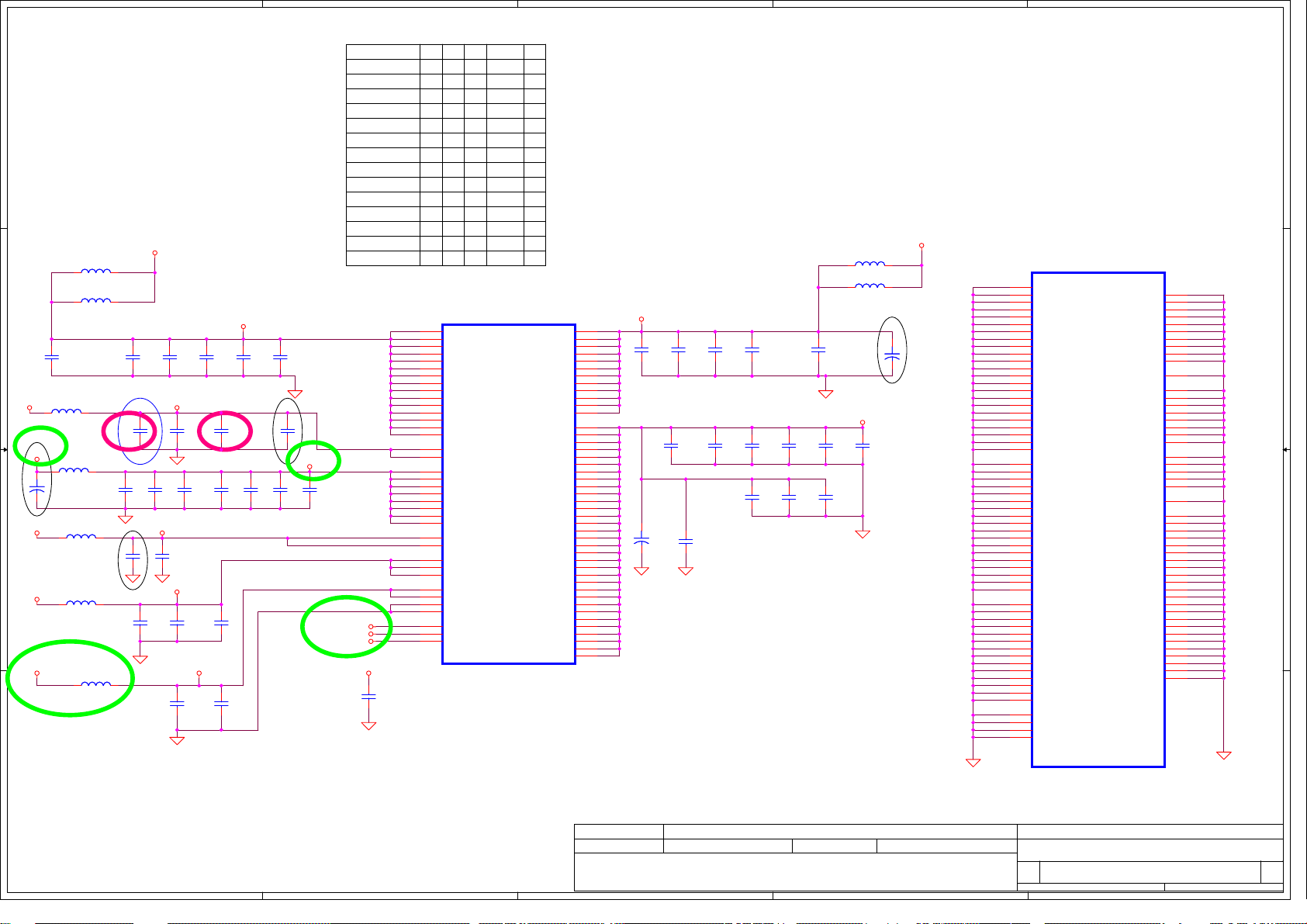

D D

DIMM3 DIMM4

DIMM1 DIMM2

3 PAIR MEM CLK

3 PAIR MEM CLK

M2 CPU

C C

M2 SOCKET

3 PAIR MEM CLK

3 PAIR MEM CLK

1 PAIR CPU CLK

200MHZ

EXTERNAL

CLK GEN.

B B

4

HTREFCLK

66MHZ

NB-OSC

14.318MHZ

NB PCIE CLK

100MHZ

SB PCIE CLK

100MHZ

SB-OSCIN

14.318MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

ATI NB -RS690

TVCLKIN

PCIE GFX SLOT - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GPP SLOT 2 - 1 LANE

PCIE GBE

PCIE STAT

SB-OSCIN

3

14.318MHZ OSC INPUT

14.318MHZ

48MHZ OSC INPUT FOR USB

(OPTION)

SB-OSCIN

14.318MHZ

PCIE CLK

100MHZ

USB CLK

48MHZ

(OPTION)

ATI SB

SB600

PCI CLKFB

PCI CLK

33MHZ

AZ_BITCLK

2

PCI CLK0

33MHZ

PCI CLK1

33MHZ

PCI CLK1

33MHZ

PCI CLK6

33MHZ

PCI CLK5

33MHZ

SIO_CLK

24/48MHZ

25M Hz32.768K Hz

PCI SLOT0

PCI SLOT1

PCI SLOT2

LPC BIOS

SUPER IO

IT8712F

AC97 CODEC

AZALIA

KB_CLK

KEYBOARD

MS_CLK

24.576MHZ OSC INPUT

1

MOUSE

14.31818MHz

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/10/10 2006/10/10

2005/10/10 2006/10/10

2005/10/10 2006/10/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

Date: Sheet

Date: Sheet

2

Date: Sheet

450Tuesday, June 17, 2008

450Tuesday, June 17, 2008

450Tuesday, June 17, 2008

1

2.0

2.0

2.0

of

of

of

5

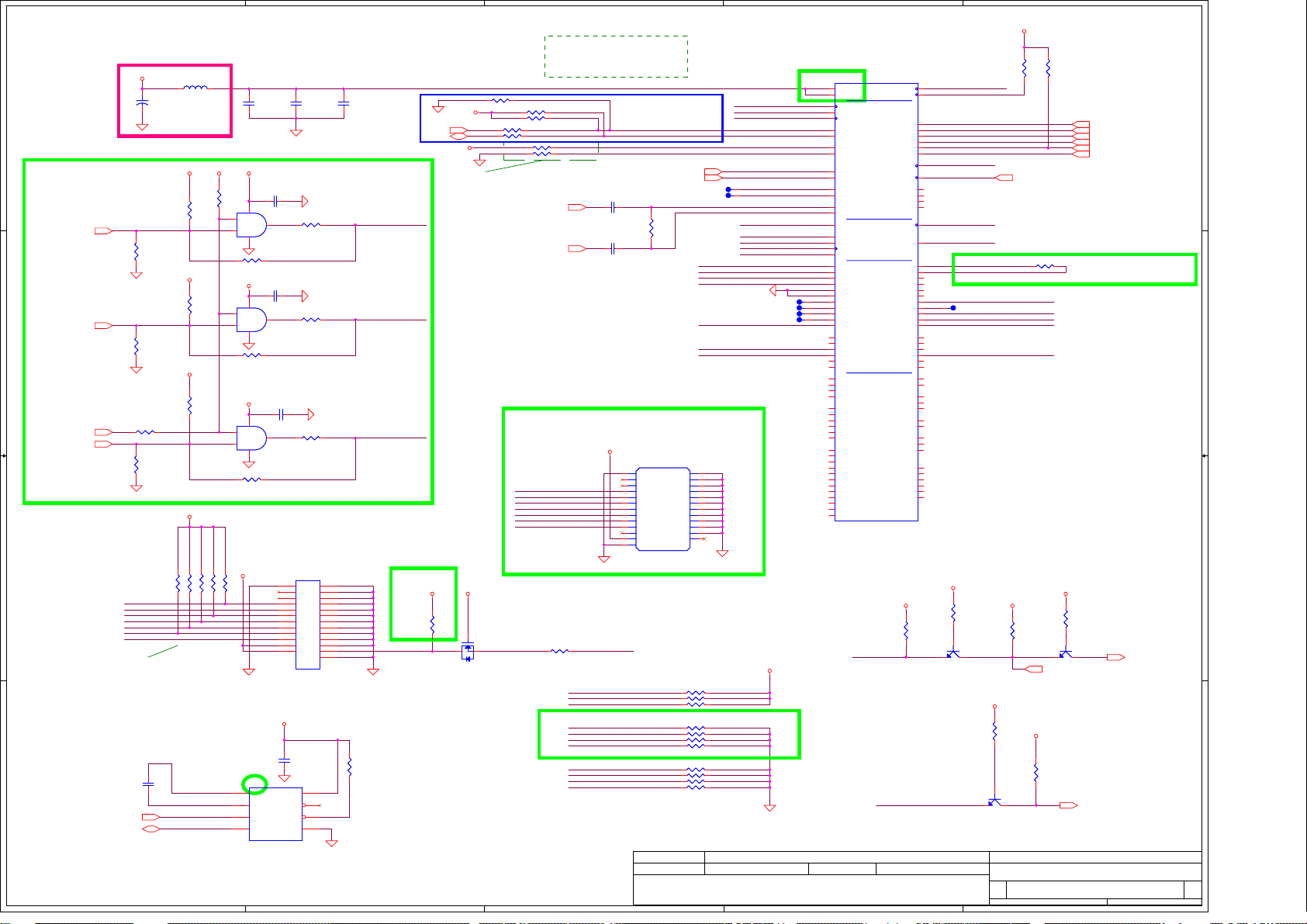

ATX P/S WITH 1A STBY CURRENT

-12V

3.3V

+/-5%

12V

+/-5%

+/-5%

5V

5VSB

+/-5%

+/-5%

D D

CPU

PW

12V

+/-5%

+5VDUAL_MEM (S0,S5)

4

2.5V SHUNT

REGULATOR

VRM SW

REGULATOR

1.8V VDD SW

REGULATOR

1.8V LINEAR

REGULATOR

VCC 1.2V SW

REGULATOR

0.9V VTT_DDR

REGULATOR

+1.8V(S0, S1)

VCC_NB (S0, S1)

3

CPU_VDDA_RUN (S0, S1)

CPU_VDD_RUN (S0, S1)

CPU_VTT_SUS (S0,S1,S3)

CPU_VDDIO_SUS(S0,S1,S3)

2

M2

VDDA 2.5V 0.1A

VDDCORE

0.8-1.55V 80A

DDRII MEM I/F VTT

0.125A, VDD 3A

VLDT 1.2V 0.5A

1

DDRII DIMMs

VTT_DDR 2A

VDD MEM 12A

RS690

VDDHT 1.2V 0.5A

PCI-E CORE&VCO

& I/O &PLL 2.25A

NB CORE VDDC

1.2V 5A

DAC 200mA LVDS

1.8V 300mA

PLL & DAC-Q 0.1A

PCI-E PLL

+3.3VSB (S0, S1, S3, S4, S5)

+3.3VSB REGULATOR

ACPI CONTROLLER

C C

+3.3VDUAL (S0, S1, S3, S4, S5)

+5VDUAL (S0, S1, S3, S4, S5)

1.2V STB LDO

REGULATOR

+1.2VSB (S5)

SB600

X4 PCI-E 0.8A

ATA I/O 0.2A

ATA PLL 0.01A

PCI-E PVDD 80mA

SB CORE 0.6A

1.2V S5 PW 0.22A

3.3V S5 PW 0.01A

USB CORE I/O 0.2A

3.3V I/O 0.45A

AZALIA CODEC

3.3V CORE 0.3A

B B

5V ANALOG 0.1A

SUPER I/O

+5V SD 0.01A

+5V 0.1A

3.0A3.0A

5.5A

CNR CONNECTOR

5V

3.3V

12V

3.3Vaux

-12V

0.5A

0.1A

X16 PCIEX1 PCIE per

3.3V

12V

PCI Slot (per slot)

5.0A

5V

3.3V

A A

12V

3.3Vaux

-12V

7.6A

0.5A

0.375A

0.1A

3.3V

12V

3.3Vaux

5VDual

+3.3VDUAL (S0, S1, S3)

5

4

1.0A

1.0A

0.5A

1.0A

0.1A

0.5A

USB X4 FR

VDD

5VDual

2.0A

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

USB X6 RL 2XPS/2

Issued Date

Issued Date

Issued Date

VDD

5VDual

2.0A

3

GBE

5VDual

1.0A

2005/10/10 2006/10/10

2005/10/10 2006/10/10

2005/10/10 2006/10/10

3.3V 0.5A (S0, S1)

3.3V 0.1A (S3)

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SATA

3.3V 0.3A (S0, S1)

2

Title

Title

Title

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

Date: Sheet

Date: Sheet

Date: Sheet

550Tuesday, June 17, 2008

550Tuesday, June 17, 2008

550Tuesday, June 17, 2008

of

of

1

of

2.0

2.0

2.0

5

4

3

2

1

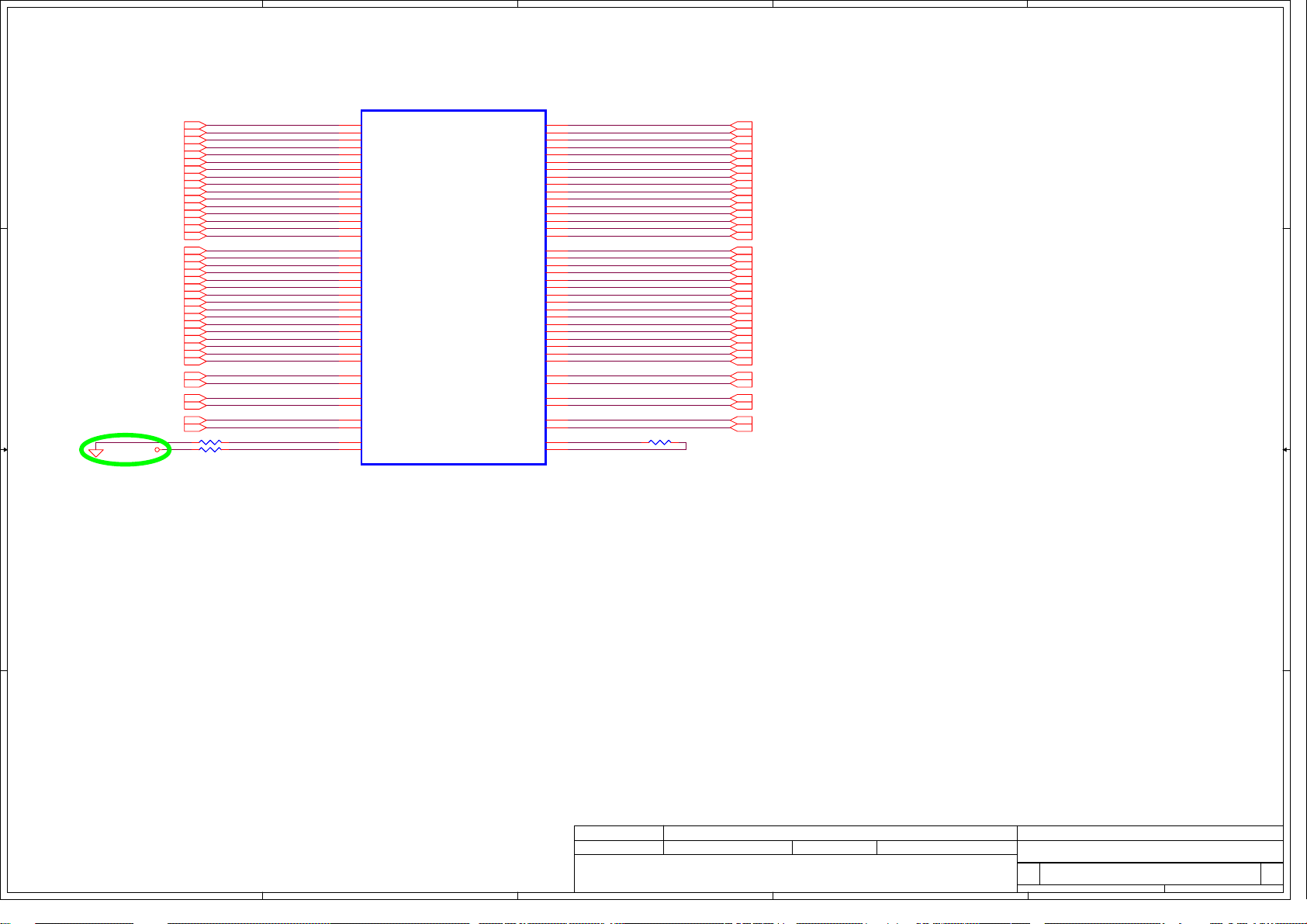

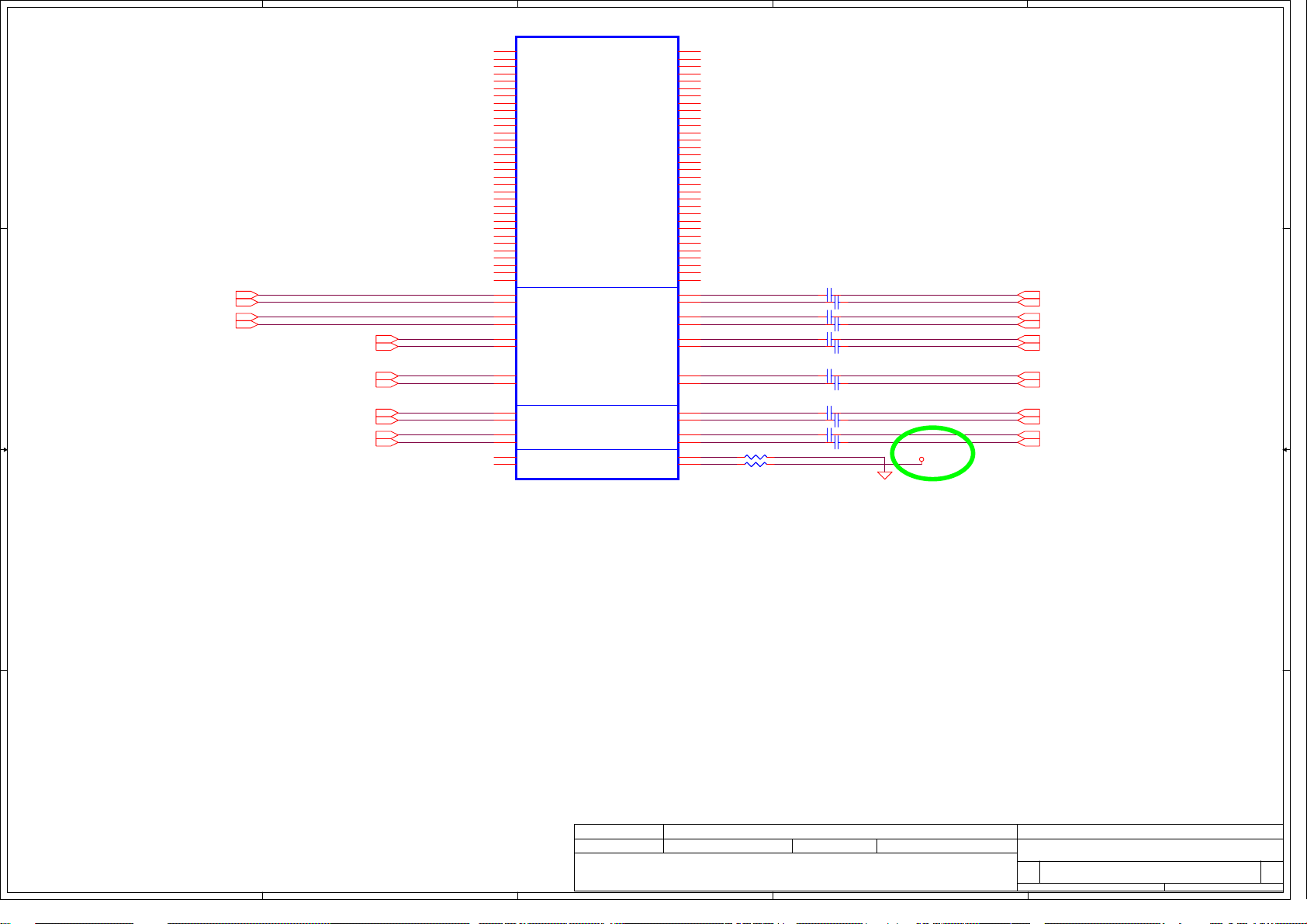

PROCESSOR HYPERTRANSPORT INTERFACE

D D

H_CADIP1512

H_CADIN1512

H_CADIP1412

H_CADIN1412

H_CADIP1312

H_CADIN1312

H_CADIP1212

H_CADIN1212

H_CADIP1112

H_CADIN1112

H_CADIP1012

H_CADIN1012

H_CADIP912

H_CADIN912

H_CADIP812

C C

+1.2V_HT

B B

H_CADIN812

H_CADIP712

H_CADIN712

H_CADIP612

H_CADIN612

H_CADIP512

H_CADIN512

H_CADIP412

H_CADIN412

H_CADIP312

H_CADIN312

H_CADIP212

H_CADIN212

H_CADIP112

H_CADIN112

H_CADIP012

H_CADIN012

H_CLKIP112

H_CLKIN112

H_CLKIP012

1 2

1 2

H_CLKIN012

H_CTLIP012

H_CTLIN012

R38 51_0402_1%R38 51_0402_1%

R37 51_0402_1%R37 51_0402_1%

Trace length limit (Don't care)

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+1.2V_HT

JCPU1A

H_CADIP15

H_CADIN15

H_CADIP14

H_CADIN14

H_CADIP13

H_CADIN13

H_CADIP12

H_CADIN12

H_CADIP11

H_CADIN11

H_CADIP10

H_CADIN10

H_CADIP9

H_CADIN9

H_CADIP8

H_CADIN8

H_CADIP7

H_CADIN7

H_CADIP6

H_CADIN6

H_CADIP5

H_CADIN5

H_CADIP4

H_CADIN4

H_CADIP3

H_CADIN3

H_CADIP2

H_CADIN2

H_CADIP1

H_CADIN1

H_CADIP0

H_CADIN0

H_CLKIP1

H_CLKIN1

H_CLKIP0

H_CLKIN0

H_CTLIP1

H_CTLIN1

H_CTLIP0

H_CTLIN0

JCPU1A

AJ4

VLDT_06

AJ3

VLDT_05

AJ2

VLDT_02

AJ1

VLDT_01

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

HT LINK

HT LINK

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

VLDT_08

VLDT_07

VLDT_04

VLDT_03

H6

H5

H2

H1

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

1 2

H_CADOP15

H_CADON15

H_CADOP14

H_CADON14

H_CADOP13

H_CADON13

H_CADOP12

H_CADON12

H_CADOP11

H_CADON11

H_CADOP10

H_CADON10

H_CADOP9

H_CADON9

H_CADOP8

H_CADON8

H_CADOP7

H_CADON7

H_CADOP6

H_CADON6

H_CADOP5

H_CADON5

H_CADOP4

H_CADON4

H_CADOP3

H_CADON3

H_CADOP2

H_CADON2

H_CADOP1

H_CADON1

H_CADOP0

H_CADON0

H_CLKOP1

H_CLKON1

H_CLKOP0

H_CLKON0

H_CTLOP0

H_CTLON0

C455

C455

4.7U_0805_10V4Z

4.7U_0805_10V4Z

SOC127MM48X51-948! 6090022000; JCPU1

TEMP SYMBOL

H_CADOP15 12

H_CADON15 12

H_CADOP14 12

H_CADON14 12

H_CADOP13 12

H_CADON13 12

H_CADOP12 12

H_CADON12 12

H_CADOP11 12

H_CADON11 12

H_CADOP10 12

H_CADON10 12

H_CADOP9 12

H_CADON9 12

H_CADOP8 12

H_CADON8 12

H_CADOP7 12

H_CADON7 12

H_CADOP6 12

H_CADON6 12

H_CADOP5 12

H_CADON5 12

H_CADOP4 12

H_CADON4 12

H_CADOP3 12

H_CADON3 12

H_CADOP2 12

H_CADON2 12

H_CADOP1 12

H_CADON1 12

H_CADOP0 12

H_CADON0 12

H_CLKOP1 12

H_CLKON1 12

H_CLKOP0 12

H_CLKON0 12

H_CTLOP0 12

H_CTLON0 12

FAN Conn

+5VS

+VCC_FAN1

EN_DFAN128

1 2

R733 0_0402_5%R733 0_0402_5%

EN_DFAN1_R

1

2

C760

C760

0.01U_0402_16V7K@

0.01U_0402_16V7K@

C47 10U_0805_10V4ZC47 10U_0805_10V4Z

1 2

U1

U1

1

VEN

2

VIN

3

VO

4

VSET

APL5605_SOP8L

APL5605_SOP8L

FAN_SPEED128

GND

GND

GND

GND

8

7

6

5

PVT

+3VS

12

R34

R34

10K_0402_5%

10K_0402_5%

+5VS

12

D3

D3

CH355PT_SOD323

CH355PT_SOD323

12

D4

D4

BAS16_SOT23-3

BAS16_SOT23-3

FAN1

PVT

1

C92

C92

1000P_0402_50V7K

1000P_0402_50V7K

2

W=40mils

+VCC_FAN1

1 2

C83 10U_0805_10V4ZC83 10U_0805_10V4Z

1 2

C90 1000P_0402_50V7KC90 1000P_0402_50V7K

JP20

JP20

1

1

2

2

3

3

4

GND

5

GND

ACES_85205-03001

ACES_85205-03001

CONN@

CONN@

+1.2V_HT

1

C164

C164

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

LAYOUT: Place bypass cap on topside of board

A A

5

1

C156

C156

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

C158

C158

0.22U_0402_10V4Z

0.22U_0402_10V4Z

1

2

1

C163

C163

2

0.22U_0402_10V4Z

0.22U_0402_10V4Z

C145

C145

180P_0402_50V8J

180P_0402_50V8J

1

2

1

2

4

C152

C152

180P_0402_50V8J

180P_0402_50V8J

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2005/10/11 2006/10/11

2005/10/11 2006/10/11

2005/10/11 2006/10/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

AMD CPU HT I/F

AMD CPU HT I/F

AMD CPU HT I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

of

of

650Friday, August 08, 2008

650Friday, August 08, 2008

650Friday, August 08, 2008

2.0

2.0

2.0

A

B

C

D

E

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

4 4

+0.9V

+1.8V

12

R13

R13

39.2_0402_1%~D

39.2_0402_1%~D

R22

R22

12

39.2_0402_1%~D

39.2_0402_1%~D

PLACE THEM CLOSE TO

CPU WITHIN 1"

3 3

2 2

PLACE CLOSE TO PROCESSOR

WITHIN 1.2 INCH

+1.8V

12

R33

R33

1K_0402_1%

1K_0402_1%

1 1

R23

R23

1K_0402_1%

1K_0402_1%

12

1000P_0402_50V7K

1000P_0402_50V7K

DDR_A_CLK2

DDR_A_CLK#2

DDR_A_CLK1

DDR_A_CLK#1

1

2

DDR_CS3_DIMMA#10

DDR_CS2_DIMMA#10

DDR_CS1_DIMMA#10

DDR_CS0_DIMMA#10

DDR_CS3_DIMMB#11

DDR_CS2_DIMMB#11

DDR_CS1_DIMMB#11

DDR_CS0_DIMMB#11

DDR_CKE1_DIMMB11

DDR_CKE0_DIMMB11

DDR_CKE1_DIMMA10

DDR_CKE0_DIMMA10

DDR_A_MA[15..0]10

C32

C32

10:8:10:8:10

DDR_A_BS#210

DDR_A_BS#110

DDR_A_BS#010

DDR_A_RAS#10

DDR_A_CAS#10

DDR_A_WE#10

1

C66

C66

1.5P_0402_50V8C

1.5P_0402_50V8C

2

1

C132

C132

1.5P_0402_50V8C

1.5P_0402_50V8C

2

1

C33

C33

1000P_0402_50V7K

1000P_0402_50V7K

2

+0.9VREF_CPU

TP3PAD TP3PAD

M_ZN

M_ZP

CPU_VREF_REF

0.1U_0402_16V4Z

0.1U_0402_16V4Z

VTT_SENSE

DDR_CS3_DIMMA#

DDR_CS2_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMA#

DDR_CS3_DIMMB#

DDR_CS2_DIMMB#

DDR_CS1_DIMMB#

DDR_CS0_DIMMB#

DDR_CKE1_DIMMB

DDR_CKE0_DIMMB

DDR_CKE1_DIMMA

DDR_CKE0_DIMMA

DDR_A_MA15

DDR_A_MA14

DDR_A_MA13

DDR_A_MA12

DDR_A_MA11

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA7

DDR_A_MA6

DDR_A_MA5

DDR_A_MA4

DDR_A_MA3

DDR_A_MA2

DDR_A_MA1

DDR_A_MA0

DDR_A_BS#2

DDR_A_BS#1

DDR_A_BS#0

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

C34

C34

D12

C12

B12

A12

AK12

AJ12

AH12

AG12

AL12

F12

E12

AH11

AJ11

AD27

AA25

AC25

AA24

AE29

AB31

AE30

AC31

M31

M29

L27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

N25

Y27

AA27

AA26

AB25

AB27

1

1

2

2

1000P_0402_50V7K

1000P_0402_50V7K

JCPU1B

JCPU1B

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA1_CS_L1

MA1_CS_L0

MA0_CS_L1

MA0_CS_L0

MB1_CS_L1

MB1_CS_L0

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK1

DDR_B_CLK#1

PLACE CLOSE TO PROCESSOR

WITHIN 1.2 INCH

+0.9VREF_CPU

1

C28

C28

C29

C29

1U_0402_6.3V4Z

1U_0402_6.3V4Z

2

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

MA1_CLK_H2

MA1_CLK_L2

MA1_CLK_H1

MA1_CLK_L1

MA1_CLK_H0

MA1_CLK_L0

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MA0_CLK_H0

MA0_CLK_L0

MB1_CLK_H2

MB1_CLK_L2

MB1_CLK_H1

MB1_CLK_L1

MB1_CLK_H0

MB1_CLK_L0

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_CLK_H0

MB0_CLK_L0

MB1_ODT0

MB0_ODT0

MA1_ODT0

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

AE20

AE19

G20

G21

V27

W27

DDR_A_CLK2

AG21

DDR_A_CLK#2

AG20

DDR_A_CLK1

G19

DDR_A_CLK#1

H19

U27

U26

AL19

AL18

C19

D19

W29

W28

DDR_B_CLK2

AJ19

DDR_B_CLK#2

AK19

DDR_B_CLK1

A18

DDR_B_CLK#1

A19

U31

U30

DDR_B_ODT1

AD31

DDR_B_ODT0

AD29

DDR_A_ODT1

AC27

DDR_A_ODT0

AC28

DDR_B_MA15

N28

DDR_B_MA14

N29

DDR_B_MA13

AE31

DDR_B_MA12

N30

DDR_B_MA11

P29

DDR_B_MA10

AA29

DDR_B_MA9

P31

DDR_B_MA8

R29

DDR_B_MA7

R28

DDR_B_MA6

R31

DDR_B_MA5

R30

DDR_B_MA4

T31

DDR_B_MA3

T29

DDR_B_MA2

U29

DDR_B_MA1

U28

DDR_B_MA0

AA30

DDR_B_BS#2

N31

DDR_B_BS#1

AA31

DDR_B_BS#0

AA28

DDR_B_RAS#

AB29

DDR_B_CAS#

AC29

DDR_B_WE#

AC30

1

C35

C35

1.5P_0402_50V8C

1.5P_0402_50V8C

2

1

C173

C173

1.5P_0402_50V8C

1.5P_0402_50V8C

2

DDR_A_CLK2 10

DDR_A_CLK#2 10

DDR_A_CLK1 10

DDR_A_CLK#1 10

DDR_B_CLK2 11

DDR_B_CLK#2 11

DDR_B_CLK1 11

DDR_B_CLK#1 11

DDR_B_ODT1 11

DDR_B_ODT0 11

DDR_A_ODT1 10

DDR_A_ODT0 10

DDR_B_MA[15..0] 11

DDR_B_BS#2 11

DDR_B_BS#1 11

DDR_B_BS#0 11

DDR_B_RAS# 11

DDR_B_CAS# 11

DDR_B_WE# 11

DDR_B_D[63..0]11

To reverse SODIMM socket

DDR_B_DQS711

DDR_B_DQS#711

DDR_B_DQS611

DDR_B_DQS#611

DDR_B_DQS511

DDR_B_DQS#511

DDR_B_DQS411

DDR_B_DQS#411

DDR_B_DQS311

DDR_B_DQS#311

DDR_B_DQS211

DDR_B_DQS#211

DDR_B_DQS111

DDR_B_DQS#111

DDR_B_DQS011

DDR_B_DQS#011

Processor DDR2 Memory Interface

JCPU1C

DDR_B_D63

DDR_B_D62

DDR_B_D61

DDR_B_D60

DDR_B_D59

DDR_B_D58

DDR_B_D57

DDR_B_D56

DDR_B_D55

DDR_B_D54

DDR_B_D53

DDR_B_D52

DDR_B_D51

DDR_B_D50

DDR_B_D49

DDR_B_D48

DDR_B_D47

DDR_B_D46

DDR_B_D45

DDR_B_D44

DDR_B_D43

DDR_B_D42

DDR_B_D41

DDR_B_D40

DDR_B_D39

DDR_B_D38

DDR_B_D37

DDR_B_D36

DDR_B_D35

DDR_B_D34

DDR_B_D33

DDR_B_D32

DDR_B_D31

DDR_B_D30

DDR_B_D29

DDR_B_D28

DDR_B_D27

DDR_B_D26

DDR_B_D25

DDR_B_D24

DDR_B_D23

DDR_B_D22

DDR_B_D21

DDR_B_D20

DDR_B_D19

DDR_B_D18

DDR_B_D17

DDR_B_D16

DDR_B_D15

DDR_B_D14

DDR_B_D13

DDR_B_D12

DDR_B_D11

DDR_B_D10

DDR_B_D9

DDR_B_D8

DDR_B_D7

DDR_B_D6

DDR_B_D5

DDR_B_D4

DDR_B_D3

DDR_B_D2

DDR_B_D1

DDR_B_D0

DDR_B_DM7

DDR_B_DM6

DDR_B_DM5

DDR_B_DM4

DDR_B_DM3

DDR_B_DM2

DDR_B_DM1

DDR_B_DM0

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS0

DDR_B_DQS#0

JCPU1C

AH13

MB_DATA63

AL13

MB_DATA62

AL15

MB_DATA61

AJ15

MB_DATA60

AF13

MB_DATA59

AG13

MB_DATA58

AL14

MB_DATA57

AK15

MB_DATA56

AL16

MB_DATA55

AL17

MB_DATA54

AK21

MB_DATA53

AL21

MB_DATA52

AH15

MB_DATA51

AJ16

MB_DATA50

AH19

MB_DATA49

AL20

MB_DATA48

AJ22

MB_DATA47

AL22

MB_DATA46

AL24

MB_DATA45

AK25

MB_DATA44

AJ21

MB_DATA43

AH21

MB_DATA42

AH23

MB_DATA41

AJ24

MB_DATA40

AL27

MB_DATA39

AK27

MB_DATA38

AH31

MB_DATA37

AG30

MB_DATA36

AL25

MB_DATA35

AL26

MB_DATA34

AJ30

MB_DATA33

AJ31

MB_DATA32

E31

MB_DATA31

E30

MB_DATA30

B27

MB_DATA29

A27

MB_DATA28

F29

MB_DATA27

F31

MB_DATA26

A29

MB_DATA25

A28

MB_DATA24

A25

MB_DATA23

A24

MB_DATA22

C22

MB_DATA21

D21

MB_DATA20

A26

MB_DATA19

B25

MB_DATA18

B23

MB_DATA17

A22

MB_DATA16

B21

MB_DATA15

A20

MB_DATA14

C16

MB_DATA13

D15

MB_DATA12

C21

MB_DATA11

A21

MB_DATA10

A17

MB_DATA9

A16

MB_DATA8

B15

MB_DATA7

A14

MB_DATA6

E13

MB_DATA5

F13

MB_DATA4

C15

MB_DATA3

A15

MB_DATA2

A13

MB_DATA1

D13

MB_DATA0

K29

MB_CHECK7

K31

MB_CHECK6

G30

MB_CHECK5

G29

MB_CHECK4

L29

MB_CHECK3

L28

MB_CHECK2

H31

MB_CHECK1

G31

MB_CHECK0

J29

MB_DM8

AJ14

MB_DM7

AH17

MB_DM6

AJ23

MB_DM5

AK29

MB_DM4

C30

MB_DM3

A23

MB_DM2

B17

MB_DM1

B13

MB_DM0

J31

MB_DQS_H8

J30

MB_DQS_L8

AK13

MB_DQS_H7

AJ13

MB_DQS_L7

AK17

MB_DQS_H6

AJ17

MB_DQS_L6

AK23

MB_DQS_H5

AL23

MB_DQS_L5

AL28

MB_DQS_H4

AL29

MB_DQS_L4

D31

MB_DQS_H3

C31

MB_DQS_L3

C24

MB_DQS_H2

C23

MB_DQS_L2

D17

MB_DQS_H1

C17

MB_DQS_L1

C14

MB_DQS_H0

C13

MB_DQS_L0

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

DDRII: DATA

DDRII: DATA

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_DQS_H8

MA_DQS_H7

MA_DQS_H6

MA_DQS_H5

MA_DQS_H4

MA_DQS_H3

MA_DQS_H2

MA_DQS_H1

MA_DQS_H0

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM8

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_L8

MA_DQS_L7

MA_DQS_L6

MA_DQS_L5

MA_DQS_L4

MA_DQS_L3

MA_DQS_L2

MA_DQS_L1

MA_DQS_L0

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

K25

J26

G28

G27

L24

K27

H29

H27

J25

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

J28

J27

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

DDR_A_D63

DDR_A_D62

DDR_A_D61

DDR_A_D60

DDR_A_D59

DDR_A_D58

DDR_A_D57

DDR_A_D56

DDR_A_D55

DDR_A_D54

DDR_A_D53

DDR_A_D52

DDR_A_D51

DDR_A_D50

DDR_A_D49

DDR_A_D48

DDR_A_D47

DDR_A_D46

DDR_A_D45

DDR_A_D44

DDR_A_D43

DDR_A_D42

DDR_A_D41

DDR_A_D40

DDR_A_D39

DDR_A_D38

DDR_A_D37

DDR_A_D36

DDR_A_D35

DDR_A_D34

DDR_A_D33

DDR_A_D32

DDR_A_D31

DDR_A_D30

DDR_A_D29

DDR_A_D28

DDR_A_D27

DDR_A_D26

DDR_A_D25

DDR_A_D24

DDR_A_D23

DDR_A_D22

DDR_A_D21

DDR_A_D20

DDR_A_D19

DDR_A_D18

DDR_A_D17

DDR_A_D16

DDR_A_D15

DDR_A_D14

DDR_A_D13

DDR_A_D12

DDR_A_D11

DDR_A_D10

DDR_A_D9

DDR_A_D8

DDR_A_D7

DDR_A_D6

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D2

DDR_A_D1

DDR_A_D0

DDR_A_DM7

DDR_A_DM6

DDR_A_DM5

DDR_A_DM4

DDR_A_DM3

DDR_A_DM2

DDR_A_DM1

DDR_A_DM0

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_D[63..0] 10

DDR_A_DM[7..0] 10DDR_B_DM[7..0]11

DDR_A_DQS7 10

DDR_A_DQS#7 10

DDR_A_DQS6 10

DDR_A_DQS#6 10

DDR_A_DQS5 10

DDR_A_DQS#5 10

DDR_A_DQS4 10

DDR_A_DQS#4 10

DDR_A_DQS3 10

DDR_A_DQS#3 10

DDR_A_DQS2 10

DDR_A_DQS#2 10

DDR_A_DQS1 10

DDR_A_DQS#1 10

DDR_A_DQS0 10

DDR_A_DQS#0 10

To normal SODIMM socket

AF1

A1

Athlon 64 S1g1

uPGA638

Top View

A26

VDD_VREF_SUS_CPU

LAYOUT:PLACE CLOSE TO CPU

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2005/10/11 2006/10/11

2005/10/11 2006/10/11

2005/10/11 2006/10/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Title

Title

Title

AMD CPU DDRII MEMORY I/F

AMD CPU DDRII MEMORY I/F

AMD CPU DDRII MEMORY I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

Date: Sheet

Date: Sheet

Date: Sheet

E

of

of

of

750Friday, August 08, 2008

750Friday, August 08, 2008

750Friday, August 08, 2008

2.0

2.0

2.0

5

+2.5VS

FCM2012C-800_0.25ohm/600mA_0805

FCM2012C-800_0.25ohm/600mA_0805

1

+

+

150U_D2_6.3VM

150U_D2_6.3VM

2

@

D D

CPU_PWRGD18

680_0402_5%

680_0402_5%

LDT_STOP#14,18

C C

680_0402_5%

680_0402_5%

SB_PWROK18,28,37

LDT_RST#18

680_0402_5%

680_0402_5%

@

Un-stuff

R63

R63

300_0402_5% @

300_0402_5% @

12

R688

R688

R88

R88

300_0402_5% @

300_0402_5% @

12

R689

R689

R71

R71

300_0402_5% @

300_0402_5% @

@

@

1 2

R82 0_0402_5%

R82 0_0402_5%

12

R690

R690

1 2

C506

C506

+1.8VS

12

+1.8VS

12

+1.8VS

12

SB_PWROK_R

LDT_RST#

+1.8V

L4

L4

1

C189

C189

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

+1.8V+3VS

12

R64

R64

4.7K_0402_5%@

4.7K_0402_5%@

R543 0_0402_5%R543 0_0402_5%

R544 0_0402_5%R544 0_0402_5%

R545 0_0402_5%R545 0_0402_5%

2

B

1

A

1 2

2

B

1

A

1 2

2

B

1

A

1 2

+1.8V

+1.8V

5

U5

P

Y

G

NC7SZ08P5X_NL_SC70-5@U5NC7SZ08P5X_NL_SC70-5@

3

5

U8

P

Y

G

NC7SZ08P5X_NL_SC70-5@U8NC7SZ08P5X_NL_SC70-5@

3

5

U6

P

Y

G

NC7SZ08P5X_NL_SC70-5@U6NC7SZ08P5X_NL_SC70-5@

3

C147 0.1U_0402_16V4Z

C147 0.1U_0402_16V4Z

1 2

@

@

R70

R70

4

C155 0.1U_0402_16V4Z

C155 0.1U_0402_16V4Z

1 2

@

@

R79

R79

4

C282 0.1U_0402_16V4Z

C282 0.1U_0402_16V4Z

1 2

@

@

R65

R65

4

1

C187

C187

2

0.22U_0603_16V7K

0.22U_0603_16V7K

@

@

1 2

@

@

1 2

@

@

1 2

HDT Connector

12

12

12

12

B B

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

2200P_0402_50V7K

A A

2200P_0402_50V7K

EC_SMB_CK228

EC_SMB_DA228

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

C451

C451

5

HDT@

HDT@

R361 220_0402_5%

R361 220_0402_5%

1

2

EC_SMB_CK2

EC_SMB_DA2

12

+1.8V

HDT@

HDT@

HDT@

HDT@

HDT@

HDT@

HDT@

HDT@

R364 220_0402_5%

R364 220_0402_5%

R362 220_0402_5%

R362 220_0402_5%

R363 220_0402_5%

R363 220_0402_5%

R365 220_0402_5%

R365 220_0402_5%

U38

CPU_THERMDA

CPU_THERMDC

U38

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARMZ-2REEL_MSOP8

ADM1032ARMZ-2REEL_MSOP8

U4524 CLOSE CPU,

CPU_THERMDA&CPU_THERMDC PLACE

CLOSE TO PROCESSOR WITHIN 1" INCH

JP4

JP4

1

3

5

7

9

11

13

15

17

19

21

SAMTEC_ASP-68200-07

SAMTEC_ASP-68200-07

CONN@

CONN@

+3VS

1

C454

C454

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

VDD1

ALERT#

THERM#

GND

2

4

6

8

10

12

14

16

18

20

22

2423

26

1

6

4

5

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

0_0402_5%

4

1

C136

C136

3300P_0402_50V7K

3300P_0402_50V7K

2

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_HT_RESET#

12

R374

R374

10K_0402_5%@

10K_0402_5%@

4

W=50mils

3V_LDT_RST#

R572

R572

220_0402_5%

220_0402_5%

HDT@

HDT@

R372 300_0402_5%R372 300_0402_5%

+1.8VS

CPU_SIC18

CPU_SID18

+1.2V_HT

place them to CPU within 1"

+3VALW+3VS

12

2

G

G

1 3

D

D

Q33

Q33

2N7002_SOT23HDT@

2N7002_SOT23HDT@

1 2

R582 300_0402_5%@R582 300_0402_5%@

1 2

R583 300_0402_5%

R583 300_0402_5%

1 2

@

R584 0_0402_5%@R584 0_0402_5%@

R585 0_0402_5%

R585 0_0402_5%

S

S

@

1 2

1 2

@

@

R36 44.2_0603_1%R36 44.2_0603_1%

1 2

R35 44.2_0603_1%R35 44.2_0603_1%

1 2

CPUCLK17

CPUCLK#17

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST21_SCANEN

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST24_SCANCLK1

CPU_TEST20_SCANCLK2

R683 0_0402_5%

R683 0_0402_5%

1 2

3

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

12/22 Modify

CPU_SIC_R

CPU_SID_R

CPU_HTREF1

CPU_HTREF0

5:10

CPU_VCC_SENSE48

CPU_VSS_SENSE48

C501

C501

1 2

3900P_0402_50V7K

3900P_0402_50V7K

C502

C502

1 2

3900P_0402_50V7K

3900P_0402_50V7K

169_0402_1%

169_0402_1%

R389

R389

12

SCAN Connector

+1.8V

JP38

JP38

1

3

5

7

9

11

13

15

17

19

21

23

25

ASP-68200-03

ASP-68200-03

CONN@

CONN@

CPU_HT_RESET#CPU_HT_RESET#_R

@

@

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST12_SCANSHIFTENB

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

3

R366 300_0402_5%R366 300_0402_5%

R369 1K_0402_5%R369 1K_0402_5%

R47 510_0402_5%R47 510_0402_5%

R684 300_0402_5% @R684 300_0402_5% @

R685 300_0402_5% @R685 300_0402_5% @

R686 300_0402_5% @R686 300_0402_5% @

R687 300_0402_5% @R687 300_0402_5% @

R368 300_0402_5%R368 300_0402_5%

R54 510_0402_5%R54 510_0402_5%

R92 300_0402_5%R92 300_0402_5%

R91 300_0402_5%R91 300_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

TP2PAD TP2PAD

TP1PAD TP1PAD

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST12_SCANSHIFTENB

CPU_THERMDC

CPU_THERMDA

10:10

2

4

6

8

10

12

14

16

18

20

22

24

KEY

KEY

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2

ATHLON Control and Debug

JCPU1D

VDDA=300mA

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_VCC_SENSE

CPU_VSS_SENSE

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

TP5PAD TP5PAD

TP6PAD TP6PAD

TP8PAD TP8PAD

TP9PAD TP9PAD

+1.8V

Compal Secret Data

Compal Secret Data

2005/03/08 2006/03/08

2005/03/08 2006/03/08

2005/03/08 2006/03/08

Compal Secret Data

JCPU1D

C10

VDDA2

D10

C7

C9

D8

AL6

AK6

V8

V7

G2

G1

AK11

AL11

A8

B8

B6

AL9

AH10

AJ10

AL10

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

Deciphered Date

Deciphered Date

Deciphered Date

THERMTRIP_L

VDDA1

PROCHOT_L

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

AMD AM2 Processor Socket

2

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PRESENT_L

PSI_L

NC#1

NC#2

NC#3

NC#4

DBREQ_L

TDO

TEST29_H

TEST29_L

NC#5

NC#6

NC#7

NC#8

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

MISC

MISC

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

+1.8V

12

R5

R5

300_0402_5%

300_0402_5%

H_THERMTRIP_S# H_THERMTRIP#

CPU_PROCHOT#_1.8

AK7

AL7

D2

D1

C1

E3

E2

E1

AL3

F1

H3

H4

H20

H21

A5

AK10

C11

D11

AE7

AD19

AE8

AD18

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

Y31

Y30

AG31

V31

W31

AF31

Q3

Q3

MMBT3904_SOT23

MMBT3904_SOT23

R7

R7

300_0402_5%

H_THERMTRIP_S#

CPU_PROCHOT#_1.8

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

TP7 PADTP7 PAD

3 1

300_0402_5%

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PRESENT#

PSI#

CPU_DBREQ#

CPU_TDO

5:4:5

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST26_BURNIN#

+1.8V

12

R4

R4

1K_0402_5%

1K_0402_5%

2

+1.8V

12

R8

R8

10K_0402_5%

10K_0402_5%

CPU_PH_G

B

B

2

Q4

Q4

E

E

3 1

C

C

MMBT3904_SOT23

MMBT3904_SOT23

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

+1.8V

12

12

R78

R78

300_0402_5%

300_0402_5%

PSI# 48

R68

R68

1 2

80.6_0402_1%

80.6_0402_1%

+3VALW

12

R3

R3

10K_0402_5%

10K_0402_5%

AMD CPU CTRL & DEBUG

AMD CPU CTRL & DEBUG

AMD CPU CTRL & DEBUG

KAW60 LA-4661P

KAW60 LA-4661P

KAW60 LA-4661P

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

+3VALW

12

R2

1K_0402_5%@R21K_0402_5%@

2

Q2

3 1

H_THERMTRIP# 18

+3VS

12

R6

R6

4.7K_0402_5%

4.7K_0402_5%

@

@

EC_THERM# 19,28

1

VID5 48

VID4 48

VID3 48

VID2 48

VID1 48

VID0 48

MMBT3904_SOT23@Q2MMBT3904_SOT23@

1

MAINPWON 42,43,45

of

of

of

850Friday, August 08, 2008

850Friday, August 08, 2008

850Friday, August 08, 2008

2.0

2.0

2.0

5

+CPU_CORE

D D

C C

B B

A A

JCPU1E

JCPU1E

A4

VDD1

A6

VDD2

AA8

VDD3

AA10

VDD4

AA12

VDD5

AA14

VDD6

AA16

VDD7

AA18

VDD8

AB7

VDD9

AB9

VDD10

AB11

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

AC10

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

AE10

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

AH2

VDD26

AH3

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

E10

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

F11

VDD46

G6

VDD47

G8

VDD48

G10

VDD49

G12

VDD50

H7

VDD51

H11

VDD52

H23

VDD53

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

JCPU1G

JCPU1G

A3

VSS1

A7

VSS2

A9

VSS3

A11

VSS4

AA4

VSS5

AA5

VSS6

AA7

VSS7

AA9

VSS8

AA11

VSS9

AA13

VSS10

AA15

VSS11

AA17

VSS12

AA19

VSS13

AA21

VSS14

AA23

VSS15

AB2

VSS16

AB3

VSS17

AB8

VSS18

AB10

VSS19

AB12

VSS20

AB14

VSS21

AB16

VSS22

AB18

VSS23

AB20

VSS24

AB22

VSS25

AC7

VSS26

AC9

VSS27

AC11

VSS28

AC13

VSS29

AC15

VSS30

AC17

VSS31

AC19

VSS32

AC21

VSS33

AC23

VSS34

AD8

VSS35

AD10

VSS36

AD12

VSS37

AD14

VSS38

AD16

VSS39

AD20

VSS40

AD22

VSS41

AD24

VSS42

AE4

VSS43

AE5

VSS44

AE9

VSS45

AE11

VSS46

AF2

VSS47

AF3

VSS48

AF8

VSS49

AF10

VSS50

AF12

VSS51

AF14

VSS52

AF16

VSS53

AF18

VSS54

AF20

VSS55

AF22

VSS56

AF24

VSS57

AF26

VSS58

AF28

VSS59

AG10

VSS61

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

5

GND1

GND1

POWER1

POWER1

VDD106

VDD105

VDD104

VDD103

VDD102

VDD101

VDD100

VDD99

VDD98

VDD97

VDD96

VDD95

VDD94

VDD93

VDD92

VDD91

VDD90

VDD89

VDD88

VDD87

VDD86

VDD85

VDD84

VDD83

VDD82

VDD81

VDD80

VDD79

VDD78

VDD77

VDD76

VDD75

VDD74

VDD73

VDD72

VDD71

VDD70

VDD69

VDD68

VDD67

VDD66

VDD65

VDD64

VDD63

VDD62

VDD61

VDD60

VDD59

VDD58

VDD57

VDD56

VDD55

VDD54

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

R10

R8

R5

R4

P19

P17

P15

P13

P11

P9

P7

N18

N16

N14

N12

N10

N8

M19

M17

M15

M13

M11

M9

M7

M3

M2

L18

L16

L14

Y19

Y17

L12

L10

L8

L5

L4

K23

K21

K19

K17

K15

K13

K11

K9

K7

J24

J22

J20

J18

J16

J14

J12

J8

H10

H8

G11

G9

F30

F28

F26

F24

F22

F20

F18

F16

F14

F4

E11

D30

D28

D26

D24

D22

D20

D18

D16

D14

C3

B30

B28

B26

B24

B22

B20

B18

B16

B14

B11

B9

B4

AL5

AK30

AK28

AK26

AK24

AK22

AK20

Y16

Y14

AK18

AK16

AK14

AK2

AH30

AH28

AH26

AH24

AH22

AH20

AH18

AH16

AH14

AG11

AM2 Processor

Socket

AM2 Processor Socket

4

+CPU_CORE

4

JCPU1F

JCPU1F

R12

VDD107

R14

VDD108

R16

VDD109

R18

VDD110

R20

VDD111

T2

VDD112

T3

VDD113

T7

VDD114

T9

VDD115

T11

VDD116

T13

VDD117

T15

VDD118

T17

VDD119

T19

VDD120

T21

VDD121

U8

VDD122

U10

VDD123

U12

VDD124

U14

VDD125

U16

VDD126

U18

VDD127

U20

VDD128

V9

VDD129

V11

VDD130

V13

VDD131

V15

VDD132

V17

VDD133

V19

VDD134

V21

VDD135

W4

VDD136

W5

VDD137

W8

VDD138

W10

VDD139

W12

VDD140

W14

VDD141

W16

VDD142

W18

VDD143

W20

VDD144

Y2

VDD145

Y3

VDD146

Y7

VDD147

Y9

VDD148

Y11

VDD149

Y13

VDD150

Y15

VDD151

Y21

VDD152

AA20

VDD153

AA22

VDD154

AB13

VDD155

AB15

VDD156

AB17

VDD157

AB19

VDD158

AB21

VDD159

AB23

VDD160

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

JCPU1H

JCPU1H

T22

VSS183

T20

VSS182

T18

VSS181

T16

VSS180

T14

VSS179

T12

VSS178

T10

VSS177

T8

VSS176

R23

VSS175

R21

VSS174

R19

VSS173

R17

VSS172

R15

VSS171

R13

VSS170

R11

VSS169

R9

VSS168

R7

VSS167

P22

VSS166

P20

VSS165

P18

VSS164

P16

VSS163

P14

VSS162

P12

VSS161

P10

VSS160

P8

VSS159

P3

VSS158

P2

VSS157

N23

VSS156

N21

VSS155

N19

VSS154

N17

VSS153

Y18

VSS152

K22

VSS151

K20

VSS150

K18

VSS149

K16

VSS148

K14

VSS147

K12

VSS146

K10

VSS145

K8

VSS144

K3

VSS143

K2

VSS142

J23

VSS141

J21

VSS140

J19

VSS139

J17

VSS138

J15

VSS137

J13

VSS136

J11

VSS135

J9

VSS134

J7

VSS133

J5

VSS132

J4

VSS131

H30

VSS130

H28

VSS129

H26

VSS128

H24

VSS127

H22

VSS126

H18

VSS125

H16

VSS124

H14

VSS123

H12

VSS122

TYCO_1-1735315-4_940P

TYCO_1-1735315-4_940P

CONN@

CONN@

GND2

GND2

3

+1.8V+CPU_CORE

Y29

VDDIO28

Y28

VDDIO27

Y26

VDDIO26

Y24

VDDIO25

V30

VDDIO24

V28

VDDIO23

V26

VDDIO22

V25

VDDIO21

T30

VDDIO20

T28

VDDIO19

T26

VDDIO18

T24

VDDIO17

P30

VDDIO16

P28

VDDIO15

P26

VDDIO14

P24

VDDIO13

M30

VDDIO12

M28

VDDIO11

M26

VDDIO10

M24

VDDIO9

AF30

VDDIO

AD30

VDDIO8

AD28

VDDIO7

AD26

VDDIO6

AC24

POWER2

POWER2

VDDIO5

AB30

VDDIO4

AB28

VDDIO3

AB26

VDDIO2

VDDIO1

VDD184

VDD183

VDD182

VDD181

VDD180

VDD179

VDD178

VDD177

VDD176

VDD175

VDD174

VDD173

VDD172

VDD171

VDD170

VDD169

VDD168

VDD167

VDD166

VDD165

VDD164

VDD163

VDD162

VDD161

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

AB24

Y23

W22

V23

U22

T23

R22

P23

P21

N22

N20

M23

M21

L22

L20

AF11

AE12

AD23

AD11

AC22

AC20

AC18

AC16

AC14

AC12

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

+CPU_CORE

+CPU_CORE

1

C70

C70

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

+1.8V

KAW60

1

C82

C82

22U_0805_6.3V6M

22U_0805_6.3V6M

2

A1

PVT

1

C120

C120

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C102

C102

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Athlon 64 S1g1

uPGA638

Top View

AF1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+CPU_CORE

1

+

+

C505

C505

330U_D2E_2.5VM_R9

330U_D2E_2.5VM_R9

2

+CPU_CORE

10U_0805_10V6M

10U_0805_10V6M

1

C17

C17

@

@

2

10U_0805_10V6M

10U_0805_10V6M

1

2

1

C195

C195

2

10U_0805_10V6M

10U_0805_10V6M

@

@

CPU SOCKET AM2 DECOUPLING

+CPU_CORE

1

C73

C73

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C100

C100

180P_0402_50V8J

180P_0402_50V8J

2

1

C72

C72