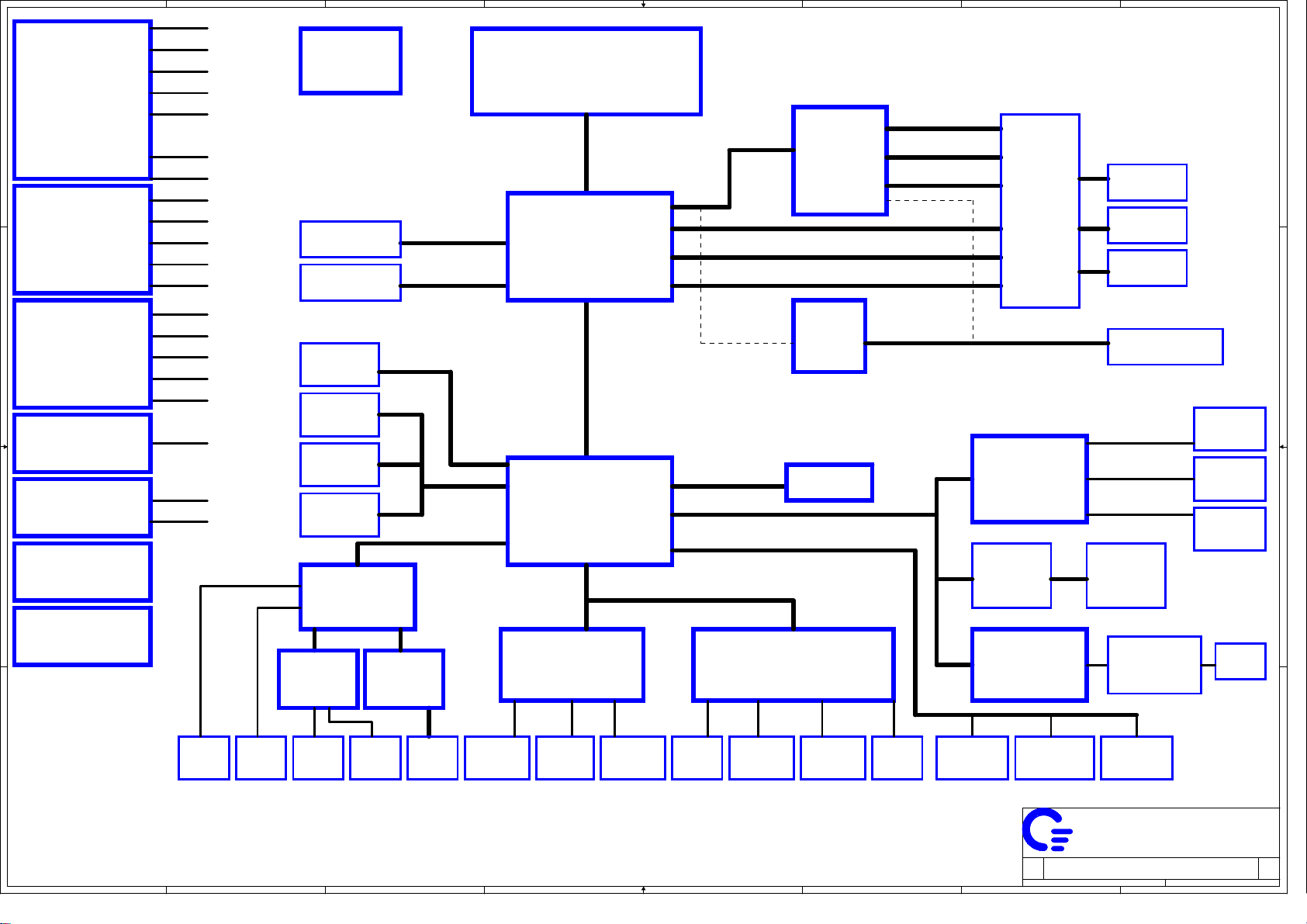

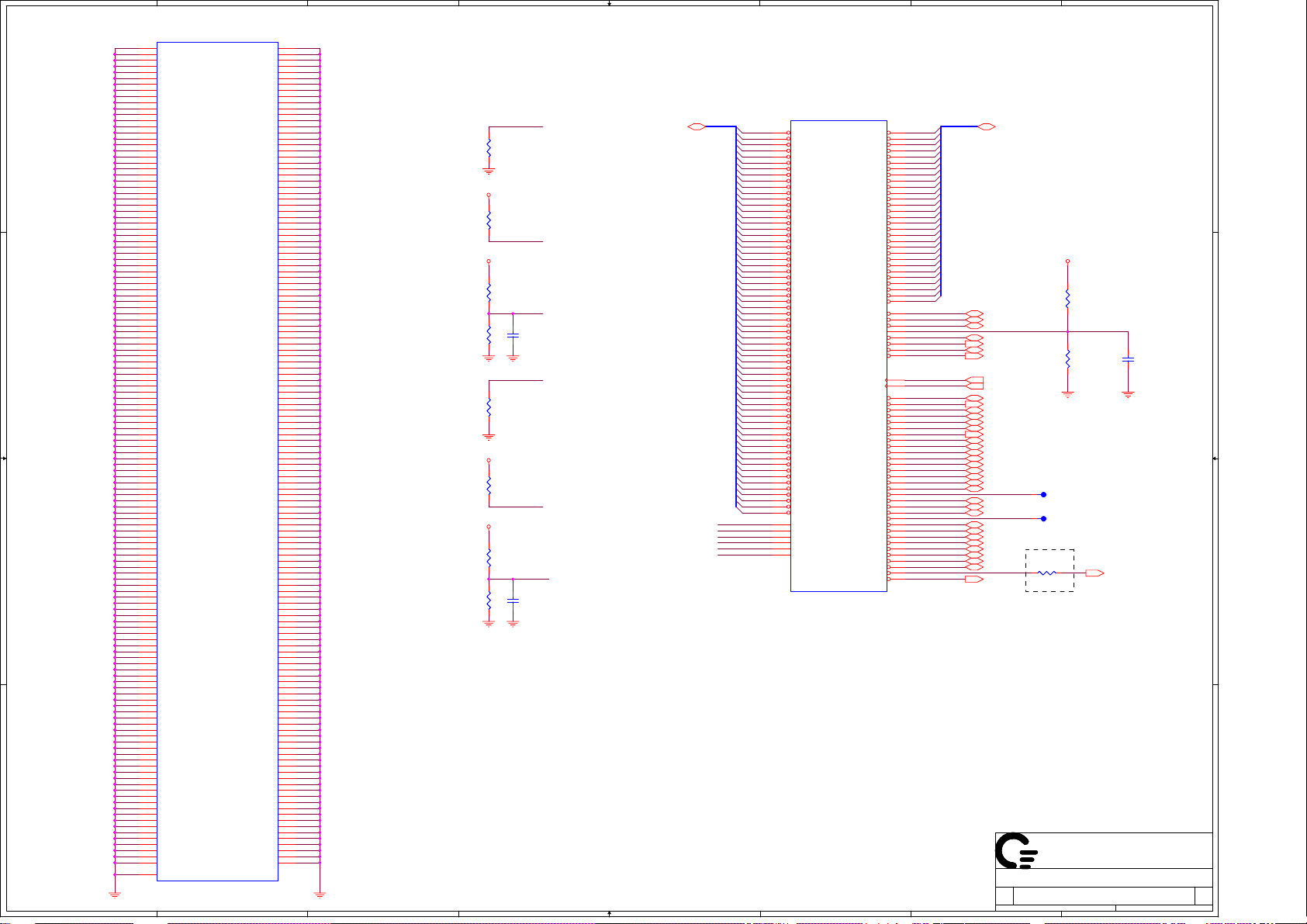

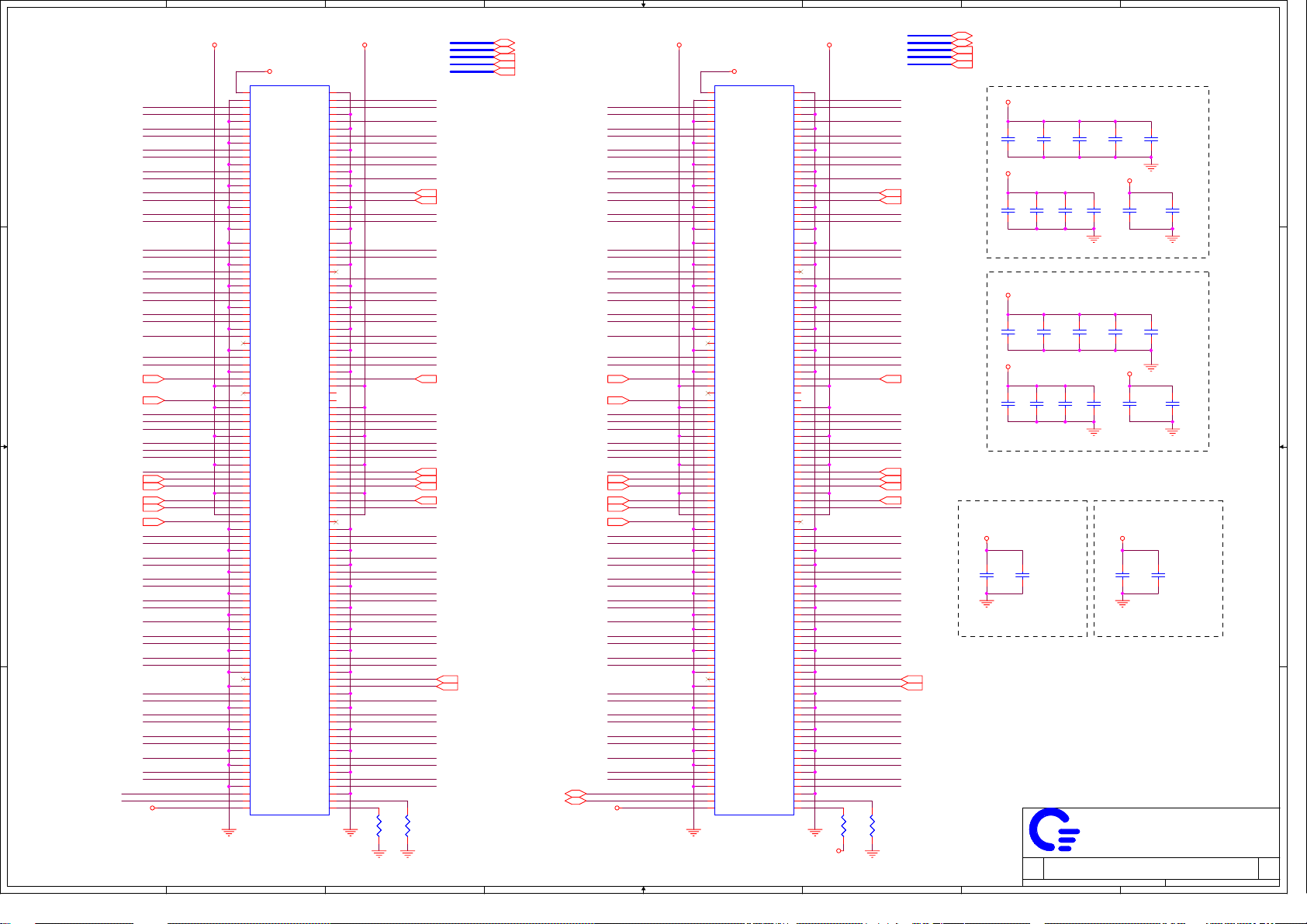

Acer Aspire 5510, Aspire 5514, Aspire 5512 Schematics

1

5VPCU

5V / 3.3V / 12V

Page : 35

A A

1.8V / 0.9V

Page : 36

1.5V / 1.05V / 1.8V

B B

Page : 37

3V_ALWAYS

+12V

+5V

3V_S5

3VSUS

5VSUS

2.5VSUS

+2.5V

+1.8V

MVREF_DM

SMDDR_VTERM

1.5V_S5

+1.5V

AGP_VCC (+1.5V)

1.2VCCT

VTT

2

CLOCK GEN

ICS

ICS954217

Page : 2

DDR2-SODIMM1

Page:9~10

DDR2-SODIMM2

Page:9~10

3

400/533MHZ DDR2

400/533MHZ DDR2

4

Centrino

DOTHAN

CELEROM-M

INTEL Mobile_479 CPU

ALVISO

1257 BGA

Page : 5 ~ 8

Page : 3 , 4

HOST BUS 533MHz

HOST BUS 400MHz

5

6

CRANE3 ( ZL7 )

PCIE

LVDS

RGB

TVOUT

ATI

M26P/M24P

64M /

128M

Page : 11 ~ 14

EXT_LVDS

EXT_CRT

EXT_TV-OUT

INT_LVDS

INT_CRT

INT_TV-OUT

7

ED@ INT. VGA WITH DOCK

ID@ INT. VGA WITH DOCK

ND@ W/O DOCKING

要打

SWITCH

CIRCUIT

BOM MARK

E@ EXT VGA

I@ INTVGA

SA@ SATA

F@ FIXED ODD

SW@ SWAPPABLE ODD

3@ 3in1

N@ NEW CARD

4@ 4401

5@ 5788M

D@ DOCKING

8

要打

要打

要打

要打

要打

要打

要打

要打

要打

CRT

Page:17

LVDS

Page:16

TV-OUT

Page:16

要打

DVI

CH7307

DOCKING/DVI

SATA - HDD

Page:21

Page:15

Page: 33

IDE - HDD

CPU CORE

Page : 34

+1.2V

Page : 38

BATTERY

C C

CHARGER

Page : 39

VCC_CORE

VGA_CORE

2.5V_VGA

BATTERY

SELECT

Page : 40

Page:21

IDE-ODD

Page:21

MEDIA BAY

Page:21

AUDIO CODEC

CONEXANT

20468-31

Page:27

AMP

MAX9755

Page:28

CONEXANT

MODEM

20493-21

Page:27

SATA

ATA 66/100

AC97

DMI I/F

ICH6-M

609 BGA

Page : 18 ~ 20

LPC

NS

KBC(97551)

Page : 29

PCIE

PCI BUS

USB 2.0

NEW CARD

Page : 32

NS

SIO (87383)

Page : 31

TI

PCMCIA+1394

+3 IN 1

PCI7411

Page: 23

MINI-PCI

Wireless LAN

Modem/LAN

Page : 22

BROADCOM

10/100/1G LAN

4401 / 5705M

Page:25

TV-TUNER

Page : 22

BOTHHAND

TRANSFORMER

Page:26

3 IN 1

Page: 24

PCMCIA

Page: 24

1394

Page: 23

RJ45

Page:26

MIC IN

D D

Page:27

LINE

IN

SPEKER

Page:28Page:27

LINE

OUT

Page:28

RJ11

Page:27

PCI ROUTING TABLE

REQ0# / GNT0#

REQ2# / GNT2#

REQ1# / GNT1#

DOCKING

PS2

Page:33

Touchpad

IDSEL

AD24

AD19

AD17

Keyboard

Page:30Page:30

IrDA

Page:31

INTERUPT

INTA#

INTB# , INTD#

INTC#,INTD#,INTA#

DOCKING

Print Port

Page:33

DEVICE

BROADCOM LAN

MINI-PCI

TI 7411

DOCKING

COM Port

Page:33

CIR

Page:33

REQ3# / GNT3# AD18 INTB# , INTD# MINI-PCI(TV Tuner)

1

2

3

4

5

6

SYSTEM 3

USB PORT

Page : 22

USB2,3,5

REV.C

DOCKING 2

USB PORT

Page : 22

USB0,1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet

Date: Sheet

Date: Sheet

7

MINI-USB

Page: 22

USB4

PROJECT : ZL7

PROJECT : ZL7

Quanta Computer Inc.

Quanta Computer Inc.

140Thursday, June 23, 2005

140Thursday, June 23, 2005

140Thursday, June 23, 2005

8

C

C

C

of

of

of

1

2

3

4

5

6

7

8

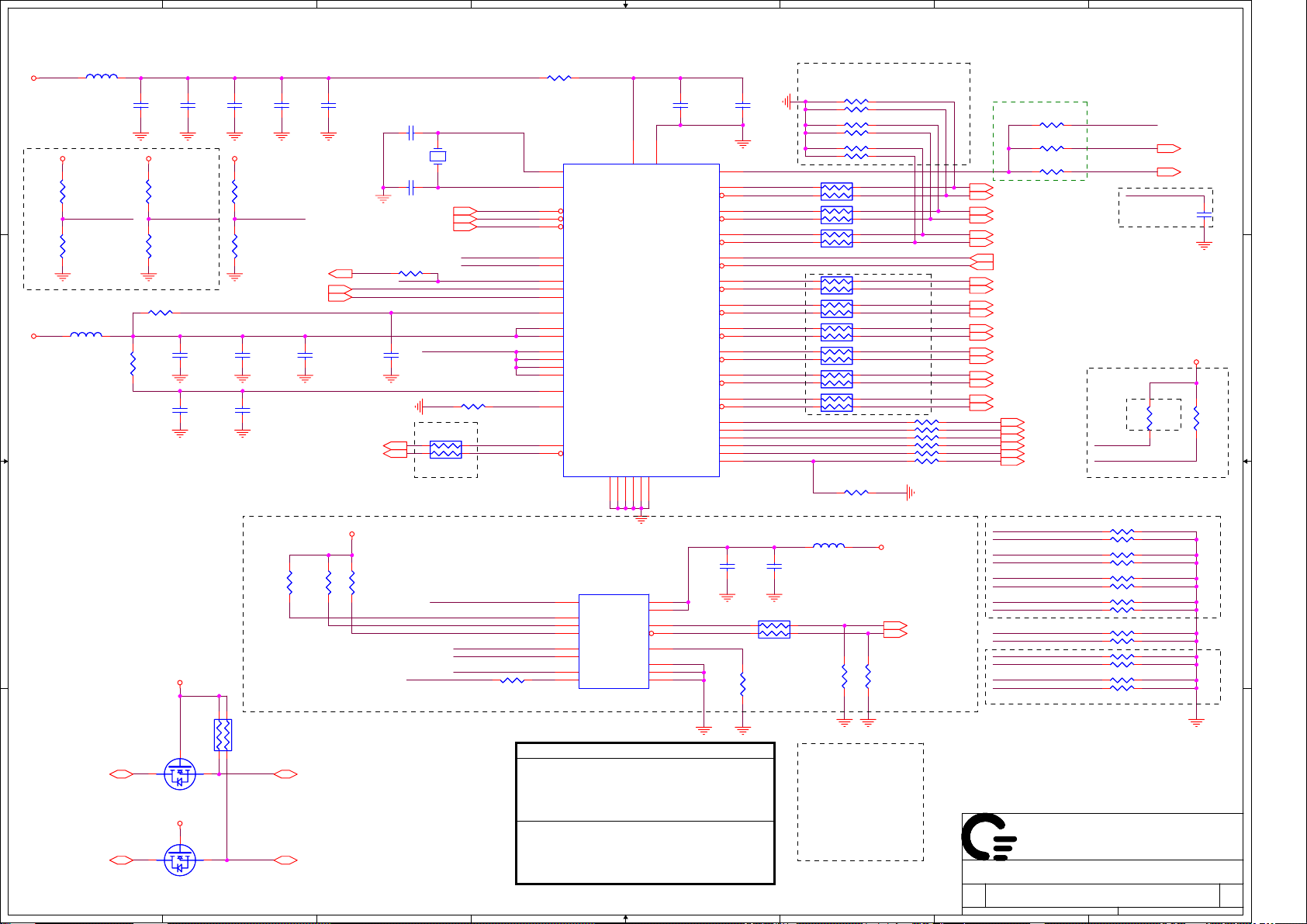

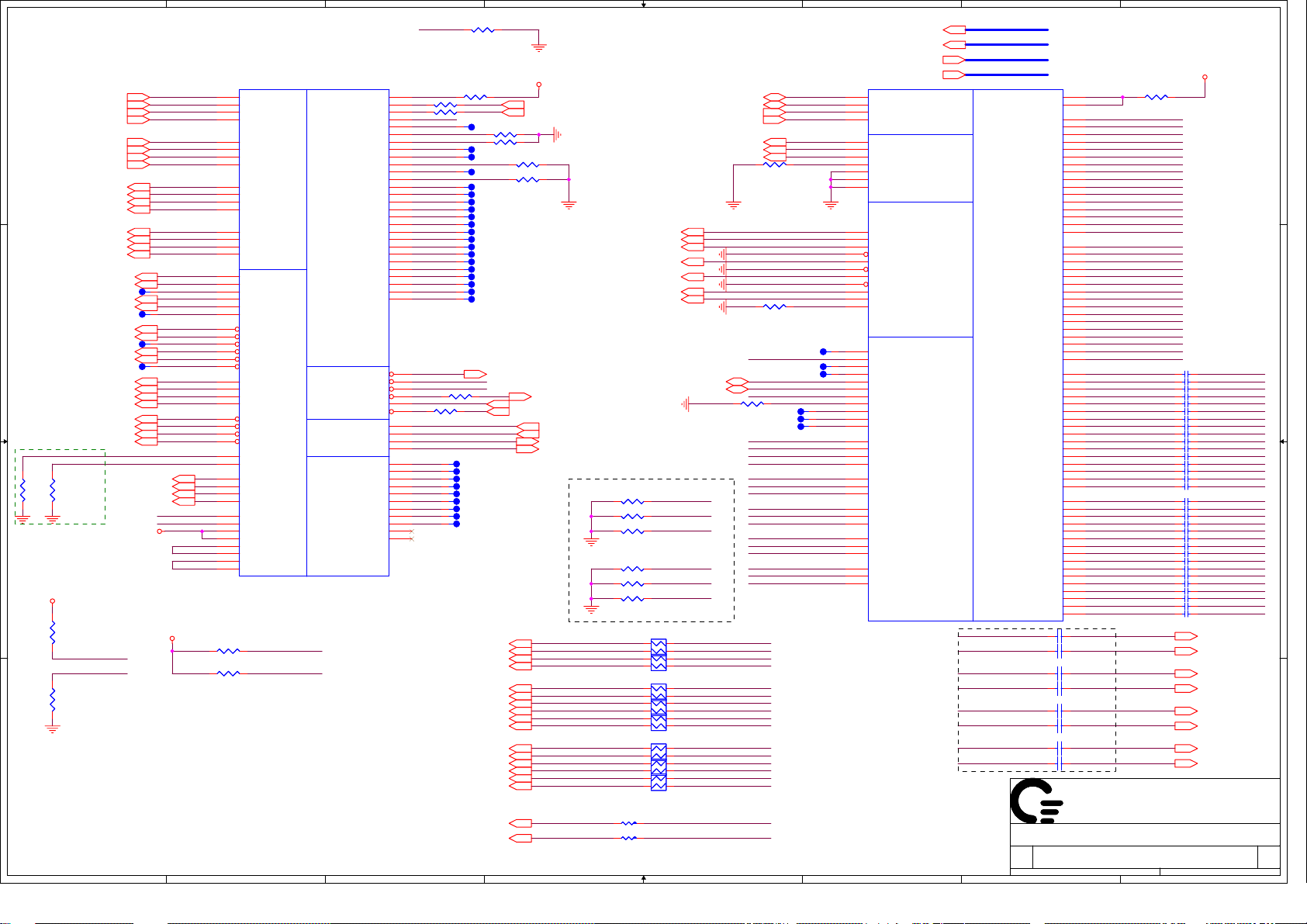

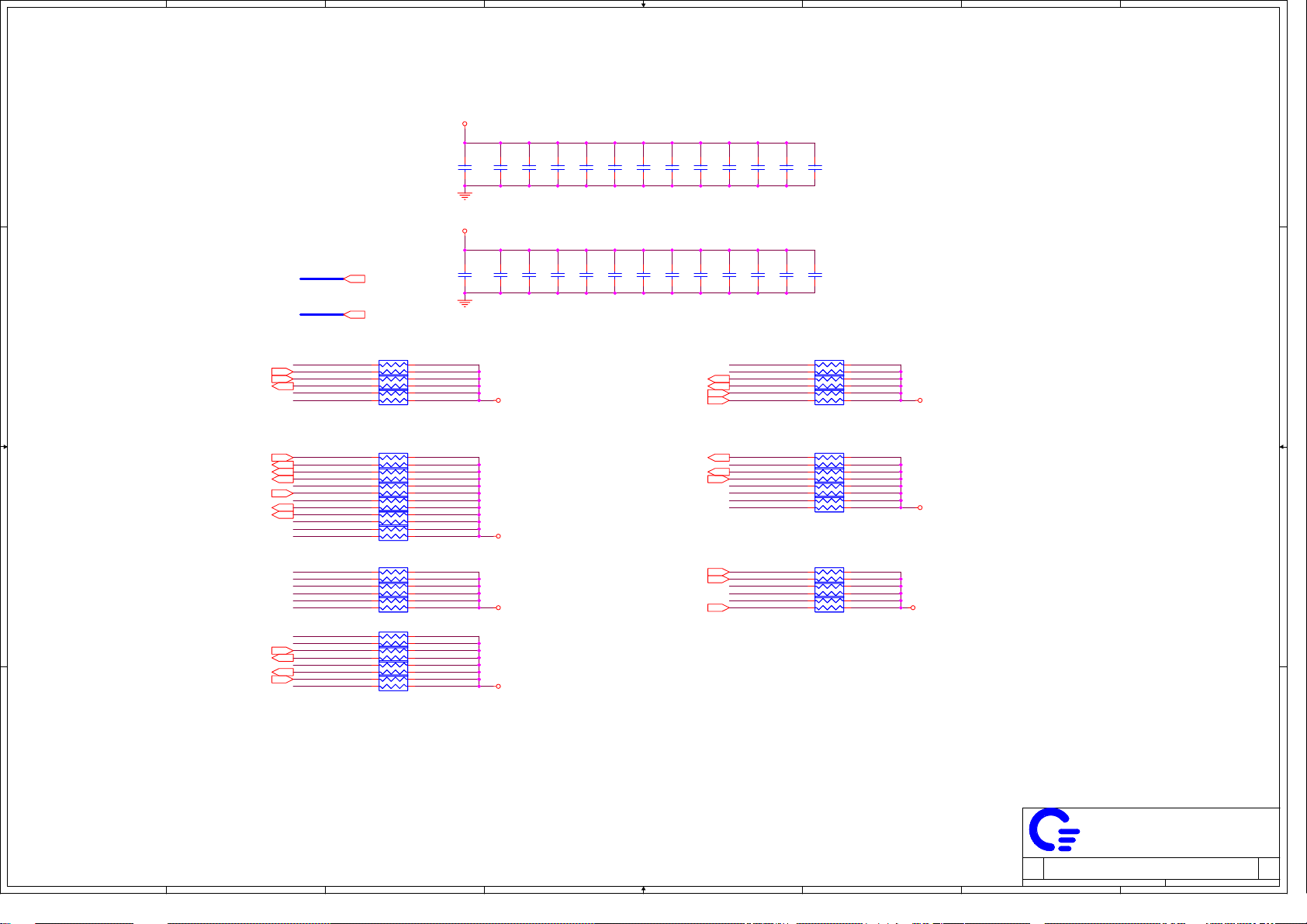

Place these termination

R205

IREF

R205

2.2

2.2

U35

U35

50

XTAL_IN

49

XTAL_OUT

10

VTT_PWRGD#/PD

55

PCI/SRC_STOP#

54

CPU_STOP#

46

SCLK

47

SDATA

12

FSA/USB_48

16

FSB/TEST_MODE

53

FSC/TEST_SEL

48

VDD_REF

1

VDD_PCI_1

7

VDD_PCI_2

42

VDD_CPU

21

VDD_SRC0

28

VDD_SRC1

34

VDD_SRC2

11

VDD_48

39

IREF

*Internal Pull-Down Resistor

*Internal Pull-Down Resistor

14

DOT96

15

DOT96#

12

C722

C722

10U/10V_8

10U/10V_8

1 2

1 2

R4631R463

1

R212

R212

2.2

2.2

R468

R468

1K_4

1K_4

R470

R470

*0_4

*0_4

12

12

VDD_CKG_CPU

12

C368

C368

.047U_4

.047U_4

C366

C366

10U/10V_8

10U/10V_8

C373

C373

10U/10V_8

10U/10V_8

12

C361

C361

.047U_4

.047U_4

R489

R489

10K_4

10K_4

1 2

R488

R488

*10K_4

*10K_4

1 2

VDD_CKGREF

CLKVDD

12

C371

C371

.047U_4

.047U_4

12

C370

C370

.047U_4

.047U_4

SELPSB1_CLK<4,6>

SELPSB2_CLK<4,6>

12

CLK48_USB<19>

C369

C369

.047U_4

.047U_4

12

C372

C372

.047U_4

.047U_4

12

C707

C707

.047U_4

.047U_4

C706

C706

.047U_4

.047U_4

DOT96<6>

DOT96#<6>

C718

C718

33P_4

33P_4

12

12

C709

C709

33P_4

33P_4

12

CLK_EN#<34>

STP_PCI#<19>

STP_CPU#<19,34>

SMbus address D2

R482 33_4R482 33_4

1 2

12

Iref=5mA,

Ioh=4*Iref

VDD_CKG_CPU

R465 475/F_4R465 475/F_4

I@4P2R-S-33

I@4P2R-S-33

4

2

RP15

RP15

CG_XIN

Y4

Y4

14.318MHZ/20PF

14.318MHZ/20PF

CG_XOUT R_HCLK_CPU

CLK_EN#

SMBCK

SMBDT

SELPSB0_CLK

SELPSB1_CLK

SELPSB2_CLK

VDD_CKG_48

1 2

R_DOT96

3

R_DOT96#

1

+3V

A A

+3V

B B

1 2

L50 ACB2012L-120L50 ACB2012L-120

+VCCP +3V+VCCP

R203

R203

1K_4

1K_4

1 2

SELPSB2_CLK SELPSB0_CLKSELPSB1_CLK

R204

R204

*0_4

*0_4

1 2

1 2

L51 ACB2012L-120L51 ACB2012L-120

SMBUS ADDRESS: D2, D3

+3V

12

12

*10K_4

C C

+3V

2

3

Q40

3

Q40

2N7002

2N7002

Q41

Q41

2N7002

2N7002

+3V

2

D D

PCLK_SMB<19,25,32,33> SMBCK <9>

1

*10K_4

2

4

RP9

RP9

4P2R-S-10K

4P2R-S-10K

1

3

SMBDT

1

SMBCK

1

2

R106

R106

*10K_4

*10K_4

R109

R109

SMBDT <9>PDAT_SMB<19,25,32,33>

12

*10K_4

*10K_4

R111

R111

SMBUS ADDRESS: D4, D5

CLK_SSC_IN

SMBCK

SMBDT

SSCD_VDD

CLK_EN#

DOTHAN-A 400

DOTHAN-A 533

3

U9

U9

1

SSC_S3

SSC_S2

SSC_S1

1 2

R117 *10K_4R117 *10K_4

CLKIN

2

S3

3

S2

4

S1

7

SCLK

8

SDATA

5

PWRDWN

6

REFOUT/SEL

*MK1493-05GT

*MK1493-05GT

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

0 1 1 166 100 33

0 1 0 200 100 33

0 0 0 266 100 33

1 0 0 333 100 33

1 1 0 400 100 33

1 1 1 RSVD 100 33

4

37

VDDA

CK-410M

CK-410M

GND_REF

GND_PCI_26GND_SRC29GND_CPU

GND_PCI_1

GND_48

2

51

13

VDDA

VDD

CLKOUT

CLKOUT#

IREF

VSSIREF

VSS

VSSA

VDDA_CKG

38

VSSA

CPU2_ITP/SRC5

CPU2#_ITP/SRC5#

*PERREQ1#

*PERREQ2#

PCIF0/ITP_EN

45

ICS954217

ICS954217

250mA ( MAX. )

16

9

12

11

14

13

10

15

12

C708

C708

.047U_4

.047U_4

REF

CPU0

CPU0#

CPU1

CPU1#

SRC4

SRC4#

SATACLK

SATACLK#

SRC3

SRC3#

SRC2

SRC2#

SRC1

SRC1#

SRC0

SRC0#

PCI5

PCI4

PCI3

PCI2

PCIF1

SSCD_VDD

R_DREFSSCLK

R_DREFSSCLK#

5

12

C355

C355

10U/10V_8

10U/10V_8

14M_REF

52

44

R_HCLK_CPU#

43

R_HCLK_MCH

41

R_HCLK_MCH#

40

R_MCH_3GPLL

36

R_MCH_3GPLL#

35

33

32

R_PCIE_VGA

31

R_PCIE_VGA#

30

R_PCIE_SATA

26

R_PCIE_SATA#

27

R_PCIE_EZ1

24

R_PCIE_EZ1#

25

R_PCIE_ICH

22

R_PCIE_ICH#

23

R_PCIE_EZ2

19

R_PCIE_EZ2#

20

R_PCIE_NEWC

17

R_PCIE_NEWC#

18

R_PCLK_591

5

R_PCLK_PCM

4

R_PCLK_LAN

3

R_PCLK_SIO

56

R_PCLK_MINI

9

R_PCLK_ICH

8

PULL HIGH TO SET PIN35,36 TO HOST CLK

C241

C241

4

2

R108

R108

*475/F_4

*475/F_4

1 2

12

C229

C229

*10U/10V_8

*10U/10V_8

RP2

RP2

*4P2R-S-33

*4P2R-S-33

12

*.1U_4

*.1U_4

to close CK410M.

R199 49.9/F_4R199 49.9/F_4

1 2

R198 49.9/F_4R198 49.9/F_4

1 2

R197 49.9/F_4R197 49.9/F_4

1 2

R196 49.9/F_4R196 49.9/F_4

1 2

R195 49.9/F_4R195 49.9/F_4

1 2

R194 49.9/F_4R194 49.9/F_4

1 2

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

2

1

4

3

R480 10K_4R480 10K_4

1 2

L23

L23

1 2

*ACB2012L-120

*ACB2012L-120

3

1

R110

R110

*49.9/F_4

*49.9/F_4

1 2

6

RP10

RP10

4P2R-S-33

4P2R-S-33

RP11

RP11

4P2R-S-33

4P2R-S-33

RP12

RP12

4P2R-S-33

4P2R-S-33

RP13

RP13

E@4P2R-S-33

E@4P2R-S-33

RP20

RP20

SA@4P2R-S-33

SA@4P2R-S-33

RP19

RP19

D@4P2R-S-33

D@4P2R-S-33

RP18

RP18

4P2R-S-33

4P2R-S-33

RP17

RP17

D@4P2R-S-33

D@4P2R-S-33

RP16

RP16

N@4P2R-S-33

N@4P2R-S-33

R478 33_4R478 33_4

1 2

R477 33_4R477 33_4

1 2

R476 33_4R476 33_4

1 2

R464 33_4R464 33_4

1 2

R481 33_4R481 33_4

1 2

R479 33_4R479 33_4

1 2

Define pin35,36 function

+3V

DREFSSCLK <6>

DREFSSCLK# <6>

R114

R114

*49.9/F_4

*49.9/F_4

1 2

R201 *12_4R201 *12_4

1 2

R200 12_4R200 12_4

1 2

R202 12_4R202 12_4

1 2

HCLK_CPU <3>

HCLK_CPU# <3>

HCLK_MCH <5>

HCLK_MCH# <5>

CLK_MCH_3GPLL <6>

CLK_MCH_3GPLL# <6>

NEW_CLKREQ# <32>

EZ_CLKREQ# <33>

CLK_PCIE_VGA <11>

CLK_PCIE_VGA# <11>

CLK_PCIE_SATA <18>

CLK_PCIE_SATA# <18>

CLK_PCIE_EZ1 <33>

CLK_PCIE_EZ1# <33>

CLK_PCIE_ICH <19>

CLK_PCIE_ICH# <19>

CLK_PCIE_EZ2 <33>

CLK_PCIE_EZ2# <33>

CLK_PCIE_NEWC <32>

CLK_PCIE_NEWC# <32>

PCLK_591 <29>

PCLK_PCM <23>

PCLK_LAN <25>

PCLK_SIO <31>

PCLK_MINI <22>

PCLK_ICH <18>

DOT96

DOT96#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_EZ2

CLK_PCIE_EZ2#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_EZ1

CLK_PCIE_EZ1#

CLK_PCIE_NEWC

CLK_PCIE_NEWC#

CLK_SSC_IN

14M_SIO

14M_SIO

PEREQ1# - SRC0, 2, SATA

PEREQ2# - SRC1, 3, 4

14M_SIO <31>

14M_ICH <19>

DEFALT OFF

DEFALT OFF

+3V

R615

R615

*1K_4

*1K_4

EZ_CLKREQ#

NEW_CLKREQ#

R490 I@49.9/F_4R490 I@49.9/F_4

1 2

R491 I@49.9/F_4R491 I@49.9/F_4

1 2

R193 E@49.9/F_4R193 E@49.9/F_4

1 2

R192 E@49.9/F_4R192 E@49.9/F_4

1 2

R486 SA@49.9/F_4R486 SA@49.9/F_4

1 2

R487 SA@49.9/F_4R487 SA@49.9/F_4

1 2

R492 D@49.9/F_4R492 D@49.9/F_4

1 2

R493 D@49.9/F_4R493 D@49.9/F_4

1 2

R209 49.9/F_4R209 49.9/F_4

1 2

R208 49.9/F_4R208 49.9/F_4

1 2

R207 D@49.9/F_4R207 D@49.9/F_4

1 2

R206 D@49.9/F_4R206 D@49.9/F_4

1 2

R211 N@49.9/F_4R211 N@49.9/F_4

1 2

R210 N@49.9/F_4R210 N@49.9/F_4

1 2

1 2

1 2

12

C915

C915

10P_4

10P_4

R616

R616

1K_4

1K_4

Place these termination

to close CK410M.

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

COMPUTER

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

ZL7 C

ZL7 C

ZL7 C

of

240Thursday, June 23, 2005

240Thursday, June 23, 2005

7

240Thursday, June 23, 2005

8

1

2

3

4

5

6

7

8

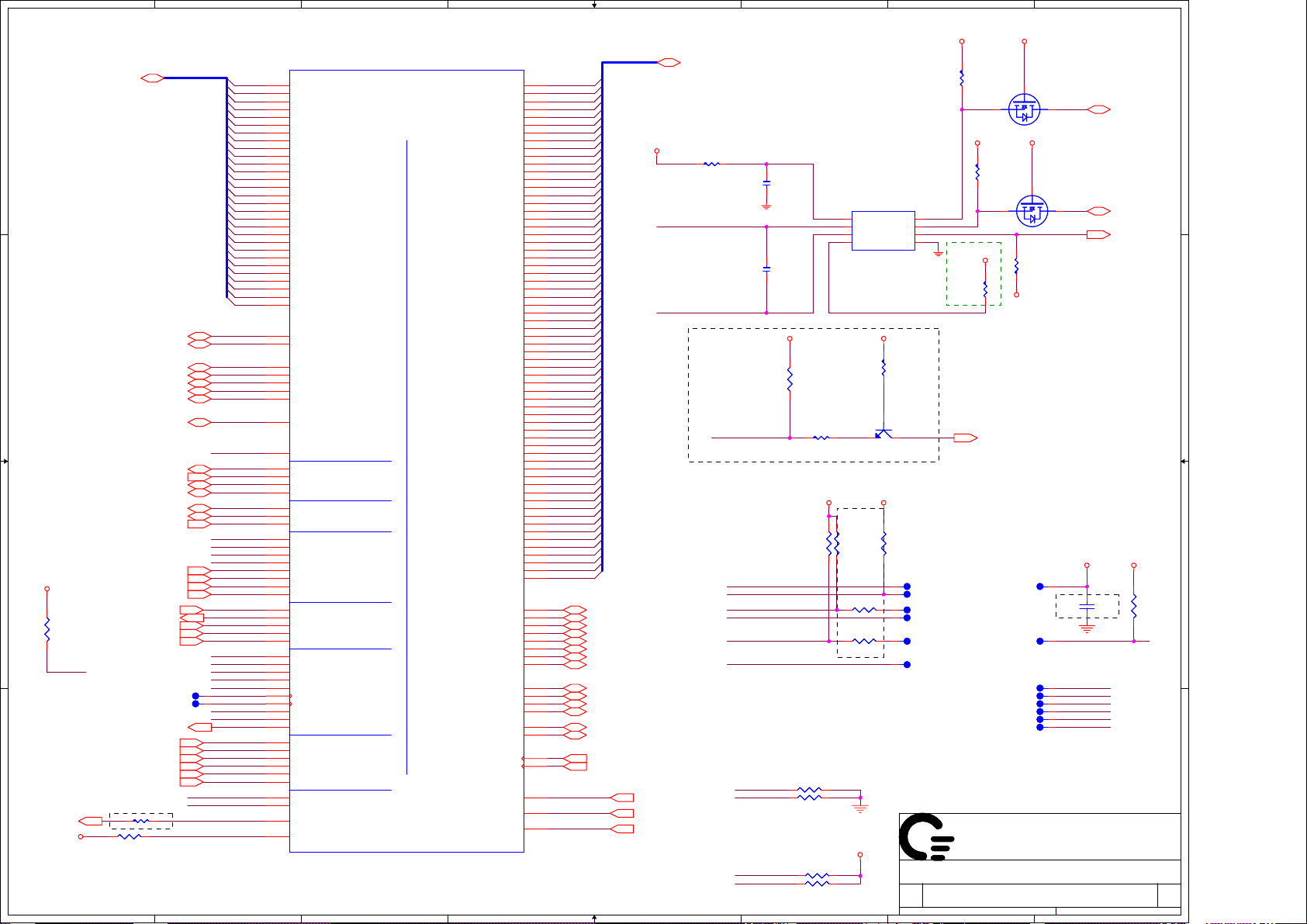

+3V

U31A

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A13

A12

C12

C11

B13

A16

A15

B10

A10

B18

A18

C17

B17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

N2

A4

N4

J3

L1

J2

K3

K4

L4

C8

B8

A9

C9

M3

H1

K1

L2

C2

D3

A3

E4

B4

A7

D1

D4

C6

A6

B7

G1

U31A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BPM0#

BPM1#

BPM2#

BPM3#

TRDY#

RS0#

RS1#

RS2#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

ITP_CLK0

ITP_CLK1

PREQ#

PRDY#

DBR#

LINT0

LINT1

STPCLK#

SLP#

DPSLP#

DPRSTP#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

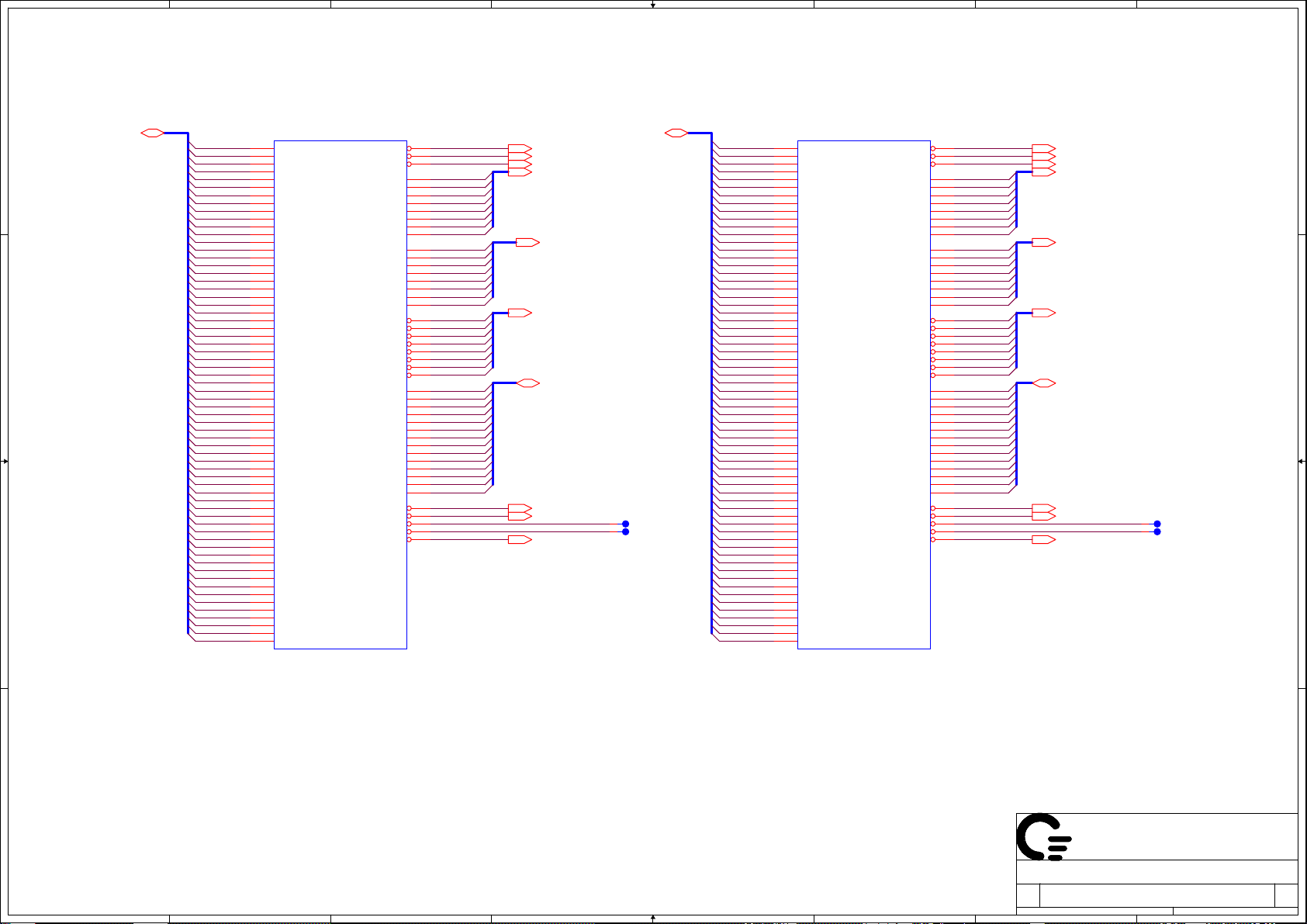

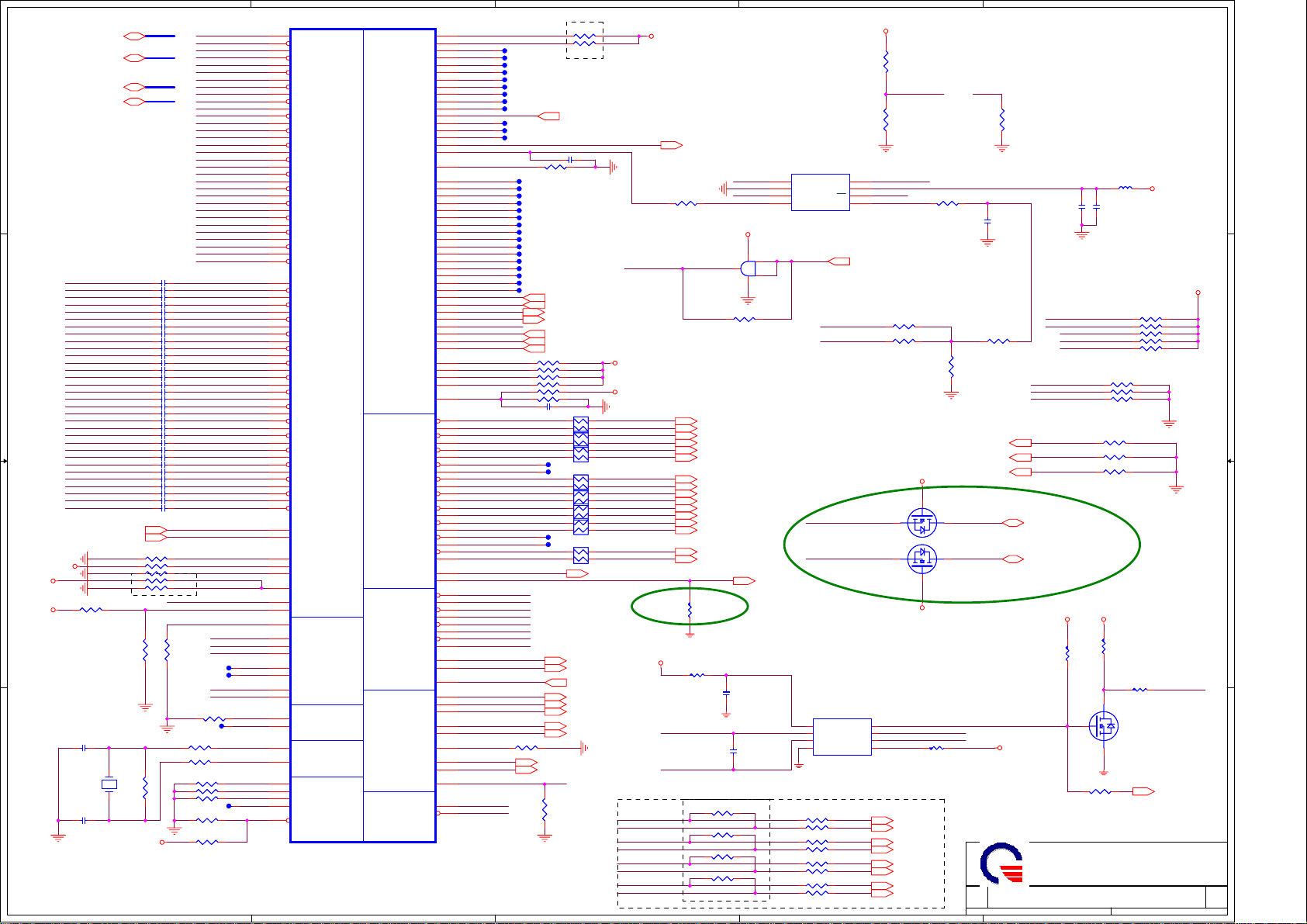

Dothan Processor

Dothan Processor

Dothan

Dothan

REQUEST

REQUEST

PHASE

PHASE

SIGNALS

SIGNALS

ERROR

ERROR

SIGNALS

SIGNALS

ARBITRATION

ARBITRATION

PHASE

PHASE

SIGNALS

SIGNALS

SNOOP PHASE

SNOOP PHASE

SIGNALS

SIGNALS

RESPONSE

RESPONSE

PHASE

PHASE

SIGNALS

SIGNALS

PC

PC

COMPATIBILITY

COMPATIBILITY

SIGNALS

SIGNALS

DIAGNOSTIC

DIAGNOSTIC

& TEST

& TEST

SIGNALS

SIGNALS

EXECUTION

EXECUTION

CONTROL

CONTROL

SIGNALS

SIGNALS

THERMAL DIODE

THERMAL DIODE

3

1 OF 3

1 OF 3

DATA

DATA

PHASE

PHASE

SIGNALS

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DINV0#

DINV1#

DINV2#

DINV3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

HD#0

A19

HD#1

A25

HD#2

A22

HD#3

B21

HD#4

A24

HD#5

B26

HD#6

A21

HD#7

B20

HD#8

C20

HD#9

B24

HD#10

D24

HD#11

E24

HD#12

C26

HD#13

B23

HD#14

E23

HD#15

C25

HD#16

H23

HD#17

G25

HD#18

L23

HD#19

M26

HD#20

H24

HD#21

F25

HD#22

G24

HD#23

J23

HD#24

M23

HD#25

J25

HD#26

L26

HD#27

N24

HD#28

M25

HD#29

H26

HD#30

N25

HD#31

K25

HD#32

Y26

HD#33

AA24

HD#34

T25

HD#35

U23

HD#36

V23

HD#37

R24

HD#38

R26

HD#39

R23

HD#40

AA23

HD#41

U26

HD#42

V24

HD#43

U25

HD#44

V26

HD#45

Y23

HD#46

AA26

HD#47

Y25

HD#48

AB25

HD#49

AC23

HD#50

AB24

HD#51

AC20

HD#52

AC22

HD#53

AC25

HD#54

AD23

HD#55

AE22

HD#56

AF23

HD#57

AD24

HD#58

AF20

HD#59

AE21

HD#60

AD21

HD#61

AF25

HD#62

AF22

HD#63

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

CPUINIT#

B5

CPURST#

B11

C19

4

HA#[3..31]<5>

A A

B B

C C

+VCCP

R429

R429

150_4

150_4

TDI

G1: NC for Dothan and

DPRSTP# for Yonah

D D

THERMTRIP#<6,18>

+VCCP

1

CPUPWRGD<18>

R441 *0_4R441 *0_4

R436 56_4R436 56_4

HA#[3..31]

HADSTB0#<5>

HADSTB1#<5>

HREQ#0<5>

HREQ#1<5>

HREQ#2<5>

HREQ#3<5>

HREQ#4<5>

ADS#<5>

HBREQ0#<5>

BPRI#<5>

BNR#<5>

HLOCK#<5>

HIT#<5>

HITM#<5>

DEFER#<5>

HTRDY#<5>

RS#0<5>

RS#1<5>

RS#2<5>

A20M#<18>

FERR#<18>

IGNNE#<18>

SMI#<18>

T180T180

T179T179

DBR#<19>

INTR<18>

NMI<18>

STPCLK#<18>

CPUSLP#<5,18>

DPSLP#<18>

DPRSLP#<18>

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

IERR#

BPM0#

BPM1#

BPM2#

BPM3#

A20M#

FERR#

IGNNE#

CPUPWRGD

SMI#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

DBR#

STPCLK#

CPUSLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#_PWR

CPU_PROCHOT#

2

HD#[0..63]

CPU junction temp up to 125 degree C

output signal. shut down system

HDSTBN0# <5>

HDSTBP0# <5>

HDSTBN1# <5>

HDSTBP1# <5>

HDSTBN2# <5>

HDSTBP2# <5>

HDSTBN3# <5>

HDSTBP3# <5>

HDBI0# <5>

HDBI1# <5>

HDBI2# <5>

HDBI3# <5>

DBSY# <5>

DRDY# <5>

HCLK_CPU# <2>

HCLK_CPU <2>

CPUINIT# <18>

CPURST# <5>

DPWR# <5>

HD#[0..63] <5>

+3V

R439 47R439 47

THERMDC

10 mil trace /

10 mil space

THERMDA MAX6648_OV#

15 MIL

THERMTRIP#_PWR

TDI

TMS

TDO

TRST#

CPURST#

TCK

3V_THM

C661

C661

.1U_4

.1U_4

C674

C674

2200P

2200P

R422

R422

54.9/F_4

54.9/F_4

U33

U33

1

3

2

MAX6657

MAX6657

R618

R618

56_4

56_4

R619

R619

330_4

330_4

+VCCP +VCCP

R426

R426

*54.9/F_4

*54.9/F_4

R425 *22.6/F_4R425 *22.6/F_4

R421 *22.6/F_4R421 *22.6/F_4

VCC

DXN

DXP

-OVT4GND

1 3

Q53 MMBT3904Q53 MMBT3904

TCK NO STUB

close to ITP conn

TCK

R430 27.4/F_4R430 27.4/F_4

TRST#

R427 680_4R427 680_4

close to CPU

IERR#

CPUPWRGD

5

R393 56_4R393 56_4

R402 200/F_4R402 200/F_4

+VCCP

6

R442

R442

10K_4

10K_4

+3V

KBSMDAT

7

SMDATA

KBSMCLK

8

SMCLK

6

-ALT

5

R449

R449

*10K_4

*10K_4

+VCCP+VCCP

R617

R617

330_4

330_4

2

DEPOP R425, R426, R421, C640 WHEN NO JITP

R428

R428

39.2/F_4

39.2/F_4

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

JITP CONN

T177T177

T173T173

T166T166

T176T176

T162T162

T178T178

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

Dothan Processor (HOST)

Dothan Processor (HOST)

Dothan Processor (HOST)

ZL7 C

ZL7 C

ZL7 C

7

+3V

1

R435

R435

10K_4

10K_4

1

+3V

+3V

1999_SHT# <35>

T171T171

T157T157

T155T155

T156T156

T158T158

T160T160

T163T163

T161T161

2

+3V

2

R448

R448

10K_4

10K_4

Q38

Q38

2N7002

2N7002

Q37

Q37

2N7002

2N7002

MBDATA

3

Level shift

MBCLK

3

+VCCP

C640

C640

*.1U_4

*.1U_4

1 2

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

340Thursday, June 23, 2005

340Thursday, June 23, 2005

340Thursday, June 23, 2005

MBDATA <11,29,40>

MBCLK <11,29,40>

MAX6648_AL# <29>

+3V_S5

R409

R409

150_4

150_4

DBR#

of

8

1

2

3

4

5

6

7

8

+VCCP

T152T152

T153T153

T181T181

CPU_VCCA

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

VCC_CORE

COMP0

COMP1

COMP2

COMP3

A A

B B

C C

R458

R458

R457

R457

27.4/F_4

27.4/F_4

12

C262

C262

10U_6.3V

10U_6.3V

12

C325

C325

10U_6.3V

10U_6.3V

12

C672

C672

10U_6.3V

10U_6.3V

C660

C660

10U_6.3V

10U_6.3V

1 2

54.9/F_4

54.9/F_4

Place pulldown resistors within

0.5" of COMP pins

VCC_CORE

12

12

C250

C250

C328

C328

10U_6.3V

10U_6.3V

10U_6.3V

10U_6.3V

VCC_CORE

12

12

C320

C320

C281

C281

10U_6.3V

10U_6.3V

10U_6.3V

10U_6.3V

12

12

C301

C301

C309

C309

10U_6.3V

10U_6.3V

10U_6.3V

10U_6.3V

VCC_CORE

C292

C292

C666

C666

10U_6.3V

10U_6.3V

10U_6.3V

10U_6.3V

1 2

1 2

R132

R132

27.4/F_4

27.4/F_4

.01U/16V_4

.01U/16V_4

12

C286

C286

10U_6.3V

10U_6.3V

12

C294

C294

10U_6.3V

10U_6.3V

12

C671

C671

10U_6.3V

10U_6.3V

C279

C279

10U_6.3V

10U_6.3V

1 2

R124

R124

54.9/F_4

54.9/F_4

C704

C704

12

C298

C298

10U_6.3V

10U_6.3V

12

C300

C300

10U_6.3V

10U_6.3V

12

C653

C653

10U_6.3V

10U_6.3V

C299

C299

10U_6.3V

10U_6.3V

1 2

1 2

12

C702

C702

10U_6.3V

10U_6.3V

12

C255

C255

10U_6.3V

10U_6.3V

12

C313

C313

10U_6.3V

10U_6.3V

C663

C663

10U_6.3V

10U_6.3V

1 2

1K/F

1K/F

2K/F_4

2K/F_4

CPU_VCCA

12

C649

C649

10U_6.3V

10U_6.3V

12

C322

C322

10U_6.3V

10U_6.3V

C668

C668

10U_6.3V

10U_6.3V

1 2

R455

R455

R456

R456

VCC_CORE

VCC_CORE

VCC_COREVCC_CORE

+1.8V

+1.5V

12

C656

C656

10U_6.3V

10U_6.3V

12

C329

C329

10U_6.3V

10U_6.3V

C659

C659

10U_6.3V

10U_6.3V

1 2

Place voltage

divider within

0.5" of GTLREF

pin

R407

R407

*1K_4

*1K_4

T182T182

T128T128

T151T151

R461

R461

R462

R462

12

12

10U_6.3V

10U_6.3V

12

10U_6.3V

10U_6.3V

10U_6.3V

10U_6.3V

1 2

C310

C310

C321

C321

C305

C305

C683

C683

10U_6.3V

10U_6.3V

12

C684

C684

10U_6.3V

10U_6.3V

C657

C657

10U_6.3V

10U_6.3V

1 2

R459

R459

*1K_4

*1K_4

*0_8

*0_8

0_8

0_8

Total caps = 2633 uF

ESR = 15m ohm/5 // 5m ohm/25 // 5m ohm/15

D D

+VCCP

12

C351

C351

+

+

150U/4V

150U/4V

<Type>

<Type>

CC3528

CC3528

12

12

C304

C304

.1U_4

.1U_4

1

C681

C681

.1U_4

.1U_4

12

.1U_4

.1U_4

C327

C327

12

C652

C652

.1U_4

.1U_4

2

12

C651

C651

.1U_4

.1U_4

+VCCP

C285

C285

.1U_4

.1U_4

3

C307

C307

.1U_4

.1U_4

C650

C650

.1U_4

.1U_4

C678

C678

.1U_4

.1U_4

C682

C682

.1U_4

.1U_4

4

P25

P26

AB2

AB1

AD26

AF7

AC1

E26

AC26

D18

D20

D22

E17

E19

E21

G21

H22

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

C5

F23

B2

C3

N1

B1

F26

D6

D8

E5

E7

E9

F6

F8

F18

F20

F22

G5

H6

J5

J21

U5

V6

W5

Y6

U31B

U31B

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

NC1

RSVD2

RSVD3

RSVD4

RSVD5

VCCA3

VCCA2

VCCA1

VCCA0

VCC00

VCC01

VCC02

VCC03

VCC04

VCC05

VCC06

VCC07

VCC08

VCC09

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Dothan Processor

Dothan Processor

Dothan

Dothan

2 OF 3

2 OF 3

POWER,

POWER,

GROUND,

GROUND,

RESERVED

RESERVED

SIGNALS

SIGNALS

A2

VSS00

A5

VSS01

A8

VSS02

A11

VSS03

A14

VSS04

A17

VSS05

A20

VSS06

A23

VSS07

A26

VSS08

B3

VSS09

B6

VSS10

B9

VSS11

B12

VSS12

B16

VSS13

B19

VSS14

B22

VSS15

B25

VSS16

C1

VSS17

C4

VSS18

C7

VSS19

C10

VSS20

C13

VSS21

C15

VSS22

C18

VSS23

C21

VSS24

C24

VSS25

D2

VSS26

D5

VSS27

D7

VSS28

D9

VSS29

D11

VSS30

D13

VSS31

D15

VSS32

D17

VSS33

D19

VSS34

D21

VSS35

D23

VSS36

D26

VSS37

E3

VSS38

E6

VSS39

E8

VSS40

E10

VSS41

E12

VSS42

E14

VSS43

E16

VSS44

E18

VSS45

E20

VSS46

E22

VSS47

E25

VSS48

F1

VSS49

F4

VSS50

F5

VSS51

F7

VSS52

F9

VSS53

F11

VSS54

F13

VSS55

F15

VSS56

F17

VSS57

F19

VSS58

F21

VSS59

F24

VSS60

G2

VSS61

G6

VSS62

G22

VSS63

G23

VSS64

G26

VSS65

H3

VSS66

H5

VSS67

H21

VSS68

H25

VSS69

J1

VSS70

J4

VSS71

J6

VSS72

J22

VSS73

J24

VSS74

K2

VSS75

K5

VSS76

K21

VSS77

K23

VSS78

K26

VSS79

L3

VSS80

L6

VSS81

L22

VSS82

L25

VSS83

M1

VSS84

M4

VSS85

M5

VSS86

M21

VSS87

M24

VSS88

N3

VSS89

N6

VSS90

N22

VSS91

N23

VSS92

N26

VSS93

P2

VSS94

P5

VSS95

P21

VSS96

P24

VSS97

R1

VSS98

R4

VSS99

5

CPU_VID0<34>

CPU_VID1<34>

CPU_VID2<34>

CPU_VID3<34>

CPU_VID4<34>

CPU_VID5<34>

T159T159

T154T154

SELPSB2_CLK<2,6>

SELPSB1_CLK<2,6>

SELPSB2_CLK

SELPSB1_CLK

1 2

1 2

T146T146

DOTHAN-A NC

DOTHAN-B POP

Bus speed select

6

+VCCP

Z0501

Z0502

0_4

0_4

BSEL0

R433

R433

BSEL1

R432

R432

0_4

0_4

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

U31C

U31C

W23

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCQ0

W4

VCCQ1

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSSENSE

C16

BSEL0

C14

BSEL1

E1

PSI

R6

VSS100

R22

VSS101

R25

VSS102

T3

VSS103

T5

VSS104

T21

VSS105

T23

VSS106

T26

VSS107

U2

VSS108

U6

VSS109

U22

VSS110

U24

VSS111

V1

VSS112

V4

VSS113

V5

VSS114

V21

VSS115

V25

VSS116

W3

VSS117

W6

VSS118

W22

VSS119

Dothan Processor

Dothan Processor

Dothan Processor (POWER)

Dothan Processor (POWER)

Dothan Processor (POWER)

ZL7 C

ZL7 C

ZL7 C

Dothan

Dothan

3 OF 3

3 OF 3

POWER, GROUND AND NC

POWER, GROUND AND NC

VID

VID

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

7

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

440Thursday, June 23, 2005

440Thursday, June 23, 2005

440Thursday, June 23, 2005

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

8

1

U34E

U34E

AF23

VSS136

H23

VSS137

AL22

VSS138

AH22

VSS139

J22

VSS140

E22

VSS141

D22

VSS142

A22

VSS143

AN21

VSS144

AF21

VSS145

F21

VSS146

C21

VSS147

A A

B B

C C

D D

1

AK20

AN19

AG19

AL18

AN17

AF17

AL16

AN14

AL14

AG14

AN11

AL11

AG11

AF11

AA11

AA10

AN24

AL24

VSS148

V20

VSS149

G20

VSS150

F20

VSS151

E20

VSS152

D20

VSS153

A20

VSS154

VSS155

VSS156

W19

VSS157

T19

VSS158

J19

VSS159

H19

VSS160

C19

VSS161

VSS162

U18

VSS163

B18

VSS164

A18

VSS165

VSS166

AJ17

VSS167

VSS168

G17

VSS169

C17

VSS170

VSS171

K16

VSS172

H16

VSS173

D16

VSS174

A16

VSS175

K15

VSS176

C15

VSS177

VSS178

VSS179

AJ14

VSS180

VSS181

K14

VSS182

J14

VSS183

F14

VSS184

B14

VSS185

A14

VSS186

J12

VSS187

D12

VSS188

B12

VSS189

VSS190

VSS191

AJ11

VSS192

VSS193

VSS194

VSS195

Y11

VSS196

H11

VSS197

F11

VSS198

VSS199

Y10

VSS200

L10

VSS201

D10

VSS202

AN9

VSS203

AH9

VSS204

AE9

VSS205

AC9

VSS206

AA9

VSS207

V9

VSS208

T9

VSS209

K9

VSS210

H9

VSS211

A9

VSS212

AL8

VSS213

Y8

VSS214

P8

VSS215

L8

VSS216

E8

VSS217

C8

VSS218

AN7

VSS219

AK7

VSS220

AG7

VSS221

AA7

VSS222

V7

VSS223

G7

VSS224

AJ6

VSS225

AE6

VSS226

AC6

VSS227

AA6

VSS228

T6

VSS229

P6

VSS230

L6

VSS231

J6

VSS232

B6

VSS233

AP5

VSS234

AL5

VSS235

W5

VSS236

E5

VSS237

AN4

VSS238

AF4

VSS239

Y4

VSS240

U4

VSS241

P4

VSS242

L4

VSS243

H4

VSS244

C4

VSS245

AJ3

VSS246

AC3

VSS247

AB3

VSS248

AA3

VSS249

C3

VSS250

A3

VSS251

AN2

VSS252

AL2

VSS253

AH2

VSS254

AE2

VSS255

AD2

VSS256

V2

VSS257

T2

VSS258

P2

VSS259

L2

VSS260

B27

VSS261

J26

VSS262

G26

VSS263

E26

VSS264

A26

VSS265

VSS266

VSS267

J2

VSS268

G2

VSS269

D2

VSS270

Y1

VSS271

B36

VSSALVDS

VSS

VSS

2

2

AG37

VSS0

Y37

VSS1

V37

VSS2

T37

VSS3

P37

VSS4

M37

VSS5

K37

VSS6

H37

VSS7

E37

VSS8

AN36

VSS9

AL36

VSS10

AJ36

VSS11

AF36

VSS12

AE36

VSS13

AD36

VSS14

AC36

VSS15

AB36

VSS16

AA36

VSS17

C36

VSS18

AE35

VSS19

Y35

VSS20

W35

VSS21

V35

VSS22

U35

VSS23

T35

VSS24

R35

VSS25

P35

VSS26

N35

VSS27

M35

VSS28

L35

VSS29

K35

VSS30

J35

VSS31

H35

VSS32

G35

VSS33

F35

VSS34

E35

VSS35

D35

VSS36

B35

VSS37

AN34

VSS38

AH34

VSS39

AD34

VSS40

AC34

VSS41

AB34

VSS42

AA34

VSS43

C34

VSS44

AL33

VSS45

AF33

VSS46

AD33

VSS47

W33

VSS48

V33

VSS49

U33

VSS50

T33

VSS51

R33

VSS52

P33

VSS53

N33

VSS54

M33

VSS55

L33

VSS56

K33

VSS57

J33

VSS58

H33

VSS59

G33

VSS60

F33

VSS61

E33

VSS62

D33

VSS63

AN32

VSS64

AJ32

VSS65

AD32

VSS66

AC32

VSS67

AB32

VSS68

AA32

VSS69

Y32

VSS70

C32

VSS71

A32

VSS72

AL31

VSS73

AG31

VSS74

AD31

VSS75

W31

VSS76

V31

VSS77

U31

VSS78

T31

VSS79

R31

VSS80

P31

VSS81

N31

VSS82

M31

VSS83

L31

VSS84

K31

VSS85

J31

VSS86

H31

VSS87

G31

VSS88

F31

VSS89

E31

VSS90

D31

VSS91

AP30

VSS92

AE30

VSS93

AC30

VSS94

AB30

VSS95

AA30

VSS96

Y30

VSS97

C30

VSS98

AM29

VSS99

AJ29

VSS100

AG29

VSS101

AD29

VSS102

AA29

VSS103

W29

VSS104

V29

VSS105

U29

VSS106

P29

VSS107

L29

VSS108

H29

VSS109

G29

VSS110

F29

VSS111

E29

VSS112

D29

VSS113

A29

VSS114

AC28

VSS115

AB28

VSS116

AA28

VSS117

W28

VSS118

E28

VSS119

AN27

VSS120

AL27

VSS121

AJ27

VSS122

AG27

VSS123

AF27

VSS124

AB27

VSS125

AA27

VSS126

W27

VSS127

G27

VSS128

E27

VSS129

AJ24

VSS130

AG24

VSS131

J24

VSS132

F24

VSS133

D24

VSS134

B24

VSS135

@ALVISO_GM/GML

@ALVISO_GM/GML

3

+VCCP

+VCCP

R438

R438

221/F_4

221/F_4

R437

R437

100/F_4

100/F_4

R454

R454

24.9/F_4

24.9/F_4

+VCCP

+VCCP

R453

R453

221/F_4

221/F_4

R452

R452

100/F_4

100/F_4

3

HXRCOMP

R434

R434

24.9/F_4

24.9/F_4

R150

R150

54.9/F_4

54.9/F_4

HXSCOMP

HYRCOMP

R451

R451

54.9/F_4

54.9/F_4

HYSCOMP

HXSWING

C665

C665

.1U_4

.1U_4

1 2

HYSWING

C690

C690

.1U_4

.1U_4

1 2

4

4

5

HD#[0..63]<3>

HD#[0..63]

HD#0

E4

HD#1

E1

HD#2

F4

HD#3

H7

HD#4

E2

HD#5

F1

HD#6

E3

HD#7

D3

HD#8

K7

HD#9

F2

HD#10

J7

HD#11

J8

HD#12

H6

HD#13

F3

HD#14

K8

HD#15

H5

HD#16

H1

HD#17

H2

HD#18

K5

HD#19

K6

HD#20

J4

HD#21

G3

HD#22

H3

HD#23

J1

HD#24

L5

HD#25

K4

HD#26

J5

HD#27

P7

HD#28

L7

HD#29

J3

HD#30

P5

HD#31

L3

HD#32

U7

HD#33

V6

HD#34

R6

HD#35

R5

HD#36

P3

HD#37

T8

HD#38

R7

HD#39

R8

HD#40

U8

HD#41

R4

HD#42

T4

HD#43

T5

HD#44

R1

HD#45

T3

HD#46

V8

HD#47

U6

HD#48

W6

HD#49

U3

HD#50

V5

HD#51

W8

HD#52

W7

HD#53

U2

HD#54

U1

HD#55

Y5

HD#56

Y2

HD#57

V4

HD#58

Y7

HD#59

W1

HD#60

W3

HD#61

Y3

HD#62

Y6

HD#63

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

5

W2

C1

C2

D1

T1

L1

P1

U34A

U34A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

@ALVISO_GM/GML

@ALVISO_GM/GML

6

HA#3

G9

HA3#

HA#4

C9

HA4#

HA#5

E9

HA5#

HA#6

B7

HA6#

HA#7

A10

HA7#

HA#8

F9

HA8#

HA#9

D8

HA9#

HA#10

B10

HA10#

HA#11

E10

HA11#

HA#12

G10

HA12#

HA#13

D9

HA13#

HA#14

E11

HA14#

HA#15

F10

HA15#

HA#16

G11

HA16#

HA#17

G13

HA17#

HA#18

C10

HA18#

HA#19

C11

HA19#

HA#20

D11

HA20#

HA#21

C12

HA21#

HA#22

B13

HA22#

HA#23

A12

HA23#

HA#24

F12

HA24#

HA#25

G12

HA25#

HA#26

E12

HA26#

HA#27

C13

HA27#

HA#28

B11

HA28#

HA#29

D13

HA29#

HA#30

A13

HA30#

HA#31

F13

HA31#

F8

HADS#

B9

HADSTB0#

E13

HADSTB1#

J11

HVREF

A5

HBNR#

D5

HBPRI#

E7

BREQ0#

H10

HCPURST#

HOST

HOST

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

HCPUSLP#_GMCH

HA#[3..31]

7

HA#[3..31] <3>

ADS# <3>

HADSTB0# <3>

HADSTB1# <3>

BNR# <3>

BPRI# <3>

HBREQ0# <3>

CPURST# <3>

HCLK_MCH# <2>

HCLK_MCH <2>

DBSY# <3>

DEFER# <3>

HDBI0# <3>

HDBI1# <3>

HDBI2# <3>

HDBI3# <3>

DPWR# <3>

DRDY# <3>

HDSTBN0# <3>

HDSTBN1# <3>

HDSTBN2# <3>

HDSTBN3# <3>

HDSTBP0# <3>

HDSTBP1# <3>

HDSTBP2# <3>

HDSTBP3# <3>

HIT# <3>

HITM# <3>

HLOCK# <3>

HREQ#0 <3>

HREQ#1 <3>

HREQ#2 <3>

HREQ#3 <3>

HREQ#4 <3>

RS#0 <3>

RS#1 <3>

RS#2 <3>

HTRDY# <3>

HVREF

R162

R162

1 2

0_4

0_4

T60

T60

*PAD

*PAD

T170

T170

*PAD

*PAD

+VCCP

R178

R178

100/F_4

100/F_4

R173

R173

200/F_4

200/F_4

8

C331

C331

.1U_4

.1U_4

1 2

CPUSLP# <3,18>

DO NOT INSTALL FOR DOTHAN-A AND INSTALL FOR DOTHAN-B

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

6

Date: Sheet

7

COMPUTER

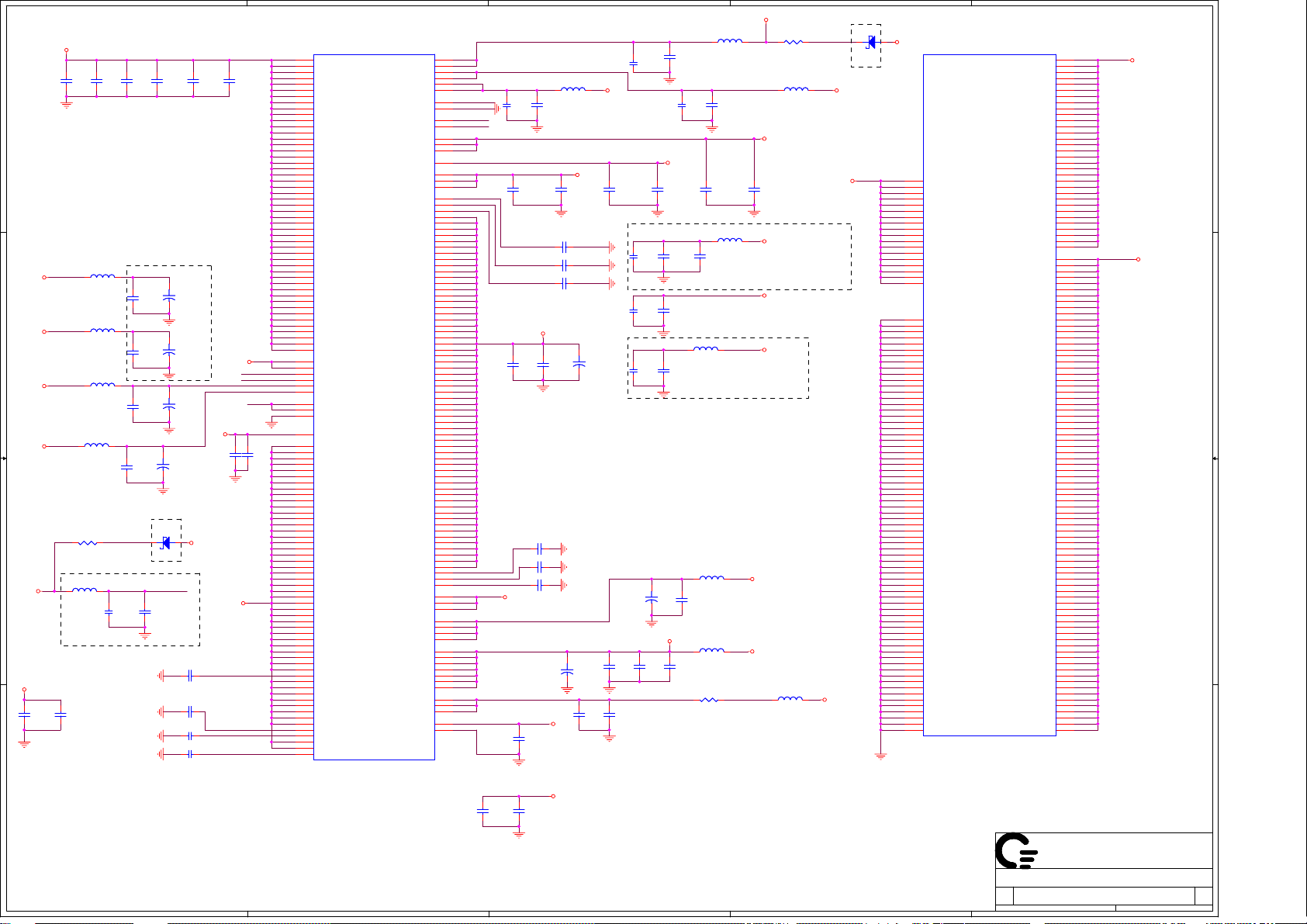

Alviso (Host)

Alviso (Host)

Alviso (Host)

ZL7 C

C

ZL7 C

C

ZL7 C

C

540Thursday, June 23, 2005

540Thursday, June 23, 2005

540Thursday, June 23, 2005

8

of

of

of

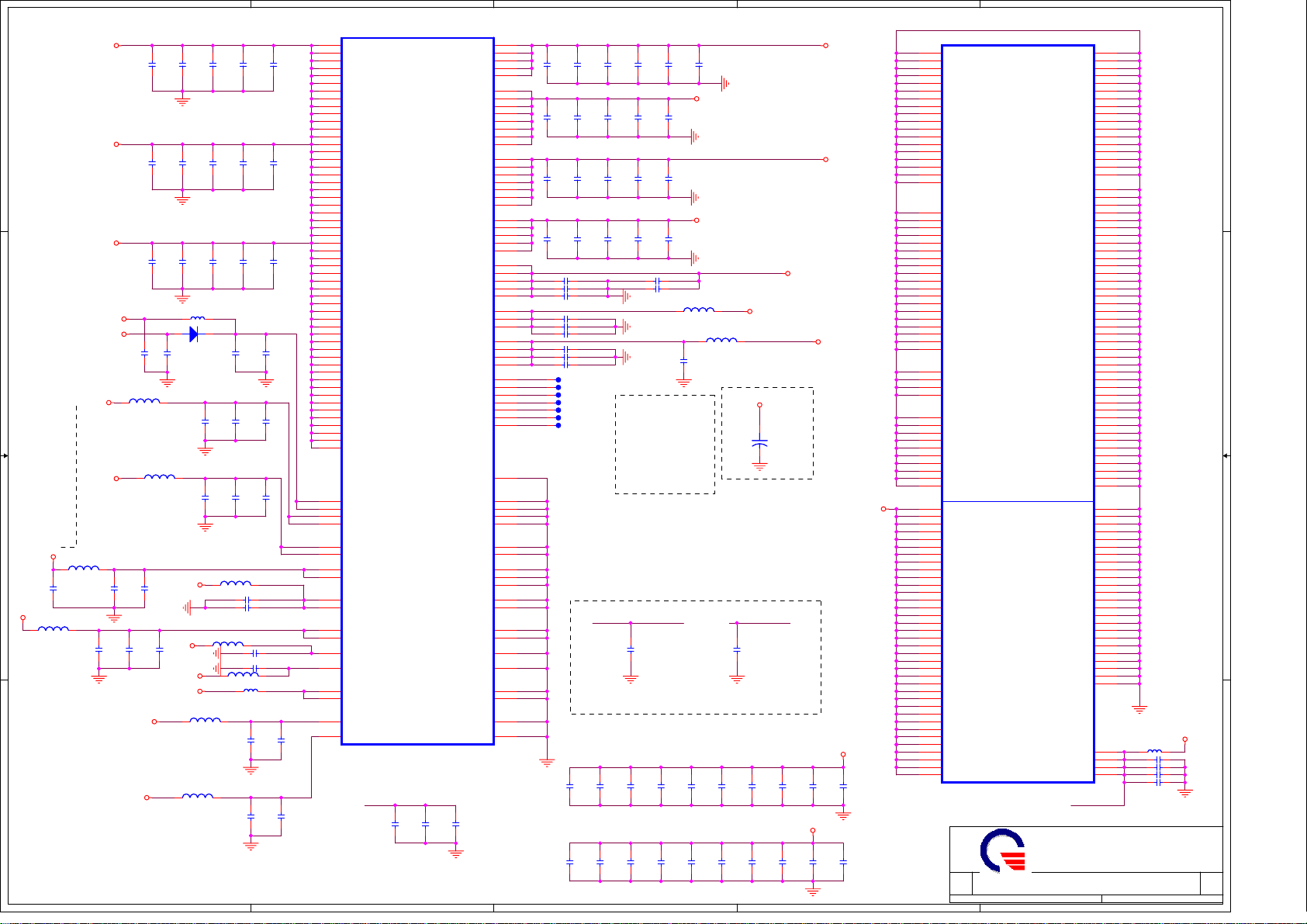

1

DMI_TXN0<19>

DMI_TXN1<19>

12

R184

R184

*40.2/F_4

*40.2/F_4

12

12

R190

R190

80.6/F_4

80.6/F_4

M_RCOMPN

M_RCOMPP

R188

R188

80.6/F_4

80.6/F_4

DMI_TXN2<19>

DMI_TXN3<19>

DMI_TXP0<19>

DMI_TXP1<19>

DMI_TXP2<19>

DMI_TXP3<19>

DMI_RXN0<19>

DMI_RXN1<19>

DMI_RXN2<19>

DMI_RXN3<19>

DMI_RXP0<19>

DMI_RXP1<19>

DMI_RXP2<19>

DMI_RXP3<19>

CLK_SDRAM0<9>

CLK_SDRAM1<9>

CLK_SDRAM3<9>

CLK_SDRAM4<9>

CLK_SDRAM0#<9>

CLK_SDRAM1#<9>

CLK_SDRAM3#<9>

CLK_SDRAM4#<9>

SM_CS0#<9,10>

SM_CS1#<9,10>

SM_CS2#<9,10>

SM_CS3#<9,10>

1

T79T79

T74T74

T78T78

T73T73

CKE0<9,10>

CKE1<9,10>

CKE2<9,10>

CKE3<9,10>

M_OCDCOMP0

M_OCDCOMP1

M_ODT0<9,10>

M_ODT1<9,10>

M_ODT2<9,10>

M_ODT3<9,10>

+0.9VSUS

It's point to point,

55ohm trace, keep as

short as possible.

CLK_SDRAM2

CLK_SDRAM5

CLK_SDRAM2#

CLK_SDRAM5#

CKE0

CKE1

CKE2

CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

+2.5V

A A

B B

12

R186

R186

*40.2/F_4

*40.2/F_4

Route as short

as possible.

Depop for SMVREF

C C

over current issue

+1.8VSUS

D D

2

CFG[0:2]=100 FOR FSB 533

CFG[0:2]=101 FOR FSB 400

U34C

U34C

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

SMYSLEWIN

AF10

SMYSLEWOUT

@ALVISO_GM/GML

@ALVISO_GM/GML

R171 10K_4R171 10K_4

1 2

R170 10K_4R170 10K_4

1 2

PM_EXTTS#0

PM_EXTTS#1

2

DMIDDR MUXING

DMIDDR MUXING

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

CFG/RSVDPMLCKNC

CFG/RSVDPMLCKNC

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSTIN#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

3

CFG3

R168

R168

*1K_4

*1K_4

R174 4.7K_4R174 4.7K_4

CFG0

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

3

1 2

R164 1K_4R164 1K_4

R167 1K_4R167 1K_4

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

CFG[17:3] have internal pullup resistors.

CFG[19:18] have internal pulldown resistors

PM_EXTTS#0

PM_EXTTS#1

DOT96#

DOT96

DREFSSCLK#

DREFSSCLK

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

T56T56

R177 0_4R177 0_4

1 2

R460 100R460 100

T187T187

T183T183

T186T186

T185T185

T184T184

T188T188

T175T175

T167T167

T172T172

TXLCLKOUT-<11,16>

TXLCLKOUT+<11,16>

TXUCLKOUT-<11,16>

TXUCLKOUT+<11,16>

TXLOUT0-<11,16>

TXLOUT0+<11,16>

TXLOUT1-<11,16>

TXLOUT1+<11,16>

TXLOUT2-<11,16>

TXLOUT2+<11,16>

TXUOUT0-<11,16>

TXUOUT0+<11,16>

TXUOUT1-<11,16>

TXUOUT1+<11,16>

TXUOUT2-<11,16>

TXUOUT2+<11,16>

DISP_ON<11,16>

BLON<11,16>

R166 *1K_4R166 *1K_4

R157

R157

1K_4

1K_4

T50T50

T70T70

R153

R153

T58T58

R161

R161

T52T52

T63T63

T49T49

T72T72

T69T69

T67T67

T66T66

T59T59

T55T55

T64T64

T68T68

T71T71

T169T169

T168T168

T54T54

T51T51

PM_BMBUSY# <19>

IMVP_PWRGD <19,34>

PLTRST# <11,15,18,21,29,31,32,33>

4

FOR DDR533

+VCCP

SELPSB1_CLK <2,4>

SELPSB2_CLK <2,4>

*1K_4

*1K_4

1K_4

1K_4

THERMTRIP# <3,18>

DOT96# <2>

DOT96 <2>

DREFSSCLK# <2>

DREFSSCLK <2>

TXLCLKOUT+

TXUCLKOUTTXUCLKOUT+

TXLOUT0TXLOUT1-

TXLOUT1+

TXLOUT2TXLOUT2+

TXUOUT0TXUOUT0+

TXUOUT1TXUOUT1+

TXUOUT2TXUOUT2+

DISP_ON

BLON

4

CFG5 Low=DMIx2

High=DMIx4

CFG6 Low=DDR2

High=DDR

CFG9 Low=REVERSE LANE

High=NORMAL

CFG11 FOR CPU533

R147 150/F_4R147 150/F_4

1 2

R148 150/F_4R148 150/F_4

1 2

R151 150/F_4R151 150/F_4

1 2

R143 150/F_4R143 150/F_4

1 2

R152 150/F_4R152 150/F_4

1 2

R159 150/F_4R159 150/F_4

1 2

INT_DDCCLK<17>

INT_DDCDAT<17>

INT_VGA_BLU<17>

INT_VGA_GRN<17>

INT_VGA_RED<17>

INT_VSYNC<17>

INT_HSYNC<17>

241

241

241

241

241

241

241

241

R134I@0_4 R134I@0_4

R139I@0_4 R139I@0_4

CLK_MCH_3GPLL#<2>

CLK_MCH_3GPLL<2>

I_EDIDCLK<16>

I_EDIDDATA<16>

R156 1.5K/FR156 1.5K/F

INT_TV_C/R

INT_TV_COMP

INT_TV_Y/G

INT_VGA_RED

INT_VGA_GRN

INT_VGA_BLU

RN110I@4P2R-S-0 RN110I@4P2R-S-0

3

RN9I@4P2R-S-0 RN9I@4P2R-S-0

3

RN107I@4P2R-S-0 RN107I@4P2R-S-0

3

RN108I@4P2R-S-0 RN108I@4P2R-S-0

3

RN109I@4P2R-S-0 RN109I@4P2R-S-0

3

RN12I@4P2R-S-0 RN12I@4P2R-S-0

3

RN11I@4P2R-S-0 RN11I@4P2R-S-0

3

RN10I@4P2R-S-0 RN10I@4P2R-S-0

3

INT_DISP_ON

INT_BLON

5

SDVO_CTRLDATA<15>

SDVO_CTRLCLK<15>

INT_TV_COMP<16>

INT_TV_Y/G<16>

INT_TV_C/R<16>

INT_TXLCLKOUT-TXLCLKOUTINT_TXLCLKOUT+

INT_TXUCLKOUTINT_TXUCLKOUT+

INT_TXLOUT0-

INT_TXLOUT0+TXLOUT0+

INT_TXLOUT1-

INT_TXLOUT1+

INT_TXLOUT2-

INT_TXLOUT2+

INT_TXUOUT0-

INT_TXUOUT0+

INT_TXUOUT1-

INT_TXUOUT1+

INT_TXUOUT2-

INT_TXUOUT2+

5

R169 4.99K/FR169 4.99K/F

R176 255/F_4R176 255/F_4

INT_BLON

T47T47

T48T48

INT_DISP_ON

T53T53

T62T62

T61T61

INT_TXLCLKOUTINT_TXLCLKOUT+

INT_TXUCLKOUTINT_TXUCLKOUT+

INT_TXLOUT0INT_TXLOUT1INT_TXLOUT2-

INT_TXLOUT0+

INT_TXLOUT1+

INT_TXLOUT2+

INT_TXUOUT0INT_TXUOUT1INT_TXUOUT2-

INT_TXUOUT0+

INT_TXUOUT1+

INT_TXUOUT2+

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

TV_REFSET

REFSET

T57T57

H24

H25

AB29

AC29

A15

C16

A17

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

J18

J20

6

GMCHEXP_TXP[0..15]<11>

GMCHEXP_TXN[0..15]<11>

GMCHEXP_RXP[0..15]<11,15>

GMCHEXP_RXN[0..15]<11,15>

U34F

U34F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

@ALVISO_GM/GML

@ALVISO_GM/GML

6

7

GMCHEXP_TXP[0..15]

GMCHEXP_TXN[0..15]

GMCHEXP_RXP[0..15]

GMCHEXP_RXN[0..15]

R158 24.9/F_4R158 24.9/F_4

MISC

MISC

TV VGA LVDS

TV VGA LVDS

CGMCHEXP_TXP0

CGMCHEXP_TXN0

CGMCHEXP_TXP1

CGMCHEXP_TXN1

CGMCHEXP_TXP2

CGMCHEXP_TXN2

CGMCHEXP_TXP3

CGMCHEXP_TXN3

EXP_COMPI

EXP_ICOMPO

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

Title

Title

Title

Size Document Number Rev

Custom

Size Document Number Rev

Custom

Size Document Number Rev

Custom

Date: Sheet

Date: Sheet

Date: Sheet

D36

D34

GMCHEXP_RXN0

E30

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

Alviso (VGA,DMI)

Alviso (VGA,DMI)

Alviso (VGA,DMI)

ZL7 C

ZL7 C

ZL7 C

7

GMCHEXP_RXN1

F34

GMCHEXP_RXN2

G30

GMCHEXP_RXN3

H34

GMCHEXP_RXN4

J30

GMCHEXP_RXN5

K34

GMCHEXP_RXN6

L30

GMCHEXP_RXN7

M34

GMCHEXP_RXN8

N30

GMCHEXP_RXN9

P34

GMCHEXP_RXN10

R30

GMCHEXP_RXN11

T34

GMCHEXP_RXN12

U30

GMCHEXP_RXN13

V34

GMCHEXP_RXN14

W30

GMCHEXP_RXN15

Y34

GMCHEXP_RXP0

D30

GMCHEXP_RXP1

E34

GMCHEXP_RXP2

F30

GMCHEXP_RXP3

G34

GMCHEXP_RXP4

H30

GMCHEXP_RXP5

J34

GMCHEXP_RXP6

K30

GMCHEXP_RXP7

L34

GMCHEXP_RXP8

M30

GMCHEXP_RXP9

N34

GMCHEXP_RXP10

P30

GMCHEXP_RXP11

R34

GMCHEXP_RXP12

T30

GMCHEXP_RXP13

U34

GMCHEXP_RXP14

V30

GMCHEXP_RXP15

W34

CGMCHEXP_TXN0

E32

CGMCHEXP_TXN1

F36

CGMCHEXP_TXN2

G32

CGMCHEXP_TXN3

H36

CGMCHEXP_TXN4

J32

CGMCHEXP_TXN5

K36

CGMCHEXP_TXN6

L32

CGMCHEXP_TXN7

M36

CGMCHEXP_TXN8

N32

CGMCHEXP_TXN9

P36

CGMCHEXP_TXN10

R32

CGMCHEXP_TXN11

T36

CGMCHEXP_TXN12

U32

CGMCHEXP_TXN13

V36

CGMCHEXP_TXN14

W32

CGMCHEXP_TXN15

Y36

CGMCHEXP_TXP0

D32

CGMCHEXP_TXP1

E36

CGMCHEXP_TXP2

F32

CGMCHEXP_TXP3

G36

CGMCHEXP_TXP4

H32

CGMCHEXP_TXP5

J36

CGMCHEXP_TXP6

K32

CGMCHEXP_TXP7

L36

CGMCHEXP_TXP8

M32

CGMCHEXP_TXP9

N36

CGMCHEXP_TXP10

P32

CGMCHEXP_TXP11

R36

CGMCHEXP_TXP12

T32

CGMCHEXP_TXP13

U36

CGMCHEXP_TXP14

V32

CGMCHEXP_TXP15

W36

C629ID@.1U_4 C629ID@.1U_4

12

C627ID@.1U_4 C627ID@.1U_4

12

C308ID@.1U_4 C308ID@.1U_4

12

C312ID@.1U_4 C312ID@.1U_4

12

C625ID@.1U_4 C625ID@.1U_4

12

C620ID@.1U_4 C620ID@.1U_4

12

C318ID@.1U_4 C318ID@.1U_4

12

C323ID@.1U_4 C323ID@.1U_4

12

QUANTA

QUANTA

QUANTA

COMPUTER

COMPUTER

COMPUTER

1 2

SDVOB_R+

SDVOB_R-

SDVOB_G+

SDVOB_G-

SDVOB_B+

SDVOB_B-

SDVOB_CLK+

SDVOB_CLK-

8

VCC3G_PCIE

GMCHEXP_TXN0

C626E@.1U_4 C626E@.1U_4

GMCHEXP_TXN1

C667E@.1U_4 C667E@.1U_4

GMCHEXP_TXN2

C619E@.1U_4 C619E@.1U_4

GMCHEXP_TXN3

C673E@.1U_4 C673E@.1U_4

GMCHEXP_TXN4

C613E@.1U_4 C613E@.1U_4

GMCHEXP_TXN5

C685E@.1U_4 C685E@.1U_4

GMCHEXP_TXN6

C605E@.1U_4 C605E@.1U_4

GMCHEXP_TXN7

C689E@.1U_4 C689E@.1U_4

GMCHEXP_TXN8

C599E@.1U_4 C599E@.1U_4

GMCHEXP_TXN9

C692E@.1U_4 C692E@.1U_4

GMCHEXP_TXN10

C594E@.1U_4 C594E@.1U_4

GMCHEXP_TXN11

C695E@.1U_4 C695E@.1U_4

GMCHEXP_TXN12

C592E@.1U_4 C592E@.1U_4

GMCHEXP_TXN13

C698E@.1U_4 C698E@.1U_4

GMCHEXP_TXN14

C590E@.1U_4 C590E@.1U_4

GMCHEXP_TXN15

C587E@.1U_4 C587E@.1U_4

GMCHEXP_TXP0

C628E@.1U_4 C628E@.1U_4

GMCHEXP_TXP1

C664E@.1U_4 C664E@.1U_4

GMCHEXP_TXP2

C624E@.1U_4 C624E@.1U_4

GMCHEXP_TXP3

C669E@.1U_4 C669E@.1U_4

GMCHEXP_TXP4

C616E@.1U_4 C616E@.1U_4

GMCHEXP_TXP5

C679E@.1U_4 C679E@.1U_4

GMCHEXP_TXP6

C608E@.1U_4 C608E@.1U_4

GMCHEXP_TXP7

C686E@.1U_4 C686E@.1U_4

GMCHEXP_TXP8

C601E@.1U_4 C601E@.1U_4

GMCHEXP_TXP9

C691E@.1U_4 C691E@.1U_4

GMCHEXP_TXP10

C595E@.1U_4 C595E@.1U_4

GMCHEXP_TXP11

C693E@.1U_4 C693E@.1U_4

GMCHEXP_TXP12

C593E@.1U_4 C593E@.1U_4

GMCHEXP_TXP13

C697E@.1U_4 C697E@.1U_4

GMCHEXP_TXP14

C591E@.1U_4 C591E@.1U_4

GMCHEXP_TXP15

C588E@.1U_4 C588E@.1U_4

SDVOB_R+ <15>

SDVOB_R- <15>

SDVOB_G+ <15>

SDVOB_G- <15>

SDVOB_B+ <15>

SDVOB_B- <15>

SDVOB_CLK+ <15>

SDVOB_CLK- <15>

640Thursday, June 23, 2005

640Thursday, June 23, 2005

640Thursday, June 23, 2005

8

of

of

of

1

2

3

4

5

6

7

8

A A

B B

C C

R_A_MD[0..63]<9>

R_A_MD0

R_A_MD1

R_A_MD2

R_A_MD3

R_A_MD4

R_A_MD5

R_A_MD6

R_A_MD7

R_A_MD8

R_A_MD9

R_A_MD10

R_A_MD11

R_A_MD12

R_A_MD13

R_A_MD14

R_A_MD15

R_A_MD16

R_A_MD17

R_A_MD18

R_A_MD19

R_A_MD20

R_A_MD21

R_A_MD22

R_A_MD23

R_A_MD24

R_A_MD25

R_A_MD26

R_A_MD27

R_A_MD28

R_A_MD29

R_A_MD30

R_A_MD31

R_A_MD32

R_A_MD33

R_A_MD34

R_A_MD35

R_A_MD37

R_A_MD38

R_A_MD39

R_A_MD40

R_A_MD41

R_A_MD42

R_A_MD43

R_A_MD44

R_A_MD45

R_A_MD46

R_A_MD47

R_A_MD48

R_A_MD49

R_A_MD50

R_A_MD51

R_A_MD52

R_A_MD53

R_A_MD54

R_A_MD55

R_A_MD56

R_A_MD57

R_A_MD58

R_A_MD59

R_A_MD60

R_A_MD61

R_A_MD62

R_A_MD63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

U34B

U34B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

@ALVISO_GM/GML

@ALVISO_GM/GML

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

R_A_BS0#

R_A_BS1#

R_A_BS2#

R_A_DM0

R_A_DM1

R_A_DM2

R_A_DM3

R_A_DM4

R_A_DM5

R_A_DM6

R_A_DM7

R_A_DQS0

R_A_DQS1

R_A_DQS2

R_A_DQS3

R_A_DQS4

R_A_DQS5

R_A_DQS6

R_A_DQS7

R_A_DQS#0

R_A_DQS#1

R_A_DQS#2

R_A_DQS#3

R_A_DQS#4

R_A_DQS#5

R_A_DQS#6

R_A_DQS#7

R_A_MA0

R_A_MA1

R_A_MA2

R_A_MA3

R_A_MA4

R_A_MA5

R_A_MA6

R_A_MA7

R_A_MA8

R_A_MA9

R_A_MA10

R_A_MA11

R_A_MA12

R_A_MA13

R_A_SCASA#

R_A_SRASA#

SA_RCVENIN#

SA_RCVENOUT#

R_A_BMWEA#

R_A_BS0# <9,10>

R_A_BS1# <9,10>

R_A_BS2# <9,10>

R_A_DM[0..7] <9>

R_A_DQS[0..7] <9>

R_A_DQS#[0..7] <9>

R_A_MA[0..13] <9,10>

R_A_SCASA# <9,10>

R_A_SRASA# <9,10>

R_A_BMWEA# <9,10>

R_B_MD[0..63]<9>

T77T77 T75T75

T80T80

R_B_MD0

R_B_MD1

R_B_MD2

R_B_MD3

R_B_MD4

R_B_MD5

R_B_MD6

R_B_MD7

R_B_MD8

R_B_MD9

R_B_MD10

R_B_MD11

R_B_MD12

R_B_MD13

R_B_MD14

R_B_MD15

R_B_MD16

R_B_MD17

R_B_MD18

R_B_MD19

R_B_MD20

R_B_MD21

R_B_MD22

R_B_MD23

R_B_MD24

R_B_MD25

R_B_MD26

R_B_MD27

R_B_MD28

R_B_MD29

R_B_MD30

R_B_MD31

R_B_MD32

R_B_MD33

R_B_MD34

R_B_MD35

R_B_MD36R_A_MD36

R_B_MD37

R_B_MD38

R_B_MD39

R_B_MD40

R_B_MD41

R_B_MD42

R_B_MD43

R_B_MD44

R_B_MD45

R_B_MD46

R_B_MD47

R_B_MD48

R_B_MD49

R_B_MD50

R_B_MD51

R_B_MD52

R_B_MD53

R_B_MD54

R_B_MD55

R_B_MD56

R_B_MD57

R_B_MD58

R_B_MD59

R_B_MD60

R_B_MD61

R_B_MD62

R_B_MD63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U34G

U34G

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

@ALVISO_GM/GML

@ALVISO_GM/GML

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

R_B_BS0#

R_B_BS1#

R_B_BS2#

R_B_DM0

R_B_DM1

R_B_DM2

R_B_DM3

R_B_DM4

R_B_DM5

R_B_DM6

R_B_DM7

R_B_DQS0

R_B_DQS1

R_B_DQS2

R_B_DQS3

R_B_DQS4

R_B_DQS5

R_B_DQS6

R_B_DQS7

R_B_DQS#0

R_B_DQS#1

R_B_DQS#2

R_B_DQS#3

R_B_DQS#4

R_B_DQS#5

R_B_DQS#6

R_B_DQS#7

R_B_MA0

R_B_MA1

R_B_MA2

R_B_MA3

R_B_MA4

R_B_MA5

R_B_MA6

R_B_MA7

R_B_MA8

R_B_MA9

R_B_MA10

R_B_MA11

R_B_MA12

R_B_MA13

R_B_SCASA#

R_B_SRASA#

SB_RCVENIN#

SB_RCVENOUT#

R_B_BMWEA#

R_B_BS0# <9,10>

R_B_BS1# <9,10>

R_B_BS2# <9,10>

R_B_DM[0..7] <9>

R_B_DQS[0..7] <9>

R_B_DQS#[0..7] <9>

R_B_MA[0..13] <9,10>

R_B_SCASA# <9,10>

R_B_SRASA# <9,10>

R_B_BMWEA# <9,10>