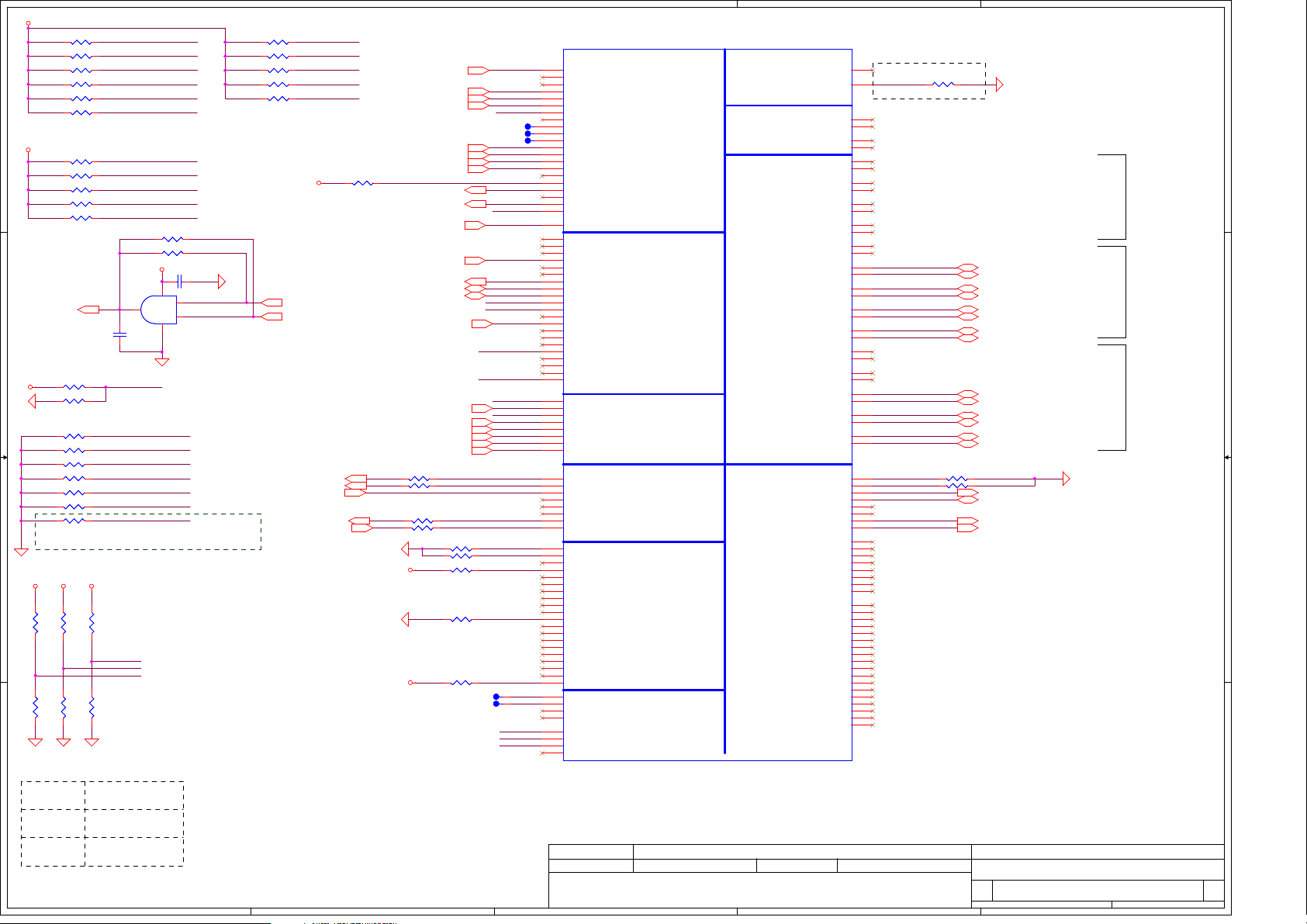

Acer Aspire 5253 Laptop Schematics

A

1 1

B

C

D

E

Compal Confidential

2 2

JE50/HM50/SJV50_BZ

P5WE6/P5WH6/P5WS6 Schematics Document

AMD Brazos

Brazos with Zacate / Hudson M1 / Seymour XT

3 3

DIS only / UMA only / PX Muxless / PX Muxless with BACO

ZZZ

2010-11-16

LA-7092P REV: 1.0

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

ZZZ

PCB

PCB

Part Number = DAZ0IC00100

Part Number = DAZ0IC00100

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

E

1.0

1.0

1 47Tuesday, November 16, 2010

1 47Tuesday, November 16, 2010

1 47Tuesday, November 16, 2010

1.0

A

B

C

D

E

Compal Confidential

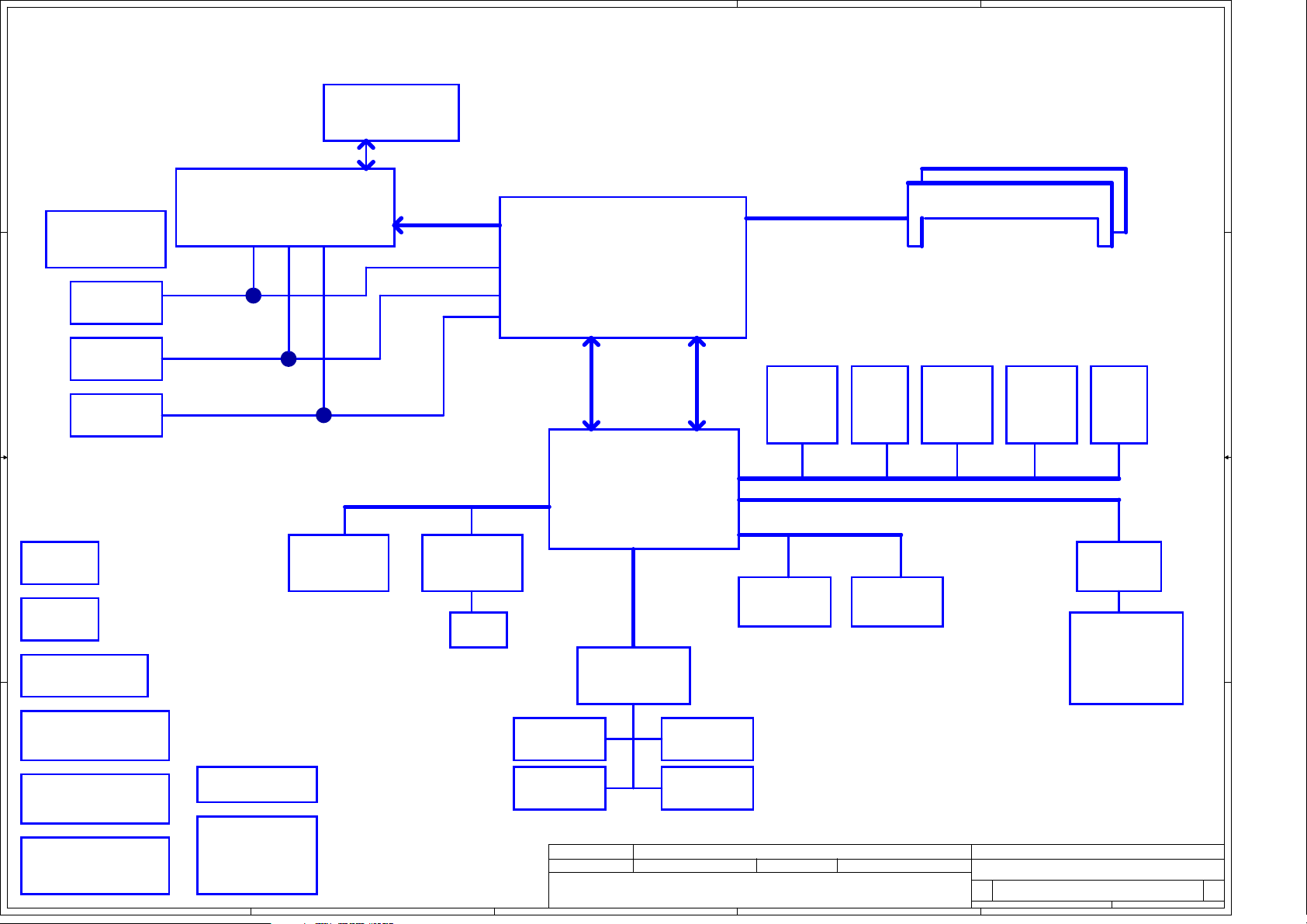

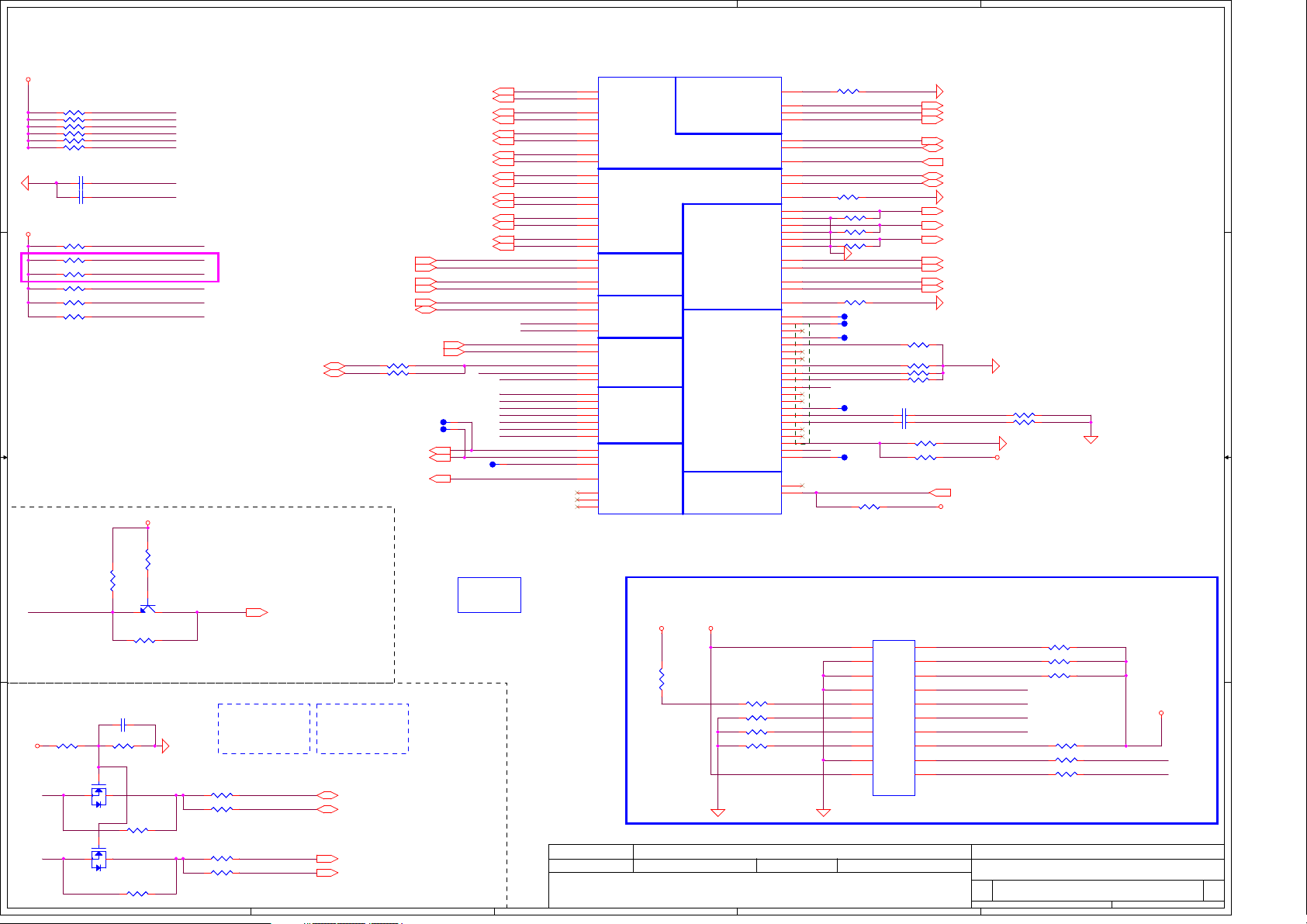

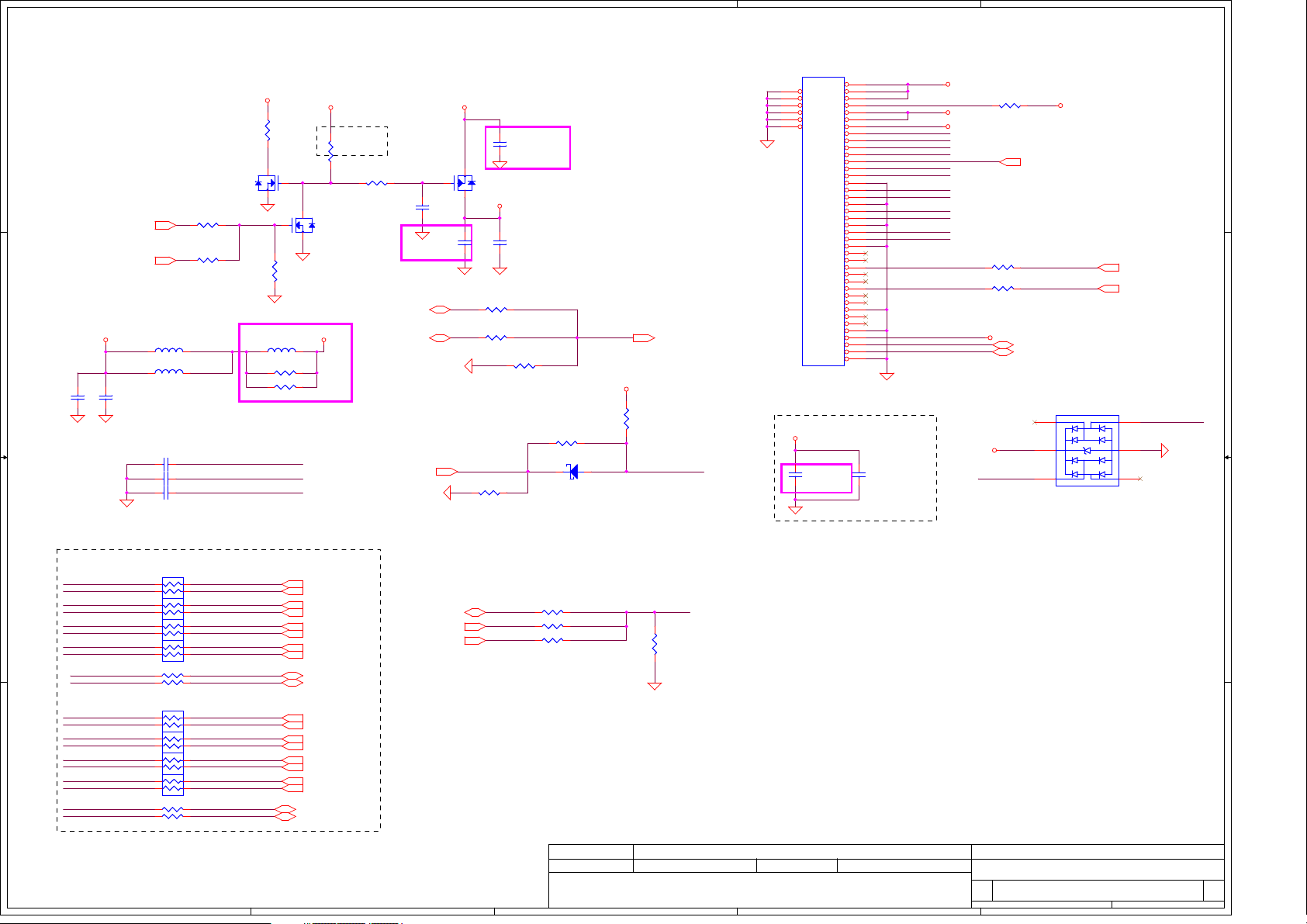

Model Name : P5WE6/P5WH6/P5WS6

JE50/HM50/SJV50_BZ

1 1

PCB PN : DAZ0IC00100

VRAM 512M/1G

64M16/128M16 x 4

page 23

DDR3

Brazos

Vancuver Seymour

ATI

Thermal Sensor

ADM1032

page 19

Page 18,19,20,21,22

LVDS

page 10

uFCBGA-962

2 2

CRT

page 12

PCI-Express x 4

Gen2

DP0

DP1

AMD Brazos APU

FT1

BGA 413-Ball

19mm x 19mm

page 5,6,7

UMI Gen.1 x4

PCI-Express

HDMI

Conn.

page 11

2.5GT/s per lane

Memory BUS(DDR3)

Single Channel

1.5V DDRIII 800~1066MHz

USB port 0,1,2

USB

Conn x 3

page 33 page 10 page 33

USB port 5 USB port 7

CMOS

Camera

204pin DDRIII-SO-DIMM X2

USB port6

Card

Reader

RT5137

page 29

page 8,9

USB port 8

BANK 0, 1, 2, 3

Bluetooth

Conn

Mini

card

(WL)X1

page 29

FCH

Hudson-M1

BGA 605-Ball

3.3V 48MHz

3.3V 24.576MHz/48Mhz

23mm x 23mm

page 30

port 0

Gen2

SATA ODD

Sub/B

LED

3 3

page 32

MINI Card

WLAN

page 29

RTC CKT.

page 13

LAN(GbE)

Atheros

AR8151

page 26

GPP2GPP3

RJ45

page 26

LPC BUS

Power On/Off CKT.

page 34

page 13,14,15,16,17

ENE KB930

page 31

S-ATA

SATA HDD

Conn.

HD Audio

page 30

port 1

USB

HDA Codec

CX20584

page 27

MIC Jack x 1

HP Jack x 1

Int MIC x 1

Int SPK x 1

page 28

Power sequence

VGA

DC/DC

page 24,25

DC/DC Interface CKT.

4 4

page 35

Fan Control

page 34

Touch Pad

page 32

EC I/O Buffer

page 32

Int.KBD

page 32

BIOS

page 32

Extend Card/B

Security Classification

Security Classification

Power Circuit

page 36,37,38,39,40,41

42,43,44,45

A

1. USB X2

2. ODD X1

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

E

1.0

1.0

2 47Monday, November 15, 2010

2 47Monday, November 15, 2010

2 47Monday, November 15, 2010

1.0

A

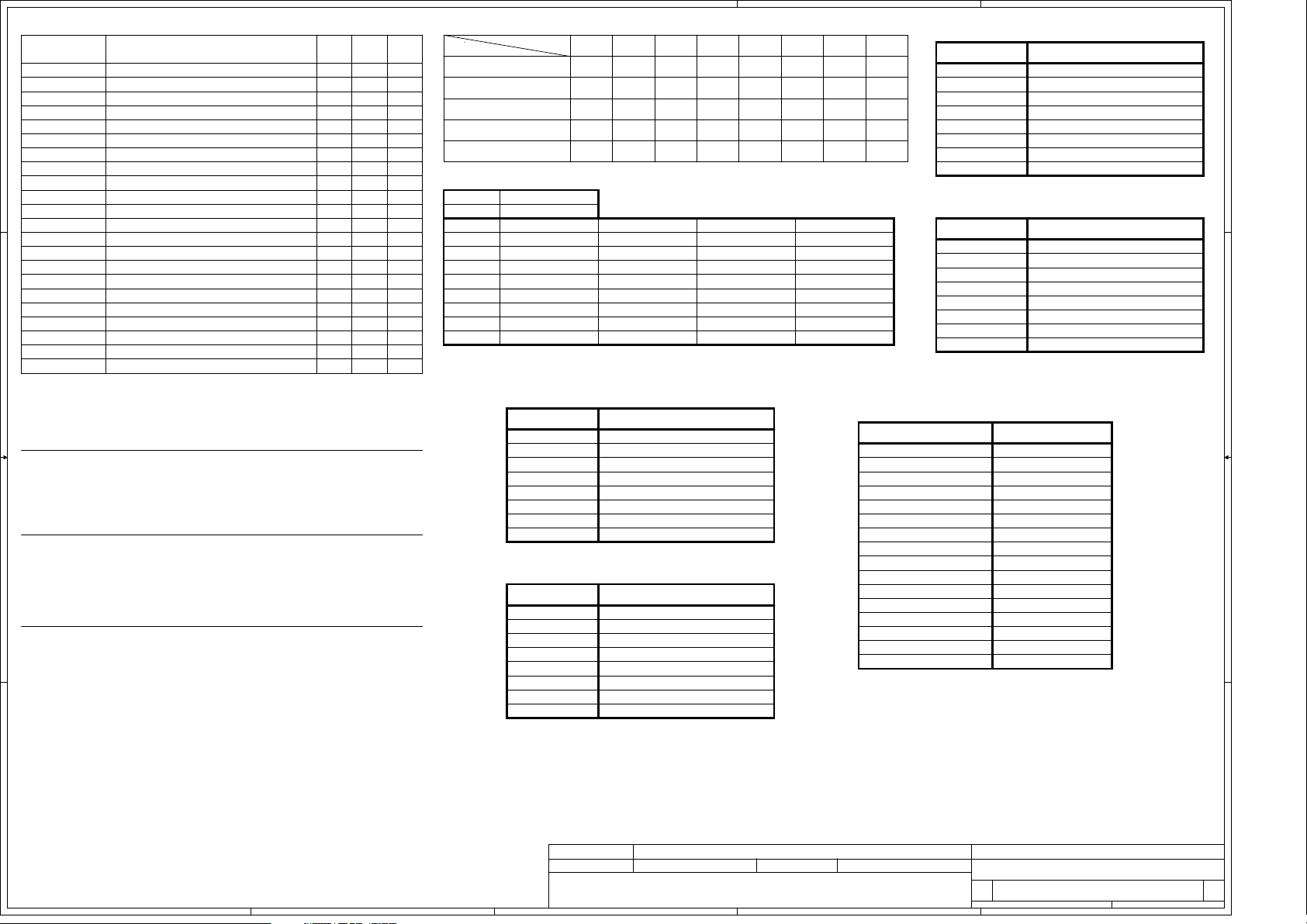

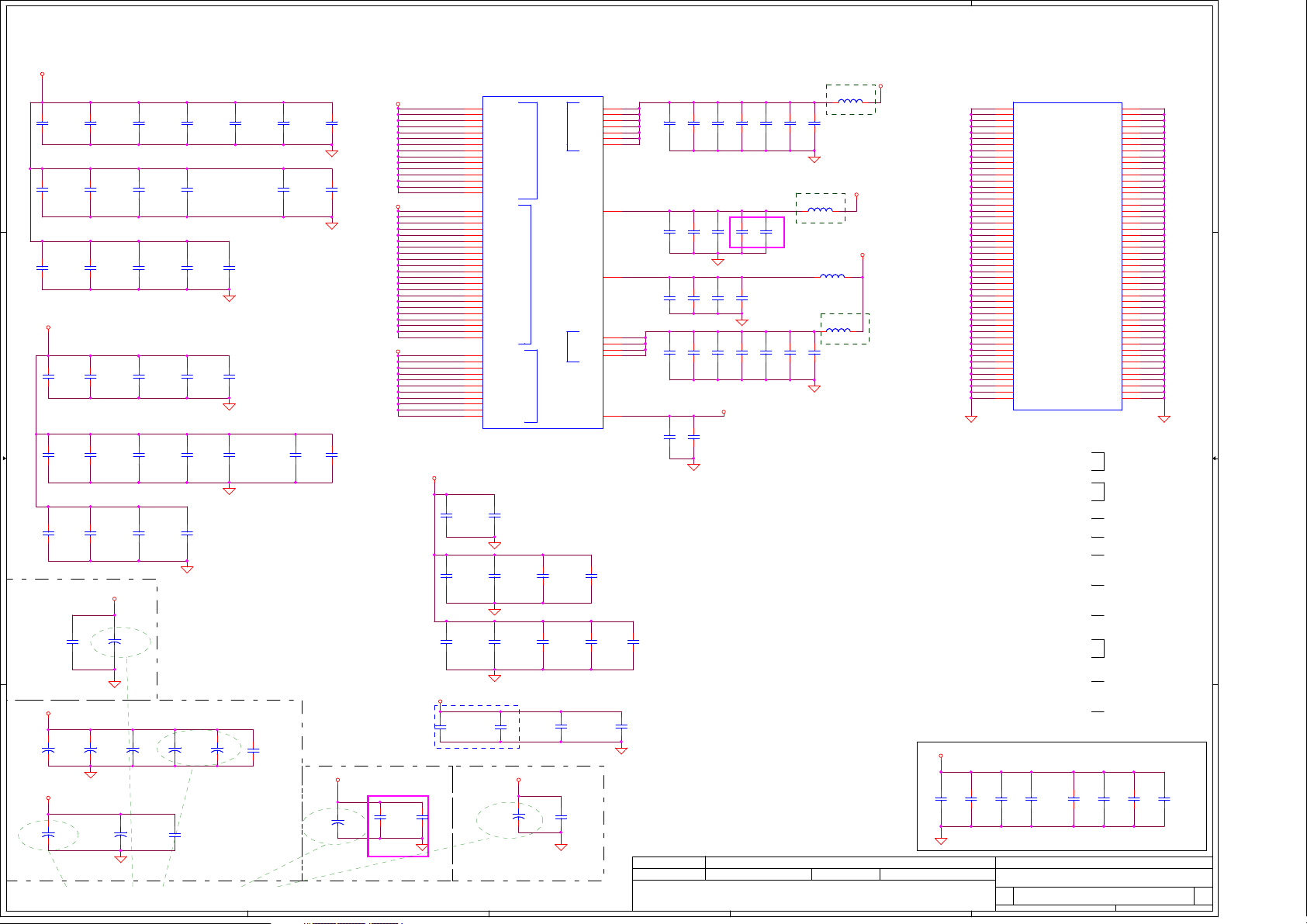

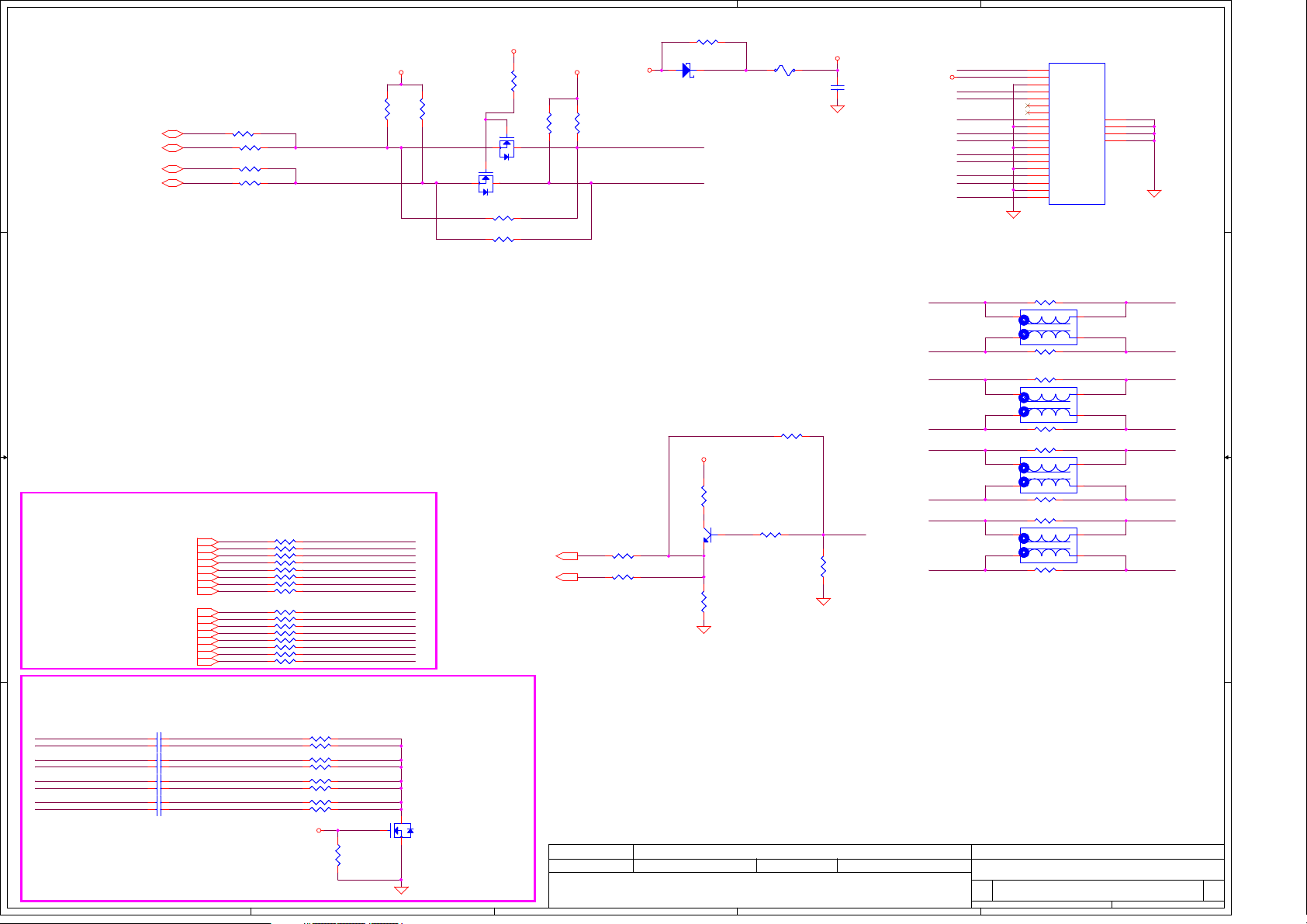

Voltage Rails

Power Plane Description

VIN

B+

+VSB VSB always on power rail ON ON*ON

1 1

+APU_CORE_NB

+1.5V 1.5V power rail for CPU VDDIO and DDRIII ON OFF

+0.75VS 0.75VS switched power rail for DDR terminator

+1.05VS

+1.1VS 1.1VS switched power rail ON OFF OFF

+VGA_CORE Core voltage for GPU ON OFF OFF

+1.5VSG 1.5V switched power rail for GPU ON OFF OFF

+1.0VSG 1.0V switched power rail for GPU ON OFF OFF

2 2

+3V_LAN 3.3V power rail for LAN ON ON

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

EC SM Bus1 address

Device

SM Bus Controller 0

Device Address

APU SIC/SID (FCH_SMB3)

3 3

H_THERMTRIP# (FCH_ALERT#)

SM Bus Controller 1

Device Address HEX

DDR DIMM1 (FCH_SMB0)

DDR DIMM2 (FCH_SMB0)

WLAN (FCH_SMB0 )

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU (0.7-1.2V) ON+APU_CORE

1.0V switched power rail

1.05V switched power rail for APU VDD10 ON OFF OFF

EC SM Bus2 address

Address Address

(FCH_SMB1 ~ FCH_SMB4, SMB_AL ERT#)

(FCH_SMB0)

1001-000xb

1001-001xb

DeviceHEX

ADM1032 (GPU) 1001-101xb

HEX

90

92

B

S1 S3 S5

N/A N/A N/A

ON ON ON*+3VALW 3.3V always on power rail

ON ON ON*+5VALW 5V always on power rail

ON OFF

ON OFF

ON OFF+1.8VS 1.8V switched power rail OFF

ON+RTCVCC RTC power ON ON

N/AN/AN/A

ON ON*+1.1VALW 1.1V always on power rail ON

OFF

OFF

OFF

ON

OFF

OFFON OFF+3VS 3.3V switched power rail

OFFON OFF+5VS 5V switched power rail

OFF+3VSG 3.3V switched power rail for GPU ON OFF

OFF+1.8VSG 1.8V switched power rail for GPU ON OFF

ON

HEX

9AH

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

w/ X'tal X1

wo/ X'tal X1

Project ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

ON

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

V typ

AD_BID

V

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

*UMA only :

D

BOARD ID Table

ON ON

ON

OFF

OFF

OFF

LOW

OFF

OFF

OFF

Board ID

0

1

2

3

4

5

6

7

Project ID Table

max

Board ID

0

1

2

3

4

5

6

7

BTO Option Table

BTO Item BOM Structure

Display from APU

Display from VGA

Use VGA

Muxless w/BACO

Muxless wo/BACO WOBACO@

Muxless

w/Vancouver Serise

w/Manhttan Serise MAN@

Bluetooth BT@

AR8151 8151@

Seymour

wo/Muxless

wo/VGA WOVGA@

APU 1.5G

APU 1.6G

UMA@

BT@ 8151@

WOVGA@ WOPX@

E

PCB Revision

PCB Revision

UMA@

DISO@

VGA@

BACO@

PX@

VAN@

Seymour@

WOPX@

15G@

16G@

VGA Chip SEL:

1. Seymour@ + Van@

2. Robson@ + Man@

*DIS only :

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

*Muxless w/BACO :

Muxless wo/BACO :

Deciphered Date

Deciphered Date

Deciphered Date

D

APU Chip SEL:

1. 16G@

2. 15G@

DISO@VGA@

UMA@

UMA@

WOBACO@

VGA@ BACO@PX@

VGA@ WOBACO@PX@

Date: Sheet of

Date: Sheet of

Date: Sheet of

BT@ 8151@

WOPX@

BT@ 8151@

BT@ 8151@

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

E

3 4 7Tuesday, November 16, 2010

3 4 7Tuesday, November 16, 2010

3 4 7Tuesday, November 16, 2010

1.0

1.0

1.0

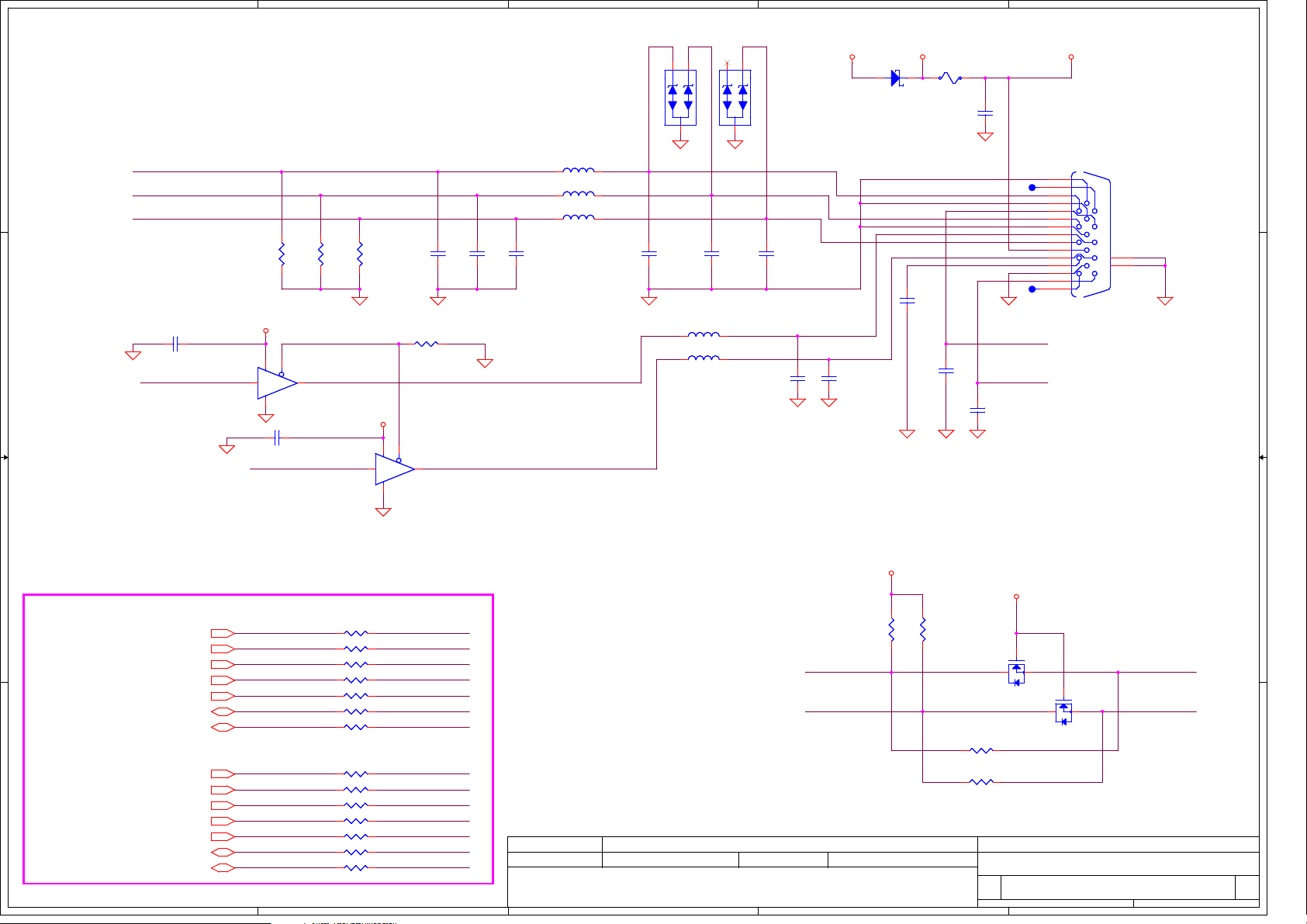

5

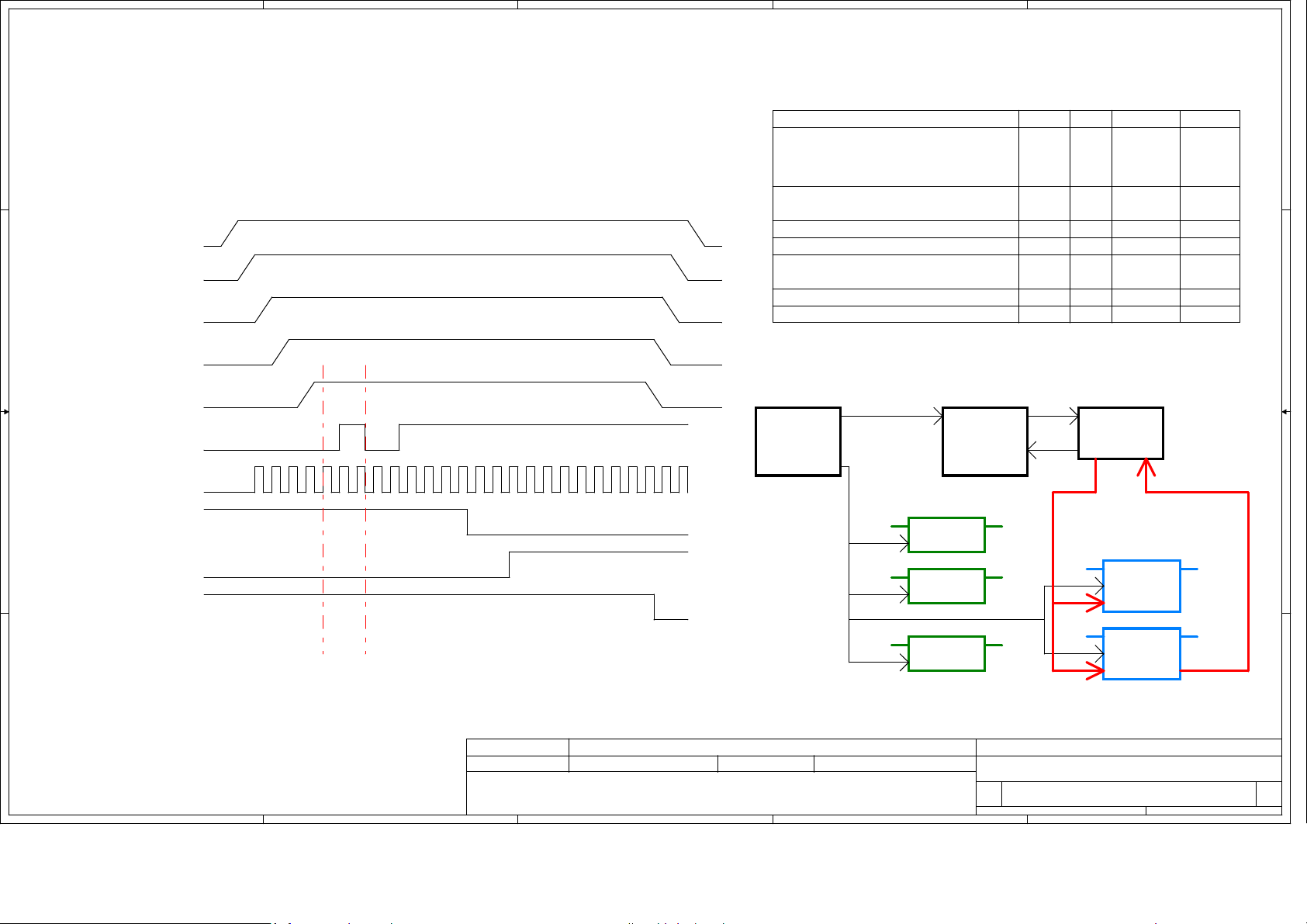

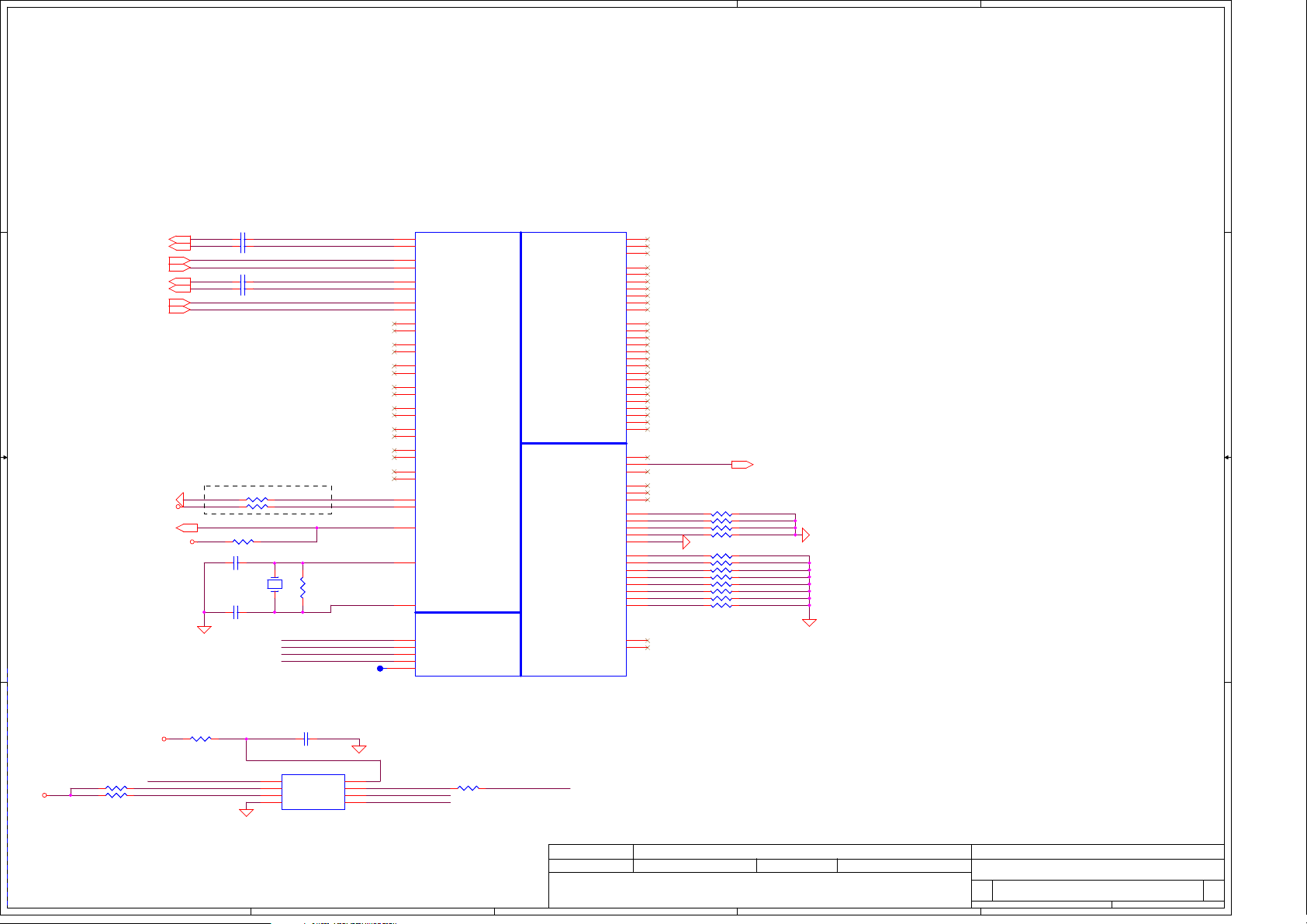

Power-Up/Down Sequence

1. All the ASIC supplies must fully reach their respective nominal voltages within 20 ms of the start of the ramp-up

sequence, though a shorter ramp-up duration is preferred.

2. VDDR3 should ramp-up before or simultaneously with VDDC.

3. For LVDS, DPx_VDD10 should ramp-up before DPx_VDD18 and the PCIe Reference clock should begin before

D D

DPx_VDD18. For power-down, DPx_VDD18 should ramp-down before DPx_VDD10.

4. The external pull-ups on the DDC/AUX signals (if applicable) should ramp-up before or after both VDDC and

VDD_CT have ramped up.

5.VDDC and VDD_CT should not ramp-up simultaneously. (e.g., VDDC should reach 90% before VDD_CT starts to

ramp-up (or vice versa).)

4

3

2

1

Without BACO option :

PE_GPIO0 : Low -> Reset dGPU ; High ->Normal operation

PE_GPIO1 : Low -> dGPU Power OFF ; High -> dGPU Power ON

BACO option :

PE_GPIO0 : High ->Normal operation (dGPU is not reseton BACO mode)

PE_GPIO1 : Low -> dGPU Power OFF ; High -> dGPU Power ON (always High)

dGPU Power Pins Max current

PCIE_PVDD, PCIE_VDDR, TSVDD, VDDR4, VDD_CT,

DPE_PVDD, DP[F:E]_VDD18, DP[D:A]_PVDD,

DP[D:A]_VDD18, AVDD, VDD1DI, A2VDDQ, VDD2DI,

DPLL_PVDD, MPV18, and SPV18

DP[F:E]_VDD10, DP[D:A]_VDD10, DPLL_VDDC, and

Voltage

1.8V

1.0V

PX 3.0

OFF

OFF

BACO Mode

ON

ON

1679mA

575mA

SPV10

VDDR3(3.3VSG)

Note: Do not drive any IOs before VDDR3 is ramped up.

PCIE_VDDC

VDDR3 , and A2VDD

BIF_VDDC (current consumption = 55mA@1.0V, in

PCIE_VDDC(1.0V)

BACO mode)

VDDR1

C C

VDDR1(1.5VSG)

VDDC/VDDCI

1.0V

3.3V

Same as

VDDC

1.5V

1.12V

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

Same as

PCIE_VDDC

OFF

OFF

2A

190mA

70mA

2.8A

12.9A

VDDC/VDDCI(1.12V)

VDD_CT(1.8V)

iGPU

PERSTb

REFCLK

B B

Straps Reset

Straps Valid

PE_GPIO0 PE_EN

dGPU

BIF_VDDC

PE_GPIO1

+3.3VALW

+1.0V

MOS

Regulator

+3.3VSG

1

+1.0VSG

2

PX_mode

+1.5V

BACO Switch

SI4800

+1.5VSG

3

Global ASIC Reset

+B

+1.8V

T4+16clock

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SI4800

2

+1.8VSG

5

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

Regulator

dGPU Block Diagram

dGPU Block Diagram

dGPU Block Diagram

4

1

+VGA_CORE

PWRGOOD

4 47Monday, November 15, 2010

4 47Monday, November 15, 2010

4 47Monday, November 15, 2010

1.0

1.0

1.0

5

4

3

2

1

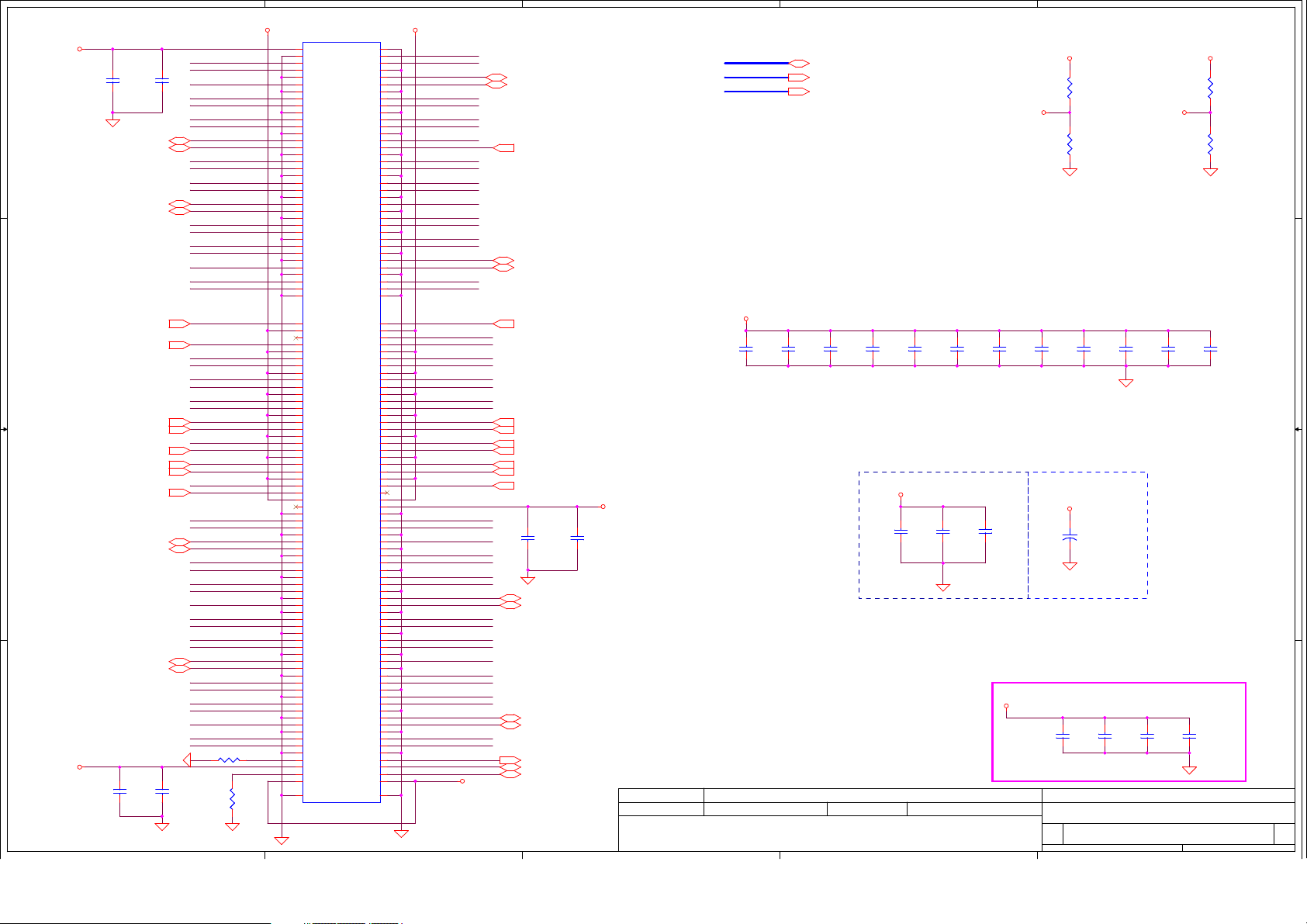

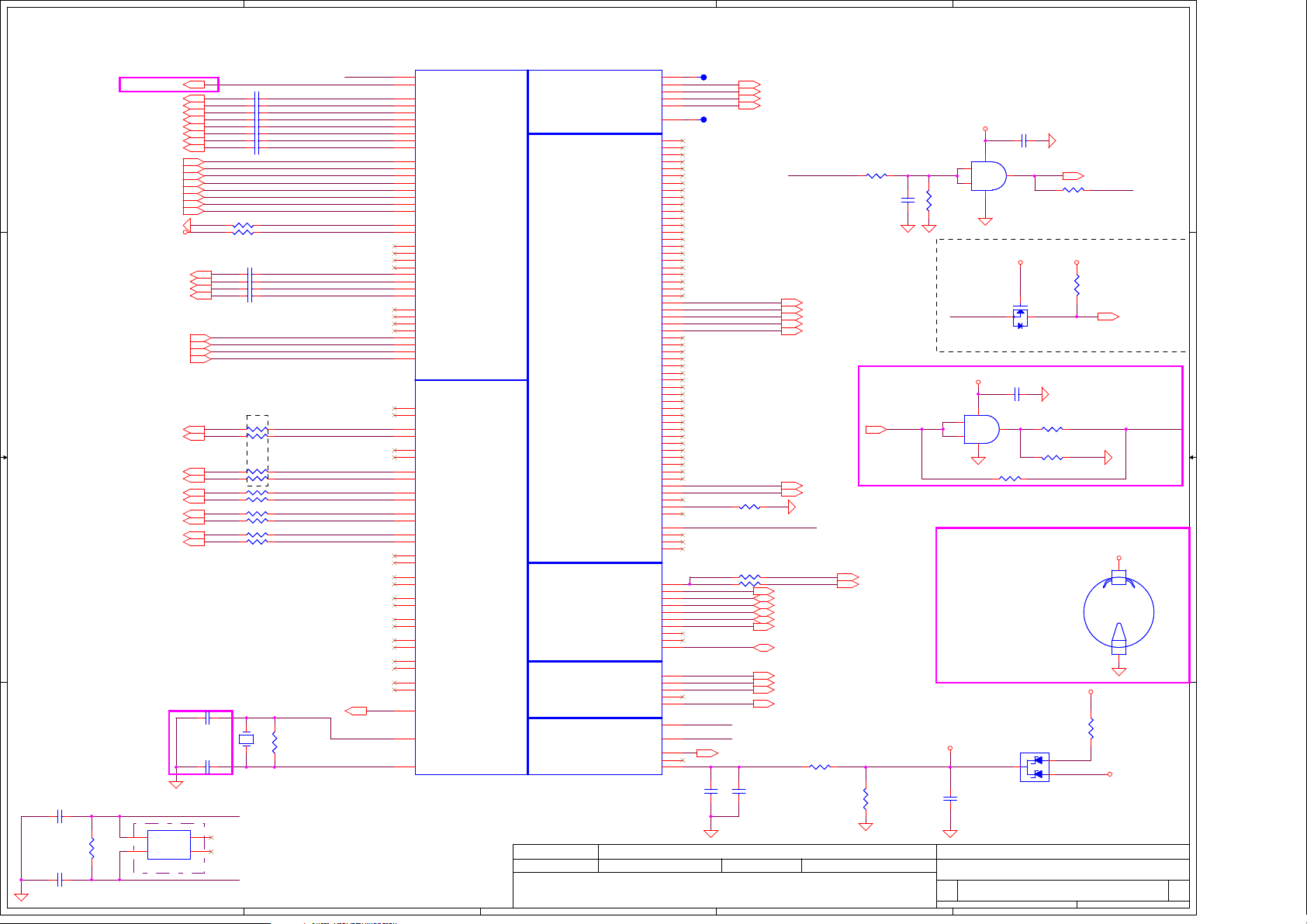

+1.8VS

APU_HDMI_TX2P<11>

APU_RST#<13>

APU_PWRGD<13>

APU_HDMI_TX2N<11>

APU_HDMI_TX1P<11>

APU_HDMI_TX1N<11>

APU_HDMI_TX0P<11>

APU_HDMI_TX0N<11>

APU_HDMI_CLKP<11>

APU_HDMI_CLKN<11>

APU_TXOUT2+<10>

APU_TXOUT2-<10>

APU_TXOUT1+<10>

APU_TXOUT1-<10>

APU_TXOUT0+<10>

APU_TXOUT0-<10>

APU_TXCLK+<10>

APU_TXCLK-<10>

T93PADT93PAD

T94PADT94PAD

Close to APU

APU_SIC

APU_SID

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#_R

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

T77PADT77PAD

APU : SA00004DO60 (S IC ZACATE 2M151132B1240 1.5G BGA)

APU : SA000046G80 (S IC ZACATE 2M161232B2240 1.6G BGA )

U22

16G@U22

16G@

Zacate FT1 B0

Zacate FT1 B0

R399 1K_0402_5%R399 1K_0402_5%

1 2

R400 1K_0402_5%R400 1K_0402_5%

D D

C C

B B

1 2

R142 300_0402_5%

R142 300_0402_5%

R401 300_0402_5%R401 300_0402_5%

R402 510_0402_1%R402 510_0402_1%

R141 1K_0402_5%R141 1K_0402_5%

+3VS

R410 1K_0402_5%R410 1K_0402_5%

R109 4.7K_0402_5%UMA@R109 4.7K_0402_5%UMA@

R155 4.7K_0402_5%UMA@R155 4.7K_0402_5%UMA@

R411 1K_0402_5%R411 1K_0402_5%

R143 1K_0402_5%R143 1K_0402_5%

R414 1K_0402_5%R414 1K_0402_5%

APU_THERMTRIP#

If FCH internal pull-up disabl ed, level-shift er could be del eted.

Need BIOS to di sable internal pull-up!!

12

12

1 2

1 2

C237 0.01U_0402_25V7K

C237 0.01U_0402_25V7K

@

@

1 2

C238 0.01U_0402_25V7K

C238 0.01U_0402_25V7K

@

@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R425

R425

1K_0402_5%

1K_0402_5%

APU_SVC

APU_SVD

APU_RST#

APU_PWRGD

TEST_25_L

TEST36

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_CRT_DDC_SCL

APU_CRT_DDC_SDA

APU_ALERT#_R

APU_SIC

APU_SID

+3VS

12

R424

R424

10K_0402_5%

10K_0402_5%

B

B

2

1 2

Q79

Q79

E

E

3 1

C

C

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

1 2

R427 0_0402_5%@R427 0_0402_5%@

For DVT 1011

EC_THERM#<31>

FCH_PROCHOT#<13>

H_THERMTRIP# < 14>

APU_CLKP<13>

APU_CLKN<13>

APU_DISP_CLKP<13>

APU_DISP_CLKN<13>

APU_SVC<44>

APU_SVD<44>

R169 0_0402_5%R169 0_0402_5%

1 2

R168 0_0402_5%@R168 0_0402_5%@

1 2

APU_VDDNB_RUN_FB_ H<44>

APU_VDD0_RUN_FB_H<44>

APU_VDD0_RUN_FB_L<44>

CPU TSI interface level shift

@

@

C236 0.1U_0402_10V7K

C236 0.1U_0402_10V7K

@

@

R428

R428

1 2

+3VS

31.6K_0402_1%

31.6K_0402_1%

A A

1 2

@

@

R160

R160

1 2

30K_0402_1%

30K_0402_1%

G

G

2

13

D

S

D

S

@

@

Q22

Q22

BSH111 1N_SOT23-3

BSH111 1N_SOT23-3

1 2

R431 0_0402_5%R431 0_0402_5%

G

G

2

13

D

S

D

S

@

@

Q23

Q23

BSH111 1N_SOT23-3

BSH111 1N_SOT23-3

1 2

R434 0_0402_5%R434 0_0402_5%

5

EC_SMB_DAAPU_SID

EC_SMB_CKAPU_SIC

BSH111, the Vgs is:

min = 0.4V

Typ = 1.0V

Max = 1.3V

1.607V for Gate

@

@

1 2

R429 0_0402_5%

R429 0_0402_5%

1 2

R430 0_0402_5%R430 0_0402_5%

@

@

1 2

R432 0_0402_5%

R432 0_0402_5%

1 2

R433 0_0402_5%R433 0_0402_5%

FDV301N, the Vgs is:

min = 0.65V

Typ = 0.85V

Max = 1.5V

If use level sh ift, EC_SMB nee d pull up

(pop R747 & R74 8)

FCH_SID

EC_SMB_DA2

FCH_SIC

EC_SMB_CK2

FCH_SID <14>

EC_SMB_DA2 <19,31>

FCH_SIC <14>

EC_SMB_CK2 <19,31>

4

T0 FCH

TO EC

T0 FCH

TO EC

U22B

U22B

A8

TDP1_TXP0

B8

TDP1_TXN0

B9

TDP1_TXP1

A9

TDP1_TXN1

D10

TDP1_TXP2

C10

TDP1_TXN2

A10

TDP1_TXP3

B10

TDP1_TXN3

B5

LTDP0_TXP0

A5

LTDP0_TXN0

D6

LTDP0_TXP1

C6

LTDP0_TXN1

A6

LTDP0_TXP2

B6

LTDP0_TXN2

D8

LTDP0_TXP3

C8

LTDP0_TXN3

V2

CLKIN_H

V1

CLKIN_L

D2

DISP_CLKIN_H

D1

DISP_CLKIN_L

J1

SVC

J2

SVD

P3

SIC

P4

SID

T3

RESET_L

T4

PWROK

U1

PROCHOT_L

U2

THERMTRIP_L

T2

ALERT_L

N2

TDI

N1

TDO

P1

TCK

P2

TMS

M4

TRST_L

M3

DBRDY

M1

DBREQ_L

F4

VDDCR_NB_SENSE

G1

VDDCR_CPU_SENSE

F3

VDDIO_MEM_S_SENSE

F1

VSS_SENSE

B4

RSVD_1

W11

RSVD_2

V5

RSVD_3

ONTARIO-2M161000-1.6G_BGA413

ONTARIO-2M161000-1.6G_BGA413

15G@

15G@

DP_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP MISC

DP MISC

TDP1_AUXP

VGA DAC

VGA DAC

TEST

TEST

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_REDB

DAC_GREEN

DAC_GREENB

DAC_BLUE

DAC_BLUEB

DAC_HSYNC

DAC_VSYNC

DAC_SCL

DAC_SDA

DAC_ZVSS

TEST4

TEST5

TEST6

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST31

TEST33_H

TEST33_L

TEST34_H

TEST34_L

TEST35

TEST36

TEST37

TEST38

DMAACTIVE_L

DISPLAYPORT 1

DISPLAYPORT 1

DISPLAYPORT 0

DISPLAYPORT 0

CLK

CLK

SER

SER

JTAG CTRL

JTAG CTRL

R398 150_0402_1%R398 150_0402_1%

H3

1 2

G2

H2

H1

APU_HDMI_CLK

B2

APU_HDMI_DATA

C2

C1

APU_LCD_CLK

A3

APU_LCD_DATA

B3

R406 100K_0402_5%R406 100K_0402_5%

D3

1 2

C12

R407 150_0402_1%R407 150_0402_1%

D13

A12

B12

A13

B13

E1

E2

F2

D4

D12

R1

R2

R6

T5

E4

K4

L1

L2

M2

K1

K2

L5

M5

M21

J18

J19

U15

T15

H4

N5

R5

K3

T1

1 2

R408 150_0402_1%R408 150_0402_1%

1 2

R409 150_0402_1%R409 150_0402_1%

1 2

R144 499_0402_1%R144 499_0402_1%

1 2

T66

T66

PAD

PAD

T67

T67

PAD

PAD

T68

T68

PAD

PAD

TEST15

TEST18

TEST19

TEST25_H

TEST_25_L

TEST31

TEST33_H

TEST33_L

Delete Test point for layout limitation

20100917

TEST35

TEST36

TEST37

R423 1K_0402_5%R423 1K_0402_5%

R415 1K_0402_5%@R415 1K_0402_5%@

R416 1K_0402_5%R416 1K_0402_5%

R417 1K_0402_5%R417 1K_0402_5%

R418 510_0402_1%R418 510_0402_1%

T73

T73

PAD

PAD

C516 0.1U_0402_16V4ZC516 0.1U_0402_16V4Z

C517 0.1U_0402_16V4ZC517 0.1U_0402_16V4Z

T76

T76

PAD

PAD

1 2

APU_ENBKL <10>

APU_ENVDD <10>

APU_BLPWM <10>

APU_HDMI_CLK <11>

APU_HDMI_DATA <11>

APU_HDMI_HPD <11>

APU_LCD_CLK <10>

APU_LCD_DATA <10>

APU_CRT_R <12>

APU_CRT_G <12>

APU_CRT_B <12>

APU_CRT_HSYNC <12>

APU_CRT_VSYNC <12>

APU_CRT_DDC_SCL <12>

APU_CRT_DDC_SDA <12>

1 2

1 2

1 2

1 2

1 2

1 2

R422 1K_0402_5%@R422 1K_0402_5%@

1 2

R958 1K_0402_5%R958 1K_0402_5%

1 2

ALLOW_STOP# <13>

+1.8VS

AMD Debug

+1.8VS +1.8VS

R842

R842

1K_0402_5%

1K_0402_5%

1 2

APU_TRST#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

0_0402_5%

0_0402_5%

R846

R846

R847 10K_0402_5%R847 10K_0402_5%

R176 10K_0402_5%R176 10K_0402_5%

R177 10K_0402_5%R177 10K_0402_5%

APU_TRST#_R

1 2

12

12

12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

JHDT1

JHDT1

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

SAMTE_ASP-136446-07-B

SAMTE_ASP-136446-07-B

CONN@

CONN@

2

APU_TCK

2

APU_TMS

4

APU_TDI

6

APU_TDO

8

APU_PWRGD

10

APU_RST#

12

APU_DBRDY

14

APU_DBREQ#

16

J108_PLLTST0

18

J108_PLLTST1

20

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

R420 51_0402_1%R420 51_0402_1%

1 2

R421 51_0402_1%R421 51_0402_1%

1 2

+1.8VS

R843 1K_0402_5%R843 1K_0402_5%

R840 1K_0402_5%R840 1K_0402_5%

R798 1K_0402_5%R798 1K_0402_5%

R178 300_0402_5%R178 300_0402_5%

R799 0_0402_5%R799 0_0402_5%

R863 0_0402_5%R863 0_0402_5%

1 2

1 2

1 2

12

12

12

+1.8VS

TEST19

TEST18

Please be noted about TEST_18 and TEST_19

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Compal Electronics, Inc.

FT1 CTRL/DP/CRT

FT1 CTRL/DP/CRT

FT1 CTRL/DP/CRT

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

5 47Wednesday, November 24, 2010

5 47Wednesday, November 24, 2010

5 47Wednesday, November 24, 2010

1

1.0

1.0

1.0

A

U22E

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

4 4

3 3

2 2

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS0<8,9>

DDR_A_BS1<8,9>

DDR_A_BS2<8,9>

DDR_A_DQS0<8,9>

DDR_A_DQS#0<8,9>

DDR_A_DQS1<8,9>

DDR_A_DQS#1<8,9>

DDR_A_DQS2<8,9>

DDR_A_DQS#2<8,9>

DDR_A_DQS3<8,9>

DDR_A_DQS#3<8,9>

DDR_A_DQS4<8,9>

DDR_A_DQS#4<8,9>

DDR_A_DQS5<8,9>

DDR_A_DQS#5<8,9>

DDR_A_DQS6<8,9>

DDR_A_DQS#6<8,9>

DDR_A_DQS7<8,9>

DDR_A_DQS#7<8,9>

DDR_A_CLK0<8>

DDR_A_CLK#0<8>

DDR_A_CLK1<8>

DDR_A_CLK#1<8>

DDR_B_CLK2<9>

DDR_B_CLK#2<9>

DDR_B_CLK3<9>

DDR_B_CLK#3<9>

DDR_RST#<8,9>

DDR_EVENT#<8,9>

DDR_CKE0<8,9>

DDR_CKE1<8,9>

DDR_A_ODT0< 8>

DDR_A_ODT1< 8>

DDR_B_ODT0< 9>

DDR_B_ODT1< 9>

DDR_CS0_DIMMA#<8>

DDR_CS1_DIMMA#<8>

DDR_CS0_DIMMB#<9>

DDR_CS1_DIMMB#<9>

DDR_A_RAS#<8,9>

DDR_A_CAS#<8,9>

DDR_A_WE#<8,9>

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

DDR_RST#

DDR_EVENT#

DDR_CKE0

DDR_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_B_ODT0

DDR_B_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

U22E

R17

M_ADD0

H19

M_ADD1

J17

M_ADD2

H18

M_ADD3

H17

M_ADD4

G17

M_ADD5

H15

M_ADD6

G18

M_ADD7

F19

M_ADD8

E19

M_ADD9

T19

M_ADD10

F17

M_ADD11

E18

M_ADD12

W17

M_ADD13

E16

M_ADD14

G15

M_ADD15

R18

M_BANK0

T18

M_BANK1

F16

M_BANK2

D15

M_DM0

B19

M_DM1

D21

M_DM2

H22

M_DM3

P23

M_DM4

V23

M_DM5

AB20

M_DM6

AA16

M_DM7

A16

M_DQS_H0

B16

M_DQS_L0

B20

M_DQS_H1

A20

M_DQS_L1

E23

M_DQS_H2

E22

M_DQS_L2

J22

M_DQS_H3

J23

M_DQS_L3

R22

M_DQS_H4

P22

M_DQS_L4

W22

M_DQS_H5

V22

M_DQS_L5

AC20

M_DQS_H6

AC21

M_DQS_L6

AB16

M_DQS_H7

AC16

M_DQS_L7

M17

M_CLK_H0

M16

M_CLK_L0

M19

M_CLK_H1

M18

M_CLK_L1

N18

M_CLK_H2

N19

M_CLK_L2

L18

M_CLK_H3

L17

M_CLK_L3

L23

M_RESET_L

N17

M_EVENT_L

F15

M_CKE0

E15

M_CKE1

W19

M0_ODT0

V15

M0_ODT1

U19

M1_ODT0

W15

M1_ODT1

T17

M0_CS_L0

W16

M0_CS_L1

U17

M1_CS_L0

V16

M1_CS_L1

U18

M_RAS_L

V19

M_CAS_L

V17

M_WE_L

ONTARIO-2M161000-1.6G _BGA413

ONTARIO-2M161000-1.6G _BGA413

15G@

15G@

DDR SYSTEM MEMORY

DDR SYSTEM MEMORY

B

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_VREF

M_ZVDDIO_MEM_S

B14

A15

A17

D18

A14

C14

C16

D16

C18

A19

B21

D20

A18

B18

A21

C20

C23

D23

F23

F22

C22

D22

F20

F21

H21

H23

K22

K21

G23

H20

K20

K23

N23

P21

T20

T23

M20

P20

R23

T22

V20

V21

Y23

Y22

T21

U23

W23

Y21

Y20

AB22

AC19

AA18

AA23

AA20

AB19

Y18

AC17

Y16

AB14

AC14

AC18

AB18

AB15

AC15

M23

M22

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+MEM_VREF

R437

R437

39.2_0402_1%

39.2_0402_1%

15 mils

12

C

DDR_A_D[0..63]

DDR_A_MA[0..15]

DDR_A_DM[0..7]

PCIE_GTX_C_FRX_P0<18>

PCIE_GTX_C_FRX_N0<18>

PCIE_GTX_C_FRX_P1<18>

PCIE_GTX_C_FRX_N1<18>

PCIE_GTX_C_FRX_P2<18>

PCIE_GTX_C_FRX_N2<18>

PCIE_GTX_C_FRX_P3<18>

PCIE_GTX_C_FRX_N3<18>

+1.5V

+1.05VS

UMI_RX0P<13>

UMI_RX0N<1 3>

UMI_RX1P<13>

UMI_RX1N<1 3>

UMI_RX2P<13>

UMI_RX2N<1 3>

UMI_RX3P<13>

UMI_RX3N<1 3>

R435 2K_0402_1%R435 2K_0402_1%

Less than 1"

1 2

DDR_A_D[0..63] <8,9>

DDR_A_MA[0..15] <8,9>

DDR_A_DM[0..7] <8,9>

PCIE_GTX_C_FRX_P0

PCIE_GTX_C_FRX_N0

PCIE_GTX_C_FRX_P1

PCIE_GTX_C_FRX_N1

PCIE_GTX_C_FRX_P2

PCIE_GTX_C_FRX_N2

PCIE_GTX_C_FRX_P3

PCIE_GTX_C_FRX_N3

P_ZVDD_10

U22A

U22A

AA6

P_GPP_RXP0

Y6

P_GPP_RXN0

AB4

P_GPP_RXP1

AC4

P_GPP_RXN1

AA1

P_GPP_RXP2

AA2

P_GPP_RXN2

Y4

P_GPP_RXP3

Y3

P_GPP_RXN3

Y14

P_ZVDD_10

AA12

P_UMI_RXP0

Y12

P_UMI_RXN0

AA10

P_UMI_RXP1

Y10

P_UMI_RXN1

AB10

P_UMI_RXP2

AC10

P_UMI_RXN2

AC7

P_UMI_RXP3

AB7

P_UMI_RXN3

ONTARIO-2M161000-1.6G _BGA413

ONTARIO-2M161000-1.6G _BGA413

15G@

15G@

PCIE I/F

PCIE I/F

UMI I/F

UMI I/F

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_ZVSS

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

D

PCIE_FTX_GRX_P0

AB6

PCIE_FTX_GRX_N0

AC6

PCIE_FTX_GRX_P1

AB3

PCIE_FTX_GRX_N1

AC3

PCIE_FTX_GRX_P2

Y1

PCIE_FTX_GRX_N2

Y2

PCIE_FTX_GRX_P3

V3

PCIE_FTX_GRX_N3

V4

P_ZVSS

AA14

AB12

AC12

AC11

AB11

AA8

Y8

AB8

AC8

C518 0.1U_0402_16V7KVGA@C518 0.1U_0402_16V7KVGA@

C519 0.1U_0402_16V7KVGA@C519 0.1U_0402_16V7KVGA@

C520 0.1U_0402_16V7KVGA@C520 0.1U_0402_16V7KVGA@

C521 0.1U_0402_16V7KVGA@C521 0.1U_0402_16V7KVGA@

C522 0.1U_0402_16V7KVGA@C522 0.1U_0402_16V7KVGA@

C523 0.1U_0402_16V7KVGA@C523 0.1U_0402_16V7KVGA@

C524 0.1U_0402_16V7KVGA@C524 0.1U_0402_16V7KVGA@

C525 0.1U_0402_16V7KVGA@C525 0.1U_0402_16V7KVGA@

R436 1.27K_0402_1%R436 1.27K_0402_1%

1 2

Less than 1"

UMI_TX0P_C

UMI_TX0N_C

UMI_TX1P_C

UMI_TX1N_C

UMI_TX2P_C

UMI_TX2N_C

UMI_TX3P_C

UMI_TX3N_C

C526 0.1U_0402_16V7KC526 0.1U_0402_16V7K

C527 0.1U_0402_16V7KC527 0.1U_0402_16V7K

C528 0.1U_0402_16V7KC528 0.1U_0402_16V7K

C529 0.1U_0402_16V7KC529 0.1U_0402_16V7K

C530 0.1U_0402_16V7KC530 0.1U_0402_16V7K

C531 0.1U_0402_16V7KC531 0.1U_0402_16V7K

C532 0.1U_0402_16V7KC532 0.1U_0402_16V7K

C533 0.1U_0402_16V7KC533 0.1U_0402_16V7K

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

E

PCIE_FTX_C_GRX_P0 <18>

PCIE_FTX_C_GRX_N0 <1 8>

PCIE_FTX_C_GRX_P1 <18>

PCIE_FTX_C_GRX_N1 <1 8>

PCIE_FTX_C_GRX_P2 <18>

PCIE_FTX_C_GRX_N2 <1 8>

PCIE_FTX_C_GRX_P3 <18>

PCIE_FTX_C_GRX_N3 <1 8>

UMI_TX0P <13>

UMI_TX0N < 13>

UMI_TX1P <13>

UMI_TX1N < 13>

UMI_TX2P <13>

UMI_TX2N < 13>

UMI_TX3P <13>

UMI_TX3N < 13>

+1.5V

+1.5V

R149

R149

1 2

1K_0402_5%

1K_0402_5%

1 1

DDR_EVENT#

A

R438

R438

1K_0402_1%

1K_0402_1%

R439

R439

1K_0402_1%

1K_0402_1%

1 2

1

C534

C534

1000P_0402_50V7K

1000P_0402_50V7K

2

1 2

Place within 1000 mils to APU

20100526

B

C535

C535

+MEM_VREF

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

FT1 DDRIII/UMI/PCIE

FT1 DDRIII/UMI/PCIE

FT1 DDRIII/UMI/PCIE

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

E

6 47Wednesday, November 24, 2010

6 47Wednesday, November 24, 2010

6 47Wednesday, November 24, 2010

1.0

1.0

1.0

5

4

3

2

1

+APU_CORE

U22C

U22C

1

C539

C539

D D

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

C550

C550

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C559

C559

0.1U_0402_16V7K

0.1U_0402_16V7K

2

+APU_CORE_NB

C C

C575

C575

10U_0603_6.3V6M

10U_0603_6.3V6M

C582

C582

1U_0402_6.3V6K

1U_0402_6.3V6K

C591

C591

0.1U_0402_16V7K

0.1U_0402_16V7K

B B

1

2

1

2

1

2

1

C536

C536

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C551

C551

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C560

C560

0.1U_0402_16V7K

0.1U_0402_16V7K

2

1

C576

C576

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

C583

C583

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C592

C592

0.1U_0402_16V7K

0.1U_0402_16V7K

2

POWER

1

C620

C620

@

@

10U_0603_6.3V6M

10U_0603_6.3V6M

2

+APU_CORE

1

1

330U_D2E_2.5VM_R9M

330U_D2E_2.5VM_R9M

+

+

+

C605

C605

@

@

330U_D2E_2.5VM_R9M

330U_D2E_2.5VM_R9M

+APU_CORE_NB

A A

C617

C617

390U_2.5V_10M

390U_2.5V_10M

+

C606

C606

2

2

1

+

+

2

C541

C541

10U_0603_6.3V6M

10U_0603_6.3V6M

C552

C552

1U_0402_6.3V6K

1U_0402_6.3V6K

C561

C561

0.1U_0402_16V7K

0.1U_0402_16V7K

C577

C577

10U_0603_6.3V6M

10U_0603_6.3V6M

C584

C584

1U_0402_6.3V6K

1U_0402_6.3V6K

C593

C593

0.1U_0402_16V7K

0.1U_0402_16V7K

+1.05VS

1

+

+

C621

C621

@

@

390U_2.5V_10M

390U_2.5V_10M

2

1

+

+

C607

C607

@

@

330U_D2E_2.5VM_R9M

330U_D2E_2.5VM_R9M

2

1

+

+

C618

C618

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

2

1

2

1

2

1

2

1

2

1

2

1

2

1

C542

C542

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C553

C553

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C562

C562

0.1U_0402_16V7K

0.1U_0402_16V7K

2

1

C578

C578

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

C585

C585

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C594

C594

0.1U_0402_16V7K

0.1U_0402_16V7K

2

1

390U_2.5V_10M

390U_2.5V_10M

+

+

C1104

C1104

2

Near CPU Socket

1

C619

C619

10U_0603_6.3V6M

10U_0603_6.3V6M

2

C543

C543

10U_0603_6.3V6M

10U_0603_6.3V6M

C563

C563

C579

C579

C586

C586

1U_0402_6.3V6K

1U_0402_6.3V6K

1

+

+

C1105

C1105

390U_2.5V_10M

390U_2.5V_10M

2

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

180P_0402_50V8J

180P_0402_50V8J

1

0.1U_0402_16V7K

0.1U_0402_16V7K

2

1

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

2

POWER

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C616

C616

@

@

2

1

C544

C544

2

1

C554

C554

2

1

C587

C587

180P_0402_50V8J

180P_0402_50V8J

2

1

C540

C540

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

C555

C555

180P_0402_50V8J

180P_0402_50V8J

2

1

C588

C588

180P_0402_50V8J

180P_0402_50V8J

2

+1.5V +1.8VS

1

C622

C622

390U_2.5V_10M

390U_2.5V_10M

2

+APU_CORE

+APU_CORE_NB

+1.5V

change 0603 for DVT

1

C623

C623

+

+

10U_0603_6.3V6M

10U_0603_6.3V6M

2

Near CPU Socket Near CPU Socket

11A

E5

VDDCR_CPU_1

E6

VDDCR_CPU_2

F5

VDDCR_CPU_3

F7

VDDCR_CPU_4

G6

VDDCR_CPU_5

G8

VDDCR_CPU_6

H5

VDDCR_CPU_7

H7

VDDCR_CPU_8

J6

VDDCR_CPU_9

J8

VDDCR_CPU_10

L7

VDDCR_CPU_11

M6

VDDCR_CPU_12

M8

VDDCR_CPU_13

N7

VDDCR_CPU_14

R8

VDDCR_CPU_15

10A

E8

VDDCR_NB_1

E11

VDDCR_NB_2

E13

VDDCR_NB_3

F9

VDDCR_NB_4

F12

VDDCR_NB_5

G11

VDDCR_NB_6

G13

VDDCR_NB_7

H9

VDDCR_NB_8

H12

VDDCR_NB_9

K11

VDDCR_NB_10

K13

VDDCR_NB_11

L10

VDDCR_NB_12

L12

VDDCR_NB_13

L14

VDDCR_NB_14

M11

VDDCR_NB_15

M12

VDDCR_NB_16

M13

VDDCR_NB_17

N10

VDDCR_NB_18

N12

VDDCR_NB_19

N14

VDDCR_NB_20

P11

VDDCR_NB_21

P13

VDDCR_NB_22

2A

G16

VDDIO_MEM_S_1

G19

VDDIO_MEM_S_2

E17

VDDIO_MEM_S_3

J16

VDDIO_MEM_S_4

L16

VDDIO_MEM_S_5

L19

VDDIO_MEM_S_6

N16

VDDIO_MEM_S_7

R16

VDDIO_MEM_S_8

R19

VDDIO_MEM_S_9

W18

VDDIO_MEM_S_10

U16

VDDIO_MEM_S_11

ONTARIO-2M161000-1.6G_BGA413

ONTARIO-2M161000-1.6G_BGA413

15G@

15G@

+1.5V

C589

C589

10U_0603_6.3V6M

10U_0603_6.3V6M

C595

C595

1U_0402_6.3V6K

1U_0402_6.3V6K

C599

C599

0.1U_0402_16V7K

0.1U_0402_16V7K

+1.5V

2

1

1

2

1

2

1

2

C101

C101

0.1U_0402_16V7K

0.1U_0402_16V7K

1

C590

C590

10U_0603_6.3V6M

10U_0603_6.3V6M

2

1

C596

C596

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C600

C600

0.1U_0402_16V7K

0.1U_0402_16V7K

2

180PF Qt'y follow the distance between

CPU socket and DIMM0. <2.5inch>

2

1

C102

C102

0.1U_0402_16V7K

0.1U_0402_16V7K

GPU AND NB CORE

GPU AND NB CORE

DDR3

DDR3

1

C597

C597

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C601

C601

0.1U_0402_16V7K

0.1U_0402_16V7K

2

TSense/PLL/DP/PCIE/IO

TSense/PLL/DP/PCIE/IO

CPU CORE

CPU CORE

DAC

DAC

VDD_18_DAC

POWER

POWER

PCIE/IO/DDR3 Phy

PCIE/IO/DDR3 Phy

1

C103

C103

180P_0402_50V8J

180P_0402_50V8J

2

VDD_18_1

VDD_18_2

VDD_18_3

VDD_18_4

VDD_18_5

VDD_18_6

VDD_18_7

DIS PLL

DIS PLL

VDDPL_10

VDD_10_1

VDD_10_2

VDD_10_3

VDD_10_4

DP Phy/IO

DP Phy/IO

180P_0402_50V8J

180P_0402_50V8J

POWER POWER

1

1

C685

C685

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C624

C624

390U_2.5V_10M

390U_2.5V_10M

Near CPU Socket

+

+

2

1

C625

C625

@

@

10U_0603_6.3V6M

10U_0603_6.3V6M

2

(390uF_2.5V_6.3x5.7_ESR10m)*1=(SF000002O00)

5

4

U8

W8

U6

U9

W6

T7

V7

W9

U11

U13

W13

V12

T12

A4

VDD_33

1

C598

C598

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C602

C602

2

2A

0.15A

0.2A

5.5A

0.5A

+VDD_18

C545

C545

+VDD_18_DAC

C556

C556

+VDDL_10

C564

C564

+VDD_10

C568

C568

C580

C580

1

1

1

C546

C546

C537

C537

2

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

180P_0402_50V8J

180P_0402_50V8J

add Cap. for CRT DVT

1

1

2

1

2

1

2

1

2

1

C557

C557

C558

C558

2

2

180P_0402_50V8J

180P_0402_50V8J

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C566

C566

C565

C565

2

2

180P_0402_50V8J

180P_0402_50V8J

0.1U_0402_16V7K

0.1U_0402_16V7K

1

1

C570

C570

C569

C569

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

180P_0402_50V8J

180P_0402_50V8J

+3VS

1

C581

C581

2

1U_0402_6.3V6K

1U_0402_6.3V6K

0.1U_0402_16V7K

0.1U_0402_16V7K

1

1

C538

C538

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C604

C604

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

C567

C567

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C571

C571

2

0.1U_0402_16V7K

0.1U_0402_16V7K

Power Cap. Summ ary

APU

S POLY C 330U 2.5V M D2E TPE LESR9M H1.8 --->+APU_CORE(Qty : 3) Unpop:2

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU --->+APU_CORE(Qty : 2)

S POLY C 330U 2.5V Y D2 LESR9M EEFS H1.9 --->+APU_CORE_NB(Qty : 1)

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU--->+APU_CORE_NB(Qty : 1)

1

C547

C547

C548

C548

C549

C549

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

1

@

@

Change from SM010014520 to SD002000080

C684

C684

20100816

2

10U_0603_6.3V6M

10U_0603_6.3V6M

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

1

1

C572

C572

C574

C574

C573

C573

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

L30

L30

L31

L31

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU --->+1.5V(Qty : 1)

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU --->1.05VS(Qty : 1)

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU --->+1.8VS(Qty : 1)

DDR3 Socket

S POLY C 330U 2V M X LESR6M SX H1.9 --->1.5V(Qty : 1)

FCH

S POLY C 330U 2.5V Y D2 LESR9M EEFS H1.9 --->1.1VS(Qty : 1) UMA unpop

1

C603

C603

180P_0402_50V8J

180P_0402_50V8J

2

GPU

S POLY C 330U 2V M X LESR6M SX H1.9 --->VGA_CORE(Qty : 2) Unpop:1

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU --->+VGA_CORE(Qty : 1)

S_A-P_CAP 390U 2.5V M 6.3X5.7 LESR10M VU --->+1.5VSG(Qty : 1)

USB

1

C104

C104

180P_0402_50V8J

180P_0402_50V8J

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

S_A-P_CAP 220U 6.3V M C45 R17M SVPE H4.4 --->+USB_VCCA(Qty : 1)

Compal Secret Data

Compal Secret Data

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+1.8VS

L29

L29

12

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

Change from SM010014520 to SD002000080

20100816

+1.8VS

12

+1.05VS

12

L32

L32

12

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

Change from SM010014520 to SD002000080

20100816

By case (Along split)

2

+1.5V

0.1U_0402_16V7K

0.1U_0402_16V7K

U22D

U22D

A7

VSS_1

B7

VSS_2

B11

VSS_3

B17

VSS_4

B22

VSS_5

C4

VSS_6

D5

VSS_7

D7

VSS_8

D9

VSS_9

D11

VSS_10

D14

VSS_11

B15

VSS_12

D17

VSS_13

D19

VSS_14

E7

VSS_15

E9

VSS_16

E12

VSS_17

E20

VSS_18

F8

VSS_19

F11

VSS_20

F13

VSS_21

G4

VSS_22

G5

VSS_23

G7

VSS_24

G9

VSS_25

G12

VSS_26

G20

VSS_27

G22

VSS_28

H6

VSS_29

H11

VSS_30

H13

VSS_31

J4

VSS_32

J5

VSS_33

J7

VSS_34

J20

VSS_35

K10

VSS_36

K14

VSS_37

L4

VSS_38

L6

VSS_39

L8

VSS_40

L11

VSS_41

L13

VSS_42

L20

VSS_43

L22

VSS_44

M7

VSS_45

N4

VSS_46

N6

VSS_47

N8

VSS_48

N11

VSS_49

ONTARIO-2M161000-1.6G_BGA413

ONTARIO-2M161000-1.6G_BGA413

15G@

15G@

GND

GND

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSSBG_DAC

N13

N20

N22

P10

P14

R4

R7

R20

T6

T9

T11

T13

U4

U5

U7

U12

U20

U22

V8

V9

V11

V13

W1

W2

W4

W5

W7

W12

W20

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

AA4

AA22

AB2

AB5

AB9

AB13

AB17

AB21

AC5

AC9

AC13

A11

+APU_CORE

+APU_CORE_NB

+1.5V

+1.05VS

+1.8VS

+1.5V

+1.1VS

+GPU_CORE

+1.5VSG

+USB_VCCA

1

1

C608

C608

C609

C609

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

1

1

C611

C611

C610

C610

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

P07-FT1 PWR/VSS

P07-FT1 PWR/VSS

P07-FT1 PWR/VSS

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

1

1

C613

C613

C612

C612

2

2

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

1

1

1

C615

C615

C614

C614

2

2

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

180P_0402_50V8J

7 47Monday, November 15, 2010

7 47Monday, November 15, 2010

7 47Monday, November 15, 2010

1.0

1.0

1.0

5

+1.5V

JDIMM1

+VREF_DQ

1

C626

C626

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

D D

DDR_A_DQS#1<6,9>

DDR_A_DQS1<6,9>

DDR_A_DQS#2<6,9>

DDR_A_DQS2<6,9>

C C

DDR_CS1_DIMMA#<6>

B B

A A

+3VS

DDR_A_DQS#4<6,9>

DDR_A_DQS4<6,9>

DDR_A_DQS#6<6,9>

DDR_A_DQS6<6,9>

C646

C646

2.2U_0603_6.3V4Z

2.2U_0603_6.3V4Z

1000P_0402_50V7K

1000P_0402_50V7K

DDR_CKE0<6,9>

DDR_A_BS2<6,9>

DDR_A_CLK0<6>

DDR_A_CLK#0<6>

DDR_A_BS0<6,9>

DDR_A_WE#<6,9>

DDR_A_CAS#<6,9>

1

2

5

1

C627

C627

2

1

C647

C647

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

DDR_A_D0

DDR_A_D1

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_MA13

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

1 2

R150 10K_0402_5%R150 10K_0402_5%

12

R151

R151

10K_0402_5%

10K_0402_5%

JDIMM1

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

FOX_AS0A626-U8SN-7F

FOX_AS0A626-U8SN-7F

CONN@

CONN@

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

DQ14

DQ15

DQ20

DQ21

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

4

+1.5V

2

DDR_A_D4

4

DDR_A_D5

6

8

10

12

14

DDR_A_D6

16

DDR_A_D7

18

20

DDR_A_D12

22

DDR_A_D13

24

26

DDR_A_DM1

28

30

32

DDR_A_D14

34

DDR_A_D15

36

38

DDR_A_D20

40

DDR_A_D21

42

44

DDR_A_DM2

46

48

DDR_A_D22

50

DDR_A_D23

52

54

DDR_A_D28

56

DDR_A_D29

58

60

62

64

66

DDR_A_D30

68

DDR_A_D31

70

72

74

76

DDR_A_MA15

78

A15

A14

A11

A7

A6

A4

A2

A0

S0#

G2

DDR_A_MA14

80

82

DDR_A_MA11

84

DDR_A_MA7

86

88

DDR_A_MA6

90

DDR_A_MA4

92

94

DDR_A_MA2

96

DDR_A_MA0

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR3 SO-DIMM A H:8mm

Standard Type

P/N:SP07000HA00

F/P:FOX_AS0A626-U8SN-7F_204P

4

+0.75VS

DDR_A_DQS#0 <6,9>

DDR_A_DQS0 <6,9>

DDR_RST# <6,9>

DDR_A_DQS#3 <6,9>

DDR_A_DQS3 <6,9>

DDR_CKE1 <6,9>

DDR_A_CLK1 <6>

DDR_A_CLK#1 <6>

DDR_A_BS1 <6,9>

DDR_A_RAS# <6,9>

DDR_CS0_DIMMA# <6>

DDR_A_ODT0 <6>

DDR_A_ODT1 <6>

1

C645

C645

1000P_0402_50V7K

1000P_0402_50V7K

2

DDR_A_DQS#5 <6,9>

DDR_A_DQS5 <6,9>

DDR_A_DQS#7 <6,9>

DDR_A_DQS7 <6,9>

DDR_EVENT# <6,9>

FCH_SMDAT0 <9 ,14,29>

FCH_SMCLK0 <9,14,29>

1

C644

C644

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

3

DDR_A_D[0..63]

DDR_A_MA[0..15]

DDR_A_DM[0..7]

+1.5V

2

C628

C628

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C629

C629

1

DDR_A_D[0..63] <6,9>

DDR_A_MA[0..15] <6,9>

DDR_A_DM[0..7] <6,9>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C630

C630

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C631

C631

1

2

2

C632

C632

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C633

C633

1

+VREF_DQ

2

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CRB 0.1u X1 4.7u X1

+0.75VS

+VREF_CA

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

2010/08/20 2011/08/20

2010/08/20 2011/08/20

2010/08/20 2011/08/20

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

C640

C640

@

@

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

Place near JDIMM1

2

C641

C641

2

1

1

C642

C642

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

2

EMI For DVT 10/20

+1.5V

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C638

C638

1

+1.5V

+1.5V

R145

R145

1K_0402_1%

2

C635

C635

1

1K_0402_1%

1 2

R147

R147

1K_0402_1%

1K_0402_1%

1 2

2

C636

C636

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C637

C637

1

+VREF_CA

0.1U_0402_16V4Z

0.1U_0402_16V4Z

15mil 15mil

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C634

C634

CRB 100U X2

+1.5V

1

+

+

C1102

C1102

330U_D2E_2.5VM_R9M

330U_D2E_2.5VM_R9M

2

330U ESR:9m H:2

P/N:SGA20331E10

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C676

C676

1

1

0.1U_0402_16V4Z

2

C678

C678

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

C643

C643

C675

1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

C675

1

Compal Electronics, Inc.

DDR3 SODIMM-I Socket

DDR3 SODIMM-I Socket

DDR3 SODIMM-I Socket

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

LA-7092P P5WE6/H6/S6

R146

R146

1K_0402_1%

1K_0402_1%

1 2

R148

R148

1K_0402_1%

1K_0402_1%

1 2

2

C110

C110

1

8 47Wednesday, November 24, 2010

8 47Wednesday, November 24, 2010

8 47Wednesday, November 24, 2010

1.0

1.0

1.0

5

4

3

2

1

+1.5V

JDIMM2

11

13

15

17

19

21

23

25

27

33

35

39

41

45

47

49

51

53

55

57

59

63

67

69

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

205

1 2

JDIMM2

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS129RESET#

VSS1131VSS12

DQ10

DQ11

VSS1337VSS14

DQ16

DQ17

VSS1543VSS16

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS2261DQS#3

DM3

VSS2365VSS24

DQ26

DQ27

VSS2571VSS26

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

G1

FOX_AS0A626-U4SN-7F

FOX_AS0A626-U4SN-7F

CONN@

CONN@

DQS#0

DQS0

DQ12

DQ13

VSS10