Acer Aspire 5220 Schematics REV 1.0Se

A

hexainf@hotmail.com

GRATIS - FOR FREE

1 1

B

C

D

E

2 2

Compal Confidential

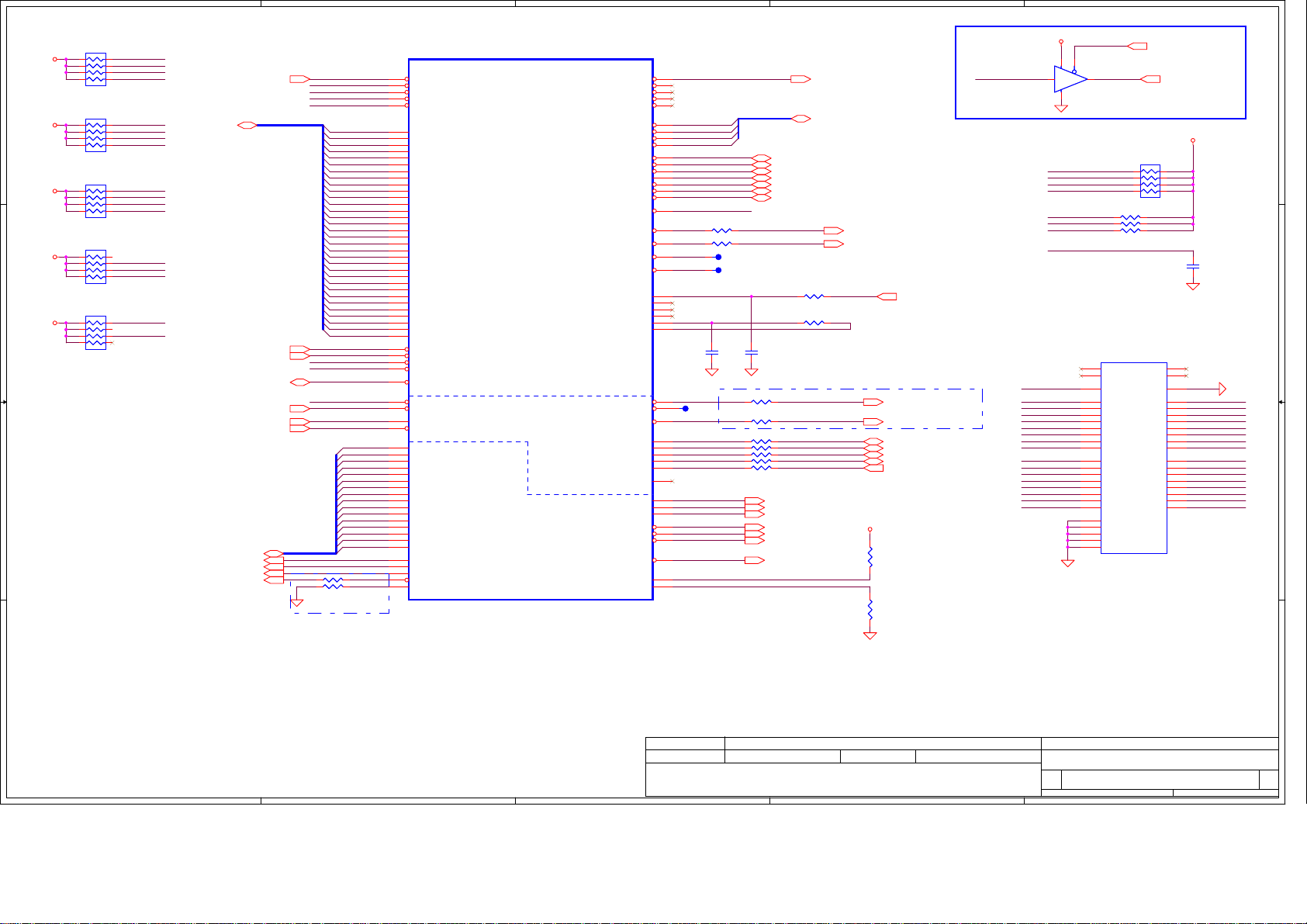

ICW50 Schematics Document

AMD Turion/Sempron + Nvidia MCP67-MV

2007 / 04 / 20 FOR Pre-MP

3 3

4 4

Rev:1.0

Compal Electronics, Inc.

Compal Electronics, Inc.

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

Date: Sheet of

Date: Sheet

Date: Sheet

E

of

of

142Friday, April 20, 2007

142Friday, April 20, 2007

142Friday, April 20, 2007

1.0

1.0

1.0

5

4

3

2

1

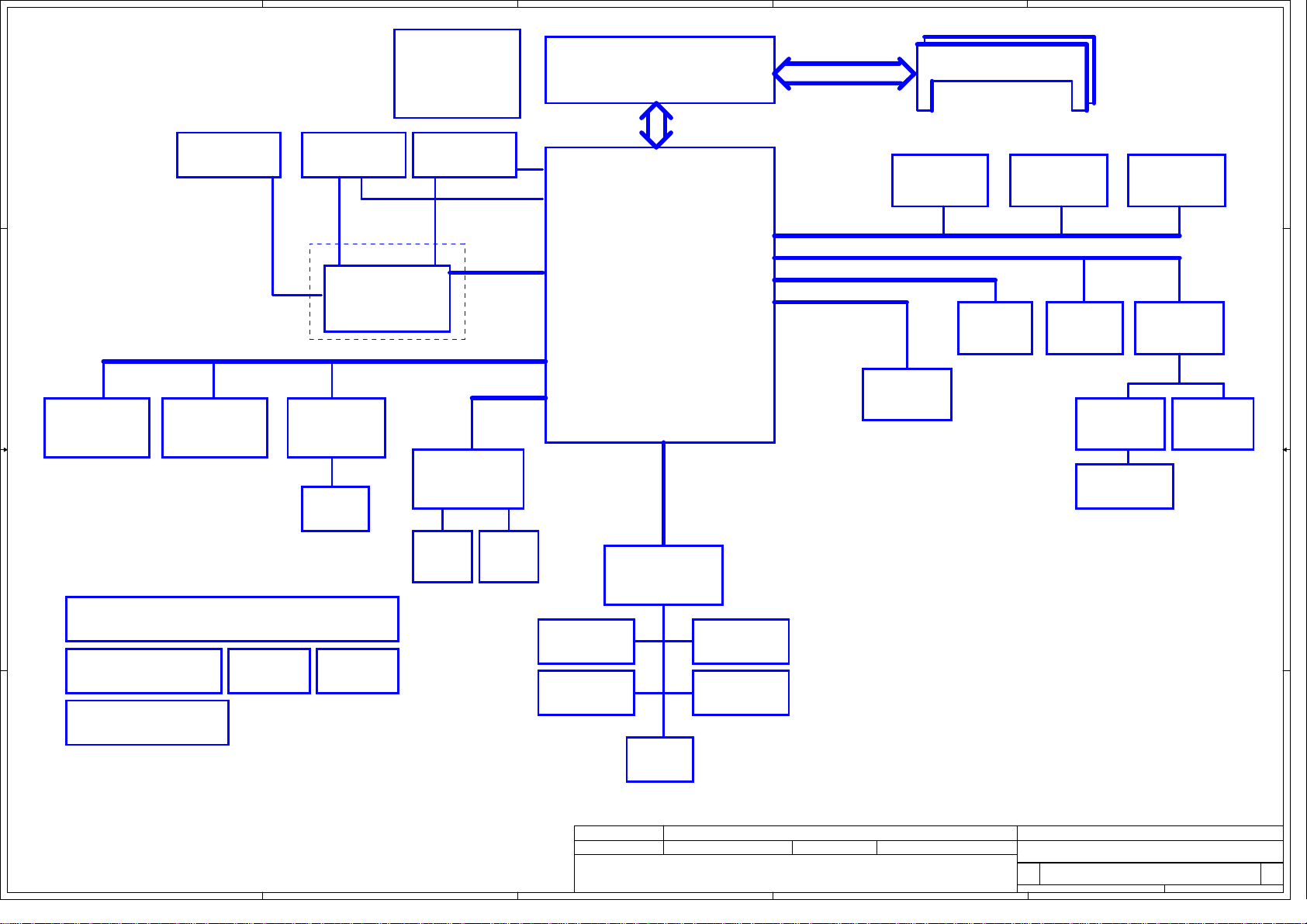

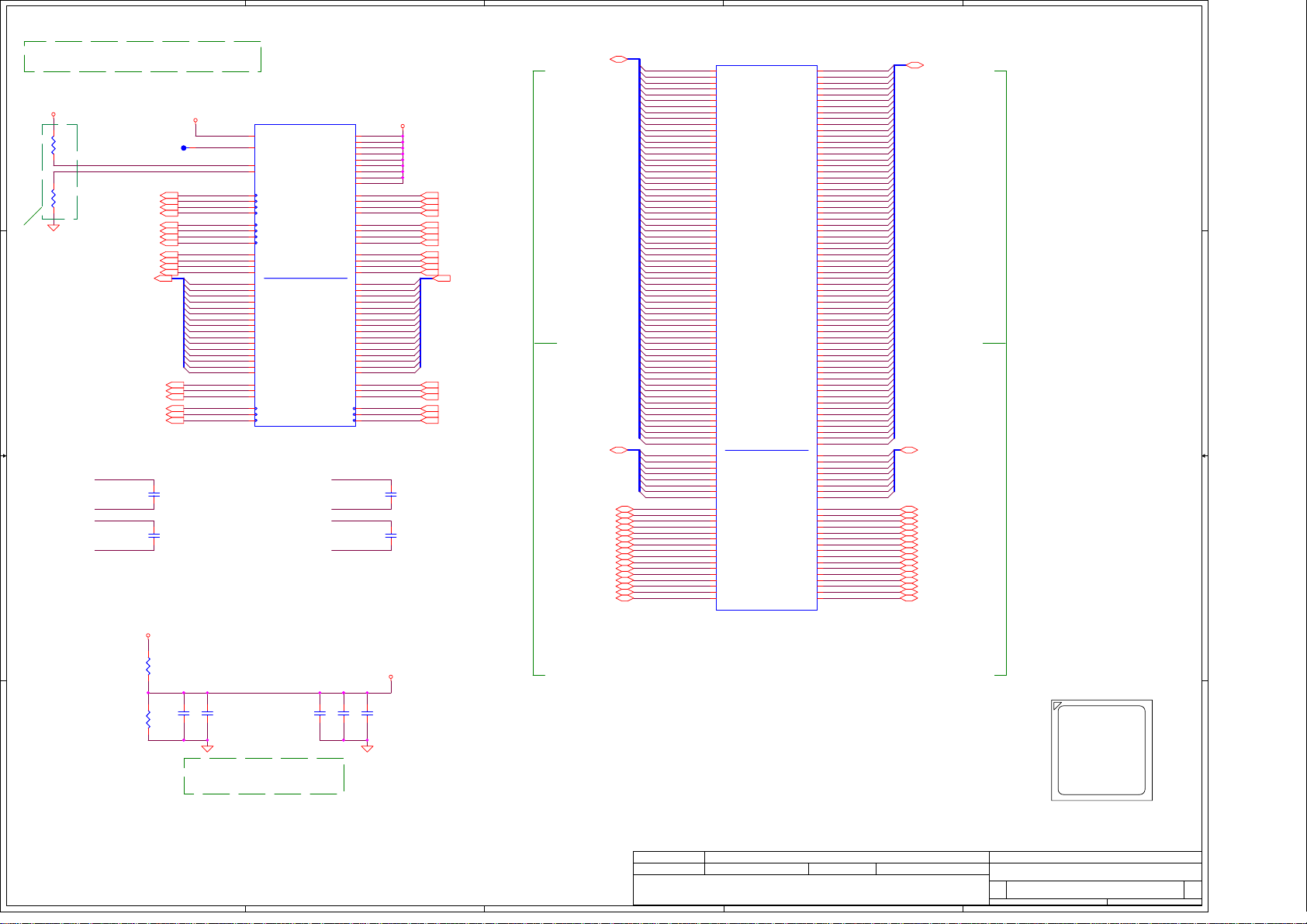

Compal confidential

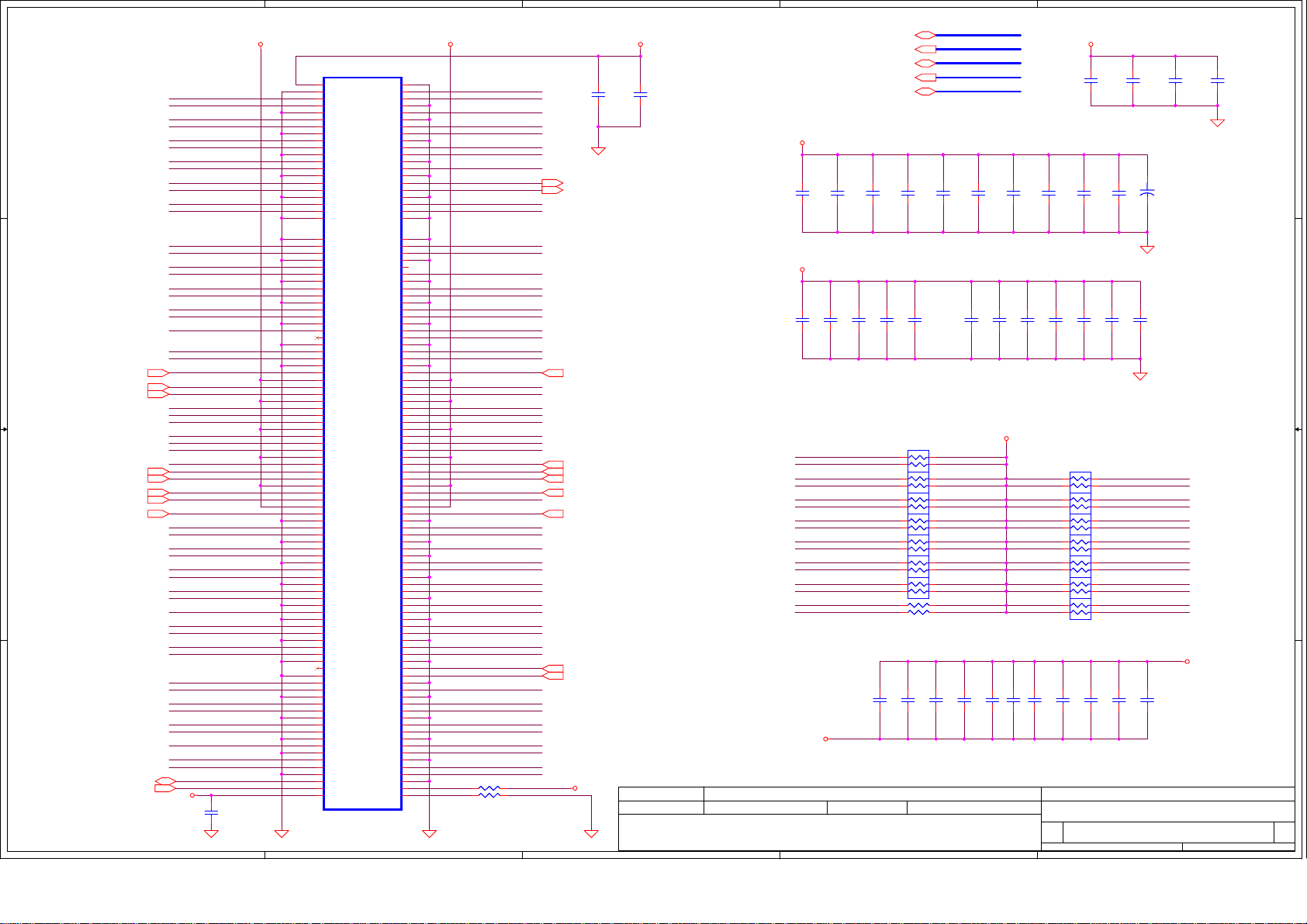

Project Code: ICW50

File Name : LA-3581P

D D

DVI-D Conn. LCD Conn.

page 20page 20

Thermal Sensor

ADM1032ARM

page 6

CRT & TV-out

page 19

AMD Turion/Sempron CPU

Socket S1 638P

page 4,5,6,7

HT LINK

200-800MHz

DDRII DDRII-SO-DIMM X2

Nvidia

LVDS

LVDSDVI

PCI-Express

MXM II VGA/B

page 18

C C

PCI-Express

MCP67-MV

836 BGA

USB 2.0 BUS

HD Audio

IDE BUS

SATA BUS

533/667/800

Dual Channel

3.3V 24.576MHz/48Mhz

3.3V ATA-100

port 1

USB conn x4

CDROM

Conn.

page 08,09

page 21

Bluetooth

Conn

MDC 1.5

Conn

CMOS

Camera

page 20page 29page 25,26

HDA Codec

page 29 page 31

ALC268

New Card

Socket

MINI Card x2

WLAN, TV-Tuner

PHY(GbE)

RTL8211B

page 22

IDSEL:AD20

(PIRQE#,

GNT#0,

REQ#0)

PCI BUS

3.3V 33 MHz

page 10,11,12,13,14,15,16,17

S-ATA HDD

Conn.

page 21

Audio AMP

page 32

Card Reader

RJ45

RICOH R5C833

page 22

1394

B B

Conn.

page 23

page 23

6 in 1

socket

page 24

LPC BUS

ENE KB926

page 27,28

Power On/Off CKT / LID switch / Power OK CKT

DC/DC Interface CKT.

page 33

CIR/LED

page 29

page 30

RTC CKT.

page 16

Touch Pad

page 29

EC I/O Buffer BIOS

page 29

Int.KBD

page 29

page 29

Power Circuit DC/DC

page 35~41

CIR

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

page 30

3

Compal Secret Data

Compal Secret Data

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Phone Jack x3

page 32

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

1.0

1.0

242Friday, April 20, 2007

242Friday, April 20, 2007

242Friday, April 20, 2007

1

1.0

of

of

of

5

hexainf@hotmail.com

GRATIS - FOR FREE

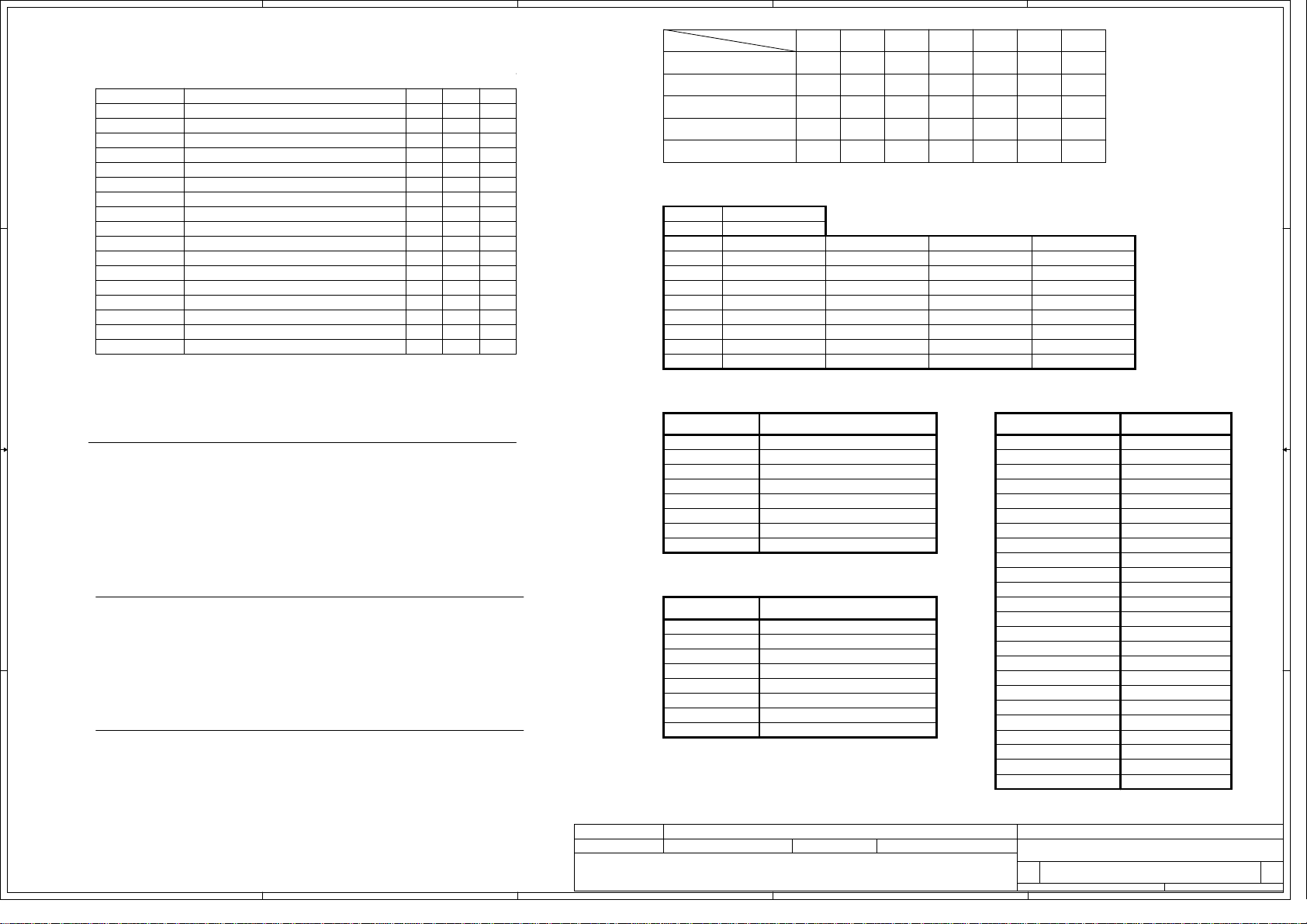

Voltage Rails

Power Plane

D D

C C

VIN

B+

+CPU_CORE

+0.9V

+1.5VS

+1.2VALW ON ON ON*

+1.2VS ON

+1.2V_HT

+1.8V

+1.8VS

+2.5VS

+3VALW/+3V/+3VAUX

+3VS

+5VALW

+5VS

+VSB

+RTCVCC

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

0.9V switched power rail for DDR terminator

1.5V switched power rail

1.2V always on power rail

1.2V switched power rail

1.2V switched power rail

1.8V power rail for DDR

1.8V switched power rail

2.5V switched power rail

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

RTC power

4

S1 S3 S5

N/A N/A N/A

ON

ON ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFFOFF

OFF OFF

OFF OFF

OFF

ON

OFF

OFF

OFF

OFF

ON*

ON

OFF

OFF

ON

ON*

OFF

OFF

ON*ON

ON

ON

3

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW

2

SLP_S5# +VALW +V +VS Clock

HIGHHIGH

LOW

HIGH

LOWLOW

HIGH

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

ON

ON

ON

OFF

OFF

ON ON

ON

OFF

OFF

OFF

V

AD_BID

ON

ON

ON

ON

ON

V typ

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

1

LOW

OFF

OFF

OFF

max

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

Device

1394

IDSEL#

AD20 0

REQ#/GNT#

Interrupts

PIRQE

BOARD ID Table

Board ID

0

1

2

PCB Revision

UMA (0V)

DISCRETE (3.3V)

3

4

5

6

7

B B

EC SM Bus1 address

Device

Smart Battery

Address Address

EC SM Bus2 address

Device

ADM1032

1001 100X b0001 011X b

SKU ID Table

SKU ID

0

1

SKU

B - PHASE

C - PHASE

MINI CARD 2(WLAN) MINI2@

2

BTO Option Table

BTO Item BOM Structure

UMA UMA@

VGA VGA@

UMA & TV-OUT UMA&TV@

2 SATA HDD SATA2@

CAMERA CMOS@

BLUETOOTH BT@

MINI CARD 1(TV) MINI1@

NEW CARD EXPRESS@

TV-OUT

DVI DVI@

1394

CARD READER

HT Debug Port

45@DIP CAP & RTC

TV@

1394@

5IN1@

HT@

3

4

5

MCP67 SM Bus address

Device Address

DDR DIMM0

A A

DDR DIMM2

5

1001 000Xb

1001 001Xb

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

6

7

Compal Secret Data

Compal Secret Data

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

Date: Sheet

Date: Sheet

Date: Sheet

1

of

of

of

342Friday, April 20, 2007

342Friday, April 20, 2007

342Friday, April 20, 2007

1.0

1.0

1.0

5

4

3

2

1

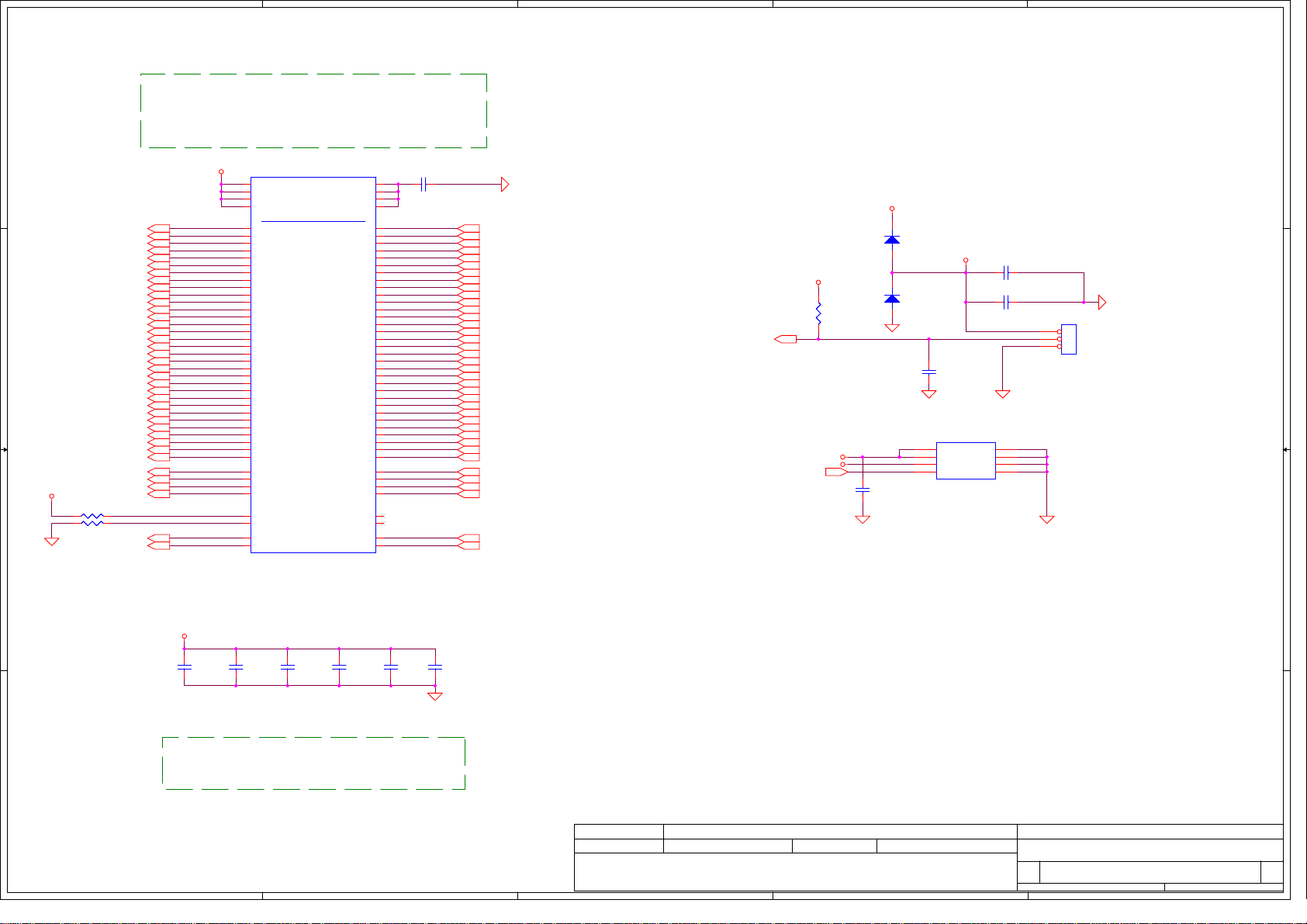

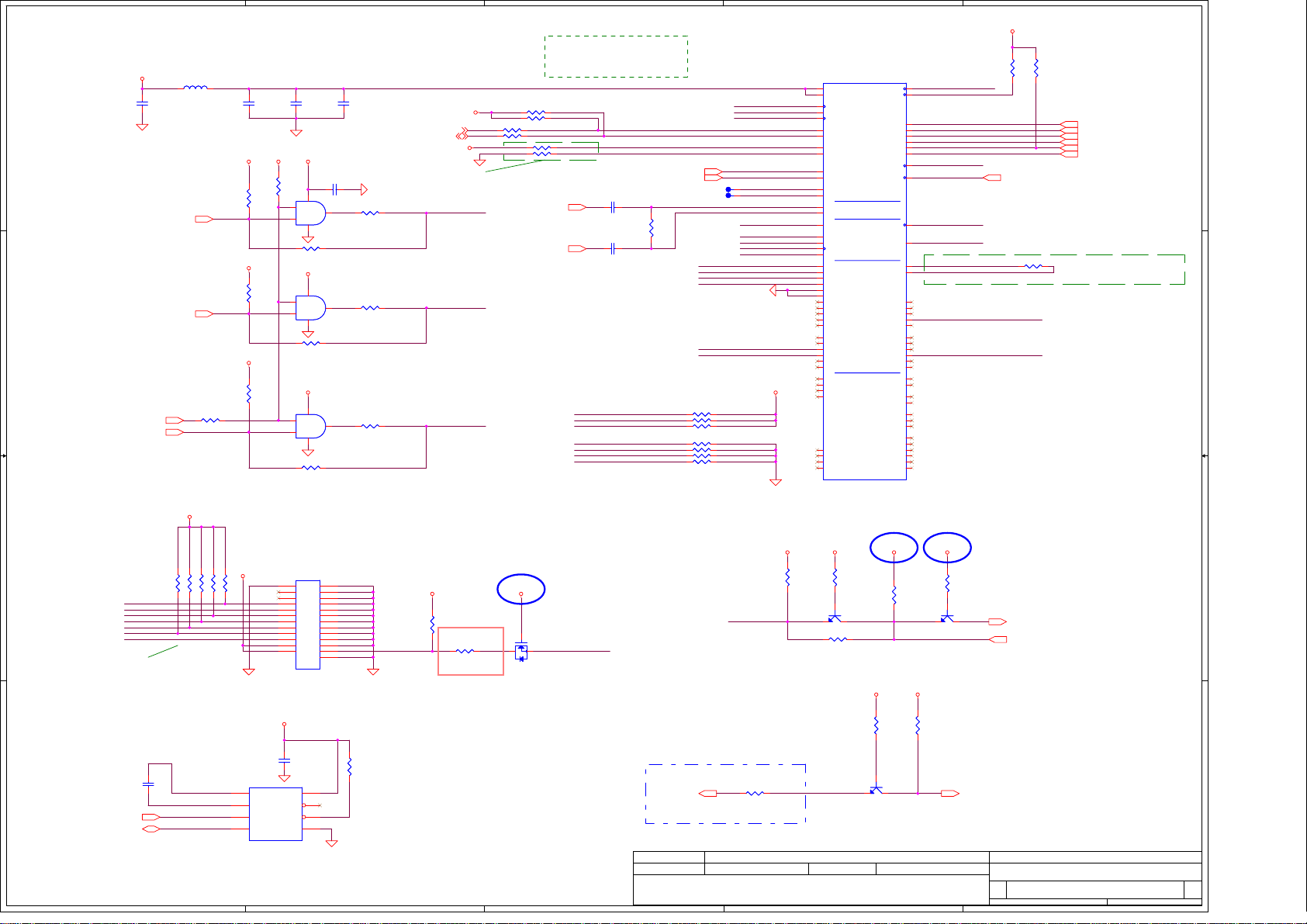

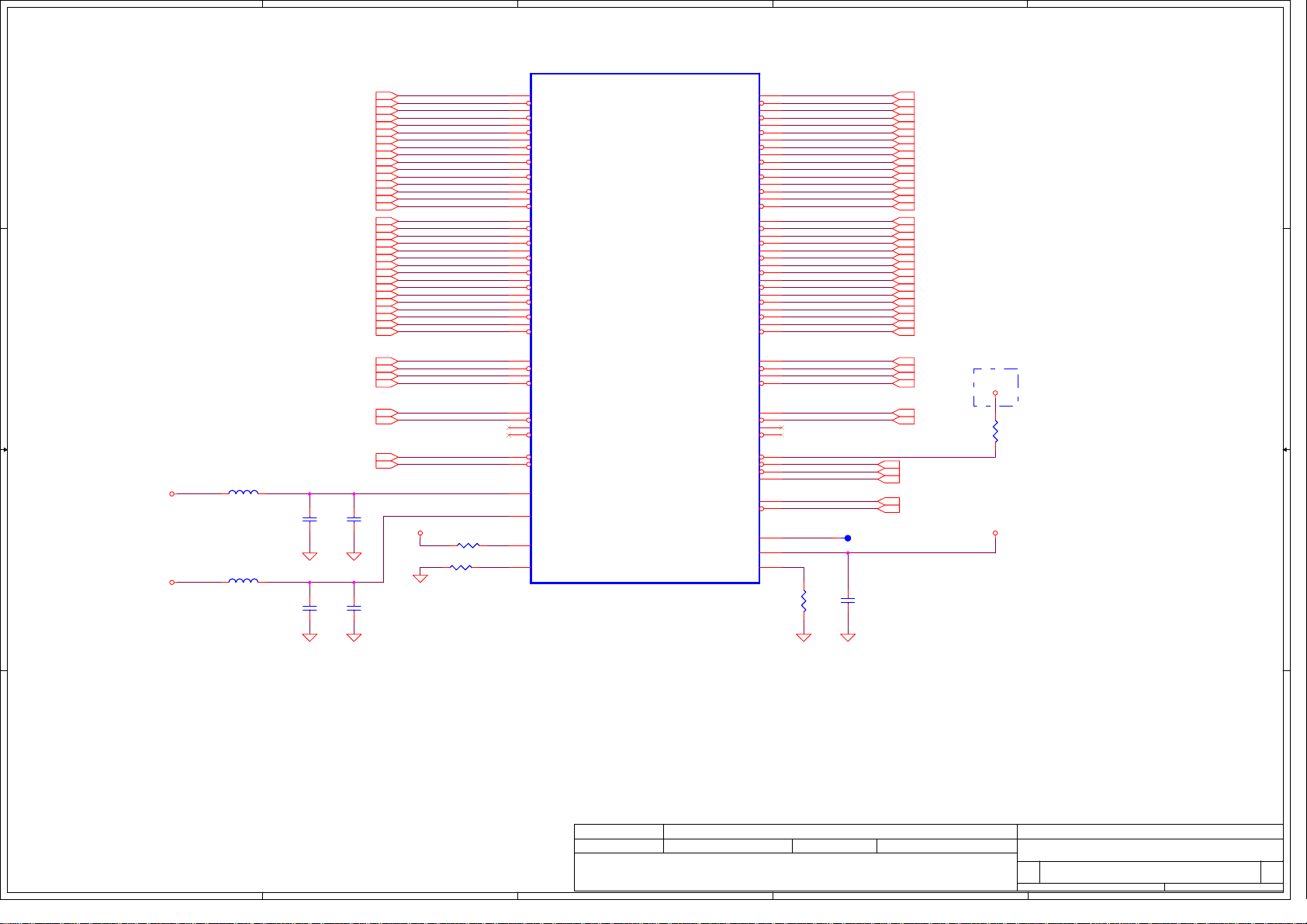

PROCESSOR HYPERTRANSPORT INTERFACE

D D

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+1.2V_HT

JP22A

JP22A

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

H_CADIP15(10) H_CADOP15 (10)

H_CADIN15(10)

H_CADIP14(10)

H_CADIN14(10)

H_CADIP13(10)

H_CADIN13(10)

H_CADIP12(10)

H_CADIN12(10)

H_CADIP11(10)

H_CADIN11(10)

H_CADIP10(10)

H_CADIN10(10)

H_CADIP9(10)

H_CADIN9(10)

H_CADIP8(10)

C C

+1.2V_HT

B B

H_CADIN8(10)

H_CADIP7(10)

H_CADIN7(10)

H_CADIP6(10)

H_CADIN6(10)

H_CADIP5(10)

H_CADIN5(10)

H_CADIP4(10)

H_CADIN4(10)

H_CADIP3(10)

H_CADIN3(10)

H_CADIP2(10)

H_CADIN2(10)

H_CADIP1(10)

H_CADIN1(10)

H_CADIP0(10)

H_CADIN0(10)

H_CLKIP1(10)

H_CLKIN1(10)

H_CLKIP0(10)

H_CLKIN0(10)

R143 51_0402_1%

R143 51_0402_1%

1 2

R142 51_0402_1%

R142 51_0402_1%

1 2

H_CTLIP0(10)

H_CTLIN0(10)

H_CADIP15

H_CADIP14

H_CADIN14

H_CADIP13

H_CADIN13

H_CADIP12

H_CADIN12

H_CADIP11

H_CADIN11

H_CADIP10

H_CADIN10

H_CADIP9

H_CADIN9

H_CADIP8

H_CADIN8

H_CADIP7

H_CADIN7

H_CADIP6

H_CADIN6

H_CADIP5

H_CADIN5

H_CADIP4

H_CADIN4

H_CADIP3

H_CADIN3

H_CADIP2

H_CADIN2

H_CADIP1

H_CADIN1

H_CADIP0

H_CADIN0

H_CLKIP1

H_CLKIN1

H_CLKIP0

H_CLKIN0

H_CTLIP1

H_CTLIN1

H_CTLIP0

H_CTLIN0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

FOX_PZ63823-284S-41F

FOX_PZ63823-284S-41F

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

HTT Interface

HTT Interface

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1

Processor Socket

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

T5

R5

R2

R3

1 2

H_CADOP15

H_CADON15H_CADIN15

H_CADOP14

H_CADON14

H_CADOP13

H_CADON13

H_CADOP12

H_CADON12

H_CADOP11

H_CADON11

H_CADOP10

H_CADON10

H_CADOP9

H_CADON9

H_CADOP8

H_CADON8

H_CADOP7

H_CADON7

H_CADOP6

H_CADON6

H_CADOP5

H_CADON5

H_CADOP4

H_CADON4

H_CADOP3

H_CADON3

H_CADOP2

H_CADON2

H_CADOP1

H_CADON1

H_CADOP0

H_CADON0

H_CLKOP1

H_CLKON1

H_CLKOP0

H_CLKON0

H_CTLOP0

H_CTLON0

C533

C533

4.7U_0805_10V4Z

4.7U_0805_10V4Z

H_CADON15 (10)

H_CADOP14 (10)

H_CADON14 (10)

H_CADOP13 (10)

H_CADON13 (10)

H_CADOP12 (10)

H_CADON12 (10)

H_CADOP11 (10)

H_CADON11 (10)

H_CADOP10 (10)

H_CADON10 (10)

H_CADOP9 (10)

H_CADON9 (10)

H_CADOP8 (10)

H_CADON8 (10)

H_CADOP7 (10)

H_CADON7 (10)

H_CADOP6 (10)

H_CADON6 (10)

H_CADOP5 (10)

H_CADON5 (10)

H_CADOP4 (10)

H_CADON4 (10)

H_CADOP3 (10)

H_CADON3 (10)

H_CADOP2 (10)

H_CADON2 (10)

H_CADOP1 (10)

H_CADON1 (10)

H_CADOP0 (10)

H_CADON0 (10)

H_CLKOP1 (10)

H_CLKON1 (10)

H_CLKOP0 (10)

H_CLKON0 (10)

H_CTLOP0 (10)

H_CTLON0 (10)

+3VS

12

R88

R88

10K_0402_5%

10K_0402_5%

FAN_SPEED1(27,28)

+5VS

+VCC_FAN1

EN_DFAN1(27,28)

FAN Conn

+5VS

12

D20

D20

1SS355_SOD323-2

1SS355_SOD323-2

12

D21

D21

BAS16_SOT23-3

BAS16_SOT23-3

Update Footprint

EN_DFAN1

1

C310

C310

10U_0805_10V4Z

10U_0805_10V4Z

2

W=40mils

+VCC_FAN1

FAN1

1

C52

C52

1000P_0402_50V7K

1000P_0402_50V7K

2

U11

U11

1

VEN

2

VIN

3

VO

4

VSET

G993P1UF_SOP8

G993P1UF_SOP8

FAN1 Conn

1 2

C510 10U_0805_10V4Z

C510 10U_0805_10V4Z

1 2

C509 1000P_0402_50V7K

C509 1000P_0402_50V7K

ACES_85205-03001

ACES_85205-03001

8

GND

7

GND

6

GND

5

GND

JP16

JP16

1

2

3

+1.2V_HT

1

2

C542

C542

4.7U_0805_10V4Z

4.7U_0805_10V4Z

LAYOUT: Place bypass cap on topside of board

A A

5

C541

C541

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

2

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

1

2

C540

C540

0.22U_0402_10V4Z

0.22U_0402_10V4Z

C536

C536

0.22U_0402_10V4Z

0.22U_0402_10V4Z

1

2

C538

C538

180P_0402_50V8J

180P_0402_50V8J

C539

C539

180P_0402_50V8J

180P_0402_50V8J

1

1

2

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

AMD CPU HT I/F

AMD CPU HT I/F

AMD CPU HT I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

Date: Sheet

Date: Sheet

2

Date: Sheet

442Friday, April 20, 2007

442Friday, April 20, 2007

442Friday, April 20, 2007

1

1.0

1.0

1.0

of

of

of

A

hexainf@hotmail.com

GRATIS - FOR FREE

B

C

D

E

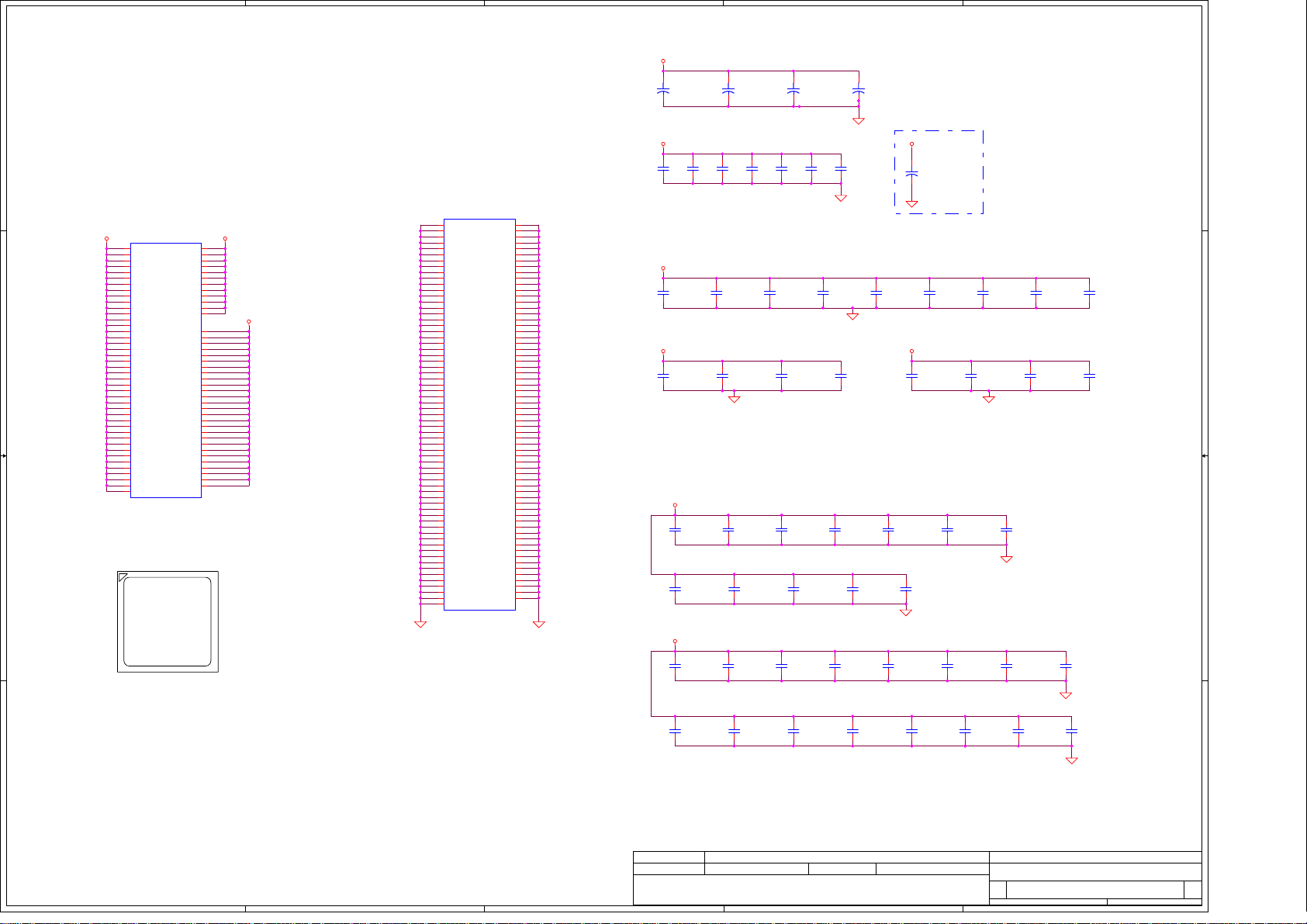

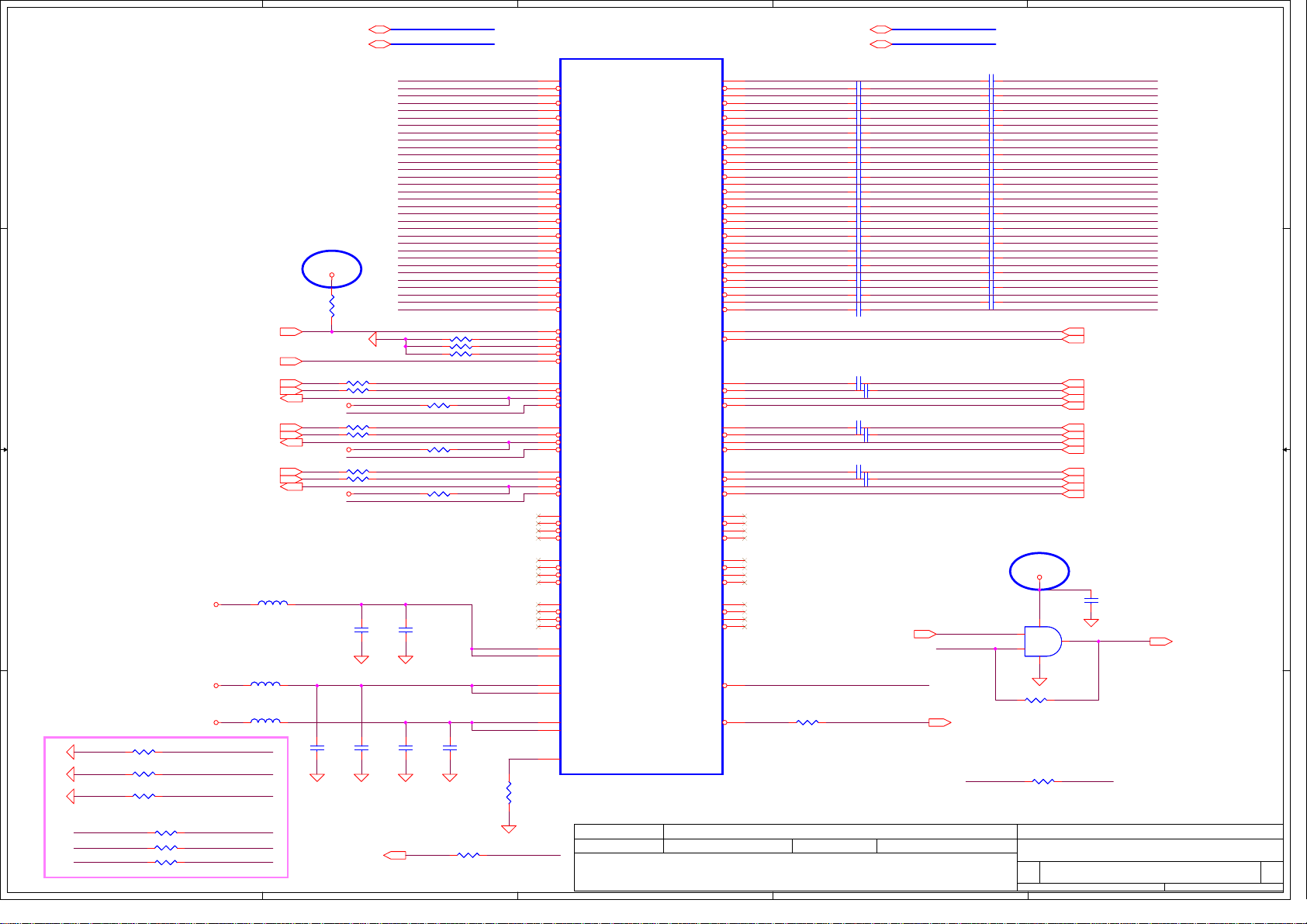

Processor DDR2 Memory Interface

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+1.8V

4 4

3 3

2 2

1 1

12

R386

R386

39.2_0402_1%~D

39.2_0402_1%~D

R388

R388

12

39.2_0402_1%~D

39.2_0402_1%~D

PLACE THEM CLOSE TO

CPU WITHIN 1"

DDR_CS3_DIMMA#(8)

DDR_CS2_DIMMA#(8)

DDR_CS1_DIMMA#(8)

DDR_CS0_DIMMA#(8)

DDR_CS3_DIMMB#(9)

DDR_CS2_DIMMB#(9)

DDR_CS1_DIMMB#(9)

DDR_CS0_DIMMB#(9)

DDR_CKE1_DIMMB(9)

DDR_CKE0_DIMMB(9)

DDR_CKE1_DIMMA(8)

DDR_CKE0_DIMMA(8)

DDR_A_MA[15..0](8)

DDR_A_BS#2(8)

DDR_A_BS#1(8)

DDR_A_BS#0(8)

DDR_A_RAS#(8)

DDR_A_CAS#(8)

DDR_A_WE#(8)

DDR_A_CLK2

DDR_A_CLK#2

DDR_A_CLK1

DDR_A_CLK#1

PLACE CLOSE TO PROCESSOR

WITHIN 1.2 INCH

+1.8V

R228

R228

1K_0402_1%

1K_0402_1%

R222

R222

1K_0402_1%

1K_0402_1%

TP2PAD TP2PAD

M_ZN

M_ZP

10:8:10:8:10

DDR_CS3_DIMMA#

DDR_CS2_DIMMA#

DDR_CS1_DIMMA#

DDR_CS0_DIMMA#

DDR_CS3_DIMMB#

DDR_CS2_DIMMB#

DDR_CS1_DIMMB#

DDR_CS0_DIMMB#

DDR_CKE1_DIMMB

DDR_CKE0_DIMMB

DDR_CKE1_DIMMA

DDR_CKE0_DIMMA

1

C336

C336

1.5P_0402_50V8C

1.5P_0402_50V8C

2

1

C344

C344

1.5P_0402_50V8C

1.5P_0402_50V8C

2

12

1

12

2

1000P_0402_50V7K

1000P_0402_50V7K

+0.9VREF_CPU

W17

VTT_SENSE

Y10

AE10

AF10

V19

J22

V22

T19

Y26

J24

W24

U23

H26

J23

J20

DDR_A_MA15

DDR_A_MA14

DDR_A_MA13

DDR_A_MA12

DDR_A_MA11

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA7

DDR_A_MA6

DDR_A_MA5

DDR_A_MA4

DDR_A_MA3

DDR_A_MA2

DDR_A_MA1

DDR_A_MA0

DDR_A_BS#2

DDR_A_BS#1

DDR_A_BS#0

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

C358

C358

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

1

C363

C363

1000P_0402_50V7K

1000P_0402_50V7K

2

VDD_VREF_SUS_CPU

LAYOUT:PLACE CLOSE TO CPU

JP22B

JP22B

M_VREF

VTT_SENSE

M_ZN

M_ZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

FOX_PZ63823-284S-41F

FOX_PZ63823-284S-41F

Athlon 64 S1

Processor

Socket

CPU_VREF_REF

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+0.9V

D10

VTT1

C10

VTT2

B10

VTT3

AD10

VTT4

W10

VTT5

AC10

VTT6

AB10

VTT7

AA10

VTT8

A10

VTT9

DDR_A_CLK2

Y16

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

DDRII Cmd/Ctrl//Clk

DDRII Cmd/Ctrl//Clk

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

1

C345

C345

2

1000P_0402_50V7K

1000P_0402_50V7K

DDR_A_CLK#2

AA16

DDR_A_CLK1

E16

DDR_A_CLK#1

F16

DDR_B_CLK2

AF18

DDR_B_CLK#2

AF17

DDR_B_CLK1

A17

DDR_B_CLK#1

A18

DDR_B_ODT1

W23

DDR_B_ODT0

W26

DDR_A_ODT1

V20

DDR_A_ODT0

U19

DDR_B_MA15

J25

DDR_B_MA14

J26

DDR_B_MA13

W25

DDR_B_MA12

L23

DDR_B_MA11

L25

DDR_B_MA10

U25

DDR_B_MA9

L24

DDR_B_MA8

M26

DDR_B_MA7

L26

DDR_B_MA6

N23

DDR_B_MA5

N24

DDR_B_MA4

N25

DDR_B_MA3

N26

DDR_B_MA2

P24

DDR_B_MA1

P26

DDR_B_MA0

T24

DDR_B_BS#2

K26

DDR_B_BS#1

T26

DDR_B_BS#0

U26

DDR_B_RAS#

U24

DDR_B_CAS#

V26

DDR_B_WE#

U22

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK1

DDR_B_CLK#1

PLACE CLOSE TO PROCESSOR

WITHIN 1.2 INCH

1

2

C357

C357

1

2

1

2

+0.9VREF_CPU

1

C350

C350

1U_0402_6.3V4Z

1U_0402_6.3V4Z

2

C349

C349

1.5P_0402_50V8C

1.5P_0402_50V8C

C348

C348

1.5P_0402_50V8C

1.5P_0402_50V8C

DDR_A_CLK2 (8)

DDR_A_CLK#2 (8)

DDR_A_CLK1 (8)

DDR_A_CLK#1 (8)

DDR_B_CLK2 (9)

DDR_B_CLK#2 (9)

DDR_B_CLK1 (9)

DDR_B_CLK#1 (9)

DDR_B_ODT1 (9)

DDR_B_ODT0 (9)

DDR_A_ODT1 (8)

DDR_A_ODT0 (8)

DDR_B_MA[15..0] (9)

DDR_B_BS#2 (9)

DDR_B_BS#1 (9)

DDR_B_BS#0 (9)

DDR_B_RAS# (9)

DDR_B_CAS# (9)

DDR_B_WE# (9)

DDR_B_D[63..0](9)

To reverse SODIMM socket

DDR_B_DM[7..0](9) DDR_A_DM[7..0] (8)

DDR_B_DQS7(9)

DDR_B_DQS#7(9)

DDR_B_DQS6(9)

DDR_B_DQS#6(9)

DDR_B_DQS5(9)

DDR_B_DQS#5(9)

DDR_B_DQS4(9)

DDR_B_DQS#4(9)

DDR_B_DQS3(9)

DDR_B_DQS#3(9)

DDR_B_DQS2(9)

DDR_B_DQS#2(9)

DDR_B_DQS1(9)

DDR_B_DQS#1(9)

DDR_B_DQS0(9)

DDR_B_DQS#0(9)

DDR_B_D63

DDR_B_D62

DDR_B_D61

DDR_B_D60

DDR_B_D59

DDR_B_D58

DDR_B_D57

DDR_B_D56

DDR_B_D55

DDR_B_D54

DDR_B_D53

DDR_B_D52

DDR_B_D51

DDR_B_D50

DDR_B_D49

DDR_B_D48

DDR_B_D47

DDR_B_D46

DDR_B_D45

DDR_B_D44

DDR_B_D43

DDR_B_D42

DDR_B_D41

DDR_B_D40

DDR_B_D39

DDR_B_D38

DDR_B_D37

DDR_B_D36

DDR_B_D35

DDR_B_D34

DDR_B_D33

DDR_B_D32

DDR_B_D31

DDR_B_D30

DDR_B_D29

DDR_B_D28

DDR_B_D27

DDR_B_D26

DDR_B_D25

DDR_B_D24

DDR_B_D23

DDR_B_D22

DDR_B_D21

DDR_B_D20

DDR_B_D19

DDR_B_D18

DDR_B_D17

DDR_B_D16

DDR_B_D15

DDR_B_D14

DDR_B_D13

DDR_B_D12

DDR_B_D11

DDR_B_D10

DDR_B_D9

DDR_B_D8

DDR_B_D7

DDR_B_D6

DDR_B_D5

DDR_B_D4

DDR_B_D3

DDR_B_D2

DDR_B_D1

DDR_B_D0

DDR_B_DM7

DDR_B_DM6

DDR_B_DM5

DDR_B_DM4

DDR_B_DM3

DDR_B_DM2

DDR_B_DM1

DDR_B_DM0

DDR_B_DQS7

DDR_B_DQS#7

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS0

DDR_B_DQS#0

JP22C

JP22C

AD11

MB_DATA63

AF11

MB_DATA62

AF14

MB_DATA61

AE14

MB_DATA60

Y11

MB_DATA59

AB11

MB_DATA58

AC12

MB_DATA57

AF13

MB_DATA56

AF15

MB_DATA55

AF16

MB_DATA54

AC18

MB_DATA53

AF19

MB_DATA52

AD14

MB_DATA51

AC14

MB_DATA50

AE18

MB_DATA49

AD18

MB_DATA48

AD20

MB_DATA47

AC20

MB_DATA46

AF23

MB_DATA45

AF24

MB_DATA44

AF20

MB_DATA43

AE20

MB_DATA42

AD22

MB_DATA41

AC22

MB_DATA40

AE25

MB_DATA39

AD26

MB_DATA38

AA25

MB_DATA37

AA26

MB_DATA36

AE24

MB_DATA35

AD24

MB_DATA34

AA23

MB_DATA33

AA24

MB_DATA32

G24

MB_DATA31

G23

MB_DATA30

D26

MB_DATA29

C26

MB_DATA28

G26

MB_DATA27

G25

MB_DATA26

E24

MB_DATA25

E23

MB_DATA24

C24

MB_DATA23

B24

MB_DATA22

C20

MB_DATA21

B20

MB_DATA20

C25

MB_DATA19

D24

MB_DATA18

A21

MB_DATA17

D20

MB_DATA16

D18

MB_DATA15

C18

MB_DATA14

D14

MB_DATA13

C14

MB_DATA12

A20

MB_DATA11

A19

MB_DATA10

A16

MB_DATA9

A15

MB_DATA8

A13

MB_DATA7

D12

MB_DATA6

E11

MB_DATA5

G11

MB_DATA4

B14

MB_DATA3

A14

MB_DATA2

A11

MB_DATA1

C11

MB_DATA0

AD12

MB_DM7

AC16

MB_DM6

AE22

MB_DM5

AB26

MB_DM4

E25

MB_DM3

A22

MB_DM2

B16

MB_DM1

A12

MB_DM0

AF12

MB_DQS_H7

AE12

MB_DQS_L7

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AC25

MB_DQS_H4

AC26

MB_DQS_L4

F26

MB_DQS_H3

E26

MB_DQS_L3

A24

MB_DQS_H2

A23

MB_DQS_L2

D16

MB_DQS_H1

C16

MB_DQS_L1

C12

MB_DQS_H0

B12

MB_DQS_L0

FOX_PZ63823-284S-41F

FOX_PZ63823-284S-41F

DDRII Data

DDRII Data

Athlon 64 S1

Processor Socket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

DDR_A_D63

DDR_A_D62

DDR_A_D61

DDR_A_D60

DDR_A_D59

DDR_A_D58

DDR_A_D57

DDR_A_D56

DDR_A_D55

DDR_A_D54

DDR_A_D53

DDR_A_D52

DDR_A_D51

DDR_A_D50

DDR_A_D49

DDR_A_D48

DDR_A_D47

DDR_A_D46

DDR_A_D45

DDR_A_D44

DDR_A_D43

DDR_A_D42

DDR_A_D41

DDR_A_D40

DDR_A_D39

DDR_A_D38

DDR_A_D37

DDR_A_D36

DDR_A_D35

DDR_A_D34

DDR_A_D33

DDR_A_D32

DDR_A_D31

DDR_A_D30

DDR_A_D29

DDR_A_D28

DDR_A_D27

DDR_A_D26

DDR_A_D25

DDR_A_D24

DDR_A_D23

DDR_A_D22

DDR_A_D21

DDR_A_D20

DDR_A_D19

DDR_A_D18

DDR_A_D17

DDR_A_D16

DDR_A_D15

DDR_A_D14

DDR_A_D13

DDR_A_D12

DDR_A_D11

DDR_A_D10

DDR_A_D9

DDR_A_D8

DDR_A_D7

DDR_A_D6

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D2

DDR_A_D1

DDR_A_D0

DDR_A_DM7

DDR_A_DM6

DDR_A_DM5

DDR_A_DM4

DDR_A_DM3

DDR_A_DM2

DDR_A_DM1

DDR_A_DM0

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_D[63..0] (8)

DDR_A_DQS7 (8)

DDR_A_DQS#7 (8)

DDR_A_DQS6 (8)

DDR_A_DQS#6 (8)

DDR_A_DQS5 (8)

DDR_A_DQS#5 (8)

DDR_A_DQS4 (8)

DDR_A_DQS#4 (8)

DDR_A_DQS3 (8)

DDR_A_DQS#3 (8)

DDR_A_DQS2 (8)

DDR_A_DQS#2 (8)

DDR_A_DQS1 (8)

DDR_A_DQS#1 (8)

DDR_A_DQS0 (8)

DDR_A_DQS#0 (8)

To normal SODIMM socket

A1

AF1

A26

Athlon 64 S1g1

uPGA638

Top View

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Title

Title

Title

AMD CPU DDRII MEMORY I/F

AMD CPU DDRII MEMORY I/F

AMD CPU DDRII MEMORY I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

Date: Sheet

Date: Sheet

Date: Sheet

E

of

of

of

542Friday, April 20, 2007

542Friday, April 20, 2007

542Friday, April 20, 2007

1.0

1.0

1.0

5

+2.5VS

1

C266

C266

FCM2012C-800_0805

FCM2012C-800_0805

22U_0805_6.3V6M

22U_0805_6.3V6M

D D

C C

2

HTCPU_PWRGD(10)

HTCPU_STOP#(10)

MCP_PWRGD(15,18,27,28)

HTCPU_RST#(10)

1 2

R375

R375

0_0402_5% @

0_0402_5% @

1 2

+1.8V

L28

L28

MCP_PWRGD_R

1

C276

C276

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

+1.8V

12

R379

R379

300_0402_5%

300_0402_5%

+1.8V

12

R184

R184

300_0402_5%

300_0402_5%

+1.8V

12

R373

R373

300_0402_5%

300_0402_5%

1

C271

C271

2

0.22U_0603_16V7K

0.22U_0603_16V7K

+1.8V+3VS

12

R381

R381

4.7K_0402_5%

4.7K_0402_5%

@

@

5

U26

U26

2

P

B

1

A

G

NC7SZ08P5X_NL_SC70-5

NC7SZ08P5X_NL_SC70-5

3

@

@

1 2

R380 0_0402_5%

R380 0_0402_5%

+1.8V

5

U9

U9

2

P

B

1

A

G

NC7SZ08P5X_NL_SC70-5

NC7SZ08P5X_NL_SC70-5

3

@

@

1 2

R183 0_0402_5%

R183 0_0402_5%

+1.8V

5

U25

U25

2

P

B

1

A

G

NC7SZ08P5X_NL_SC70-5

NC7SZ08P5X_NL_SC70-5

3

@

@

1 2

R374 0_0402_5%

R374 0_0402_5%

1

C277

C277

3300P_0402_50V7K

3300P_0402_50V7K

2

C543 0.1U_0402_16V4Z

C543 0.1U_0402_16V4Z

1 2

4

1 2

Y

R383 0_0402_5%

R383 0_0402_5%

4

1 2

Y

R189 0_0402_5%

R189 0_0402_5%

4

1 2

Y

R377 0_0402_5%

R377 0_0402_5%

4

W=50mils

place them to CPU within 1"

@

@

@

@

@

@

+1.8V

CPU_SIC(15)

CPU_SID(15)

+1.2V_HT

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_HT_RESET#

R370 300_0402_5%R370 300_0402_5%

1 2

R371 300_0402_5%R371 300_0402_5%

1 2

R369 0_0402_5%R369 0_0402_5%

1 2

R368 0_0402_5%R368 0_0402_5%

1 2

R378 44.2_0603_1%R378 44.2_0603_1%

1 2

R376 44.2_0603_1%R376 44.2_0603_1%

1 2

CPUCLK(10)

CPUCLK#(10)

3

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

+2.5VS_VDDA

CPU_SIC_R

CPU_SID_R

CPU_HTREF1

CPU_HTREF0 VID0

5:10

CPU_VCC_SENSE(41)

CPU_VSS_SENSE(41)

C545

C545

1 2

3900P_0402_50V7K

3900P_0402_50V7K

C544

C544

1 2

3900P_0402_50V7K

3900P_0402_50V7K

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

169_0402_1%

169_0402_1%

12

R382

R382

R199 300_0402_5%R199 300_0402_5%

R198 1K_0402_5%

R198 1K_0402_5%

R188 510_0402_5%

R188 510_0402_5%

R197 300_0402_5%R197 300_0402_5%

R387 510_0402_5%R387 510_0402_5%

R385 300_0402_5%R385 300_0402_5%

R215 300_0402_5%R215 300_0402_5%

TP3PAD TP3PAD

TP1PAD TP1PAD

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_THERMDC

CPU_THERMDA

10:10

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2

ATHLON Control and Debug

JP22D

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_VCC_SENSE

CPU_VSS_SENSE

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

+1.8V

JP22D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

AF4

SIC

AF5

SID

P6

HTREF1

R6

HTREF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

TEST25_HE9TEST29_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

THERMDC

W8

THERMDA

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

FOX_PZ63823-284S-41F

FOX_PZ63823-284S-41F

AMD NPT S1 SOCKET

Processor Socket

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

DBREQ_L

TEST29_L

MISC

MISC

TEST28_H

TEST28_L

PSI_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

VID5

VID4

VID3

VID2

VID1

VID0

TDO

H_THERMTRIP_S#

AF6

CPU_PROCHOT#_1.8

AC7

VID5

A5

VID4

C6

VID3

A6

VID2

A4

VID1

C5

B5

CPU_PRESENT#

AC6

PSI#

A3

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

5:5:5

AE7

AD7

AE8

CPU_TEST21_SCANEN

AB8

AF7

J7

H8

AF8

CPU_TEST26_BURNIN#

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

R155

R155

300_0402_5%

300_0402_5%

+1.8V

12

PSI# (41)

80.6_0402_1%

80.6_0402_1%

1

12

R156

R156

300_0402_5%

300_0402_5%

VID5 (41)

VID4 (41)

VID3 (41)

VID2 (41)

VID1 (41)

VID0 (41)

R384

R384

1 2

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

HDT Connector

12

12

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TDI

CPU_TRST#

CPU_TDO

1

2

12

R163 220_0402_5%HT@R163 220_0402_5%HT@

EC_SMB_CK2

EC_SMB_DA2

B B

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

C275

C275

2200P_0402_50V7K

A A

2200P_0402_50V7K

EC_SMB_CK2(27,28)

EC_SMB_DA2(27,28)

5

12

12

+1.8V

R160 220_0402_5%HT@R160 220_0402_5%HT@

R162 220_0402_5% HT@R162 220_0402_5% HT@

R159 220_0402_5%HT@R159 220_0402_5%HT@

R161 220_0402_5%HT@R161 220_0402_5%HT@

U4

CPU_THERMDA

CPU_THERMDC

U4

2

D+

3

D-

8

SCLK

7

SDATA

U2 CLOSE CPU,

CPU_THERMDA&CPU_THERMDC PLACE

CLOSE TO PROCESSOR WITHIN 1" INCH

+3VS

1

C269

C269

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

VDD1

ALERT#

THERM#

GND

ADM1032ARM_RM8

ADM1032ARM_RM8

JP7

JP7

2

1

4

3

6

5

8

7

10

9

12

11

14

13

16

15

18

17

20

19

22

21

2423

26

SAMTEC_ASP-68200-07

SAMTEC_ASP-68200-07

@

@

1

6

4

5

R113

R113

220_0402_5%

220_0402_5%

HT@

HT@

3V_LDT_RST#

+3VS

12

1 2

R535 0_0402_5%

R535 0_0402_5%

+3V

2

G

G

CPU_HT_RESET#

1 3

D

S

D

@

@

S

Q14

Q14

2N7002_SOT23

2N7002_SOT23

HT@

HT@

H_THERMTRIP_S# H_THERMTRIP#CPU_TMS

PVT Modify 2007/03/22

12

R186

R186

10K_0402_5%@

10K_0402_5%@

PROCHOT#(10)

R141 0_0402_5%

R141 0_0402_5%

Connect to MCP67

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+1.8V +1.8V +3V +3V

12

R114

R114

300_0402_5%

300_0402_5%

CPU_PROCHOT#_1.8

1 2

@

@

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

12

R127

R127

1K_0402_5%

1K_0402_5%

2

Q16

Q16

3 1

MMBT3904_SOT23

MMBT3904_SOT23

1 2

R115 0_0402_5%

R115 0_0402_5%

10K_0402_5%

10K_0402_5%

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

@

@

+1.8V +3VS

12

R133

R133

CPU_PH_G

B

B

2

Q19

Q19

E

E

3 1

MMBT3904_SOT23

MMBT3904_SOT23

C

C

12

R116

R116

10K_0402_5%

10K_0402_5%

12

R130

R130

4.7K_0402_5%

4.7K_0402_5%

12

2

3 1

R117

R117

1K_0402_5%@

1K_0402_5%@

Q15

Q15

MMBT3904_SOT23

MMBT3904_SOT23

@

@

MAINPWON (35,36,37)

H_THERMTRIP# (10)

EC_THERM# (15,27,28)

Title

Title

Title

AMD CPU CTRL & DEBUG

AMD CPU CTRL & DEBUG

AMD CPU CTRL & DEBUG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

Date: Sheet

Date: Sheet

Date: Sheet

1

1.0

1.0

1.0

of

of

of

642Friday, April 20, 2007

642Friday, April 20, 2007

642Friday, April 20, 2007

5

hexainf@hotmail.com

GRATIS - FOR FREE

D D

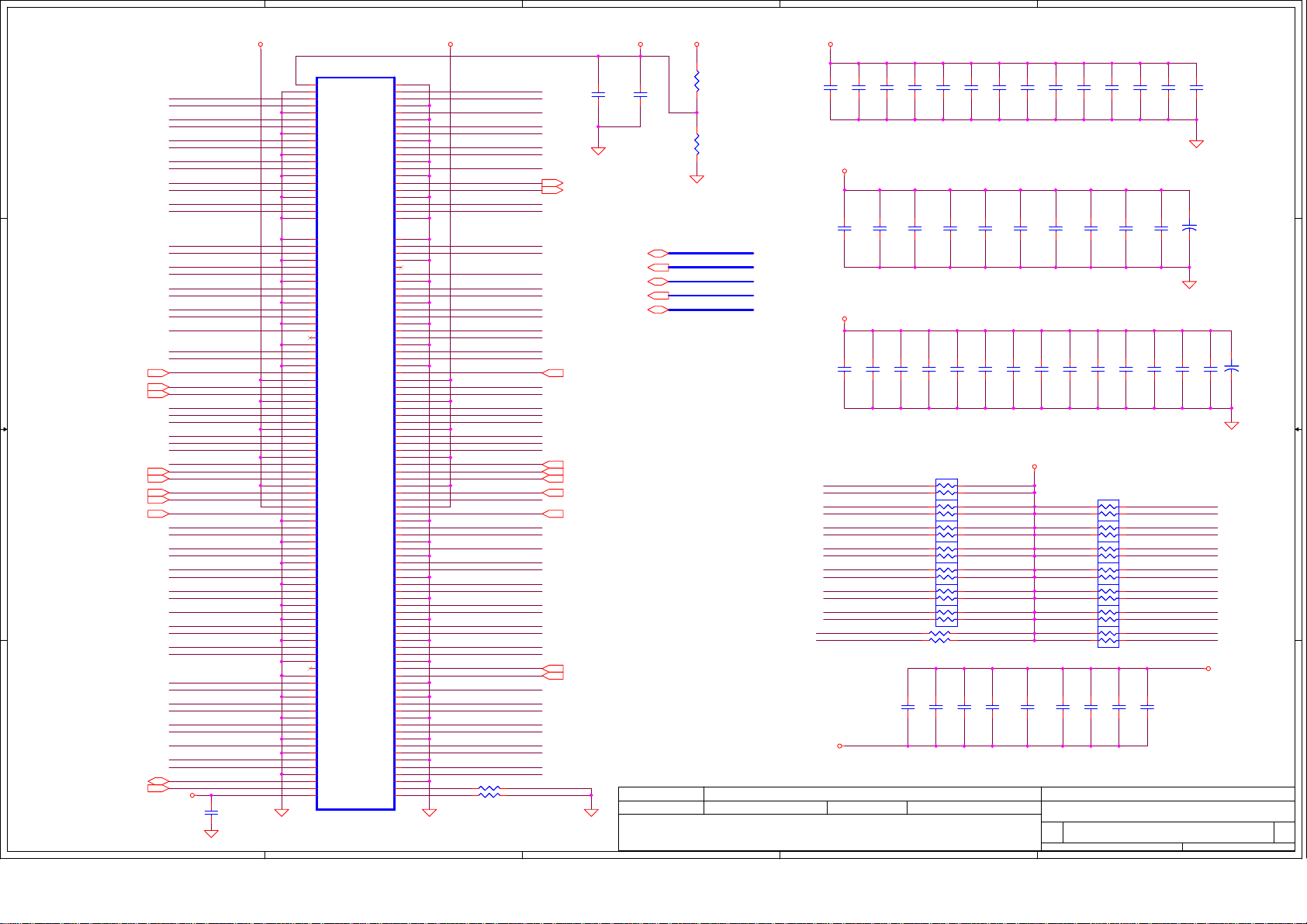

PROCESSOR POWER AND GROUND

JP22E

JP22E

AC4

VDD1

AD2

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

C C

B B

M6

M8

M10

N7

N9

N11

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

V6

V8

V10

A1

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

Power

Power

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

FOX_PZ63823-284S-41F

FOX_PZ63823-284S-41F

Athlon 64 S1

Processor Socket

Athlon 64 S1g1

uPGA638

Top View

AF1

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

+CPU_CORE+CPU_CORE

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

+1.8V

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

A26

4

JP22F

JP22F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

FOX_PZ63823-284S-41F

FOX_PZ63823-284S-41F

Athlon 64 S1

Processor Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

Ground

Ground

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3

+CPU_CORE

1

+

+

2

+CPU_CORE

1

2

C279

C279

10U_0805_10V6M

10U_0805_10V6M

C548

C548

470U_D2E_2VM_R9

470U_D2E_2VM_R9

C287

C287

10U_0805_10V6M

10U_0805_10V6M

1

1

2

2

C280

C280

10U_0805_10V6M

10U_0805_10V6M

1

+

+

C550

C550

470U_D2E_2VM_R9

470U_D2E_2VM_R9

2

C288

C288

10U_0805_10V6M

10U_0805_10V6M

1

2

1

+

+

2

1

2

C282

C282

10U_0805_10V6M

10U_0805_10V6M

C546

C546

470U_D2E_2VM_R9

470U_D2E_2VM_R9

C289

C289

10U_0805_10V6M

10U_0805_10V6M

1

2

2

1

+

+

C547

C547

330U_D2E_2.5VM_R9

330U_D2E_2.5VM_R9

2

1

2

C281

C281

10U_0805_10V6M

10U_0805_10V6M

+CPU_CORE

1

+

+

2

C551

C551

820U_E9_2.5V_M_R7

820U_E9_2.5V_M_R7

45@

45@

1

10/2 Modify

CPU SOCKET S1 DECOUPLING

+CPU_CORE

1

C319

C319

180P_0402_50V8J

180P_0402_50V8J

2

1

C333

C333

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

2

1

C327

C327

10U_0805_10V6M

10U_0805_10V6M

2

C309

C309

0.01U_0402_16V7K

0.01U_0402_16V7K

1

C328

C328

10U_0805_10V6M

10U_0805_10V6M

2

1

C353

C353

10U_0805_10V6M

10U_0805_10V6M

2

1

C324

C324

10U_0805_10V6M

10U_0805_10V6M

2

1

C343

C343

10U_0805_10V6M

10U_0805_10V6M

2

1

C316

C316

10U_0805_10V6M

10U_0805_10V6M

2

1

C361

C361

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C334

C334

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C356

C356

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

C308

C308

0.22U_0402_10V4Z

0.22U_0402_10V4Z

1

C332

C332

10U_0805_10V6M

10U_0805_10V6M

2

1

C315

C315

22U_0805_6.3V6M

22U_0805_6.3V6M

2

+CPU_CORE +1.8V

1

C318

C318

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C326

C326

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

2

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

+1.8V

1

C352

C352

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C381

C381

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

+0.9V

1

C304

C304

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C342

C342

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

2

1

C320

C320

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

C385

C385

0.01U_0402_16V7K

0.01U_0402_16V7K

1

C351

C351

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C382

C382

0.01U_0402_16V7K

0.01U_0402_16V7K

2

1

C303

C303

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C388

C388

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

2

1

C302

C302

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C362

C362

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

C340

C340

180P_0402_50V8J

180P_0402_50V8J

1

C313

C313

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C360

C360

180P_0402_50V8J

180P_0402_50V8J

2

1

C386

C386

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C312

C312

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C383

C383

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C314

C314

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C298

C298

0.22U_0402_10V4Z

0.22U_0402_10V4Z

2

1

C299

C299

1000P_0402_50V7K

1000P_0402_50V7K

2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1

C300

C300

1000P_0402_50V7K

1000P_0402_50V7K

2

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

1

C307

C307

1000P_0402_50V7K

1000P_0402_50V7K

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

1

C306

C306

1000P_0402_50V7K

1000P_0402_50V7K

2

1

2

C305

C305

180P_0402_50V8J

180P_0402_50V8J

1

2

1

C297

C297

180P_0402_50V8J

180P_0402_50V8J

2

Title

Title

Title

AMD CPU PWR & GND

AMD CPU PWR & GND

AMD CPU PWR & GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

ICW50 / ICY70 LA-3581P

Date: Sheet

Date: Sheet

Date: Sheet

C296

C296

180P_0402_50V8J

180P_0402_50V8J

1

C295

C295

180P_0402_50V8J

180P_0402_50V8J

2

1

of

of

of

742Friday, April 20, 2007

742Friday, April 20, 2007

742Friday, April 20, 2007

1.0

1.0

1.0

5

4

3

2

1

+1.8V+DIMM_VREF+1.8V+1.8V

C579 4.7U_0805_10V4ZC579 4.7U_0805_10V4Z

C428 0.1U_0402_16V4Z C428 0.1U_0402_16V4Z

JP28

JP28

1

VREF

3

DDR_A_D0

D D

C C

DDR_CKE0_DIMMA(5)

DDR_CS2_DIMMA#(5)

DDR_A_BS#2(5)

DDR_A_BS#0(5)

DDR_A_WE#(5)

DDR_A_CAS#(5)

DDR_CS1_DIMMA#(5)

DDR_A_ODT1(5)

B B

A A

MEM_SMBDATA(9,15)

MEM_SMBCLK(9,15)

DDR_A_D1

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18 DDR_A_D22

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_CKE0_DIMMA

DDR_CS2_DIMMA#

DDR_A_BS#2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_BS#0

DDR_A_WE#

DDR_A_CAS#

DDR_CS1_DIMMA#

DDR_A_ODT1

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43 DDR_A_D47

DDR_A_D48

DDR_A_D49 DDR_A_D53

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51 DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

MEM_SMBDATA

MEM_SMBCLK

+3VS

5

1

C429

C429

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

DIMM1 REV H:5.2mm (BOT)

VSS

5

DQ0

7

DQ1

9

VSS

11

DQS0#

13

DQS0

15

VSS

17

DQ2

19

DQ3

21

VSS

23

DQ8

25

DQ9

27

VSS

29

DQS1#

31

DQS1

33

VSS

35

DQ10

37

DQ11

39

VSS

41

VSS

43

DQ16

45

DQ17

47

VSS

49

DQS2#

51

DQS2

53

VSS

55

DQ18

57

DQ19

59

VSS

61

DQ24

63

DQ25

65

VSS

67

DM3

69

NC

71

VSS

73

DQ26

75

DQ27

77

VSS

79

CKE0

81

VDD

83

NC

85

BA2

87

VDD

89

A12

91

A9

93

A8

95

VDD

97

A5

99

A3

101

A1

103

VDD

105

A10/AP

107

BA0

109

WE#

111

VDD

113

CAS#

115

NC/S1#

117

VDD

119

NC/ODT1

121

VSS

123

DQ32

125

DQ33

127

VSS

129

DQS4#

131

DQS4

133

VSS

135

DQ34

137

DQ35

139

VSS

141

DQ40

143

DQ41

145

VSS

147

DM5

149

VSS

151

DQ42

153

DQ43

155

VSS

157

DQ48

159

DQ49

161

VSS

163

NC,TEST

165

VSS

167

DQS6#

169

DQS6

171

VSS

173

DQ50

175

DQ51

177

VSS

179

DQ56

181

DQ57

183

VSS

185

DM7

187

VSS

189

DQ58

191

DQ59

193

VSS

195

SDA

197

SCL

199

VDDSPD

FOX_AS0A426-M2RN-7F

FOX_AS0A426-M2RN-7F

<BOM Structure>

<BOM Structure>

DM0

VSS

DQ6

DQ7

VSS

DQ12

DQ13

VSS

DM1

VSS

CK0#

VSS

DQ14

DQ15

VSS

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

NC/CKE1

VDD

NC/A15

NC/A14

VDD

VDD

VDD

RAS#

VDD

ODT0

NC/A13

VDD

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

CK1#

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

SAO

VSS

DQ4

DQ5

VSS

CK0

A11

BA1

S0#

CK1

SA1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

NC

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

A7

94

A6

96

98

A4

100

A2

102

A0

104

106

108

110

112

114

116

118

120

NC

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

4

DDR_A_D4

DDR_A_D5

DDR_A_DM0

DDR_A_D6

DDR_A_D7

DDR_A_D12

DDR_A_D13

DDR_A_DM1

DDR_A_CLK1

DDR_A_CLK#1

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D23

DDR_A_D28

DDR_A_D29

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_D30

DDR_A_D31

DDR_CKE1_DIMMA

DDR_A_MA15

DDR_A_MA14

DDR_A_MA11

DDR_A_MA7

DDR_A_MA6DDR_A_MA8

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_A_BS#1

DDR_A_RAS#

DDR_CS0_DIMMA#

DDR_A_ODT0

DDR_A_MA13

DDR_CS3_DIMMA#

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_DQS#5

DDR_A_DQS5

DDR_A_D46

DDR_A_D52

DDR_A_CLK2

DDR_A_CLK#2

DDR_A_DM6

DDR_A_D54

DDR_A_D60

DDR_A_D61

DDR_A_DQS#7

DDR_A_DQS7

DDR_A_D62

DDR_A_D63

R281 10K_0402_5%R281 10K_0402_5%

1 2

R282 10K_0402_5%R282 10K_0402_5%

1 2

1

2

DDR_A_CLK1 (5)

DDR_A_CLK#1 (5)

DDR_A_D[0..63](5)

DDR_A_DM[0..7](5)

DDR_A_DQS[0..7](5)

DDR_A_MA[0..15](5)

DDR_A_DQS#[0..7](5)

DDR_CKE1_DIMMA (5)

DDR_A_BS#1 (5)

DDR_A_RAS# (5)

DDR_CS0_DIMMA# (5)

DDR_A_ODT0 (5)

DDR_CS3_DIMMA# (5)

DDR_A_CLK2 (5)

DDR_A_CLK#2 (5)

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

2

Issued Date

Issued Date

Issued Date

3

12

R275

R275

1K_0402_1%

1K_0402_1%

12

R274

R274

1K_0402_1%

1K_0402_1%

DDR_A_D[0..63]

DDR_A_DM[0..7]

DDR_A_DQS[0..7]

DDR_A_MA[0..15]

DDR_A_DQS#[0..7]

2006/08/18 2007/8/18

2006/08/18 2007/8/18

2006/08/18 2007/8/18

+1.8V

C399

C399

4.7U_0805_6.3V6K

4.7U_0805_6.3V6K

1

1

2

2

C413

C413

4.7U_0805_6.3V6K

4.7U_0805_6.3V6K

+1.8V

4.7U_0805_10V4Z

4.7U_0805_10V4Z

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

C407

C407

2

+0.9V

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

2

2

C436

C436

C437

C437

DDR_CKE0_DIMMA

DDR_CS2_DIMMA#

DDR_A_BS#2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_MA10

DDR_A_BS#0

DDR_A_WE#

DDR_A_CAS#

DDR_CS1_DIMMA#

DDR_CS3_DIMMA#

+0.9V

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

C427

1

2

C424

C424

0.01U_0402_16V7K

0.01U_0402_16V7K

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

C409

C409

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C434

C434

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C438

C438

C427

0.01U_0402_16V7K

0.01U_0402_16V7K

1

2

4.7U_0805_10V4Z

4.7U_0805_10V4Z

C410

C410

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C433

C433

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C439

C439

0.1U_0402_16V4Z

0.1U_0402_16V4Z

C414

C414

4.7U_0805_6.3V6K

4.7U_0805_6.3V6K

1

1

2

2

C398

C398

4.7U_0805_6.3V6K

4.7U_0805_6.3V6K

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

1

C408

C408

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C435

C435

Layout Note:

Place one cap close to every 2 pullup

resistors terminated to +0.9V

RP10 47_0404_4P2R_5%RP10 47_0404_4P2R_5%

RP11 47_0404_4P2R_5%RP11 47_0404_4P2R_5%

RP12 47_0404_4P2R_5%RP12 47_0404_4P2R_5%

RP13 47_0404_4P2R_5%RP13 47_0404_4P2R_5%

RP14 47_0404_4P2R_5%RP14 47_0404_4P2R_5%

RP9 47_0404_4P2R_5%RP9 47_0404_4P2R_5%

RP8 47_0404_4P2R_5%RP8 47_0404_4P2R_5%

R277 47_0402_1%R277 47_0402_1%

1 2

R280 47_0402_1%R280 47_0402_1%

1 2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C443

C443

Layout Note:

Place one 0.1uF cap close to every 2 pullup

resistors terminated to +0.9V

2

1

2

C426

C426

10P_0402_50V8K

10P_0402_50V8K

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

C411

C411

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

2

C431

C431

1

2

C445

C445

C425

C425

10P_0402_50V8K

10P_0402_50V8K

1

2

1

C412

C412

2