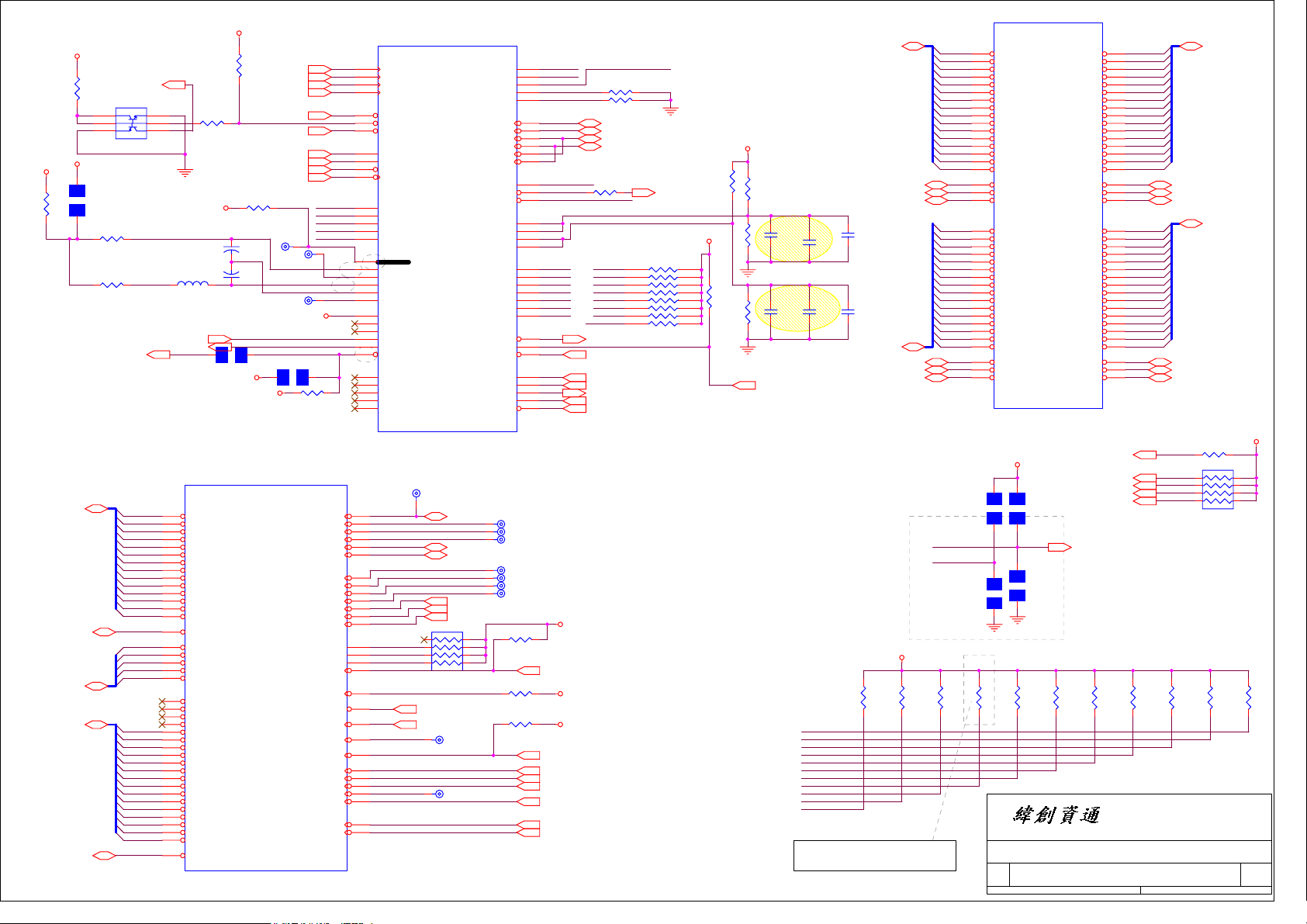

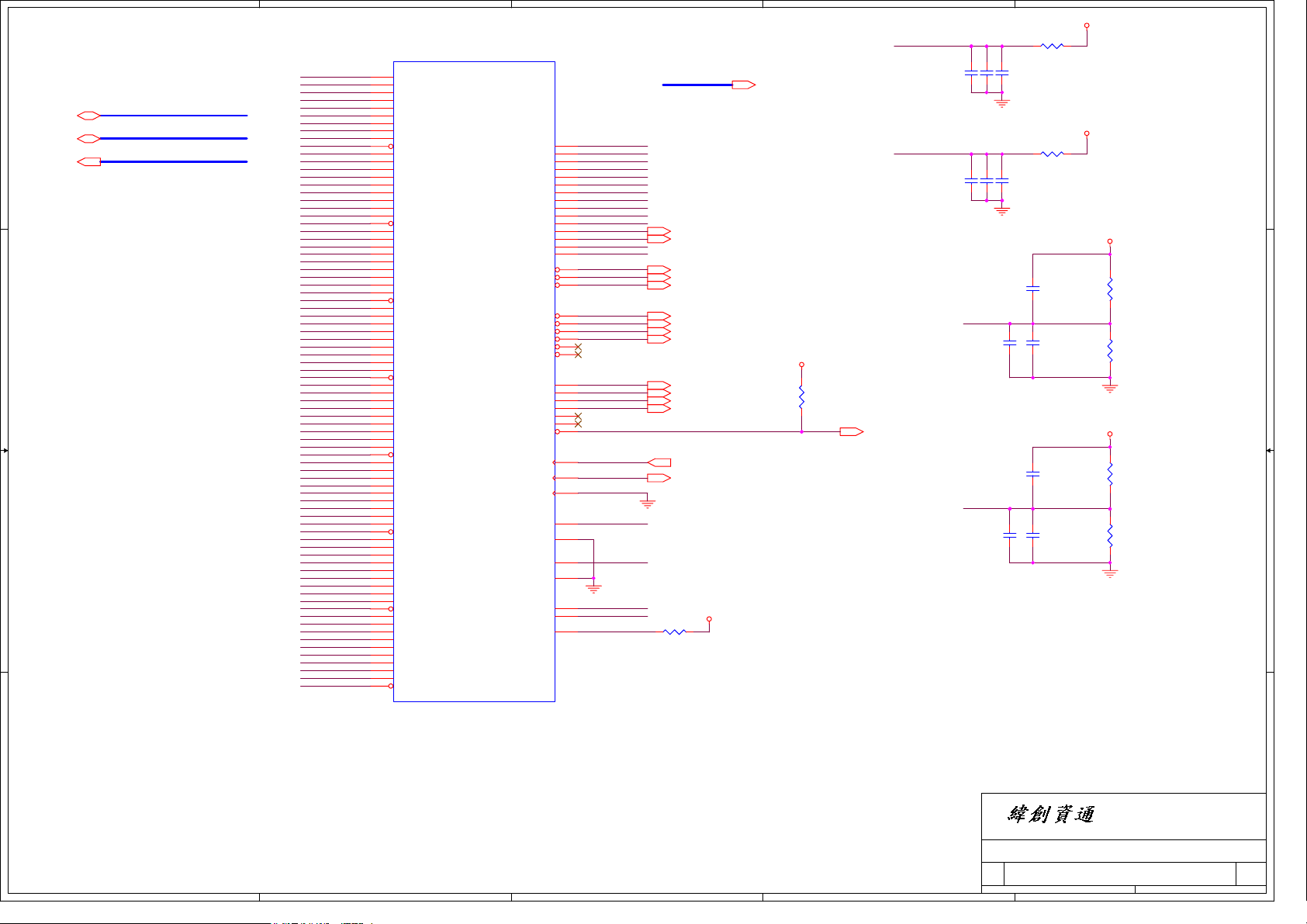

Page 1

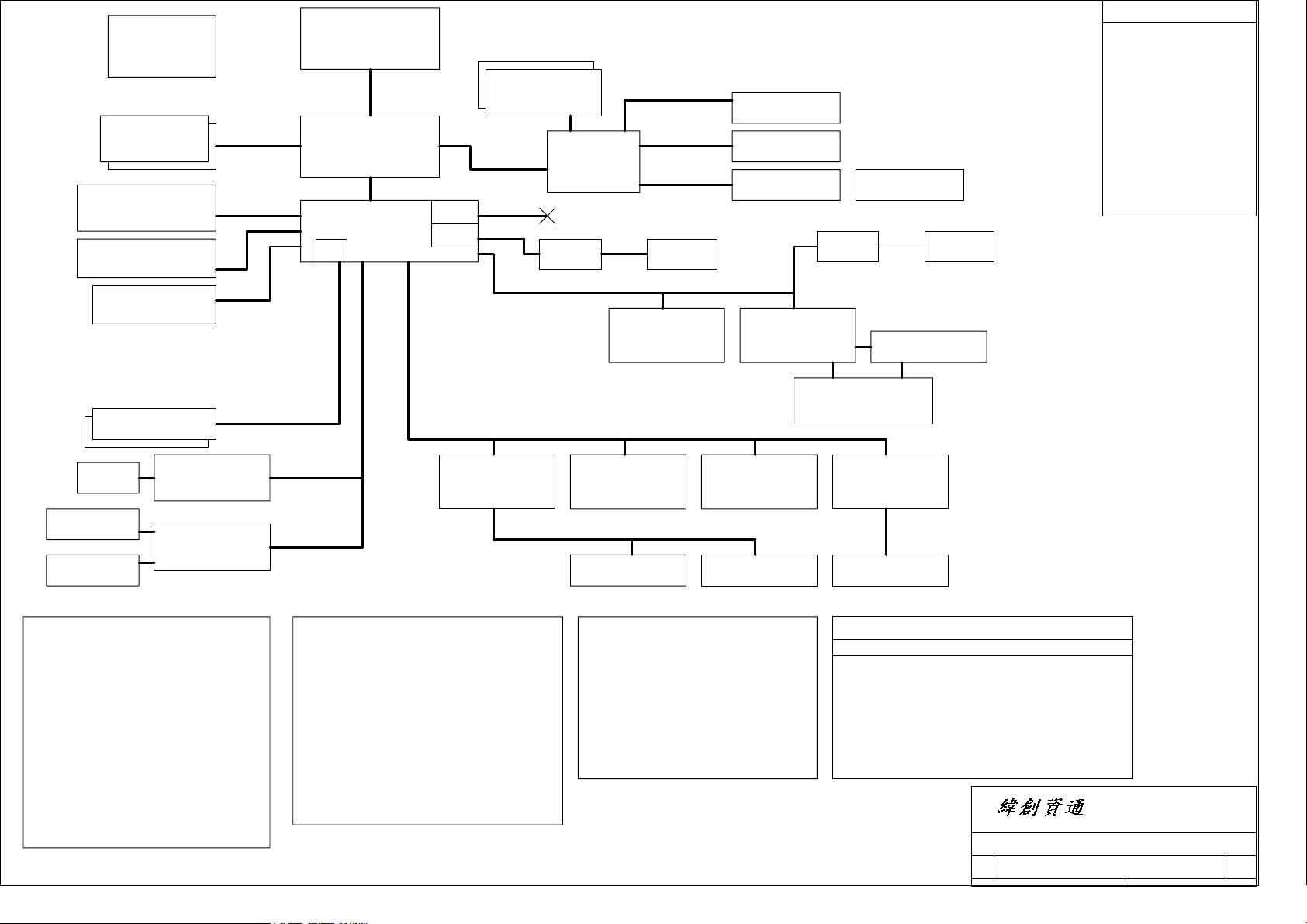

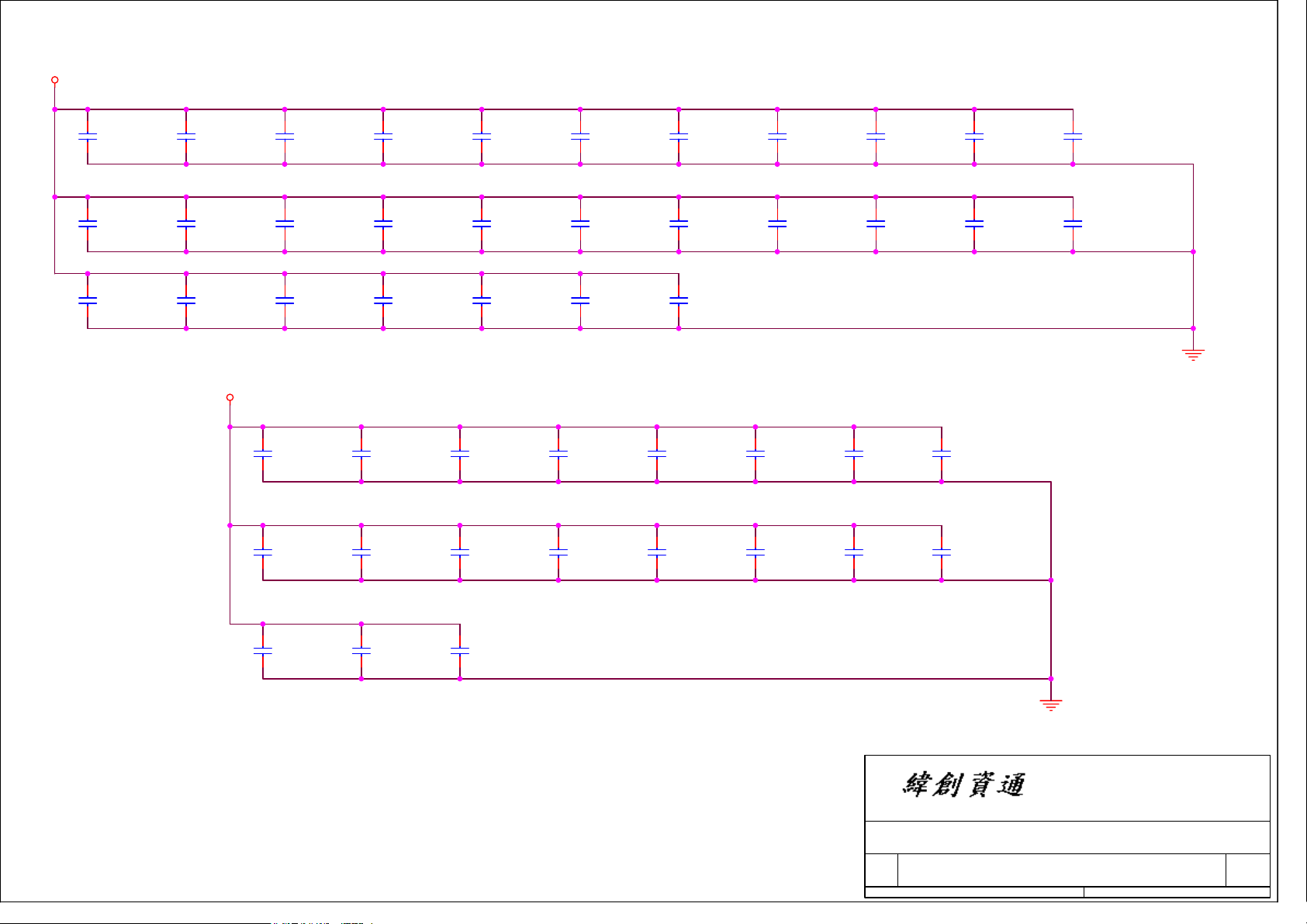

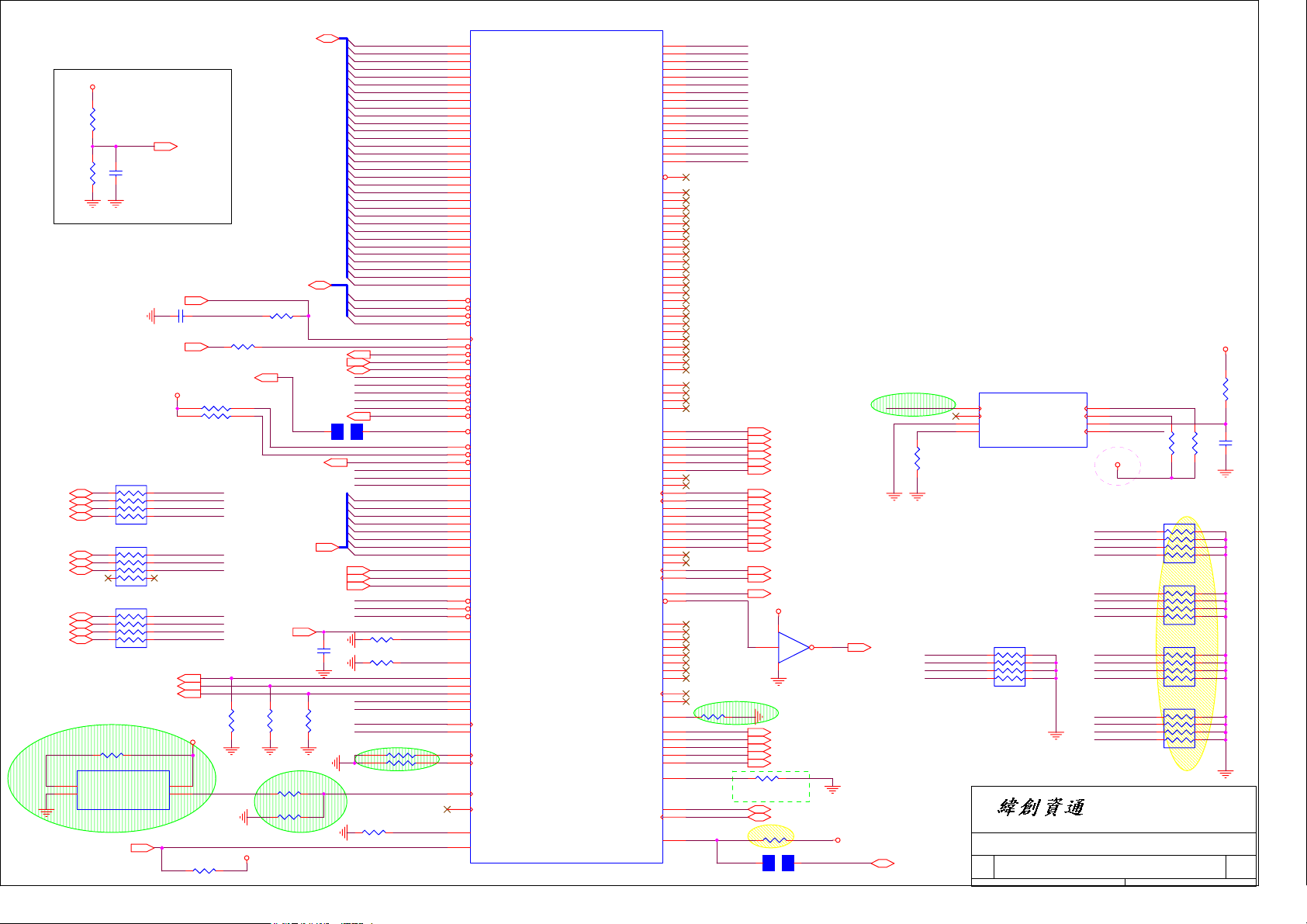

CLK GEN

ICS:ICS952004AG

DDRBUF:ICS93732

DDR * 2

11,12,13

Primary EIDE

HDD ATA100

Secondary EIDE

CD-ROM

Thermal

G768D

USB*4

3,4

2.5V

200MHz/266MHz

24

24

25

26

DesKtop-CPU

Northwood

2.2~3.06GHz

SiS645DX

SiS962

USB 2.0

962 only

W/RTC

5,6

FSB

533/400MHz

7,8,9,10

MuTIOL 66MHz

16bits/533MBs

LPC Bus

33MHz

LAN MAC

1394 MAC

962 only

20,21,22,23

TOUCAN2

VRAM*2

K4D263238M-QC40

AGP 4X

MII

1394

PCI Bus

33MHz

17

ATI M9-P

14,15,16

PHY

Agere FW802A

28 28

Dual LVDS

1394

conn.

Mini PCI

802.11a/b

(Dummy)

Project code:

PCB P/N :

REVISION :

CRT

TV

LCD

15"

CardBus

TI1520

31 29

18

18

INVERTER

19

LAN

RTL 8100BL

27

SLOT A/B

Power Switch

TPS2223DB

30

91.47Y01.001

12/18/2002

38

RJ45

27

PCB LAYER

Signal 1

L1:

GND

L2:

Signal 2

L3:

L4:

Signal 3

VCC

L5:

GND

L6:

L7:

Signal 4

L8:

Signal 5

RJ11

LINE-IN

MIC-IN

Line-Out

S/PDIF

MDC

CODEC

Sigmatel

STAC9766

POWER BOARD

SYSTEM DC/DC

MAX1631

INPUT OUTPUT

DCBATOUT

CHARGER

PIC12C509 / MAX1645

INPUT

AD+ BT+

AD+, BT+ UP+5V

5V_S5

5V_S3

3D3V_S5

OUTPUT

32,33

AC Link

26

SYSTEM DC/DC

MAX1715 / FDS9412 / APL1085 / G913C /

S2N3906

DCBATOUT

5V_S3

3D3V_S5

3D3V_LANAC

2D5V_S3 or

3D3V_S0

KBC

M38857

OUTPUTINPUT

5V_S0

3D3V_S3

3D3V_S0

3D3V_LANAC

1D8V_S5

2D5V_LANAC

1D8V_S0

1D5V_S0

LPC ROM

ST M50LPW040

34 36 36 37

PLCC32

Touch Pad

Debug Port

Internal KB Floppy

35 35 37

DDR & VDDR DC/DC

MAX1715 / CM8501 / FDS9412 /

2SB1184F5 / FDC653N

INPUT

DCBATOUT

2D5V_S3

43,45

OUTPUT

DDR_VDD

= 2D5V_S3

DDR_VTT

= 1D25V_S3

VCC_VDDR

= 2D5V_S0

SIO

NS87392

CPU VCC_CORE DC/DC

DESKTOP CPU

Controller-ISL6301 Drive-ISL6207 * 3 (3 Phase)

INPUT OUTPUT

DCBATOUT VCC_CORE

RANGE RANGE

9V~20V 1.1Vcore~1.85Vcore

V_VID V_AGTL+ BUS

1D2V_VID(Northwood only)

VCC_CORE(Willamette)

WILLAMETTE/NORTHWOOD) CPU

VCC_CORE

39,40,4144

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

BLOCK DIAGRAM

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

TOUCAN2

147Wednesday, December 18, 2002

1

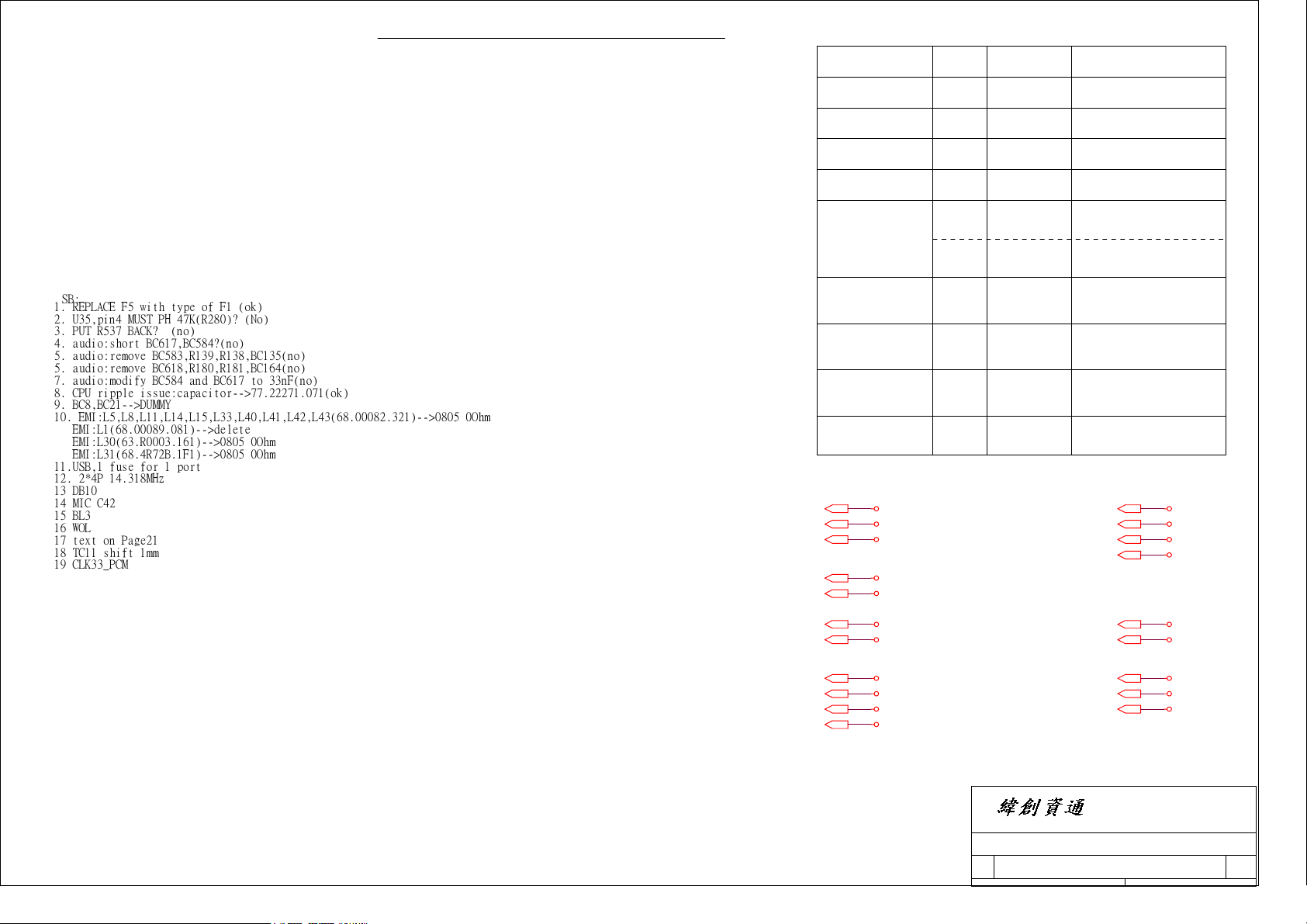

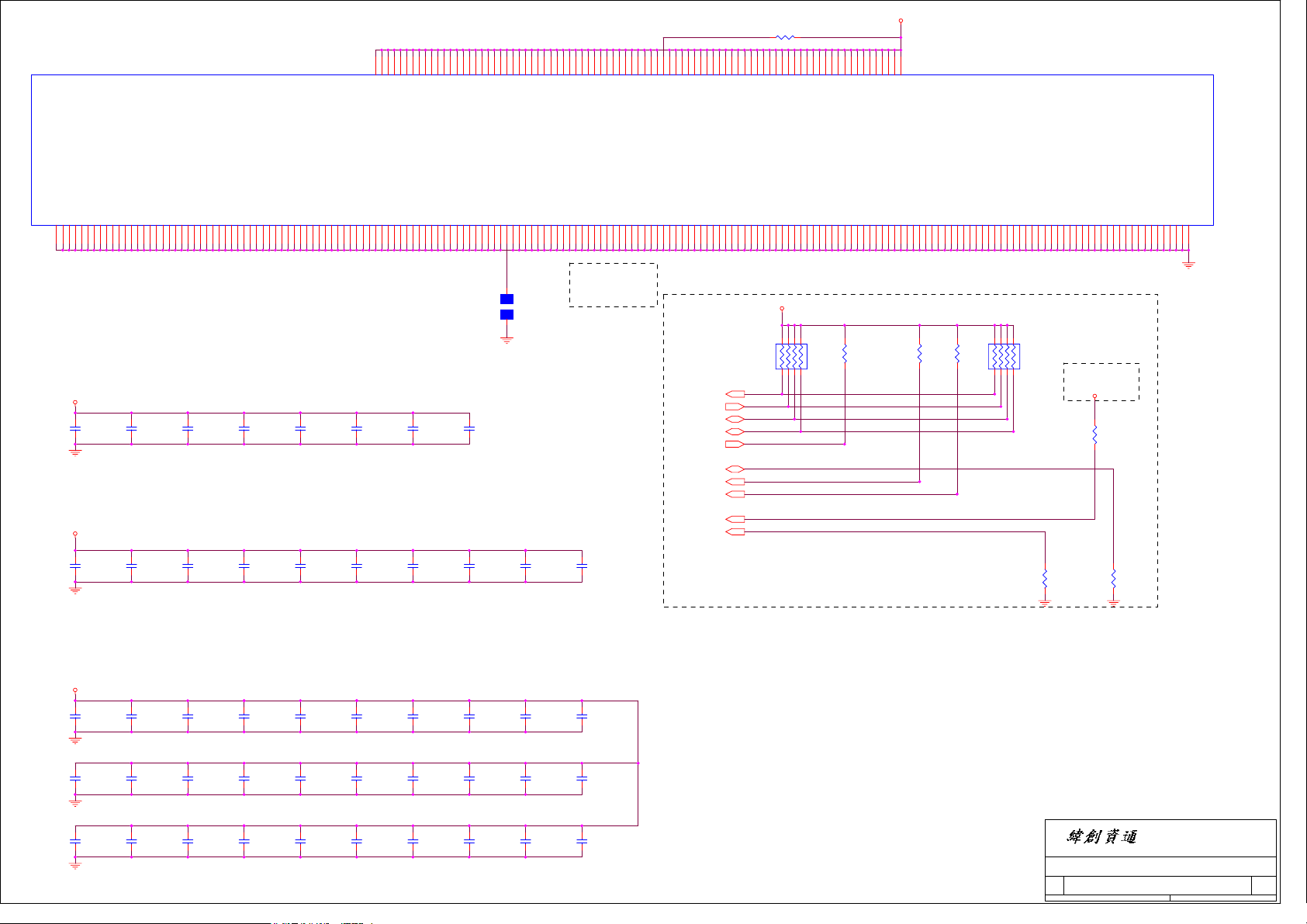

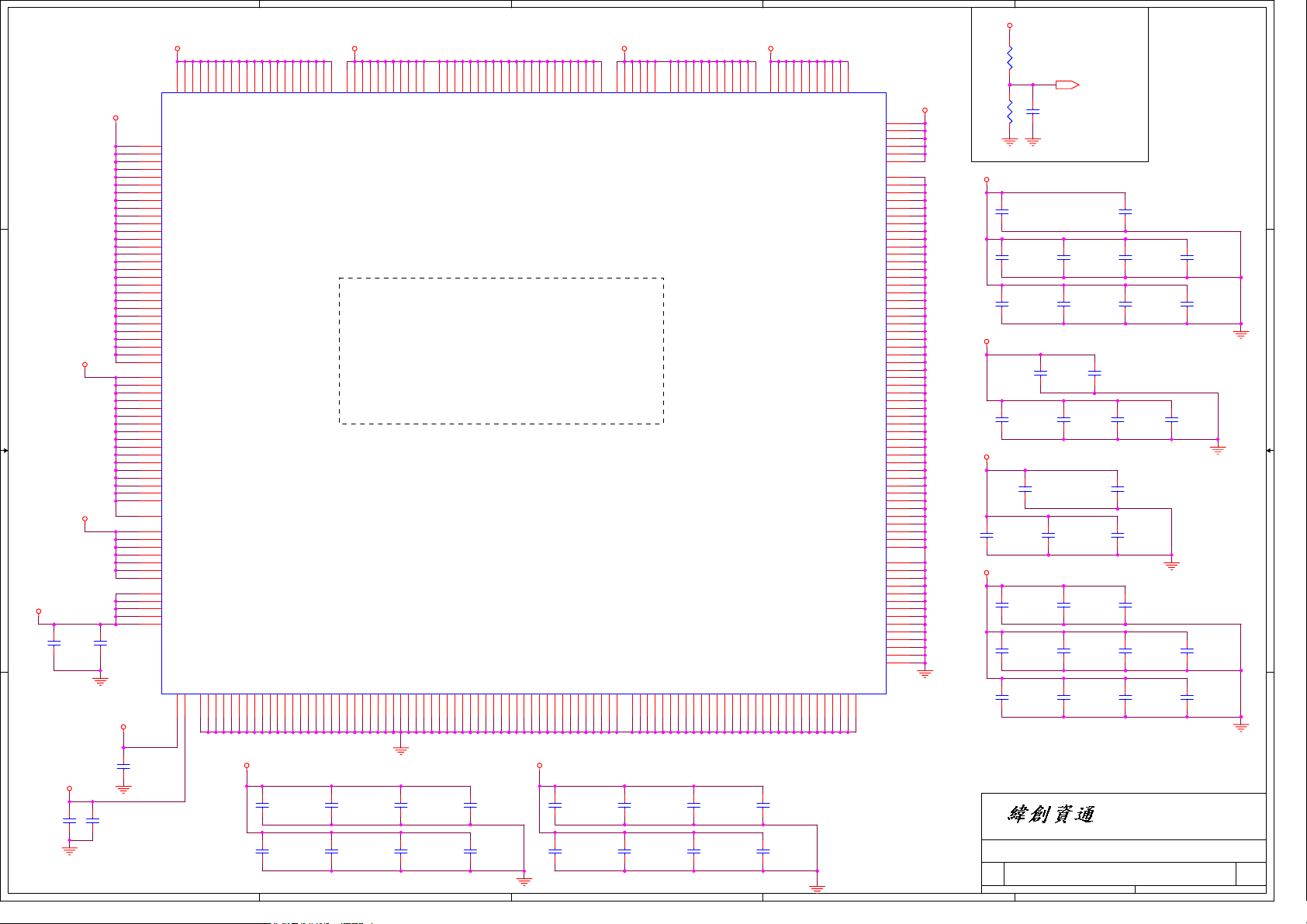

Page 2

REVISION HISTORY

PCI RESOURCE TABLE

SA-2:

1.GPIO 16,pull-high take it away,(DUMMY R537)

2.CODEC,S/PDIF,10K PULL DOWN (ADD R539)

3.PANEL ID FROM SIO

4.LCDPOWER_S0 FUSE/1A (RAYCHEM)

5.USB .fuse-->RAYCHEM

6.RTL8100.PIN80-->1K-->3D3V

7.FDD POWER RAIL-->1A FUSE

8.CODECP/N UPDATE:71.09766.A0G

9.DB1,DB3,DB4 CHANGE SOURCE

SB:

1. REPLACE F5 with type of F1 (ok

. U35,pin4 MUST PH 47K(R280)? (No

. PUT R537 BACK? (no

. audio:short BC617,BC584?(no

. audio:remove BC583,R139,R138,BC135(no

. audio:remove BC618,R180,R181,BC164(no

. audio:modify BC584 and BC617 to 33nF(no

. CPU ripple issue:capacitor-->77.22271.071(ok)9

. BC8,BC21-->DUMM

0. EMI:L5,L8,L11,L14,L15,L33,L40,L41,L42,L43(68.00082.321)-->0805 0Oh

EMI:L1(68.00089.081)-->delete

EMI:L30(63.R0003.161)-->0805 0Ohm

EMI:L31(68.4R72B.1F1)-->0805 0Ohm1

1.USB,1 fuse for 1 port

2. 2*4P 14.318MHz1

3 DB1

01

4 MIC C421

5 BL31

6 WOL1

7 text on Page2

8 TC11 shift 1m

9 CLK33_PCM

)4

Y1

1

11

m1

)2

)3

)5

)5

)7

)8

SC

1.Board revision ID

2.USB controller change;replace USB port3 with port5

3.KBC-P60-->EN_MINI_PCI

4.VGA floating input-->PD "SSIN","SSOUT",HPD"

5.

NOTE:

1.F2 : NOT RAYCHEM

m

IDSEL

INTERNAL_LAN

EXTERNAL_LAN

Mini-PCI

IEEE 1394

USB 2.0

AD13

AD18

AD21

AD13

AD14

USB 1.1

AD14

CARDBUS

LPC

AC97

IDE

AD+42,46

BT+25,42

DCBATOUT25,38,40,41,42,43,44,46

5V_S018,20,24,25,26,30,31,32,33,34,35,36,37,38,39,40,41,43,47

5V_S342,43,44

5V_AUDIO_S032,33,47

+5V_UP_S538,42

3D3V_S03,5,7,8,9,10,11,14,16,18,19,20,21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,41,43,44,46,47

3D3V_S39,22,34,38,43,46,47

3D3V_S59,10,21,22,23,25,34,35,38,42,43,45,46,47

3D3V_LAN_S321,26,27,31,43

AD+

BT+

DCBATOUT

5V_S0

5V_S3

5V_AUDIO_S0

+5V_UP_S5

3D3V_S0

3D3V_S3

3D3V_S5

3D3V_LAN_S3

AD20

AD13

AD13

AD13

PCI IRQDEVICE REQ# / GNT#

INTC#/INTG#

INTD#

INTC#

REQ4#/GNT4#

REQ3#/GNT3#

INTD#/INTE#

INTD#/INTH#

INTA#

REQ1#/GNT1#

INTC#/INTF#

INTH#

1D25V_S012,13,45

2D5V_S04,16,17,43,47

2D5V_S39,10,11,12,13,43,44,45

1D5V_S07,10,14,16,44,47

1D8V_S08,10,16,20,21,23,44,47

1D8V_S510,22,23,45

1D2V_VID_S05,41

VCC_CORE_S05,6,7,10,23,25,36,39,40,41

VCC_RTC_S521

1D25V_S0

2D5V_S0

2D5V_S3

1D5V_S0

1D8V_S0

1D8V_S5

1D2V_VID_S0

VCC_CORE_S0

VCC_RTC_S5

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

REVISION HISTORY

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

TOUCAN2

247Wednesday, December 18, 2002

1

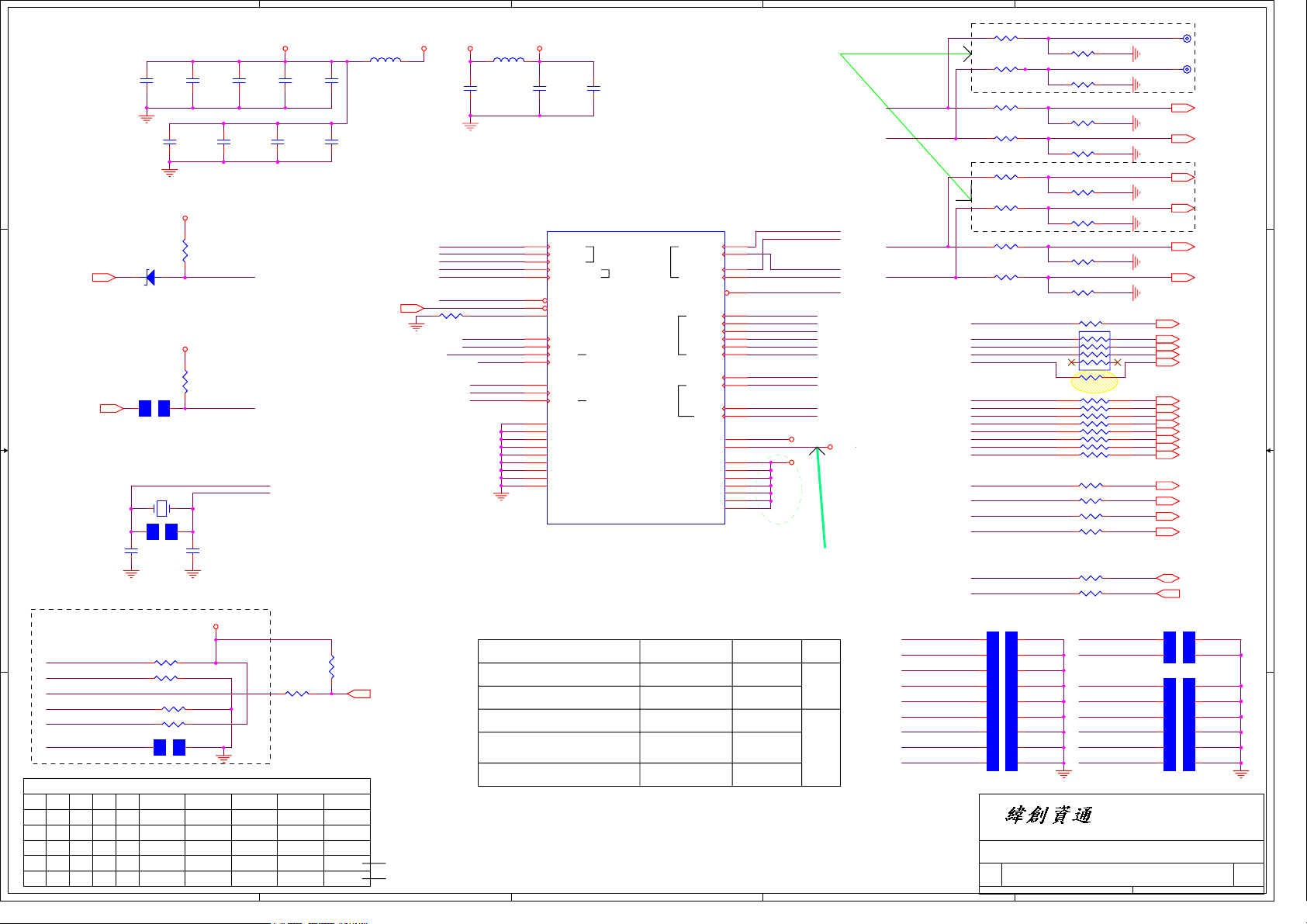

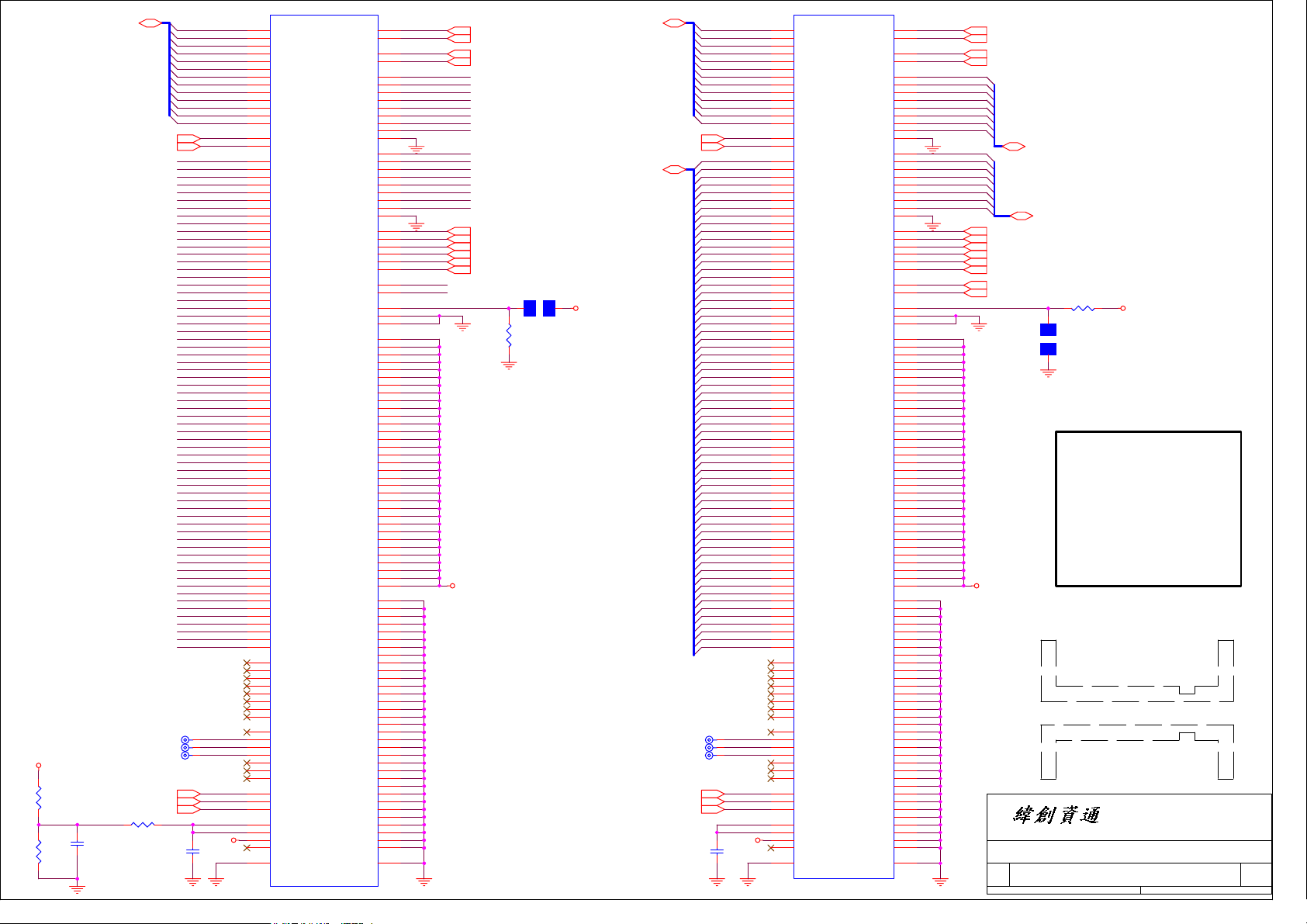

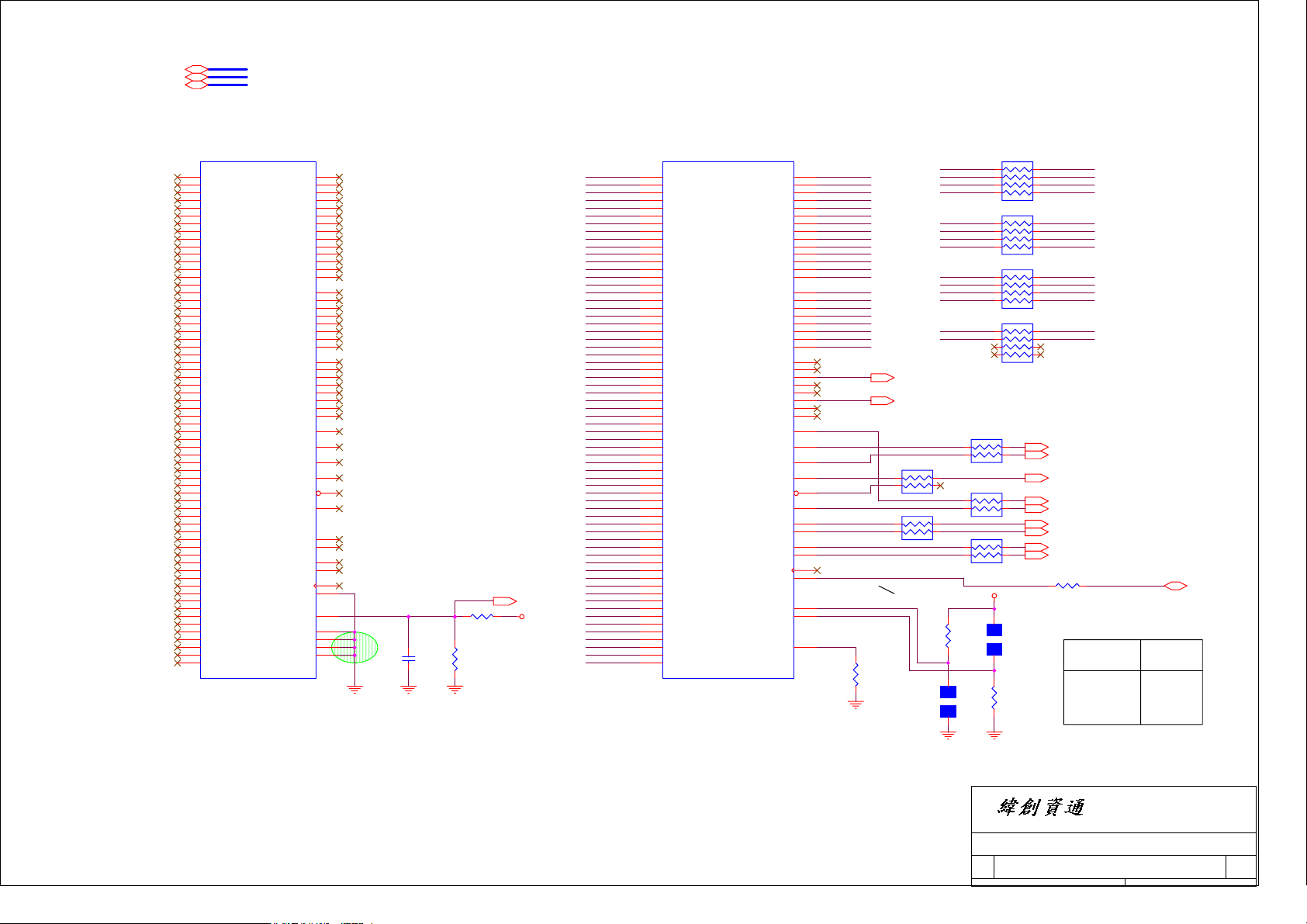

Page 3

A

12

BC533

3D3V_S0

12

3D3V_S0

RB22

1KR3

12

BC479

SCD1U16V3KX

BC483

SC1000P50V

RB20

10KR3

1 2

PM_CPUSTP#_1

12

PM_STP_PCI#_1

XTAL_CLK_X1

XTAL_CLK_X2

12

SCD1U16V3KX

4 4

Pull high 10kR with low

forward voltage diode

PM_CPUSTP#21

Prevent leakage in

S3 mode

3 3

PM_STP_PCI#21

2 2

SC4P-manual

78.4R074.1F1

DB7

DUMMY-RB751V-40

R408

DUMMY-R3

1 2

X-14D318MHZ-1-U

1 2

12

BC104

X8

R77

DUMMY-R3

SCD1U16V3KX

BC478

SC1000P50V

BC78

SC4P-manual

78.4R074.1F1

BC532

BC477

SC4D7U25V-U

BC534

SC1000P50V

The frequency can be program by software

3D3V_S0

CLK14_SIS650_FS0

CLK14_SIS962_FS1

CLK14_SIO_FS2

CLK33_SIS962_FS3

CLK33_KBC_FS4

MULTISEL

1 1

000

0

0

0

0001

0

1

01101

R405 2K7R3

1 2

R407 2K7R3

1 2

R410 2K7R3

1 2

R409 2K7R3

1 2

R86 DUMMY-R3

1 2

FREQUENCY TABLE

FS0FS1FS2FS3FS4

CPU DDRRAM ZCLK

0

100.00

1

100.00

A

66.67

100.90 100.90

133.33

0

0

1

001

R406 2K7R3

1 2

66.67

100.00

133.33

66.67 66.67

66.67

67.27 67.27

100.00 66.67 66.67 33.33

12

AGPCLK PCI

33.33

66.6766.67

33.33

33.33

66.67

L38

1 2

MLB-201209-11

BC484

SC4D7U10V6KX

BC535

SC1000P50V

VCORE_PWROK21,39

R404

10KR3

H_BSEL0 5,21

33.63

Default Setting

B

B

3D3V_S0CLK_3D3V_S0

1 2

R377 475R3F

C

L34

1 2

MLB-201209-11

BC482

SCD1U16V3KX

CLK14_SIS650_FS0

CLK14_SIS962_FS1

CLK14_SIO_FS2

CLK33_SIS962_FS3

CLK33_KBC_FS4

PM_STP_PCI#_1

ICS952004_IREF

XTAL_CLK_X1

XTAL_CLK_X2

CLK48_SIS962_USB_1

MULTISEL

SMBD_SIS92_1

SMBC_SIS92_1

CLK133_DDR_1

CLKGEN_VDDA3D3V_S0

BC481

SCD1U16V3KX

U13

2

FS0/REF0

3

FS1/REF1

4

FS2/REF2

14

FS3/PCICLK_F0

15

FS4/PCICLK_F1

12

PCI_STOP#

33

PD#/VTT_PWRGD

38

IREF

6

X1

7

X2

27

48MHZ

26

MULTISEL/24_48MHZ

34

SDATA

35

SCLK

47

SDRAM

5

GNDREF

8

GNDZ

18

GNDPCI

24

GNDPCI

25

GND48

32

GNDAGP

37

GNDA

41

GNDCPU

46

GNDSD

ICS952004AG

71.95204.00W

ICS952004AG is TSOIC48 package

The part number is

71.952004.00W

BC480

SCD01U50V3KX

14MHz

33MHz

48MHz

133MHz

GTL CLK

33MHz

66MHz

CPUCLKC_0

CPUCLKC_1

CPUCLKT_0

CPUCLKT_1

CPU_STOP#

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

AGPCLK1

AGPCLK0

ZCLK0

ZCLK1

VDDA48

VDDREF

VDDPCI

VDDPCI

VDDAGP

VDDCPU

VDDSD

VDDA

VDDZ

39

43

40

44

45

16

17

20

21

22

23

30

31

9

10

28

36

1

11

13

19

29

42

48

R1,R3,R9,R11

please as possible

closed to trace's

branch node.

CLKH_CPUL1

CLKH_CPU#L1

CLKH_SIS650L1

PM_CPUSTP#_1

CLK33_LAN_1

CLK33_MINI_1

CLK33_PCM_1

CLK33_LPCROM_1

CLK33_P80_1

CLK33_SIO_1

ATI_AGPCLK_1

SIS650_AGPCLK_1

CLK66_SIS650_1

CLK66_SIS962_1

Layout trace 25mil

Layout trace 10mil

CLOCK GROUP JITTER SKEW NOTE

HOST:CPUCLK0/#,CPUCLK1/#

HOST Bus To Memory Bus:

CPUCLK1/#,SDCLK

MuTIOL: ZCLK0, ZCLK1

AGP: ACLK0,ACLK1

PCI Bus:

PCICLK_F[0:1],PCICLK[0:5]

<0.25ns

<0.25ns

<0.25ns

<0.25ns

<0.5ns

<0.4ns

<0.4ns

<0.325ns

<0.325ns

<0.65ns

Note:

1. These skews are all calculated at the receiver's clock pin,

including clock driver pin to pin skew and PCB clock

routing skew.

2. All skews aare reference to the crossing point for

differential clock signals and 1.5V rising edge for 3.3V

clock signals.

C

CLK_3D3V_S0

CLK_3D3V_S0

1,2

CLKGEN_VDDA

D

CLKH_CPUL1

CLKH_CPU#L1

CLKH_SIS650L1

CLKH_SIS650#L1

CLK66_SIS650

CLK14_SIO

CLK14_SIS962

XTALIN_CODEC

CLK48_SIS962_USB

SMBC_SIS962

SMBD_SIS962

CLK133_DDR

SIS650_AGPCLK

D

E

R84 DUMMY-33R3

1 2

R81 DUMMY-33R3

1 2

R83 33R3

1 2

R82 33R3

1 2

R79 DUMMY-33R3

1 2

R78 DUMMY-33R3

1 2

R80 33R3

1 2

R76 33R3

1 2

CLK33_MINI_1

CLK33_SIO_1

CLK33_P80_1

CLK33_LPCROM_1

CLK33_PCM_1

CLK33_LAN_1

CLK33_KBC_FS4

CLK33_SIS962_FS3

CLK66_SIS962_1

CLK66_SIS650_1

CLK14_SIO_FS2

CLK14_SIS962_FS1

CLK14_SIS650_FS0

CLK48_SIS962_USB_1

CLK133_DDR_1

SIS650_AGPCLK_1

ATI_AGPCLK_1

SMBD_SIS92_1

SMBC_SIS92_1

C15 DUMMY-C3

1 2

C44 DUMMY-C3

1 2

C14 DUMMY-C3

1 2

C43 DUMMY-C3

1 2

C36 DUMMY-C3

1 2

C33 DUMMY-C3

1 2

C34 DUMMY-C3

1 2

C32 DUMMY-C3

1 2

C35 DUMMY-C3

1 2

Title

Size Document Number Rev

A3

Date: Sheet

CLKCON

R56 DUMMY-49D9R3F

1 2

CLKCON#

R53 DUMMY-49D9R3F

1 2

CLKH_CPU

R55 49D9R3F

1 2

CLKH_CPU#

R54 49D9R3F

1 2

CLKH_ITP

R51 DUMMY-49D9R3F

1 2

CLKH_ITP#

R50 DUMMY-49D9R3F

1 2

CLKH_SIS650

R52 49D9R3F

1 2

CLKH_SIS650#CLKH_SIS650#L1

R49 49D9R3F

1 2

R110 33R3

1 2

RN13 SRN33

1

8

2

7

3

6

4 5

1 2

1

2

3

4

5

6

7

8 9

RN12 RS8M33ROJ

1 2

R381 22R3

1 2

R376 10R3

1 2

R380 33R3

1 2

R85 33R3

1 2

R379 0R3-0-U

1 2

R378 0R3-0-U

SB

R540 10R3

16

15

14

13

12

11

10

CLK66_SIS962

CLK33_MINI

CLK33_LPCROM

CLK33_P80

CLK33_SIO

CLK33_LAN

CLK33_KBC

CLK33_SIS962

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

CLOCK GENERATOR

TOUCAN2

E

TP7 TPAD30

TP6 TPAD30

CLKH_CPU 5

CLKH_CPU# 5

CLKH_ITP 5

CLKH_ITP# 5

CLKH_SIS650 7

CLKH_SIS650# 7

CLK33_MINI 31

CLK33_SIO 37

CLK33_P80 36

CLK33_LPCROM 36

CLK33_PCM 29

CLK33_LAN 27

CLK33_KBC 34

CLK33_SIS962 20

CLK66_SIS962 20

CLK66_SIS650 8

CLK14_SIO 37

CLK14_SIS962 21

XTALIN_CODEC 32

CLK48_SIS962_USB 22

CLK133_DDR 9

SIS650_AGPCLK 7

ATI_AGPCLK 14

SMBD_SIS962 4,11,21

SMBC_SIS962 4,11,21

C16 DUMMY-C3

1 2

C37

1 2

C39 DUMMY-C3

1 2

C40 DUMMY-C3

1 2

C41 DUMMY-C3

1 2

C46 DUMMY-C3

1 2

C17 DUMMY-C3

1 2

C45 DUMMY-C3

1 2

DUMMY-C3

347Wednesday, December 18, 2002

of

1

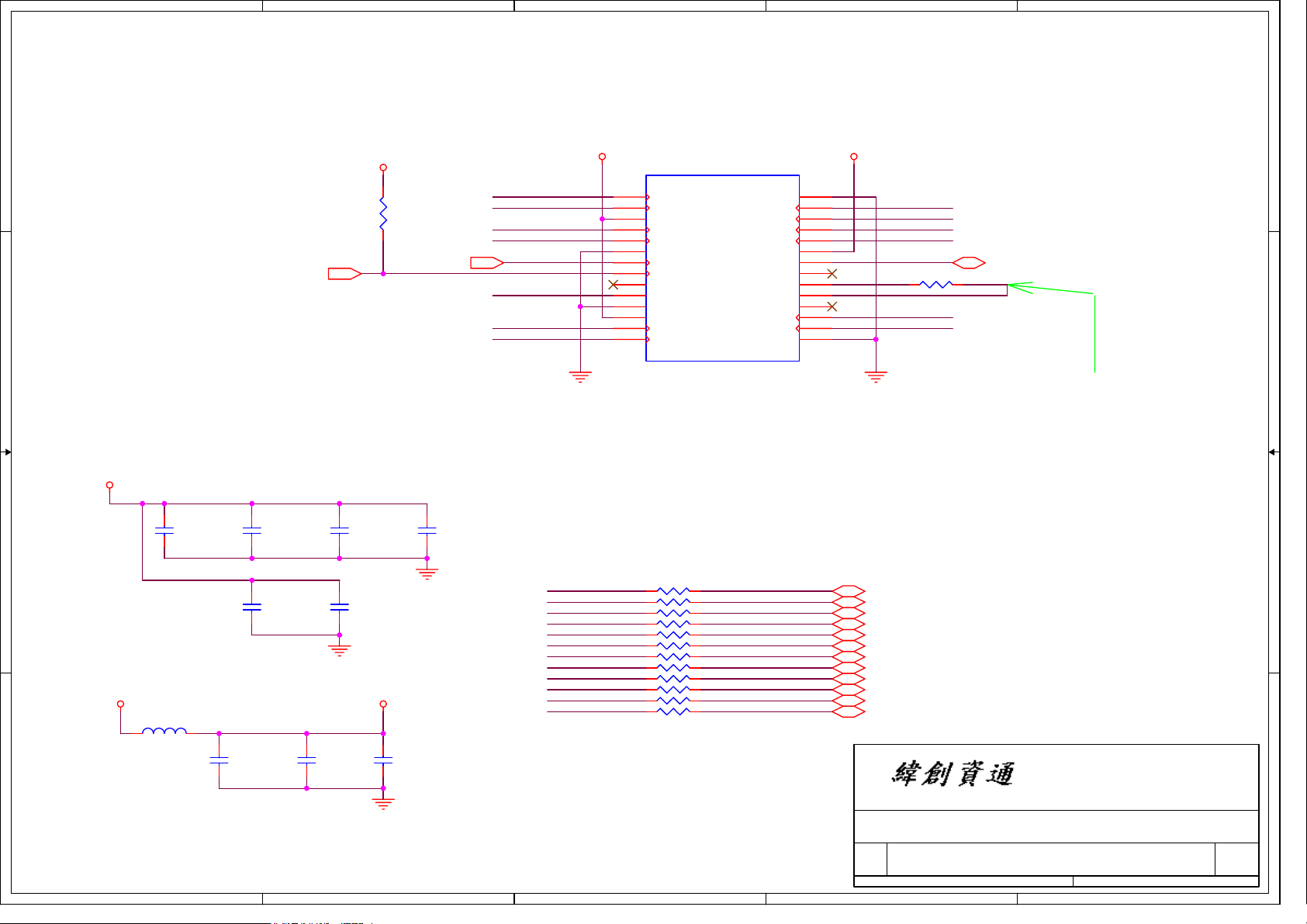

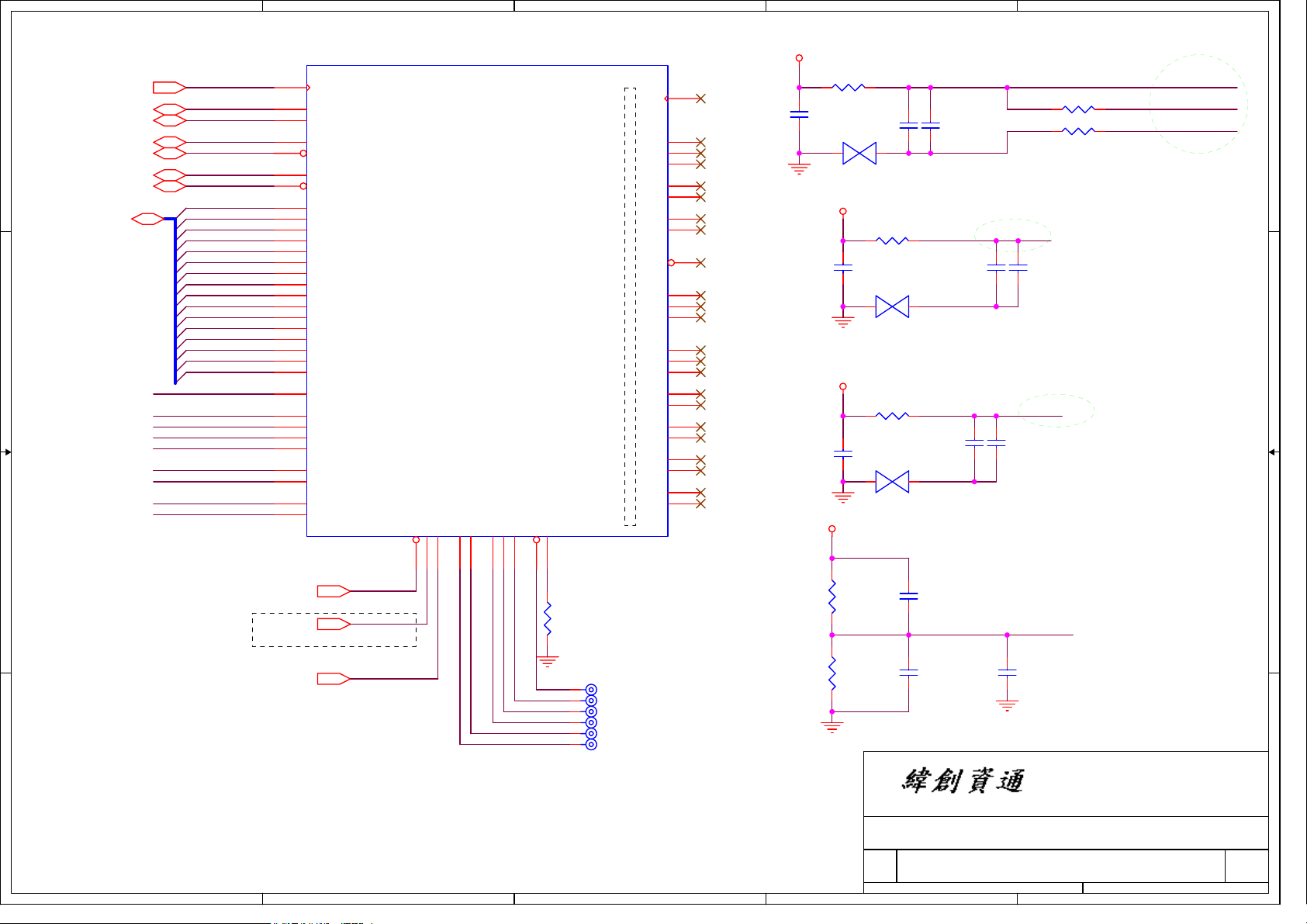

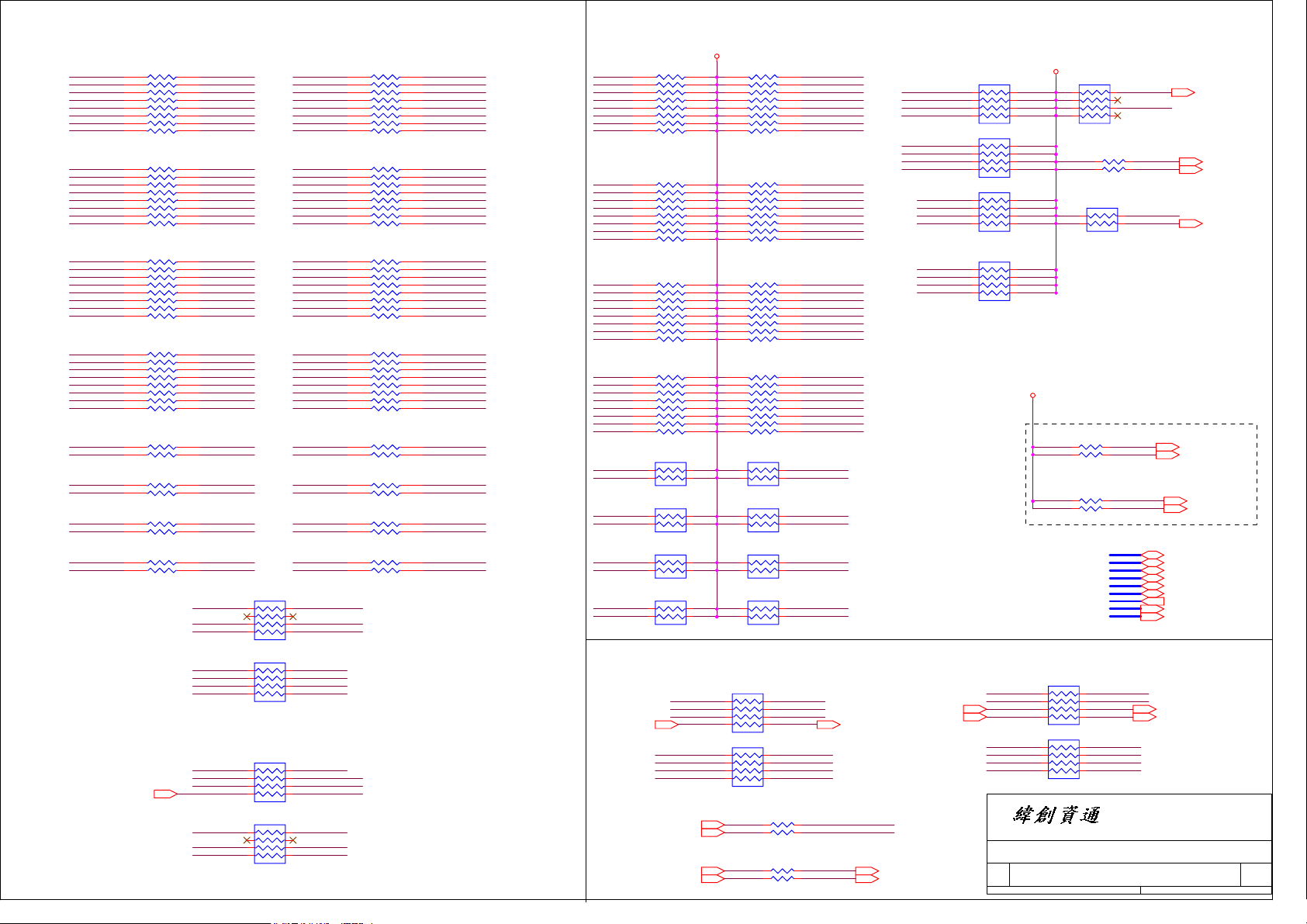

Page 4

A

4 4

CLK133_DDRBUF9

3 3

B

2D5V_S0

R435

4K7R3

1 2

SMBC_SIS9623,11,21 SMBD_SIS962 3,11,21

U2_DDR0#

U2_DDR0

U2_DDR1

U2_DDR1#

SMBC_SIS962

CLK133_DDRBUF

2D5V_VDDA_S0

U2_DDR2

U2_DDR2#

2D5V_S0

C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

U23

CLKC0

CLKT0

VDD

CLKT1

CLKC1

GND

SCLK

CKL_INT

N/C

VDDA

GND

VDD

CLKT2

CLKC2

CY28352OC

GND

CLKC5

CLKT5

CLKC4

CLKT4

VDD

SDATA

N/C

FB_INT

FB_OUTT

N/C

CLKT3

CLKC3

GND

28

27

26

25

24

23

22

21

ICS93722_FBI

20

19

18

17

16

15

D

2D5V_S0

U2_DDR5#

U2_DDR5

U2_DDR4#

U2_DDR4

SMBD_SIS962

ICS93722_FBO

U2_DDR3

U2_DDR3#

R403

1 2

22R3

E

The PLL trace need match the specific

H2U

P/N:71.93732.00I

L4 = L2+L3-L1+3.2"

L2 : SiS645 to Buffer length.(< 6" )

L3 : Buffer to DIMM socket length.(<4" )

L1 : 2 " ~ 4"(SIS645 to DDR-Socket)

L4 = need less 12.6"

2D5V_S0

12

BC525

SC1000P50V

2 2

2D5V_S0

L15

1 2

MLB-201209-11

1 1

BC129

SC4D7U10V6KX

BC130

SC1000P50V

Layout trace 10 mil

12

SC4D7U10V6KX

2D5V_VDDA_S0

BC125

BC570

SCD1U16V3KX

BC128

SCD1U16V3KX

BC126

SCD1U16V3KX

2D5V_VDDA_S0

BC127

SCD1U16V3KX

BC571

SCD1U16V3KX

U2_DDR0#

U2_DDR0

U2_DDR1

U2_DDR1#

U2_DDR2

U2_DDR2#

U2_DDR5#

U2_DDR5

U2_DDR4#

U2_DDR4

U2_DDR3

U2_DDR3#

R170 0R2-0

1 2

R171 0R2-0

1 2

R173 0R2-0

1 2

R172 0R2-0

1 2

R132 0R2-0

1 2

R133 0R2-0

1 2

R213 0R2-0

1 2

R212 0R2-0

1 2

R217 0R2-0

1 2

R218 0R2-0

1 2

R216 0R2-0

1 2

R215 0R2-0

1 2

CLK_DDR0#

CLK_DDR0

CLK_DDR1

CLK_DDR1#

CLK_DDR2

CLK_DDR2#

CLK_DDR5#

CLK_DDR5

CLK_DDR4#

CLK_DDR4

CLK_DDR3

CLK_DDR3#

CLK_DDR0# 11

CLK_DDR0 11

CLK_DDR1 11

CLK_DDR1# 11

CLK_DDR2 11

CLK_DDR2# 11

CLK_DDR5# 11

CLK_DDR5 11

CLK_DDR4# 11

CLK_DDR4 11

CLK_DDR3 11

CLK_DDR3# 11

Title

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DDRCLK_BUFFER

Size Document Number Rev

A4

Date: Sheet

A

B

C

D

TOUCAN2

of

447Wednesday, December 18, 2002

E

1

Page 5

CPU Socket: P/N 62.10053.051

3D3V_S0

12

R324

470R3

1D2V_VID_S0

VCC_CORE_S0

12

R303

0R5

VCCSENSE_S0

L:RATED I = 60mA

C:ESR < 0.3 OHM, ESL < 5nH, +/- 20% TOLERANT

GTL_A#[16..3]7

GTL_ADSTB#07

GTL_REQ#[4..0]7

GTL_A#[31..17]7

GTL_ADSTB#17

Q3_C

12

R392

DUMMY-R5

ZZ.DUMMY.XR5

R332

0R3-0-U

1 2

R333

0R3-0-U

1 2

CC_THRMTRIP_S#25

6

5

CC_FERR#21

Q29

UMX1N

1

2

34

HVCCA2

GTL_A#16

GTL_A#15

GTL_A#14

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

GTL_REQ#4

GTL_REQ#3

GTL_REQ#2

GTL_REQ#1

GTL_REQ#0

GTL_A#31

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

Q3_B

1D2V_VID_S0

L32

IND-4D7UH

1 2

68.4R72B.1F1

THERMDP125

THERMDN25

U9D

N5

N4

N2

M1

N1

M4

M3

L2

M6

L3

K1

L6

K4

K2

L5

H3

J3

J4

K5

J1

AB1

Y1

W2

V3

U4

T5

W1

R6

V2

T4

U3

P6

U1

T2

R3

P4

P3

R2

T1

R5

VCC_CORE_S0

R326

56R3

R325

1 2

470R3

TC5

ST33U10VCM-U

TC4

ST33U10VCM-U

77.23361.001

1 2

R495 DUMMY-R2

1D2V_VID_S0

VCC_CORE_S0

A#16

A#15

A#14

A#13

A#12

A#11

A#10

A#9

A#8

A#7

A#6

A#5

A#4

A#3

ADSTB#0

REQ#4

REQ#3

REQ#2

REQ#1

REQ#0

A#35

A#34

A#33

A#32

A#31

A#30

A#29

A#28

A#27

A#26

A#25

A#24

A#23

A#22

A#21

A#20

A#19

A#18

A#17

ADSTB#1

CPU-SOCKET-479-NB

62.10053.051

12

R390

1 2

0R3-0-U

12

1 2

CLKH_CPU3

CLKH_CPU#3

CLKH_ITP3

CLKH_ITP#3

CC_A20M#21

CC_IGNNE#21

CC_INTR21

CC_NMI21

CC_SMI#21,47

CC_STPCLK#21

TP48

TPAD30

TP41

TPAD30

H_VCCA1

H_VCCA2

H_VSSA

TP42

TPAD30

1D2V_VID_S0

CC_THRMTRIP#_P

R382 DUMMY-R2

1 2

ZZ.DUMMY.X02

1 2

R386

51R2

63.51034.1D1

U9C

CC_FERR_S#

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

SIS650_AF3

H_VCCS

H_VSSS

ADS#

AP#0

AP#1

BINIT#

BNR#

BPRI#

DP#3

DP#2

DP#1

DP#0

DEFER#

DRDY#

DBSY#

TESTHI10

TESTHI9

TESTHI8

BR#0

IERR#

INIT#

LOCK#

MCERR#

RESET#

RS#2

RS#1

RS#0

RSP#

TRDY#

HIT#

HITM#

AF22

AF23

AC26

AD26

AD20

AE23

AD22

AF25

AF24

AE21

G1

AC1

V5

AA3

G2

D2

L25

K26

K25

J26

E2

H2

H5

Y3

W4

U6

H6

AC3

W5

G4

V6

AB25

F4

G5

F1

AB2

J6

F3

E3

AE1

AE2

AE3

AE4

AE5

AD3

AD2

AF3

AF4

A22

C6

B6

B2

D1

E5

B5

Y4

A5

A4

B3

C4

A2

A7

H_AP#0

H_AP#1

H_BINIT#

H_BR3#

H_BR2#

H_BR1#

H_IERR_PU#

H_MCERR#

H_RSP#

BCLK0

BCLK1

ITP_CLK0

ITP_CLK1

A20M#

FERR#

IGNNE#

LINT0

LINT1

SMI#

STPCLK#

VID4

VID3

VID2

VID1

VID0

RSVD3

VCCVID

VCCA

VCCSENSE

VCCIOFLL

VSSA

VSSSENSE

VCCVID

NC

NC

THERMDA

THERMDC

THERMTRIP#

NC

NC

NC

NC

NC

CPU-SOCKET-479-NB

62.10053.051

TP52

TPAD30

H_DP#3

H_DP#2

H_DP#1

H_DP#0

RN92

1

2

3

4 5

SRN56

CC_INIT# 21,36

GTL_LOCK# 7

TESTHI11

TESTHI0

DPSLP#

GTLREF

GTLREF

GTLREF

GTLREF

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

PROCHOT#

PWRGOOD

GTL_ADS# 7

GTL_BNR# 7

GTL_BPRI# 7

GTL_DEFER# 7

GTL_DRDY# 7

GTL_DBSY# 7

8

7

6

TP44

TPAD30

TP47

TPAD30

BSEL0

BSEL1

COMP1

COMP0

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

DBR#

SLP#

TCK

TDI

TDO

TMS

TRST#

1 2

1 2

R441 10KR3

1 2

R329 51R3F

AD6

H_BSEL0

H_BSEL1

AD5

A6

P1

H_COMP1

L24

H_COMP0

AB4

AA5

Y6

AC4

AB5

AC6

AD24

H_BYPASSEN#

AE25

AD25

F6

F20

AA6

AA21

AA2

H_ODT

AC21

H_MCLK0

AC20

H_MCLK1

AC24

H_MCLK2

AC23

H_MCLK3

AA20

H_MCLKIO0

AB22

H_MCLKIO1

C3

AB23

AB26

D4

C1

D5

F7

E6

TP53 TPAD30

TP45 TPAD30

TP46 TPAD30

TP34 TPAD30

TP33 TPAD30

TP32 TPAD30

TP35 TPAD30

R387

220R3F

GTL_BR0# 7

GTL_CPURST# 7

GTL_RS#2 7

GTL_RS#1 7

GTL_RS#0 7

GTL_TRDY# 7

GTL_HIT# 7

GTL_HITM# 7

DBRST#

CC_DPSLP#

VCC_CORE_S0

VCC_CORE_S0

VCC_CORE_S0

PM_CPUPERF#

R438 51D1R3F

1 2

1 2

R327 51D1R3F

H_BPM5_PREQ# 6

H_BPM4_PRDY# 6

H_BPM1_ITP# 6

H_BPM0_ITP# 6

R302

0R3-0-U

1 2

H_GTLREF_3

H_GTLREF_1

1

H_ODT

H_MCLKIO0

2

3

H_MCLK1

4

H_MCLKIO1

5

H_MCLK0

6

H_MCLK3

7

H_MCLK2

H_BYPASSEN#

CC_PROCHOT_S# 25

CC_CPUSLP# 21

H_TCK 6

H_TDI 6

H_TDO 6

H_TMS 6

H_TRST# 6

8 9

ITP_RST# 6

VCC_CORE_S0

RN77

RS8M56ROJ

U9B

GTL_D#[15..0]7

VCC_CORE_S0

12

12

R371

12

R328

300R3

100R3F

R370

R368

49D9R3F

SB

12

R369

BC365

100R3F

SCD1U

SB

12

BC374

SCD1U

CC_CPUPWROK 7

BC486

SCD1U

BC426

SCD1U

49D9R3F

16

15

14

13

12

11

10

GTL_DINV#07

GTL_DSTBN#07 GTL_DSTBN#2 7

GTL_DSTBP#07

BC419

SC1U10V3ZY

BC491

SC1U10V3ZY

GTL_D#[31..16]7

GTL_DINV#17

GTL_DSTBN#17

CPU Speed Setting Strap Pin

H2U Only Support Desktop

CPU

VCC_CORE_S0

12

12

R439

R385

200R3

56R3

PM_CPUPERF#

CC_A20M#

CC_IGNNE#

CC_INTR

CC_NMI

CC_SMI#

CC_STPCLK#

CC_DPSLP#

CC_CPUSLP#

CC_INIT#

CC_PROCHOT_S#

Desktop: 1KR3 pull to Vcore

Mobile: 200R3 pull to Vcore

GTL_D#15

GTL_D#14

GTL_D#13

GTL_D#12

GTL_D#11

GTL_D#10

GTL_D#9

GTL_D#8

GTL_D#7

GTL_D#6

GTL_D#5

GTL_D#4

GTL_D#3

GTL_D#2

GTL_D#1

GTL_D#0

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#28

GTL_D#27

GTL_D#26

GTL_D#25

GTL_D#24

GTL_D#23

GTL_D#22

GTL_D#21

GTL_D#20

GTL_D#19

GTL_D#18

GTL_D#17

GTL_D#16

DUMMY-R3

H_BSEL0

H_BSEL1

DUMMY-R3

12

R330

200R3

R389

E21

E22

H25

K23

M21

G25

K22

R391

D25

J21

D23

C26

H21

G22

B25

C24

C23

B24

D22

C21

A25

A23

B22

B21

F21

J24

L22

H24

G26

L21

D26

F26

E25

F24

F23

G23

E24

H22

J23

D#15

D#14

D#13

D#12

D#11

D#10

D#9

D#8

D#7

D#6

D#5

D#4

D#3

D#2

D#1

D#0

DINV#0

STBN#0

STBP#0

D#31

D#30

D#29

D#28

D#27

D#26

D#25

D#24

D#23

D#22

D#21

D#20

D#19

D#18

D#17

D#16

DINV#1

STBN#1

STBP#1

CPU-SOCKET-479-NB

62.10053.051

VCC_CORE_S0

12

12

R388

DUMMY-R3

12

12

R442

DUMMY-R3

D#47

D#46

D#45

D#44

D#43

D#42

D#41

D#40

D#39

D#38

D#37

D#36

D#35

D#34

D#33

D#32

DINV#2

STBN#2

STBP#2

D#63

D#62

D#61

D#60

D#59

D#58

D#57

D#56

D#55

D#54

D#53

D#52

D#51

D#50

D#49

D#48

DINV#3

STBN#3

STBP#3

H_VID439

H_VID339

H_VID239

H_VID139

H_VID039

H_BSEL0 3,21

T23

T22

T25

T26

R24

R25

P24

R21

N25

N26

M26

N23

M24

P21

N22

M23

P26

R22

P23

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

V22

U21

V25

U23

U24

U26

V21

W22

W23

GTL_D#47

GTL_D#46

GTL_D#45

GTL_D#44

GTL_D#43

GTL_D#42

GTL_D#41

GTL_D#40

GTL_D#39

GTL_D#38

GTL_D#37

GTL_D#36

GTL_D#35

GTL_D#34

GTL_D#33

GTL_D#32

GTL_D#63

GTL_D#62

GTL_D#61

GTL_D#60

GTL_D#59

GTL_D#58

GTL_D#57

GTL_D#56

GTL_D#55

GTL_D#54

GTL_D#53

GTL_D#52

GTL_D#51

GTL_D#50

GTL_D#49

GTL_D#48

< 3" from CPU

12

12

12

12

R440

R331

1KR3

Title

Size Document Number Rev

A3

Date: Sheet

R384

200R3

200R3

NORTHWOOD (1/2)

TOUCAN2

12

R418

R417

200R3

200R3

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

GTL_D#[47..32] 7

GTL_DINV#2 7

GTL_DSTBP#2 7

GTL_D#[63..48] 7

GTL_DINV#3 7

GTL_DSTBN#3 7

GTL_DSTBP#3 7GTL_DSTBP#17

R443 1KR3

1 2

RN93

1

2

3

4 5

SRN1K

12

12

R412

200R3

547Wednesday, December 18, 2002

of

R383

200R3

3D3V_S0

8

7

6

12

1

R367

1KR3

Page 6

VSSH1VSSH4VSS

H23

E14

E16

VCC

VSSF5VSSF8VSS

VCC_CORE_S0

E18

E20

F11

F13

F15

F17

F19

F9

VCC

VCC

VCC

VCCE8VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSSG3VSSG6VSSJ2VSS

VSS

VSSJ5VSS

VSS

VSSK3VSSK6VSSL1VSS

VSS

VSSL4VSSM2VSS

VSSM5VSS

VSS

VSSN3VSSN6VSSP2VSS

VSS

VSSP5VSSR1VSS

VSS

VSSR4VSS

VSS

VSST3VSSY5VSS

VSS

VSSY2VSSW6VSSW3VSS

VSS

VSSV4VSS

VSS

VSSV1VSSU5VSS

VSS

VSST6VSSU2VSS

J22

J25

L23

L26

K21

G21

G24

K24

N21

N24

M22

T21

P22

T24

P25

Y25

Y22

V26

V23

R23

R26

W24

W21

A24

U25

U22

A26

VSS

M25

VSS

VSS

C5

U9A

CPU-SOCKET-479-NB

62.10053.051

R419

CPU_AF2_S0

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

VCC

VCC

VCC

VCC

VCC

VCC

VCCA8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D20

VSS

VSS

D21

VSS

VSSD3VSSD6VSSD8VSSE1VSS

D24

VCCB7VCCB9VCC

E11

*AF2 :

VCCFUSEPRG

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSA3VSSA9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB4VSSB8VSS

VSS

VSS

VSS

VSS

VSSC2VSS

VSS

VSSC7VSSC9VSS

VSS

VSS

VSS

VSS

A11

A13

A15

A17

A19

A21

H26

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC2

AC5

AC7

AC9

AC11

AC13

AC15

AC17

AD1

AC19

AC22

AC25

AD4

AD8

AE11

AE13

AD10

AD12

AD14

AD16

AE15

AD18

AD21

AD23

AE17

AE19

AE22

AE24

AE26

AF1

AE7

AE9

AF10

AF12

B10

B12

B14

B16

B18

B20

B23

AF6

AF8

AF14

AF16

AF18

AF20

AF26

B26

C11

C13

C15

C17

C19

C22

C25

D10

D12

D14

D16

D18

0R3-0-U

1 2

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

E10

E12

VCC

VCC

VCC

VCC

VCC

VCCC8VCC

VCC

VCC

VCC

VCC

VCCD7VCCD9VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSSE4VSSE7VSSE9VSS

VSS

VSS

VSS

VSS

VSSF2VSS

VSS

F10

F12

F14

F16

F18

F22

E13

E15

E17

E19

E23

E26

F25

VCC_CORE_S0

12

VCC_CORE_S0

12

SC10U6D3V6MX-1-U

VCC_CORE_S0

BC371

SCD1U16V3KX

10U/X7R 1206 DECOUPLING CAPS

8X IN SOCKET CAVITY

10X IN CRB

12

BC424

SC10U6D3V6MX-1-U

BC360

BC425

SC10U6D3V6MX-1-U

10U/X7R 1206 DECOUPLING CAPS

10X AROUND SOCKET

28X IN CRB

12

BC359

SC10U6D3V6MX-1-U

0.1U/X5R 0603 DECOUPLING CAPS

20X AROUND SOCKET

0.47U/X5R 0603 10X IN CRB

BC418

SCD1U16V3KX

12

BC423

SC10U6D3V6MX-1-U

12

BC414

D-SC10U6D3V6MX-1-U

DUMMY

BC416

SCD1U16V3KX

12

BC422

SC10U6D3V6MX-1-U

12

BC415

SC10U6D3V6MX-1-U

BC375

SCD1U16V3KX

12

BC420

SC10U6D3V6MX-1-U

12

BC324

SC10U6D3V6MX-1-U

BC427

SCD1U16V3KX

12

BC421

SC10U6D3V6MX-1-U

12

BC429

D-SC10U6D3V6MX-1-U

BC492

SCD1U16V3KX

12

BC366

SC10U6D3V6MX-1-U

12

BC430

SC10U6D3V6MX-1-U

BC428

SCD1U16V3KX

12

BC373

SC10U6D3V6MX-1-U

12

BC431

SC10U6D3V6MX-1-U

BC372

SCD1U16V3KX

CPU_AF26

12

R5

DUMMY-R2

ZZ.DUMMY.X02

12

BC432

D-SC10U6D3V6MX-1-U

BC417

SCD1U16V3KX

Desktop: NC

Mobile: GND

12

BC496

SC10U6D3V6MX-1-U

BC364

SCD1U16V3KX

VCC_CORE_S0

LAYOUT:RE-PLACEMENT

678

123

H_BPM5_PREQ#5

H_BPM4_PRDY#5

H_BPM1_ITP#5

H_BPM0_ITP#5

H_TDO5

H_TCK5

H_TDI5

H_TMS5

ITP_RST#5

H_TRST#5

12

RN90

R411

SRN51-U

75R3

4 5

12

R414

150R3F

12

R416

39R3F

123

678

RN91

SRN51-U

4 5

12

R415

680R3

TOUCAN2-SA

VCC_CORE_S0

12

R301

51R3F

12

R413

27D4R3F

BC488

SCD1U16V3KX

BC361

SCD1U16V3KX

BC487

SCD1U16V3KX

BC536

SCD1U16V3KX

BC367

SCD1U16V3KX

BC537

SCD1U16V3KX

BC368

SCD1U16V3KX

BC325

SCD1U16V3KX

BC369

SCD1U16V3KX

BC326

SCD1U16V3KX

BC489

SCD1U16V3KX

BC362

SCD1U16V3KX

BC490

SCD1U16V3KX

BC494

SCD1U16V3KX

BC370

SCD1U16V3KX

BC495

SCD1U16V3KX

BC538

SCD1U16V3KX

BC493

SCD1U16V3KX

BC363

SCD1U16V3KX

BC327

SCD1U16V3KX

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

NORTHWOOD (2/2)

Size Document Number Rev

Custom

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

TOUCAN2

647Wednesday, December 18, 2002

of

1

Page 7

A

B

C

D

E

C1XAVDD

AJ25

AH27

C4XAVSS

C1XAVDD

HD#58

HD#57

HD#56

B22

D20

C22

GTL_D#57

GTL_D#56

GTL_D#58

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HNCOMP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

C4XAVDD

U21

T21

P21

N21

AJ27

HVREF0

HVREF1

HVREF2

C4XAVDD

HD#55

HD#54

HD#53

HD#52

HD#51

F22

B23

A23

D21

D24

D23

GTL_D#55

GTL_D#51

GTL_D#53

GTL_D#54

GTL_D#52

GTL_D#50

HVREF

J17

HVREF3

HVREF4

HD#50

HD#49

B24

C24

GTL_D#48

GTL_D#49

HNCOMP

HPCOMP

B20

B19

HPCOMP

HNCOMP

HD#48

HD#47

HD#46

E25

E23

GTL_D#46

GTL_D#47

HNCVREF

AGP_ST0

AGP_ST1

AGP_ST2

A19

B7

ST0A7ST1F9ST2

HNCOMPVREF

HD#45

HD#44

HD#43

HD#42

A25

B26

B27

D25

C26

GTL_D#45

GTL_D#42

GTL_D#44

GTL_D#43

GTL_D#41

AGP_AD[31..0]14

AGP_C/BE#[3..0]14

AGP_SBA[7..0]14

AGP_ST[0..2]14

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AAD0M6AAD1M5AAD2M4AAD3L3AAD4L6AAD5L4AAD6K6AAD7L2AAD8K3AAD9

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

F28

F27

F26

B28

E26

D26

GTL_D#39

GTL_D#40

H24

G25

G24

GTL_D#33

GTL_D#32

GTL_D#38

GTL_D#35

GTL_D#34

GTL_D#37

GTL_D#36

C

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

J3

AAD10K4AAD11J2AAD12J6AAD13J4AAD14J1AAD15H6AAD16F4AAD17F1AAD18G6AAD19E3AAD20F5AAD21E2AAD22E4AAD23E1AAD24D3AAD25D4AAD26C2AAD27F7AAD28C3AAD29E6AAD30B2AAD31

AGP / VB

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

J26

J25

J24

J29

J28

L26

L25

L28

K28

K27

H26

H28

G29

G26

G28

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#27

GTL_D#28

GTL_D#26

M24

GTL_D#23

GTL_D#20

GTL_D#22

GTL_D#25

GTL_D#21

GTL_D#24

GTL_D#19

L29

K26

P26

N24

M26

GTL_D#12

GTL_D#16

GTL_D#14

GTL_D#18

GTL_D#17

GTL_D#11

GTL_D#15

GTL_D#13

GTL_DINV#35

GTL_DINV#25

GTL_DINV#15

GTL_DINV#05

AGP_AD30

AGP_AD31

D5

HD#9

HD#11

HD#10

N28

N26

M27

GTL_D#8

GTL_D#9

GTL_D#10

AGP_SBA7

HD#8

P27

GTL_D#7

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

C7

SBA7D6SBA6A3SBA5D7SBA4C5SBA3A5SBA2C6SBA1D8SBA0

HD#7

HD#6

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

P28

N29

R24

R28

R26

R29

M28

GTL_D#5

GTL_D#1

GTL_D#0

GTL_D#3

GTL_D#6

GTL_D#4

GTL_D#2

GTL_DINV#3

GTL_DINV#2

GTL_DINV#1

GTL_DINV#0

D

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

PIPE#

AGP8XDET

ADBIH

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

DBI#3

DBI#2

DBI#1

DBI#0

E21

A27

H27

R25

AGP_ADSTB0#

AGP_ADSTB1#

AGP_SBSTB#

AGP_ADSTB0

AGP_ADSTB1

AGP_SBSTB

AGP_C/BE#3

F6

F3

AGP_C/BE#2

H4

AGP_C/BE#1

AGP_C/BE#0

K5

C9

A6

G2

G1

G3

G4

AGP_ASERR#

H5

H1

H3

E8

F8

AGP_WBF#

AGP_PIPE#

D9

D10

B3

C4

B5

A4

K1

L1

C1

D1

B10

AGPRCOMP

M1

B9

A9

B8

A4XAVDD

A8

M3

M2

F20

GTL_DSTBN#3

GTL_DSTBN#2

F23

GTL_DSTBN#1

K24

P24

GTL_DSTBN#0

F21

GTL_DSTBP#3

GTL_DSTBP#2

F24

GTL_DSTBP#1

L24

N25

GTL_DSTBP#0

1

2

3

4 5

1

2

3

4 5

R48 60D4R3F

1 2

A1XAVDD

RN76

8

7

6

SRN8K2

1D5V_S0

RN84

8

7

6

SRN8K2

AGP_REQ# 14

AGP_GNT# 14

AGP_FRAME# 14

AGP_IRDY# 14

AGP_TRDY# 14

AGP_DEVSEL# 14

AGP_STOP# 14

AGP_PAR 14

AGP_RBF# 14

AGP_WBF# 14

AGP_SBSTB 14

AGP_SBSTB# 14

AGP_ADSTB0 14

AGP_ADSTB0# 14

AGP_ADSTB1 14

AGP_ADSTB1# 14

SiS650_AGPCLK 3

SCD01U50V2ZY

AGP_STOP#

AGP_TRDY#

AGP_IRDY#

AGP_DEVSEL#

AGP_GNT#

AGP_REQ#

AGP_WBF#

AGP_PIPE#

AGP_RBF#

AGP_FRAME#

AGP_ASERR#

1D5V_S0

Layout trace 10/10 mil

BC316

12

BC315

SCD1U16V3KX

AGP_VREF_SIS 14

C9

SCD1U16V3KX

78.10421.2B1

GTL_DSTBN#[3..0] 5

GTL_DSTBP#[3..0] 5

1

2

3

4 5

1

2

3

4 5

1

2

3

4 5

1D5V_S0

RN2

8

7

6

SRN8K2

RN3

8

7

6

SRN8K2

RN4

8

7

6

SRN8K2

BC314

SC4D7U10V5ZY

L30

0R5

Layout trace 10/10 mil

A4XAVDD

BC313

SCD01U50V2ZY

Title

SiS645DX_GTL_AGP(1/4)

Size Document Number Rev

A3

Date: Sheet

TOUCAN2

BC312

12

SCD1U16V3KX

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

747Wednesday, December 18, 2002

E

BC311

SC4D7U10V5ZY

of

3D3V_S0

1 2

3D3V_S0

L29

0R5

1

1 2

VCC_CORE_S0

12

12

BC323

R323

SCD01U50V2ZY

150R3F

4 4

Layout trace 10/10 mil

12

12

BC322

R321

SCD01U50V2ZY

75R3F

HNCVREF

12

BC321

SCD1U10V2MX-1

VCC_CORE_S0

R320 20R3F

1 2

1 2

R322 113R3F

Closed to SiS650

U8A

AH25

GTL_HITM#5

GTL_HIT#5

GTL_DRDY#5

GTL_DBSY#5

GTL_BNR#5

GTL_ADSTB#15

GTL_ADSTB#05

CLKH_SIS650

CLKH_SIS650#

GTL_RS#2

GTL_RS#1

GTL_RS#0

GTL_ADS#5

GTL_REQ#4

GTL_REQ#3

GTL_REQ#2

GTL_REQ#1

GTL_REQ#0

GTL_A#31

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

GTL_A#16

GTL_A#15

GTL_A#14

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

CLKH_SIS6503

CLKH_SIS650#3

GTL_LOCK#5

VCC_CORE_S0

12

12

BC410

R366

3 3

75R3F

SCD01U50V2ZY

Layout trace 10/10 mil

12

12

BC411

R365

SCD01U50V2ZY

150R3F

Closed to SiS650

3D3V_S0

L37

0R5

1 2

2 2

BC531

SC4D7U10V5ZY

3D3V_S0

L12

0R5

1 2

1 1

BC103

SC4D7U10V5ZY

HVREF

12

BC412

SCD1U10V2MX-1

GTL_REQ#[4..0]5

BC530

SCD01U50V3KX

GTL_A#[31..3]5

Layout trace 10/10 mil

BC528

SCD01U50V3KX

A

GTL_DEFER#5

GTL_TRDY#5

GTL_CPURST#5

CC_CPUPWROK5

GTL_BPRI#5

GTL_BR0#5

GTL_RS#[2..0]5

Layout trace 10/10 mil

C4XAVDD

BC529

SCD1U16V3KX

C1XAVDD

BC102

SCD1U16V3KX

AJ26

CPUCLK

AH26

CPUCLK#

U24

HLOCK#

U26

DEFER#

V26

HTRDY#

C20

CPURST#

D19

CPUPWRGD

T27

BPRI#

U25

BREQ0#

T24

RS#2

T26

RS#1

U29

RS#0

V28

ADS#

T28

HITM#

U28

HIT#

W26

DRDY#

V24

DBSY#

V27

BNR#

W28

HREQ#4

W29

HREQ#3

W24

HREQ#2

W25

HREQ#1

Y27

HREQ#0

AD24

HASTB#1

AA24

HASTB#0

AF26

HA#31

AE25

HA#30

AH28

HA#29

AD26

HA#28

AG29

HA#27

AE26

HA#26

AF28

HA#25

AC24

HA#24

AG28

HA#23

AE29

HA#22

AD28

HA#21

AC25

HA#20

AD27

HA#19

AE28

HA#18

AF27

HA#17

AB24

HA#16

AB26

HA#15

AC28

HA#14

AC26

HA#13

AC29

HA#12

AA26

HA#11

AB28

HA#10

AB27

HA#9

AA25

HA#8

AA29

HA#7

AA28

HA#6

Y26

HA#5

Y24

HA#4

Y28

HA#3

SIS645DX

GTL_D#[63..0]5

B

C1XAVSS

HOST BUS(AGTL+)

HD#63

HD#62

HD#61

HD#60

HD#59

F19

B21

A21

E19

D22

GTL_D#60

GTL_D#59

GTL_D#62

GTL_D#63

GTL_D#61

Page 8

A

B

C

D

E

U8C

CLK66_SIS6503

MUTIOL_ZUREQ20

4 4

3 3

2 2

MUTIOL_ZDREQ20

MUTIOL_ZSTB020

MUTIOL_ZSTB0#20

MUTIOL_ZSTB120

MUTIOL_ZSTB1#20

MUTIOL_ZAD[15..0]20

CLK66_SIS650

MUTIOL_ZAD0

MUTIOL_ZAD1

MUTIOL_ZAD2

MUTIOL_ZAD3

MUTIOL_ZAD4

MUTIOL_ZAD5

MUTIOL_ZAD6

MUTIOL_ZAD7

MUTIOL_ZAD8

MUTIOL_ZAD9

MUTIOL_ZAD10

MUTIOL_ZAD11

MUTIOL_ZAD12

MUTIOL_ZAD13

MUTIOL_ZAD14

MUTIOL_ZAD15

SIS650_ZVREF

SIS650_VDDZCMP

SIS650_ZCMP_N

SIS650_ZCMP_P

SIS650_VSSZCMP

SIS650_Z1XAVDD

SIS650_Z1XAVSS

SIS650_Z4XAVDD

SIS650_Z4XAVSS

V3

ZCLK

U6

ZUREQ

U1

ZDREQ

T3

ZSTB0

T1

ZSTB#0

P1

ZSTB1

P3

ZSTB#1

T4

ZAD0

R3

ZAD1

T5

ZAD2

T6

ZAD3

R2

ZAD4

R6

ZAD5

R1

ZAD6

R4

ZAD7

P4

ZAD8

N3

ZAD9

P5

ZAD10

P6

ZAD11

N1

ZAD12

N6

ZAD13

N2

ZAD14

N4

ZAD15

U3

ZVREF

V5

VDDZCMP

U4

ZCMP_N

U2

ZCMP_P

V6

VSSZCMP

W1

Z1XAVDD

W2

Z1XAVSS

V2

Z4XAVDD

V1

Z4XAVSS

SIS645DX

PCIRST#14,20,22,27,28

PWROK21,25,42

RSMRST#21,25

MuTIOL

PCIRST#

PWROK

RSMRST#

PCIRST#

PWROKW4AUXOKW6TRAP1

Y3

TRAP0

TESTMODE2

A10

E10

D11

SIS645_D11

SIS645_A10

SIS645_E10

SIS645_F11

These Pin NC

for SIS645DX

CRT

DLLEN#

ENTEST

TESTMODE1

TESTMODE0

F10

F11

E11

C11

ENTEST

12

R362

4K7R2

SIS645_E11

SIS645_C11

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

TP40TPAD30

TP39TPAD30

TP37TPAD30

TP31TPAD30

TP36TPAD30

TP38TPAD30

C15

A12

B13

A13

F13

E13

D13

D12

B11

E12

A11

F12

E14

D14

F14

B12

C12

C13

C14

B15

A15

B14

A14

SC4D7U10V5ZY

1D8V_S0

BC72

BC97

SC4D7U10V5ZY

BC457

SC4D7U10V5ZY

1D8V_S0

L8

1 2

0R5

G1

1 2

GAP-CLOSE

3D3V_S0

L9 0R5

1 2

1 2

3D3V_S0

L36 0R5

1 2

1 2

12

R46

150R3F

12

R47

150R3F

BC400

SCD1U16V3KX

SCD1U16V3KX

G2

GAP-CLOSE

SCD1U16V3KX

G9

GAP-CLOSE

BC54

SCD1U16V3KX

BC55

SCD1U16V3KX

R75 56R3F

1 2

BC75

SCD01U50V3KX

SIS650_VSSZCMP

Layout trace 10/10 mil

SIS650_Z1XAVDD

BC74

SIS650_Z1XAVSS

Layout trace 10/10 mil

BC398

SIS650_Z4XAVSS

Layout trace 10 mil

R363 56R3F

1 2

BC73

SCD01U50V3KX

SIS650_Z4XAVDD

BC397

SCD01U50V3KX

SIS650_ZVREF

BC399

SCD1U16V3KX

Layout trace 10/10 mil

SIS650_VDDZCMP

SIS650_ZCMP_N

SIS650_ZCMP_P

1 1

Title

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

SiS645DX_MuTIOL(2/4)

Size Document Number Rev

A4

A

B

C

Date: Sheet

D

TOUCAN2

of

847Wednesday, December 18, 2002

E

1

Page 9

A

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA[63..0]12

4 4

M_DM#[7..0]12

M_DQS[7..0]12

3 3

2 2

M_DATA5

M_DATA6

M_DATA7

M_DM#0

M_DQS0

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DM#1

M_DQS1

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DM#2

M_DQS2

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DM#3

M_DQS3

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DM#4

M_DQS4

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DM#5

M_DQS5

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DM#6

M_DQS6

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_DM#7

M_DQS7

U8D

AJ23

AG22

AH21

AJ21

AD23

AE23

AF22

AF21

AD22

AH22

AD21

AG20

AE19

AF19

AE21

AD20

AD19

AH19

AF20

AH20

AF18

AG18

AH17

AD16

AD18

AD17

AF17

AJ17

AE17

AH18

AD14

AG14

AJ13

AE13

AJ15

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AE9

AD8

AG10

AF10

AH9

AF9

AD9

AJ9

AH5

AG4

AE5

AH3

AG6

AF6

AF5

AF4

AH4

AJ3

AE4

AD6

AE2

AC5

AG2

AG1

AF3

AC6

AD4

AF2

AB6

AD3

AA6

AB3

AC4

AE1

AD2

AC1

AB4

AC2

B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB#0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB#1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

SIS645DX

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

SDCLK

FWDSDCLKO

SDRCLKI

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

AH11

AF12

AH12

AG12

AD12

AH15

AF15

AH16

AE15

AD15

AF11

AG8

AJ11

AG16

AF16

AH8

AJ7

AH7

AE7

AF7

AH6

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

SIS650_S3AUXSW#

AA3

AD11

AE11

Y1

SIS650_SDAVDD

Y2

AA1

SIS650_DDRAVDD

AA2

SIS650_DDRVREFA

AJ19

AH2

SIS650_DDRVREFB

W3

SIS650_DIMM_SEL

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_BS0_FR#

M_BS1_FR#

M_A11

M_A12

M_RAS#

M_CAS#

M_WE#

M_CS0_R#

M_CS1_R#

M_CS2_R#

M_CS3_R#

M_CKE0_R#

M_CKE1_R#

M_CKE2_R#

M_CKE3_R#

C

1 2

R375 4K7R3

M_BS0_FR# 11,12

M_BS1_FR# 11,12

M_RAS# 12

M_CAS# 12

M_WE# 12

M_CS0_R# 11,12

M_CS1_R# 11,12

M_CS2_R# 11,12

M_CS3_R# 11,12

M_CKE0_R# 11,12

M_CKE1_R# 11,12

M_CKE2_R# 11,12

M_CKE3_R# 11,12

CLK133_DDR 3

CLK133_DDRBUF 4

3D3V_S3

M_A[12..0] 12

3D3V_S5

Layout trace 10/10 mil

Layout trace 10/10 mil

12

R374

10KR3

D

SIS650_SDAVDD

SCD01U50V3KX

SIS650_DDRAVDD

SCD01U50V3KX

SIS650_S3AUXSW# 21

L35 0R5

BC461

SCD1U16V3KX

BC458

BC77

Layout trace 10/10 mil

Layout trace 10/10 mil

BC459

SC4D7U10V5ZY

BC460

SCD1U16V3KX

BC76

SC4D7U10V5ZY

SIS650_DDRVREFA

BC527

SCD1U16V

SIS650_DDRVREFB

BC526

SCD1U16V

L10 0R5

3D3V_S0

12

3D3V_S0

12

BC100

SCD01U50V3KX

BC101

SCD01U50V3KX

BC98

SCD01U50V3KX

BC99

SCD01U50V3KX

2D5V_S3

12

R108

150R3F

12

R109

150R3F

2D5V_S3

12

R107

150R3F

12

R106

150R3F

E

1 1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

SiS645DX-DDRRAM(3/4)

Size Document Number Rev

A3

A

B

C

D

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

TOUCAN2

947Wednesday, December 18, 2002

E

1

of

Page 10

A

VCC_CORE_S0

A16

A17

A18

B16

B17

B18

C16

C17

C18

D15

D16

D17

D18

E15

E16

E17

E18

F15

F16

F17

F18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VTT

VSS

VSS

VSS

VSS

VSS

VSS

F25

T25

K25

P25

H25

M25

1D8V_S0

3D3V_S0

BC122

SC1U10V3ZY

VCC_CORE_S0

AA20

AA21

AA22

AB21

AB22

BC467

SCD1U16V3KX

1D8V_S5

W20

W11

W13

W15

W17

W10

H21

H22

K16

K17

K18

K19

K20

K21

M20

N20

P20

R20

R21

U20

V20

Y20

Y21

M11

M19

N11

P19

R11

U11

V19

P11

K15

K10

K12

K14

M10

Y11

Y13

Y15

Y17

VTT

VTT

J16

VTT

J20

VTT

J21

VTT

J22

VTT

VTT

VTT

VTT

VTT

VTT

VTT

L20

VTT

VTT

VTT

VTT

VTT

VTT

T20

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

L12

IVDD

L14

IVDD

L15

IVDD

L16

IVDD

L18

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

T19

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDDZ

J14

OVDD

J15

OVDD

OVDD

PVDD

PVDD

PVDD

PVDD

PVDDM

PVDDM

PVDDM

PVDDM

PVDDM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AUX1.8

U9

U10

AUX3.3

A20

A22

A24

A26

C19

VSS

E20

E22

E24

C21

C23

C25

C27

4 4

3 3

2 2

3D3V_S5

B

2D5V_S3 1D8V_S01D5V_S0

AB5

AD5

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE22

V10

V11

W18

Y10

Y12

Y14

Y16

Y18

Y19

AA8

AA9

AA10

AA13

AA14

AA15

AA16

AA17

AB8

AB9

AB13

AB17

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDMY9VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDQE5VDDQE7VDDQE9VDDQG5VDDQJ5VDDQL5VDDQH8VDDQH9VDDQJ8VDDQJ9VDDQ

VCC_Core_S0:266mA(1.7V)

1D8V_S0:995mA

1D5V_S0:33mA

3D3V_S0: 108mA

2D5V_S3:487mA

1D8V_S5:10mA

3D3V_S5:25mA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB4VSSB6VSSC8VSS

VSSD2VSSF2VSSH2VSSK2VSSP2VSST2VSSV4VSS

J27

V25

Y25

AB25

AD25

E27

L27

N27

R27

G27

F29

T29

K29

P29

V29

U27

D29

W27

AA27

AE27

AC27

Y29

H29

M29

AB29

AD29

AF29

AE24

AG25

C10

C

J10

J13

K11

K13

L10

AD1

AF1

VSS

AC3

VSS

AE3

VSS

AG3

VSS

AG5

VSS

AG7

VSS

VDDQ

VSS

AG9

VDDQK9VDDQ

VSS

VSS

AG11

AG13

VDDQ

VSS

AG15

VDDQ

VSS

AG17

N10

VDDQN9VDDQ

VSS

VSS

AG19

AG21

VDDZN5VDDZR5VDDZU5VDDZW5VDDZP9VDDZ

VSS

VSS

VSS

VSS

AJ4

AJ6

AJ8

AJ10

AG23

VSS

P10

R10

T10

VDDZR9VDDZ

VDDZT9VDDZ

VSS

VSS

VSS

VSS

VSS

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

VSS

T11

VDDZ

VSS

AJ24

SIS645DX

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

VSS

AG27

U8B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D

L17

L19

N19

R19

U19

W19

M12

M13

M14

M15

M16

M17

M18

N12

N13

N14

N15

N16

N17

N18

P12

P13

P14

P15

P16

P17

P18

R12

R13

R14

R15

R16

R17

R18

T12

T13

T14

T15

T16

T17

T18

U12

U13

U14

U15

U16

U17

U18

V12

V13

V14

V15

V16

V17

V18

B25

C28

C29

D27

D28

E28

E29

AF23

AF24

AF25

AG24

AG26

AH23

AH24

1D8V_S0

1D5V_S0

R360

100R3F

1D8V_S0

3D3V_S0

1D5V_S0

12

BCB25

SCD01U16V2KX

2D5V_S3

12

R364

100R3F

12

BC401

SCD1U

BC407

SC10U10V6ZY-U

BC406

SCD1U16V3KX

BC354

SCD1U16V3KX

SCD1U16V3KX

BC348

SCD1U16V3KX

BC343

SC10U10V6ZY-U

BC462

SC10U10V6ZY-U

BC469

SCD1U16V3KX

BC465

SCD1U16V3KX

AGP_VREF_VGA 14

CLOSE TO SIS645DX

BC641

SCD1U16V3KX

BC351

SCD1U16V3KX

BC346

BC350

SCD1U16V3KX

BC341

SCD1U16V3KX

BC466

SC10U10V6ZY-U

BC470

SCD1U16V3KX

BC468

SCD1U16V3KX

BC405

SCD1U16V3KX

E

BC96

SC1U10V3ZY

BC408

SCD1U16V3KX

BC344

SCD1U16V3KX

BC345

SCD1U16V3KX

BC342

SCD1U16V3KX

BC340

SCD1U16V3KX

BC402

SC10U10V6ZY-U

BC464

SCD1U16V3KX

BC471

SCD1U16V3KX

BC565

SCD1U16V3KX

BC472

SCD1U16V3KX

BC347

SCD1U16V3KX

BC463

SCD1U16V3KX

BC475

SCD1U16V3KX

BC403

SC1U10V3ZY

BC113

SCD1U16V3KX

A

BC404

SCD1U16V3KX

3D3V_S5

1 1

VCC_CORE_S0

12

BC355

SCD1U10V2MX-1

BC357

SCD1U16V3KX

12

BC409

SCD1U10V2MX-1

BC319

SCD1U16V3KX

BC474

SCD1U16V3KX

BC353

SCD1U16V3KX

B

BC318

SCD1U16V3KX

BC356

SCD1U16V3KX

VCC_CORE_S0

BC352

SC10U10V6ZY-U

BC349

SC1U10V3ZY

BC317

SC10U10V6ZY-U

BC473

SC1U10V3ZY

C

BC476

SC10U10V6ZY-U

BC320

SC1U10V3ZY

BC358

SCD1U16V3KX

BC413

SC1U10V3ZY

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

SiS645DX_POWER_PLANE(4/4)

Size Document Number Rev

A3

D

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

TOUCAN2

10 47Wednesday, December 18, 2002

E

1

of

Page 11

2D5V_S3

12

12

R135

470R3F

64.47005.651

R134

470R3F

64.47005.651

1D25V_DDR

DM1

BC195

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

201

GND

DDR-SODIMM-N 62.10017.191

M_A_FR_0

M_A_FR_1

M_A_FR_2

M_A_FR_3

M_A_FR_4

M_A_FR_5

M_A_FR_6

M_A_FR_7

M_A_FR_8

M_A_FR_9

M_A_FR_10

M_A_FR_11

M_A_FR_12

M_BS0_FR#9,12

M_BS1_FR#9,12

M_RAS_FR#12

M_CAS_FR#12 M_CAS_SR#12

M_WE_FR#12

1 2

R136

BC131

0R3-0-U

SCD1U

TP21TPAD30

TP25TPAD30

TP20TPAD30

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

DM1_RESET#

DM1_A13

DM1_BA2

DDR_VREF_SKT

12

SCD01U16V2KX

78.10321.2F1

121

/CS0

122

/CS1

96

CKE0

95

CKE1

11

25

47

61

133

147

169

183

77

12

26

48

62

134

148

170

184

78

35

37

160

158

89

91

195

193

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

202

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

SMBC_SIS962

SMBD_SIS962

DM1_SA0

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

NORMAL TYPE

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

M_CS0_R# 9,12

M_CS1_R# 9,12

M_CKE0_R# 9,12

M_CKE1_R# 9,12

M_DM#_R0

M_DM#_R1

M_DM#_R2

M_DM#_R3

M_DM#_R4

M_DM#_R5

M_DM#_R6

M_DM#_R7

CLK_DDR1 4

CLK_DDR1# 4

CLK_DDR2 4

CLK_DDR2# 4

CLK_DDR0 4

CLK_DDR0# 4

R162

DUMMY-R3

1 2

12

R161

0R3-0-U

2D5V_S3 2D5V_S3

M_A_SR_[12..0]12M_A_FR_[12..0]12

M_BS0_SR#12

M_BS1_SR#12

M_DATA_R_[63..0]12

M_RAS_SR#12

M_WE_SR#12

TP26TPAD30

TP27TPAD30

TP24TPAD30

BC159

SCD1U

M_A_SR_0

M_A_SR_1

M_A_SR_2

M_A_SR_3

M_A_SR_4

M_A_SR_5

M_A_SR_6

M_A_SR_7

M_A_SR_8

M_A_SR_9

M_A_SR_10

M_A_SR_11

M_A_SR_12

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

DM2_RESET#

DM2_A13

DM2_BA2

DDR_VREF_SKT

3D3V_S03D3V_S0

DM2

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS