Vinafix.com

5

4

3

2

1

01

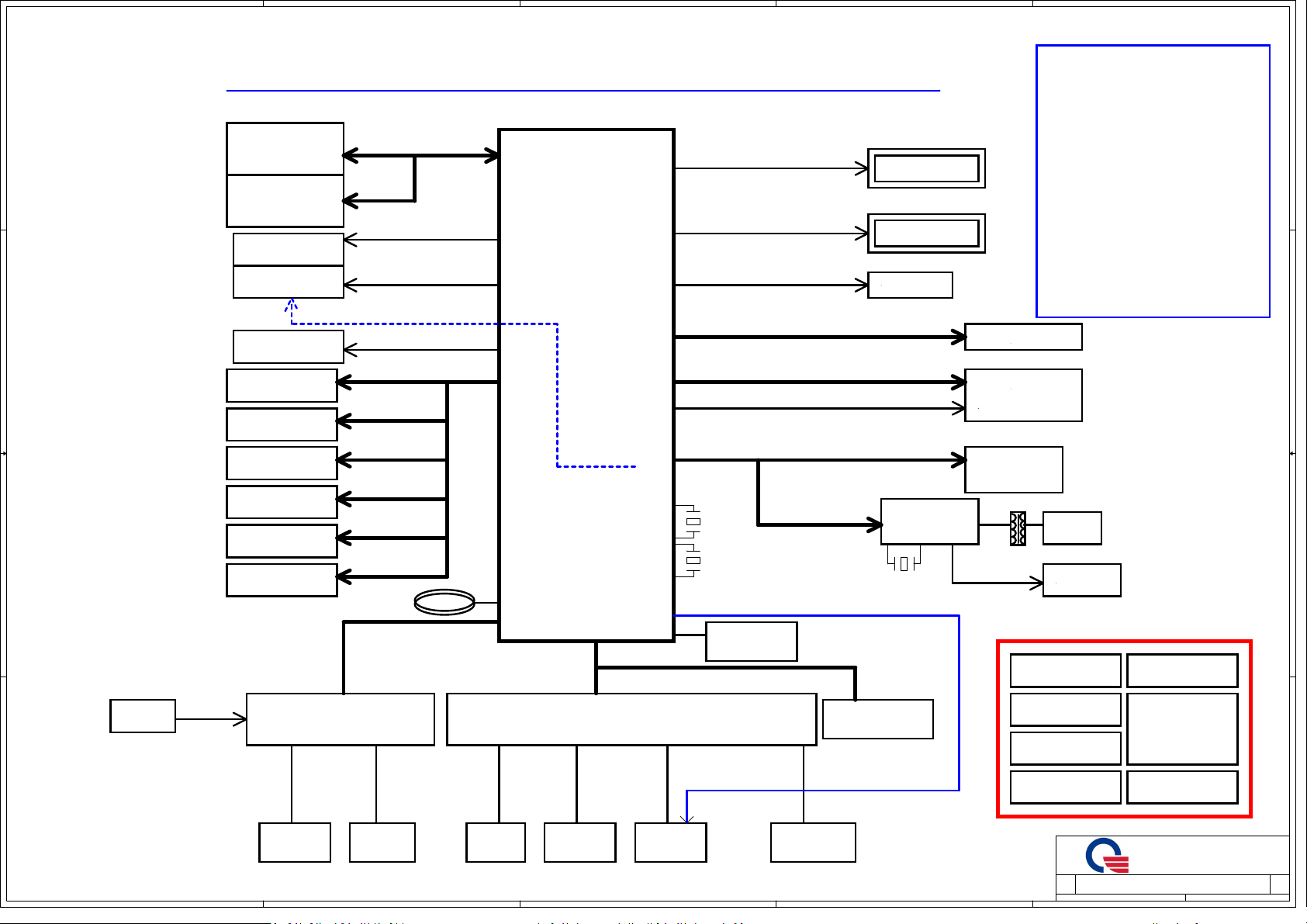

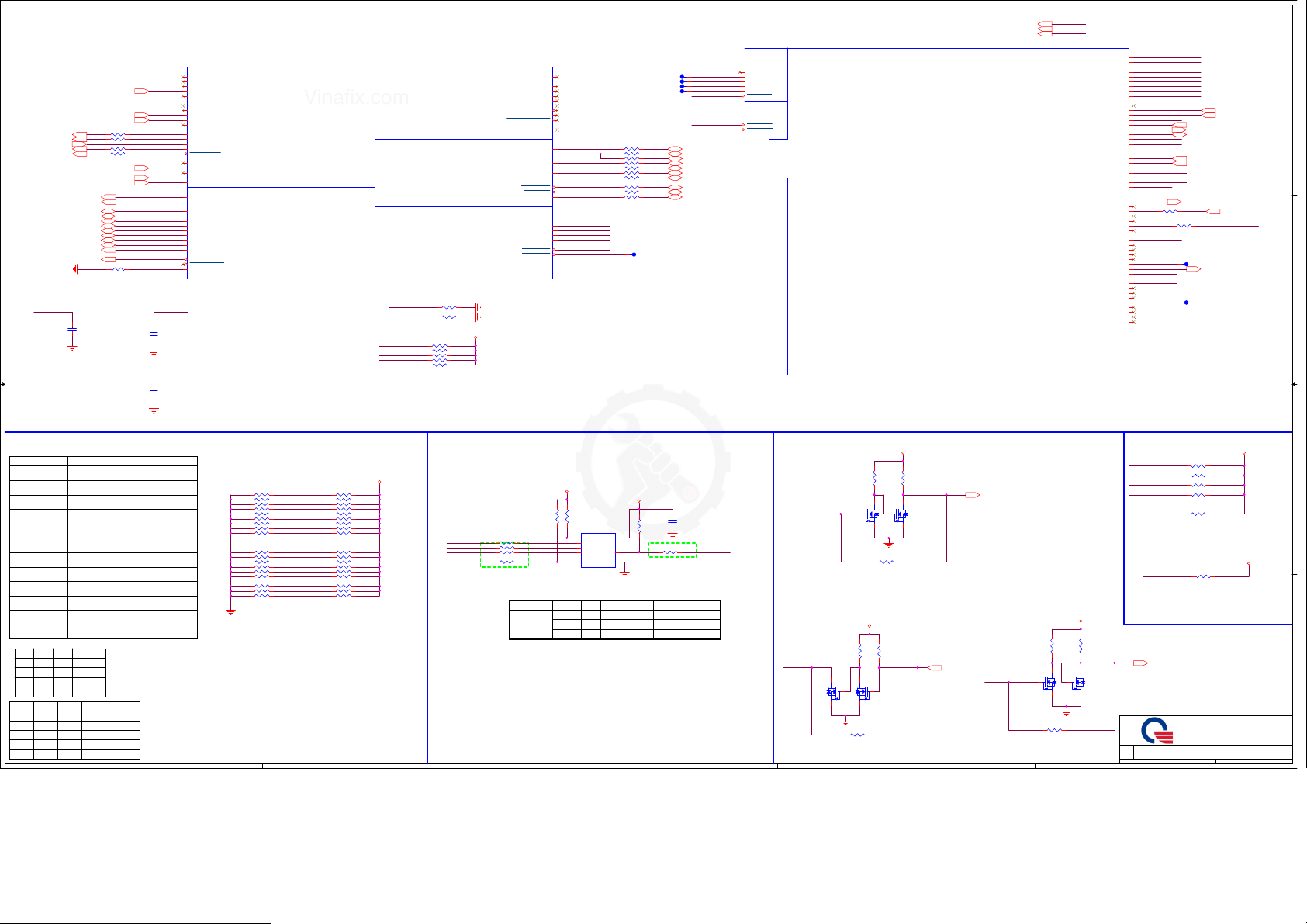

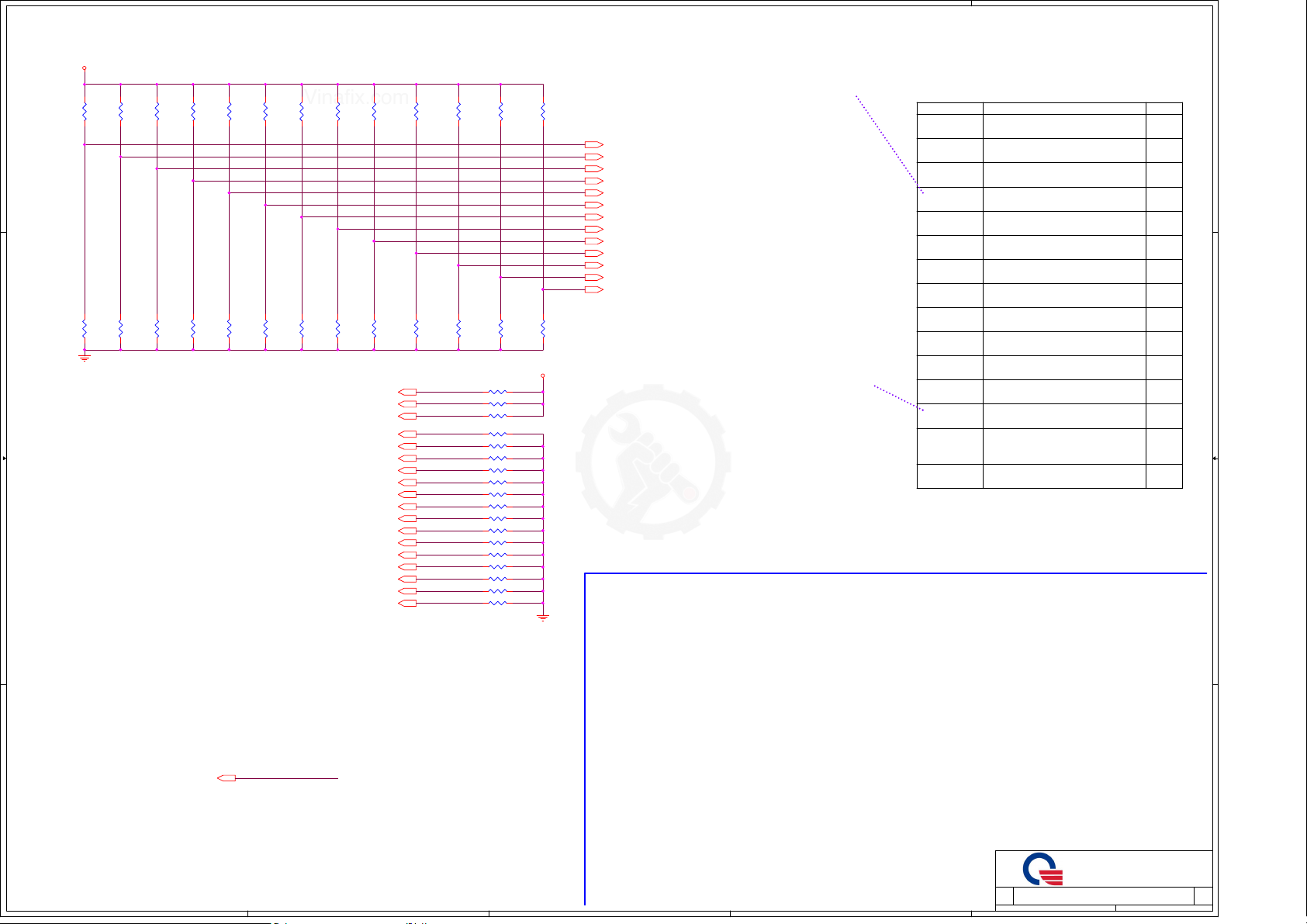

Z8G SYSTEM BLOCK DIAGRAM

TPM@ : TPM

GS@ : G-SENSOR

CB@ : Cloud book SKU

D D

DDR4

DIMM CHA

DDR4

Memory down CHB

SATA - HDD

SATA SSD M.2

P10

P11

P17

P17

Dual Channel DDR4

2400 MHz MAX

SATA0

SATA1

Gemini Lake - 6W

(BROXTON-P)

MCP 1090 pins

SATA

SMB

eDP

DP

EDP

DDI0

eDP Conn.

HDMI Conn.

G-sensor

P13

P15

P19

EJ@ : EJ sereies SKU

KBL@ : keyboard backlight

NVL@ : none LED panel boost

DBG@ : Debug card

VL@ : LED panel boost

EC@ : EMMC

TPC@ : Type C function

w/o GS@: stuff with none GS sku

SSD@ : SATA interface SSD

PSD@ : PCIE interfance SSD

ODD@ : ODD function

SDM@ : SO-DIMM

OBM@ : On board Memory

CNV@ : CNVi WLAN card

BOM

I2C_0

SPI

USB3-0 + USB2-0

USB3-1 + USB3-2

USB2-1

X'TAL

32.768KHz

X'TAL 19.2MHz

SPI ROM 8M

P5

P22

PCIE-3

PCIE-2

X'TAL 25MHz

TPM(NPCT650)

RTL8411B-CG

10/100/1G

P17

C C

B B

32GB/64GB

USB2.0 Port 1

USB2.0 Port 2

Blue Tooth

Touch Screen

CCD(Camera)

ODD bridge

ASM1153

P17

USB2-2

P20

USB2-3

P20

USB2-4

P18

USB2-5

P13

USB2-6

P13

USB2-7

P17

Azalia

D-MIC

P14

AUDIO CODEC

ALC255

P6

EMMC

BATTERY

P14

EMMC5.0

USB2.0

Integrated PCH

RTC

IHDA

PCIE-0/1

LPC

USB3.0/2.0

PCI-E

P2~P8

EC

IT8987

USB3.0 Port

M.2 NGFF

WLAN+BT

P16

Type C port

BQ24780SRUYR

Batery Charger

RT6256BGQUF

+3VPCU/+5VPCU

G5335QT2U

P20

P21

P17

RJ45

Cardreader

+1.05V

P16

P16

P23

P24

P25

RT8231BGQW

+1.2VSUS

G5719CTB1U

M5671RE1U

G9661MF11U

+1.8V_S5 / +1.24V_S5/+1.5V

P26

P29

A A

P14

Speaker

P14

4

HP JACK

5

K/B Con.

P19

SPI ROM 1M

P22

Touch PAD

P19

3

Fan module

(PWM signal)

P19

2

RT3601EAGQW

+VCCGI / +VNN

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

P27~28

Thermal Protection

Discharger

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Block Diagram

Block Diagram

Block Diagram

1

Z8G

Z8G

Z8G

P30

1 35Tuesday, December 26, 2017

1 35Tuesday, December 26, 2017

1 35Tuesday, December 26, 2017

1A

1A

1A

Vinafix.com

5

4

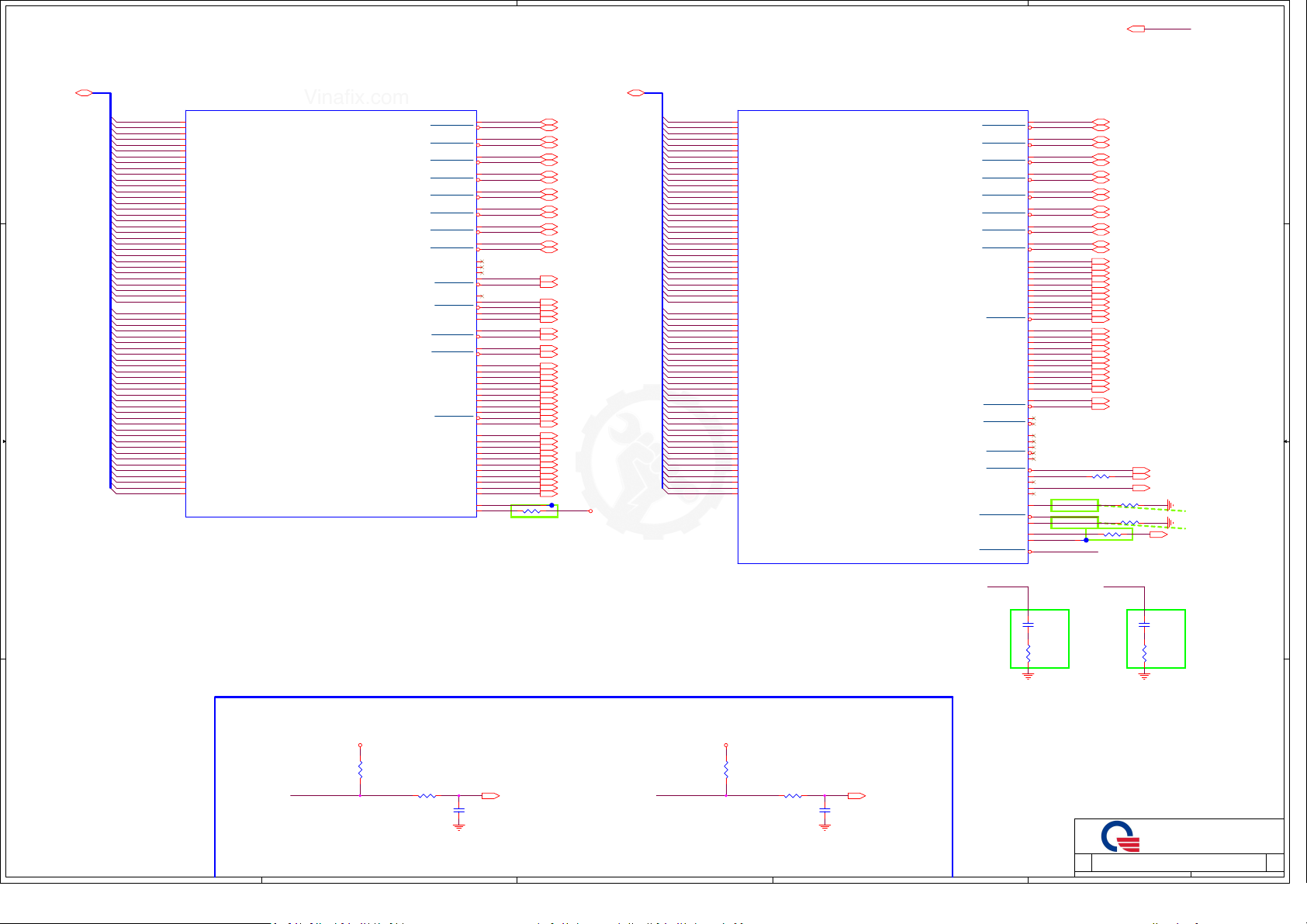

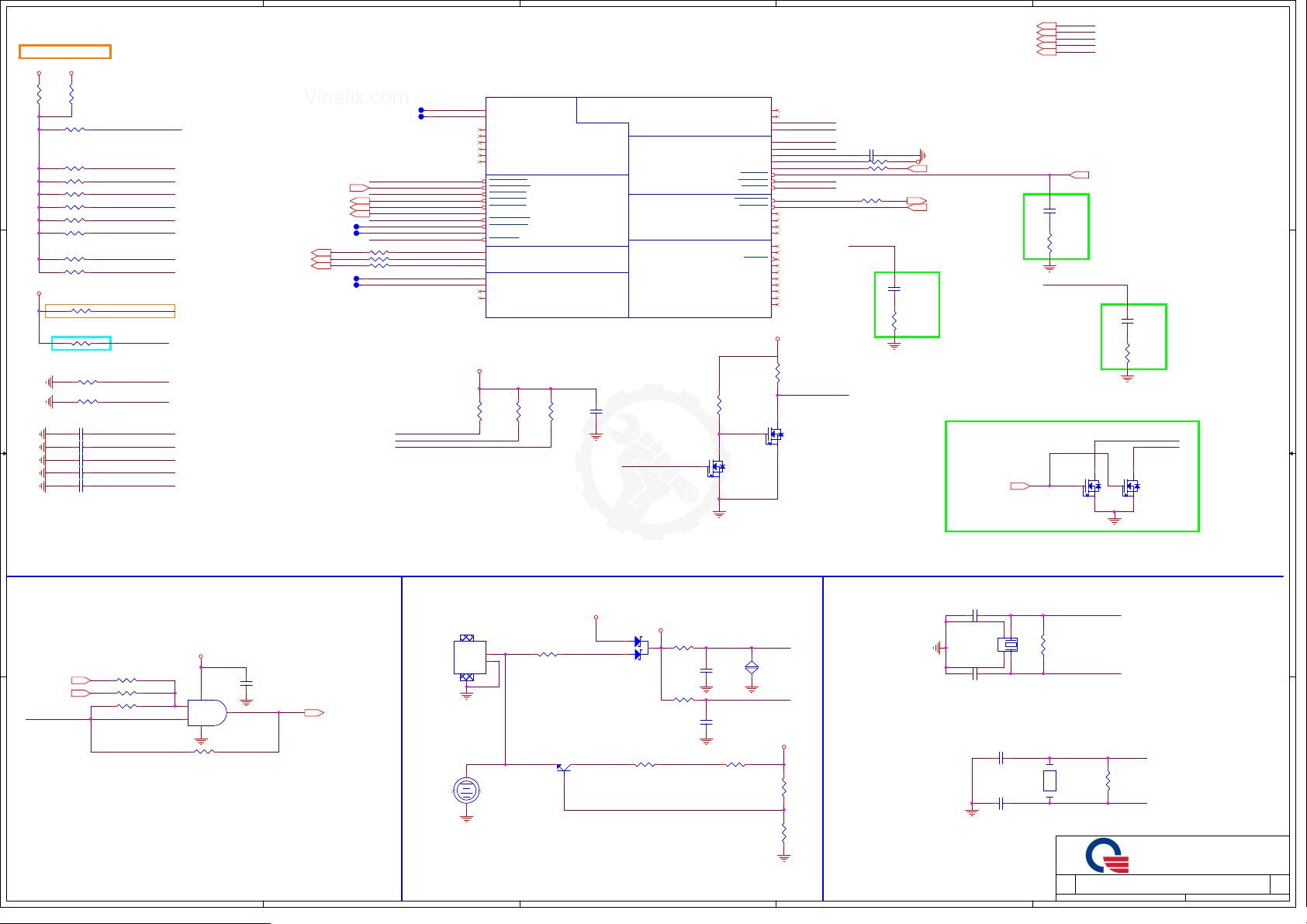

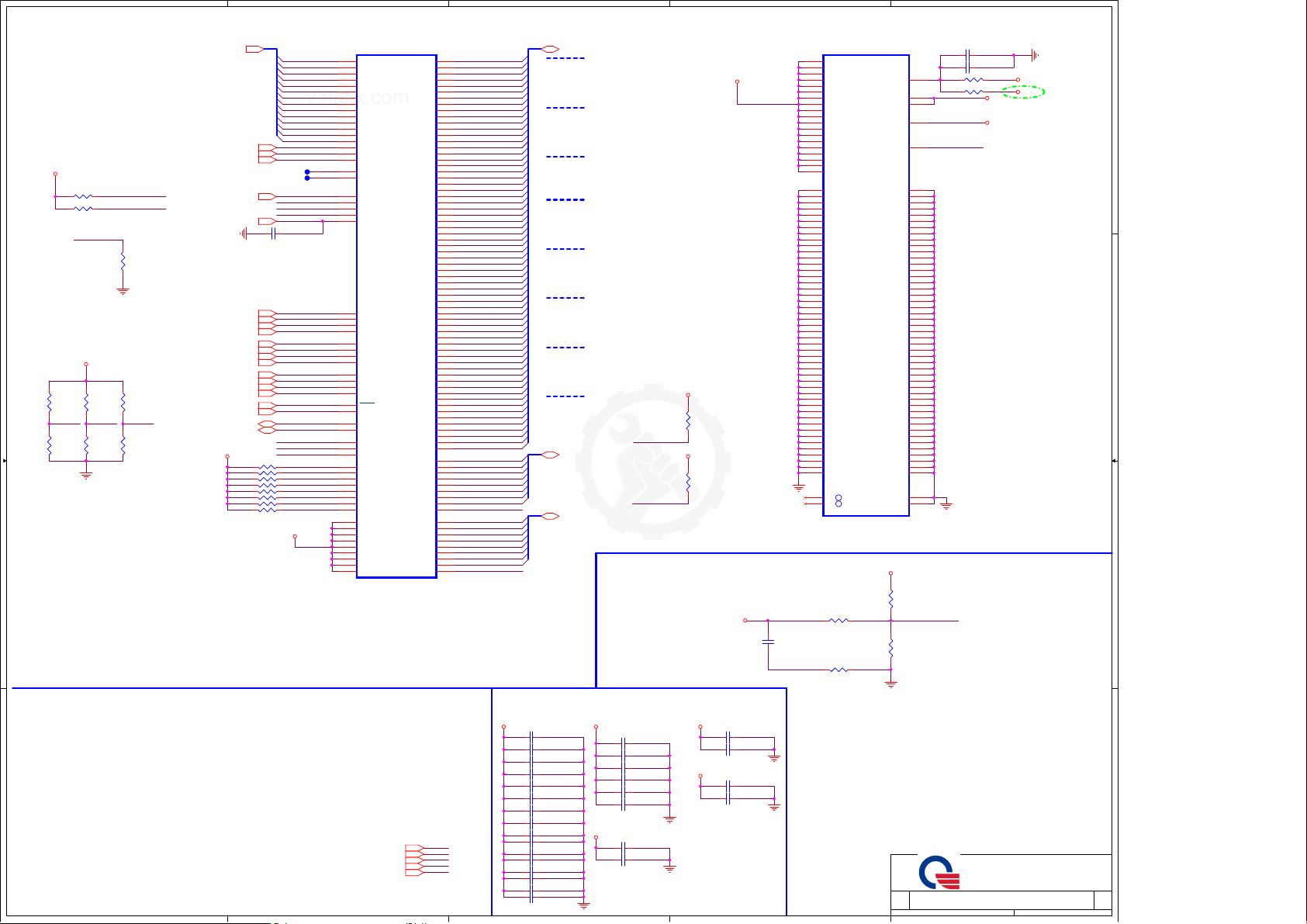

GLK ULT (DDR4)

3

2

+1.2VSUS_ Q[7]

1

02

M_A_DQ[63:0][10]

D D

C C

B B

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

AW53

BJ36

BK37

BJ35

BL36

BJ39

BL40

BJ40

BK41

BA35

AY33

BA33

AY35

BA37

AY37

AY39

BA39

BL34

BL30

BJ29

BK29

BJ33

BK33

BJ34

BJ30

BD29

BF29

BH29

BF33

BC29

BD33

BF35

BH35

AR53

AP55

AP53

AN54

AU54

AV53

AV55

AU51

AU48

AU49

BA46

BA48

BA49

BA51

AR51

AY55

BA54

BA53

AY53

BC53

BD55

BE54

BD53

AN43

AN44

AR48

AU41

AU43

AN41

AN39

AU44

U27A

MEM_CH0_DQ 40

MEM_CH0_DQ 41

MEM_CH0_DQ 42

MEM_CH0_DQ 43

MEM_CH0_DQ 44

MEM_CH0_DQ 45

MEM_CH0_DQ 46

MEM_CH0_DQ 47

MEM_CH0_DQ 32

MEM_CH0_DQ 33

MEM_CH0_DQ 34

MEM_CH0_DQ 35

MEM_CH0_DQ 36

MEM_CH0_DQ 37

MEM_CH0_DQ 38

MEM_CH0_DQ 39

MEM_CH0_DQ 56

MEM_CH0_DQ 57

MEM_CH0_DQ 58

MEM_CH0_DQ 59

MEM_CH0_DQ 60

MEM_CH0_DQ 61

MEM_CH0_DQ 62

MEM_CH0_DQ 63

MEM_CH0_DQ 48

MEM_CH0_DQ 49

MEM_CH0_DQ 50

MEM_CH0_DQ 51

MEM_CH0_DQ 52

MEM_CH0_DQ 53

MEM_CH0_DQ 54

MEM_CH0_DQ 55

MEM_CH0_DQ 0

MEM_CH0_DQ 1

MEM_CH0_DQ 2

MEM_CH0_DQ 3

MEM_CH0_DQ 4

MEM_CH0_DQ 5

MEM_CH0_DQ 6

MEM_CH0_DQ 7

MEM_CH0_DQ 8

MEM_CH0_DQ 9

MEM_CH0_DQ 10

MEM_CH0_DQ 11

MEM_CH0_DQ 12

MEM_CH0_DQ 13

MEM_CH0_DQ 14

MEM_CH0_DQ 15

MEM_CH0_DQ 16

MEM_CH0_DQ 17

MEM_CH0_DQ 18

MEM_CH0_DQ 19

MEM_CH0_DQ 20

MEM_CH0_DQ 21

MEM_CH0_DQ 22

MEM_CH0_DQ 23

MEM_CH0_DQ 24

MEM_CH0_DQ 25

MEM_CH0_DQ 26

MEM_CH0_DQ 27

MEM_CH0_DQ 28

MEM_CH0_DQ 29

MEM_CH0_DQ 30

MEM_CH0_DQ 31

DDR4_LP3_LP4DDR4_LP3_LP4

MEM_CH0_DQ S0_P

MEM_CH0_DQ S0

MEM_CH0_DQ S1_P

MEM_CH0_DQ S1

MEM_CH0_DQ S2_P

MEM_CH0_DQ S2

MEM_CH0_DQ S3_P

MEM_CH0_DQ S3

MEM_CH0_DQ S4_P

MEM_CH0_DQ S4

MEM_CH0_DQ S5_P

MEM_CH0_DQ S5

MEM_CH0_DQ S6_P

MEM_CH0_DQ S6

MEM_CH0_DQ S7_P

MEM_CH0_DQ S7

DDR0

1 OF 13

NCTF1

NCTF2

NCTF3

MEM_CH0_O DT1

MEM_CH0_CS 1

NCTF4

MEM_CH0_O DT0

MEM_CH0_CS 0

MEM_CH0_CK E1

MEM_CH0_CK E0

MEM_CH0_CL K0_P

MEM_CH0_CL K0

MEM_CH0_CL K1_P

MEM_CH0_CL K1

MEM_CH0_MA 0

MEM_CH0_MA 1

MEM_CH0_MA 2

MEM_CH0_MA 10

MEM_CH0_MA 13

MEM_CH0_MA 16

MEM_CH0_B A1

MEM_CH0_B A0

MEM_CH0_B G1

MEM_CH0_A CT

MEM_CH0_MA 3

MEM_CH0_MA 4

MEM_CH0_MA 5

MEM_CH0_MA 6

MEM_CH0_MA 7

MEM_CH0_MA 8

MEM_CH0_MA 9

MEM_CH0_MA 11

MEM_CH0_MA 12

MEM_CH0_MA 14

MEM_CH0_MA 15

MEM_CH0_B G0

MEM_CH0_V REFDQ

MEM_CH0_V REFCA

M_A_DQSP 0

AT53

M_A_DQSN0

AT55

M_A_DQSP 1

AW49

M_A_DQSN1

AW48

M_A_DQSP 2

BC54

M_A_DQSN2

BB53

M_A_DQSP 3

AR41

M_A_DQSN3

AR43

M_A_DQSP 4

AV37

M_A_DQSN4

AV35

M_A_DQSP 5

BL38

M_A_DQSN5

BJ38

M_A_DQSP 6

BF31

M_A_DQSN6

BD31

M_A_DQSP 7

BJ32

M_A_DQSN7

BK31

BG54

BH54

BJ42

M_A_ODT1

BF39

M_A_CS#1

BK43

BL44

M_A_ODT0

BD39

M_A_CS#0

BJ43

M_A_CKE1

BF54

M_A_CKE0

BF55

M_A_CLK0

BE49

M_A_CLK0 #

BE51

M_A_CLK1

BC49

M_A_CLK1 #

BC48

M_A_A0

BD45

M_A_A1

BH50

M_A_A2

BH47

M_A_A10

BF45

M_A_A13

BH43

M_A_RAS#

BD41

M_A_BA#1

BH51

M_A_BA#0

BD43

M_A_BG#1

BF43

M_A_ACT#

BF41

M_A_A3

BG52

M_A_A4

BK45

M_A_A5

BJ46

M_A_A6

BJ44

M_A_A7

BJ47

M_A_A8

BJ45

M_A_A9

BK47

M_A_A11

BJ51

M_A_A12

BJ52

M_A_WE #

BJ48

M_A_CAS#

BJ50

M_A_BG#0

BL50

M0_VREF_DQ

AY31

AV29

R188 *0_5%_4

Default no stuff

M_B_DQ[63:0][11]

M_A_DQSP 0 [10]

M_A_DQSN0 [10]

M_A_DQSP 1 [10]

M_A_DQSN1 [10]

M_A_DQSP 2 [10]

M_A_DQSN2 [10]

M_A_DQSP 3 [10]

M_A_DQSN3 [10]

M_A_DQSP 4 [10]

M_A_DQSN4 [10]

M_A_DQSP 5 [10]

M_A_DQSN5 [10]

M_A_DQSP 6 [10]

M_A_DQSN6 [10]

M_A_DQSP 7 [10]

M_A_DQSN7 [10]

M_A_ODT1_DIMM [10]

M_A_CS#1 [10]

M_A_ODT0_DIMM [10]

M_A_CS#0 [10]

M_A_CKE1 [10]

M_A_CKE0 [10]

M_A_CLK0 [10]

M_A_CLK0 # [10]

M_A_CLK1 [10]

M_A_CLK1 # [10]

M_A_A0 [10]

M_A_A1 [10]

M_A_A2 [10]

M_A_A10 [10]

M_A_A13 [10]

M_A_RAS# [10]

M_A_BA#1 [10]

M_A_BA#0 [10]

M_A_BG#1 [10]

M_A_ACT# [10]

M_A_A3 [10]

M_A_A4 [10]

M_A_A5 [10]

M_A_A6 [10]

M_A_A7 [10]

M_A_A8 [10]

M_A_A9 [10]

M_A_A11 [10]

M_A_A12 [10]

M_A_WE # [10]

M_A_CAS# [10]

M_A_BG#0 [10]

TP12

+VREF_CA_CPU

VREF trace must be at least

20 mils wide and space

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

AN15

AN17

AU12

AN12

AN13

AU13

AU15

BA10

BJ26

BL26

BJ27

BK27

BJ23

BK23

BJ22

BL22

BD27

BF27

BH27

BC27

BH21

BF23

BD23

BF21

BK19

BJ20

BL20

BJ21

BJ17

BJ16

BK15

BL16

BA21

AY23

BA23

BA17

AY21

AY17

AY19

BA19

AY3

BD3

BD1

BC3

AY1

BA3

BA2

BE2

AR8

AP3

AU2

AV3

AW3

AN2

AP1

AR3

AV1

AR5

BA8

AU7

AU5

BA5

BA7

AU8

U27B

MEM_CH1_DQ 40

MEM_CH1_DQ 41

MEM_CH1_DQ 42

MEM_CH1_DQ 43

MEM_CH1_DQ 44

MEM_CH1_DQ 45

MEM_CH1_DQ 46

MEM_CH1_DQ 47

MEM_CH1_DQ 32

MEM_CH1_DQ 33

MEM_CH1_DQ 34

MEM_CH1_DQ 35

MEM_CH1_DQ 36

MEM_CH1_DQ 37

MEM_CH1_DQ 38

MEM_CH1_DQ 39

MEM_CH1_DQ 56

MEM_CH1_DQ 57

MEM_CH1_DQ 58

MEM_CH1_DQ 59

MEM_CH1_DQ 60

MEM_CH1_DQ 61

MEM_CH1_DQ 62

MEM_CH1_DQ 63

MEM_CH1_DQ 48

MEM_CH1_DQ 49

MEM_CH1_DQ 50

MEM_CH1_DQ 51

MEM_CH1_DQ 52

MEM_CH1_DQ 53

MEM_CH1_DQ 54

MEM_CH1_DQ 55

MEM_CH1_DQ 0

MEM_CH1_DQ 1

MEM_CH1_DQ 2

MEM_CH1_DQ 3

MEM_CH1_DQ 4

MEM_CH1_DQ 5

MEM_CH1_DQ 6

MEM_CH1_DQ 7

MEM_CH1_DQ 8

MEM_CH1_DQ 9

MEM_CH1_DQ 10

MEM_CH1_DQ 11

MEM_CH1_DQ 12

MEM_CH1_DQ 13

MEM_CH1_DQ 14

MEM_CH1_DQ 15

MEM_CH1_DQ 16

MEM_CH1_DQ 17

MEM_CH1_DQ 18

MEM_CH1_DQ 19

MEM_CH1_DQ 20

MEM_CH1_DQ 21

MEM_CH1_DQ 22

MEM_CH1_DQ 23

MEM_CH1_DQ 24

MEM_CH1_DQ 25

MEM_CH1_DQ 26

MEM_CH1_DQ 27

MEM_CH1_DQ 28

MEM_CH1_DQ 29

MEM_CH1_DQ 30

MEM_CH1_DQ 31

DDR4_LP3_LP4DDR4_LP3_LP4

MEM_CH1_DQ S0_P

MEM_CH1_DQ S0

MEM_CH1_DQ S1_P

MEM_CH1_DQ S1

MEM_CH1_DQ S2_P

MEM_CH1_DQ S2

MEM_CH1_DQ S3_P

MEM_CH1_DQ S3

MEM_CH1_DQ S4_P

MEM_CH1_DQ S4

MEM_CH1_DQ S5_P

MEM_CH1_DQ S5

MEM_CH1_DQ S6_P

MEM_CH1_DQ S6

MEM_CH1_DQ S7_P

MEM_CH1_DQ S7

DDR1

2 OF 13

MEM_CH1_MA 0

MEM_CH1_MA 1

MEM_CH1_MA 2

MEM_CH1_MA 3

MEM_CH1_MA 10

MEM_CH1_MA 13

MEM_CH1_MA 16

MEM_CH1_B A0

MEM_CH1_B A1

MEM_CH1_B G1

MEM_CH1_A CT

MEM_CH1_MA 11

MEM_CH1_MA 12

MEM_CH1_MA 14

MEM_CH1_MA 15

MEM_CH1_B G0

MEM_CH1_MA 4

MEM_CH1_MA 5

MEM_CH1_MA 6

MEM_CH1_MA 7

MEM_CH1_MA 8

MEM_CH1_MA 9

MEM_CH1_CL K0_P

MEM_CH1_CL K0

MEM_CH1_CL K1_P

MEM_CH1_CL K1

NCTF3

NCTF4

NCTF1

MEM_CH1_CS 1

MEM_CH1_O DT1

MEM_CH1_CS 0

MEM_CH1_O DT0

NCTF2

MEM_CH1_CK E0

MEM_CH1_CK E1

MEM_CH0_RCOMP

MEM_CH1_RE SET

MEM_CH1_RCOMP

MEM_CH1_V REFCA

MEM_CH1_V REFDQ

MEM_CH0_RE SET

MA_DRAMRST# MB_DRAMRST#

BJ24

BK25

BD25

BF25

BL18

BJ18

AV19

AV21

AR13

AR15

BB3

BC2

AW7

AW8

AT1

AT3

BH9

BC13

BD11

BD13

BF11

BE5

BH5

BH6

BF13

BG4

BE7

BK11

BJ12

BK9

BJ11

BJ10

BJ4

BL6

BJ5

BJ9

BJ6

BJ8

BF17

BD17

BF15

BH15

BJ13

BL12

BF1

BF2

BC7

BH2

BC8

BG2

BK13

BJ14

AY29

BC15

AY27

AV27

AY25

BC43

M_B_CS#0

M_B_ODT0

M_B_CKE0

M1_VREF_CA

M1_VREF_DQ

M_B_DQSP 0

M_B_DQSN0

M_B_DQSP 1

M_B_DQSN1

M_B_DQSP 2

M_B_DQSN2

M_B_DQSP 3

M_B_DQSN3

M_B_DQSP 4

M_B_DQSN4

M_B_DQSP 5

M_B_DQSN5

M_B_DQSP 6

M_B_DQSN6

M_B_DQSP 7

M_B_DQSN7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A10

M_B_A13

M_B_A16

M_B_BA#0

M_B_BA#1

M_B_BG#1

M_B_ACT#

M_B_A11

M_B_A12

M_B_A14

M_B_A15

M_B_BG#0

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_CLK0

M_B_CLK0 #

R172 *0_5%_4

MEM_CH0_RCOMP

MB_DRAMRST#

MEM_CH1_RCOMP

R491 *0_5%_4

MA_DRAMRST#

Default no stuff

M_B_DQSP 0 [11]

M_B_DQSN0 [11]

M_B_DQSP 1 [11]

M_B_DQSN1 [11]

M_B_DQSP 2 [11]

M_B_DQSN2 [11]

M_B_DQSP 3 [11]

M_B_DQSN3 [11]

M_B_DQSP 4 [11]

M_B_DQSN4 [11]

M_B_DQSP 5 [11]

M_B_DQSN5 [11]

M_B_DQSP 6 [11]

M_B_DQSN6 [11]

M_B_DQSP 7 [11]

M_B_DQSN7 [11]

M_B_A0 [11]

M_B_A1 [11]

M_B_A2 [11]

M_B_A3 [11]

M_B_A10 [11]

M_B_A13 [11]

M_B_A16 [11]

M_B_BA#0 [11]

M_B_BA#1 [11]

M_B_BG#1 [11]

M_B_ACT# [11]

M_B_A11 [11]

M_B_A12 [11]

M_B_A14 [11]

M_B_A15 [11]

M_B_BG#0 [11]

M_B_A4 [11]

M_B_A5 [11]

M_B_A6 [11]

M_B_A7 [11]

M_B_A8 [11]

M_B_A9 [11]

M_B_CLK0 [11]

M_B_CLK0 # [11]

R179 110_1%_ 4

R183 110_1%_ 4

TP13

M_B_CS#0 [11]

M_B_ODT0_MD [11]

M_B_CKE0 [11]

R179 , R183 close to CPU

Trace length < 500 mils

Trace width = 15 mils

Trace spacing = 20 mils

+VREFDQ_SB_M3 [11]

VREF trace must be at least

20 mils wide and space

colsed to CPU pin within 100 mils

C544

*1000p/5 0V_4

R583

*10_5%_4

C545

*1000p/5 0V_4

R584

*10_5%_4

DRAMRST-SODIMM

+1.2VSUS_ Q +1.2VSUS_ Q

A A

5

CPU

MA_DRAMRST# MB_DRAMRST#

Trace length < 4500 mils, 50 ohm impendence

Trace spacing = 15 mils

R187

1K_1%_4

R178 *S_4

4

C144

*0.1u/16V_4

SO-DIMM1

M_A_DRAMRS T# [10]

Trace length < 4500 mils, 50 ohm impendence

Trace spacing = 15 mils

CPU

3

R180

1K_1%_4

R182 *S_4

C142

*0.1u/16V_4

SO-DIMM2

M_B_DRAMRS T# [11]

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

PROJECT :

GLK(MEMORY)

GLK(MEMORY)

GLK(MEMORY)

1

Z8G

Z8G

Z8G

2 35

2 35

2 35

1A

1A

1A

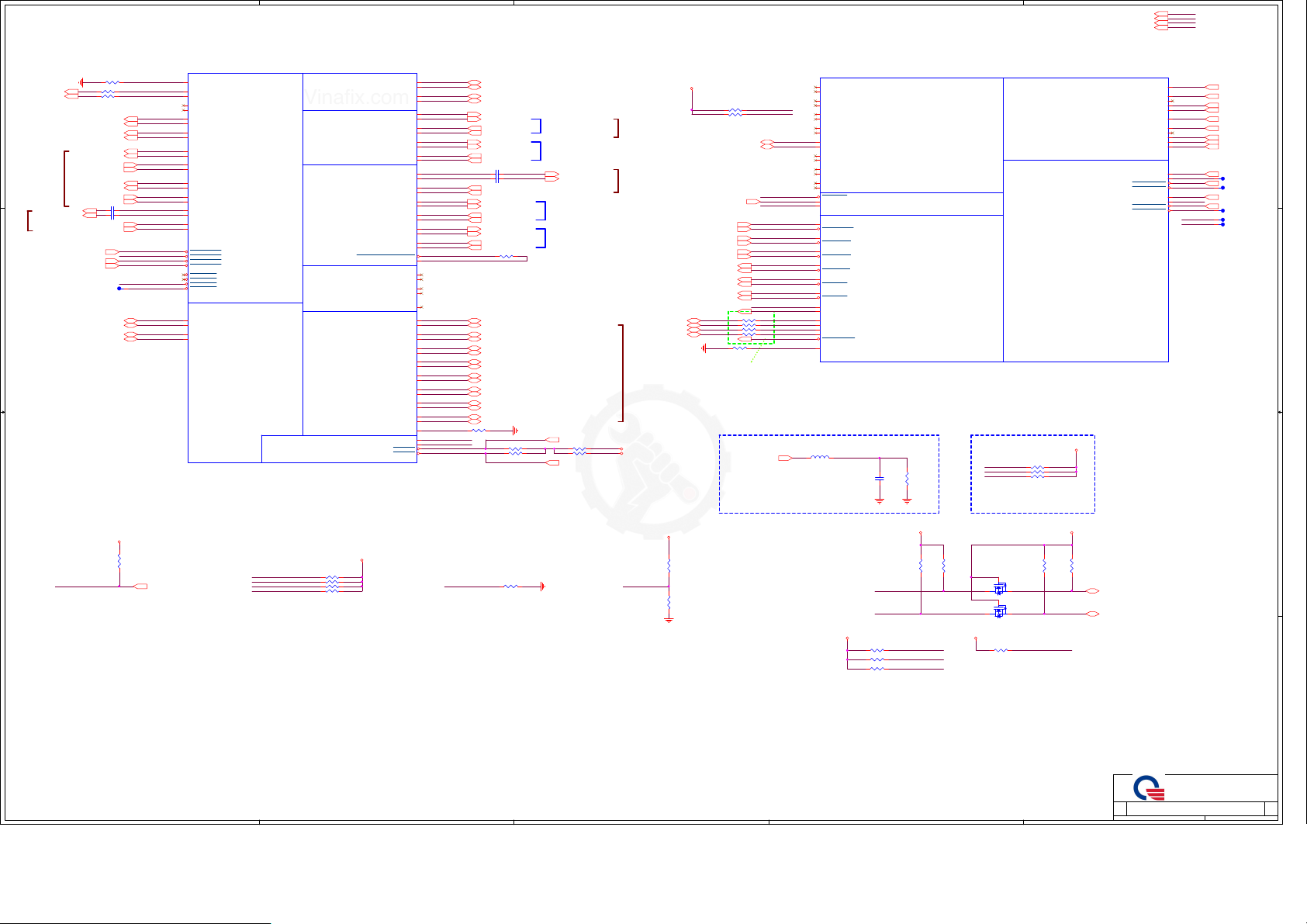

Vinafix.com

5

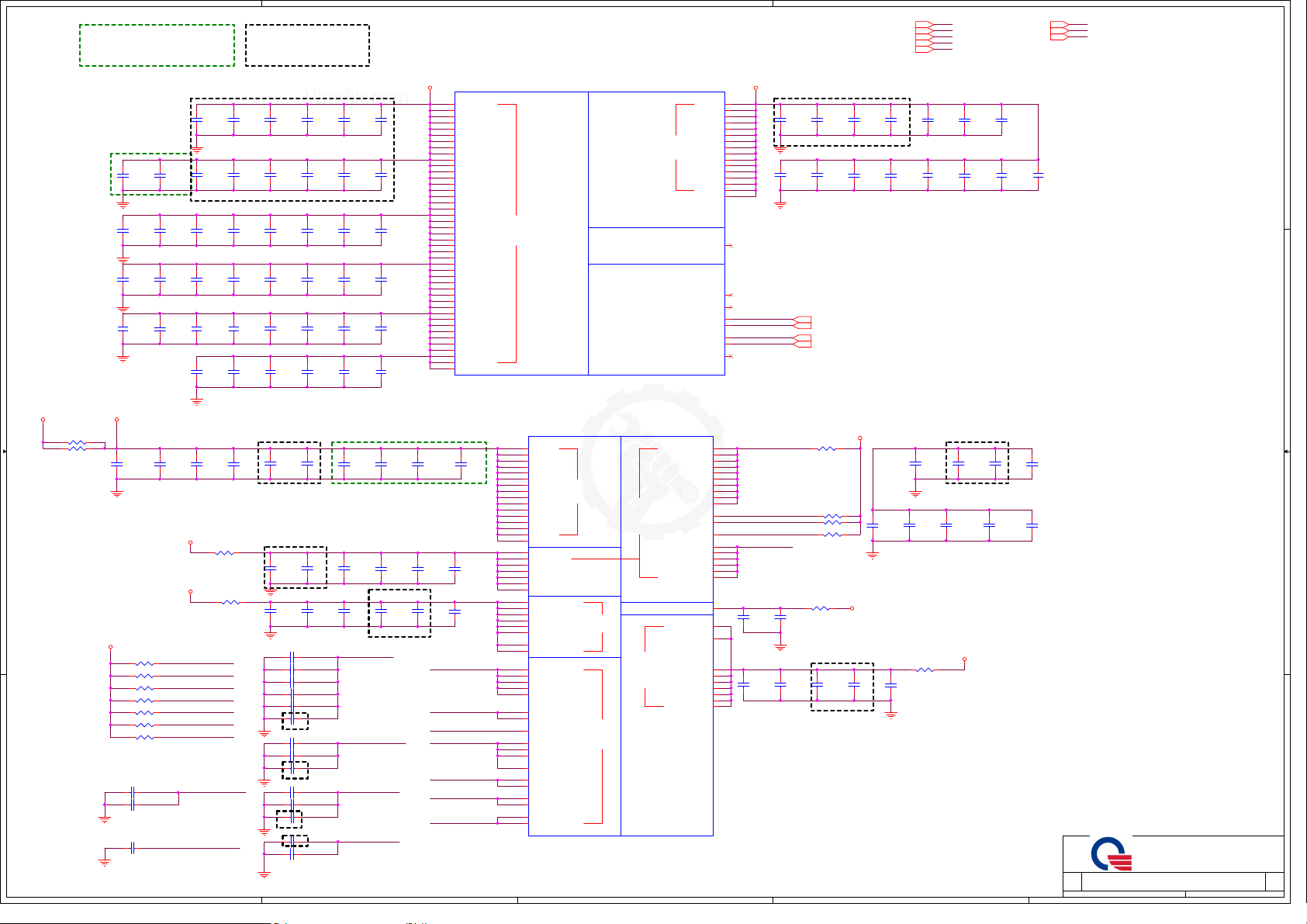

Gemini lake (SATA , ODD, CLK ,USB,PCIE)

U27D

<1000mil

PCIE_CLK_RCOMP

CLK_PCIE_SSDP_R

CLK_PCIE_SSDN_R

PCIE_TXP2_LAN_C

PCIE_TXN2_LAN_C

PCIE_LAN_WAKE#

PCIE_WLAN_WAKE#

PCIE_LAN_WAKE# [16]

L10

PCIE_REF_CLK_RCOMP

R12

PCIE_CLKOUT0P

R10

PCIE_CLKOUT0N

N7

PCIE_CLKOUT1P

N5

PCIE_CLKOUT1N

R7

PCIE_CLKOUT2P

R5

PCIE_CLKOUT2N

N8

PCIE_CLKOUT3P

N10

PCIE_CLKOUT3N

E2

PCIE_P0_TXP

F2

PCIE_P0_TXN

G7

PCIE_P0_RXP

H6

PCIE_P0_RXN

A7

PCIE_P1_TXP

C7

PCIE_P1_TXN

D4

PCIE_P1_RXP

E5

PCIE_P1_RXN

C9

PCIE_P2_TXP

B9

PCIE_P2_TXN

E7

PCIE_P2_RXP

F6

PCIE_P2_RXN

A46

PCIE_CLKREQ0

C45

PCIE_CLKREQ1

B45

PCIE_CLKREQ2

C44

PCIE_CLKREQ3

F47

PCIE_WAKE0

D47

PCIE_WAKE1

F45

PCIE_WAKE2

D50

PCIE_WAKE3

J3

SATA_P0_TXP

J2

SATA_P0_TXN

J7

SATA_P0_RXP

J5

SATA_P0_RXN

PCIe

SATA

PCIE_CLKREQ1

PCIE_CLKREQ_WLAN#

CLK_PCIE_LAN_REQ#

CLK_PCIE_SSD_REQ#

SATA/USB3

USB3

PCIe/USB3

SSIC

USB2

4 OF 13

R441 10K_5%_4

R32 *10K_5%_4

R33 *10K_5%_4

R440 *10K_5%_4

level shift already PU

R71 56_1%_4

LAN

WLAN4~12 inch

PCIE_TXP2_LAN[16]

PCIE_TXN2_LAN[16]

CLK_PCIE_SSD_REQ#[17]

CLK_PCIE_LAN_REQ#[16]

PCIE_CLKREQ_WLAN#[18]

SATA HDD

R116 *S_4

R109 *S_4

CLK_PCIE_LANP[16]

CLK_PCIE_LANN[16]

CLK_PCIE_WLANP[18]

CLK_PCIE_WLANN[18]

PCIE_TX0+_SSD[17]

PCIE_TX0-_SSD[17]

PCIE_RX0+_SSD[17]

PCIE_RX0-_SSD[17]

PCIE_TX1+_SSD[17]

PCIE_TX1-_SSD[17]

PCIE_RX1+_SSD[17]

PCIE_RX1-_SSD[17]

PCIE_RXP2_LAN[16]

PCIE_RXN2_LAN[16]

SATA_TXP0[17]

SATA_TXN0[17]

SATA_RXP0[17]

SATA_RXN0[17]

PCIE_LAN_WAKE#

C327 0.1u/16V_4

C328 0.1u/16V_4

TP2

+1.8V_S5

CLK_PCIE_SSD_REQ#

PCIE_CLKREQ1

CLK_PCIE_LAN_REQ#

PCIE_CLKREQ_WLAN#

R52

*10K_5%_4

CLK_PCIE_SSD_P[17]

CLK_PCIE_SSD_N[17]

D D

PCIE SSD

2.5~10 inch(Gen2)

LAN

2.5~12 inch(Gen1)

C C

B B

4

SATA_P1_USB3_P5_TXP

SATA_P1_USB3_P5_TXN

SATA_P1_USB3_P5_RXP

SATA_P1_USB3_P5_RXN

USB3_P0_TXP

USB3_P0_TXN

USB3_P0_RXP

USB3_P0_RXN

USB3_P1_TXP

USB3_P1_TXN

USB3_P1_RXP

USB3_P1_RXN

PCIE_P3_USB3_P4_TXP

PCIE_P3_USB3_P4_TXN

PCIE_P3_USB3_P4_RXP

PCIE_P3_USB3_P4_RXN

PCIE_P4_USB3_P3_TXP

PCIE_P4_USB3_P3_TXN

PCIE_P4_USB3_P3_RXP

PCIE_P4_USB3_P3_RXN

PCIE_P5_USB3_P2_TXP

PCIE_P5_USB3_P2_TXN

PCIE_P5_USB3_P2_RXP

PCIE_P5_USB3_P2_RXN

PCIE2_USB3_SATA3_RCOMP

PCIE2_USB3_SATA3_RCOMP_P

USB2_DP0

USB2_DN0

USB2_DP1

USB2_DN1

USB2_DP2

USB2_DN2

USB2_DP3

USB2_DN3

USB2_DP4

USB2_DN4

USB2_DP5

USB2_DN5

USB2_DP6

USB2_DN6

USB2_DP7

USB2_DN7

USB2_RCOMP

USB2_DUALROLE

USB2_VBUS_SNS

USB2_OC0

USB2_OC1

+3V_S5

NC1

NC2

NC5

NC4

NC3

H1

H2

H4

G5

B15

C15

F15

D15

C14

A14

J11

H11

PCIE_TXP3_WLAN_C

C10

PCIE_TXN3_WLAN_C

A10

H9

F9

C11

B11

D11

F11

B13

C13

F13

D13

PCIE_RCOMPN

C5

PCIE_RCOMPP

C6

AA10

AA8

W13

W12

U15

U7

U5

N2

N3

L2

L3

R13

R15

M1

M3

R2

R3

P1

P3

U8

U10

U12

USBCOMP

USB_OTG_ID

V1

USB_VBUS_SNS

V3

USB_OC0#

U54

USB_OC1#

U53

R122 113_1%_4

USB_OTG_ID

SATA_TXP1 [17]

SATA_TXN1 [17]

SATA_RXP1 [17]

SATA_RXN1 [17]

USB30_TX0+ [20]

USB30_TX0- [20]

USB30_RX0+ [20]

USB30_RX0- [20]

USB3_1_TXP [21]

USB3_1_TXN [21]

USB3_1_RXP [21]

USB3_1_RXN [21]

C409 0.1u/16V_4

C408 0.1u/16V_4

PCIE_RXP3_WLAN [18]

PCIE_RXN3_WLAN [18]

USB3_3_TXP [17]

USB3_3_TXN [17]

USB3_3_RXP [17]

USB3_3_RXN [17]

USB3_2_TXP [21]

USB3_2_TXN [21]

USB3_2_RXP [21]

USB3_2_RXN [21]

R50 100_1%_4

USBP0+ [20]

USBP0- [20]

USBP1+ [21]

USBP1- [21]

USB2.0_CONN1+ [20]

USB2.0_CONN1- [20]

USB2.0_CONN2+ [20]

USB2.0_CONN2- [20]

USBP4+ [18]

USBP4- [18]

USBP_TOUCH+ [13]

USBP_TOUCH- [13]

USBP7_CCD+ [13]

USBP7_CCD- [13]

USBP7+_ODD [17]

USBP7-_ODD [17]

R468 *10K_5%_4

R81 *10K_5%_4

R490 *0_5%_4

M.2 SATA SSD

USB Type C

ODD

USB Type C

USB3.0

Type C

USB2 .0

USB2 .0

BT

Touch Panel

CCD

ODD

R565 *0_5%_4

R566 *0_5%_4

PCIE_TXP3_WLAN [18]

PCIE_TXN3_WLAN [18]

USB_OC0# [9,21]

USB_OC1# [20]

3

+1.8V_S5

2~8 inchUSB3.0

Touch PAD

I2C standard/fast mode

I2C total lenght is about 4500 mils = 4.5inchs

Cb = 4.5*5pF +7pF = 29.5pF

PU resistor = 2K ohm

WLAN

2.5~12 inch(Gen1)

CNVI_BRI_DT[9,18]

CNVI_BRI_RSP[9,18]

CNVI_RGI_DT[9,18,22]

CNVI_RGI_RSP[9,18]

3~12 inch

+1.8V_S5

+1.8V

USB_VBUS_SNS

SMB_SOC_CLK[9]

CNVI_WGR_CLK_P[18]

CNVI_WGR_CLK_N[18]

CNVI_WGR_DAT0_P[18]

CNVI_WGR_DAT0_N[18]

CNVI_WGR_DAT1_P[18]

CNVI_WGR_DAT1_N[18]

CNVI_WT_CLK_P[18]

CNVI_WT_CLK_N[18]

CNVI_WT_DAT0_P[18]

CNVI_WT_DAT0_N[18]

CNVI_WT_DAT1_P[18]

CNVI_WT_DAT1_N[18]

XTAL_CLKREQ[9,18]

CNVI_BRI_DT

CNVI_BRI_RSP

CNVI_RGI_DT

CNVI_RGI_RSP

CNVI_RF_RESET#[9,18]

33 ohm resistor must be placed at a distance <2000mils/50.8 mm from SoC

Minimum Length for BRI/RGIsignals is 3000 mils /76.2 mm

+1.8V_S5

R501

*10K_5%_4

R502

*S_4

R792K_1%_4

R802K_1%_4

I2C4_SCL[19]

I2C4_SDA[19]

R54 33_5%_4

R60 33_5%_4

R61 33_5%_4

R37 33_5%_4

R58 150_1%_4

CLKIN_XTAL_LCP_C[18]

I2C4_SDA

I2C4_SCL

SMB1ALERT#

SMB_SOC_CLK

SMB_SOC_DAT

CLKIN_XTAL_LCP

CNVI_BRI_DT_C

CNVI_BRI_RSP_C

CNVI_RGI_DT_C

CNVI_RGI_RSP_C

CNVI_RF_RESET#

CNVI_WT_RCOMP

AA39

AA41

I2C4_SCL

I2C4_SDA

1 2

L13 BLM15AG121SN1D

U49

U51

U46

U48

R44

R43

R49

R51

C50

A50

C48

C47

B47

C46

A26

B27

C27

H29

H31

M31

P31

D29

F29

F35

D35

J35

H35

L31

J31

J29

F19

H17

J17

D19

D17

F17

F33

SIO_I2C0_SCL

SIO_I2C0_SDA

SIO_I2C1_SCL

SIO_I2C1_SDA

SIO_I2C2_SCL

SIO_I2C2_SDA

SIO_I2C3_SCL

SIO_I2C3_SDA

SIO_I2C4_SCL

SIO_I2C4_SDA

SIO_I2C5_SCL

SIO_I2C5_SDA

SIO_I2C6_SCL

SIO_I2C6_SDA

SIO_I2C7_SCL

SIO_I2C7_SDA

SMB_ALERT

SMB_CLK

SMB_DATA

CNV_WGR_CLK_P

CNV_WGR_CLK

CNV_WGR_D0_P

CNV_WGR_D0

CNV_WGR_D1_P

CNV_WGR_D1

CNV_WT_CLK_P

CNV_WT_CLK

CNV_WT_D0_P

CNV_WT_D0

CNV_WT_D1_P

CNV_WT_D1

CLKIN_XTAL_LCP

XTAL_CLKREQ

CNV_BRI_DT

CNV_BRI_RSP

CNV_RGI_DT

CNV_RGI_RSP

CNV_RF_RESET

CNV_WT_RCOMP

U27I

SMBUS set 3.3V

Close to SOC for ESD

SoC

+1.8V_S5

R6 *1K_1%_4

R24 *1K_1%_4

R21 *1K_1%_4

CLKIN_XTAL_LCP

C540

4.7p/50V_4

SMBus

SMB_SOC_DAT

SMB_SOC_CLK

2

LPSS_I2C

LPSS SMBus

CNVI

R95

10K_5%_4

+3V_S5 +3V

R18

R8

1K_1%_4

1K_1%_4

SMB_SOC_DAT

SMB_SOC_CLK

SMB1ALERT#

LPSS_SPI

6 OF 13

CNVI_BRI_RSP

R113 20K_1%_4

CNVI_RGI_DT

R119 20K_1%_4

CNVI_RGI_RSP

R104 20K_1%_4

INTEL CNVi check list suggestion

5

Q4A

3 4

2

Q4B

6 1

2N7002KDW

+3V_S5

R15 *1K_1%_4

SMB1ALERT#

LPSS_UART

R27

2.2K_5%_4

1

+1.8V_S5[4,5,6,7,9,12,16,19,23,27,29]

+1.8V[4,13,15,29,30]

+3V_S5[6,7,12,15,16,17,18,19,21,22,24,26,29]

+1.8V_S5

R7

2.2K_5%_4

+3V[4,5,6,10,13,14,15,16,17,18,19,22,24,25,26,27,28,29,30]

CLK_SDATA [10,19]

CLK_SCLK [10,19]

SIO_SPI_0_CLK

SIO_SPI_0_TXD

SIO_SPI_0_RXD

SIO_SPI_0_FS0

SIO_SPI_0_FS1

SIO_SPI_2_CLK

SIO_SPI_2_TXD

SIO_SPI_2_RXD

SIO_SPI_2_FS0

SIO_SPI_2_FS1

SIO_SPI_2_FS2

SIO_UART0_TXD

SIO_UART0_RXD

SIO_UART0_RTS

SIO_UART0_CTS

SIO_UART2_TXD

SIO_UART2_RXD

SIO_UART2_RTS

SIO_UART2_CTS

DDR4

M39

J37

L39

L37

J39

M37

M33

P35

P33

P37

L35

N54

P53

N53

M55

GPIO_65

L54

GPIO_64

M53

K53

L53

GPIO_65

GPIO_64

GPIO_79 [9]

GPIO_83 [9]

GPIO_80 [9]

GPIO_81 [9]

GPIO_84 [9]

GPIO_89 [9]

GPIO_85 [9]

GPIO_86 [9]

GPIO_87 [9]

GPIO_61 [9]

TP41

GPIO_62 [9]

TP40

GPIO_65 [9]

GPIO_66 [9]

TP37

TP38

TP39

03

S0 GML S5

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

Z8G

PROJECT :

Z8G

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

GLK(PCIE/USB/SATA/CNVI)

GLK(PCIE/USB/SATA/CNVI)

GLK(PCIE/USB/SATA/CNVI)

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

5

4

3

2

Tuesday, December 26, 2017

1

Z8G

3 35

3 35

3 35

1A

1A

1A

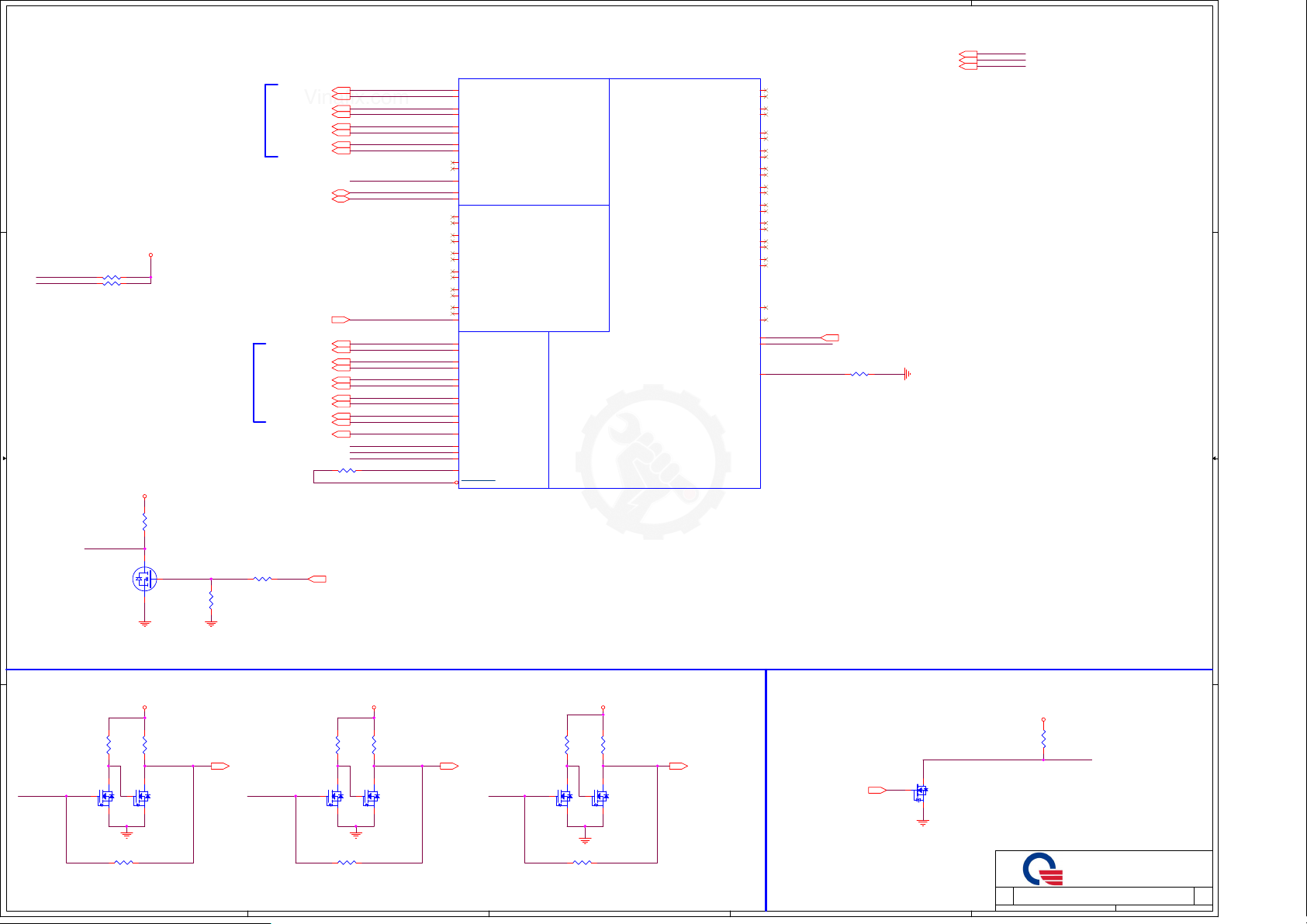

Vinafix.com

5

4

3

2

1

Gemini lake (DISPLAY,eDP)

U27C

AC12

AC10

AE12

AE13

AC15

AC17

AE10

AH1

AH3

AE2

AE3

AJ2

AJ3

AG2

AG3

C39

B43

C43

AA2

AA3

Y3

Y1

AD1

AD3

AC2

AC3

AC7

AC5

C42

A42

C38

AE8

AE5

AE7

W17

W15

B39

B41

C40

C41

AA5

AA7

DDI0_TXP_0

DDI0_TXN_0

DDI0_TXP_1

DDI0_TXN_1

DDI0_TXP_2

DDI0_TXN_2

DDI0_TXP_3

DDI0_TXN_3

DDI0_AUXP

DDI0_AUXN

DDI0_HPD

DDI0_DDC_SCL

DDI0_DDC_SDA

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

DDI1_AUXP

DDI1_AUXN

DDI1_DDC_SCL

DDI1_DDC_SDA

DDI1_HPD

EDP_TXP_0

EDP_TXN_0

EDP_TXP_1

EDP_TXN_1

EDP_TXP_2

EDP_TXN_2

EDP_TXP_3

EDP_TXN_3

EDP_AUXP

EDP_AUXN

EDP_HPD

PNL0_BKLCTL

PNL0_BKLTEN

PNL0_VDDEN

EDP_RCOMP_P

EDP_RCOMP

DDI0/DDI_B

MDSI

DDI1/DDI_C

eDP/DDI_A

3 OF 13

INT_HDMITX2P[15]

INT_HDMITX2N[15]

INT_HDMITX1P[15]

D D

Max 7.5 inch

HDMI

HDMI_HPD

+3V

TypeC_HPD#

INT_EDP_HPD#

C C

HDMI HPD

B B

R184 10K_5%_4

R3 10K_5%_4

INT_HDMI_HPD#

RUC002N05GZT116

eDP Panel

<10000 mil

+1.8V

change to 3.3V

R35

10K_5%_4

3

Q3

HDMI_HPD_R

2

1

R11 *S_4

R12

100K_1%_4

INT_HDMITX1N[15]

INT_HDMITX0P[15]

INT_HDMITX0N[15]

INT_HDMICLK+[15]

INT_HDMICLK-[15]

INT_HDMI_HPD#

HDMI_DDCCLK_SW[15]

HDMI_DDCDATA_SW[15]

TypeC_HPD#[21]

EDP_TXP0[13]

EDP_TXN0[13]

EDP_TXP1[13]

EDP_TXN1[13]

EDP_TXP2[13]

EDP_TXN2[13]

EDP_TXP3[13]

EDP_TXN3[13]

EDP_AUXP[13]

EDP_AUXN[13]

INT_EDP_HPD#[13]

R497 100_1%_4

HDMI_HPD_C [15]

INT_EDP_HPD#

PCH_BKLTCTL

PCH_BKLTEN

PCH_VDDEN

EDP_RCOMP_P

EDP_RCOMP_N

MDSI_A_CLKP

MDSI_A_CLKN

MDSI_C_CLKP

MDSI_C_CLKN

MDSI_A_DP_0

MDSI_A_DN_0

MDSI_A_DP_1

MDSI_A_DN_1

MDSI_A_DP_2

MDSI_A_DN_2

MDSI_A_DP_3

MDSI_A_DN_3

MDSI_C_DP_0

MDSI_C_DN_0

MDSI_C_DP_1

MDSI_C_DN_1

MDSI_C_DP_2

MDSI_C_DN_2

MDSI_C_DP_3

MDSI_C_DN_3

MIPI_I2C_SCL

MIPI_I2C_SDA

MDSI_C_TE

MDSI_A_TE

MDSI_RCOMP

AL2

AM3

AG13

AG12

AN5

AN7

AJ15

AJ17

AJ7

AJ5

AJ10

AJ12

AG15

AG17

AG8

AG10

AG7

AG5

AE15

AE17

R53

R54

T53

SOC_OVRIDE

T55

GPIO_42 HW Strap

MDSI_RCOMP

AL5

GPIO_43 [9]

R162 150_1%_4

+1.8V_S5[3,5,6,7,9,12,16,19,23,27,29]

+1.8V[3,13,15,29,30]

+3V[3,5,6,10,13,14,15,16,17,18,19,22,24,25,26,27,28,29,30]

04

+3V +3V +3V

R129

*10K_5%_4

PCH_VDDEN PCH_BKLTEN PCH_BKLTCTL

A A

5

Q10A

R90 *S_4

R115

*10K_5%_4

34

61

2

*SSM6N43FU

Q10B

5

EDP_VDD_EN [13] PCH_BLON [13] PCH_BRIGHT [13]

R36

*10K_5%_4

5

Q6A

R17 *S_4

R22

*10K_5%_4

34

61

2

*SSM6N43FU

Q6B

4

R105

*10K_5%_4

5

Q9A

R74 *S_4

R89

*10K_5%_4

34

61

2

*SSM6N43FU

Q9B

3

Override

Flash Descriptor Override (SOC_OVRIDE)

0 = Normal Override(Normal operation)

1 = Override

3

2

ME_WR#[22]

2

1

Q30

2N7002K

+1.8V_S5

R465

2.2K_5%_4

SOC_OVRIDE

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

PROJECT :

GLK (HDMI/eDP)

GLK (HDMI/eDP)

GLK (HDMI/eDP)

Z8G

Z8G

Z8G

4 35

4 35

1

4 35

1A

1A

1A

Vinafix.com

5

?

?

U27J

C26

AVS_I2S0_MCLK

B25

AVS_I2S0_BCLK

C25

AVS_I2S0_WS_SYNC

HDA_BCLK_R

HDA_SYNC_R

HDA_SDO_R

HDA_RST#_R

EMMC_RCOMP

PCLK_TPM

C399

*18P/50V_4

CLK_PCI_LPC

C400

*18P/50V_4

C24

AVS_I2S0_SDI

B23

AVS_I2S0_SDO

M23

AVS_I2S1_MCLK

L21

AVS_I2S1_BCLK

J21

AVS_I2S1_WS_SYNC

M21

AVS_I2S1_SDI

P23

AVS_I2S1_SDO

A22

AVS_HDA_BCLK

C23

AVS_HDA_WS_SYNC

B21

AVS_HDA_SDI

C22

AVS_HDA_SDO

C21

AVS_HDA_RST

B19

AVS_DMIC_CLK_A1

C20

AVS_DMIC_CLK_B1

C19

AVS_DMIC_DATA_1

C18

AVS_DMIC_CLK_AB2

A18

AVS_DMIC_DATA_2

J13

EMMC_CLK

L15

EMMC_RCLK

M19

EMMC_D0

H19

EMMC_D1

J19

EMMC_D2

P17

EMMC_D3

P19

EMMC_D4

J15

EMMC_D5

L17

EMMC_D6

M17

EMMC_D7

M13

EMMC_CMD

U44

EMMC_RST

G51

EMMC_PWR_EN

L13

EMMC_RCOMP

GLK_SOC_RVP1

?

AUDIO-AVS

eMMC

EMMC_CLK[13]

EMMC_RCLK[13]

EMMC_DATA_0[13]

EMMC_DATA_1[13]

EMMC_DATA_2[13]

EMMC_DATA_3[13]

EMMC_DATA_4[13]

EMMC_DATA_5[13]

EMMC_DATA_6[13]

EMMC_DATA_7[13]

EMMC_CMD[13]

EMMC_RST[13]

C402

*33p/50V_4

GPIO_159[9]

GPIO_163[9]

GPIO_164[9]

R449 33_5%_4

R435 33_5%_4

R422 33_5%_4

R421 33_5%_4

GPIO_172[9]

GPIO_174[9]

GPIO_175[9]

R87 200_1%_4

D D

HDA

AZ_CODEC_BITCLK[14]

AZ_CODEC_SYNC[14]

AZ_CODEC_SDIN0[9,14]

AZ_CODEC_SDOUT[14]

AZ_CODEC_RST#[14]

C C

AZ_CODEC_BITCLK

4

Gemini lake (EMMC/LPC/I2C/GPIO/HDA)

L29

SDCARD

LPC/eSPI

LPC set 3.3V

FAST_SPI

7 OF 13

XDP_TCK

XDP_TRST#

XDP_PREQ#

XDP_PRDY#

XDP_TMS

XDP_TDO

XDP_TDI

R504 51_5%_4

R512 51_5%_4

R508 51_5%_4

R509 169_1%_4

R506 51_5%_4

R505 169_1%_4

R510 51_5%_4

SPI is 1.8V

+1.8V_S5

SDCARD_CLK

SDCARD_D0

SDCARD_D1

SDCARD_D2

SDCARD_D3

SDCARD_CMD

SDCARD_CD

SDCARD_LVL_W P

SDCARD_PWR_D WN

SDCARD_RCOMP

LPC_CLKOUT0

LPC_CLKOUT1

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_CLKRUN

LPC_FRAME

LPC_SERIRQ

FST_SPI_CLK

FST_SPI_MOSI_IO0

FST_SPI_MISO_IO1

FST_SPI_IO2

FST_SPI_IO3

FST_SPI_CS0

FST_SPI_CS1

M29

P29

M27

P27

L27

L25

P25

L23

J25

LPC_CLKOUT0

C37

LPC_CLKOUT1

A38

LPC_LAD0_R

A34

LPC_LAD1_R

C34

LPC_LAD2_R

B35

LPC_LAD3_R

C35

LPC_CLKRUN#_R

C33

LPC_LFRAME#_R

B33

SOC_SERIRQ_R

B37

B29

B31

C30

A30

C29

C31

C32

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

PCH_SPI_CS1#

3

R427 22_5%_4

R448 22_5%_4

R447 DBG@22_5%_4

R438 22_5%_4

R423 22_5%_4

R426 22_5%_4

R446 22_5%_4

R439 22_5%_4

R425 22_5%_4

R445 22_5%_4

TP4

TP43

TP42

TP45

TP46

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_PRDY#

XDP_PREQ#

CLK_PCI_EC [22]

PCLK_TPM [17]

CLK_PCI_LPC [18]

LPC_LAD0 [17,18,22]

LPC_LAD1 [17,18,22]

LPC_LAD2 [17,18,22]

LPC_LAD3 [17,18,22]

CLKRUN# [17,22]

LPC_LFRAME# [17,18,22]

SOC_SERIRQ [12]

2

+1.8V_S5[3,4,6,7,9,12,16,19,23,27,29]

+1.8V[3,4,13,15,29,30]

U27H

AH53

JTAGX

AM53

JTAG_TCK

AJ54

JTAG_TDI

AL53

JTAG_TDO

AL54

JTAG_TMS

AK53

JTAG_TRST

AH55

JTAG_PRDY

AJ53

JTAG_PREQ

JTAG

ITP

GPIO

5 OF 13

+3V_S5[3,6,7,12,15,16,17,18,19,21,22,24,26,2 9]

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

GPIO_34

GPIO_35

GPIO_36

GPIO_37

GPIO_38

GPIO_39

GPIO_40

GPIO_41

GPIO_105

GPIO_134

GPIO_135

GPIO_136

GPIO_137

GPIO_138

GPIO_139

GPIO_140

GPIO_141

GPIO_142

GPIO_143

GPIO_144

GPIO_145

GPIO_146

GPIO_210

GPIO_212

GPIO_213

GPIO_214

AG53

AG54

AE54

AE53

AD55

AD53

AC54

AC53

AB53

AA49

AC48

AC46

AE51

AE49

AC51

AC49

AA51

AA46

AE41

AE39

AE46

AE44

AC41

AC39

AC44

AC43

AA44

AA54

AA53

Y55

Y53

W54

W53

V53

L46

H45

H47

L43

M43

H37

H43

J43

D43

F43

H41

F39

L41

F41

H27

U43

U41

U39

RF_KILL#_R

IERR

SATA_GP0

PCH_PCIERST#

GPIO_140

GPIO_141

GPIO_142

AC_PRESENT

1

05

Board_ID0

Board_ID1

Board_ID2

Board_ID3

Board_ID4

Board_ID5

Board_ID6

Board_ID7

Board_ID8

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID3

RAM_ID4

RAM_ID5

eMMC_ID0

eMMC_ID1

eMMC_ID2

R477 *S_4

R473 *S_4

GPIO_105

PCH_TPD_INT# [19]

ACCEL_INTA [19]

CNVI_MFUART2_RXD [18]

CNVI_MFUART2_TXD [18]

CNVI_GNSS_PA_BLANKING [18]

GPIO_27 [9]

GPIO_28 [9]

SPKR [14]

SIO_EXT_SCI# [22]

SOC_PCI_SERR#

TP6

PCH_PCIERST# [6]

set to 3.3V

TP53

HW strap ID

Board_ID0

B B

Board_ID1

Board_ID2

Board_ID3

Board_ID4

Board_ID5

Board_ID6

Board_ID7

Board_ID8

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID5

0

A A

0

0

0

eMMC_ID0eMMC_ID1

0

0

0 1

1 1

Strap pin Description

0 = w/o type C

1 = w/ type C

0 = with EMMC

1 = without EMMC <HDD only>

0 = M.2 SATA SSD

1 = M.2 PCIE SSD

0 = none G sensor

1 = G sensor

0 = none TPM

1 = TPM

0 = With SATA Port 0 Connector

1 = Without SATA Port 0 Connector

0 = With SATA Port 1 Connector

1 = Without SATA Port 1 Connector

0 = EJ series

1 = Cloud book

0 = UMA

1 = GPU

0 = With on board RAM

1 = Without on board RAM(SODIMM only)

0 = On board RAM 2GB

1 = On board RAM 4GB

(Reserved)

Vender

RAM_ID3RAM_ID4

0

0

Miron-2GB

0

1

Hynix-2GB

01

Samsung-2GB

1 1

eMMC_ID0

0

1

0

1

Sandisk 32G/64G/128GB

1

Vender

Samsung 32/64GB

Hynix 32/64GB

Kingston 32/64GB

Toshiba 128GB

0

0

10

BOARD ID SETTING

Board_ID0

R496 *10K_5%_4

R498 10K_5%_4

R487 10K_5%_4

R493 *10K_5%_4

R485 *10K_5%_4

R482 10K_5%_4

R483 10K_5%_4

R488 10K_5%_4

R475 10K_5%_4

R138 10K_5%_4

R102 *10K_5%_4

R88 10K_5%_4

R137 10K_5%_4

R146 *10K_5%_4

R111 10K_5%_4

R118 10K_5%_4

R135 *10K_5%_4

R124 *10K_5%_4

5

R499 10K_5%_4

Board_ID1

R507 *10K_5%_4

Board_ID2

R484 *10K_5%_4

Board_ID3

R492 10K_5%_4

Board_ID4

R486 10K_5%_4 R107 *10K_5%_4

Board_ID5

R476 *10K_5%_4

Board_ID6

R481 *10K_5%_4

Board_ID7

R489 *10K_5%_4

Board_ID8

R474 *10K_5%_4

RAM_ID0

R131 *10K_5%_4

RAM_ID1

R96 10K_5%_4

RAM_ID2

R86 *10K_5%_4

RAM_ID3

R147 *10K_5%_4

RAM_ID4

R121 10K_5%_4

RAM_ID5

R112 *10K_5%_4

eMMC_ID0

R117 *10K_5%_4

eMMC_ID1

R132 10K_5%_4

eMMC_ID2

R83 10K_5%_4

+1.8V_S5

Board ID

RAM ID

eMMC ID

4

R414

R413 33_5%_4

R408 33_5%_4

R412 33_5%_4

R416 33_5%_4

3.3K_5%_4

SPI_CLK_A

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

Series resistance 33R is recommended

for signals as per PDG Table 27-2

SP@ socket P/N: DFHS08FS023 only for A-TEST

SPI ROM

1.8V

+1.8V_S5

R410

*3.3K_5%_4

U24

1

8

CE#

VCC

6

SCLK

5

SI

2

7

SO

IO3

3

4

IO2

VSS

GD25LB64CSIGR

Vender Size Quanta P/N

8M

AKE5EZN0N01WND

8M

AKE5EG-0Q01 GD25LB64CSIGRGGD

8M

AKE5EZN0Z01 MX25U6473FM2I-10GMAX

+1.8V_S5

R409

3.3K_5%_4

R411 33_5%_4

Vender P/N

W25Q64FWSSIQ

3

C392

0.1u/16V_4

PCH_SPI_IO3

GPIO_142

GPIO_140

Q31A

R470

*10K_5%_4

34

5

R464 *S_4

*10K_5%_4

BOARD ID SETTING

R157

34

5

Q13A

R149 *0_5%_4

+3V

61

2

Q31B

*2N7002KDW

2

R467

10K_5%_4

+3V

61

R156

*10K_5%_4

Q13B

*SSM6N43FU

2

NGFF_SATA_DET# [17]

SATA_DEVSLP0 [17]

GPIO_141

R457

*10K_5%_4

5

Q29A

R460 *S_4

SOC_PCI_SERR#

R472 *10K_5%_4

PCH_TPD_INT#

R567 10K_5%_4

SIO_EXT_SCI#

R478 10K_5%_4

ACCEL_INTA

R106 *GS@10K_5%_4

RF_KILL#_R

GPIO_105

R82 *10K_5%_4

+3V

R456

10K_5%_4

61

34

2

Q29B

*SSM6N43FU

SATA_DEVSLP1 [17]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Do cument Number Rev

Size Do cument Number Rev

Size Do cument Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

GLK (GPIO/LPC/I2C/HDA)

GLK (GPIO/LPC/I2C/HDA)

GLK (GPIO/LPC/I2C/HDA)

Tuesday, December 26, 2017

Tuesday, December 26, 2017

Tuesday, December 26, 2017

1

set to PU

Z8G

Z8G

Z8G

+1.8V_S5

+1.8V_S5

5 35

5 35

5 35

1A

1A

1A

Vinafix.com

5

PMU set to 3.3V

+3V_S5 +1.8V_S5

R49

R69

0_5%_4

*0_5%_4

D D

R68 *10K_5%_4

R70 100K_1%_4

R424 10K_5%_4

R436 *1K_1%_4

R442 *10K_5%_4

R19 *20K_1%_4

R14 20K_1%_4

R57 *10K_5%_4

R10 *1K_1%_4

+1.8V_S5

check list use 20k

R455 1K_1%_4

C C

R48 *1K_1%_4

R59 *100K_1%_4

R443 100K_1%_4

C31 *0.1u/16V_4

C39 *0.1u/16V_4

C38 *0.1u/16V_4

C405 0.1u/16V_4

C28 *0.1u/16V_4

PCH_SUSPWRDNACK

PCH_BATLOW#

PMU_RSTBTN#

PCH_PLTRST#

PMU_SLP_S0#

SOC_RSMRST#

CORE_PWROK

PCH_SUS_STAT#

DNBSWON#

H_PROCHOT#

THRMTRIP#_R

CORE_PWROK

PCH_PLTRST#

CORE_PWROK

PCH_BATLOW#

SOC_RSMRST#

PMU_RSTBTN#

DNBSWON#

DNBSWON#[22]

SUSB#[22]

SUSC#[22]

PCH_SUSPWRDNACK[22]

TP36

TP5

H_CPU_SVIDCLK[27,28]

H_CPU_SVIDDAT[27,28]

VR_SVID_ALERT#_VCORE[27,28]

TP7

TP3

4

TP10

TP9

PCH_PLTRST#

DNBSWON#

PMU_SLP_S0#

SUSB#

SUSC#

PCH_SUSPWRDNACK

PCH_BATLOW#

PMU_RSTBTN#

PMU_SUSCLK

PCH_SUS_STAT#

R450 *S_4

R451 *S_4

R452 220_5%_4

H_CPU_SVIDDAT

VR_SVID_ALERT#_VCORE

H_CPU_SVIDCLK

SVID_CLK#_R

SVID_DAT#_R

SVID_ALERT#_R

3

Gemini lake (PMU/PMIC/RTC)

U27E

R46

PMC_I2C_SCL

R48

PMC_I2C_SDA

L48

PMC_SPI_CLK

N48

PMC_SPI_FS0

N44

PMC_SPI_FS1

L49

PMC_SPI_FS2

L51

PMC_SPI_RXD

N49

PMC_SPI_TXD

D54

PMU_PLTRST

E54

PMU_PWRBTN

C52

PMU_SLP_S0

D51

PMU_SLP_S3

J49

PMU_SLP_S4

F54

SUSPWRDNACK

J48

PMU_BATLOW

C51

PMU_RSTBTN

G49

PMU_SUSCLK

E52

SUS_STAT

F55

SVID0_CLK

G53

SVID0_DATA

G54

SVID0_ALERT_B

D1

DEBUG_PORT_A0

D2

DEBUG_PORT_A1

A54

NC2

C54

NC11

+1.05V

R428

240_1%_4

PMU set 3.3V

R429

R430

68_5%_4

*160_1%_4

PMC

PMU

SVID

Misc

C401

1000p/50V_4

iCLK

RTC

Thermal

Spare

8 OF 13

THRMTRIP#_R

RTC is 3.3V

2

OSC_CLK_OUT_0

OSC_CLK_OUT_1

OSCIN

OSCOUT

RTC_X1

RTC_X2

VCC_RTC_EXTPAD

INTRUDER

SOC_PWROK

RSM_RST

RTC_TEST

RTC_RST

THERMTRIP

1.8V

PROCHOT

SKTOCC

R67

*10K_5%_4

61

Q8B

*PJT138K

GND

NC15

NC16

NC14

NC10

NC17

NC3

NC4

NC1

NC5

NC6

NC7

NC8

NC9

5

B17

C17

XTAL192_IN

U2

XTAL192_OUT

T1

RTC_X1

D23

RTC_X2

F23

BVCCRTC_EXTPAD

J23

H25

INTRUDER#

CORE_PWROK

D25

SOC_RSMRST#

F27

RTC_TEST#

F25

RTC_RST#

D27

THRMTRIP#_R

J53

H_PROCHOT#

J54

AG43

H53

AG44

H55

A4

BH1

A53

F37

BL2

BL3

BL53

C2

C3

R41

+3VPCU

R31

*10K_5%_4

34

Q8A

*PJT138K

THERMTRIP#

C49 0.1u/16V_4

R25 330K_5%_4

R23 *S_4

R47 *S_4

RTC_RST#

2

+1.8V_S5[3,4,5,7,9,12,16,19,23,27,29]

+1.05V[7,25,27,28]

+3V_S5[3,7,12,15,16,17,18,19,21,22,24,26,29]

+3VPCU[13,14,16,20,22,23,24,29]

+3V_RTC[7,22]

+3V_RTC

EC_PWROK [22]

THERMTRIP# [22]

H_PROCHOT# [22,23,27,28]

colsed to CPU pin within 100 mils

C543

1000p/50V_4

R582

10_5%_4

EC reset RTC

CLR_CMOS[22]

SOC_RSMRST# [12]

colsed to CPU pin within 100 mils

C76

1000p/50V_4

R154

10_5%_4

CORE_PWROK

34

5

Q5A

1

06

colsed to CPU pin within 100 mils

C30

1000p/50V_4

R9

10_5%_4

RTC_TEST#

RTC_RST#

61

2

Q5B

2N7002KDW

B B

RTC Circuitry (RTC)

CN7

+3V

EC_PLTRST#[22]

PCH_PCIERST#[5]

PCH_PLTRST#

A A

R579 *0_5%_4

R580 *0_5%_4

R581 *0_5%_4

5

1

2

CMOS

U33

3 5

*MC74VHC1G08DFT2G

R578 0_5%_4

C542

*0.1u/16V_4

4

PLTRST#

PLTRST# [13,16,17,18,22]

CB@cable RTC

4

34

12

+-

3 4

ML1220 Coin type

AHL03001031 [VDE] 17mAH

AHL03001057 [DBV] 17mAH

1

2

CN13

EJ@53014-00201-V09

R532 1K_1%_4

Trace width = 20 mils

+3VPCU

+3V_RTC_1

1 3

Q34 EJ@PMST3904

20MIL

2

+3V_RTC

D13

2

1

R543 EJ@4.7K_5%_4

BAT54CW

R534

3

20K_1%_4

R533

20K_1%_4

VCCRTC_4VCCRTC_3VCCRTC_2

3

+3V_RTC

Trace width = 20 mils

C485

1u/6.3V_4

C486

1u/6.3V_4

R539 EJ@4.7K_5%_4

EJ@68.1K_1%_4

EJ@150K_1%_4

RTC_RST#

12

J1

*JUMP

RTC_TEST#

R541

R540

+5V_S5

19.2MHZ/20ppm

RTC Clock 32.768KHz (CPU)

Trace length < 1000 mils

2

C411 15p/50V_4

Y4

C416 15p/50V_4

C403 18p/50V_4

C404 18p/50V_4

XTAL192_OUT

4

3

R480

200K_1%_4

1

2

XTAL192_IN

CH01006JB08 -> 10p

CH01506JB06 -> 15p

CH-6806TB01 -> 6.8p

12

Y3

32.768KHZ/20ppm

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

RTC_X1

R444

10M_5%_4

RTC_X2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

GLK (PMU/PMIC/SMB/RTC)

GLK (PMU/PMIC/SMB/RTC)

GLK (PMU/PMIC/SMB/RTC)

Tuesday, December 26, 2017

Tuesday, December 26, 2017

Tuesday, December 26, 2017

Z8G

Z8G

Z8G

6 35

6 35

1

6 35

1A

1A

1A

Vinafix.com

5

EDGE DECAPS

FOR EXPOSED POWER PLANES

BACK side cap

4

Gemini (POWER)

3

2

+3V_S5[3,6,12,15,16,17,18,19,21,22,24,26,29]

+1.24V_S5[29]

+1.8V_S5[3,4,5,6,9,12,16,19,23,27,29]

+3V_RTC[6,22]

+1.2VSUS_Q[2]

+VNN[28]

+VCC_VCCGI[27]

+1.05V[6,25,27,28]

1

07

VNN1

VNN2

VNN3

VNN4

VNN5

VNN6

VNN7

VNN8

VNN9

VNN10

VNN11

VNN12

VNN13

VNN14

VNN15

VNN16

NC1

NC2

NC3

NC4

AF35

AG27

AG28

AG36

AG46

AG48

AJ27

AJ28

AJ46

AJ48

AL27

AL28

AL48

AL49

AM27

AM28

AJ49

AW44

BH55

AG41

AG39

AJ41

AJ43

BL54

AC33

AC35

AE33

AE35

AE36

AE38

AF27

AF28

AF36

AF38

+VCCRAM_1P05_FHV0

AG51

+VCCRAM_1P05_FHV1

AG49

+VCCRAM_1P05_FUSE

AJ51

AA36

AA38

AC36

AC38

Y36

Y38

P15

AJ21

U17

AG21

T18

T20

V18

V20

Y18

Y20

+VNN+VCC_VCCGI

+VCCRAM_1P05

VRTC_3P3

C45

*1u/6.3V_4

C52

*1u/6.3V_4

C106

1u/6.3V_4

C125

*1u/6.3V_4

R171 *S_6

R103 *S_6

C47

1u/6.3V_4

C66

*1u/6.3V_4

R155 *S_6

R167 *S_6

R169 *S_6

C119

C92

1u/6.3V_4

1u/6.3V_4

C89

C124

*22u/6.3V_6

*1u/6.3V_4

VCCGI_SENSE [27]

VCCGISS_SENSE [27]

VNN_SENSE [28]

VNNSS_SENSE [28]

+1.05V

+3V_RTC

C82

C64

1u/6.3V_4

1u/6.3V_4

*47u/10V_8

C110

22u/6.3V_6

C126

1u/6.3V_4

C129

C143

*1u/6.3V_4

R123 *S_6

C50

22u/6.3V_6

2

22u/6.3V_6

C23

*47u/10V_8

+VCCRAM_1P05+VCCRAM_1P05

C78

*1u/6.3V_4

C111

1u/6.3V_4

C139

*1u/6.3V_4

+3V_S5

C136

22u/6.3V_6

C394

*47u/10V_8

C73

C85

1u/6.3V_4

C77

1u/6.3V_4

C105

22u/6.3V_6

C114

*47u/10V_8

C393

*47u/10V_8

C434

22u/6.3V_6

C95

*22u/6.3V_6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

PROJECT :

GLK (POWER)

GLK (POWER)

GLK (POWER)

Z8G

Z8G

Z8G

1

7 35

7 35

7 35

1A

1A

1A

U27F

AA28

VCC_VCG1

AA29

VCC_VCG2

AA31

D D

C395

0.1u/16V_4

C390

22u/6.3V_6

22u/6.3V_6

C17

*22u/6.3V_6

C373

C C

+1.2VSUS

R229 *S_8

R228 *S_8

B B

+1.24V_S5

A A

*47u/10V_8

+1.2VSUS_Q

+1.2VSUS_Q

C155

22u/6.3V_6

R139 *S_6

R148 *S_6

R170 *S_6

R152 *S_6

R151 *S_6

R130 *S_6

R158 *S_6

C86 *47u/10V_8

C83 1u/6.3V_4

C109 22u/6.3V_6

5

22u/6.3V_6

1u/6.3V_4

C61

1u/6.3V_4

0.1u/16V_4

C10

22u/6.3V_6

C20

*22u/6.3V_6

*22u/6.3V_6

C7

C14

*47u/10V_8

*47u/10V_8

C9

*47u/10V_8

C153

22u/6.3V_6

+1.05V

R173 *S_8

+1.8V_S5

+VDD2_1P24_MPHY

+VDD2_1P24_AUD_ISH

+VDD2_1P24_DSI_CSI

+VDD2_1P24_GLML

+VDD2_1P24_PLL

+VDD2_1P24_VNNAON

+VDD2_1P24_USB2

+VDD2_1P24_AUD_ISH

+VDD2_1P24_DSI_CSI

C70

C388

C72

C16

C148

R73 *S_6

C53

1u/6.3V_4

C91

1u/6.3V_4

C18

22u/6.3V_6

C22

*22u/6.3V_6

C372

*47u/10V_8

C11

*47u/10V_8

C152

22u/6.3V_6

C65

1u/6.3V_4

1u/6.3V_4

C81

1u/6.3V_4

1u/6.3V_4

C80

22u/6.3V_6

22u/6.3V_6

C19

*22u/6.3V_6

*22u/6.3V_6

C24

*1u/6.3V_4

*1u/6.3V_4

C21

*47u/10V_8

*47u/10V_8

C118

1u/6.3V_4

1u/6.3V_4

C113

1u/6.3V_4

1u/6.3V_4

C35

*1u/6.3V_4

*1u/6.3V_4

C67 47u/6.3V_6

C63 47u/6.3V_6

C62 22u/6.3V_6

C71 1u/6.3V_4

C69 1u/6.3V_4

C75 1u/6.3V_4

C117 22u/6.3V_6

C103 22u/6.3V_6

C120 1u/6.3V_4

C94 22u/6.3V_6

C104 1u/6.3V_4

C100 1u/6.3V_4

C84 1u/6.3V_4

C87 *22u/6.3V_6

C385

C88

C386

C8

C25

C5

C115

+VCCIOA

C116

C34

+VDD2_1P24_MPHY

+VDD2_1P24_PLL

+VDD2_1P24_USB2

C57

1u/6.3V_4

C59

1u/6.3V_4

C13

22u/6.3V_6

C2

*22u/6.3V_6

C108

*1u/6.3V_4

C12

*47u/10V_8

C133

0.1u/16V_4

C112

1u/6.3V_4

C33

1u/6.3V_4

C68

1u/6.3V_4

C58

1u/6.3V_4

C74

22u/6.3V_6

C27

*22u/6.3V_6

C26

*1u/6.3V_4

C15

*47u/10V_8

C141

0.1u/16V_4

C122

22u/6.3V_6

C60

1u/6.3V_4

4

VCC_VCG3

AA33

VCC_VCG4

AC28

VCC_VCG5

AC31

VCC_VCG6

AE28

VCC_VCG7

AE29

VCC_VCG8

AE31

VCC_VCG9

AF31

VCC_VCG10

AF33

VCC_VCG11

AG31

VCC_VCG12

AG33

VCC_VCG13

AJ31

VCC_VCG14

AJ33

VCC_VCG15

AJ35

VCC_VCG16

AL31

VCC_VCG17

AL33

VCC_VCG18

AL35

VCC_VCG19

AM33

VCC_VCG20

AM35

VCC_VCG21

AM36

VCC_VCG22

D31

VCC_VCG23

D33

VCC_VCG24

D37

VCC_VCG25

D39

VCC_VCG26

P39

VCC_VCG27

P41

VCC_VCG28

T28

VCC_VCG29

T29

VCC_VCG30

T31

VCC_VCG31

T33

VCC_VCG32

T35

VCC_VCG33

T36

VCC_VCG34

V28

VCC_VCG35

V29

VCC_VCG36

V31

VCC_VCG37

V33

VCC_VCG38

V35

VCC_VCG39

V36

VCC_VCG40

Y28

VCC_VCG41

Y29

VCC_VCG42

Y33

VCC_VCG43

Y35

VCC_VCG44

C137

0.1u/16V_4

C134

22u/6.3V_6

C90

1u/6.3V_4

22u/6.3V_6

+VDD2_1P24_MPHY

+VDD2_1P24_AUD_ISH

+VDD2_1P24_DSI_CSI

+VDD2_1P24_GLML+VDD2_1P24_GLML

+VDD2_1P24_PLL

+VDD2_1P24_VNNAON

+VDD2_1P24_USB2

C140

0.1u/16V_4

C123

2.2u/10V_4

C42

25A

AW12

AP18

AP21

AP36

AP38

AT18

AT20

AT21

AT35

AT36

AT38

BA13

BA15

BA25

BA31

BA41

BA43

AP25

AP31

AT25

AT27

AT28

AT29

AT31

AJ23

AG23

AC21

AE20

AE21

AF20

AF21

AC18

AC20

AL36

AL38

AP20

AM20

AL18

AM18

AA18

AA20

AG18

AJ20

T21

T23

T25

V21

V23

V25

U27G

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

3A

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VCCIOA1

VCCIOA2

VCCIOA3

VCCIOA4

VCCIOA5

VCCIOA6

VCCIOA7

VCC_1P8V_A3

VCC_1P8V_A4

VDD1(1.8V)

VCC_1P8V_A5

VCC_1P8V_A6

VCC_1P8V_A7

VCC_1P8V_A8

VCC_1P8V_A2

VCC_1P8V_A1

VDD2_1P2_MPHY1

VDD2_1P2_MPHY2

VDD2_1P2_MPHY3

VDD2_1P2_MPHY4

VDD2_1P2_MPHY5

VDD2_1P2_AUD1

VDD2_1P2_AUD2

VDD2_1P2_DSI_CSI

VDD2_1P2_GLM1

VDD2_1P2_GLM2

VDD2_1P2_GLM4

VDD2_1P2_GLM3

VDD2_1P2_PLL1

VDD2_1P2_PLL2

VDD2_1P2_VNNAON1

VDD2_1P2_VNNAON2

VDD2_1P2_USB2

VDD2_1P2_USB3

VDD2(1.2V)

9 OF 13

0.4A

3A

10 OF 13

4.5A

VCCRAM(1.05V)

RTC

0.15A

VDD3(3.3V)

3

A

4

VCC_VCG_SENSE

VSS_VCG_SENSE

VNN_SENSE

VNN_VSS_SENSE

VCCRAM_1P053

VCCRAM_1P054

VCCRAM_1P057

VCCRAM_1P058

VCCRAM_1P059

VCCRAM_1P0510

VCCRAM_1P0511

VCCRAM_1P0512

VCCRAM_1P0513

VCCRAM_1P0514

VCC_1P05_INT2

VCC_1P05_INT1

VCC_1P05_INT3

VCCRAM_1P051

VCCRAM_1P052

VCCRAM_1P055

VCCRAM_1P056

VCCRAM_1P0515

VCCRAM_1P0516

VCCRTC_3P3V

VCC_3P3V_A2

VCC_3P3V_A5

VCC_3P3V_A1

VCC_3P3V_A3

VCC_3P3V_A4

VCC_3P3V_A6

VCC_3P3V_A7

VCC_3P3V_A8

VCC_3P3V_A9

Vinafix.com

5

4

3

2

1

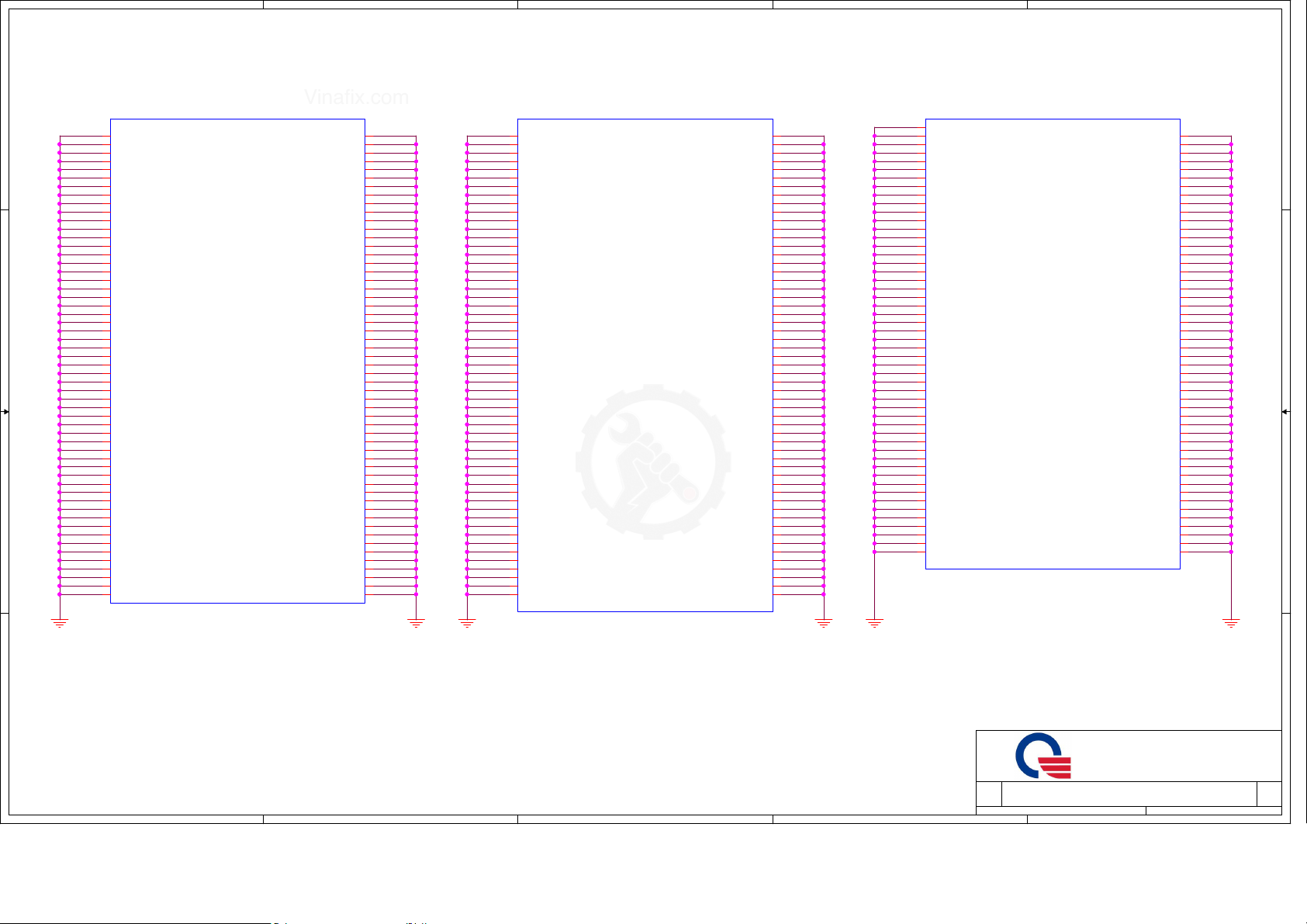

GLK ULT (GND)

08

D D

C C

B B

A12

A16

A20

A24

A28

A32

A36

A40

A44

A48

A51

AA12

AA13

AA15

AA17

AA21

AA23

AA25

AA27

AA35

AA43

AA48

AB1

AB3

AB55

AC8

AC13

AC23

AC25

AC27

AC29

AE18

AE23

AE25

AE27

AE43

AE48

AF1

AF3

AF4

AF6

AF8

AF9

AF11

AF12

AF14

AF16

AF18

AF23

AF25

AF29

AF40

AF42

U27K

A3

VSS6

A6

VSS13

VSS1

VSS2

VSS3

VSS4

VSS5

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS33

VSS28

VSS29

VSS30

VSS31

VSS32

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS49

VSS50

VSS61

VSS62

VSS63

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS51

VSS52

11 OF 13

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS64

VSS87

VSS65

VSS66

VSS67

VSS68

VSS77

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS78

VSS79

VSS80

VSS90

VSS97

VSS98

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS88

VSS89

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS108

VSS110

VSS107

VSS109

AF44

AF45

AF47

AF48

AF50

AF52

AF53

AF55

AG20

AL21

AG25

AG29

AG35

AG38

AJ8

AJ13

AJ18

AJ25

AJ29

AJ36

AJ38

AJ39

AJ44

AK1

AK3

AK55

AL3

AL7

AL8

AL10

AL12

AL13

AL15

AL17

AL20

AL25

AL29

AL39

AL41

AL43

AL44

AL46

AL51

AM1

AM21

AM23

AM25

AM29

AM31

AM38

AM55

AN3

AN8

AN10

AN46

AN48

AN49

AN51

AN53

AP23

AP27

AP28

AP29

AP33

AP35

AR2

AR7

AR10

AR12

AR17

AR39

AR44

AR46

AR49

AR54

AT23

AT33

AU3

AU10

AU28

AU46

AU53

AV15

AV17

AV23

AV25

AV31

AV33

AV39

AV41

AW2

AW5

AW10

AW28

AW46

AW51

AW54

AY13

AY15

AY28

AY41

AY43

B55

BA27

BA29

BB1

BB28

BB55

BC5

B2

U27M

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_124

VSS_130

VSS_121

VSS_122

VSS_123

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_131

VSS_132

VSS_135

VSS_133

VSS_134

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_147

VSS_150

VSS_146

VSS_148

VSS_149

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_178

12 OF 13

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_179

VSS_187

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_189

VSS_188

VSS_190

VSS_194

VSS_191

VSS_192

VSS_193

VSS_195

VSS_199

VSS_196

VSS_197

VSS_198

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_215

VSS_213

VSS_214

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

BC11

BC17

BC19

BC21

BC23

BC25

BC31

BC33

BC35

BC37

BC39

BC41

BC45

BC51

BD9

BD15

BD19

BD21

BD28

BD35

BD37

BD47

BE3

BE28

BE53

BF9

BF19

BF37

BF47

BG1

BG6

BG28

BG50

BG55

BH11

BH13

BH17

BH19

BH23

BH25

BH28

BH31

BH33

BH37

BH39

BH41

BH45

BJ2

BJ15

BJ19

BJ25

BJ28

BJ31

BJ37

BJ41

AL23

BJ54

BK1

BK17

BK21

BK35

BK39

BK55

BL5

BL8

BL10

BL14

BL24

BL28

BL32

BL42

BL46

BL48

BL51

C12

C16

C28

C36

D21

D28

D41

D45

D55

E28

E50

E55

F21

F31

G28

H13

H15

H21

H23

H28

H33

H39

J27

J33

J41

J45

U27L

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS17

VSS19

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS18

C1

VSS20

VSS21

VSS22

VSS23

VSS24

D6

VSS30

D9

VSS31

VSS25

VSS26

VSS27

VSS28

VSS29

VSS32

VSS33

VSS34

F1

VSS35

F4

VSS38

VSS36

VSS37

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

J8

VSS52

VSS47

VSS48

VSS49

VSS50

13 OF 13

VSS51

VSS53

VSS55

VSS54

VSS56

VSS59

VSS60

VSS61

VSS57

VSS58

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS74

VSS73

VSS75

VSS77

VSS78

VSS80

VSS81

VSS82

VSS84

VSS85

VSS93

VSS95

VSS96

VSS83

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS94

VSS97

VSS98

VSS99

VSS100

VSS101

VSS76

VSS79

J51

K1

K3

K28

K55

L5

L7

L8

L19

L33

M15

M25

M28

M35

M41

N12

N28

N46

N51

P21

P55

R8

R28

T27

T38

U13

V27

V38

V55

W2

W3

W5

W7

W8

W10

W39

W41

W43

W44

W46

W48

W49

W51

Y21

Y23

Y25

Y27

Y31

T3

U3

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

5

4

3

2

Tuesday, December 26, 2017

PROJECT :

GLK (GND)

GLK (GND)

GLK (GND)

1

Z8G

Z8G

Z8G

8 35

8 35

8 35

1A

1A

1A

Vinafix.com

5

4

3

2

1

HARDWARE STRAPS

09

+1.8V_S5

Note: If platform is using eMMC as boot device, then

provide a pull down for this strap to disable

R463

R418

*4.7K_1%_4

R431

10K_5%_4

*4.7K_1%_4

R462

10K_5%_4

D D

C C

B B

R150

*4.7K_1%_4

R144

4.7K_1%_4

R120

4.7K_1%_4

R136

*10K_5%_4

R458

*4.7K_1%_4

R459

10K_5%_4

R76

*10K_5%_4

R92

4.7K_1%_4

R419

*10K_5%_4

R434

4.7K_1%_4

R453

*4.7K_1%_4

R454

10K_5%_4

CNVI_RF_RESET#[3,18]

R45

*4.7K_1%_4

R56

4.7K_1%_4

GPIO_43[4]

GPIO_81[3]

CNVI_RGI_DT[3,18,22]

USB_OC0#[3,21]

GPIO_62[3]

GPIO_79[3]

GPIO_80[3]

GPIO_85[3]

GPIO_86[3]

GPIO_87[3]

GPIO_89[3]

GPIO_159[5]

GPIO_164[5]

SMB_SOC_CLK[3]

CNVI_BRI_RSP[3,18]

CNVI_RGI_RSP[3,18]

XTAL_CLKREQ[3,18]

*4.7K_1%_4

R433

4.7K_1%_4

*4.7K_1%_4

R432

4.7K_1%_4

R466 10K_5%_4

R29 4.7K_1%_4

R38 *10K_5%_4

R469 *10K_5%_4

R461 10K_5%_4

R108 4.7K_1%_4

R34 10K_5%_4

R110 10K_5%_4

R97 10K_5%_4

R91 10K_5%_4

R77 10K_5%_4

R99 4.7K_1%_4

R114 4.7K_1%_4

R20 *10K_5%_4

R26 *10K_5%_4

R28 *10K_5%_4

R43 *10K_5%_4

R42 *10K_5%_4

*4.7K_1%_4

R41

*4.7K_1%_4

+1.8V_S5

*4.7K_1%_4

R94

4.7K_1%_4

GPIO_174 [5]

GPIO_61 [3]

GPIO_27 [5]

GPIO_28 [5]

GPIO_65 [3]

GPIO_163 [5]

AZ_CODEC_SDIN0 [5,14]

GPIO_66 [3]

GPIO_83 [3]

GPIO_172 [5]

GPIO_175 [5]

CNVI_BRI_DT [3,18]

GPIO_84 [3]

R93

R53

R417

R420

SPI.

Note: The default for A0 will be eSPI

due to a bug on LPC.

Hardware Strap Strap Description

PIO_174

GPIO_61

GPIO_27

GPIO_28

GPIO_65

GPIO_163

AZ_CODEC_SDIN0

GPIO_66

GPIO_83

GPIO_172 0 = Disable (default)

GPIO_42

GPIO_175

CNVI_BRI_DT

GPIO_84

VDD2 1.24V vs.1.20V select

0 = 1.2V(default)G

1 = 1.24V

Enable CSE(TXE3.0) ROM Bypass

0 = Disable bypass

1 = Enable Bypass

Allow eMMC as a boot source

0 = Disable

1 = Enable

Allow SPI as a boot source

0 = Disable

1 = Enable

Force DNX FW Load

0 = Do not force

1 = Force

SMBus 1.8V/3.3V mode select

0=buffers set to 3.3V

1=buffers set to 1.8V

PMU 1.8V/3.3V mode select

0=buffers set to 3.3V mode

1=buffers set to 1.8V mode

LPC No Re-Boot

0 = Disable (default)

1 = Enable

LPC 1.8V/3.3V mode select

0=buffers set to 3.3V mode

1=buffers set to 1.8V mode

SMbus No Re-Boot

1 = Enable

Top swap override

0 = Disable

1 = Enable

eSPI vs. LPC

0 = LPC mode (default)

1 = eSPI mode

eSPI Flash Sharing Mode:

0 = master attached flash sharing

(MAFS; default)

1 = slave attached flash sharing

(SAFS)

Allow SPI as a boot source

0 = Enable (default)

1 = Disable

Value

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

+1.8V_S5[3,4,5,6,7,16,19,23,27,29]

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

Tuesday, December 26, 2017

Date: Sheet of

5

4

3

2

Tuesday, December 26, 2017

PROJECT :

HW STRAPS/XDP

HW STRAPS/XDP

HW STRAPS/XDP

Z8G

Z8G

Z8G

9 35

9 35

1

9 35

1A

1A

1A

Vinafix.com

5

4

3

2

1

+2.5V

+3V

10

P/N and F/P

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

D D

M_A_WE#[2]

M_A_CAS#[2]

+1.2VSUS

M_A_PARITY

+3V

R278

*SDM@10K_5%_4

R279

SDM@10K_5%_4

M_A_ALERT#

M_A_EVENT#

R255

SDM@240_1%_4

R272

*SDM@10K_5%_4

R271

SDM@10K_5%_4

R273 SDM@240_1%_4

R280 SDM@240_1%_4

C C

R274

*SDM@10K_5%_4

CHA_SA0 CHA_SA2CHA_SA1

R275

SDM@10K_5%_4

B B

M_A_RAS#[2]

M_A_ACT#[2]

M_A_DRAMRST#[2]

M_A_BA#0[2]

M_A_BA#1[2]

M_A_BG#0[2]

M_A_BG#1[2]

M_A_CS#0[2]

M_A_CS#1[2]

M_A_CKE0[2]

M_A_CKE1[2]

M_A_CLK0[2]

M_A_CLK0#[2]

M_A_CLK1[2]

M_A_CLK1#[2]

M_A_ODT0_DIMM[2]

M_A_ODT1_DIMM[2]

CLK_SCLK[3,19]

CLK_SDATA[3,19]

+1.2VSUS +1.2VSUS

R268 *SDM@240_1%_4

R250 *SDM@240_1%_4

R253 *SDM@240_1%_4

R254 *SDM@240_1%_4

R267 *SDM@240_1%_4

R249 *SDM@240_1%_4

R269 *SDM@240_1%_4

R270 *SDM@240_1%_4

M_A_A10

M_A_A11

M_A_A12

M_A_A13

TP51

TP50

M_A_PARITY

M_A_ALERT#

M_A_EVENT#

C225 *SDM@0.1u/16V_4

CHA_SA0

CHA_SA1

CHA_SA2

M_A_CB0

M_A_CB1

M_A_CB2

M_A_CB3

M_A_CB4

M_A_CB5

M_A_CB6

M_A_CB7

+1.2VSUS

JDIM1A

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10/AP

120

A11

119

A12

158

A13

151

A14/WE#

156

A15/CAS#

152

A16/RAS#

162

CS2#/C0

165

CS3#/C1

114

ACT#

143

PARITY

116

ALERT#

134

EVENT#

108

RESET#

150

BA0

145

BA1

115

BG0

113

BG1

149

CS0#

157

CS1#

109

CKE0

110

CKE1

137

CK0

139

CK0#

138

CK1

140

CK1#

155

ODT0

161

ODT1

253

SCL

254

SDA

256

SA0

260

SA1

166

SA2

92

CB0

91

CB1

101

CB2

105

CB3

88

CB4

87

CB5

100

CB6

104

CB7

12

DM0

33

DM1

54

DM2

75

DM3

178

DM4

199

DM5

220

DM6

241

DM7

96

DBI8#

SDM@D4AS0-26001-1P52

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

(260P)

DDR4 SODIMM 260 PIN

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DQS#8

M_A_DQ24

7

M_A_DQ26

20

M_A_DQ28

21

M_A_DQ30

4

M_A_DQ29

3

M_A_DQ31

16

M_A_DQ27