5

www.kythuatvitinh.com

Digitally signed by dd

DN: cn=dd, o=dd, ou=dd,

email=dddd@yahoo.com,

c=US

Date: 2009.11.05 14:03:52

+07'00'

4

3

2

1

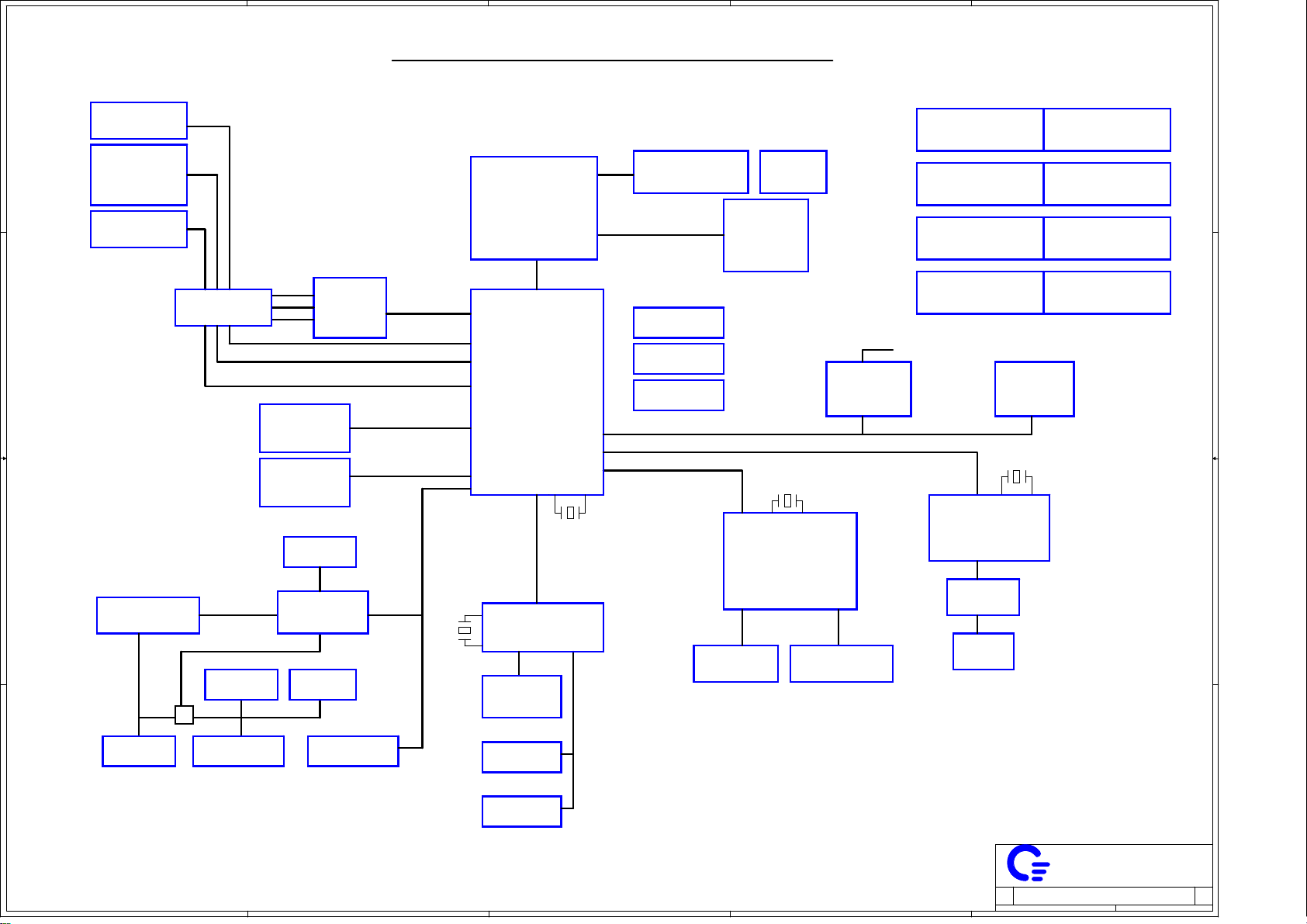

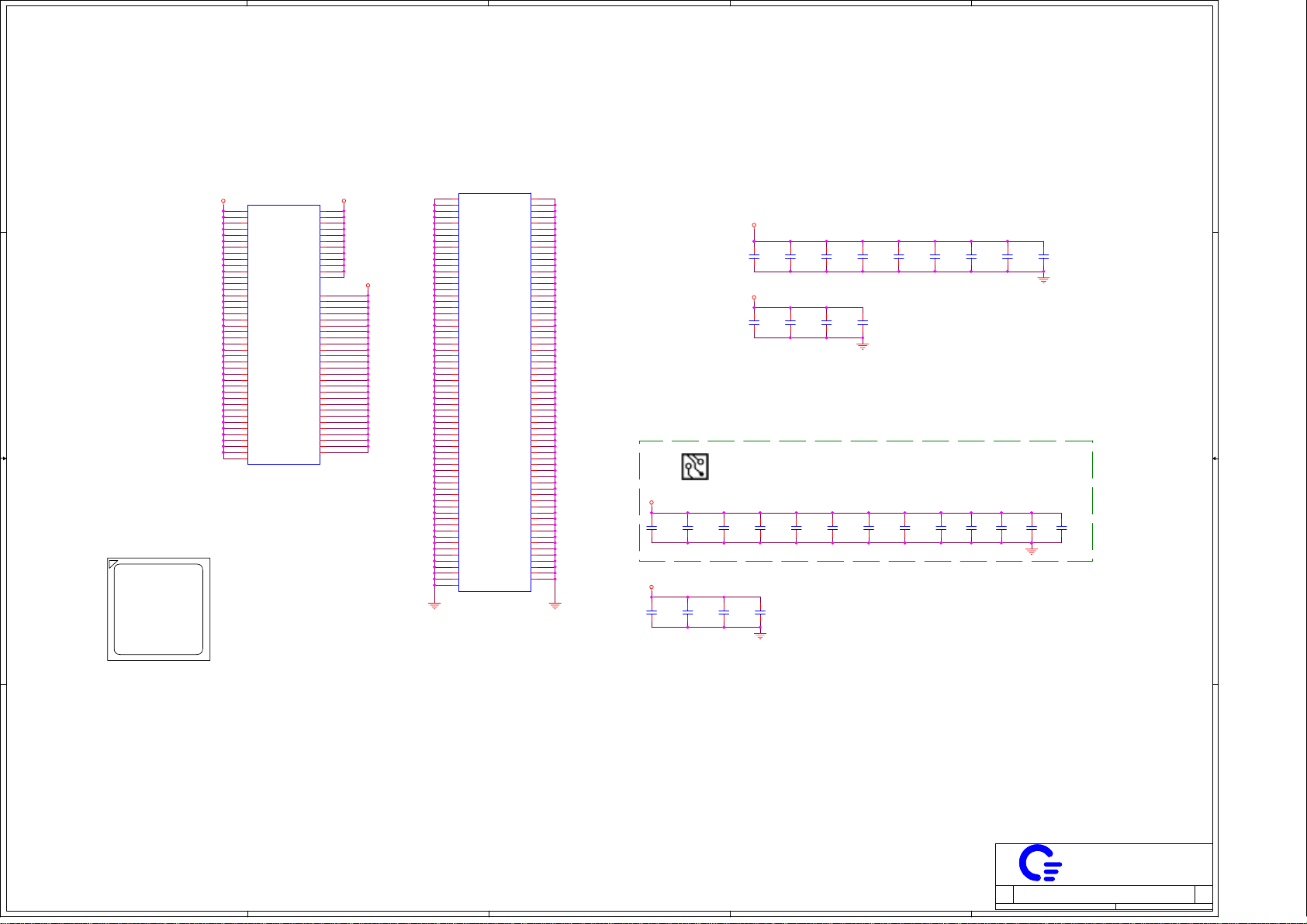

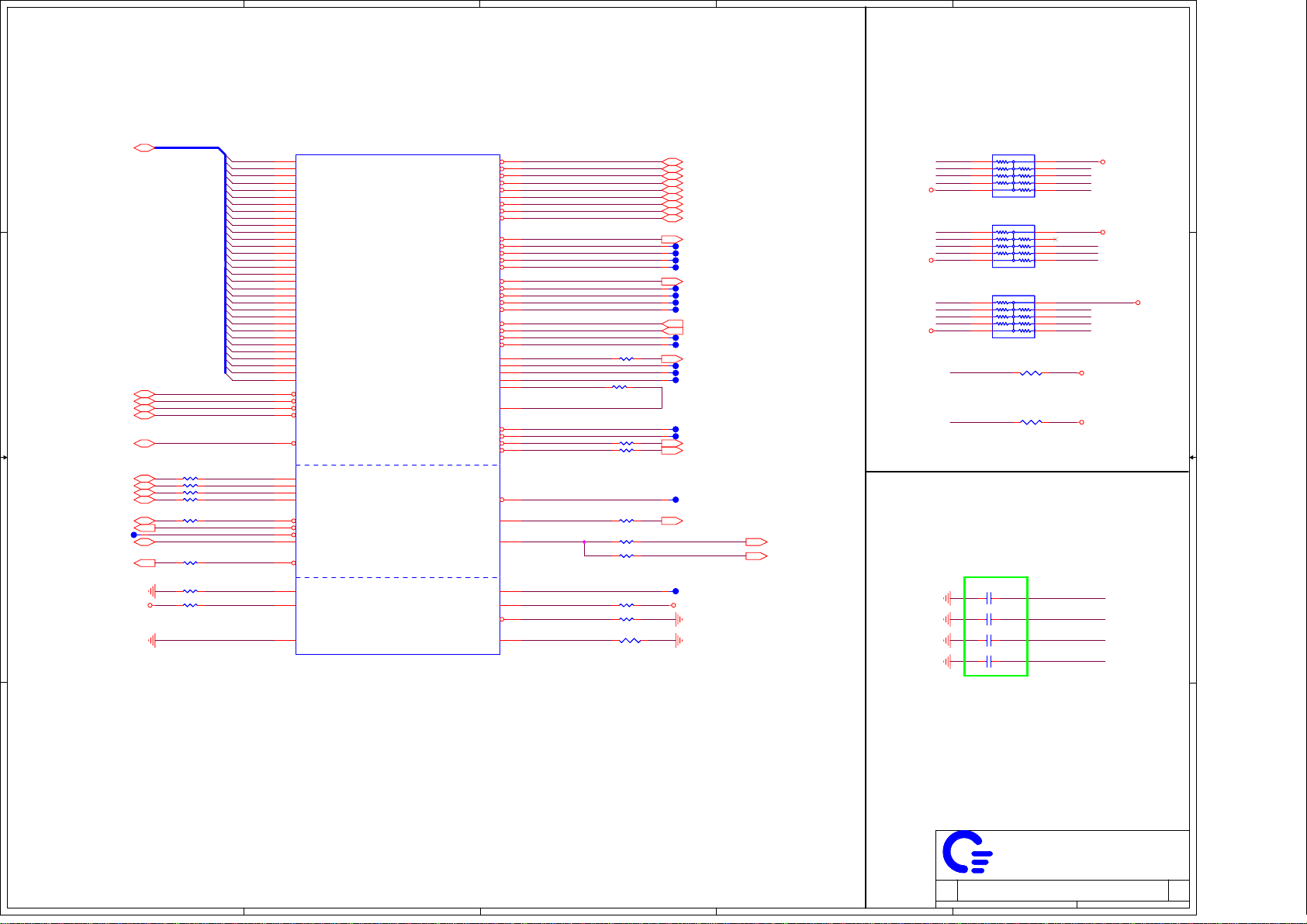

ZO3 SYSTEM BLOCK DIAGRAM

D D

C C

B B

A A

TV-OUT

P14

TFT LCD Panel

WXGA

P14

CRT

P14

Audio Amplifier

Connector

Speaker

INT or EV

selector Resistor

P19

MIC Jack

Phone Jack

LVDS

TV-out

CRT

P14

HDD (SATA)

ODD (PATA)

Int MIC

Azalia AudioController

RealTek ALC268

Line in

P19P19

MXM

P13

P18

P18

P19

P19P19

MDC 1.5

PCI-Express 16X

TV-out

LVDS

VGA

SATA0

PATA

Azalia

P19

AMD S1g1

uFCPGA638

Turion 64 Dual-Core/

Sempron Single-Core

n-Vidia

MCP67

X'TAL

32.768K

EC (WPC8769LDG)

SPI ROM

Touch Pad

Keyboard

P2,3,4,5

HT LINK

P7,8,9,10,11,12

LPC

P21

P18

P22

Dual Channel DDR2

533/667 MHz

USB 2.0

X'TAL

32.768KHZ

P21

CPU

Thermal Sensor

Bluetooth

USB Port x 4

CCD

P16

P16

P14

PCI-Express

LCI

PCI Bus

IEEE 1394 Port

CPU Fan

P4

DDRII

SO-DIMM 0

SO-DIMM 1

P6

X'TAL24.576MHZ

1394 +Cardreader

Controller

Ricoh R5C833

P20

Media Card Reader

P20

P22

Mini Card /

WLAN

P20

VCORE(ISL6262A)

5V/3.3V (TPS51120)

DISCHARGE

+1.8V

USB

New Card

P17

PCIE-6

LAN PHY

Realtek RTL8211B

Transformer

P15

RJ45/11

P15

+2.5V/ +1.25VM/ +1.25V/ +1.5V

SMDDR_VREF/ SMDDR_VTERM

P25

VGA-Core (MAX 1993)

+1.2V

P24

BATTERY SELECT

P28

BATTERYCHARGER

(ISL6251)

P27

P17

X'TAL

25M

P15

P26

P23

P23

PROJECT : ZO3

5

4

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

130Wednesday, April 25, 2007

130Wednesday, April 25, 2007

130Wednesday, April 25, 2007

of

of

1

of

1A

1A

1A

5

www.kythuatvitinh.com

4

3

2

1

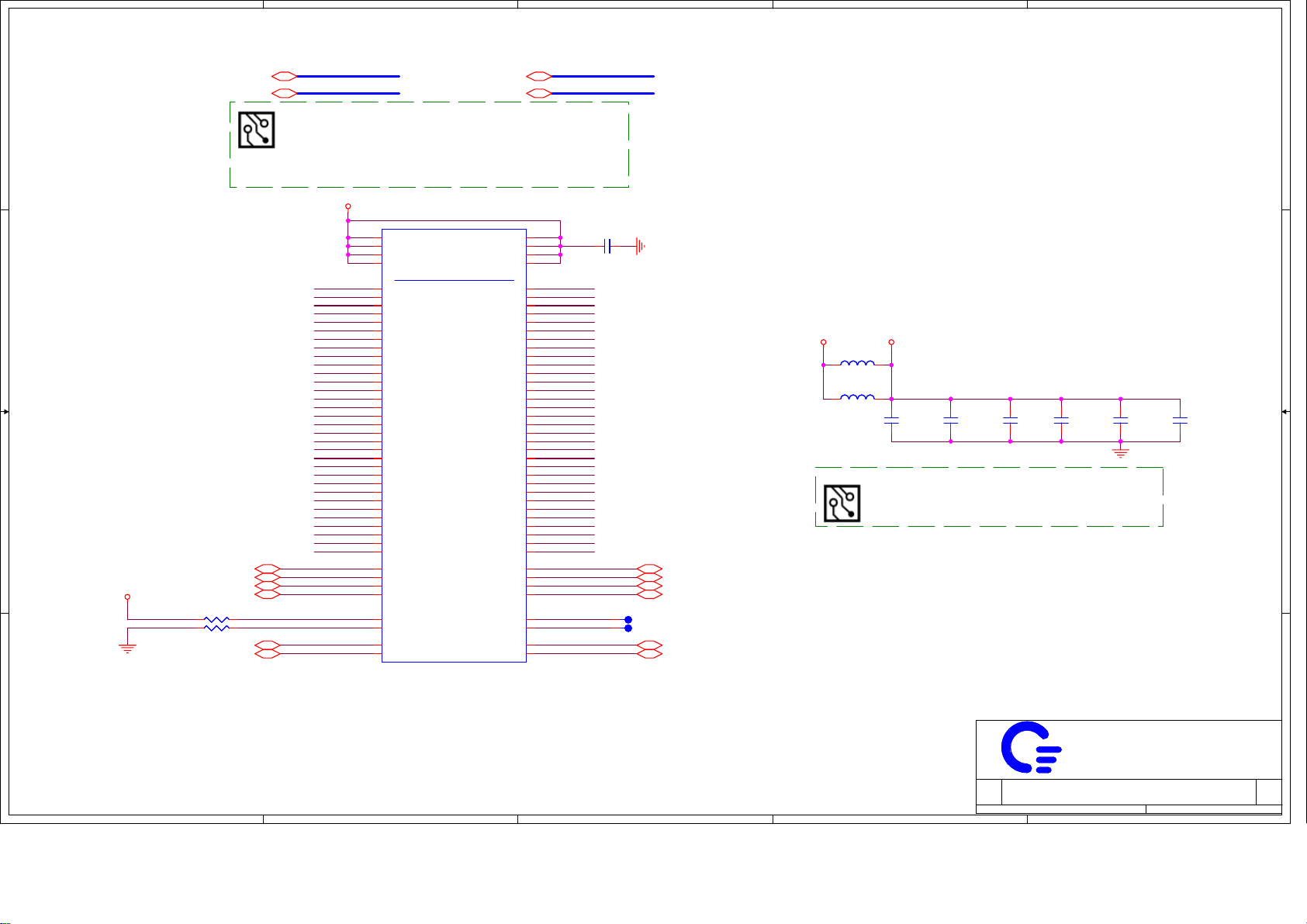

HT_RXD#[15..0](7) HT_TXD[15..0](7)

HT_RXD[15..0](7)

D D

HT_RXD#[15..0]

HT_RXD[15..0]

HT_TXD#[15..0](7)

HT_TXD[15..0]

HT_TXD#[15..0]

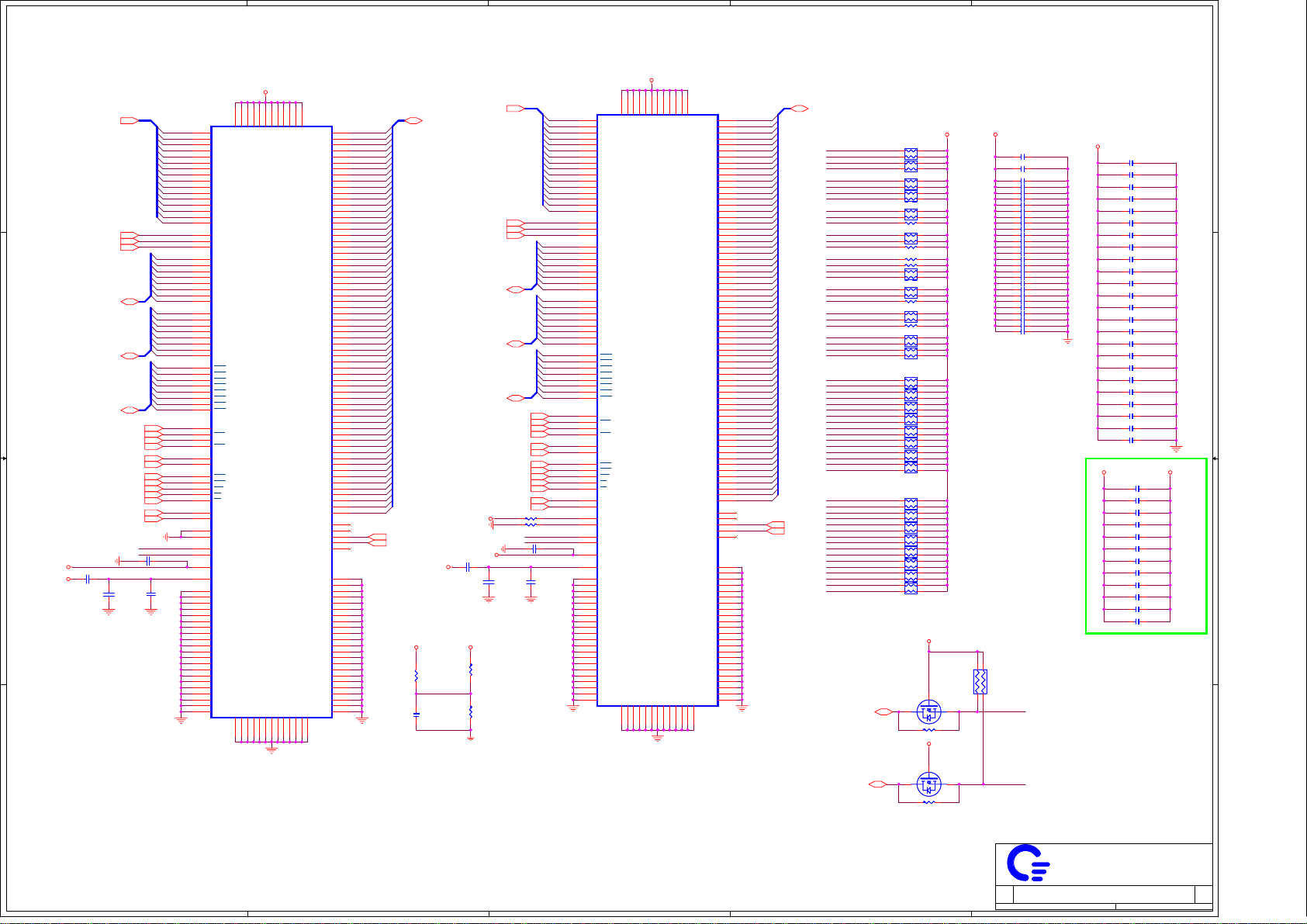

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

VLDT_RUN

HT_RXD15

HT_RXD#15

HT_RXD14

C C

B B

HT_CPU_UPCLK1(7)

HT_CPU_UPCLK#1(7)

VLDT_RUN

HT_CPU_UPCLK0(7)

HT_CPU_UPCLK#0(7)

R369 51_4R369 51_4

R370

R370

HT_CPU_UPCTL0(7)

HT_CPU_UPCTL#0(7)

51_4

51_4

HT_CTLIN1_P

HT_CTLIN1_N

HT_RXD#14

HT_RXD13

HT_RXD#13

HT_RXD12

HT_RXD#12

HT_RXD11

HT_RXD#11

HT_RXD10

HT_RXD#10

HT_RXD9

HT_RXD#9

HT_RXD8

HT_RXD#8

HT_RXD7

HT_RXD#7

HT_RXD6

HT_RXD#6

HT_RXD5

HT_RXD#5

HT_RXD4

HT_RXD#4

HT_RXD3

HT_RXD#3

HT_RXD2

HT_RXD#2

HT_RXD1

HT_RXD#1

HT_RXD0

HT_RXD#0

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

U21AU21A

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1

Processor Socket

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

AE5

AE4

AE3

AE2

HT_TXD15

T4

HT_TXD#15

T3

HT_TXD14

V5

HT_TXD#14

U5

HT_TXD13

V4

HT_TXD#13

V3

HT_TXD12

Y5

HT_TXD#12

W5

HT_TXD11

AB5

HT_TXD#11

AA5

HT_TXD10

AB4

HT_TXD#10

AB3

HT_TXD9

AD5

HT_TXD#9

AC5

HT_TXD8

AD4

HT_TXD#8

AD3

HT_TXD7

T1

HT_TXD#7

R1

HT_TXD6

U2

HT_TXD#6

U3

HT_TXD5

V1

HT_TXD#5

U1

HT_TXD4

W2

HT_TXD#4

W3

HT_TXD3

AA2

HT_TXD#3

AA3

HT_TXD2

AB1

HT_TXD#2

AA1

HT_TXD1

AC2

HT_TXD#1

AC3

HT_TXD0

AD1

HT_TXD#0

AC1

Y4

Y3

Y1

W1

HT_CPU_DWNCTL1

T5

HT_CPU_DWNCTL#1

R5

R2

R3

C516

C516

4.7U_6

4.7U_6

HT_CPU_DWNCLK1 (7)

HT_CPU_DWNCLK#1 (7)

HT_CPU_DWNCLK0 (7)

HT_CPU_DWNCLK#0 (7)

T31T31

T30T30

HT_CPU_DWNCTL0 (7)

HT_CPU_DWNCTL#0 (7)

L41

L41

L40

L40

VLDT_RUN

C488

C488

4.7U_6

4.7U_6

C493

C493

4.7U_6

4.7U_6

C492

C492

.22U_4

.22U_4

C491

C491

.22U_4

.22U_4

+1.2V_HT

FBJ3216HS800_1206

FBJ3216HS800_1206

FBJ3216HS800_1206

FBJ3216HS800_1206

80 ohm(4A)

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

C489

C489

180P_4

180P_4

C490

C490

180P_4

180P_4

A A

PROJECT : ZO3

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ATHLON64 HT I/F

ATHLON64 HT I/F

ATHLON64 HT I/F

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

of

of

of

230Wednesday, April 25, 2007

230Wednesday, April 25, 2007

230Wednesday, April 25, 2007

1A

1A

1A

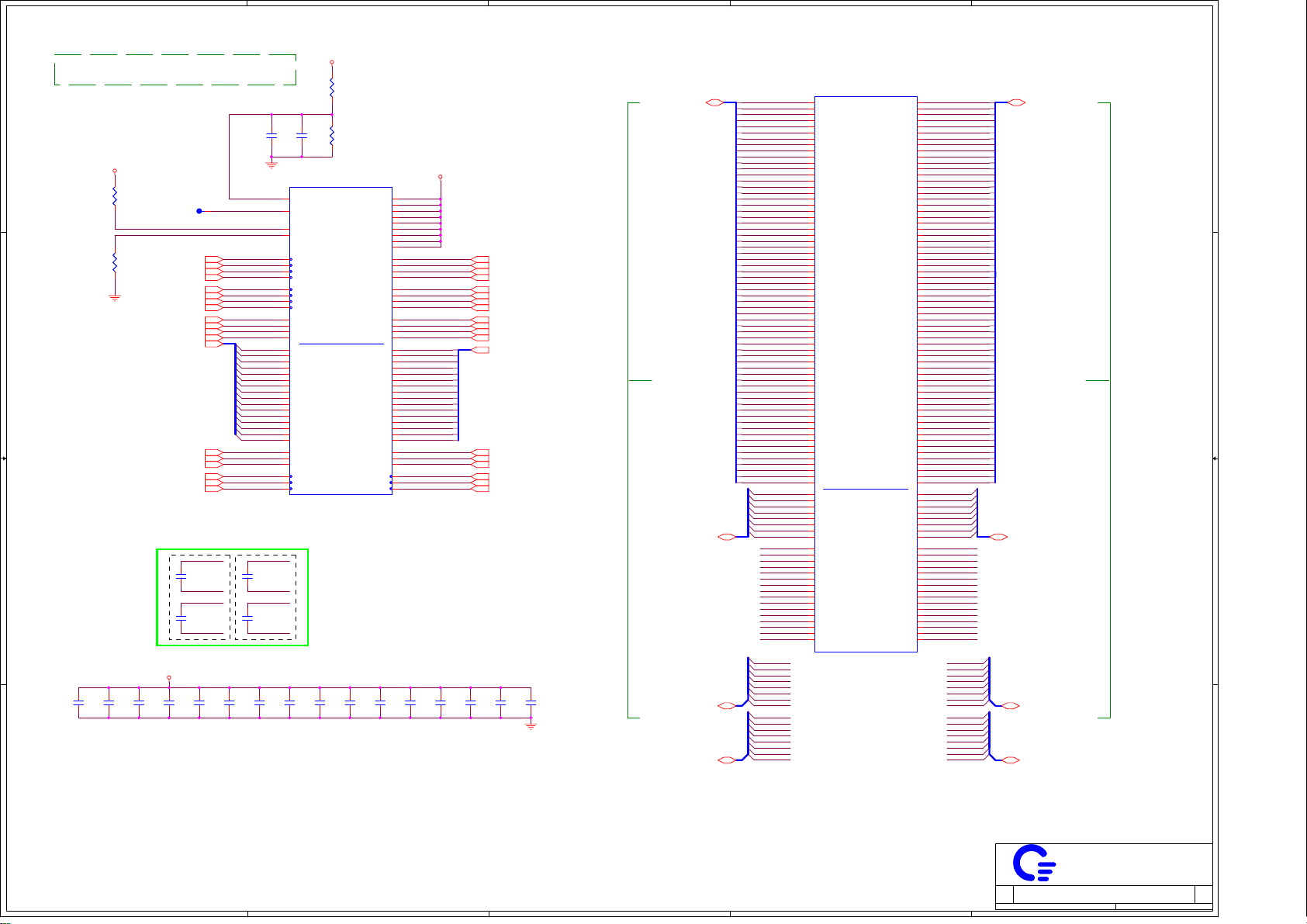

A

www.kythuatvitinh.com

B

C

D

E

Y10

V19

J22

V22

T19

Y26

J24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

C241

C241

.1U_4

.1U_4

C300

C300

1000P_4

1000P_4

U21B

U21B

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

C287

C287

.22U_4

.22U_4

+1.8VSUS

R229

R229

2K/F_4

2K/F_4

R230

R230

2K/F_4

2K/F_4

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

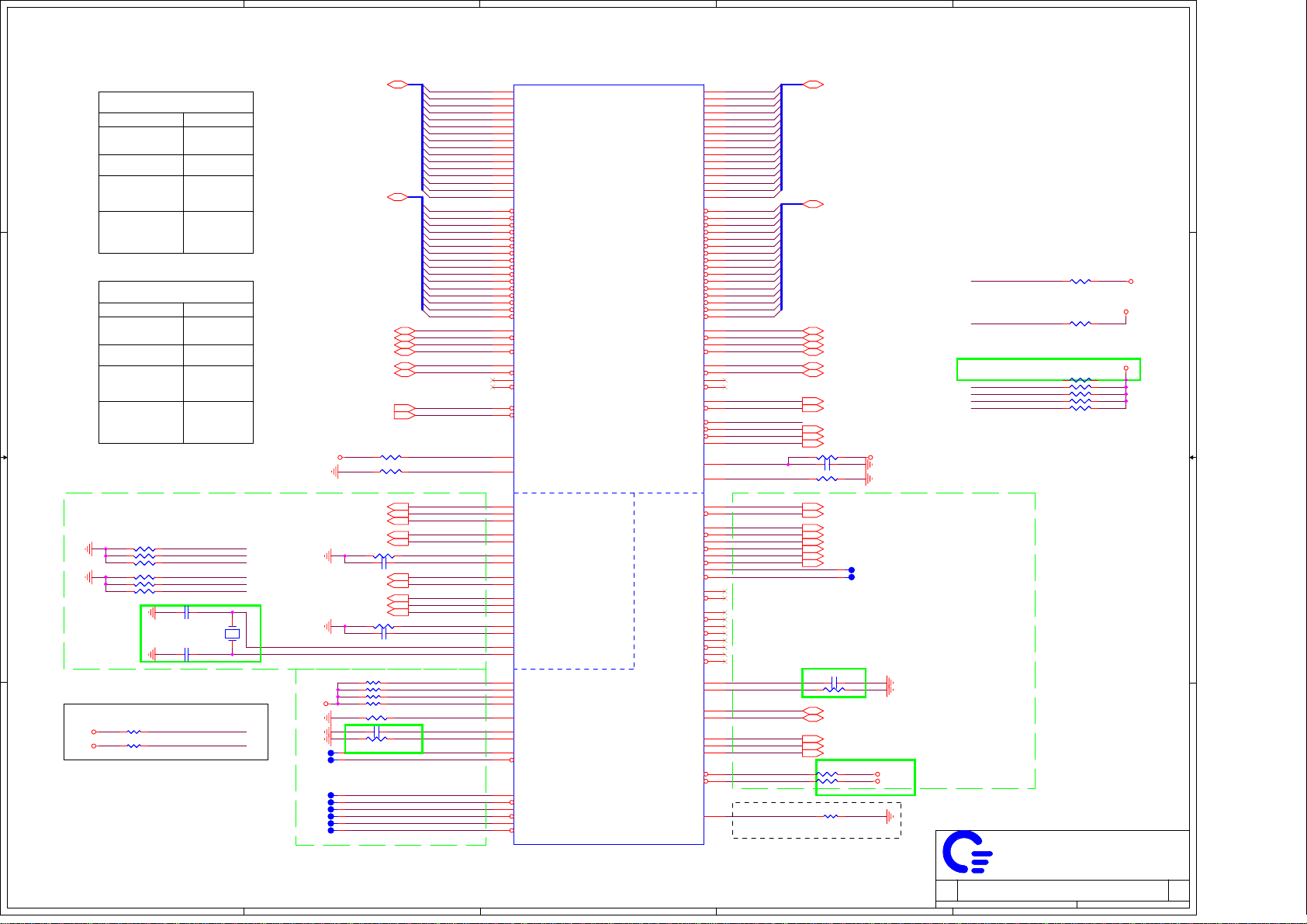

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

C288

C288

C290

C290

1000P_4

1000P_4

1000P_4

1000P_4

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

C142

C142

1000P_4

1000P_4

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

+SMDDR_VTERM

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

C286

C286

C301

C301

1000P_4

1000P_4

180P_4

180P_4

M_CLKOUT1 (6)

M_CLKOUT1# (6)

M_CLKOUT0 (6)

M_CLKOUT0# (6)

M_CLKOUT4 (6)

M_CLKOUT4# (6)

M_CLKOUT3 (6)

M_CLKOUT3# (6)

M_ODT3 (6)

M_ODT2 (6)

M_ODT1 (6)

M_ODT0 (6)

M_B_A[0..15] (6)

M_B_BS#2 (6)

M_B_BS#1 (6)

M_B_BS#0 (6)

M_B_RAS# (6)

M_B_CAS# (6)

M_B_WE# (6)

C140

C140

180P_4

180P_4

C302

C302

180P_4

180P_4

C284

C284

180P_4

180P_4

Processor DDR2 Memory Interface

U21C

M_B_DQ[0..63](6)

To SODIMM socket B (Far)

M_B_DM[0..7](6) M_A_DM[0..7] (6)

M_B_DQS[0..7](6)

M_B_DQS#[0..7](6)

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

E25

A22

B16

A12

F26

E26

A24

A23

D16

C16

C12

B12

U21C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

DDR: DATA

DDR: DATA

Athlon 64 S1

Processor Socket

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQ[0..63] (6)

To SODIMM socket A (near)

M_A_DQS[0..7] (6)

M_A_DQS#[0..7] (6)

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

4 4

+1.8VSUS

R412

R412

39.2/F_4

39.2/F_4

1 2

R413

R413

39.2/F_4

39.2/F_4

1 2

3 3

M_A_CS#3(6)

M_A_CS#2(6)

M_A_CS#1(6)

M_A_CS#0(6)

M_B_CS#3(6)

M_B_CS#2(6)

M_B_CS#1(6)

M_B_CS#0(6)

M_CKE3(6)

M_CKE2(6)

M_CKE1(6)

M_CKE0(6)

M_A_A[0..15](6)

M_A_BS#2(6)

M_A_BS#1(6)

M_A_BS#0(6)

M_A_RAS#(6)

M_A_CAS#(6)

M_A_WE#(6)

CPU_M_VREF

W17

VTT_SENSE

T35T35

M_ZN

M_ZP

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

AE10

AF10

W24

Near CPU L<1200mil

C285

C285

.22U_4

.22U_4

M_CLKOUT0

C139

C139

1.5P_4

1.5P_4

M_CLKOUT0#

M_CLKOUT1

C297

C297

1.5P_4

1.5P_4

M_CLKOUT1#

C289

C289

.22U_4

.22U_4

M_CLKOUT3

2 2

C294

C294

C145

C145

4.7U_6

4.7U_6

4.7U_6

4.7U_6

4.7U_6

4.7U_6

+SMDDR_VTERM

C239

C239

C295

C295

4.7U_6

4.7U_6

C157

C157

1.5P_4

1.5P_4

M_CLKOUT3#

M_CLKOUT4

C282

C282

1.5P_4

1.5P_4

M_CLKOUT4#

C141

C141

.22U_4

.22U_4

1 1

PROJECT : ZO3

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ATHLON64 DDRII MEMORY I/F

ATHLON64 DDRII MEMORY I/F

A

B

C

D

ATHLON64 DDRII MEMORY I/F

Date: Sheet

Date: Sheet of

Date: Sheet of

330Wednesday, April 25, 2007

330Wednesday, April 25, 2007

E

330Wednesday, April 25, 2007

1A

1A

1A

of

5

www.kythuatvitinh.com

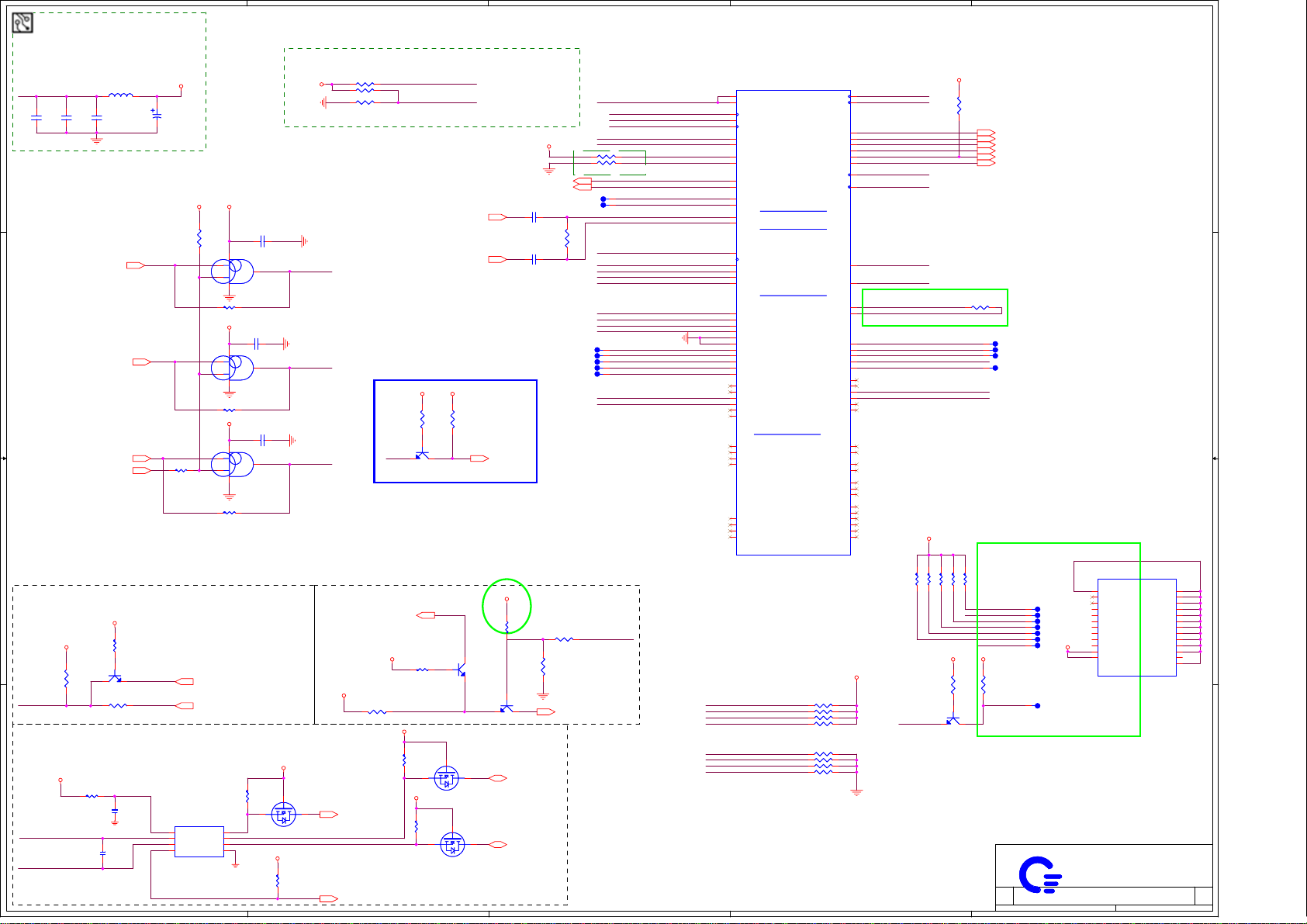

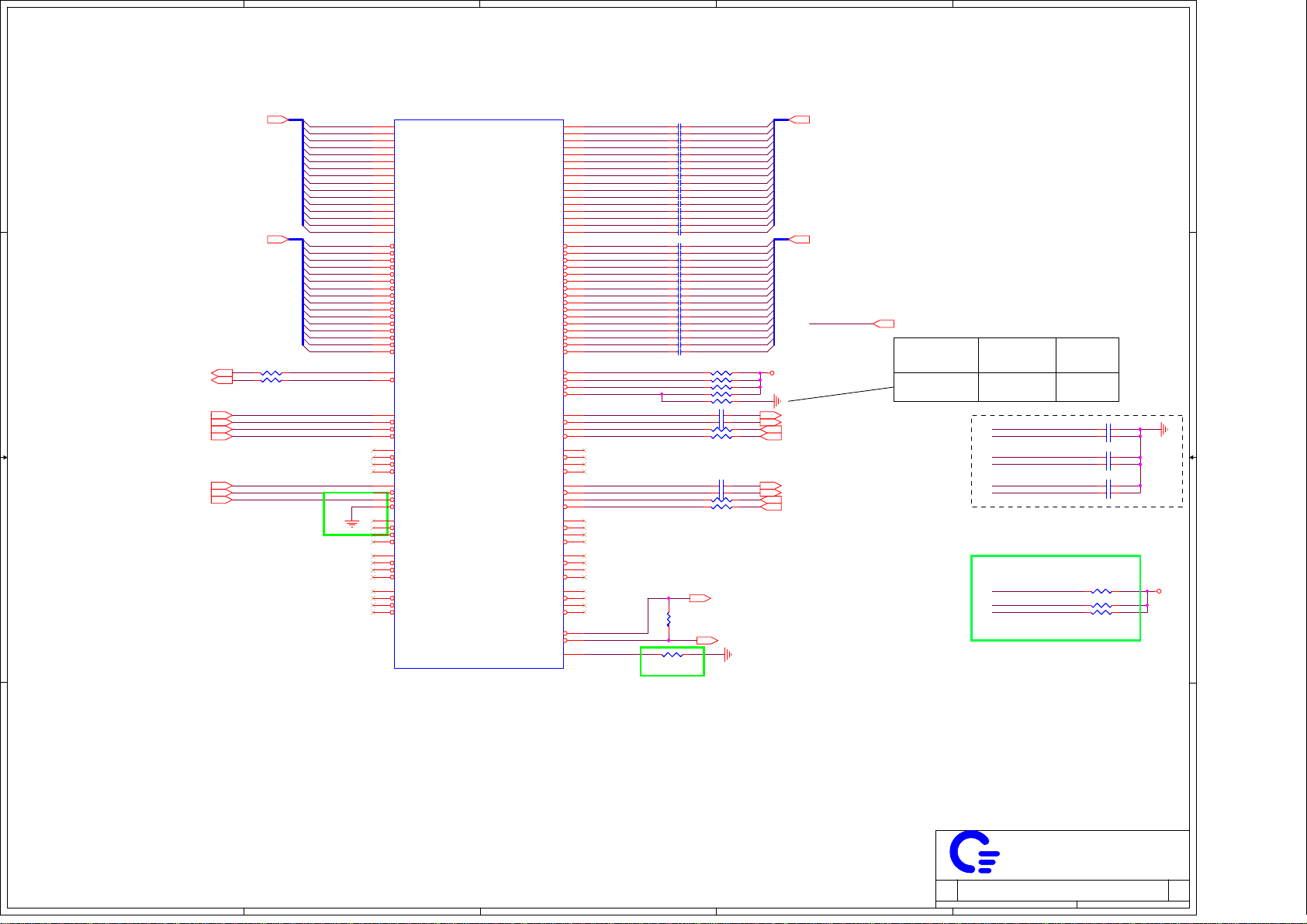

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

If AMD SI is not used, the SID pin can be left unconnected and SIC

CPU_VDDA_RUN

+2.5V

C130

C130

100U-6.3V_3528

100U-6.3V_3528

+3V +1.8VSUS

R401 *0_4R401 *0_4

R402

R402

*4.7K/F_4

*4.7K/F_4

5

1

2

U22

U22

3

*NC7SZ08P5X_NL

*NC7SZ08P5X_NL

R400 0_4R400 0_4

+1.8VSUS

C510 *.1U_4C510 *.1U_4

5

1

2

U24

U24

3

*NC7SZ08P5X_NL

*NC7SZ08P5X_NL

R223 0_4R223 0_4

+1.8VSUS

5

1

2

U23

U23

3

*NC7SZ08P5X_NL

*NC7SZ08P5X_NL

R220 0_4R220 0_4

EC_PROCHOT# (21)

MCP67_PROCHOT# (7)

C513 *.1U_4C513 *.1U_4

C512 *.1U_4C512 *.1U_4

C192

C192

.22U_4

.22U_4

HTCPU_PWRGD(7)

HTCPU_STOP#(7)

HTCPU_RST#(7)

MMBT3904

MMBT3904

L16 BLM18PG330SN1D_6L16 BLM18PG330SN1D_6

C128

C128

3300P_4

3300P_4

PWROK_EC(11,13,21)

+1.8V

R236

R236

330_4

330_4

Q14

Q14

2

13

R232

R232

*0_4

*0_4

CPU_VDDA_RUN

C137

C137

D D

4.7U_6

4.7U_6

C C

B B

+1.8VSUS

R231

R231

300_4

300_4

H_PROCHOT#

should have a 300-Ω (±5%) pulldown to VSS.

+1.8VSUS

CPU_ALL_PWROK

4

CPU_LDTSTOP#

4

CPU_HT_RESET#

4

CPU H/W MONITOR

KBSMDATCPU_TEST5_THERMDC

KBSMCLK

R244

R244

10K_4

10K_4

1

Q30 2N7002EQ30 2N7002E

+3V

+3V

10K_4

10K_4

R245

R245

2

To SB GPIO

3

To FAN

+3V

A A

R235 47/F_6R235 47/F_6

CPU_TEST4_THERMDA

10 mil trace /

10 mil space

15 MIL

3V_THM

C321

C321

.1U_4

.1U_4

C323

C323

2200P_4

2200P_4

Address 98H

U9 G781U9 G781

1

VCC

3

DXN

SMDATA

2

DXP

-OVT4GND

SMCLK

6

-ALT

7

8

5

5

4

R406 *300_4R406 *300_4

R404 *300_4R404 *300_4

R403 300_4R403 300_4

MCP67_THERMIP#(7)

+1.8VSUS

THERM_ALERT# (11)

CPUFAN#_ON (22)

4

PSI#

+1.8V

R233300_4 R233300_4

+1.8V +3V

R357

R357

10K_4

10K_4

2

1 3

Q29

Q29

MMBT3904

MMBT3904

R240 *330_4R240 *330_4

H_THERMTRIP#

+3V

R239

R239

4.7K_4

4.7K_4

1

+3V

R238

R238

4.7K_4

4.7K_4

CPU_SID_R

CPU_SIC_R

1

ATHLON Control and Debug

VLDT_RUN

COREFB+V(25)

3

C143 3900P_4C143 3900P_4

C154 3900P_4C154 3900P_4

PWR_PSI# (25)

+1.8V

R425

R425

330_4

330_4

*4.7K_4

*4.7K_4

Q16

Q16

2

MMBT3904

MMBT3904

1 3

MBDATA_CPU (21)

MBCLK_CPU (21)

R242

R242

CPU_CLK(7)

CPU_CLK#(7)

R349

R349

1K/F_4

1K/F_4

Q15

Q15

*MMBT3904

*MMBT3904

2

1 3

Q32

Q32

2

2N7002E

2N7002E

3

Q31

Q31

2

2N7002E

2N7002E

COREFB-(25)

R159

R159

169/F_6

169/F_6

R243

R243

*4.7K_4

*4.7K_4

THERM_SYS_PWR (24)

R226 44.2/F_4R226 44.2/F_4

R225 44.2/F_4R225 44.2/F_4

T32T32

T34T34

T12T12

T14T14

T26T26

T10T10

T91T91

PWROK_EC

3

CPU_VDDA_RUN

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_SIC_R

CPU_SID_R

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST5_THERMDC

CPU_TEST4_THERMDA

3

CPU_HTREF1

CPU_HTREF0

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

U21D

U21D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

AF4

SIC

AF5

SID

P6

HT_REF1

R6

HT_REF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

TEST5

W8

TEST4

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

MISC

MISC

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

TEST29_H

TEST29_L

TEST28_H

AMD NPT S1 SOCKET

Processor Socket

R409 *300_4R409 *300_4

R407 300_4R407 300_4

R234 1K/F_4R234 1K/F_4

R148 510/F_4R148 510/F_4

R405 300_4R405 300_4

R157 510/F_4R157 510/F_4

R185 300_4R185 300_4

R187 300_4R187 300_4

2

+1.8VSUS

H_THERMTRIP#

AF6

H_PROCHOT#

AC7

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

CPU_PRESENT#

PSI_L

DBREQ_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

TDO

AC6

A3

E10

AE9

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

+1.8VSUS

2

PSI#

PSI_L is a Power Status Indicator signal. This signal is asserted

when the processor is in a low powerstate. PSI_L should be

connected to the power supply controller, if the controller

supports “skipmode, or diode emulation mode”. PSI_L is asserted by

the processor during the C3 and S1 states.

CPU_DBREQ#

CPU_TDO

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

TEST29_L and TEST29_H differential pair should have an 80differential trace routed to a termination resistor. These

traces should be shorter than 1.5 inches. 6//4//6

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

+1.8VSUS

HTCPU_RST#

R411 220_4R411 220_4

R410 220_4R410 220_4

CPU_TRST#

R142

R142

300_4

300_4

R158 80.6/F_4R158 80.6/F_4

R408 220_4R408 220_4

R213 220_4R213 220_4

CPU_TCK

CPU_TMS

CPU_TDI

+1.8VSUS +3V

R339

R339

10K_4

10K_4

2

1 3

Q27

Q27

MMBT3904

MMBT3904

R147 220_4R147 220_4

CPU_DBRDY

1

H_VID5 (25)

H_VID4 (25)

H_VID3 (25)

H_VID2 (25)

H_VID1 (25)

H_VID0 (25)

T88T88

T87T87

T89T89

T90T90

HDT CONNECTOR

*ASP-68200-07-25P-LDV

*ASP-68200-07-25P-LDV

1

3

CPU_DBREQ#

CPU_TDO

R341

R341

1K/F_4

1K/F_4

H_HTCPU_RST#

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

T6T6

T29T29

T36T36

T33T33

T39T39

T37T37

T38T38

T5T5

ATHLON64 CTRL & DEBUG

ATHLON64 CTRL & DEBUG

ATHLON64 CTRL & DEBUG

5

7

9

11

13

15

17

+1.8VSUS

19

21

23

PROJECT : ZO3

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

1

CN6

CN6

GND1

RSVD1

RSVD0

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

TDO

VCC_PROC_IO_21

VCC_PROC_IO_23

KEY

KEY

HDTGND

RESET_L

430Wednesday, April 25, 2007

430Wednesday, April 25, 2007

430Wednesday, April 25, 2007

GND10

GND12

GND14

GND16

GND18

GND20

GND22

GND26

GND2

GND4

GND6

GND8

2

4

6

8

10

12

14

16

18

20

22

24

25

2A

2A

2A

of

of

of

A

www.kythuatvitinh.com

B

C

D

E

PROCESSOR POWER AND GROUND

4 4

U21F

VCC_CORE VCC_CORE

3 3

A1

2 2

A26

U21E

U21E

AC4

VDD1

AD2

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

VDD17

M6

VDD18

M8

VDD19

M10

VDD20

N7

VDD21

N9

VDD22

N11

VDD23

P8

VDD24

P10

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

R11

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

T10

VDD33

T12

VDD34

T14

VDD35

U7

VDD36

U9

VDD37

U11

VDD38

U13

VDD39

V6

VDD40

V8

VDD41

V10

VDD42

POWER

POWER

Athlon 64 S1

Processor Socket

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

+1.8VSUS

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

AMD S1g1

uPGA638

Top View

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

U21F

AA4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

AD6

VSS18

AD8

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

GROUND

GROUND

Athlon 64 S1

Processor Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+1.8VSUS

+1.8VSUS

C221

C221

4.7U_6

4.7U_6

C222

C222

22U-10V_8

22U-10V_8

VCC_CORE

C198

C205

C205

22U-10V_8

22U-10V_8

C212

C212

180P_4

180P_4

C198

22U-10V_8

22U-10V_8

C220

C220

22U-10V_8

22U-10V_8

VCC_CORE

C219

C219

22U-10V_8

22U-10V_8

C223

C223

.22U_4

.22U_4

C214

C214

22U-10V_8

22U-10V_8

C230

C230

.22U_4

.22U_4

C213

C213

22U-10V_8

22U-10V_8

C228

C228

.01U_4

.01U_4

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C229

C234

C234

4.7U_6

4.7U_6

C208

C208

22U-10V_8

22U-10V_8

C207

C207

4.7U_6

4.7U_6

C187

C187

.22U_4

.22U_4

C211

C211

4.7U_6

4.7U_6

C194

C194

.22U_4

.22U_4

C227

C227

.22U_4

.22U_4

C189

C189

.22U_4

.22U_4

C191

C191

.22U_4

.22U_4

C201

C201

.22U_4

.22U_4

C229

.01U_4

.01U_4

C204

C204

22U-10V_8

22U-10V_8

C217

C217

.01U_4

.01U_4

C218

C218

22U-10V_8

22U-10V_8

C243

C243

10P_4

10P_4

C216

C216

180P_4

180P_4

C215

C215

22U-10V_8

22U-10V_8

C244

C244

180P_4

180P_4

AF1

1 1

PROJECT : ZO3

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ATHLON64 PWR & GND

ATHLON64 PWR & GND

A

B

C

D

ATHLON64 PWR & GND

Date: Sheet

Date: Sheet of

Date: Sheet of

530Wednesday, April 25, 2007

530Wednesday, April 25, 2007

E

530Wednesday, April 25, 2007

1A

1A

1A

of

A

www.kythuatvitinh.com

B

C

D

E

A0

A1

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

A2

A3

A4

A5

A6

A7

A8

A9

REVERSE

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

(H=9.2)

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

59

+1.8VSUS

103

111

104

112

VDD8

VDD7

J4

J4

SO-DIMM

SO-DIMM

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

122

121

117

118

5

DQ0

7

DQ1

VDD9

17

DQ2

VDD10

VDD11

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

NC/TEST

196

VSS56

193

VSS55

190

VSS54

187

VSS53

184

VSS52

183

VSS51

178

VSS50

177

VSS49

172

VSS48

171

VSS47

168

VSS46

165

VSS45

162

VSS44

161

VSS43

156

VSS42

155

VSS41

150

VSS40

149

VSS39

145

VSS38

144

VSS37

139

VSS36

138

VSS35

133

VSS34

VSS33

VSS32

VSS31

VSS30

132

128

127

DDRII_SODIMM_R H9.2

DDRII_SODIMM_R H9.2

M_B_DQ4

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ5

M_B_DQ0

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ15

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ11

M_B_DQ16

M_B_DQ21

M_B_DQ19

M_B_DQ23

M_B_DQ20

M_B_DQ17

M_B_DQ18

M_B_DQ22

M_B_DQ29

M_B_DQ28

M_B_DQ26

M_B_DQ27

M_B_DQ24

M_B_DQ25

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ36

M_B_DQ39

M_B_DQ35

M_B_DQ33

M_B_DQ37

M_B_DQ34

M_B_DQ38M_A_DQ33

M_B_DQ40

M_B_DQ41

M_B_DQ46

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ47

M_B_DQ42

M_B_DQ53

M_B_DQ49

M_B_DQ55

M_B_DQ54

M_B_DQ48

M_B_DQ52

M_B_DQ50

M_B_DQ51

M_B_DQ60

M_B_DQ57

M_B_DQ62

M_B_DQ59

M_B_DQ61

M_B_DQ56

M_B_DQ63

M_B_DQ58

M_B_DQ[0..63] (3)

M_B_CS#2 (3)

M_B_CS#3 (3)

M_A_CS#2

M_CKE0

M_CKE2

M_B_CS#2

M_ODT0

M_A_A10

M_B_CS#0

M_ODT2

M_A_BS#1

M_A_A0

M_A_BS#2

M_A_CAS#

M_ODT1

M_A_RAS#

M_A_CS#0

M_A_CS#1

M_A_A13

M_A_CS#3

M_B_A2

M_B_BS#1

M_B_BS#2

M_B_WE#

M_B_CAS#

M_B_RAS#

M_B_CS#1

M_ODT3

M_B_CS#3

M_B_A13

M_A_BS#0

M_A_WE#

M_A_A2

M_A_A4

M_A_A6

M_A_A7

M_A_A11

M_A_A14

M_A_A12

M_A_A9

M_A_A3

M_A_A1

M_A_A8

M_A_A5

M_A_A15

M_CKE1

M_B_A0

M_B_A6

M_B_A4

M_B_A7

M_B_A11

M_B_A14

M_B_A3

M_B_A1

M_B_A8

M_B_A5

M_B_A12

M_B_A9

M_B_A10

M_B_BS#0

M_B_A15

M_CKE3

MSMB_DATA(11)

MSMB_CLK(11)

+SMDDR_VTERM +SMDDR_VTERM

RP6 47X2_4RP6 47X2_4

1 2

3 4

RP4

RP4

3 4

1 2

47X2_4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

3 4

1 2

1 2

3 4

1 2

3 4

1 2

3 4

3 4

1 2

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

3 4

1 2

3

R418 0_4R418 0_4

3

R417 0_4R417 0_4

+3V

+3V

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

47X2_4

2

2

RP23 47X2_4RP23 47X2_4

RP24 47X2_4RP24 47X2_4

RP19 47X2_4RP19 47X2_4

R218 47_4R218 47_4

RP27 47X2_4RP27 47X2_4

R221 47_4R221 47_4

R228 47_4R228 47_4

R227 47_4R227 47_4

RP26 47X2_4RP26 47X2_4

RP20 47X2_4RP20 47X2_4

R217 47_4R217 47_4

RP25 47X2_4RP25 47X2_4

R222 47_4R222 47_4

RP29 47X2_4RP29 47X2_4

RP28 47X2_4RP28 47X2_4

RP22 47X2_4RP22 47X2_4

RP17 47X2_4RP17 47X2_4

RP11 47X2_4RP11 47X2_4

RP7 47X2_4RP7 47X2_4

RP10 47X2_4RP10 47X2_4

RP18 47X2_4RP18 47X2_4

RP14 47X2_4RP14 47X2_4

RP5 47X2_4RP5 47X2_4

RP15

RP15

RP12

RP12

RP8

RP8

RP16

RP16

RP13

RP13

RP9

RP9

RP21

RP21

RP3

RP3

Q35

Q35

*2N7002E

*2N7002E

Q36

Q36

*2N7002E

*2N7002E

*10U-6.3V_8C322 *10U-6.3V_8C322

*10U-6.3V_8C314 *10U-6.3V_8C314

.1U_4C298 .1U_4C298

.1U_4C317 .1U_4C317

.1U_4C233 .1U_4C233

.1U_4C232 .1U_4C232

.1U_4C304 .1U_4C304

.1U_4C273 .1U_4C273

.1U_4C237 .1U_4C237

.1U_4C312 .1U_4C312

.1U_4C252 .1U_4C252

*.1U_4C272 *.1U_4C272

*.1U_4C318 *.1U_4C318

.1U_4C315 .1U_4C315

.1U_4C248 .1U_4C248

.1U_4C257 .1U_4C257

.1U_4C242 .1U_4C242

.1U_4C256 .1U_4C256

*.1U_4C236 *.1U_4C236

.1U_4C310 .1U_4C310

.1U_4C313 .1U_4C313

.1U_4C275 .1U_4C275

*.1U_4C264 *.1U_4C264

.1U_4C240 .1U_4C240

.1U_4C251 .1U_4C251

.1U_4C309 .1U_4C309

*.1U_4C281 *.1U_4C281

.1U_4C296 .1U_4C296

2

4

RP37

RP37

*4.7KX2_4

*4.7KX2_4

1

3

MEM_SMBDAT

1

MEM_SMBCLK

1

+1.8VSUS

+1.8VSUS

*10U-6.3V_8C293 *10U-6.3V_8C293

*10U-6.3V_8C238 *10U-6.3V_8C238

10U-6.3V_8C247 10U-6.3V_8C247

10U-6.3V_8C303 10U-6.3V_8C303

.1U_4C305 .1U_4C305

.1U_4C307 .1U_4C307

.1U_4C258 .1U_4C258

.1U_4C266 .1U_4C266

.1U_4C316 .1U_4C316

.1U_4C259 .1U_4C259

.1U_4C271 .1U_4C271

.1U_4C311 .1U_4C311

.1U_4C253 .1U_4C253

.1U_4C270 .1U_4C270

.1U_4C274 .1U_4C274

.1U_4C269 .1U_4C269

.1U_4C250 .1U_4C250

.1U_4C260 .1U_4C260

.1U_4C245 .1U_4C245

.1U_4C280 .1U_4C280

.1U_4C299 .1U_4C299

.1U_4C255 .1U_4C255

.1U_4C265 .1U_4C265

.1U_4C278 .1U_4C278

+SMDDR_VTERM

.1U_4C268 .1U_4C268

.1U_4C277 .1U_4C277

.1U_4C319 .1U_4C319

.1U_4C306 .1U_4C306

.1U_4C235 .1U_4C235

.1U_4C308 .1U_4C308

.1U_4C249 .1U_4C249

.1U_4C246 .1U_4C246

.1U_4C276 .1U_4C276

.1U_4C263 .1U_4C263

.1U_4C279 .1U_4C279

.1U_4C262 .1U_4C262

+1.8VSUS

103

111

104

112

117

118

5

DQ0

7

DQ1

VDD8

VDD7

VDD9

17

DQ2

VDD10

VDD11

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

NC/TEST

SO-DIMM

SO-DIMM

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

121

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

132

128

127

122

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

DDRII_SODIMM_R H5.2

DDRII_SODIMM_R H5.2

M_A_DQ1

M_A_DQ5

M_A_DQ2

M_A_DQ3

M_A_DQ0

M_A_DQ4

M_A_DQ7

M_A_DQ6

M_A_DQ12

M_A_DQ8

M_A_DQ10

M_A_DQ14

M_A_DQ13

M_A_DQ9

M_A_DQ15

M_A_DQ11

M_A_DQ21

M_A_DQ17

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ19

M_A_DQ22

M_A_DQ16

M_A_DQ29

M_A_DQ28

M_A_DQ31

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ27

M_A_DQ30

M_A_DQ38

M_A_DQ36

M_A_DQ35

M_A_DQ37

M_A_DQ32

M_A_DQ34

M_A_DQ39

M_A_DQ45

M_A_DQ44

M_A_DQ42

M_A_DQ46

M_A_DQ41

M_A_DQ40

M_A_DQ43

M_A_DQ47

M_A_DQ55

M_A_DQ54

M_A_DQ50

M_A_DQ51

M_A_DQ53

M_A_DQ48

M_A_DQ49

M_A_DQ52

M_A_DQ56

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ61

M_A_DQ63

M_A_DQ62

M_A_CS#2 (3)

M_A_CS#3 (3)

+SMDDR_VREF

M_A_DQ[0..63] (3)

+1.8VSUS

R153

R153

*0_4

*0_4

MVREF_DIM

C151

C151

1U_4

1U_4

+3V

M_A_A[0..15](3)

M_A_BS#0(3)

M_A_BS#1(3)

M_A_BS#2(3)

M_A_DM[0..7](3)

M_A_DQS[0..7](3)

M_A_DQS#[0..7](3)

C150 .1U_4C150 .1U_4

M_CLKOUT0(3)

M_CLKOUT0#(3)

M_CLKOUT1(3)

M_CLKOUT1#(3)

M_A_RAS#(3)

M_A_CAS#(3)

M_A_WE#(3)

M_A_CS#0(3)

M_A_CS#1(3)

MVREF_DIM

C149

C149

2.2U_8

2.2U_8

1 2

M_CKE0(3)

M_CKE1(3)

M_ODT0(3)

M_ODT1(3)

C522 .1U_4C522 .1U_4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

MEM_SMBDAT

MEM_SMBCLK

C160

C160

.1U_4

.1U_4

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

A0

A1

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

(H=5.2)

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

59

J3

J3

REVERSE

4 4

3 3

2 2

+1.8VSUS

1 1

M_B_A[0..15](3)

M_B_DM[0..7](3)

M_B_DQS[0..7](3)

M_B_DQS#[0..7](3)

C146 .1U_4C146 .1U_4

+1.8VSUS

M_B_BS#0(3)

M_B_BS#1(3)

M_B_BS#2(3)

+3V

R150

R150

1K/F_4

1K/F_4

R152

R152

1K/F_4

1K/F_4

M_CLKOUT3(3)

M_CLKOUT3#(3)

M_CLKOUT4(3)

M_CLKOUT4#(3)

M_CKE2(3)

M_CKE3(3)

M_B_RAS#(3)

M_B_CAS#(3)

M_B_WE#(3)

M_B_CS#0(3)

M_B_CS#1(3)

M_ODT2(3)

M_ODT3(3)

+3V

C144

C144

2.2U_8

2.2U_8

1 2

R414 10K_4R414 10K_4

R415 0_4R415 0_4

MEM_SMBDAT

MEM_SMBCLK

C520 .1U_4C520 .1U_4

MVREF_DIM

C161

C161

.1U_4

.1U_4

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15M_A_A13

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DDR-II SODIMM*2

DDR-II SODIMM*2

A

B

C

D

DDR-II SODIMM*2

Date: Sheet

Date: Sheet of

Date: Sheet of

PROJECT : ZO3

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

of

630Wednesday, April 25, 2007

630Wednesday, April 25, 2007

E

630Wednesday, April 25, 2007

1A

1A

1A

5

www.kythuatvitinh.com

MCP67 Used UMA Only

D D

MCP67 Signal Name

RGB_DAC_RSET

RGB_DAC_VREF

DDC_DATA0

TV_DAC_RSET

TV_DAC_VREF

IFPAB_RST

IFPAB_VPROBE

DDC_DATA2

HPLUG_DET3

HDMI_RSET

HDMI_VPROBE

DDC_DATA3_R

HDCP_ROM_SDATA

HPLUG_DET2_R

Component

STUFF

STUFF

*10K LEAVE NC

STUFF

STUFF

STUFF

STUFF

*10K LEAVE NC

22K PULLDOWN

STUFF

STUFF

10K PULLHIGH

10K PULLHIGH

6.2K PULLDOWN

MCP67 Unused UMA Only

MCP67 Signal Name

RGB_DAC_RSET

RGB_DAC_VREF

C C

DDC_DATA0

TV_DAC_RSET

TV_DAC_VREF

IFPAB_RST

IFPAB_VPROBE

DDC_DATA2

HPLUG_DET3

HDMI_RSET

HDMI_VPROBE

DDC_DATA3_R

HDCP_ROM_SDATA

HPLUG_DET2_R

Component

STUFF

STUFF

10K PULLHIGH

STUFF

STUFF

STUFF

STUFF

10K PULLHIGH

22K PULLDOWN

STUFF

STUFF

10K PULLHIGH

10K PULLHIGH

6.2K PULLDOWN

+1.2V_HT

FOR UMA ONLY

R344 IV@150_4R344 IV@150_4

R343 IV@150_4R343 IV@150_4 R131 124/F_4R131 124/F_4

B B

R342 IV@150_4R342 IV@150_4

R117 IV@150_4R117 IV@150_4

R120 IV@150_4R120 IV@150_4

R113 IV@150_4R113 IV@150_4

B2B: changed CAP value

R164 EV@2.2K_4R164 EV@2.2K_4

+3V

R95 EV@2.2K_4R95 EV@2.2K_4

+3V

C3A: Remove C426,R332 for Nvidia suggest.

A A

5

INT_CRT_RED

INT_CRT_GRN

INT_CRT_BLU

INT_TV_C/R

INT_TV_Y/G

INT_TV_COMP

1 2

C480 IV@27P_4C480 IV@27P_4

IV@27MHZ

IV@27MHZ

1 2

C483 IV@27P_4C483 IV@27P_4

INT_CRT_DDCDAT

INT_LVDS_EDIDDATA

Y5

Y5

+3V

T62T62

T60T60

T61T61

T55T55

T57T57

T59T59

T53T53

T58T58

4

HT_TXD[15..0](2)

HT_TXD#[15..0](2)

HT_CPU_DWNCLK0(2)

HT_CPU_DWNCLK#0(2)

HT_CPU_DWNCLK1(2)

HT_CPU_DWNCLK#1(2)

HT_CPU_DWNCTL0(2)

HT_CPU_DWNCTL#0(2)

MCP67_THERMIP#(4)

MCP67_PROCHOT#(4)

R351 150/F_4R351 150/F_4

R354 150/F_4R354 150/F_4

INT_CRT_RED(14)

INT_CRT_GRN(14)

INT_CRT_BLU(14)

INT_HSYNC(14)

INT_VSYNC(14)

C125 .01U_4C125 .01U_4

INT_CRT_DDCCLK(14)

INT_CRT_DDCDAT(14)

INT_TV_C/R(14)

INT_TV_Y/G(14)

INT_TV_COMP(14)

R119 124/F_4R119 124/F_4

C116 .01U_4C116 .01U_4

R114 *10K_4R114 *10K_4

R335 10K_4R335 10K_4

R102 *10K_4R102 *10K_4

R103 10K_4R103 10K_4

R333 6.2K_4R333 6.2K_4

C426 *.1U_4C426 *.1U_4

R332 *1K/F_4R332 *1K/F_4

UNUSED HDMI ONLY

4

HT_TXD0

HT_TXD1

HT_TXD2

HT_TXD3

HT_TXD4

HT_TXD5

HT_TXD6

HT_TXD7

HT_TXD8

HT_TXD9

HT_TXD10

HT_TXD11

HT_TXD12

HT_TXD13

HT_TXD14

HT_TXD15

HT_TXD#0

HT_TXD#1

HT_TXD#2

HT_TXD#3

HT_TXD#4

HT_TXD#5

HT_TXD#6

HT_TXD#7

HT_TXD#8

HT_TXD#9

HT_TXD#10

HT_TXD#11

HT_TXD#12

HT_TXD#13

HT_TXD#14

HT_TXD#15

MCP67_THERMIP#

MCP67_PROCHOT#

CPU_CAL_1P2V

CPU_CAL_GND

RGB_DAC_RSET

RGB_DAC_VREF

TV_DAC_RSET

TV_DAC_VREF

TV_XTALIN

TV_XTALOUT

HDCP_ROM_SCLK

HDCP_ROM_SDATA

DDC_CLK3_R

DDC_DATA3_R

HPLUG_DET2_R

HDMI_VPROBE

HDMI_RSET

HDMI_TXC_P_R

HDMI_TXC_N_R

HDMI_TXD0_P_R

HDMI_TXD0_N_R

HDMI_TXD1_P_R

HDMI_TXD1_N_R

HDMI_TXD2_P_R

HDMI_TXD2_N_R

U20A

U20A

AF16

HT_MCP_RXD0_P

AH16

HT_MCP_RXD1_P

AJ15

HT_MCP_RXD2_P

AK16

HT_MCP_RXD3_P

AG17

HT_MCP_RXD4_P

AL17

HT_MCP_RXD5_P

AL18

HT_MCP_RXD6_P

AJ19

HT_MCP_RXD7_P

AD14

HT_MCP_RXD8_P

AF14

HT_MCP_RXD9_P

AH14

HT_MCP_RXD10_P

AL13

HT_MCP_RXD11_P

AC15

HT_MCP_RXD12_P

AD16

HT_MCP_RXD13_P

AE17

HT_MCP_RXD14_P

AB17

HT_MCP_RXD15_P

AG16

HT_MCP_RXD0_N

AJ16

HT_MCP_RXD1_N

AK15

HT_MCP_RXD2_N

AL16

HT_MCP_RXD3_N

AF17

HT_MCP_RXD4_N

AK17

HT_MCP_RXD5_N

AK18

HT_MCP_RXD6_N

AK19

HT_MCP_RXD7_N

AE14

HT_MCP_RXD8_N

AG14

HT_MCP_RXD9_N

AJ14

HT_MCP_RXD10_N

AK13

HT_MCP_RXD11_N

AD15

HT_MCP_RXD12_N

AE16

HT_MCP_RXD13_N

AD17

HT_MCP_RXD14_N

AC17

HT_MCP_RXD15_N

AJ17

HT_MCP_RX_CLK0_P

AH17

HT_MCP_RX_CLK0_N

AL14

HT_MCP_RX_CLK1_P

AK14

HT_MCP_RX_CLK1_N

AH19

HT_MCP_RXCTL0_P

AG19

HT_MCP_RXCTL0_N

AC18

HT_MCP_RXCTL1_P

AD18

HT_MCP_RXCTL1_N

AC13

THERMTRIP#/GPIO_58(3V)

AB13

PROCHOT#/GPIO_20(3V_S5)

AM12

HT_MCP_COMP_VDD

AL12

HT_MCP_COMP_GND

B21

RGB_DAC_RED

C21

RGB_DAC_GREEN

B22

RGB_DAC_BLUE

G21

RGB_DAC_HSYNC

H21

RGB_DAC_VSYNC

K21

RGB_DAC_RSET

D21

RGB_DAC_VREF

G8

DDC_CLK0

H8

DDC_DATA0

C23

TV_DAC_RED

C22

TV_DAC_GREEN

D23

TV_DAC_BLUE

E23

TV_DAC_RSET

H22

TV_DAC_VREF

E17

TV_XTALIN

F17

TV_XTALOUT

AD25

HDCP_ROM_SCLK

AC26

HDCP_ROM_SDATA

L22

DDC_CLK3

K22

DDC_DATA3

AL32

HPLUG_DET2

AK32

HDMI_VPROBE

AK31

HDMI_RSET

AL29

HDMI_TXC_P

AM29

HDMI_TXC_N

AK29

HDMI_TXD0_P

AJ29

HDMI_TXD0_N

AM30

HDMI_TXD1_P

AL30

HDMI_TXD1_N

AK30

HDMI_TXD2_P

AJ30

HDMI_TXD2_N

MCP67

MCP67

3

A1:AJMCP670T00

A2:AJMCP670T04

MCP67

MCP67

1 OF 7

1 OF 7

HT

HT

DACS

DACS

FLAT PANEL

FLAT PANEL

GPIO_6(3V_S5)/FERR/SYS_SERR/IGPU_GPIO_6*

GPIO_7(3V_S5)/NFERR/SYS_PERR/IGPU_GPIO_7*

3

HT_MCP_TXD0_P

HT_MCP_TXD1_P

HT_MCP_TXD2_P

HT_MCP_TXD3_P

HT_MCP_TXD4_P

HT_MCP_TXD5_P

HT_MCP_TXD6_P

HT_MCP_TXD7_P

HT_MCP_TXD8_P

HT_MCP_TXD9_P

HT_MCP_TXD10_P

HT_MCP_TXD11_P

HT_MCP_TXD12_P

HT_MCP_TXD13_P

HT_MCP_TXD14_P

HT_MCP_TXD15_P

HT_MCP_TXD0_N

HT_MCP_TXD1_N

HT_MCP_TXD2_N

HT_MCP_TXD3_N

HT_MCP_TXD4_N

HT_MCP_TXD5_N

HT_MCP_TXD6_N

HT_MCP_TXD7_N

HT_MCP_TXD8_N

HT_MCP_TXD9_N

HT_MCP_TXD10_N

HT_MCP_TXD11_N

HT_MCP_TXD12_N

HT_MCP_TXD13_N

HT_MCP_TXD14_N

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL0_P

HT_MCP_TXCTL0_N

HT_MCP_TXCTL1_P

HT_MCP_TXCTL1_N

CLKOUT_200MHZ_P

CLKOUT_200MHZ_N

HT_MCP_REQ#

HT_MCP_STOP#

HT_MCP_RST#

HT_MCP_PWRGD

CPU_SBVREF

CLK200_TERM_GND

IFPA_TXC_P

IFPA_TXC_N

IFPA_TXD0_P

IFPA_TXD0_N

IFPA_TXD1_P

IFPA_TXD1_N

IFPA_TXD2_P

IFPA_TXD2_N

IFPA_TXD3_P

IFPA_TXD3_N

IFPB_TXC_P

IFPB_TXC_N

IFPB_TXD4_P

IFPB_TXD4_N

IFPB_TXD5_P

IFPB_TXD5_N

IFPB_TXD6_P

IFPB_TXD6_N

IFPB_TXD7_P

IFPB_TXD7_N

IFPAB_VPROBE

IFPAB_RSET

DDC_CLK2

DDC_DATA2

LCD_PANEL_PWR

LCD_BKL_ON

LCD_BKL_CTL

HPLUG_DET3

HT_RXD0

AK27

HT_RXD1

AK26

HT_RXD2

AK25

HT_RXD3

AL24

HT_RXD4

AK22

HT_RXD5

AK21

HT_RXD6

AH21

HT_RXD7

AL20

HT_RXD8

AG27

HT_RXD9

AF25

HT_RXD10

AH25

HT_RXD11

AE23

HT_RXD12

AD21

HT_RXD13

AF21

HT_RXD14

AC20

HT_RXD15

AE19

HT_RXD#0

AJ27

HT_RXD#1

AL26

HT_RXD#2

AL25

HT_RXD#3

AK24

HT_RXD#4

AL22

HT_RXD#5

AL21

HT_RXD#6

AJ21

HT_RXD#7

AM20

HT_RXD#8

AH27

HT_RXD#9

AG25

HT_RXD#10

AJ25

HT_RXD#11

AF23

HT_RXD#12

AE21

HT_RXD#13

AG21

HT_RXD#14

AD20

HT_RXD#15

AF19

AK23

AJ23

AG23

AH23

AK20

AJ20

AD19

AC19

AL28

AM28

HTCPU_REQ#

AD23

AB20

AC21

AD22

AG28

AJ28

AE30

AE31

AC30

AC29

AC27

AC28

AD30

AD29

AD31

AD32

AJ31

AJ32

AE28

AE29

AF30

AF31

AG30

AG29

AH31

AH30

AB30

AB31

L21

J22

AE27

AE25

AD24

U11

T11

AE26

CPU_SBVREF

MCP67_CTERM

INT_TXLOUT3+

INT_TXLOUT3-

IFPAB_VPROBE

IFPAB_RST

MCP67_GPIO6

MCP67_GPIO7

HPLUG_DET3

R336 0_6R336 0_6

C90 .1U_4C90 .1U_4

R110 2.37K/F_4R110 2.37K/F_4

C3A: Remove C77,R331 for Nvidia suggest.

C77 *.01U_4C77 *.01U_4

R331 *1K/F_4R331 *1K/F_4

R168 *8.2K_4R168 *8.2K_4

R139 *8.2K_4R139 *8.2K_4

R109 22K_4R109 22K_4

FOR DVI IS NOT IMPLEMENTED

2

HT_RXD[15..0] (2)

HT_RXD#[15..0] (2)

HT_CPU_UPCLK0 (2)

HT_CPU_UPCLK#0 (2)

HT_CPU_UPCLK1 (2)

HT_CPU_UPCLK#1 (2)

HT_CPU_UPCTL0 (2)

HT_CPU_UPCTL#0 (2)

CPU_CLK (4)

CPU_CLK# (4)

HTCPU_STOP# (4)

HTCPU_RST# (4)

HTCPU_PWRGD (4)

INT_TXLCLKOUT+ (14)

INT_TXLCLKOUT- (14)

INT_TXLOUT0+ (14)

INT_TXLOUT0- (14)

INT_TXLOUT1+ (14)

INT_TXLOUT1- (14)

INT_TXLOUT2+ (14)

INT_TXLOUT2- (14)

INT_LVDS_EDIDCLK (14)

INT_LVDS_EDIDDATA (14)

INT_LVDS_DIGON (14)

INT_LVDS_BLON (16)

L_BKLT_CTRL (14)

+1.2V_HT

T54T54

T56T56

+3V

+3V

2

1

HTCPU_REQ#

MCP67_THERMIP#

Datasheet error its should be +1.8 plane

MCP67_THERMIP#

HTCPU_STOP#

HTCPU_RST#

HTCPU_PWRGD

MCP67_PROCHOT#

R337 22K_4R337 22K_4

R355 *300_4R355 *300_4

R352 300_4R352 300_4

R350 300_4R350 300_4

R348 300_4R348 300_4

R338 300_4R338 300_4

R356 300_4R356 300_4

[LVDS]

FOR UMA ONLY

B2A: Remove R168,R139

PROJECT : ZO3

PROJECT : ZO3

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

MCP67(HT/VGA/FLAT_PANEL)

MCP67(HT/VGA/FLAT_PANEL)

MCP67(HT/VGA/FLAT_PANEL)

Date: Sheet

Date: Sheet of

Date: Sheet of

1

+3V

+1.8VSUS

730Wednesday, April 25, 2007

730Wednesday, April 25, 2007

730Wednesday, April 25, 2007

+3V

1A

1A

1A

of

5

www.kythuatvitinh.com

D D

C C

[MXM]

[NEW CARD]

NEW_CLKREQ#(17)

PEG_RXP[15:0](13) PEG_TXP[15:0] (13)

PEG_RXN[15:0](13)

CLK_MXM(13)

CLK_MXM#(13)

PCIE_RXP3(17)

PCIE_RXN3(17)

CPPE#(17)

R74 22_4R74 22_4

R73 22_4R73 22_4

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PE0_REFCLK_P

PE0_REFCLK_N

NEW_CLKREQ#

CPPE#

[TV]

PCIE_RXP1(17) PCIE_TXP1 (17)

[MINI CARD]

B B

PCIE_RXN1(17)

MINI_CLKREQ1#(17)

MINI_CLKREQ1#

D3B:PIN U24 GO GND DIRECTLY

4

U20B

U20B

F23

F24

D25

C28

C29

D29

F26

F28

H23

H25

H27

K24

K27

K28

J31

K31

G23

F25

D26

D28

C30

D30

F27

F29

H24

H26

H28

K25

K26

K29

J30

K30

R29

R30

L29

L30

W27

W28

M26

M27

U26

U27

N23

N22

U25

U24

N30

N31

R22

U23

P31

P30

T22

V31

P26

P27

U22

V30

MCP67

MCP67

PE0_RX0_P

PE0_RX1_P

PE0_RX2_P

PE0_RX3_P

PE0_RX4_P

PE0_RX5_P

PE0_RX6_P

PE0_RX7_P

PE0_RX8_P

PE0_RX9_P

PE0_RX10_P

PE0_RX11_P

PE0_RX12_P

PE0_RX13_P

PE0_RX14_P

PE0_RX15_P

PE0_RX0_N

PE0_RX1_N

PE0_RX2_N

PE0_RX3_N

PE0_RX4_N

PE0_RX5_N

PE0_RX6_N

PE0_RX7_N

PE0_RX8_N

PE0_RX9_N

PE0_RX10_N

PE0_RX11_N

PE0_RX12_N

PE0_RX13_N

PE0_RX14_N

PE0_RX15_N

PE0_REFCLK_P

PE0_REFCLK_N

PE1_RX_P

PE1_RX_N

PEA_CLKREQ#

PEA_PRSNT#

PE2_RX_P

PE2_RX_N

PEB_CLKREQ#

PEB_PRSNT#

PE3_RX_P

PE3_RX_N

PEC_CLKREQ#

PEC_PRSNT#

PE4_RX_P

PE4_RX_N

PED_CLKREQ#/GPIO_16(3V)

PED_PRSNT#

PE5_RX_P

PE5_RX_N

PEE_CLKREQ#/GPIO_17(3V)

PEE_PRSNT#

PE6_RX_P

PE6_RX_N

PEF_CLKREQ#/GPIO_18(3V)

PEF_PRSNT#

MCP67

MCP67

2 OF 7

2 OF 7

PCIE

PCIE

PE0_PRSNTX4#/DDC_DATA1

PE0_TX0_P

PE0_TX1_P

PE0_TX2_P

PE0_TX3_P

PE0_TX4_P

PE0_TX5_P

PE0_TX6_P

PE0_TX7_P

PE0_TX8_P

PE0_TX9_P

PE0_TX10_P

PE0_TX11_P

PE0_TX12_P

PE0_TX13_P

PE0_TX14_P

PE0_TX15_P

PE0_TX0_N

PE0_TX1_N

PE0_TX2_N

PE0_TX3_N

PE0_TX4_N

PE0_TX5_N

PE0_TX6_N

PE0_TX7_N

PE0_TX8_N

PE0_TX9_N

PE0_TX10_N

PE0_TX11_N

PE0_TX12_N

PE0_TX13_N

PE0_TX14_N

PE0_TX15_N

PE0_PRSNTX1#/DDC_CLK1

PE0_PRSNTX8#/EXP_EN

PE0_PRSNTX16#

PE1_TX_P

PE1_TX_N

PE1_REFCLK_P

PE1_REFCLK_N

PE2_TX_P

PE2_TX_N

PE2_REFCLK_P

PE2_REFCLK_N

PE3_TX_P

PE3_TX_N

PE3_REFCLK_P

PE3_REFCLK_N

PE4_TX_P

PE4_TX_N

PE4_REFCLK_P

PE4_REFCLK_N

PE5_TX_P

PE5_TX_N

PE5_REFCLK_P

PE5_REFCLK_N

PE6_TX_P

PE6_TX_N

PE6_REFCLK_P

PE6_REFCLK_N

PE_RST#

PE_RST1#

PE_CLK_COMP

3

C_PEG_TXP0

D24

C_PEG_TXP1

A24

C_PEG_TXP2

B25

C_PEG_TXP3

B26

C27

C_PEG_TXP5

A28

C_PEG_TXP6

A29

C_PEG_TXP7

A30

B31

C_PEG_TXP9PEG_RXP9

C31

C_PEG_TXP10

D31

C_PEG_TXP11

E31

C_PEG_TXP12

F31

C_PEG_TXP13

G29

C_PEG_TXP14

H29

C_PEG_TXP15

H32

C_PEG_TXN0

C24

C_PEG_TXN1

B24

C_PEG_TXN2

C25

C_PEG_TXN3

C26

C_PEG_TXN4

D27

C_PEG_TXN5

B28

B29

C_PEG_TXN7

B30

C_PEG_TXN8

B32

C_PEG_TXN9

C32

C_PEG_TXN10

D32

C_PEG_TXN11

E30

C_PEG_TXN12

F30

C_PEG_TXN13

G30

C_PEG_TXN14

H30

C_PEG_TXN15

H31

PE0_PRSNTX1

U31

PE0_PRSNTX4

U30

PE0_PRSNTX8

U29

PE0_PRSNTX16

U28

PCIE_TXP3_C

M28

PCIE_TXN3_C

M29

CLK_PCIE_NEW_C_R

T32

CLK_PCIE_NEW_C#_R

T31

M24

M25

T29

T30

PCIE_TXP1_C

M22

PCIE_TXN1_C

M23

CLK_PCIE_MINI1_R

T27

CLK_PCIE_MINI1#_R

T28

M30

M31

T25

T26

P29

P28

T23

T24

P24

P25

P23

R23

W30

W29

PE_COMP

V24

<500mil

C473 .1U_4C473 .1U_4

C468 .1U_4C468 .1U_4

C464 .1U_4C464 .1U_4

C461 .1U_4C461 .1U_4

C458 .1U_4C458 .1U_4

C456 .1U_4C456 .1U_4

C452 .1U_4C452 .1U_4

C450 .1U_4C450 .1U_4

C437 .1U_4C437 .1U_4

C439 .1U_4C439 .1U_4

C420 .1U_4C420 .1U_4

C441 .1U_4C441 .1U_4

C422 .1U_4C422 .1U_4

C433 .1U_4C433 .1U_4

C424 .1U_4C424 .1U_4

C435 .1U_4C435 .1U_4

C469 .1U_4C469 .1U_4

C465 .1U_4C465 .1U_4

C462 .1U_4C462 .1U_4

C459 .1U_4C459 .1U_4

C457 .1U_4C457 .1U_4

C454 .1U_4C454 .1U_4

C449 .1U_4C449 .1U_4

C447 .1U_4C447 .1U_4

C438 .1U_4C438 .1U_4

C440 .1U_4C440 .1U_4

C421 .1U_4C421 .1U_4

C442 .1U_4C442 .1U_4

C423 .1U_4C423 .1U_4

C434 .1U_4C434 .1U_4

C425 .1U_4C425 .1U_4

C436 .1U_4C436 .1U_4

R116 *2.37K/F_4R116 *2.37K/F_4

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4C_PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8C_PEG_TXP8PEG_RXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

PEG_TXN0PEG_RXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6C_PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

R91 *10K_4R91 *10K_4

R90 *10K_4R90 *10K_4

R99 *10K_4R99 *10K_4

R61 *10K_4R61 *10K_4

R66 *0_4R66 *0_4

C85 .1U_4C85 .1U_4

C84 .1U_4C84 .1U_4

R82 22_4R82 22_4

R86 22_4R86 22_4

C80 .1U_4C80 .1U_4

C79 .1U_4C79 .1U_4

R75 22_4R75 22_4

R76 22_4R76 22_4

PCIE_RST# (13)

Add 0R resistor, The resistor should only be

R334

R334

stuffed for MCP67D

*0_4

*0_4

PCIE_RST1# (17)

PEG_TXN[15:0] (13)

PE0_PRSNTX16

PE0_PRSNTX1#

PE0_PRSNTX4#

+3V

PE0_PRSNTX8#

Internal Pull-up

PCIE_TXP3 (17)

PCIE_TXN3 (17)

CLK_PCIE_NEW_C (17)

CLK_PCIE_NEW_C# (17)

PCIE_TXN1 (17)

CLK_PCIE_MINI1 (17)

CLK_PCIE_MINI1# (17)

C3A: Remove R116 for Nvidia suggest.

2

[NEW CARD]

[MINI CARD]