Page 1

5

4

3

2

1

VER :

D D

C C

B B

BOM P/N

1A

Ca

Description

X'

14.318MHz

rdreader

TAL

P31

DDRIII-SO

DIMM1

DDRIII-SODIMM2

SLG8LV595

CL

OCK

GENERATOR

SAT

SATA -

USB Po

rt

USB/B Co

n.

(USB Port x2)

B

luetooth Con.

U6437-GBL

A

ardreader control

C

P14,15

A - HDD

ODD

P33

P33

P33

P31

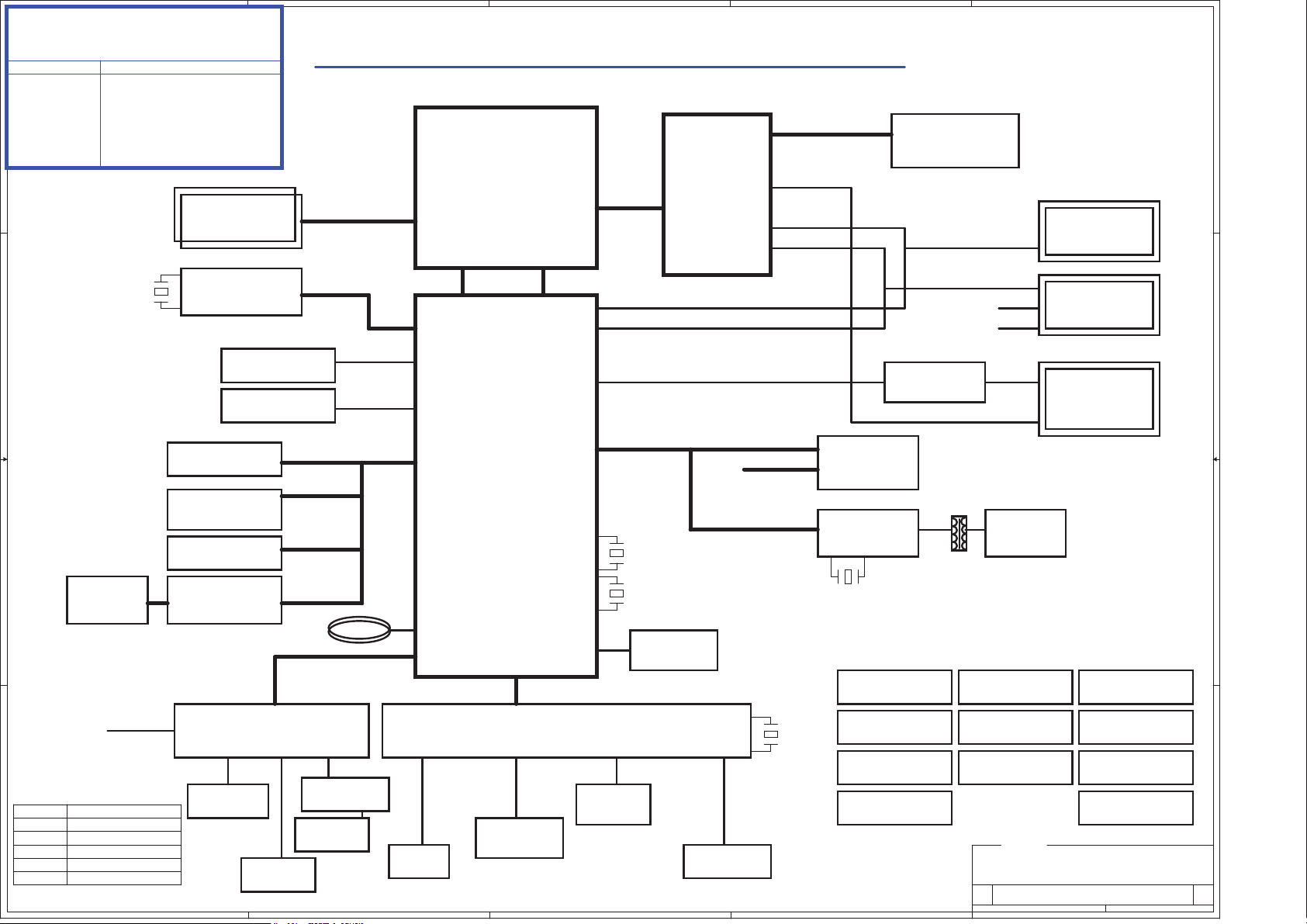

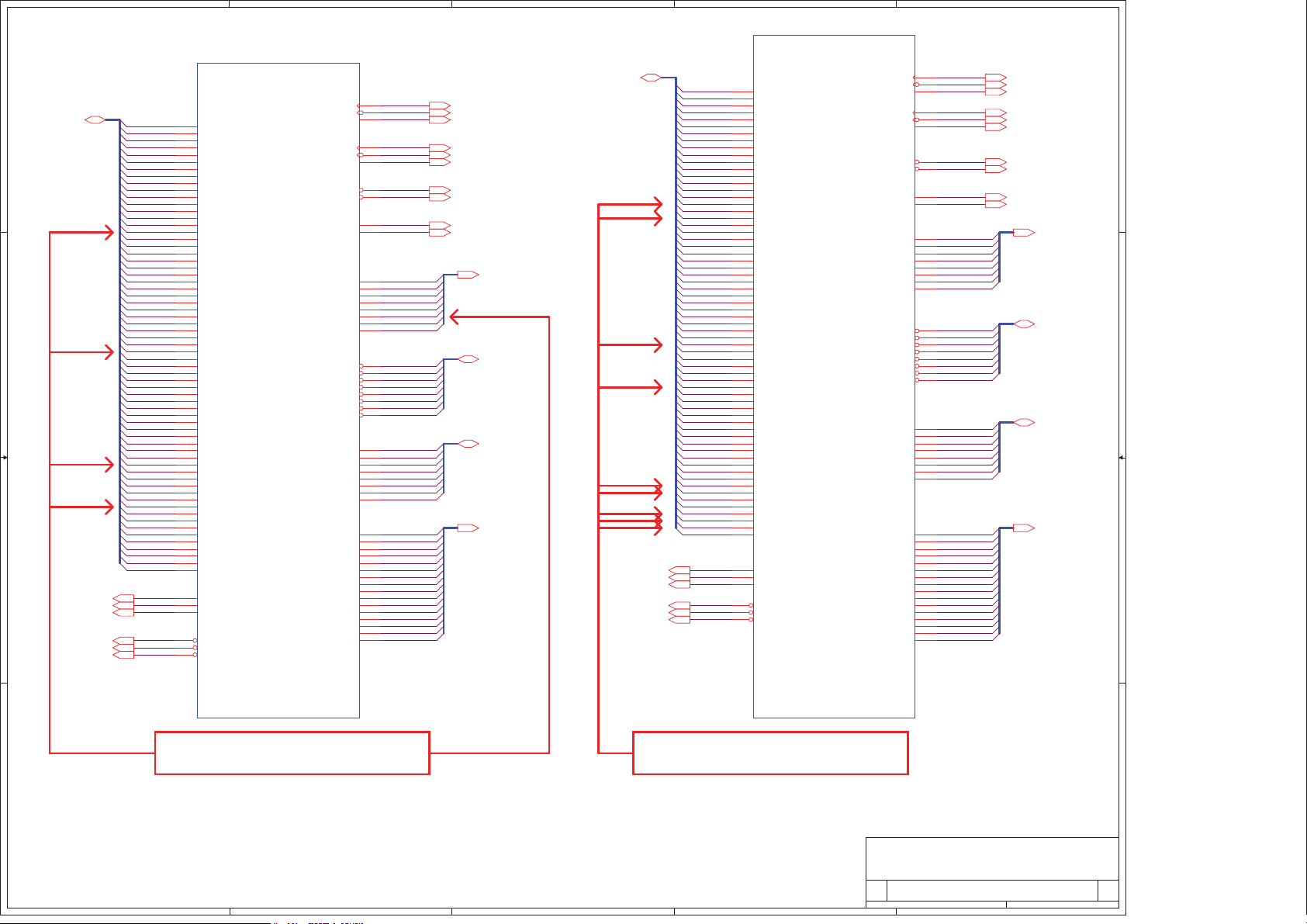

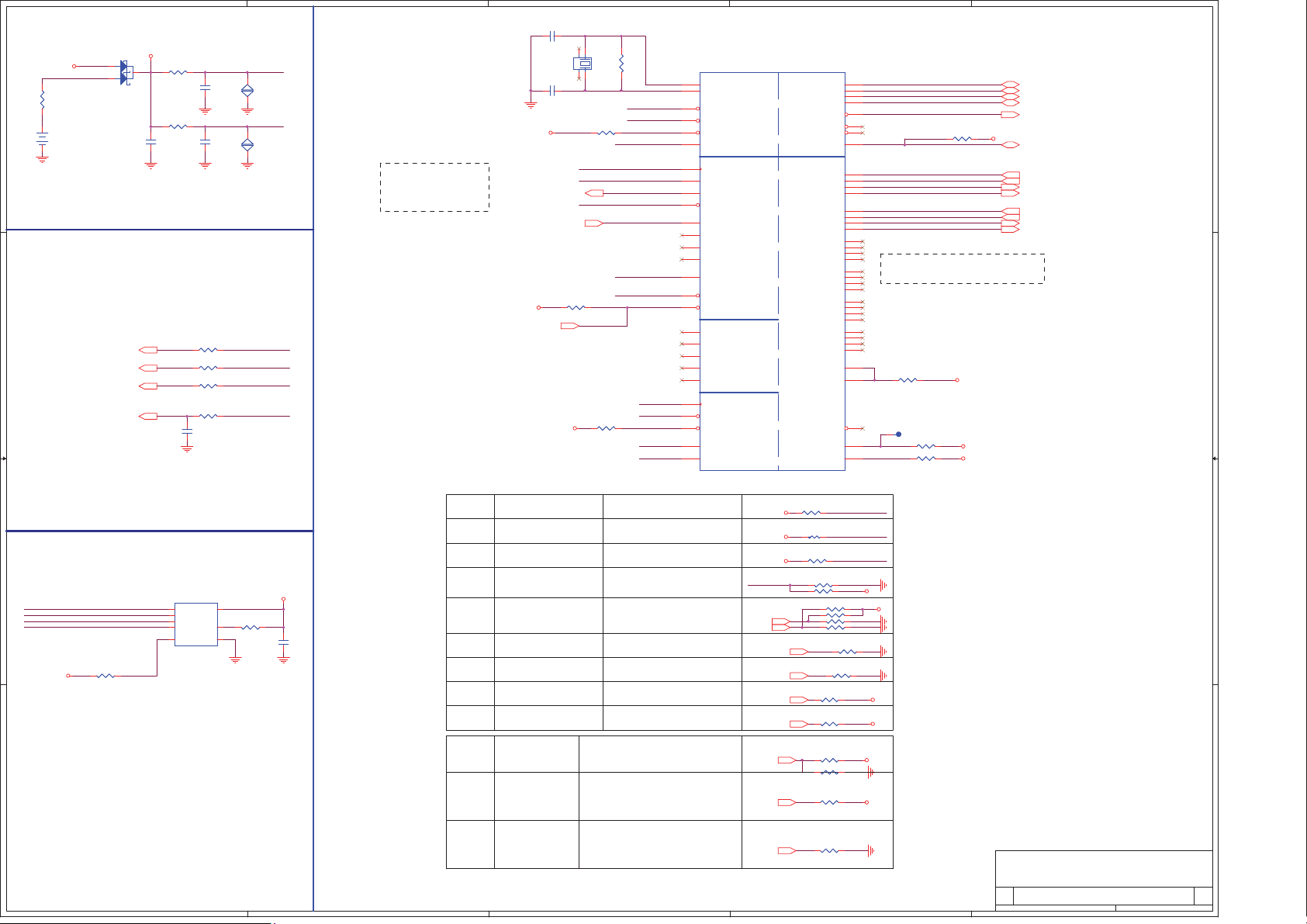

=4+6<67(0%/2&.',$*5$0

Dual Channel DDR I

800/1066 M

P3

P28

P28

U

SB-1

U

SB-3/9/11

U

SB-4

SB-12

U

P9

BAT

Az

alia

HZ

SATA 0

SATA 1

TERY

C

hannel B

A

rrandale

r

PGA 989

II

CL

SAT

USB

P4, 5, 6, 7

FDI

FDI

K

A

Ibex Peak-M

DM

DMI

I

MI(x4)

D

PC

D

GFXIMC

isplay

I-E x1

PCI

INT_CRT

I

NT_LVDS

NT_HDMI

I

-E x16

A

TI-Park

V

RAM DDRIII

512MB

P16, 17, 18, 21, 22, 23

PCIE-6

SB-13

U

T_HDMI

EX

EXT_CRT

EX

T_LVDS

M

INI CARD

WLAN

PCH

RTC

IHDA

P8, 9, 10, 11, 12, 13

LPC

LPC

SPI

X'

TAL

32.768KHz

TAL 25MHz

X'

SPI ROM

P9

PC

IE-1

B

RM 57780

GI

GA LAN

ISL88731A

Ba

X'TAL

25MHz

tery Charger

64Mb *

P

S8101

LS

P27

P26

16 *4 pc

P36

P22

P24

EX

P6111AQDD

U

+1.05V

U

SB-8

I

nt. MIC

T_HDMI

45

RJ

CRT

Con.

L

VDS/CCD/MIC

Con.

I Con.

HDM

P26

P39

P23

P23

P24

ISL62881H

+V

GFX_AXG

RZ-T

P41

nt. MIC

I

OM Option Table

B

A A

erence

Ref

IV@

EV@

VRA

M@

*

Description

for UMA only SKU

or Discrete Graphic only SKU

f

for different VRAM parts

do not stuff

5

IC JACK

M

ALC272X

AUDIO CODEC

P30

HP

P30

GMT 1453L am

P29

peaker

S

P30

P30

p

K/B Co

P34

4

NPCE7

81

P35

P37

uch Pad

To

Board Con.

3

P34

river

Fan D

PWM Type)

(

EC

25X40BVSSIG

W

SPI FLASH

n.

P34

X'

TAL

32.768KHz

R

T8206B

/5V

3V

DP3212

A

CPU core

R

T9018A

+1V

2

R

T8207A

1.5V_SUS

+

P37

AX8792ETD+T

M

+VGPU_CORE

P38

P44

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

H

PA00835RTER

+1.8V

P40

Di

P42

Ther

Quant

Quant

Quant

a Computer Inc.

a Computer Inc.

a Computer Inc.

PROJECT :

PROJECT :

PROJECT :

lock Diagram

lock Diagram

lock Diagram

B

B

B

1

scharger

P43

P43

mal Protection

ZQH

ZQH

ZQH

P44

135Monday, March 14, 2011

135Monday, March 14, 2011

135Monday, March 14, 2011

1A

1A

1A

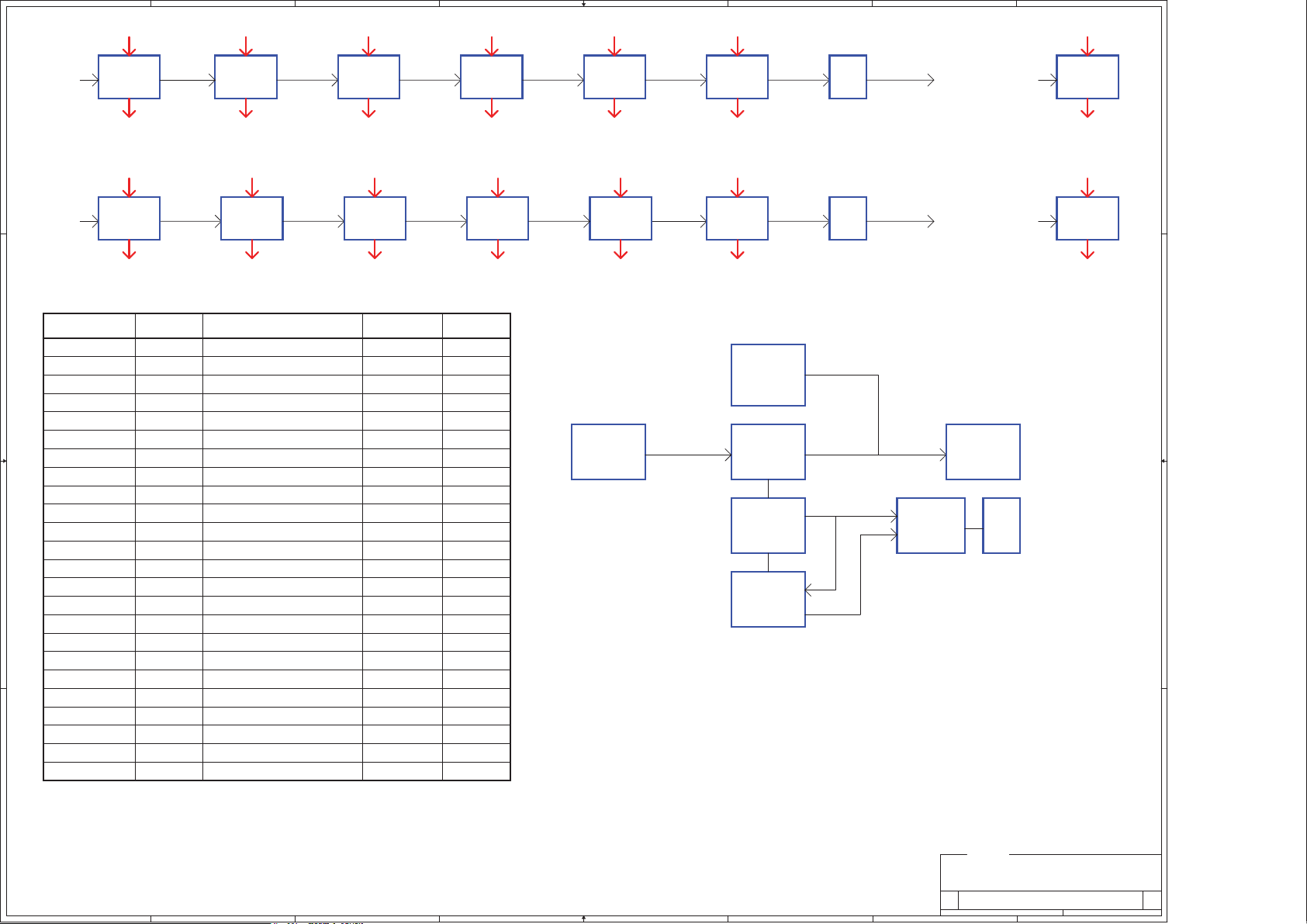

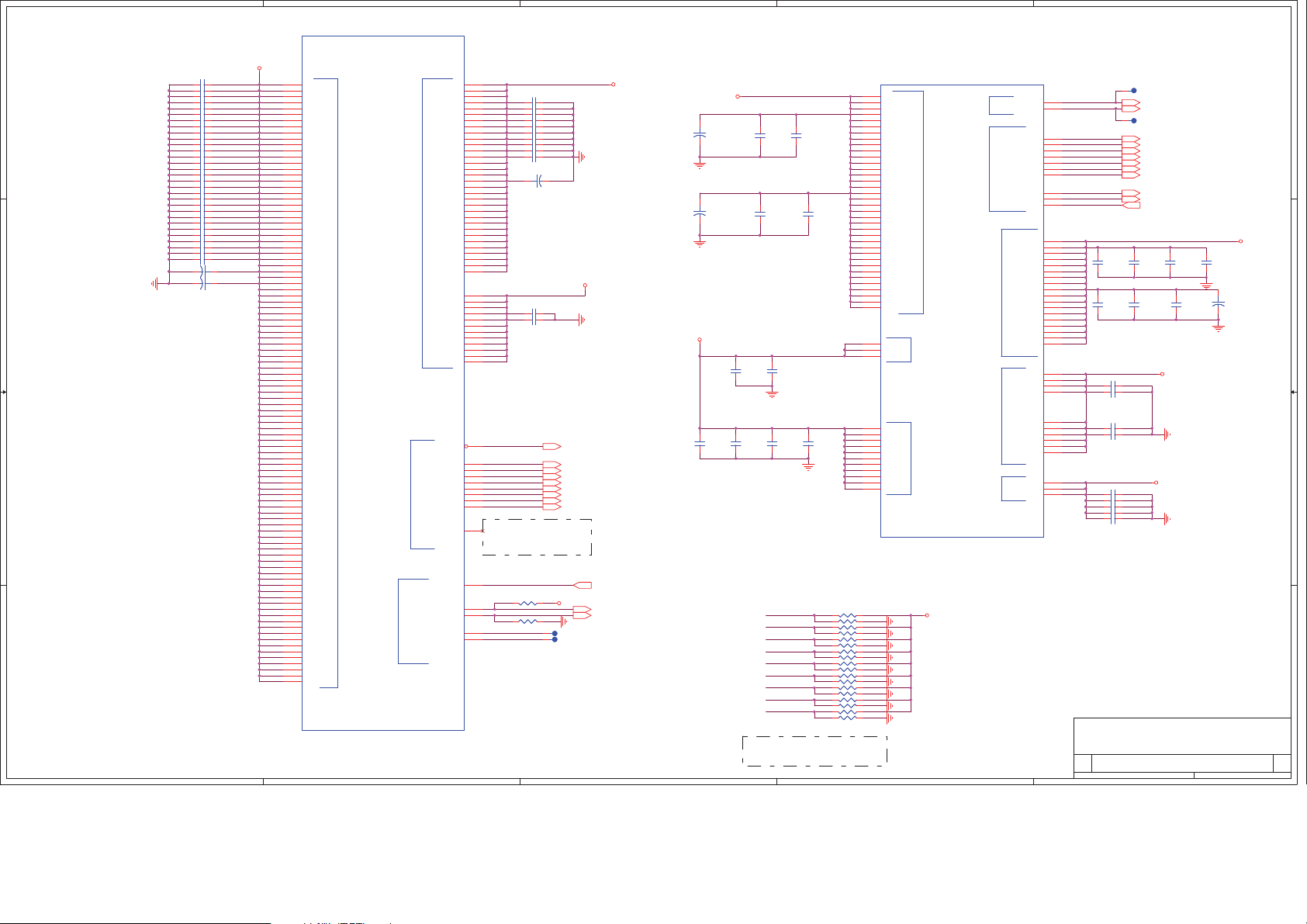

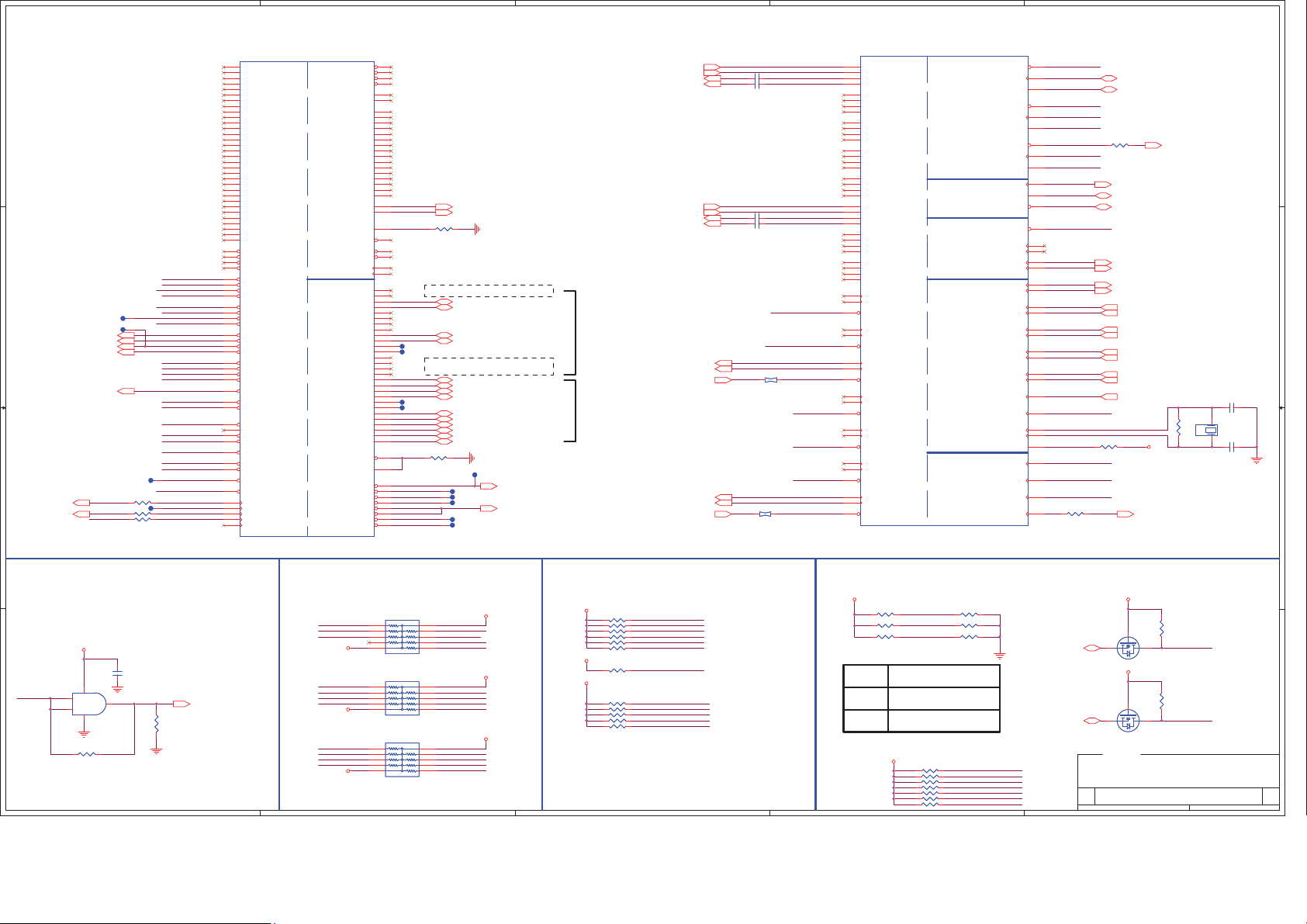

Page 2

1

WWW.AliSaler.Com

GP

U PWR CTRL Option 1 (Defaul t/ VDDR3 before VDDC)

+3.3

V

2

VIN

VIN

3

+1.5

4

V

.5V_SUS

+1

5

V

+1.8

6

7

8

+5V

O3413)

P22

+3V_

U_VRON

dGP

A A

VDDR3

MOS (A

+3_D (0.5A)

VDDC

ISL6264

+V

GPU_CORE (20A)

D

GPUIO_EN

PG_

P44

+VGP

VDDCI

SL62872

I

U_IO (4.5A)

1V_EN

PG_

P45

+1V

G9334A

+1V

(D

P PLL PWR)

DJ & MOS

(3A)

1.5V_EN

PG_

P47

VDDR1

OS (A

M

+1.5

V_GPU (10A)

O4710)

1.5V_EN

PG_

P43

VDDR4

OS (A

M

+1.8

V_GPU (3A)

O6402)

_1.5V_EN

PG

P43

BJT

U_PWROK

dGP

P22

U_PWR_EN#

dGP

MOS

AO3413

+

P22

5_GPU

GPU PWR CTRL Option 2 (VDDR3 after VDDR1)

VIN

PG_

GPUIO_EN

P44

VOLTAGE

+10V~+19V

+3V~+3.3V

+3.3V

+5V

+15V

V

+3.3

+5V

+5V

+3.3V

+1.5V

+0.75V

riation

va

+1.8V

+1.5V

+1.05V or +1.1V

+1.05V

variation

+3.3V

+5V Di

+V

GPU_CORE (20A)

er States

VDDC

ISL6264

dGP

U_VRON

Po

w

POWER PLANE

B B

C C

VIN

+VCCRTC

+3VPCU

+5VPCU

+15V

+3V_S5

+5V_S5

+5V

+1

.5VSUS

+0.75V_DDR_VTT

+VGFX_AXG S0GFX_ONInternal GPU POWER

+1.8V

V

+1.5

+1

.1V_VTT

+1.05V

+VCC_CORE

LCDVCC

+5V_GPU

+GP

U_CORE

+GPU_IO PG_GPUIO_EN+0.9V~+1.1V

VIN

PG

_1V_EN

P45

+VGP

VDDCI

ISL62872

U_IO (4.5A)

DESCRIPTION

RTC POWER

EC POWER

CHARGE POWER

CHARGE PUMP POWER

LAN/BT/CIR POWER

USB POWER

HDD/ODD/Codec/TP/CRT/HDMI POWER

P

CH/GPU/Peripheral component POWER+3V

CPU/SODIMM CORE POWER

SODIMM Termination POWER

CPU/PCH/Braidwood POWER

MINI CARD/NEW CARD POWER

PCH CORE POWER MAINON

CPU CORE POWER

LCD POWER

+1V

G9334A

+1V

+1.5

V

(D

P PLL PWR)

DJ & MOS

(3A)

CONTROL

SIGNAL

ALWAYSMAIN POWER

ALWAYS

ALW

ALWAYS

S5_

S5_O

MAINON

MAINON

SUSO

MAINON

MAINON

MAINON

MAINONCPU VTT POWER

VRON

LVDS_VDDEN

dGP

PG_1.5V_EN+1.5V+1.5V_GPU

+1.5

PG_1V_EN+1V+1V Discrete enableDP/PEG POWER

PG_

P47

AYS

ON

N

N

U_PWR_EN#

V_GPU+1.8V+1.8V_GPU

1.5V_EN

+1

.5V_SUS

VDDR1

MOS (A

+1.5

V_GPU (10A)

ACTIVE IN

ALWAYS

ALWAYS

ALWAYS

ALWAYS

ALWAYSALWAYS

S0-S5

S0-S5

S0

S0

S0-S3

S0

S0

S0

S0

S0

S0

S0

screte enableSWITCHABLE PWM IC POWER

Discrete enable+3V_DGPU CORE POWER+0.9V~+1.1V

Discrete enableGPU I/O POWER

Discrete enableVRAM CORE POWER

Discrete enableGPU_CRE/LVDS/PLL POWER

O4710)

P43

+1.5V_

GPU

Therma

+3.3

V

VDDR3

MOS (AO3413)

P22

+3_D (0.5A)

l Follow Chart

CPU

RE PWR

CO

+3V_

H_ORI

D

CHOT#

+1.8

H/W Thrott

+1.8

V

VDDR4

MOS (A

O6402)

V_GPU (3A)

NTC

The

Protection

ling

SM-Bu

P43

CPU

PCH

EC

rmal

s

PG

_1.5V_EN

PM_

THRMTRIP#

SM

CPUFAN#

BJT

P22

L1ALERT#

WIRE-

dGP

AND

U_PWROK

SYS_

SHDN#

dGP

3V/5 V

SYS PW

r

U_PWR_EN#

R

FANFAN Drive

+5V

MOS

AO3413

+

P22

5_GPU

D D

Q

Q

Q

anta Computer Inc.

anta Computer Inc.

anta Computer Inc.

u

u

u

1

2

PROJECT :

PROJECT :

Si

Si

Si

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

PW

PW

PW

Date: Sheet

onday, March 14, 2011

Date: Sheet

onday, March 14, 2011

Date: Sheet

3

4

5

6

7

onday, March 14, 2011

PROJECT :

R Status & GPU PWR CRL & THRM

R Status & GPU PWR CRL & THRM

R Status & GPU PWR CRL & THRM

ZQH

ZQH

ZQH

1A

1A

1A

of

of

of

245M

245M

245M

8

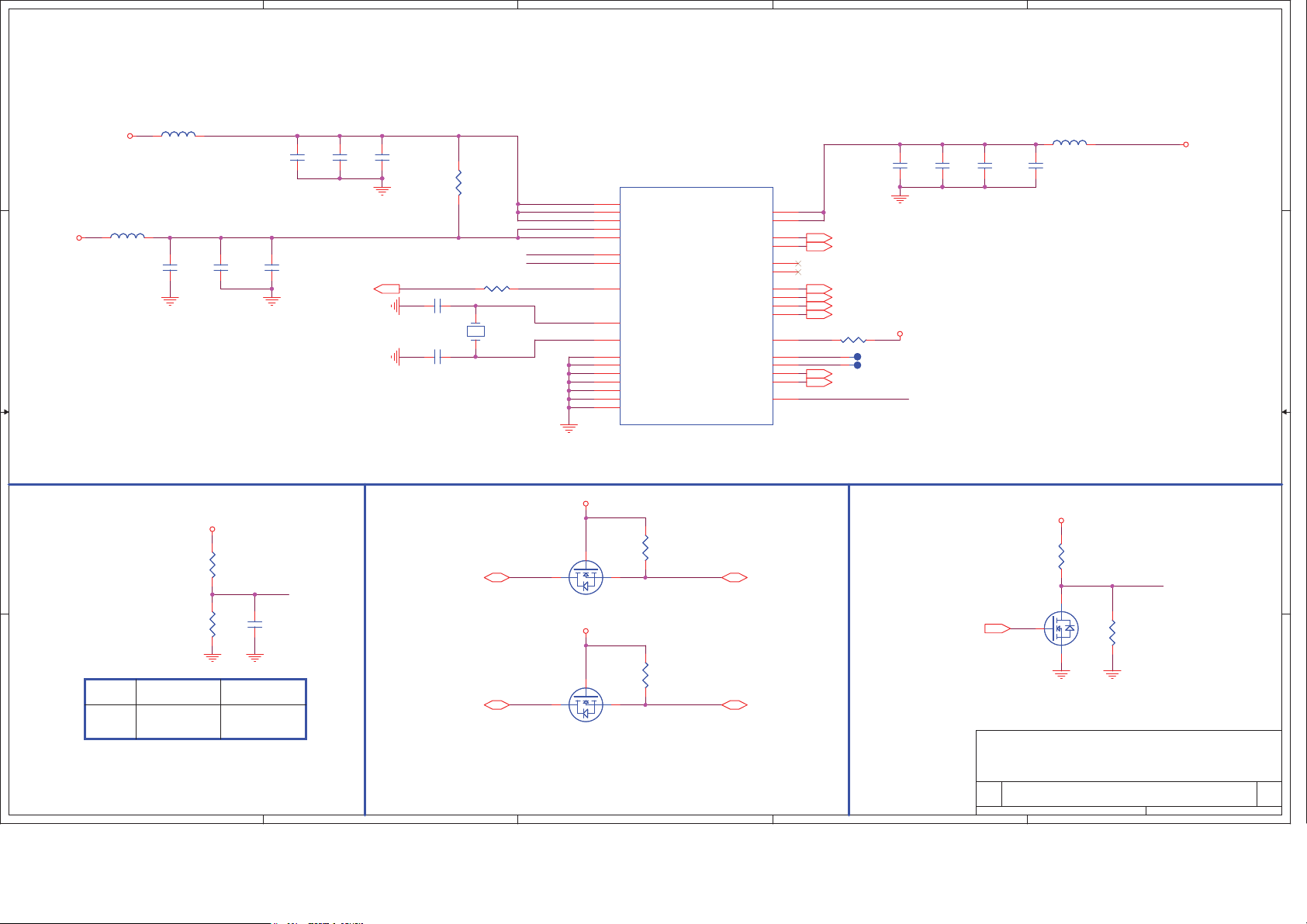

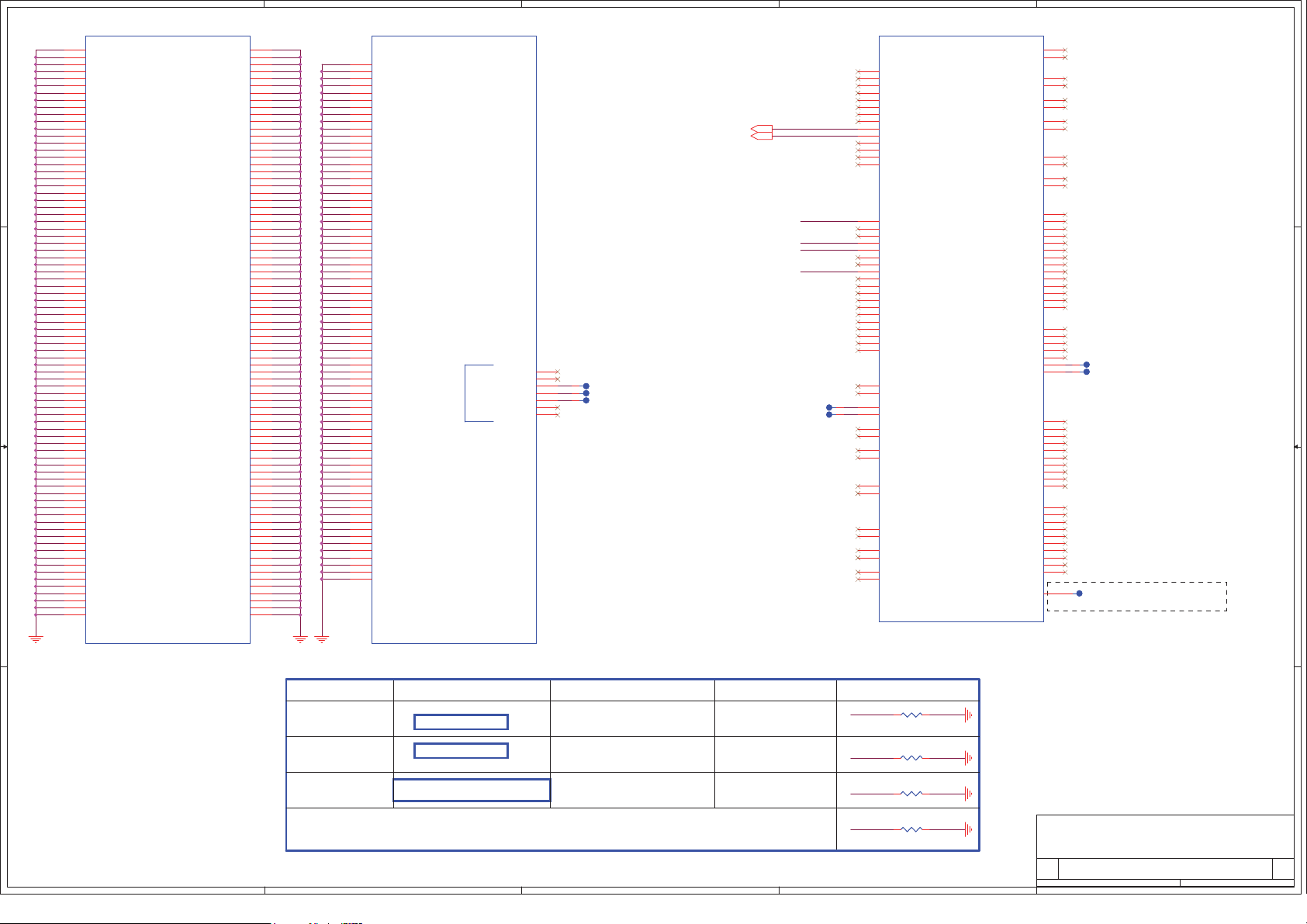

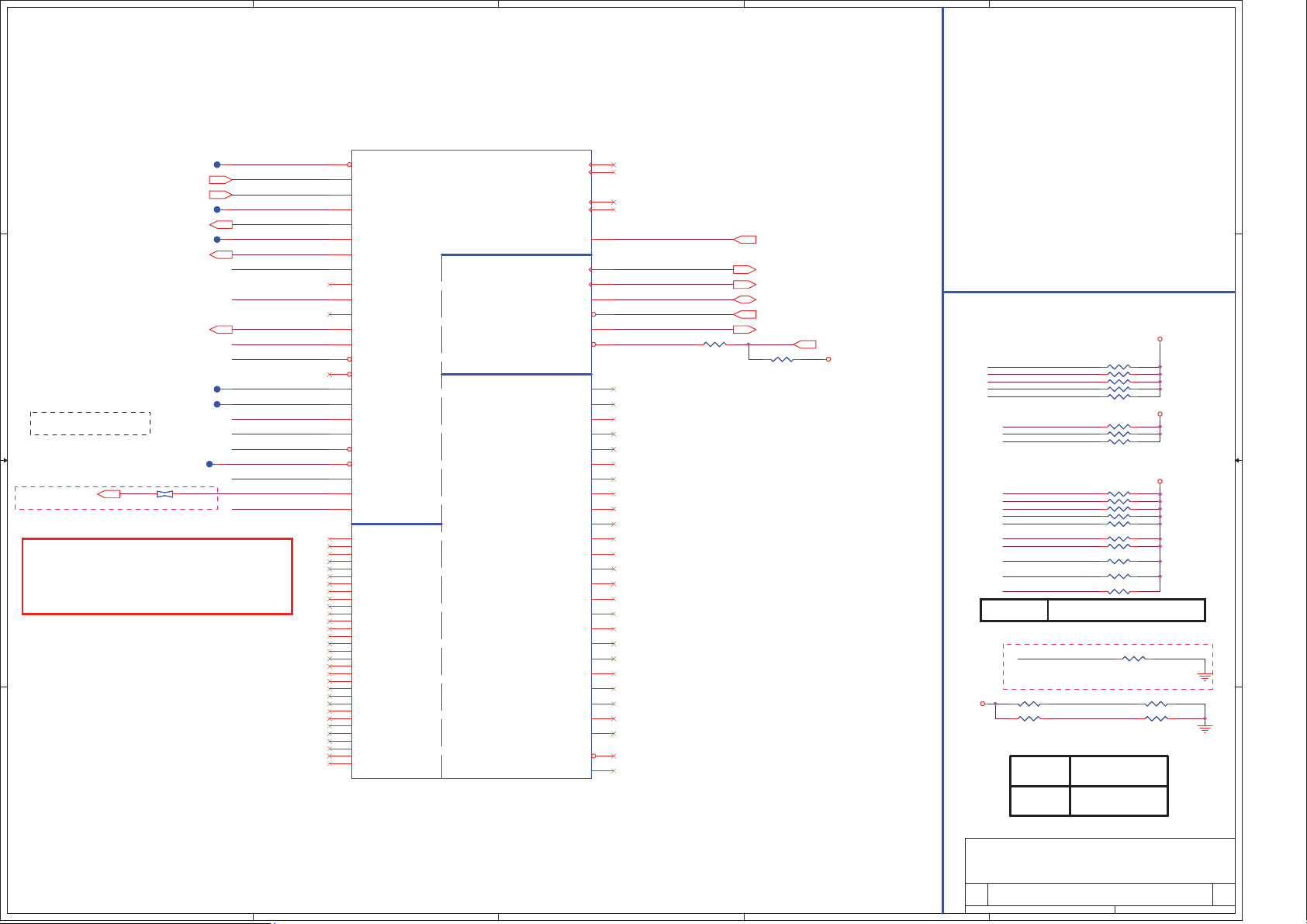

Page 3

5

4

3

2

1

D D

*PBY160808T-181Y-N/2A/180ohm_6

L50

L50

+1.

5V

BLM18AG601SN1D/200mA/600ohm_6

L23

L23

+3V

C C

B B

BLM18AG601SN1D/200mA/600ohm_6

*PBY160808T-181Y-N/2A/180ohm_6

20mil

C267

+1.

C267

.1u/16V_4

.1u/16V_4

05V

R4

R4

51

51

*10K_4

*10K_4

R4

R4

46

46

10K_4

10K_4

CP

C238

C238

4.7u/10V_8

4.7u/10V_8

150mA(30mil)

C2

C2

C6

C6

43

43

.1u/16V_4

.1u/16V_4

.1u/16V_4

.1u/16V_4

_CLK

+3V

C251

C251

.1u/16V_4

.1u/16V_4

CL

K_ICH_14M<10>

I

DT: AL003197001 (ICS9LVS3197AKLFT)

+1.

5V_CLK

C

C

246

246

27

27

.1u/16V_4

.1u/16V_4

C

C

614 33p/50V_4

614 33p/50V_4

C

C

612 33p/50V_4

612 33p/50V_4

Realtek: AL000890000 (RTM890N-632-GRT)

Silego: AL000595000 (SLG8LV595VTR)

BusCPU_CLK select

SM

CH_SMBDATA<10>

U_SEL

C

C

617

617

*10p/50V/COG_4

*10p/50V/COG_4

I

565

565

R

R

0_6

0_6

R

R

455 33_4

455 33_4

Y6

Y6

14.

14.

318MHz

318MHz

C

LK_SDATA

C

LK_SCLK

U_SEL

CP

AL_IN

XT

XT

AL_OUT

3

+3V

2

+3V

U20

U20

1

DD_DOT

V

17

V

DD_SRC

24

V

DD_CPU

5

V

DD_27

29

DD_REF

V

31

SD

A

32

SC

L

30

REF_0/CPU_SEL

28

AL_IN

XT

27

XT

AL_OUT

2

VSS_

DOT

8

VSS_27

9

VSS_

SATA

12

VSS_

SRC

21

VSS_

CPU

26

VSS_

REF

33

GN

D

ICS9LRS3197AKLFT

ICS9LRS3197AKLFT

1

Q18

Q18

7002K

7002K

2N

2N

543

543

R

R

2.2K_4

2.2K_4

C

LK_SDATA

V

DD_SRC_I/O

V

DD_CPU_I/O

SRC_1/SATA

SR

C_1#/SATA#

*

CPU_STOP#

CK

PWRGD/PD#

D

DO

27M

S

CPU_1#

CP

15

18

3

OT_96

4

T_96#

6

27M

7

_SS

10

11

13

S

RC_2

14

RC_2#

16

20

CP

U_1

19

23

CP

U_0

22

U_0#

25

C

LK_SDATA <14,15,19>

+

VDDIO_CLK

CL

K_BUF_DREFCLK <10>

CL

K_BUF_DREFCLK# <10>

C

LK_BUF_DREFSSCLK <10>

LK_BUF_DREFSSCLK# <10>

C

C

LK_BUF_PCIE_3GPLL <10>

C

LK_BUF_PCIE_3GPLL# <10>

130 10K_4

130 10K_4

R

R

TP23TP

TP24TP

LK_BUF_BCLK <10>

C

LK_BUF_BCLK# <10>

C

C

K_PWRGD_R

80mA(20mil)

C6

C6

13

13

.1u/16V_4

.1u/16V_4

Place each 0.1uF cap as close as

possible to each VDD IO pin. Place

the 10uF caps on the VDD_IO plane.

+3V

23

24

CLK Enabl

R_PWRGD_CK505#<30>

V

C

C

244

244

.1u/16V_4

.1u/16V_4

e

C

C

607

607

10u/Y5V_8

10u/Y5V_8

L48

L48

2

C

C

609

609

10u/Y5V_8

10u/Y5V_8

+3V

3

Q19

Q19

2N

2N

45

45

R5

R5

1K/F_4

1K/F_4

7002K

7002K

PBY160808T/2A/180ohm_6

PBY160808T/2A/180ohm_6

CK

_PWRGD_R

44

44

R5

R5

100K/F_4

100K/F_4

05V

+1.

542

542

R

1

7002K

7002K

3

R

2.2K_4

2.2K_4

C

LK_SCLK

C

LK_SCLK <14,15,19>

ize Document Number Rev

S

S

S

ize Document Number Rev

ize Document Number Rev

Cloc

Cloc

Cloc

Date: Sheet

Date: Sheet

2

Date: Sheet

01

A A

CPU_

SEL

CPU0/1=133MHz

(default)

5

CPU0/1=100MHz

CH_SMBCLK<10>

I

4

2

3

Q17

Q17

2N

2N

1

Quanta Com

Quanta Com

Quanta Com

PROJECT :

PROJECT :

PROJECT :

k Generator

k Generator

k Generator

puter Inc.

puter Inc.

puter Inc.

ZQH

ZQH

ZQH

34

34

34

1

1A

1A

1A

5Monday, March 14, 2011

5Monday, March 14, 2011

5Monday, March 14, 2011

of

of

of

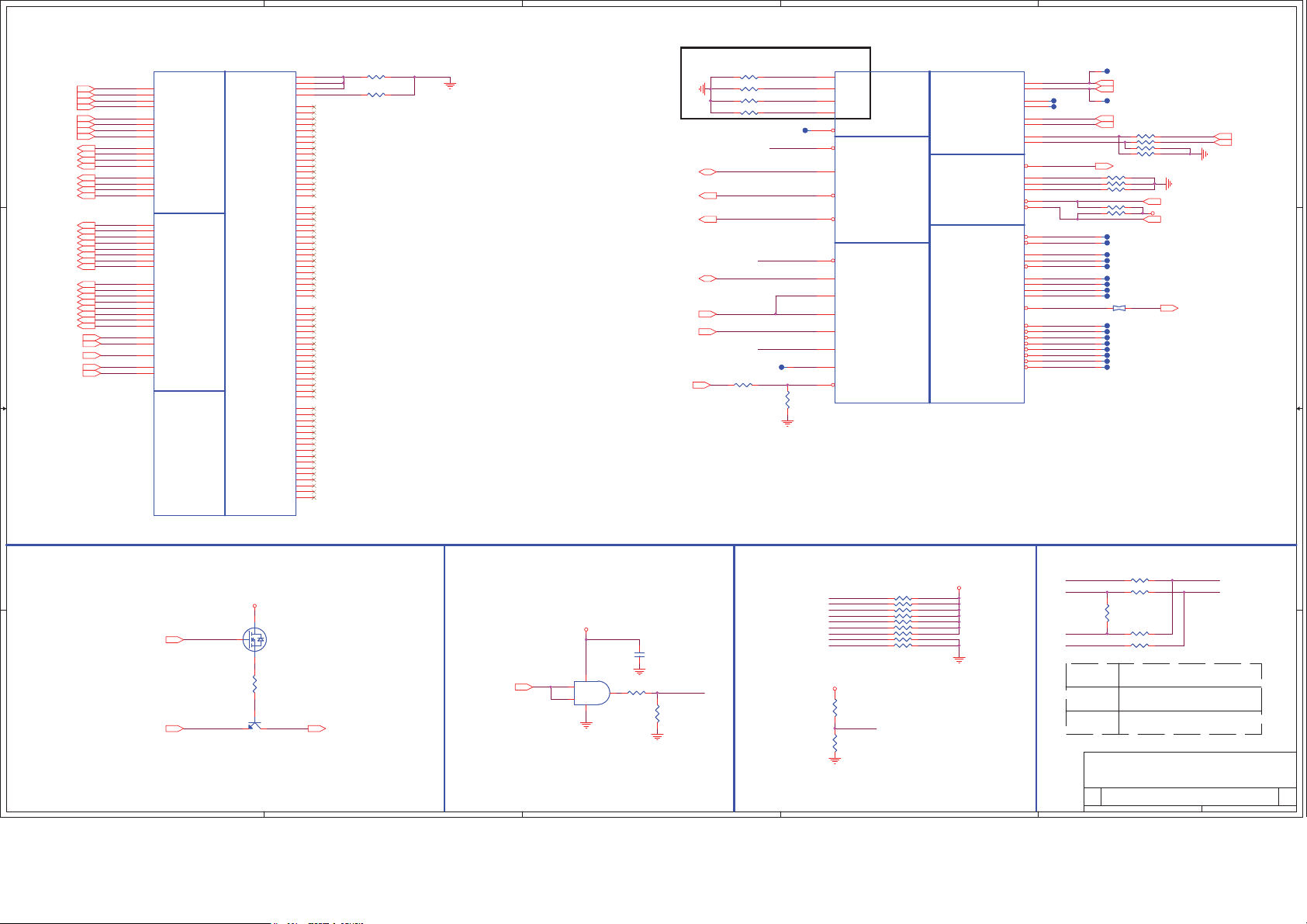

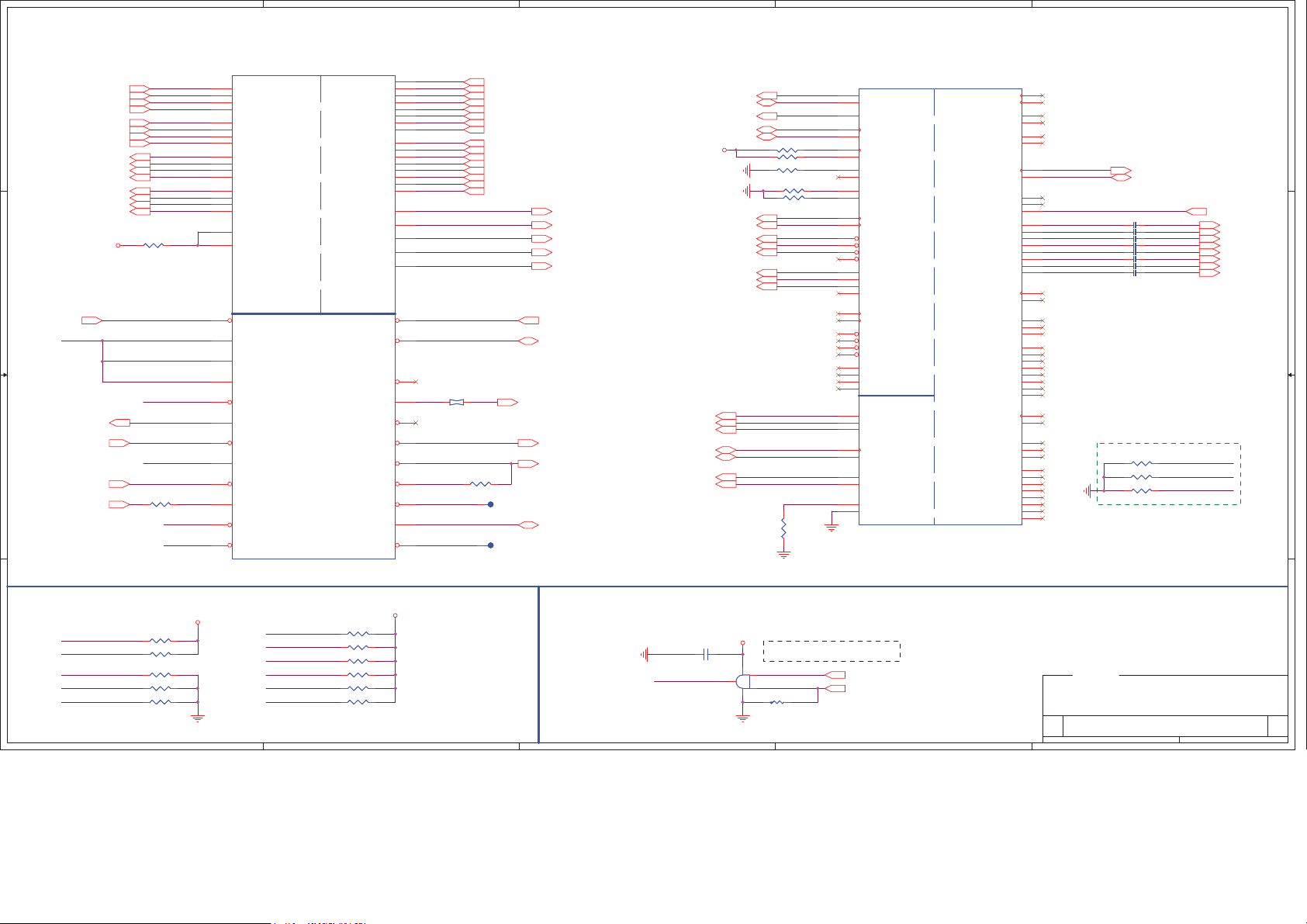

Page 4

5

WWW.AliSaler.Com

AUBURNDALE/CLARKSFIELD PROCESSOR (DMI,PEG,FDI)

U22A

U22A

DMI_T

XN0<8>

T

XN1<8>

DMI_

XN2<8>

DMI_T

XN3<8>

DMI_T

D D

C C

B B

>

I_TXP0<8 >

DM

DM

I_TXP1<8 >

DM

I_TXP2<8 >

DM

I_TXP3<8 >

DMI_RX

DMI_RX

DMI_

DMI_RX

DMI_RX

DMI_RX

DMI_RX

DMI_RX

FDI_T

FDI_T

FDI_T

FDI_T

FDI_T

FDI_T

FDI_T

FDI_T

FD

I_TXP0<8>

FD

I_TXP1<8>

FD

I_TXP2<8>

FD

I_TXP3<8>

I_TXP4<8>

FD

I_TXP5<8>

FD

FD

I_TXP6<8>

I_TXP7<8>

FD

FDI_FS

FDI_FS

FD

I_LSYNC0<8>

I_LSYNC1<8>

FD

N0<8>

N1<8>

RX

N2<8>

N3<8>

P0<8>

P1<8>

P2<8>

P3<8>

XN0<8>

XN1<8>

XN2<8>

XN3<8>

XN4<8>

XN5<8>

XN6<8>

XN7<8>

YNC0<8>

YNC1<8>

FDI_INT<8

A24

DMI

C23

DMI

B22

DM

A21

DMI

B24

DMI

D23

DMI

B23

DMI

A22

DMI

D24

DMI

G24

DMI

F23

DMI

H23

DM

D25

DMI

F24

DMI

E23

DMI

G23

DMI

E22

FDI

D21

FDI

D19

FDI

D18

FDI

G21

FDI

E19

FDI

F21

FDI

G18

FDI

D22

FDI

C21

FDI

D20

FDI

C18

FDI

G22

FDI

E20

FDI

F20

FDI

G19

FDI

F17

FDI

E17

FDI

C17

F

F18

FD

D17

FD

larksfield/Auburndale

larksfield/Auburndale

C

C

_RX#[0]

_RX#[1]

I

_RX#[2]

_RX#[3]

_RX[0]

_RX[1]

_RX[2]

_RX[3]

_TX#[0]

_TX#[1]

_TX#[2]

I

_TX#[3]

_TX[0]

_TX[1]

_TX[2]

_TX[3]

_TX#[0]

_TX#[1]

_TX#[2]

_TX#[3]

_TX#[4]

_TX#[5]

_TX#[6]

_TX#[7]

_TX[0]

_TX[1]

_TX[2]

_TX[3]

_TX[4]

_TX[5]

_TX[6]

_TX[7]

_FSYNC[0]

_FSYNC[1]

I_INT

D

I_LSYNC[0]

I_LSYNC[1]

DMI Intel(R) FDI

DMI Intel(R) FDI

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG

PEG

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

ICOMPI

ICOMPO

RCOMPO

RBIAS

RX#[0]

RX#[1]

RX#[2]

RX#[3]

RX#[4]

RX#[5]

RX#[6]

RX#[7]

RX#[8]

RX#[9]

_

RX#[10]

_

RX#[11]

RX#[12]

RX#[13]

RX#[14]

RX#[15]

RX[0]

RX[1]

RX[2]

RX[3]

RX[4]

RX[5]

RX[6]

RX[7]

RX[8]

RX[9]

RX[10]

RX[11]

RX[12]

RX[13]

RX[14]

RX[15]

TX#[0]

TX#[1]

TX#[2]

TX#[3]

TX#[4]

TX#[5]

TX#[6]

TX#[7]

TX#[8]

_

TX#[9]

TX#[10]

TX#[11]

TX#[12]

TX#[13]

TX#[14]

TX#[15]

TX[0]

TX[1]

TX[2]

TX[3]

TX[4]

TX[5]

TX[6]

TX[7]

TX[8]

TX[9]

TX[10]

TX[11]

TX[12]

TX[13]

TX[14]

TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

R436

R436

R437

R437

4

49.9/F_4

49.9/F_4

750/F_4

750/F_4

3

Processor Compensation Signals

20/F_4

20/F_4

R444

R444

20/F_4

20/F_4

R442

R442

R17

R17

3 49.9/F_4

3 49.9/F_4

R44

R44

0 49.9/F_4

0 49.9/F_4

PECI<11>

H_

H_P

ROCHOT#<27,30>

PM

_THRMTRIP#<11>

PM_SY

NC<8>

H_

PWRGOOD<11,27>

PM

_DRAM_PWRGD<8>

R193

R193

1.5K/F_4

PLTR

ST#<10,18,19,23,27>

1.5K/F_4

2

AUBURNDALE/CLARKSFIELD PROCESSOR (CLK,MISC,JTAG)

DPLL_REF_SSCLK and DPLL_REF_SSCLK# can be connected to GND on Arrandale

directly if motherboard only supports discrete graphics. If motherboard supports

integrated graphics but without eDP, these pins can also be connected to GND directly.

B

H_CP

H_V

T14T14

H_CA

H_P

ROCHOT#

URST#

TTPWRGD

CPU_

H_CO

H_CO

H_CO

H_CO

0

T10T1

TERR#

PLTRST#

R196

R196

750/

750/

MP3

MP2

MP1

MP0

F_4

F_4

U22

U22

AT23

COM

AT24

COM

G16

CO

AT26

COM

AH24

SKTO

AK14

CAT

AT

15

PEC

AN26

PRO

AK15

TH

AP26

RESET

AL15

PM_

AN14

VC

AN27

VC

AK13

SM

AM15

VT

AM26

TAPPW

AL14

RST

Clarksfield/Auburndale

Clarksfield/Auburndale

B

P3

P2

M

P1

P0

CC#

ERR#

I

CHOT#

ERMTRIP#

_OBS#

SYNC

CPWRGOOD_1

CPWRGOOD_0

_DRAMPWROK

TPWRGOOD

RGOOD

IN#

MISC THERMAL

MISC THERMAL

DPLL_RE

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

DPLL_RE

SM

SM

SM

SM

PM_

PM_

C

B

BCL

PE

PEG_

F_SSCLK

F_SSCLK#

_

DRAMRST#

_RCOMP[0]

_RCOMP[1]

_RCOMP[2]

EXT_TS#[0]

EXT_TS#[1]

TDO

BP

BP

BP

BP

BP

B

BP

BP

BCL

BCL

LK_ITP

K_ITP#

G_CLK

CLK#

PRDY

PREQ

TRS

TDI

DBR#

M#[0]

M#[1]

M#[2]

M#[3]

M#[4]

M#[5]

P

M#[6]

M#[7]

K

K#

#

#

TCK

TMS

T#

TDI

TDO

_M

_M

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN

AP2

AT27

AT

AR

AR29

AP29

AN

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

DP

D

28

8

29

27

25

T62T62

T67T67

LL_REF_SSCLK_R

P

LL_REF_SSCLK#_R

SM

_RCOMP_0

SM

_RCOMP_1

SM

_RCOMP_2

XDP_PR

XDP_T

CLK

XDP_T

MS

XDP_T

RST#

DI_R

XDP_T

DO_R

XDP_T

DI_M

XDP_T

DO_M

XDP_T

H_DB

R#_R

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

EQ#

R254

R254

R253

R253

R252

R252

R18

R18

7 10K_4

7 10K_4

3 10K_4

3 10K_4

R18

R18

R149

R149

T20T20

CLK

_CPU_BCLK <11>

K

_CPU_BCLK# <11>

CL

T21T21

CLK_PC

CLK_PC

R465

R465

R471

R471

R472

R472

R463

R463

DRAMRST# <14,15>

DDR3_

100/F_4

100/F_4

24.9/F_4

24.9/F_4

130/F_4

130/F_4

T68T68

T69T69

T8T8

T9T9

T71T71

T70T70

T66T66

T65T65

T64T64

*Short_4

*Short_4

T19T19

T18T18

T17T17

T13T13

T11T11

T15T15

T16T16

T12T12

IE_3GPLL <10>

IE_3GPLL# <10>

*0_4

*0_4

*0_4

*0_4

0_4

0_4

0_4

0_4

+1.

05V

1

Layout Note: Place

these resistors

near Processor

PM_EXT

TS#0 <14>

PM_EXT

TS#1 <15>

BRST# <8>

XDP_D

DP

LL_REF_SSCLK <10>

DP

LL_REF_SSCLK# <10>

Pro

Ther

maltrip prot e c t

05V

+1.

3

Q16

Q16

_THRMTRIP#

PM

2

1 3

FD

FD

V301N

V301N

1

R209

R209

1K_4

1K_4

2

Q15

Q15

MMBT3904

MMBT3904

SY

S_SHDN# <29,34>

4

_VR_PWRGOOD<8,30>

DELAY

A A

PM

_THRMTRIP#<11>

5

VTT P

WR_Good

ROK<27>

MPW

+3V

C30

C30

9

9

0.1u/10V_4

0.1u/10V_4

6

6

R17

2

1

R17

VTTPW RGD

2K/F_4

2K/F_4

H_

R17

R17

9

9

1K_4

1K_4

3

4

U5

U5

3 5

TC7

TC7

SH08FU

SH08FU

cessor pull-up

+1

R20

R20

5

5

1.1K/F_4

1.1K/F_4

9

9

R19

R19

3K/F_4

3K/F_4

DO

XDP_T

TERR#

H_CA

ROCHOT#

H_P

URST#

H_CP

MS

XDP_T

DI_R

XDP_T

XDP_PR

XDP_T

CLK

XDP_T

RST#

.5VSUS

_DRAM_PWRGD

PM

51/F_4

51/F_4

R420

R420

49.9/F_4

49.9/F_4

R192

R192

68_4

68_4

R137

R137

*68_4

*68_4

R438

R438

*51_4

*51_4

R135

R135

*51_4

*51_4

R435

R435

R434

R434

EQ#

*51_4

*51_4

R133

R133

*51_4

*51_4

R439 51/F_4R439 51/F_4

Use a voltage divider with VDDQ

(1.5V) rail (ON in S3) and

resistor combination of 4.75K (to

VDDQ)/12K(to GND) to generate the

required voltage.

Note: CRB uses a 3.3V (always ON)

rail with 2K and 1K combination.

2

05V

+1.

JTAG MAPPING

XDP_TDI_R XDP_TDI

XDP_TDO_M

XDP_T

DI_M

XDP_T

DO_R

Scan Chain

(Default)

CPU Only

GMCH Only

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

Si

Si

Si

Date: Sheet

Date: Sheet

Date: Sheet

0_4

0_4

R433

R433

*0_4

*0_4

R429

R429

1

1

R43

R43

0_4

0_4

R432

R432

*0_4

*0_4

R430

R430

0_4

0_4

STUFF -> R469, R491, R507

NO STUFF -> R489, R490

STUFF -> R490, R491

NO STUFF -> R469, R489, R507

STUFF -> R489, R507

NO STUFF -> R491, R490, R469

Quan

Quan

Quan

PROJECT :

PROJECT :

PROJECT :

BURNDA 1/4

BURNDA 1/4

BURNDA 1/4

AU

AU

AU

1

XDP_TDO

ta Computer Inc.

ta Computer Inc.

ta Computer Inc.

ZQH

ZQH

ZQH

1A

1A

445Monday, March 14, 2011

445Monday, March 14, 2011

445Monday, March 14, 2011

1A

of

of

of

Page 5

5

AUBURNDALE/CLARKSFIELD PROCESSOR (DDR3)

U2

U2

2C

2C

_A_DQ[63:0]<14>

M

D D

C C

B B

_A_BS#0<14>

M

_A_BS#1<14>

M

_A_BS#2<14>

M

M

_A_CAS#<14>

_A_RAS#<14>

M

M_

A_WE#<14>

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

A_DQ0

A_DQ1

A_DQ2

A_DQ3

A_DQ4

A_DQ5

A_DQ6

A_DQ7

A_DQ8

A_DQ9

A_DQ10

A_DQ11

A_DQ12

A_DQ13

A_DQ14

A_DQ15

A_DQ16

A_DQ17

A_DQ18

A_DQ19

A_DQ20

A_DQ21

A_DQ22

A_DQ23

A_DQ24

A_DQ25

A_DQ26

A_DQ27

A_DQ28

A_DQ29

A_DQ30

A_DQ31

A_DQ32

A_DQ33

A_DQ34

A_DQ35

A_DQ36

A_DQ37

A_DQ38

A_DQ39

A_DQ40

A_DQ41

A_DQ42

A_DQ43

A_DQ44

A_DQ45

A_DQ46

A_DQ47

A_DQ48

A_DQ49

A_DQ50

A_DQ51

A_DQ52

A_DQ53

A_DQ54

A_DQ55

A_DQ56

A_DQ57

A_DQ58

A_DQ59

A_DQ60

A_DQ61

A_DQ62

A_DQ63

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

DQ[0]

SA_

DQ[1]

SA_

C7

SA_

DQ[2]

A7

DQ[3]

SA_

B10

DQ[4]

SA_

SA_

DQ[5]

E10

SA_

DQ[6]

A8

SA_

DQ[7]

D8

DQ[8]

SA_

F10

DQ[9]

SA_

E6

SA_

DQ[10]

F7

SA_

DQ[11]

E9

DQ[12]

SA_

B7

DQ[13]

SA_

E7

SA_

DQ[14]

C6

DQ[15]

SA_

SA_

DQ[16]

G8

DQ[17]

SA_

K7

DQ[18]

SA_

J8

SA_

DQ[19]

G7

DQ[20]

SA_

DQ[21]

SA_

J7

DQ[22]

SA_

J10

SA_

DQ[23]

L7

DQ[24]

SA_

M6

DQ[25]

SA_

M8

DQ[26]

SA_

L9

DQ[27]

SA_

L6

SA_

DQ[28]

K8

DQ[29]

SA_

N8

SA_

DQ[30]

P9

DQ[31]

SA_

SA_

DQ[32]

DQ[33]

SA_

DQ[34]

SA_

SA_

DQ[35]

DQ[36]

SA_

SA_

DQ[37]

AJ7

DQ[38]

SA_

AJ6

SA_

DQ[39]

SA_

DQ[40]

AJ9

SA_

DQ[41]

DQ[42]

SA_

DQ[43]

SA_

SA_

DQ[44]

AL7

DQ[45]

SA_

SA_

DQ[46]

AL8

DQ[47]

SA_

SA_

DQ[48]

SA_

DQ[49]

DQ[50]

SA_

DQ[51]

SA_

DQ[52]

SA_

SA_

DQ[53]

DQ[54]

SA_

SA_

DQ[55]

DQ[56]

SA_

SA_

DQ[57]

SA_

DQ[58]

DQ[59]

SA_

SA_

DQ[60]

DQ[61]

SA_

SA_

DQ[62]

DQ[63]

SA_

SA_

BS[0]

BS[1]

SA_

U7

SA_

BS[2]

SA_

CAS#

RAS#

SA_

SA_

WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

4

AA6

SA_

CK[0]

AA7

SA_

CK#[0]

P7

CKE[0]

SA_

Y6

CK[1]

SA_

Y5

CK#[1]

SA_

P6

SA_

CKE[1]

AE2

CS#[0]

SA_

AE8

SA_

CS#[1]

AD8

SA_

ODT[0]

AF9

ODT[1]

SA_

A_DM0

M_

B9

DM[0]

SA_

SA_

DM[1]

DM[2]

SA_

DM[3]

SA_

DM[4]

SA_

DM[5]

SA_

SA_

DM[6]

DM[7]

SA_

DQS#[0]

SA_

SA_

DQS#[1]

DQS#[2]

SA_

SA_

DQS#[3]

DQS#[4]

SA_

SA_

DQS#[5]

SA_

DQS#[6]

SA_

DQS#[7]

SA_

DQS[0]

DQS[1]

SA_

SA_

DQS[2]

SA_

DQS[3]

DQS[4]

SA_

DQS[5]

SA_

DQS[6]

SA_

SA_

DQS[7]

SA_

MA[0]

MA[1]

SA_

SA_

MA[2]

MA[3]

SA_

SA_

MA[4]

MA[5]

SA_

SA_

MA[6]

SA_

MA[7]

SA_

MA[8]

SA_

MA[9]

MA[10]

SA_

SA_

MA[11]

MA[12]

SA_

SA_

MA[13]

MA[14]

SA_

SA_

MA[15]

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_

A_DM1

M_

A_DM2

A_DM3

M_

A_DM4

M_

A_DM5

M_

M_

A_DM6

A_DM7

M_

_A_DQS#0

M

M

_A_DQS#1

_A_DQS#2

M

M

_A_DQS#3

_A_DQS#4

M

M

_A_DQS#5

M

_A_DQS#6

M

_A_DQS#7

M

_A_DQS0

_A_DQS1

M

M

_A_DQS2

M

_A_DQS3

_A_DQS4

M

M

_A_DQS5

_A_DQS6

M

M

_A_DQS7

M

_A_A0

_A_A1

M

_A_A2

M

_A_A3

M

M

_A_A4

_A_A5

M

_A_A6

M

M

_A_A7

M

_A_A8

M

_A_A9

_A_A10

M

_A_A11

M

M

_A_A12

M

_A_A13

_A_A14

M

M

_A_A15

_A_CLK0 <14>

M

M

_A_CLK0# <14>

_A_CKE0 <14>

M

M

_A_CLK1 <14>

_A_CLK1# <14>

M

M

_A_CKE1 <14>

_A_CS#0 <14>

M

M

_A_CS#1 <14>

M_

A_ODT0 <14>

M_

A_ODT1 <14>

M

_A_DQS#[7:0] <14>

M

_A_DQS[7:0] <14>

M

M

_A_DM[7:0] <14>

_A_A[15:0] <14>

3

M

_B_DQ[63:0]<15>

_B_BS#0<15>

M

_B_BS#1<15>

M

M

_B_BS#2<15>

_B_CAS#<15>

M

_B_RAS#<15>

M

M_

B_WE#<15>

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

B_DQ0

B_DQ1

B_DQ2

B_DQ3

B_DQ4

B_DQ5

B_DQ6

B_DQ7

B_DQ8

B_DQ9

B_DQ10

B_DQ11

B_DQ12

B_DQ13

B_DQ14

B_DQ15

B_DQ16

B_DQ17

B_DQ18

B_DQ19

B_DQ20

B_DQ21

B_DQ22

B_DQ23

B_DQ24

B_DQ25

B_DQ26

B_DQ27

B_DQ28

B_DQ29

B_DQ30

B_DQ31

B_DQ32

B_DQ33

B_DQ34

B_DQ35

B_DQ36

B_DQ37

B_DQ38

B_DQ39

B_DQ40

B_DQ41

B_DQ42

B_DQ43

B_DQ44

B_DQ45

B_DQ46

B_DQ47

B_DQ48

B_DQ49

B_DQ50

B_DQ51

B_DQ52

B_DQ53

B_DQ54

B_DQ55

B_DQ56

B_DQ57

B_DQ58

B_DQ59

B_DQ60

B_DQ61

B_DQ62

B_DQ63

AG1

AG4

AG3

AH4

AM6

AN2

AM4

AM3

AN5

AN6

AN4

AN3

AN7

AR10

AT10

AC5

AC6

AF3

AJ3

AK1

AJ4

AK3

AK4

AK5

AK2

AP3

AT4

AT5

AT6

AP6

AP8

AT9

AT7

AP9

AB1

2

2D

2D

U2

U2

W8

SB_

CK[0]

W9

S

B_CK#[0]

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

B_CK#[1]

S

SB_

S

B_CS#[0]

S

B_CS#[1]

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

DQS#[0]

DQS#[1]

DQS#[2]

DQS#[3]

DQS#[4]

DQS#[5]

DQS#[6]

DQS#[7]

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

SB_

CKE[0]

CK[1]

CKE[1]

ODT[0]

ODT[1]

DM[0]

DM[1]

DM[2]

DM[3]

DM[4]

DM[5]

DM[6]

DM[7]

DQS[0]

DQS[1]

DQS[2]

DQS[3]

DQS[4]

DQS[5]

DQS[6]

DQS[7]

MA[0]

MA[1]

MA[2]

MA[3]

MA[4]

MA[5]

MA[6]

MA[7]

MA[8]

MA[9]

MA[10]

MA[11]

MA[12]

MA[13]

MA[14]

MA[15]

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_

M_

M_

M_

M_

M_

M_

M_

_B_DQS#0

M

M

_B_DQS#1

_B_DQS#2

M

M

_B_DQS#3

M

_B_DQS#4

_B_DQS#5

M

M

_B_DQS#6

_B_DQS#7

M

_B_DQS0

M

M

_B_DQS1

_B_DQS2

M

M

_B_DQS3

_B_DQS4

M

M

_B_DQS5

M

_B_DQS6

_B_DQS7

M

M

_B_A0

_B_A1

M

_B_A2

M

_B_A3

M

M

_B_A4

_B_A5

M

_B_A6

M

M

_B_A7

M

_B_A8

M

_B_A9

_B_A10

M

_B_A11

M

M

_B_A12

M

_B_A13

_B_A14

M

M

_B_A15

B5

DQ[0]

SB_

A5

DQ[1]

SB_

C3

SB_

DQ[2]

B3

SB_

DQ[3]

E4

DQ[4]

SB_

A6

DQ[5]

SB_

A4

DQ[6]

SB_

C4

SB_

DQ[7]

D1

DQ[8]

SB_

D2

DQ[9]

SB_

F2

SB_

DQ[10]

F1

SB_

DQ[11]

C2

SB_

DQ[12]

F5

DQ[13]

SB_

F3

DQ[14]

SB_

G4

SB_

DQ[15]

H6

SB_

DQ[16]

G2

DQ[17]

SB_

J6

DQ[18]

SB_

J3

SB_

DQ[19]

G1

DQ[20]

SB_

G5

SB_

DQ[21]

J2

DQ[22]

SB_

J1

DQ[23]

SB_

J5

SB_

DQ[24]

K2

DQ[25]

SB_

L3

DQ[26]

SB_

M1

DQ[27]

SB_

K5

SB_

DQ[28]

K4

DQ[29]

SB_

M4

DQ[30]

SB_

N5

DQ[31]

SB_

DQ[32]

SB_

SB_

DQ[33]

DQ[34]

SB_

SB_

DQ[35]

DQ[36]

SB_

SB_

DQ[37]

DQ[38]

SB_

DQ[39]

SB_

SB_

DQ[40]

DQ[41]

SB_

SB_

DQ[42]

DQ[43]

SB_

SB_

DQ[44]

SB_

DQ[45]

SB_

DQ[46]

DQ[47]

SB_

DQ[48]

SB_

SB_

DQ[49]

DQ[50]

SB_

SB_

DQ[51]

DQ[52]

SB_

SB_

DQ[53]

SB_

DQ[54]

DQ[55]

SB_

DQ[56]

SB_

DQ[57]

SB_

SB_

DQ[58]

DQ[59]

SB_

SB_

DQ[60]

DQ[61]

SB_

SB_

DQ[62]

SB_

DQ[63]

BS[0]

SB_

W5

SB_

BS[1]

R7

SB_

BS[2]

CAS#

SB_

Y7

SB_

RAS#

WE#

SB_

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

B_DM0

B_DM1

B_DM2

B_DM3

B_DM4

B_DM5

B_DM6

B_DM7

1

_B_CLK0 <15>

M

M

_B_CLK0# <15>

_B_CKE0 <15>

M

M

_B_CLK1 <15>

_B_CLK1# <15>

M

_B_CKE1 <15>

M

M_

B_CS#0 <15>

B_CS#1 <15>

M_

M

_B_ODT0 <15>

_B_ODT1 <15>

M

M

_B_DM[7:0] <15>

_B_DQS#[7:0] <15>

M

_B_DQS[7:0] <15>

M

_B_A[15:0] <15>

M

Clarksfield/Auburndale

Clarksfield/Auburndale

Clarksfield/Auburndale

Channel A DQ[15,32,48,54], DM[5]

Requires minimum 12mils spacing

with all other signals, including data signals.

A A

5

4

3

Channel B DQ[16,18,36,42,56,57,60,61,62]

Requires minimum 12mils spacing

with all other signals, including data signals.

Clarksfield/Auburndale

2

Q

Q

Q

uanta Computer Inc.

uanta Computer Inc.

uanta Computer Inc.

PROJECT :

PROJECT :

Si

Si

Si

ze Document Number Re v

ze Document Number Re v

ze Document Number Re v

AUBURNDA 2/4

AUBURNDA 2/4

AUBURNDA 2/4

Date: Sheet

Date: Sheet

Date: Sheet

PROJECT :

ZQH

ZQH

ZQH

54

54

54

1

of

of

of

1A

1A

1A

5Monday, March 14, 2011

5Monday, March 14, 2011

5Monday, March 14, 2011

Page 6

5

WWW.AliSaler.Com

U22

U22

F

35

AG

AG

34

33

AG

AG

32

AG

31

30

AG

29

AG

AG

28

27

AG

AG

26

AF

35

34

AF

AF

33

32

AF

31

AF

AF

30

AF

29

28

AF

AF

27

26

AF

AD

35

AD

34

33

AD

AD

32

AD

31

30

AD

AD

29

AD

28

AD

27

AD

26

35

AC

34

AC

AC

33

32

AC

31

AC

AC

30

29

AC

AC

28

27

AC

26

AC

AA3

5

AA3

4

3

AA3

AA3

2

1

AA3

AA3

0

AA2

9

8

AA2

AA2

7

AA2

6

5

Y3

4

Y3

Y3

3

2

Y3

Y3

1

0

Y3

9

Y2

Y2

8

7

Y2

6

Y2

V3

5

4

V3

V3

3

2

V3

1

V3

V3

0

V2

9

8

V2

V2

7

V2

6

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

5

P3

P34

P3

3

2

P3

P31

P3

0

9

P2

P2

8

P2

7

6

P2

Clarksfield/Auburndale

Clarksfield/Auburndale

F

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

CC11

V

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

CC28

V

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

V

CC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

V

CC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

CPU Core Power

ARD:

48A

CC_CORE

10U/6.3V_8

10U/6.3V_8

22U/6.3V_8

22U/6.3V_8

10U/6.3V_8

10U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

22U/6.3V_8

22U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

0.1u/10V_4_X7R

0.1u/10V_4_X7R

0.1u/10V_4_X7R

0.1u/10V_4_X7R

+

+

330u/2V_7343

330u/2V_7343

+

+

330u/2V_7343

330u/2V_7343

+V

CFD:52A

C568

C568

C626

C626

C234

C234

C589

D D

C C

B B

A A

C589

C623

C623

C643

C643

C

C

C

C

C567

C567

C640

C640

C230

C230

C588

C588

C235

C235

C569

C569

C297

C297

C624

C624

C621

C621

C638

C638

C625

C625

C566

C566

C622

C622

C266

C266

C265

C265

C236

C236

C641

C641

C287

C287

C232

C232

C633

C633

C275

C275

C271

C271

C284

C284

C285

C285

642

642

590

590

AUBURNDALE/CLARKSFIELD PROCESSOR (POWER)

5

4

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

C_DPRSLPVR

PRO

CPU VIDS

CPU VIDS

VTT

VSS_SEN

SENSE LINES

SENSE LINES

4

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VT

T0_10

T

T0_11

V

T0_12

VT

VT

T0_13

T0_14

VT

T0_15

VT

VT

T0_16

VT

T0_17

T0_18

VT

VT

T0_19

T0_20

VT

VT

T0_21

VT

T0_22

T0_23

VT

VT

T0_24

VT

T0_25

T0_26

VT

VT

T0_27

T

T0_28

V

VT

T0_29

VT

T0_30

T0_31

VT

T0_32

VT

VT

T0_33

T0_34

VT

VT

T0_35

T0_36

VT

T0_37

VT

VT

T0_38

VT

T0_39

T0_40

VT

VT

T0_41

V

T0_42

T

VT

T0_43

VT

T0_44

VID

VID

VID

VID

VID

VID

VID

_SELECT

ISEN

_SENSE

VCC

VSS_SENSE

VTT_SENSE

SE_VTT

AH14

_1

AH12

_2

AH11

_3

AH10

_4

J14

_5

J13

_6

H14

_7

H12

_8

G14

_9

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

H_

PSI#

AN

33

PSI#

H_V

AK35

[0]

H_V

AK33

[1]

H_V

AK34

[2]

H_V

AL35

[3]

H_

V

AL33

[4]

H_V

AM33

[5]

H_V

AM35

[6]

H_DP

AM34

G15

H_VTTVID1=Low, 1.1V

H_VTTVID1=High, 1.05V

AN35

SE

AJ34

AJ35

VTT_SENSE

B15

VSS_SENSE_VT

A15

ID0

ID1

ID2

ID3

ID4

ID5

ID6

RSLPVR

R104

R104

R103

R103

C658

C658

C657

C657

C634

C634

C

C

C

C

C649

C649

C644

C644

C659

C659

C652

C652

C331

C331

C313

C313

C326

C326

327

327

648

648

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

C31

C31

6

6

+

+

330u/2V_7343

330u/2V_7343

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

22U/6.3V_8

100/F_4

100/F_4

100/F_4

100/F_4

T

VTT Rail Values are

Auburndal VTT=1.05V

Clarksfield VTT=1.1V

H_PSI

H_

H_V

H_V

H_V

H_V

H_V

H_V

H_DP

CC_CORE

+V

T75T75

T74T74

18A

V

05V

+1.

# <30>

ID0 <30>

ID1 <30>

ID2 <30>

ID3 <30>

ID4 <30>

ID5 <30>

ID6 <30>

RSLPVR <30>

I_MO

VCCSENSE <30>

VSSSENSE

+1.

N <30>

05V

<30>

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR (GRAPHICS POWER)

U22

U22

G

*1K/F_4

*1K/F_4

1K_4

1K_4

1K_4

1K_4

*1K/F_4

*1K/F_4

1K_4

1K_4

*1K/F_4

*1K/F_4

1K_4

1K_4

1K_4

1K_4

*1K/F_4

*1K/F_4

*1K/F_4

*1K/F_4

1K_4

1K_4

*1K/F_4

*1K/F_4

*1K/F_4

*1K/F_4

AR

AR

AR

AR

AP2

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AH21

AH19

AH18

AH16

21

AT

AT

19

AT

18

16

AT

21

19

18

16

AJ21

AJ19

AJ18

AJ16

J24

J23

H25

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

1

VAXG

VAXG1

VAXG1

VAXG1

VAXG1

VAXG1

VAXG1

VAXG1

VAXG1

VAXG1

VAXG1

VAXG2

VAXG2

VAXG2

VAXG2

VAXG2

VAXG2

VAXG

VAXG2

VAXG2

VAXG2

VAXG3

VAXG3

VAXG3

VAXG3

VAXG3

VAXG3

VAXG3

VTT

VT

VTT

VTT

VTT

VTT

VTT

VT

VTT

VTT

VTT

VTT

VTT

VTT

Clarksfield/Auburndale

Clarksfield/Auburndale

G

9

0

1

2

GRAPHICS

GRAPHICS

3

4

5

6

7

8

9

0

1

2

3

4

5

2

6

7

8

9

0

1

2

3

4

5

6

FDI PEG & DMI

FDI PEG & DMI

1_45

1_46

T

1_47

1_48

1_49

1_50

1_51

1_52

T

1_53

1_54

1_55

1_56

1_57

1_58

+1.

05V

HFM_VID : Max 1.4V

LFM_VID : Min 0.65V

2

VAXG_

VSSAXG_

SENSE

LINES

SENSE

LINES

GF

F

G

GF

GF

GF

GF

GF

GF

X_VR_EN

X_DPRSLPVR

GF

GFX_

GRAPHICS VIDs

GRAPHICS VIDs

POWER

POWER

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VTT0

VTT0

VTT0

VTT0

VTT1

VTT1

VTT1

1.1V1.8V

1.1V1.8V

VTT1

VTT1

V

VCCP

VCCP

VCCP

SENSE

SENSE

X_VID[0]

X_VID[1]

X_VID[2]

X_VID[3]

X_VID[4]

X_VID[5]

X_VID[6]

IMON

VDDQ

DDQ

V

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

TT1

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

1

AF1

2

AE7

3

AE4

4

AC1

5

AB7

6

AB4

7

Y1

8

W7

9

W4

10

U1

11

T7

12

T4

13

P1

14

N7

15

N4

16

L1

17

H1

18

P10

_59

N10

_60

_61

_62

_63

_64

_65

_66

_67

_68

LL1

LL2

LL3

C660

C660

L10

C654

C654

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

Si

Si

Si

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

22A

VGF

X_AXG

+

+

+

C635

C635

330U/2V_7343

330U/2V_7343

*

*

+

+

C651

C651

330U/2V_7343

330U/2V_7343

*

*

+1.

05V

C332

C332

0U/6.3V_8

0U/6.3V_8

1

1

3

22u/6.3V_8

22u/6.3V_8

10u/6.3V_8

10u/6.3V_8

C31

C31

1

1

10U/6.3V_8

10U/6.3V_8

6

6

C65

C65

10U/6.3V_8

10U/6.3V_8

1

1

1

0

0

1

0

1

0

Note:

For Validating IMVP VR R6451 should be STUFF

and R2N1 NO_STUFF

0

0

1

1

C28

C28

C28

C28

22u/6.3V_8

22u/6.3V_8

9

C655

C655

22u/

22u/

C312

C312

22u/

22u/

PSI#

ID0

ID1

ID2

ID4

ID5

6.3V_8

6.3V_8

6.3V_8

6.3V_8

RSLPVR

9

C29

C29

10u/6.3V_8

10u/6.3V_8

0

0

C33

C33

22u/6.3V_8

22u/6.3V_8

R388 1K_4R388 1K_4

R395

R395

R387

R387

R394 *1K/F_4R394 *1K/F_4

R389

R389

R396

R396

R400 *1K/F_4R400 *1K/F_4

R409

R409

R401

R401

R410

R410

R404

R404

R413

R413

R402

R402

R411

R411

R403 1K_4R403 1K_4

R412

R412

R419

R419

R418 1K_4R418 1K_4

8

8

C29

C29

H_V

H_V

H_V

H_VID3

H_V

H_V

H_VID6

H_DP

H_

T72T72

T73T7

8

8

C35

C35

C35

C35

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C36

C36

C41

C41

7

7

22U/6.3V_8

22U/6.3V_8

1U/6.3V_4

1U/6.3V_4

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

10U/6.3V_8

0.6A

AUBURNDA 3/

AUBURNDA 3/

AUBURNDA 3/

onday, March 14, 2011

onday, March 14, 2011

onday, March 14, 2011

VCC

_AXG_SENSE <33>

VSS_AXG_SENSE

3

GFX_VI

D0 <33>

GFX_VI

D1 <33>

GFX_VI

D2 <33>

D3 <33>

GFX_VI

D4 <33>

GFX_VI

GFX_VI

D5 <33>

GFX_VI

D6 <33>

GFX_ON

<33>

PRSLPVR <33>

GFX_D

MON <33>

GFX_I

6

6

5

5

C35

C35

1U/6.3V_4

1U/6.3V_4

C35

C35

0

0

22U/6.3V_8

22U/6.3V_8

+1.

05V

C61

C61

810U/6.3V_8

810U/6.3V_8

C63

C63

010U/6.3V_8

010U/6.3V_8

8V

+1.

822U/6.3V_8

822U/6.3V_8

C25

C25

C27

C27

44.7U/6.3V_6

44.7U/6.3V_6

C23

C23

12.2U/6.3V_6

12.2U/6.3V_6

31U/6.3V_4

31U/6.3V_4

C23

C23

91U/6.3V_4

91U/6.3V_4

C23

C23

Quanta

Quanta

Quanta

PROJECT :

PROJECT :

PROJECT :

4 (PWR)

4 (PWR)

4 (PWR)

1

<33>

3A

ARD:

CFD:6A

+1

.5VSUS

2

2

C35

C35

1U/6.3V_4

1U/6.3V_4

+

+

C36

C36

7

7

3

3

330U/2V_7343

330U/2V_7343

Computer Inc.

Computer Inc.

Computer Inc.

ZQH

ZQH

ZQH

645M

645M

645M

of

of

of

1A

1A

1A

Page 7

5

AUBURNDALE/CLARKSFIELD PROCESSOR (GND)

22H

22H

U

U

0

AT2

VSS1

AT1

7

VSS2

AR3

1

VSS3

AR2

8

VSS4

AR2

6

VSS5

4

AR2

VSS6

AR2

3

VSS7

0

AR2

VSS8

7

AR1

VSS9

AR15

0

VSS1

D D

C C

B B

AR12

VSS1

AR9

VSS1

AR6

VSS1

AR3

VSS1

AP20

VSS1

AP17

VSS1

AP13

VSS1

AP10

VSS1

AP7

VSS1

AP4

VSS2

AP2

VSS2

AN34

VSS2

AN31

VSS2

AN23

VSS2

AN20

VSS2

AN17

VSS26

AM29

VSS2

AM27

VSS2

AM25

VSS2

AM20

VSS30

AM17

VSS3

AM14

VSS32

AM11

VSS3

AM8

VSS3

AM5

VSS3

AM2

VSS3

AL34

VSS3

AL31

VSS3

AL23

VSS3

AL20

VSS4

AL17

VSS4

AL12

VSS4

AL9

VSS4

AL6

VSS4

AL3

VSS4

AK29

VSS4

AK27

VSS4

AK25

VSS4

AK20

VSS4

AK17

VSS5

AJ31

VSS5

AJ23

VSS5

AJ20

VSS5

AJ17

VSS5

AJ14

VSS5

AJ11

VSS5

AJ8

VSS5

AJ5

VSS5

AJ2

VSS5

AH35

VSS6

AH34

VSS6

AH33

VSS6

AH32

VSS6

AH31

VSS6

AH30

VSS6

AH29

VSS6

AH28

VSS6

AH27

VSS6

AH26

VSS6

AH20

VSS7

AH17

VSS7

AH13

VSS7

AH9

VSS7

AH6

VSS7

AH3

VSS7

AG10

VSS7

AF8

VSS7

AF4

VSS7

AF2

VSS7

AE35

VSS8

Clarksfield/Auburndale

Clarksfield/Auburndale

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

7

8

9

1

3

4

5

6

7

VSS

VSS

8

9

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

0

VSS8

VSS8

VSS8

VSS8

VSS8

VSS8

VSS8

VSS8

VSS8

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS9

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS106

VSS1

VSS1

VSS1

VSS110

VSS1

VSS112

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

VSS1

AE34

1

AE33

2

AE32

3

AE31

4

AE30

5

AE29

6

AE28

7

AE27

8

AE26

9

AE6

0

AD10

1

AC8

2

AC4

3

AC2

4

AB35

5

AB34

6

AB33

7

AB32

8

AB31

9

AB30

00

AB29

01

AB28

02

AB27

03

AB26

04

AB6

05

AA10

Y8

07

Y4

08

Y2

09

W35

W34

11

W33

W32

13

W31

14

W30

15

W29

16

W28

17

W27

18

W26

19

W6

20

V10

21

U8

22

U4

23

U2

24

T35

25

T34

26

T33

27

T32

28

T31

29

T30

30

T29

31

T28

32

T27

33

T26

34

T6

35

R10

36

P8

37

P4

38

P2

39

N35

40

N34

41

N33

42

N32

43

N31

44

N30

45

N29

46

N28

47

N27

48

N26

49

N6

50

M10

51

L35

52

L32

53

L29

54

L8

55

L5

56

L2

57

K34

58

K33

59

K30

60

22I

22I

U

U

K27

VSS1

K9

VSS1

K6

VSS1

K3

VSS1

J32

VSS1

J30

VSS1

J21

VSS1

J19

VSS1

H35

VSS1

H32

VSS1

H28

VSS1

H26

VSS1

H24

VSS1

H22

VSS1

H18

VSS1

H15

VSS1

H13

VSS1

H11

VSS1

H8

VSS1

H5

VSS1

H2

VSS1

G34

VSS1

G31

VSS1

G20

VSS184

G9

VSS1

G6

VSS1

G3

VSS1

F30

VSS188

F27

VSS1

F25

VSS190

F22

VSS1

F19

VSS1

F16

VSS1

E35

VSS1

E32

VSS1

E29

VSS1

E24

VSS1

E21

VSS1

E18

VSS1

E13

VSS2

E11

VSS2

E8

VSS2

E5

VSS2

E2

VSS2

D33

VSS2

D30

VSS2

D26

VSS2

D9

VSS2

D6

VSS2

D3

VSS2

C34

VSS2

C32

VSS2

C29

VSS2

C28

VSS2

C24

VSS2

C22

VSS2

C20

VSS2

C19

VSS2

C16

VSS2

B31

VSS2

B25

VSS2

B21

VSS2

B18

VSS2

B17

VSS2

B13

VSS2

B11

VSS2

B8

VSS2

B6

VSS2

B4

VSS2

A29

VSS2

A27

VSS2

A23

VSS2

A9

VSS2

Clarksfield/Auburndale

Clarksfield/Auburndale

4

3

2

1

AUBURNDALE/CLARKSFIELD PROCESSOR( RESERVED, CFG)

2E

2E

U2

U2

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

85

86

87

89

91

92

93

94

95

VSS

VSS

96

97

98

99

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

NCTF

NCTF

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

VSS_

NCTF1

NCTF2

NCTF3

NCTF4

NCTF5

NCTF6

NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

TP20TP20

TP22TP22

TP34TP34

VREF_

VREF_

DQ_DIMM0<14>

DQ_DIMM1<15>

TP25TP25

TP26TP26

AP2

5

RSVD1

A

L25

RSVD2

L24

A

RSVD3

A

L22

RSVD4

33

AJ

RSVD5

9

AG

RSVD6

7

M2

RSVD7

L28

RSVD8

J17

DIMM_VREF

SA_

H17

SB_

DIMM_VREF

G25

1

RSVD1

G17

RSVD1

2

E31

RSVD1

3

E30

RSVD1

4

CF

G0

AM30

G[0]

CF

AM28

CFG[1]

AP31

G[2]

CF

G3

G4

CF

G7

CF

CF

AL32

CF

AL30

CF

AM31

CFG[5]

AN29

CF

AM32

CFG[7]

AK32

CF

AK31

CF

AK28

CF

AJ28

CF

AN30

CF

AN32

CF

AJ32

CF

AJ29

CF

AJ30

CF

AK30

CF

H16

RSVD_

B19

RSVD1

A19

RSVD1

A20

RSVD1

B20

RSVD1

U9

RSVD1

T9

RSVD2

AC9

RSVD2

AB9

RSVD2

C1

RSVD_

A3

RSVD_

J29

RSVD2

J28

RSVD2

A34

RSVD_

A33

RSVD_

C35

RSVD_

B35

RSVD_

Clarksfield/Auburndale

Clarksfield/Auburndale

G[3]

G[4]

G[6]

G[8]

G[9]

G[10]

G[11]

G[12]

G[13]

G[14]

G[15]

G[16]

G[17]

TP_86

5

6

7

8

9

0

1

2

NCTF_23

NCTF_24

6

7

NCTF_28

NCTF_29

NCTF_30

NCTF_31

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RESERVED

RESERVED

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD_

RSVD3

RSVD3

RSVD3

RSVD3

RSVD3

NCTF_37

RSVD3

RSVD3

NCTF_40

NCTF_41

NCTF_42

NCTF_43

RSVD4

RSVD4

RSVD47

RSVD4

RSVD4

RSVD5

RSVD51

RSVD5

RSVD53

NCTF_54

NCTF_55

NCTF_56

NCTF_57

RSVD5

TP_59

TP_60

KEY

RSVD6

RSVD6

RSVD6

RSVD6

TP_66

TP_67

TP_68

TP_69

TP_70

TP_71

TP_72

TP_73

TP_74

TP_75

TP_76

TP_77

TP_78

TP_79

TP_80

TP_81

TP_82

TP_83

TP_84

TP_85

VSS

AJ13

2

AJ12

3

AH25

4

AK26

5

AL26

6

AR2

AJ26

8

AJ27

9

AP1

AT2

AT3

AR1

AL28

5

AL29

6

AP30

AP32

8

AL27

9

AT31

0

AT32

AP33

2

AR33

AT33

AT34

AP35

AR35

AR32

8

E15

F15

A2

D15

2

C15

3

AJ15

4

5

TP8TP8

AH15

TP9TP9

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP3

4

TP19TP19

P34 can be NC on CRB; EDS/DG suggestion to GND

A

Processor Strapping

CFG0

10

(PCI-Epress

Configuration Select)

CFG3

(PCI-Epress Static

Lane Reversal)

A A

5

CFG4

(Embended

Display Port Presence)

7

V

K

,

S

H

D

Q

H

F

Q

W

F

&

R

G

H

L

O

P

O

I

D

S

%

L

U

R

*

U

F

N

Single PEG

Bifurcation enabled

Normal Operation Lane Numbers Reversed

Enabl

sabled; No Physical Display Port

Di

attached to Embedded Diplay Port

4

ed; An external Display port

device is connected to the Embedded

Display port

3

DEFAULT

1

1

1

CF

G0

128 *3.01K_NC

128 *3.01K_NC

R

R

CF

G3

125 3.01K/F_4

125 3.01K/F_4

R

R

CFG4

R

R

127 *3.01K

127 *3.01K

G7

CF

R126 *3.01K/F_4R126 *3.01K/F_4

puter Inc.

puter Inc.

Quanta Com

Quanta Com

Quanta Com

PROJECT :

PROJECT :

Si

Si

Si

ze Document Number Rev

ze Document Number Rev

ze Document Number Rev

AUBURNDA 4/4

AUBURNDA 4/4

AUBURNDA 4/4

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

1

puter Inc.

ZQH

ZQH

ZQH

745Monday, March 14, 2011

745Monday, March 14, 2011

745Monday, March 14, 2011

1A

1A

1A

Page 8

5

WWW.AliSaler.Com

IBEX PEAK-M (DMI,FDI,GPIO)

4

3

2

1

AC-coupling CAP place close to PCH

C

C

U21

U21

DBRST#

PWR_ACK_R

ACI

PM_

BATLOW#

PM_

RI#

BC24

DMI0

RXN

BJ22

RXN

DMI1

AW20

DMI2

RXN

BJ20

RXN

DMI3

BD24

RXP

DMI0

BG22

I1

RXP

DM

BA20

RXP

DMI2

BG20

DMI3

RXP

BE22

DMI0

TXN

BF21

DMI1

TXN

BD20

DMI2

TXN

BE18

TXN

DMI3

BD22

TXP

DMI0

BH21

TXP

DMI1

BC20

TXP

DMI2

BD18

DMI3

TXP

BH25

DMI_

ZCOMP

BF25

DMI_

IRCOMP

T6

RESET#

SYS_

M6

PWROK

SYS_

B17

PWRO

K

K5

MEPW

ROK

A10

N_RST#

LA

D9

DRAMP

WROK

C16

R

ST#

RSM

M1

SUS_PW

R_DN_ACK / GPIO30

P5

N#

PWRBT

N_R

P7

ACPRESENT

A6

BA

TLOW# / GPIO72

F14

RI#

IbexPeak-M_R1P0

IbexPeak-M_R1P0

DMI

FDI

DMI

FDI

CLKRUN#

SUS_ST

AT# / GPIO61

SCLK / GPIO62

SU

SL

P_S5# / GPIO63

/

GPIO31

System Power Management

System Power Management

SL

P_LAN# / GPIO29

RXN0<4>

DMI_

DMI_

D D

C C

DBRST#<4>

XDP_

SYS_PW

PM_

DRAM_PWRGD<4>

ICH_RS

B B

RXN1<4>

DMI_

RXN2<4>

DMI_

RXN3<4>

RXP0<4>

DMI_

RXP1<4>

DMI_

RXP2<4>

DMI_

DMI_

RXP3<4>

DMI_

TXN0<4>

TXN1<4>

DMI_

TXN2<4>

DMI_

TXN3<4>

DMI_

DM

I_TXP0<4>

DM

I_TXP1<4>

DM

I_TXP2<4>

I_TXP3<4>

DM

1 49.9/F _4

1 49.9/F _4

R44

R44

+1.0

5V

XDP_

ROK

RSV

_ICH_LAN_RST#

MRST#<27>

SUS_

BSWON#<27>

DN

R24

R24

6 *0_4

PCH_

ACIN<27>

6 *0_4

FD

FD

FD

FD

FD

FD

FD

F

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

FDI_

I_LSYNC0

FD

I_LSYNC1

FD

PMSY

I_RXN0

I_RXN1

I_RXN2

I_RXN3

I_RXN4

I_RXN5

I_RXN6

D

I_RXN7

RXP0

RXP1

RXP2

RXP3

RXP4

RXP5

RXP6

RXP7

FD

I_INT

FSYNC0

FSYNC1

WAKE#

/ GPIO32

P_

SL

SLP_

SLP_

TP

NCH

BA18

BH17

BD16

BJ16

BA16

BE14

BA14

BC12

BB18

BF17

BC16

BG16

AW16

BD14

BB14

BD12

BJ14

BF13

BH13

BJ12

BG14

2

J1

Y1

P8

R2

R2

34 *Short_4

34 *Short_4

F3

E4

H7

S4#

P12

S3#

R225

R225

SLP_

M#

K8

M#

N2

2

3

BJ10

PM

_SLP_LAN#

F6

_TXN0 <4>

FDI

_TXN1 <4>

FDI

FDI

_TXN2 <4>

FDI

_TXN3 <4>

FDI

_TXN4 <4>

FDI

_TXN5 <4>

_TXN6 <4>

FDI

_TXN7 <4>

FDI

FD

I_TXP0 <4>

FD

I_TXP1 <4>

FD

I_TXP2 <4>

I_TXP3 <4>

FD

I_TXP4 <4>

FD

I_TXP5 <4>

FD

I_TXP6 <4>

FD

FD

I_TXP7 <4>

*0_4

*0_4

TP32TP3

TP18TP1

H_SUSCLK <27>

IC

2

8

I_INT <4>

FD

I_FSYNC0 <4>

FD

FD

I_FSYNC1 <4>

FD

I_LSYNC0 <4>

I_LSYNC1 <4>

FD

E_WAKE# <18,19>

PCI

CLK

RUN# <27>

# <27>

SUSC

SUSB#

<27>

PM_

SYNC <4>

INT_

INT_

INT

_LVDS_BLON<16>

INT

_LVDS_DIGON<16>

INT

_LVDS_BRIGHT<16>

LVDS_EDIDCLK<16>

INT_