YAMAHA YMF753 Datasheet

YMF753

AC’97 Revision2.2 Audio CODEC

with Digital Audio I/F

OVERVIEW

YMF753 is an AC’97 Audio CODEC LSI, which is fully compliant with the industry standard “Audio

CODEC ’97” component specification (Revision 2.2).

Different from former AC’97, YMF753 supports new features like SPDIF OUT and Zoomed Video Port.

Without using a digital controller, th ese new f eatures can be enhan ced in the AC ’97 sound sy stem that h as an

ICH controller built-in chipset.

Low power con s u mption is supported not on ly in the normal mode but can be controlled in the power-down

mode.

FEATURES

• AC’97 Revision 2.2 Compliant

• Exceeds PC99 / PC2001 Analog Performance Requirement

(Mobile PC Audio Performance Compliant when analog low power supply is used.)

• Analog Inputs :

- 4 Stereo Inputs: LINE, CD, VIDEO, AUX

- 2 Monaural Inputs: Speakerphone and PC BEEP Inputs

- 2 Independent Microphone Inputs

• PC BEEP can directly output to Line Out

• Internal +20dB amplifier circuitry for microphone

• Analog Outputs : Stereo LINE Output, True LINE Level and M onaural Output

• Supports Zoomed Video Port

• Supports Consumer IEC958 Output Port (SPDIF OUT)

• SPDIF Output for AC’97 Revision 1.0 Compliant

• Different audio data from AC-Link can be output to SPDIF and Line Out

• Supports 3D Enhancement (Wide Stereo), and Bass / Treble control

• Multiple CODEC Capability

• Programmable Power Down Mode

• Supports EAPD (External Amplifier Power Down)

• Power Supplies : Analog 4.3V to 5.0V, Digital 3.3V or 5.0V

• 48-Pin SQFP Package (YMF753-S)

YAMAHA

CORPORATION

CATALOG No.:LSI-4MF753A2

YMF753 CATALOG

Decembe 3, 1998

March 6, 2001

YMF753

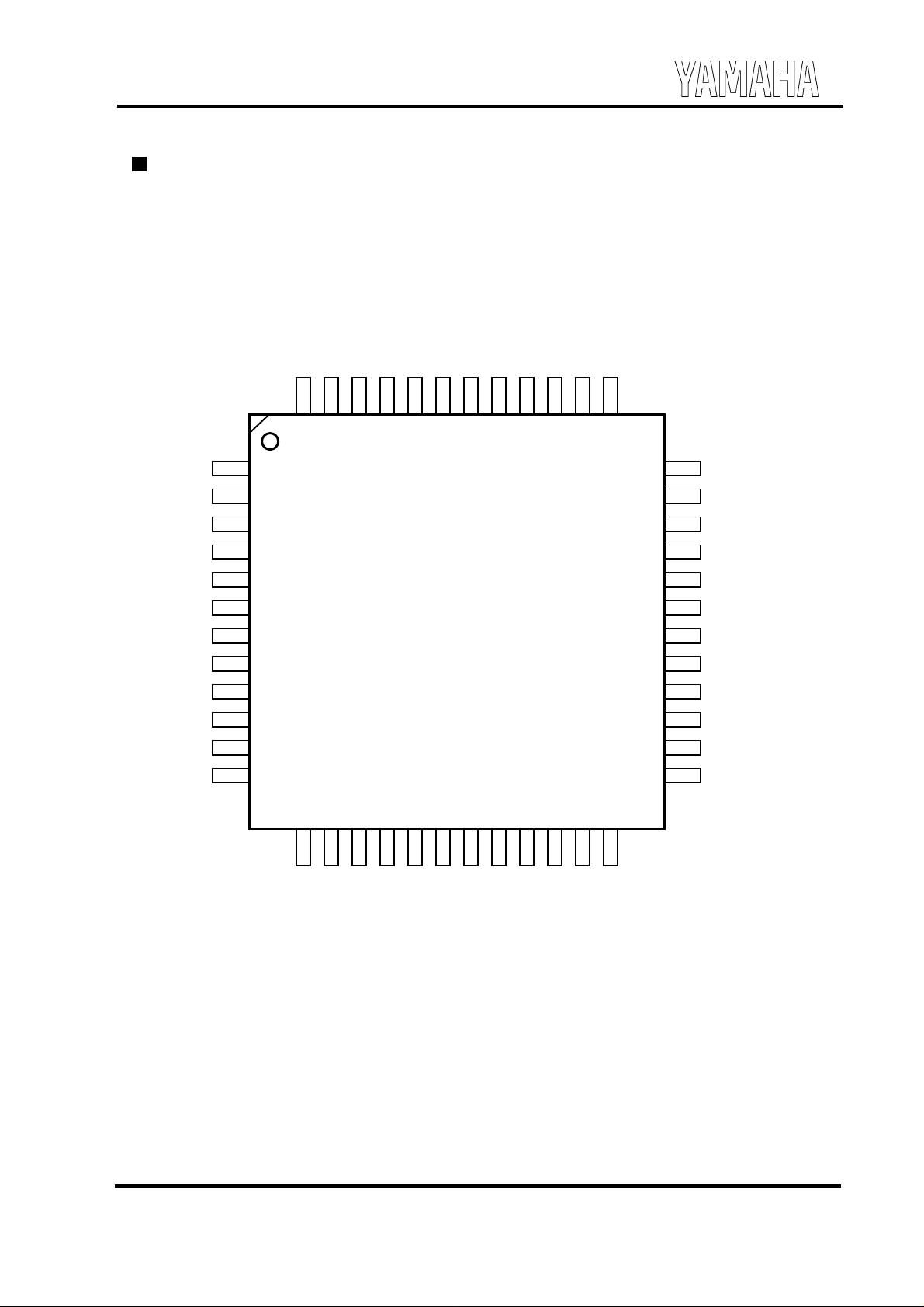

PIN CONFIGURATION

DVdd1

XTL_IN

XTL_OUT

DVss1

SDATA_OUT

BIT_CLK

DVss2

SDATA_IN

DVdd2

SYNC

RESET#

PC_BEEP

1

2

3

4

5

6

7

8

9

10

11

12

ZV_BCK / DIT

EAPD (DIT)

EXT24M / ID1#

Reserved / ID0#

ZV_SIN / Reserved

ZV_LR / DIT

AVss2

LNLVL_OUT_R

MSEL

LNLVL_OUT_L

AVdd2

MONO_OUT

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

13

14

15

16

17

18

19

20

21

22

23

24

LINE_OUT_R

LINE_OUT_L

CAP6

CAP5

CAP4

CAP3

CAP2

CAP1

Vrefout

Vref

AVss1

AVdd1

MIC1

AUX_L

PHONE

AUX_R

VIDEO_L

CD_L

VIDEO_R

CD_R

CD_GND

MIC2

LINE_IN_L

LINE_IN_R

48-Pin SQFP Top View

2

March 6, 2001

YMF753

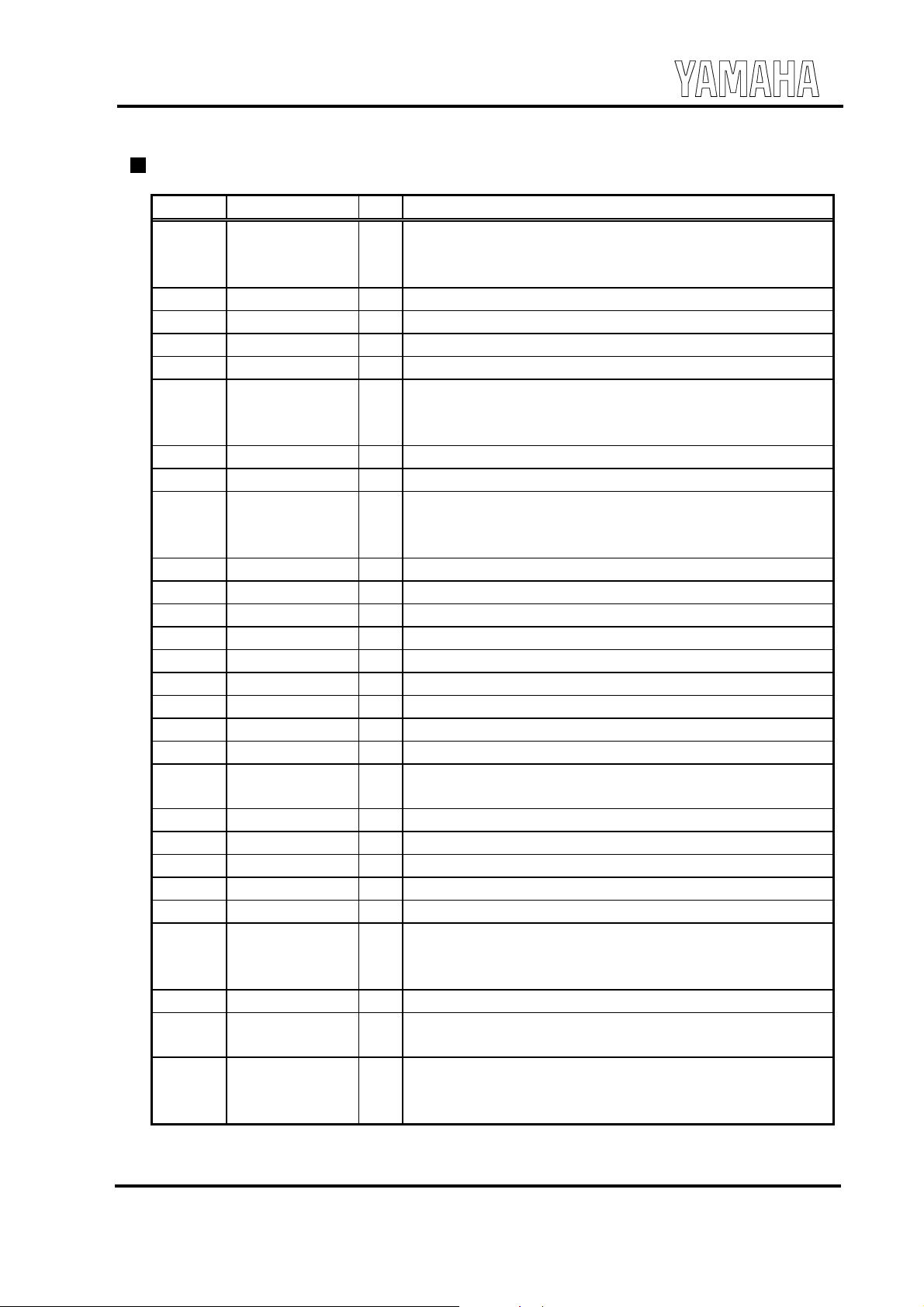

PIN DESCRIPTION

No. Name I/O Function

Digital power supply (Typ. +3.3V / +5.0V)

1 DVdd1 -

2 XTL_IN I 24.576MHz Clock Input

3 XTL_OUT O 24.576MHz Clock Output

4 DVss1 - Digital ground. Connect this pin to DVss2.

5 SDATA_OUT I AC’97 Serial Input Stream

6 BIT_CLK I/O

7 DVss2 - Digital ground. Connect this pin to DVss1.

8 SDATA_IN O AC’97 Serial Output Stream

9 DVdd2 -

10 SYNC I SYNC Input (Fixed at 48kHz)

11 RESET# I Hardware Reset

12 PC_BEEP AI PC Speaker Beep

13 PHONE AI Telephony Input

14 AUX_L AI AUX Input Left Channel

15 AUX_R AI AUX Input Right Channel

16 VIDEO_L AI Video Audio Input Left Channel

17 VIDEO_R AI Video Audio Input Right Channel

18 CD_L AI CD Audio Input Left Channel

19 CD_GND AI

20 CD_R AI CD Audio Input Right Channel

21 MIC1 AI Microphone Input 1

22 MIC2 AI Microphone Input 2

23 LINE_IN_L AI Line Input Left Channel

24 LINE_IN_R AI Line Input Right Channel

25 AVdd1 -

26 AVss1 - Analog ground. Connect this pin to AVss2.

27 Vref AO

28 Vrefout AO

Connect to the digital ground with 0.1mF and 47mF capacitors.

Connect this pin to DVdd2.

AC’97 Bit Clock

As an output pin at the primary codec where CODEC ID=00.

As an input pin at the secondary codec where CODEC ID=01,10,11.

Digital power supply (Typ. +3.3V / +5.0V)

Connect to the digital ground with 0.1mF and 47mF capacitors.

Connect this pin to DVdd1.

CD Audio Analog Ground

Connect this pin to CD Ground or Analog Ground.

Analog Power Supply (Typ. +4.3V to +5.0V)

Connect to the analog ground with 0.1mF and 47mF capacitors.

Connect this pin to AVdd2.

Analog Reference Voltage

Connect to the analog ground with 0.1mF and 22mF capacitors.

Analog Reference Voltage Output

Connect to the analog ground with 0.1mF and 22mF capacitors when

it is used to the external circuit.

3

March 6, 2001

YMF753

No. Name I/O Function

29 CAP1 A Connect to the analog ground with a 2200pF capacitor.

30 CAP2 A Connect to the analog ground with a 0.015mF capacitor.

31 CAP3 A Connect to the analog ground with a 0.01mF capacitor.

32 CAP4 A Connect to the analog ground with a 2200pF capacitor.

33 CAP5 A Connect to the analog ground with a 0.015mF capacitor.

34 CAP6 A Connect to the analog ground with a 0.01mF capacitor.

35 LINE_OUT_L AO Line Output Left Channel

36 LINE_OUT_R AO Line Output Right Channel

37 MONO_OUT AO Monaural Output

Analog power supply (Typ. +4.3V to +5.0V)

38 AVdd2 -

39 LNLVL_OUT_L AO True LINE Level Output Left Channel

40 MSEL I Mode Select, which changes the pin function of No.43 – 46, 48.

41 LNLVL_OUT_R AO True LINE Level Output Right Channel

42 AVss2 - Analog ground. Connect to AVss1.

47 EAPD (DIT) O

Connect to the analog ground with 0.1mF and 47mF capacitors.

Connect this pin to AVdd1.

The function is selected at 62h TX-7 bit.

TX-7=“0”, External Amplifier Power Down

TX-7=“1”, Digital Audio Interface Output (48kHz)

1. MSEL= “High” (Connect to analog power supply.)

No. Name I/O Function

43 ZV_LR I- Zoomed Video Port L/R clock

44 ZV_SIN I- Zoomed Video Port serial data

45 Reserved - Do not connect externally.

46 EXT24M O 24.576MHz clock output

48 ZV_BCK I- Zoomed Video Port bit clock

2. MSEL= “Low” (Connect to analog ground.)

No. Name I/O Function

43 DIT O Digital Audio Interface Output (48kHz)

44 Reserved - Do not connect externally.

45 CODEC ID0# I+ CODEC ID

46 CODEC ID1# I+ CODEC ID

48 DIT O Digital Audio Interface Output (48kHz)

Note) AI: Analog Input Pin, AO: Analog Output Pin, I+: Input Pin with a Pull-up resistor,

I-: Input Pin with a Pull-down resistor

4

March 6, 2001

YMF753

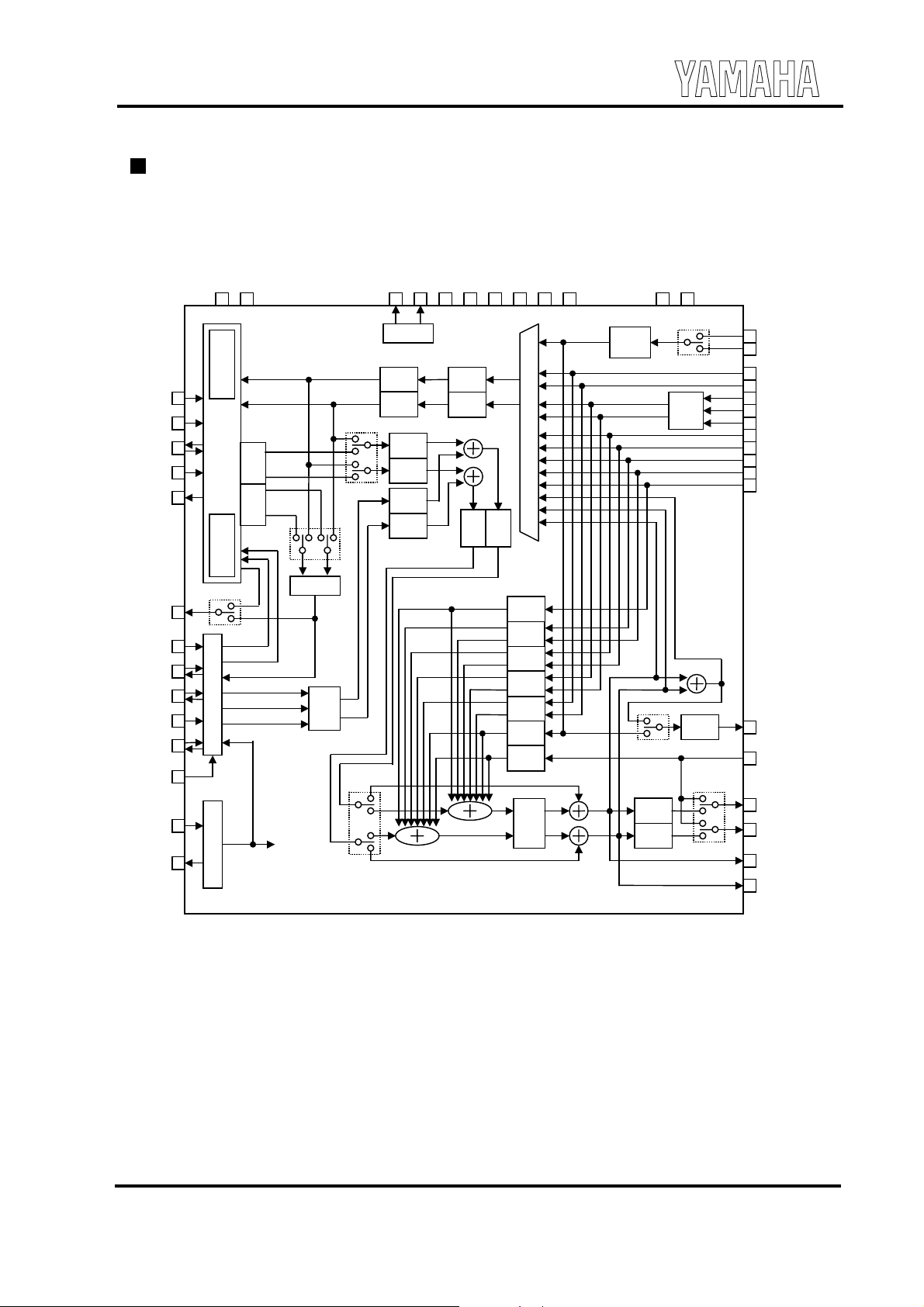

BLOCK DIAGRAM

RESET#

SYNC

BIT_CLK

SDATA_OUT

SDATA_IN

AC’97

digital

I/F

DVdd(2) DVss(2)

Control

Power down

ID0/1# SPSA

Control

Volume

UDS

Vref Vrefout

VREF

A/D

A/D

LPBK

PCM L

32step

PCM R

32step

ZV L

32step

ZV R

32step

Record R

Record L

16step

16step

CAP4

CAP5 CAP6

CAP3 CAP2 CAP1

MUX

D/A

D/A

0dB/

+20dB

CD Right

CD Left

AVss(2)

AVdd(2)

MS

BUF

MIC1

MIC2

LINE_IN_R

LINE_IN_L

CD_R

CD_GND

CD_L

VIDEO_R

VIDEO_L

AUX_R

AUX_L

PHONE

EAPD (DIT)

Reserved / ID0#

EXT24M / ID1#

ZV_LR / DIT

ZV_SIN

/ Reserved

ZV_BCK / DIT

MSEL

XTL_IN

XTL_OUT

TX-7

ID0#

ID1#

DIT

ZV_LR

MUX

ZV_SIN

ZV_BCK

EXT24M

Timing Generator

DIT

PHONE

32step

AUX

32step

VIDEO

32step

CD

32step

Left

LINE

32step

MIC

32step

PC Beep

16step

3D

tone

MIX

Master L

32step

Master R

32step

Monaural

32step

RESET#

MONO_OUT

PC_BEEP

LINE_OUT_L

LINE_OUT_R

LNLVL_OUT_L

LNLVL_OUT_R

ZV

Port

Right

POP

5

March 6, 2001

YMF753

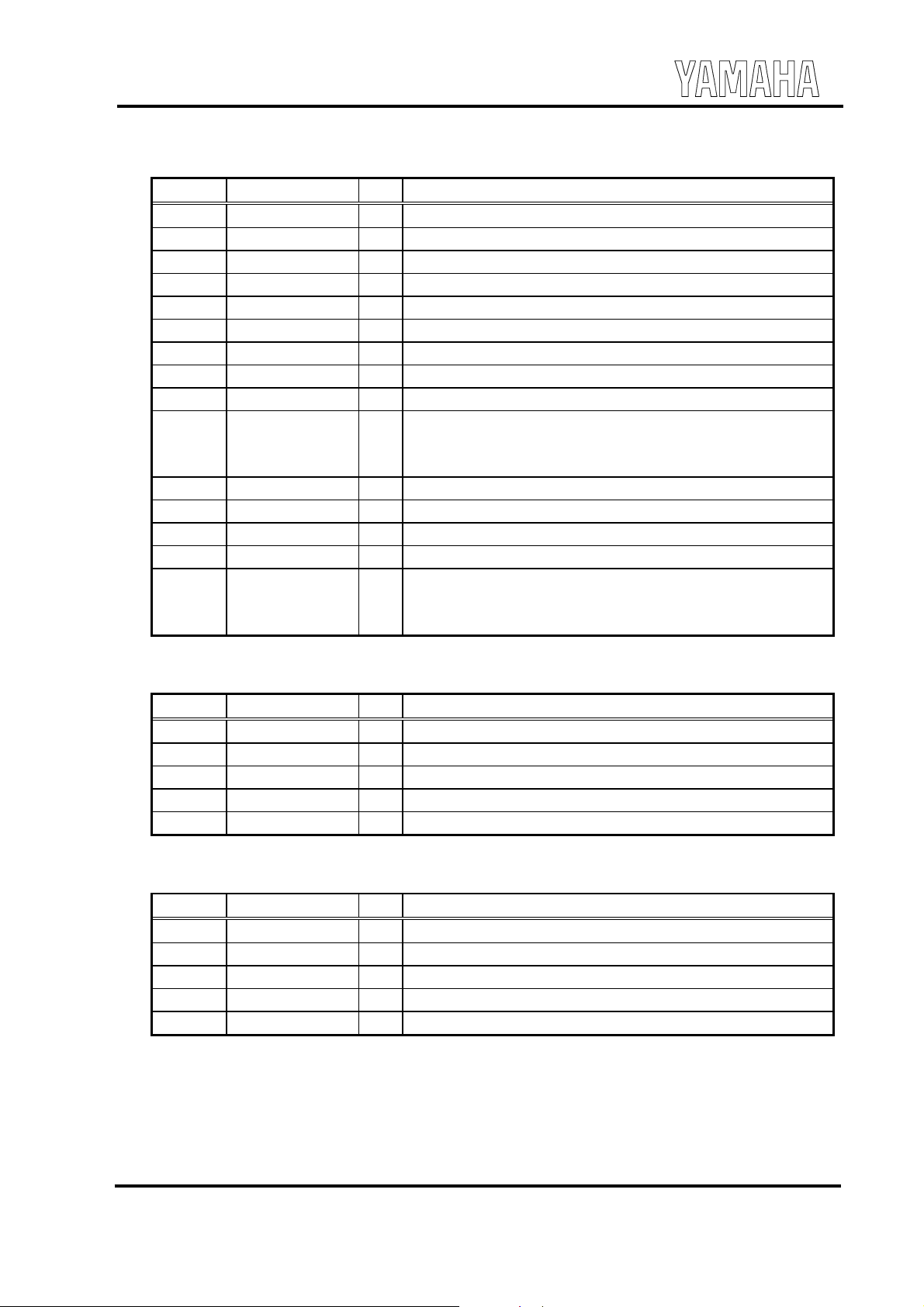

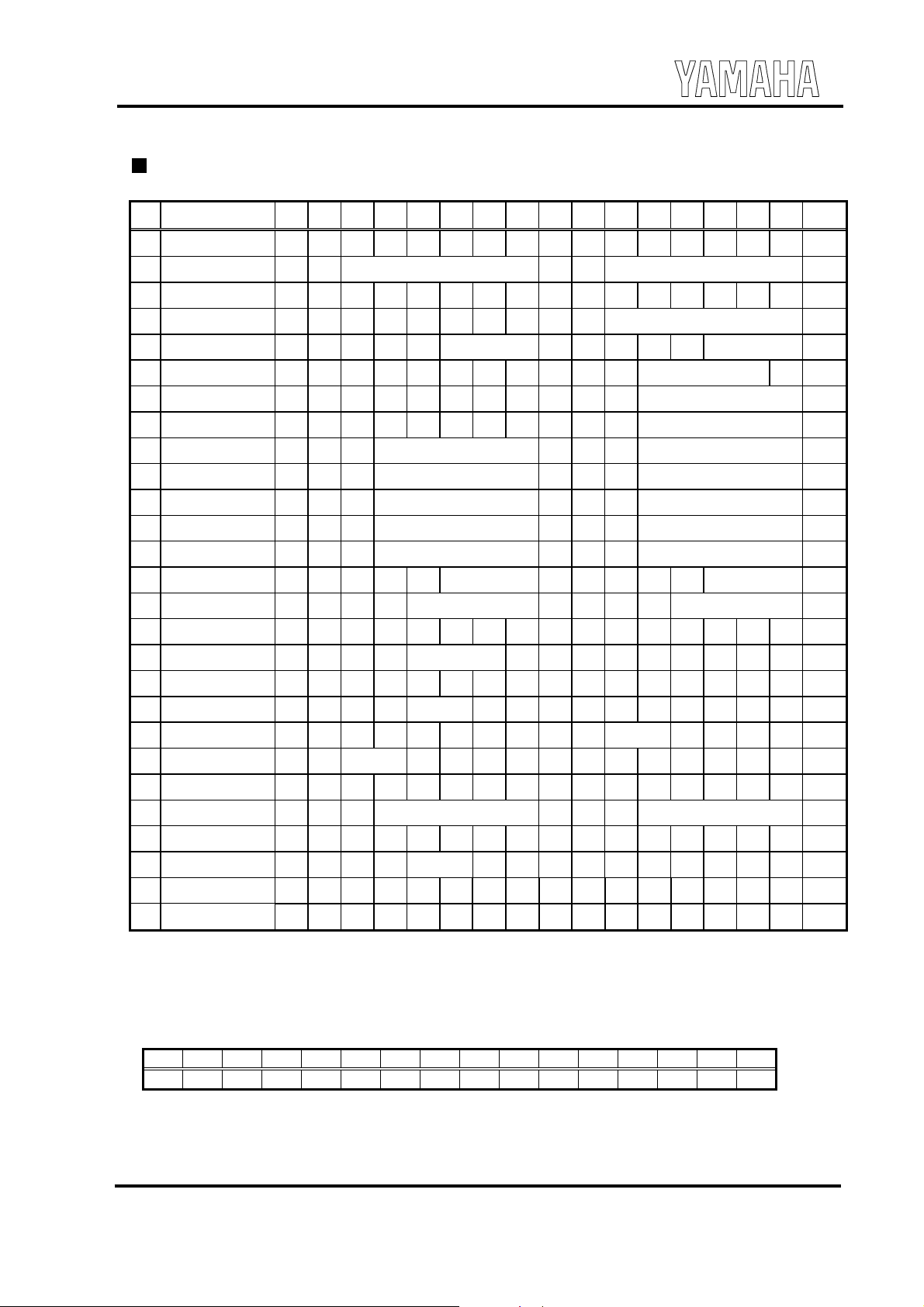

MIXER REGISTERS

NAME D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default

00h Reset “0” “0” “0” “0” “0” “0” “0” “0” “0” “1” “0” “0” “0” “0” “0” “0” 0040h

02h Master vol. Mute - ML5-0 - - MR5-0 8000h

04h LNLVL vol. - - - - - - - - - - - - - - - - 0000h

06h Master vol. Mono Mute - - - - - - - - - MM5-0 8000h

08h Master tone - - - - - BA2-0 - - - - - TR2-0 0707h

0Ah PC_BEEP vol. Mute - - - - - - - - - - PV3-0 - 0000h

0Ch Phone vol. Mute - - - - - - - - - - GN4-0 8008h

0Eh Mic vol. Mute - - - - - - - -

10h Line in vol. Mute - - GL4-0 - - - GR4-0 8808h

12h CD vol. Mute - - GL4-0 - - - GR4-0 8808h

14h Video vol. Mute - - GL4-0 - - - GR4-0 8808h

16h Aux vol. Mute - - GL4-0 - - - GR4-0 8808h

18h PCM out vol. Mute - - GL4-0 - - - GR4-0 8808h

1Ah Record Select - - - - - SL2-0 - - - - - SR2-0 0000h

1Ch Record Gain Mute - - - GL3-0 - - - - GR3-0 8000h

20h General Purpose POP - 3D - - - MIX MS

22h 3D Control - - - - WD3-1 - - - - - - - - - 0000h

26h Power Down

28h E xtended Audi o I D ID1 ID0 - - REV1-0

2Ah Ext Audio Stat/Ctrl - - - - 3Ah DIT Control 1 V - SPSR1-0 GL CC6 CC5 CC4 CC3 CC2 CC1 CC0 PRE

62h Vendor Function * * * * * * * * * * * * TX-7

64h ZV vol. Mute

66h DIT Control 2 - - - - - - - * * * TX-3 * TX-8 DMU UDS

68h 3D Mode Select - - - - WM1-0 - - - - - - - - - - 0C00h

7Ch Vendor ID 1 “0” “1” “0” “1” “1” “0” “0” “1” “0” “1” “0” “0” “1” “1” “0” “1” 594Dh

7Eh Vendor ID 2 “0” “1” “0” “0” “1” “0” “0” “0” “0” “0” “0” “0” “0” “0” “1” “1” 4803h

- PR5 PR4 PR3 PR2 PR1 PR0 - - - - REF ANL DAC ADC 000xh

EAPD

AMAP LDAC SDAC CDAC

SPCV - - - -

- GL4-0 ZEN ZAC - GR4-0 x808h

MSEL

LPBK

Note) The * bits of 62h and 66h should not be changed from the default value.

Do not access to 5Ah and 60h because they are LSI test registers.

- GN4-0 8008h

20dB

- - - - - - - 0000h

- - -

SPSA1-0 -

- - xxx4h

SPDIF

- - 0400h

SPDIF

COPY AUD#

* * 0224h

EXEN

PRO 2000h

0040h

3AWE

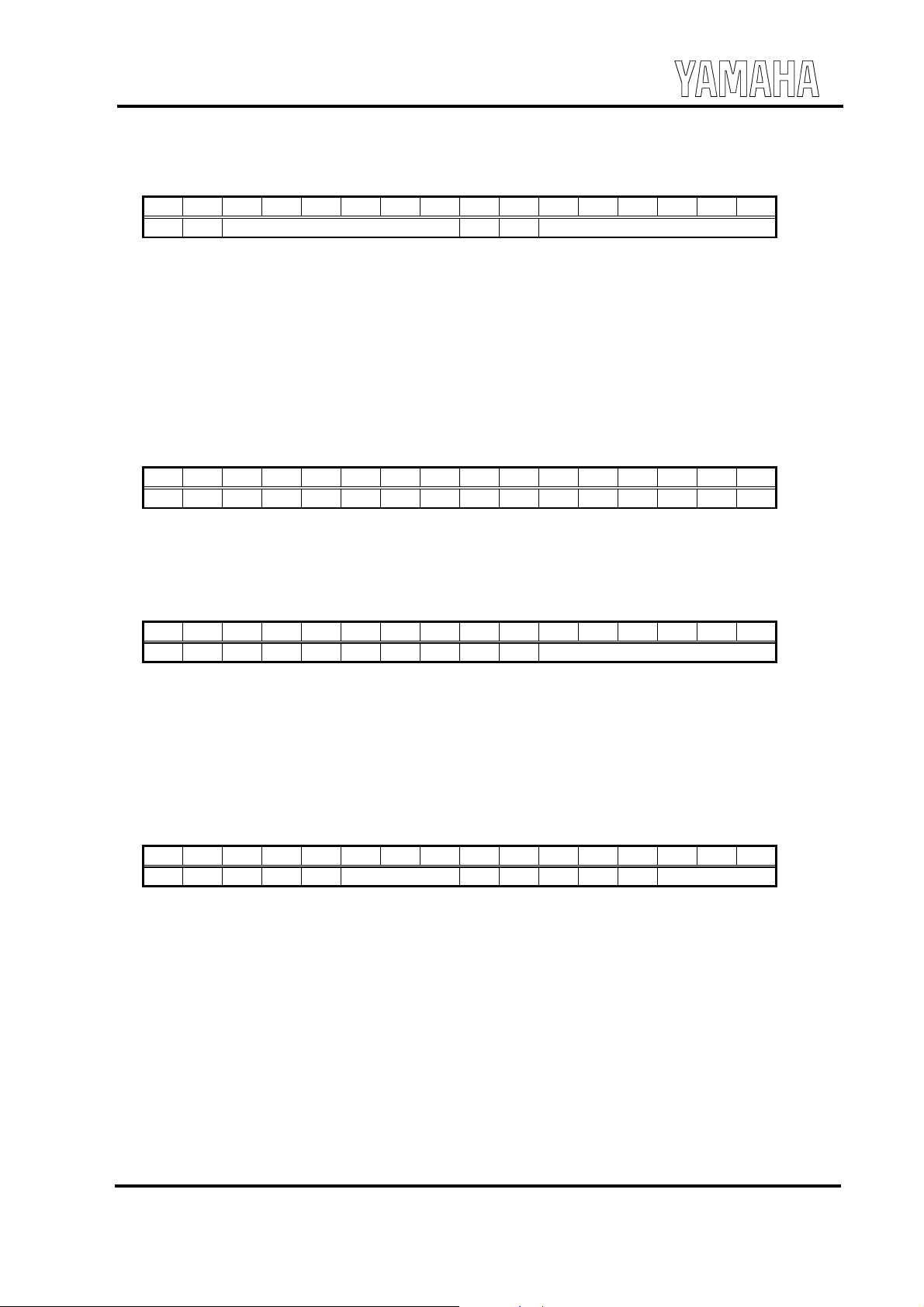

00h : Reset (Read/Write reset, Default: 0040h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

“0” “0” “0” “0” “0” “0” “0” “0” “0” “1” “0” “0” “0” “0” “0” “0”

When any value is written to this register, all registers except for the lower 4 bits of 26h:Power Down are reset

to the default value.

6

March 6, 2001

YMF753

02h : Master Volume (Read/Write, Default: 8000h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Mute - ML5-0 - - MR5-0

Mute..............Setting this bit to “1” mutes both left and right channels of the line output.

ML5-0...........These bits determ ine the v olum e level of the lin e outpu t left ch ann el by 1.5dB step. The volum e

range is from 0dB to -46.5dB. When all bits are set to “0”, volume is maximum (0dB) and when

they are set to “011111b”, volume is minimum (-46.5dB). And when ML5 bit is set to “1”, the

volume level is minimum (-46.5dB), then their status become “011111b”.

MR5-0...........These bits determine the volume level of the line output right channel by 1.5dB step.

Setting to them is the same as the upper ML5-0 bits.

04h : LNLVL Volume (Read/Write, Default: 0000h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

- - - - - - - - - - - - - - - -

Though the register c an be written any value, it does not functio n.

0000h is always read out.

06h : Master Volume Mono (Read/Write, Default: 8000h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Mute - - - - - - - - - MM5-0

Mute..............Setting this bit to “1” mutes the monaural output.

MM5-0..........These bits determine the volume level of the monaural output by 1.5dB step. The volume range

is from 0dB to -46.5dB. When all bits are set to “0”, volume is maximum (0dB) and when they

are set to “011111b”, volume is minimum (-46.5dB). And when MM5 bit is set to “1”, the

volume level is minimum (-46.5dB), then their status become “011111b”

08h : Master Tone (Read/Write, Default: 0707h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

- - - - - BA2-0 - - - - - TR2-0

BA2-0 ...........T hese bits determine the bass level by 1.5dB step. The tone range is from 0dB to +10.5dB.

When all bits are set to “0”, tone is maximum (+10.5dB) and when all bits are set to “1”, tone is

minimum (0dB)

TR2-0............These bits determine the treble level by 1.5dB step. Setting to them is the same as the upper

BA2-0.

7

March 6, 2001

YMF753

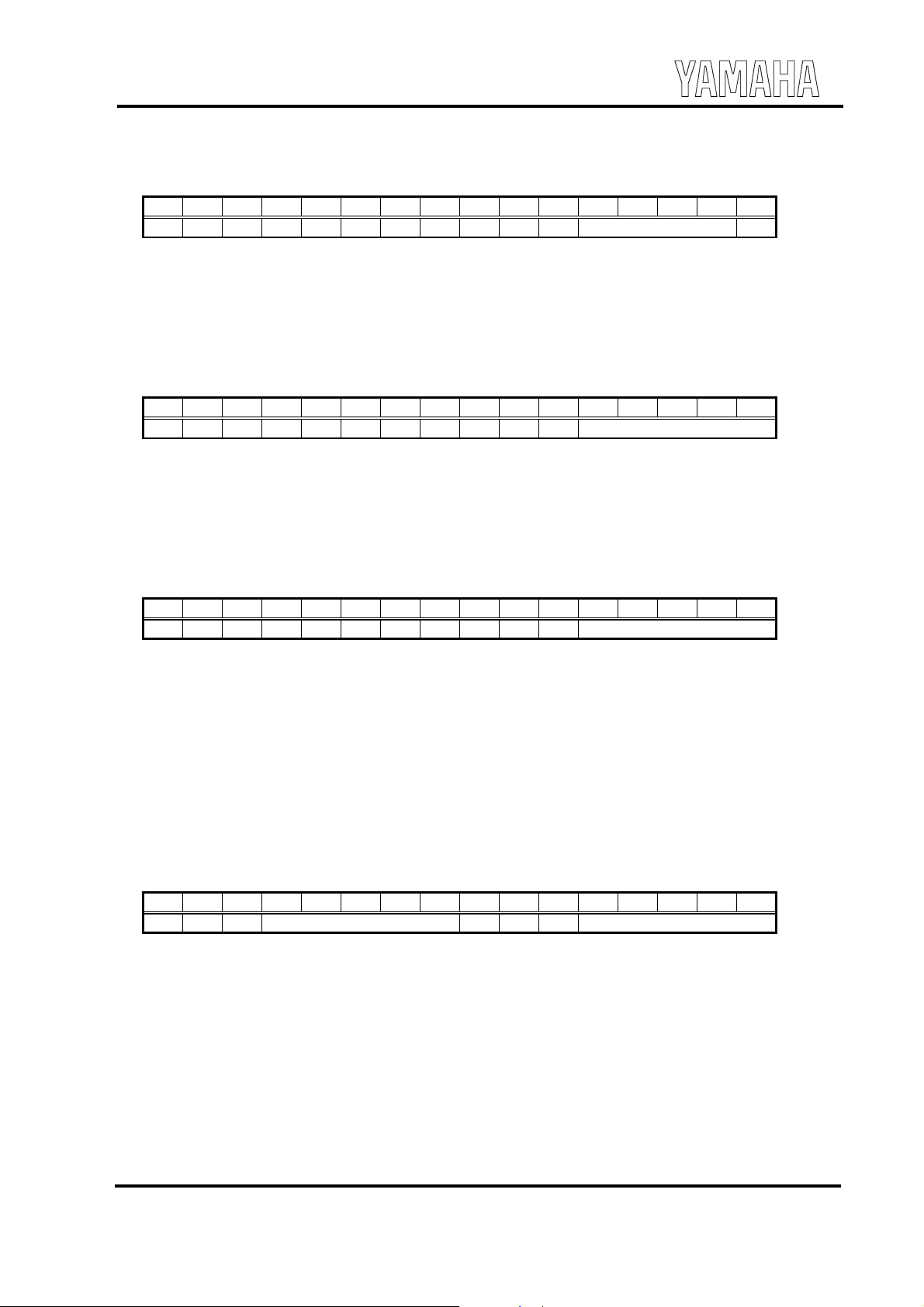

0Ah : PC_BEEP Volume (Read/Write, Default: 0000h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Mute - - - - - - - - - - PV3-0 -

Mute..............Setting this bit to “1” mutes the PC_BEEP.

PV3-0............These bits determine the volume lev el of the PC_BEEP by 3.0dB step. The v olume range is from

0dB to -45dB. When all bits are set to “0”, volume is maximum (0dB) and when all bits are set

to “1”, volume is minimum (-45dB).

0Ch : Phone Volume (Read/Write, Default: 8008h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Mute - - - - - - - - - - GN4-0

Mute..............Setting this bit to “1” mutes the Phone.

GN4-0 ...........T hese bits determine the volume level of the Phone by 1.5dB step. The volume range is from

+12dB to -34.5dB. When all bits are set to “0”, volume is maximum (+12dB) and when all bits

are set to “1”, volume is minimum (-34.5dB).

0Eh : Mic Volume (Read/Write, Default: 8008h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Mute - - - - - - - - 20dB - GN4-0

Mute..............Setting this bit to “1” mutes the Microphone.

20dB .............Setting this bit to “1” increases +20dB for the microphone volume, which is set to GN4-0 bits.

GN4-0 ...........T hese bits determine the volume level of the microphone by 1.5dB step. The volume range is

from +12dB to -34.5dB. When all bits are s et to “0”, v olum e is m axim um (+12dB) and when all

bits are set to “1”, volume is minimum (-34.5dB).

10h : Line in Volume (Read/Write, Default: 8808h)

12h : CD Volume (Read/Write, Default: 8808h)

14h : Video Volume (Read/Write, Default: 8808h)

16h : Aux Volume (Read/Write, Default: 8808h)

18h : PCM out Volume (Read/Write, Default: 8808h)

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Mute - - GL4-0 - - - GR4-0

Mute..............Setting this bit to “1” mutes both left and right channels of the each source.

GL4-0 ...........These bits determine the volume level of the left channel by 1.5dB step. The volume range is

from +12dB to -34.5dB. When all bits are s et to “0”, v olum e is m axim um (+12dB) and when all

bits are set to “1”, volume is minimum (-34.5dB).

GR4-0...........These bits determine the volume level of the right channel by 1.5dB step.

Setting to them is the same as the upper GL4-0 bits.

8

March 6, 2001

Loading...

Loading...