Yamaha YMF740C Datasheet

YMF740C

DS-1L

OVERVIEW

YMF740C (DS-1L) is a high performance audio controller for the PCI Bus. DS-1L consists of two separated

functional blocks. One is the PCI Audio block and the other is the Legacy Audio block. PCI Audio block

allows Software Driver to handle maximum of 41 concurrent audio streams with the Bus Master DMA engine.

The PCI Audio Engine converts the sampling rate of each audio stream and the streams are mixed without

utilizing the CPU or causing system latency. By using the Software Driver from YAMAHA, PCI Audio

provides 32-voice XG wavetable synthesizer with Reverb and variation. It also supports DirectSound hardware

accelerator, Downloadable Sound (DLS) and DirectMusic accelerator.

Legacy Audio block supports FM Synthesizer, Sound Blaster Pro, MPU401 UART mode and Joystick

function in order to provide hardware compatibility for numerous PC games on real DOS without any software

driver. To achieve legacy DMAC compatibility on the PCI, DS-1L supports PC/PCI protocols.

DS-1L supports the connection to AC’97 which provides high quality DAC, ADC and analog mixing.

FEATURES

• PCI 2.1 Compliant

• PC’97/PC’98 specification Compliant

• PCI Bus Power Management rev. 1.0 Compliant

(Support D0, D2 and D3 state)

• PCI Bus Master for PCI Audio

True Full Duplex Playback and Capture with

different Sampling Rate

Maximum 32-voice XG capital Wavetable

Synthesizer including GM compatibility

DirectSound Hardware Acceleration

DirectMusic Hardware Acceleration

Downloadable Sound (DLS) level-1

• Supports PC/PCI DMA for legacy DMAC (8237)

emulation

• Legacy Audio compatibility

FM Synthesizer

Hardware Sound Blaster Pro compatibility

MPU401 UART mode MIDI interface

Joystick

• Supports AC’97 Interface (AC-Link)

• Hardware Volume Control

• Single Crystal operation (24.576MHz)

• 5V Power supply for I/O. 3.3V Power supply for

Internal core logic

• 144-pin LQFP (YMF740C-V)

GENERAL MIDI logo is a trademark of Associat ion of Musical Electronics Industry (AMEI),

and indicates GM system level 1 Compliant.

XG logo is a trademark of YAMAHA Corporation.

YAMAHA

CORPORATION

YMF740C CATALOG

CATALOG No.:LSI-4MF740C20

September 21, 1998

January 14, 1999

YMF740C

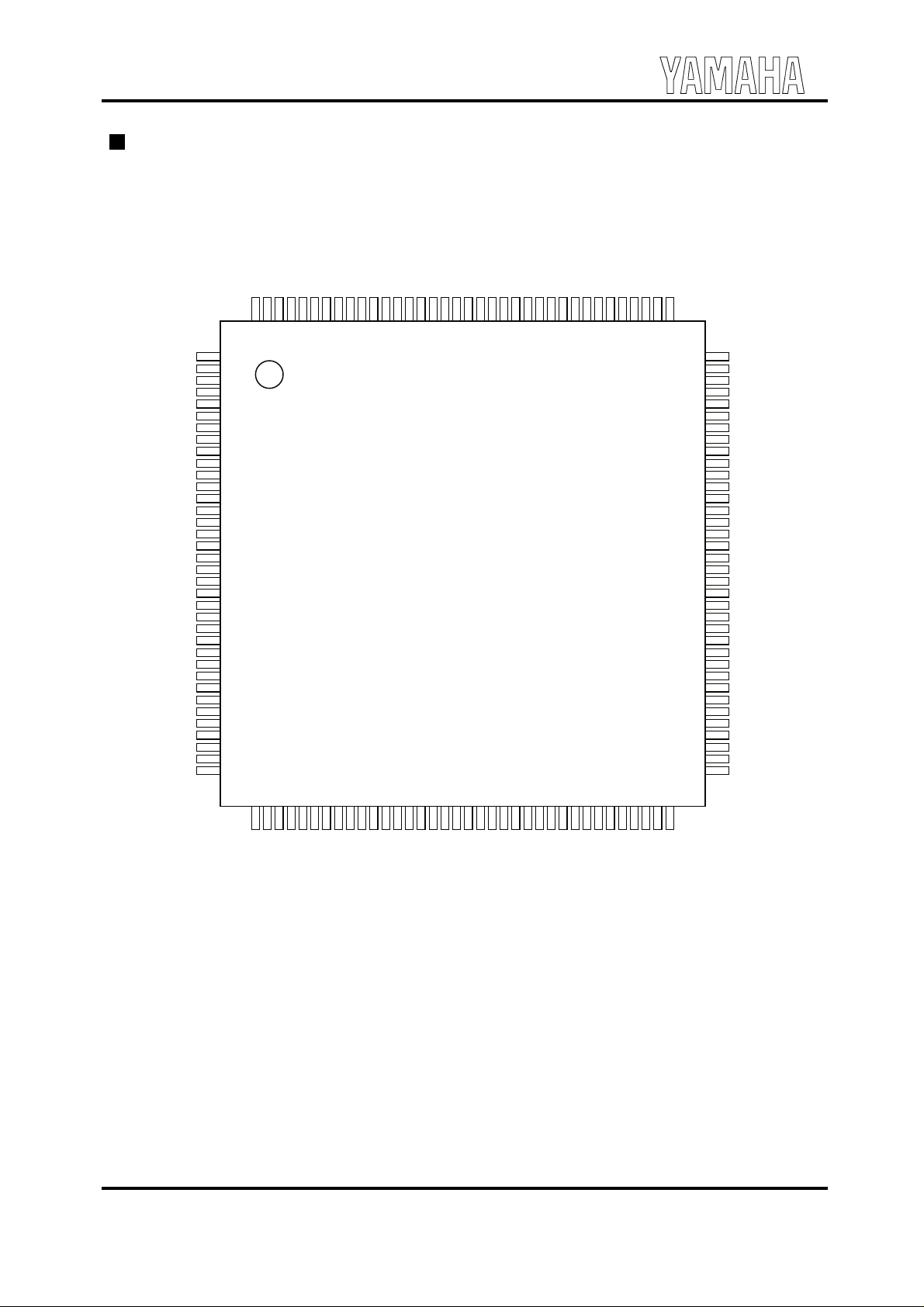

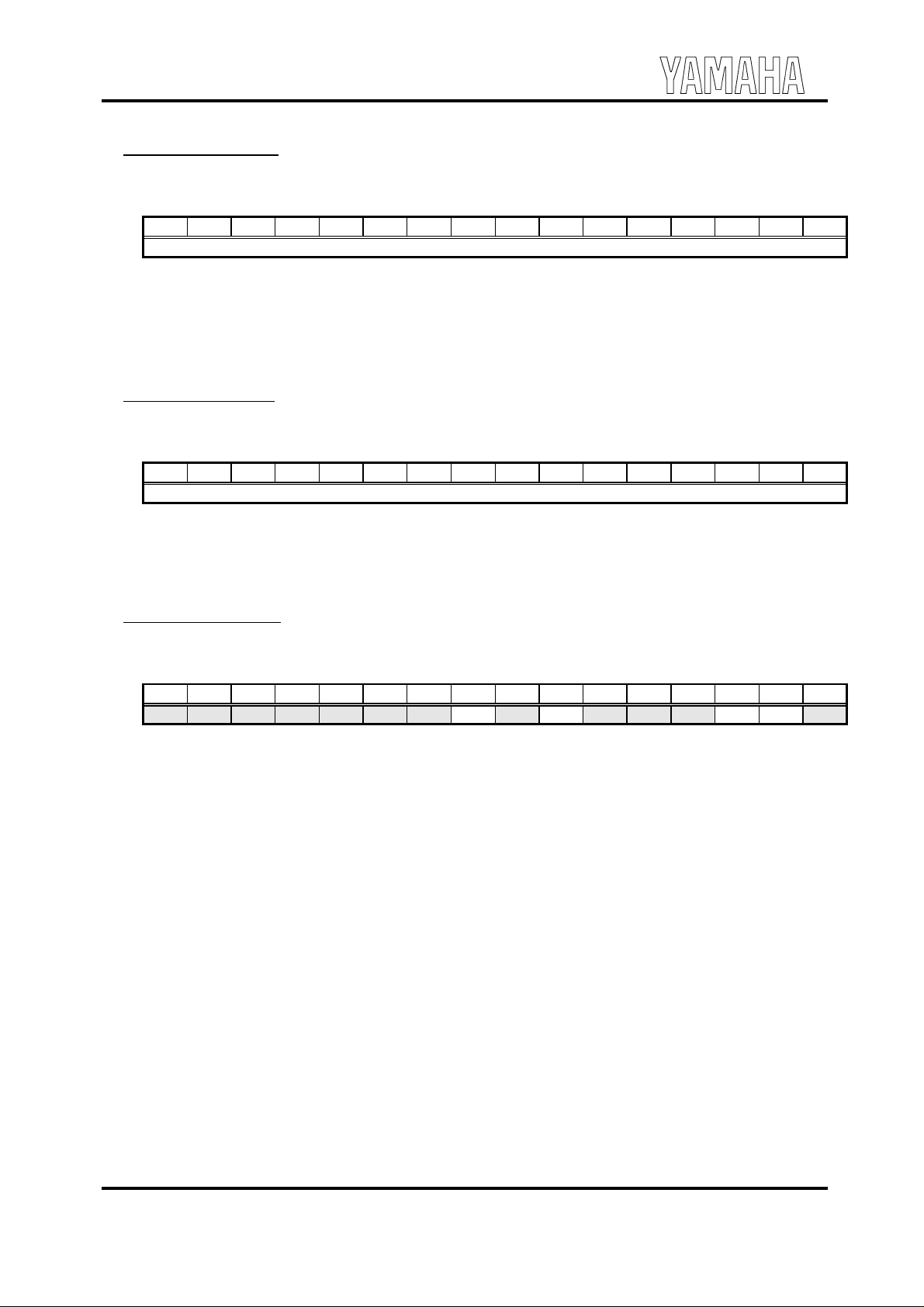

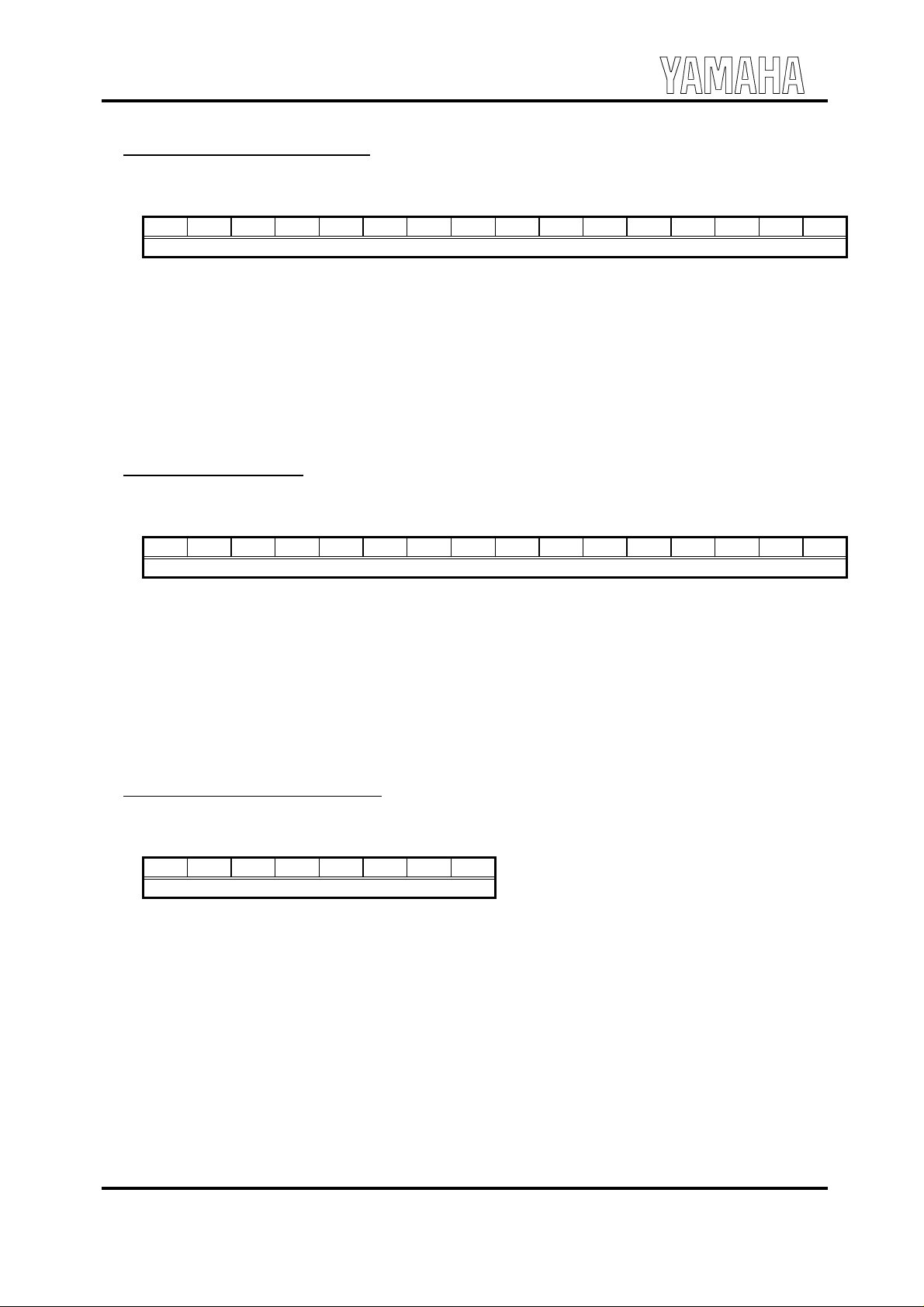

PIN CONFIGURATION

YMF740C-V

TEST2#

GP2

GP0

GP3

GP1

GREF

142

GP4

GP5

GP6

GP7

RXD

TXD

VOLDW#

VOLUP#

VDD5

VDD3

VSS

VSS

IRQ5

IRQ7

IRQ9

IRQ10

IRQ11

INTA#

VSS

RST#

VDD5

PVSS

PCICLK

PVDD

GNT#

REQ#

AD31

AD30

AD29

PVSS

AD28

AD27

AD26

PVSS

AD25

AD24

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

144

1

2

3

4

5

6

7

8

9

37

143

38

39

141

40

140

41

139

42

TEST0#

TEST1#

NC

138

136

137

44

43

45

LVSS

LOOPF1

134

135

46

47

LOOPF0

NC

LVDD

132

133

131

48

50

49

VDD5

TEST4#

XO24

128

130

129

52

51

53

XI24

VSS

126

127

54

55

VSS

125

56

VDD3

NC

124

123

58

57

TEST6#

TEST5#

TEST7#

122

120

121

60

59

61

CMCLK

CSDO

118

119

62

63

CBCLK

CSDI

117

116

64

65

CRST#

CSYNC

115

114

66

67

TEST3#

NC

NC

113

111

112

68

70

69

NC

110

71

NC

109

72

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

NC

NC

NC

NC

NC

NC

NC

NC

VSS

VSS

VDD3

VDD5

PVDD

NC

PCREQ#

PCGNT#

NC

AD0

AD1

PVSS

AD2

AD3

AD4

PVSS

AD5

AD6

AD7

PVSS

PVDD

CBE0#

AD8

AD9

PVSS

AD10

AD11

AD12

PVDD

CBE3#

PVSS

IDSEL

AD22

AD23

PVSS

AD21

AD19

AD20

AD18

PVSS

AD17

AD16

PVDD

VSS

PVSS

VDD3

144 Pin LQFP Top View

-2-

CBE2#

FRAME#

IRDY#

TRDY#

PVSS

DEVSEL#

STOP#

PERR#

PVSS

SERR#

PAR

AD15

CBE1#

PVSS

PVDD

AD14

AD13

PVSS

January 14, 1999

YMF740C

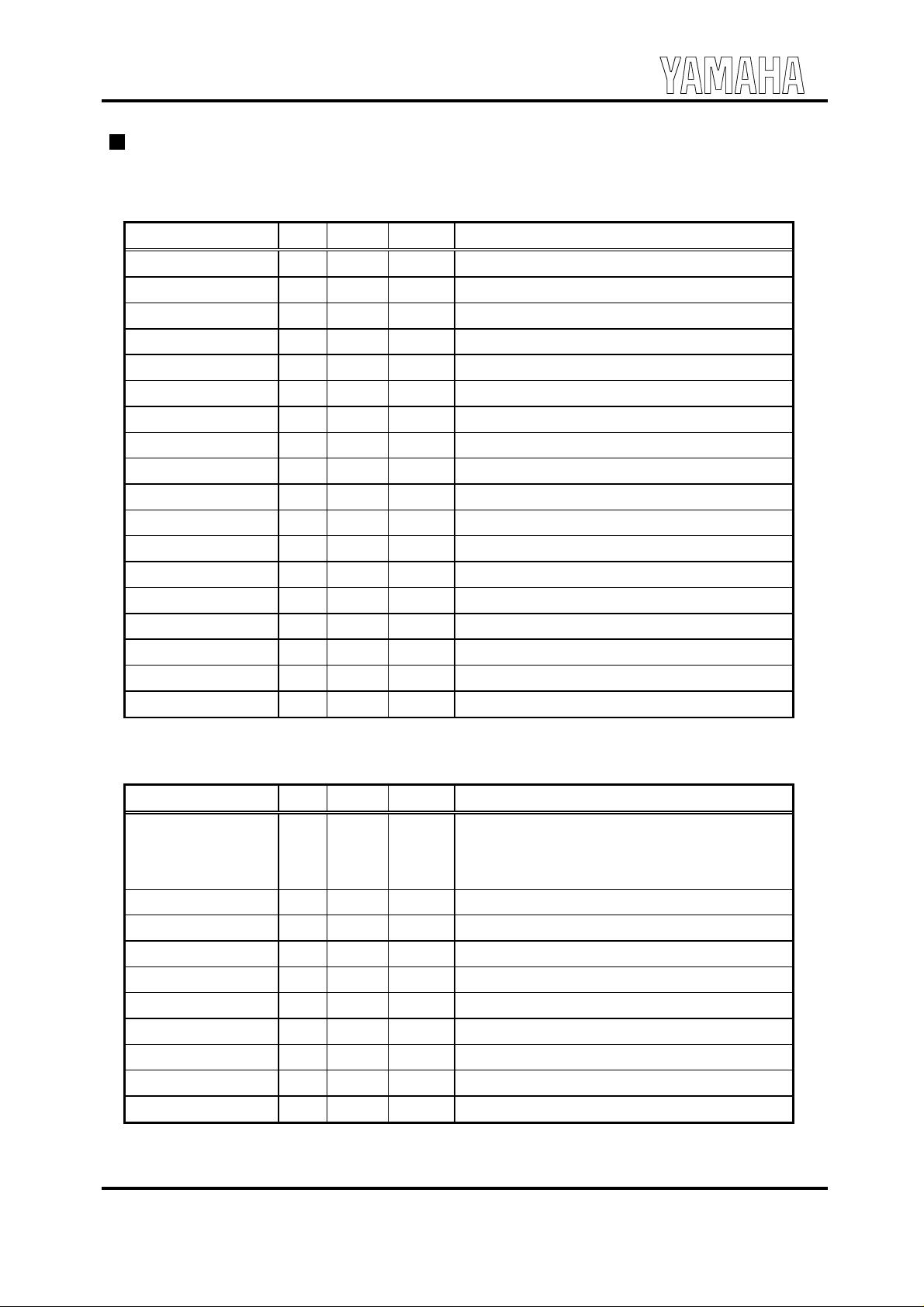

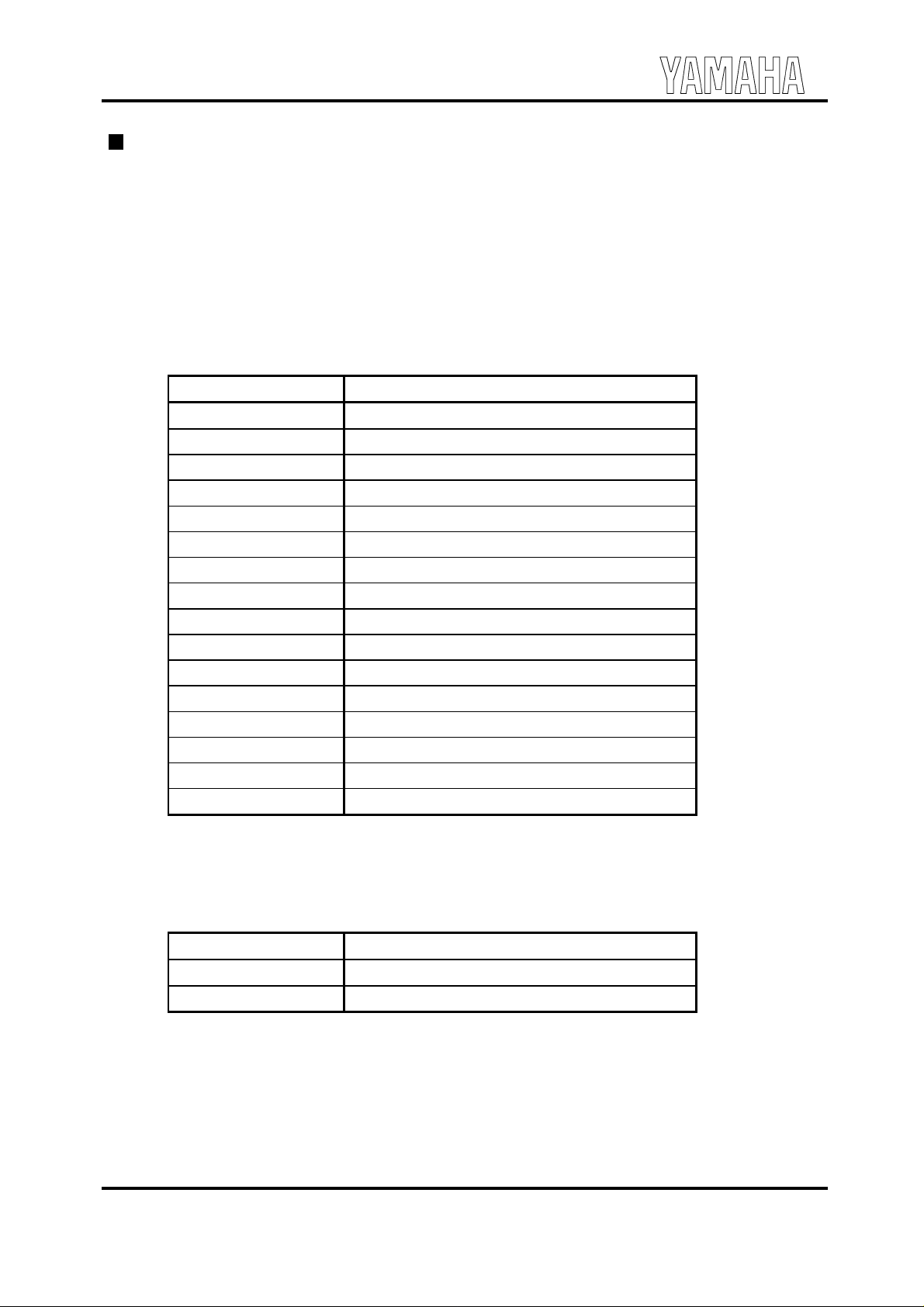

PIN DESCRIPTION

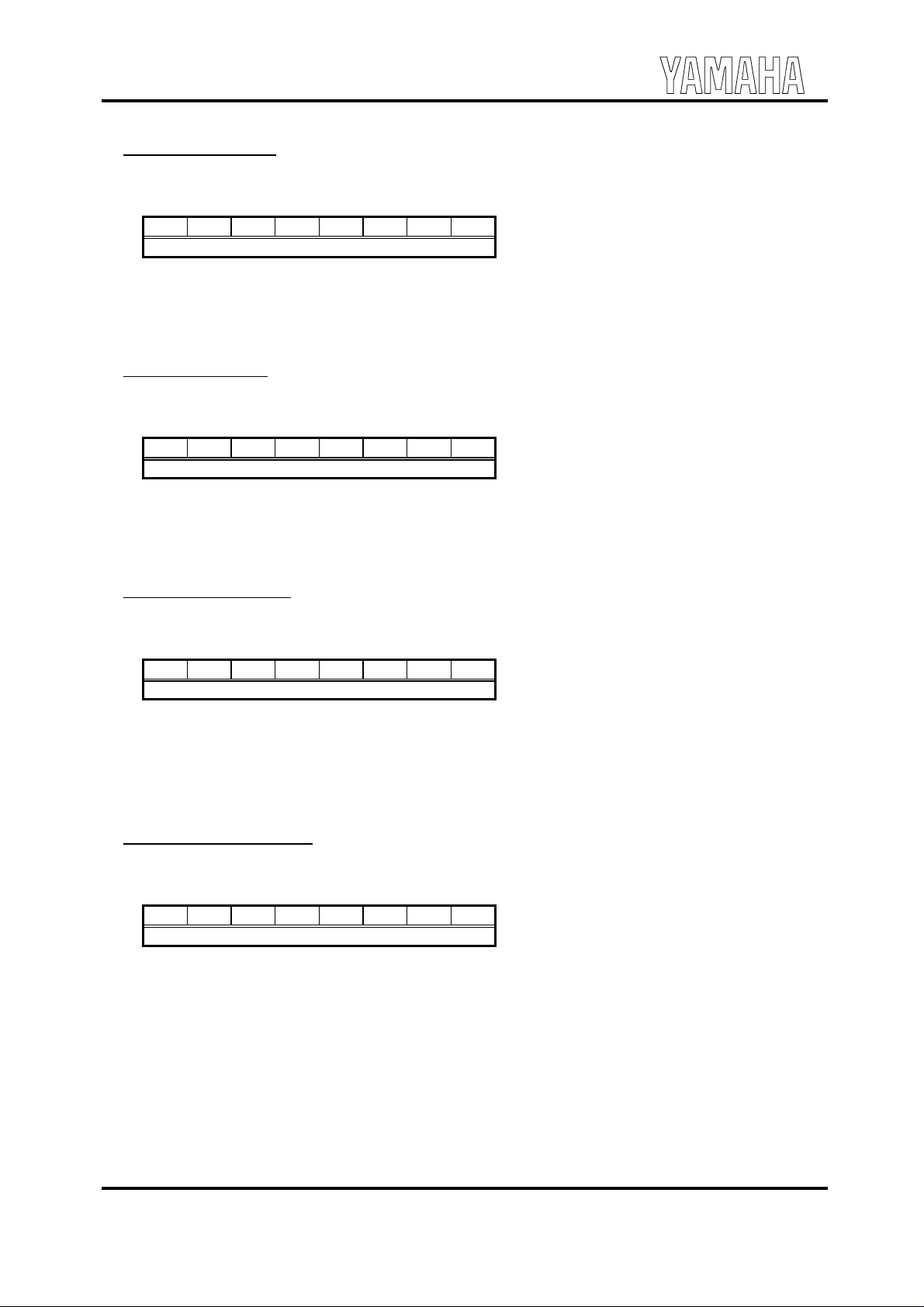

1. PCI Bus Interface (52-pin)

name I/O Type Size function

PCICLK I P PCI Clock

RST# I P Reset

AD[31:0] IO Ptr Address / Data

C/BE[3:0]# IO Ptr Command / Byte Enable

PAR IO Ptr Parity

FRAME# IO Pstr Frame

IRDY# IO Pstr Initiator Ready

TRDY# IO Pstr Target Ready

STOP# IO Pstr Stop

IDSEL I P ID Select

DEVSEL# IO Pstr Device Select

REQA# O P PCI Request

GNTA# I P PCI Grant

PCREQ# O Ptr PC/PCI Request

PCGNT# I Ptr PC/PCI Grant

PERR# IO Pstr Parity Error

SERR# O Pod System Error

INTA# O Pod Interrupt signal output for PCI bus

2. Legacy Device Interface (16-pin)

name I/O type size function

IRQ5 O Ttr 12mA Interrupt5 of Legacy Audio

It is directly connected to the interrupt signal of

System I/O chip.

IRQ7 O Ttr 12mA Interrupt7 of Legacy Audio

IRQ9 O Ttr 12mA Interrupt9 of Legacy Audio

IRQ10 O Ttr 12mA Interrupt10 of Legacy Audio

IRQ11 O Ttr 12mA Interrupt11 of Legacy Audio.

GP[3:0] I A - Game Port

GP[7:4] I Tup - Game Port

GREF I A - Reference for Game Port

RXD I Tup - MIDI Data Receive

TXD O T 3mA MIDI Data Transfer

-3-

January 14, 1999

YMF740C

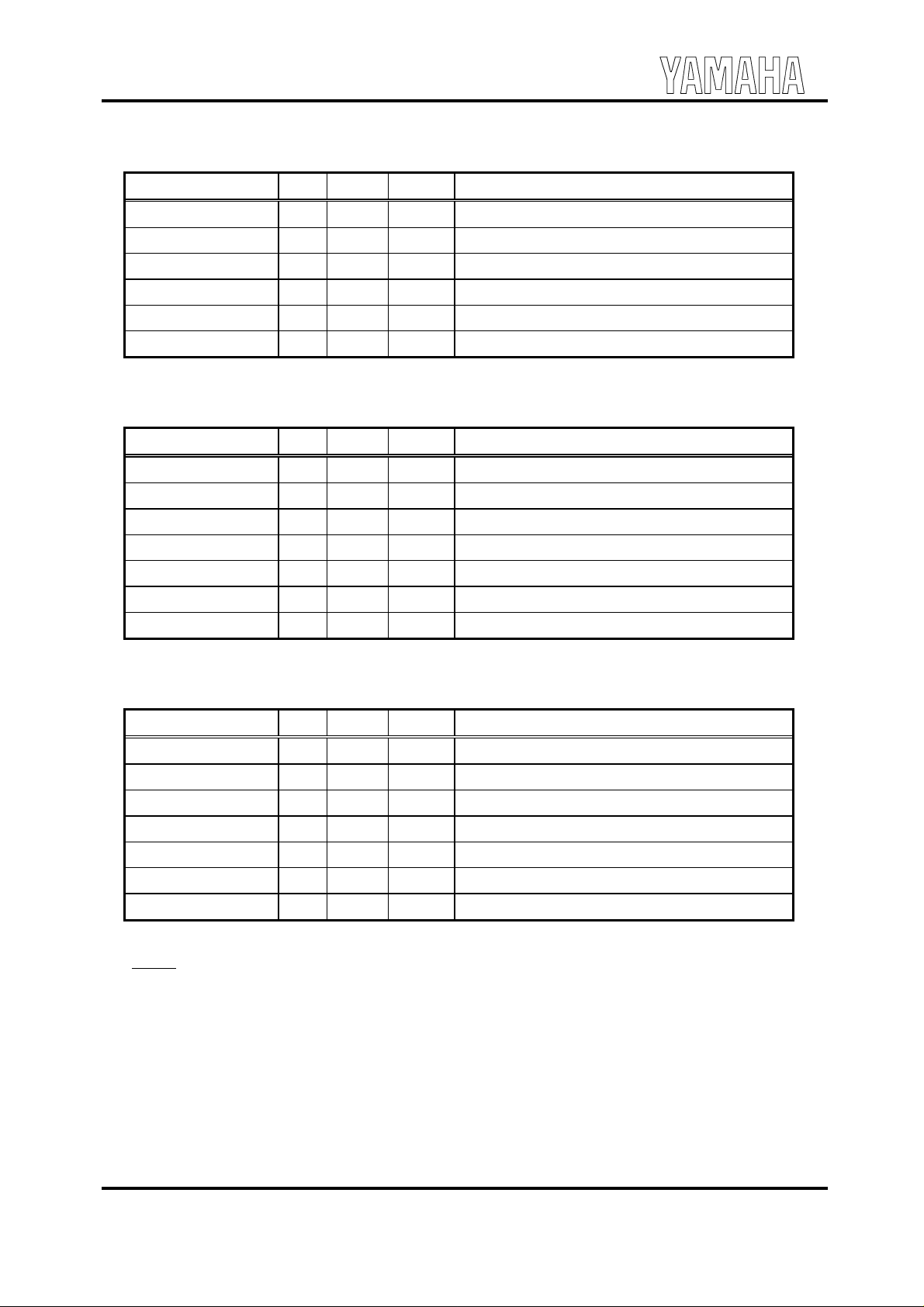

3. AC’97 Interface (6-pin)

name I/O Type Size function

CRST# O T 6mA Reset signal for AC’97

CMCLK O C - Master Clock of AC link (24.576MHz) and

CBCLK I T - AC-link: Bit Clock for AC’97 audio data

CSDO O T 6mA AC-link: AC‘97 Serial audio output data

CSDI I T - AC-link: AC’97 Serial audio input data

CSYNC O T 6mA AC-link: Synchronized signal

4. Miscellaneous (14-pin)

name I/O type size function

VOLUP# I Tup - Hardware Volume (Up)

VOLDW# I Tup - Hardware Volume (Down)

XI24 I C - 24.576 MHz Crystal

XO24 O C 2mA 24.576 MHz Crystal

TEST[7:4,2:0]# I Tup - Test pins (Do not connect externally)

TEST3# IO Tup 3mA Test pin (Connect to ground)

LOOPF[1:0] - - - Capacitor of PLL

5. Power Supply (39-pin)

name I/O type size function

PVDD[5:0] - - - Power supply for PCI Bus Interface (+5.0)

PVSS[14:0] - - - Ground for PCI Bus Interface

LVDD - - - Power supply for PLL Filter (+3.3)

LVSS - - - Ground for PLL Filter

VDD3[3:0] - - - Power supply (+3.3V)

VDD5[3:0] - - - Power supply (+5.0V)

VSS[7:0] - - - Ground

TYPE

T : TTL A : Analog Ptr : Tri-State PCI

Ttr : Tri-State TTL C : CMOS Pstr : Sustained Tri-Sate PCI

Tup : Pull up (Max. 300kohm) TTL P : PCI Pod : Open Drain PCI

Note) All pins except the above pins are NC (No Connection) pins. Do not connect externally.

-4-

January 14, 1999

YMF740C

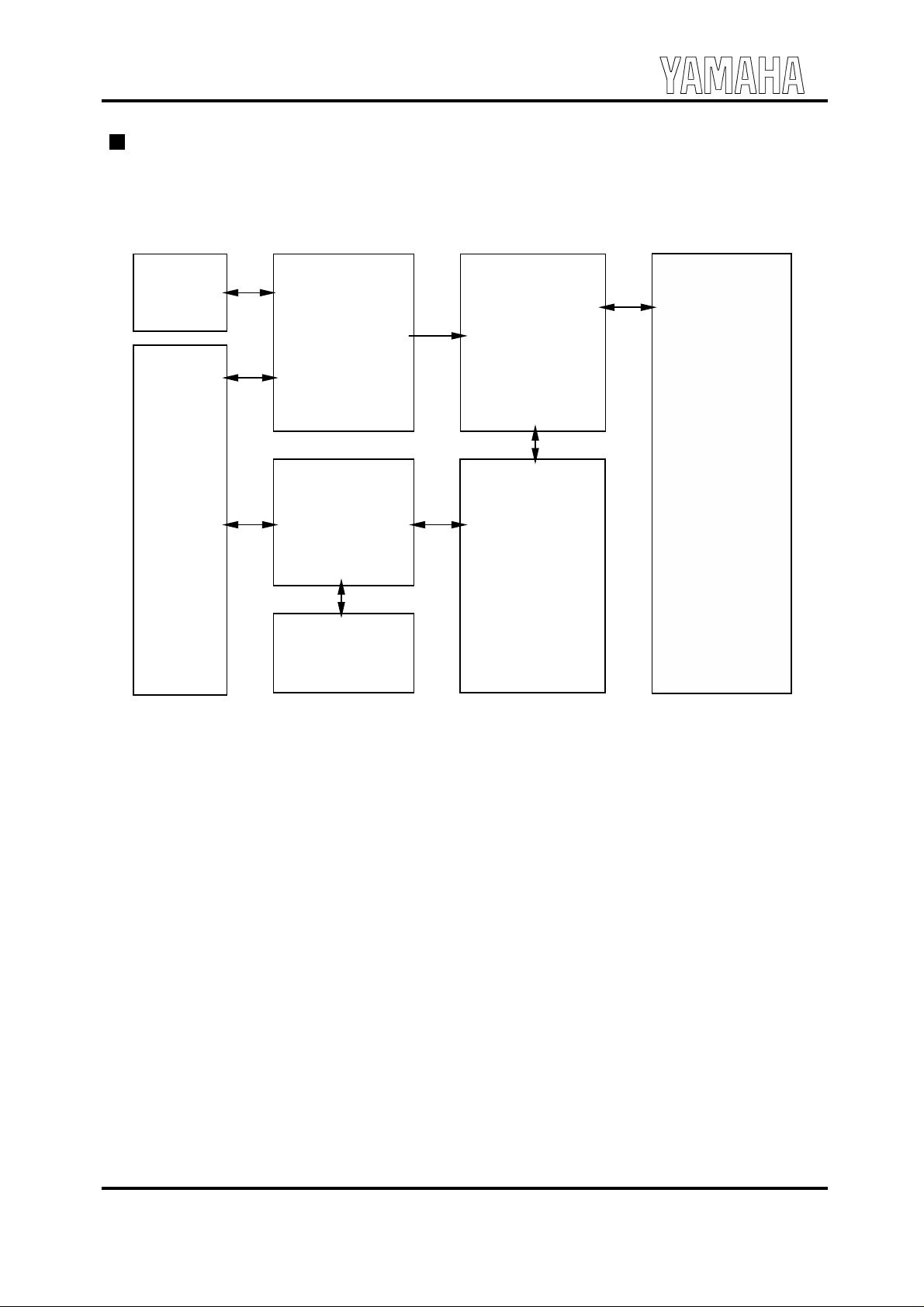

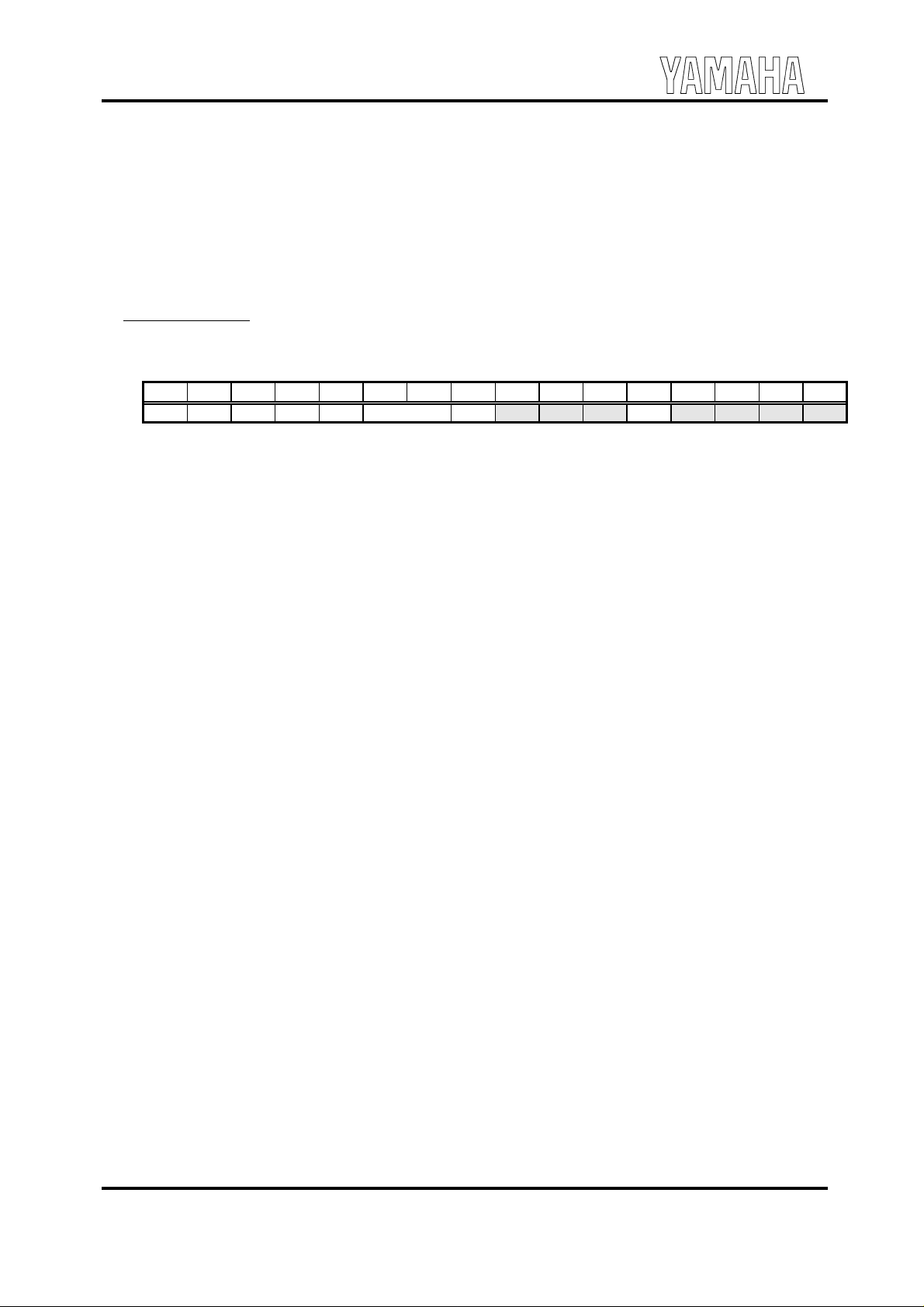

BLOCK DIAGRAM

PC-PCI

PCI Bus

Interface

Legacy Audio

SB Pro

FM

MPU401

Joystick

BUS Master

DMA Controller

Memory

Rate Converter

/ Mixer

AC'97

Interface

PCI Audio

XG Synthesizer

Direct Sound Acc.

Wave In/Out

-5-

January 14, 1999

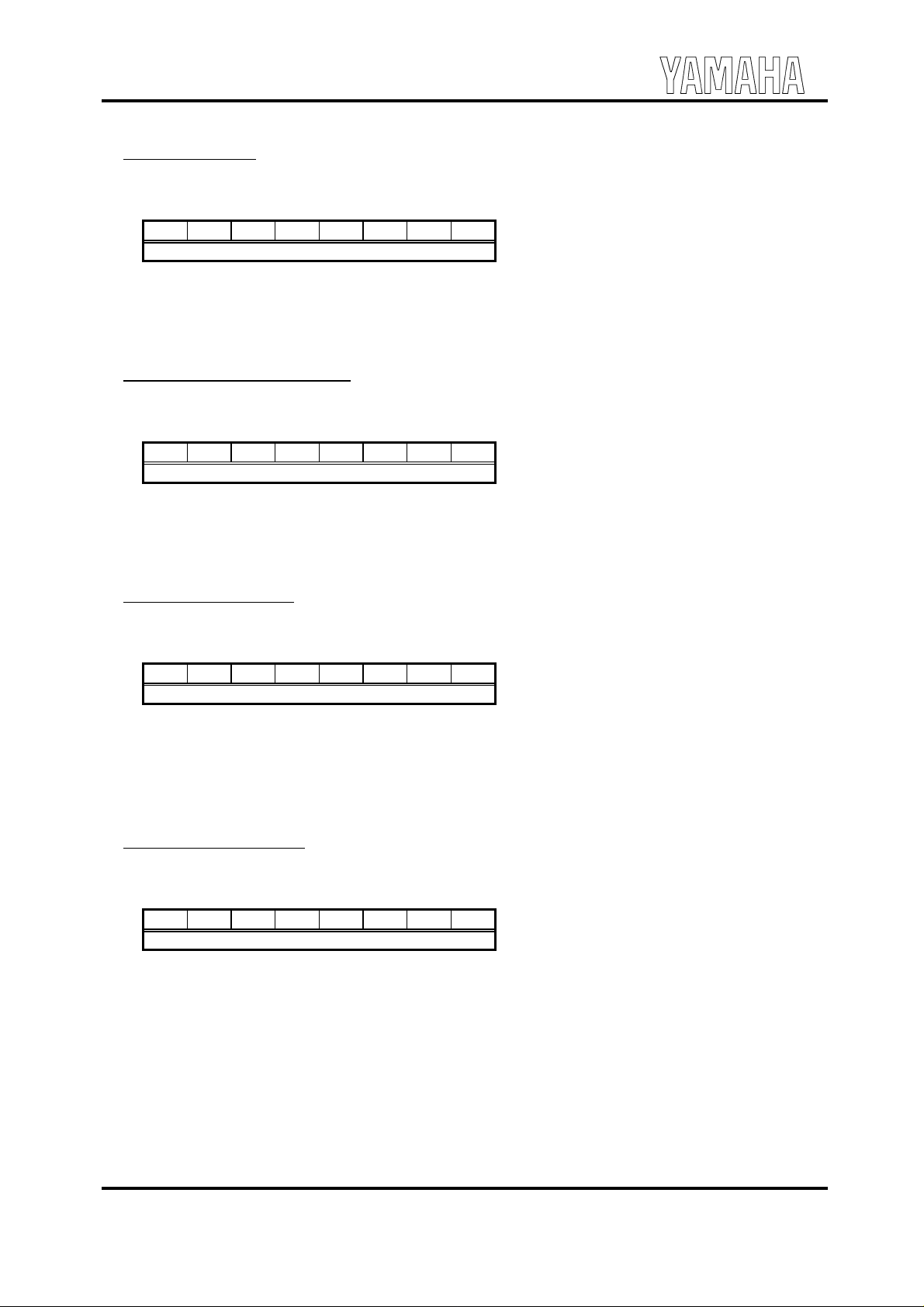

YMF740C

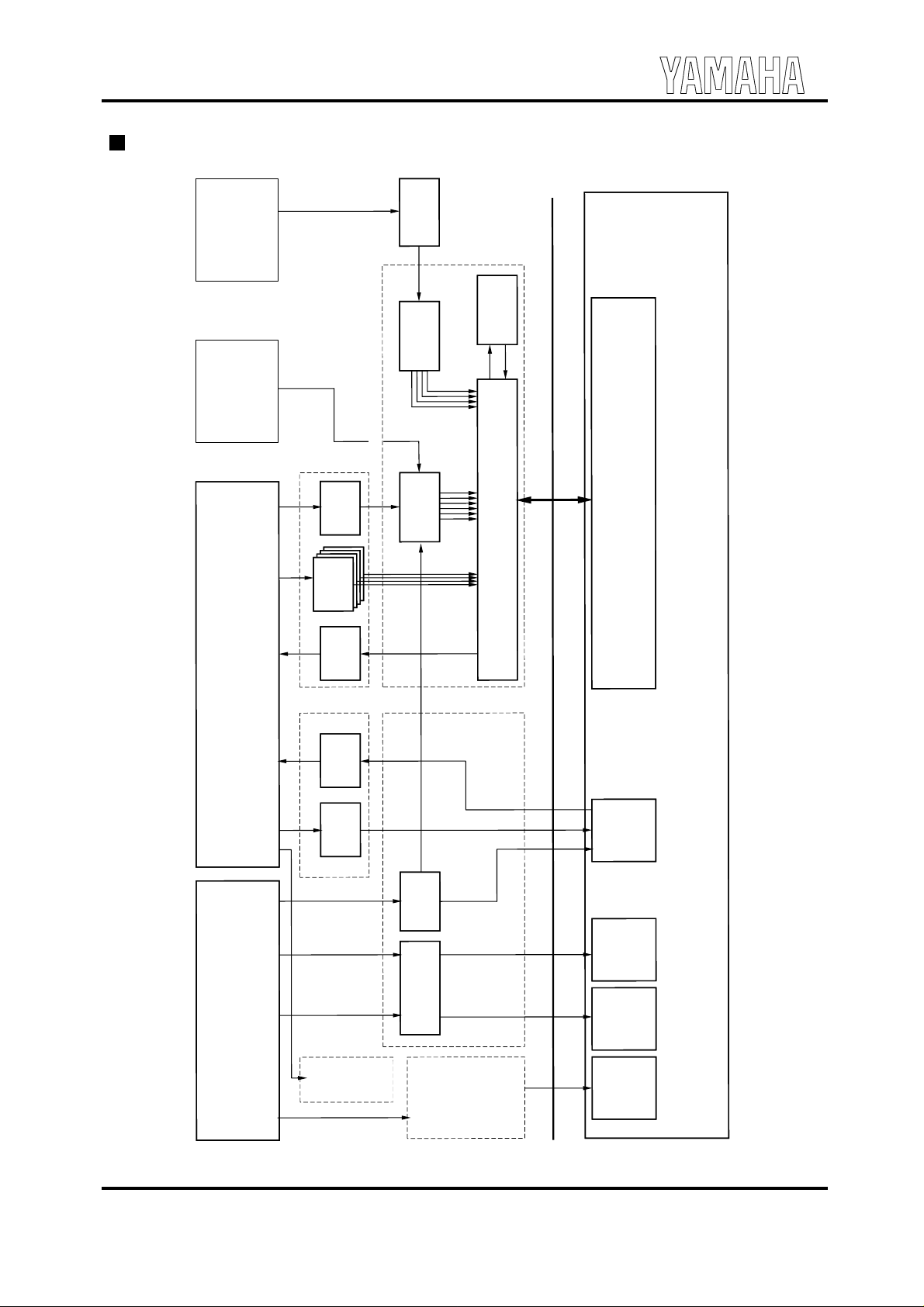

SYSTEM DIAGRAM

DirectX

Application

DLS

Appllication

VxD

DirectSound

Win32API

Soft

Effect

HAL

DirectSound

VxD for PCI Audio

Win16API

MMSystem

Device

MidiOut

Device

WaveOut

Device

WaveIn

MidiIn

Device

Device

MidiOut

DRV for PCI Audio

Engine

XG/DLS

DRV for Legacy

I/O Traps

PCI Audio

DS-1L Slot Manager (Up to 32-sound)

YMF740C(DS-1L)

VxD for Legacy

MPU401

VM

DOS

I/O Traps

Msjstck.drv

FM SB Pro

Vjoyd.vxd

Joystick

January 14, 1999

-6-

YMF740C

FUNCTION OVERVIEW

1. PCI INTERFACE

DS-1L supports the PCI bus interface and complies to PCI revision 2.1.

1-1. PCI Bus Command

DS-1L supports the following PCI Bus commands.

1-1-1. Target Device Mode

C/BE[3:0]# Command

0000Interrupt Acknowledge (not support)

0001Special Cycle (not support)

0010I/O Read

0011I/O Write

0100reserved

0101reserved

0110Memory Read

0111Memory Write

1000reserved

1001reserved

1010Configuration Read

1011Configuration Write

1100Memory Read Multiple (not support)

1101Dual Address Cycle (not support)

1110Memory Read Line (not support)

1111Memory Write and Invalidate (not support)

DS-1L does not assert DEVSEL# when accessed with commands that are indicated as (not supported) or

reserved.

1-1-2. Master Device Mode

C/BE[3:0]# Command

0110Memory Read

0111Memory Write

When DS-1L becomes a Master Device, it generates only memory write and read cycle commands.

-7-

January 14, 1999

YMF740C

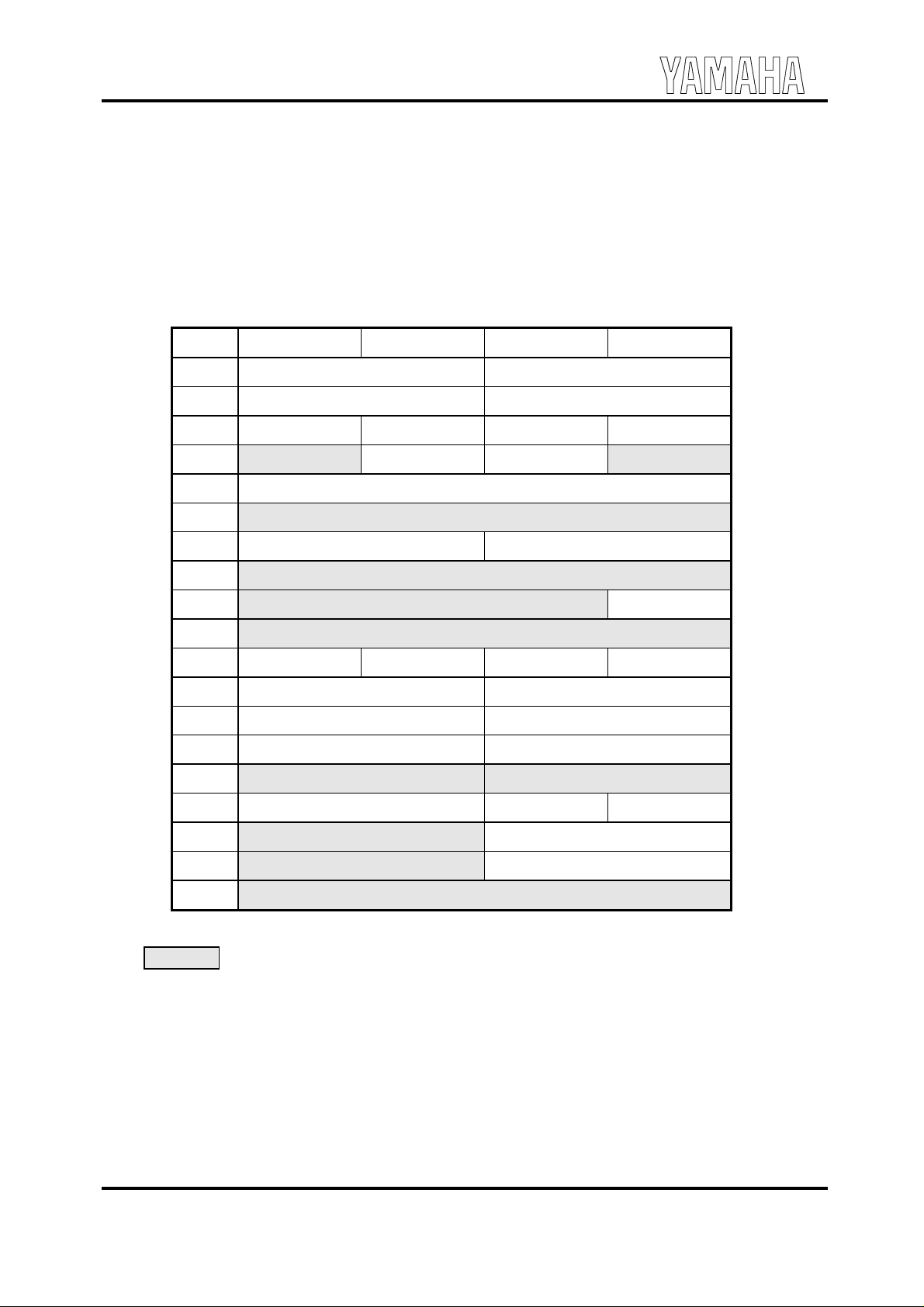

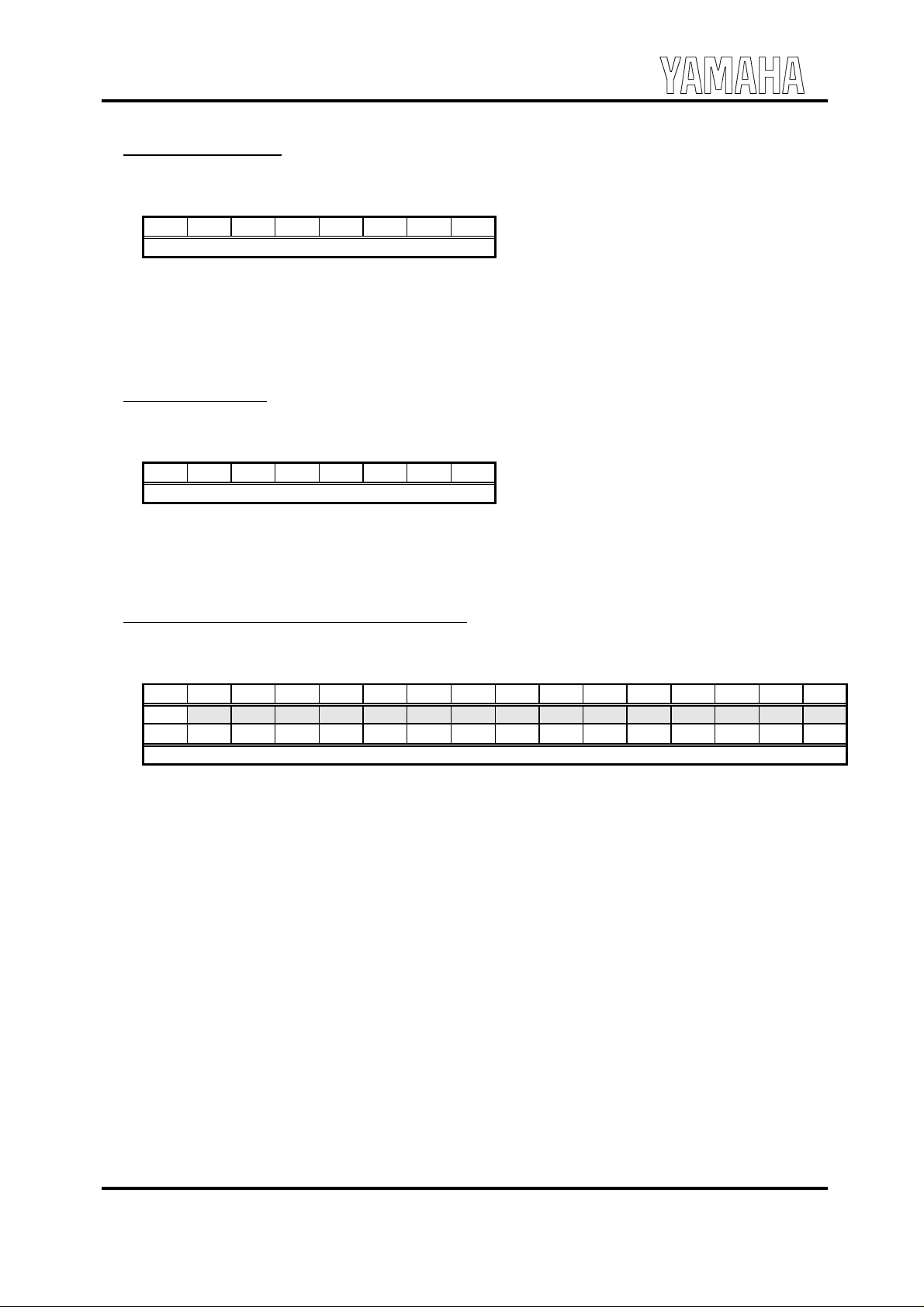

1-2. PCI Configuration Register

In addition to the Configuration Register defined by PCI Revision 2.1, DS-1L provides proprietary PCI

Configuration Registers in order to control legacy audio functio n, such as FM Synthesizer, Sound Blaster Pro,

MPU401 and Joystick. These additional registers are configured by BIOS or the configuration software

from YAMAHA Corporation.

The following shows the overview of the PCI Configuration Register.

Offset b[31..24] b[23..16] b[15..8] b[7..0]

00-03h Device ID Vendor ID

04-07h Status Command

08-0Bh Base Class Code Sub Class Code Programming IF Revision ID

0C-0Fh Reserved Header Type Latency Timer Reserved

10-13h PCI Audio Memory Base Addres s

14-2Bh Reserved

2C-2Fh Subsystem ID Subsystem Vendor ID

30-33h Reserved

34-37h Reserved Cap Pointer

38-3Bh Reserved

3C-3Fh Maximum Latency Minimum Grant Interrupt Pin Interrupt Line

40-43h Extended Legacy Audio Control Legacy Audio Control

44-47h Subsystem ID Write Subsystem Vendor ID Write

48-4Bh DS-1L Power Control DS-1L Control

4C-4Fh Reserved Reserved

50-53h Power Management Capabilities Next Item Pointer Capability ID

54-57h Reserved Power Management Control / Status

58-5Bh Reserved ACPI Mode

5C-FFh Reserved

Reserved registers are hardwired to “0”. All data written to these registers are discarded. The values

read from these registers are all zero.

DS-1L can be accessed by using any bus width, 8-bit, 16-bit or 32-bit.

-8-

January 14, 1999

YMF740C

00 - 01h: Vendor ID

Read Only

Default: 1073h

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Vendor ID

b[15:0]........Vendor ID

This register contains the YAMAHA Vendor ID registered in Revision 2.1. This register is hardwired to

1073h.

02 - 03h: Device ID

Read Only

Default: 000Ch

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Device ID

b[15:0]........Device ID

This register contains the Device ID of DS-1L. This register is hardwired to 000Ch.

04 - 05h: Command

Read / Write

Default: 0000h

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

- - - - - - - SER - PER - - - BME MS -

b1................MS: Memory Space

This bit enables DS-1L to response to Memory Space Access.

“0”: DS-1L ignores Memory Space Access. (default)

“1”: DS-1L responds to Memory Space Access.

b2................BME: Bus Master Enable

This bit enables DS-1L to act as a master device on the PCI bus.

“0”: Do not set DS-1L to be the master device. (default)

“1”: Set DS-1L to be the master device.

b6................PER: Parity Error Response

This bit enables DS-1L responses to Parity Error.

“0”: DS-1L ignores all parity errors.

“1”: DS-1L performs error operation when DS-1L detects a parity error.

-9-

January 14, 1999

YMF740C

b8................SER: SERR# Enable

This bit enables DS-1L to drive SERR#.

“0”: Do not drive SERR# . (default)

“1”: Drives SERR# when DS-1L detects an Address Parity Error on normal target cycle or a Data Parity

Error on special cycle.

06 - 07h: Status

Read / Write Clear

Default: 0210h

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

DPE SSE RMA RTA STA DEVT DPD - - - CAP - - - -

b4................CAP: Capability (Read Only)

This bit indicates that DS-1L supports the capability register. This bit is read only. When 58-59h :

ACPI Mode register, ACPI bit is “0”, the bit is “1”. When ACPI bit is “1”, the bit is “0”.

b8................DPD: Data Parity Error Detected

This bit indicates that DS-1L detects a Data Parity Error during a PCI master cycle.

b[10:9] ........DEVT: DEVSEL Timing

This bit indicates that the decoding speed of DS-1L is Medium.

b11..............STA: Signaled Target Abort

This bit indicates that DS-1L terminates a transaction with Target Abort during a target cycle.

b12..............RTA: Received Target Abort

This bit indicates that a transaction is terminated with Target Abort while DS-1L is in the master memory

cycle.

b13..............RMA: Received Master Abort

This bit indicates that a transaction is terminated with Master Abort while DS-1L is in the master memory

cycle.

b14..............SSE: Signaled System Error

This bit indicates that DS-1L asserts SERR#.

b15..............DPE: Detected Parity Error

This bit indicates that DS-1L detects Address Parity Error or Data Parity Error during a transaction.

January 14, 1999

-10-

YMF740C

08h: Revision ID

Read Only

Default: 03h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Revision ID

b[7:0]..........Revision ID

This register conta i ns the revision number of DS-1L. This register is hardwired to 03h.

09h: Programming Interface

Read Only

Default: 00h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Programming Interf ace

b[7:0]..........Programming Interface

This register indicates the programming interface of DS-1L. This register is hardwired to 00h.

0Ah: Sub-class Code

Read Only

Default: 01h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Sub-class Code

b[7:0]..........Sub-class Code

This register indicates the sub-class of DS-1L. This register is hardwired to 01h. DS-1L belongs to the

Audio Sub-class.

0Bh: Base Class Code

Read Only

Default: 04h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Base Class Code

b[7:0]..........Base Class Code

This register indicates the base class of DS-1L. This register is hardwired to 04h. DS-1L belongs to

the Multimedia Base Class.

January 14, 1999

-11-

YMF740C

0Dh: Latency Timer

Read / Write

Default: 00h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Latency Timer

b[7:0]..........Latency Timer

When DS-1L becomes a Bus Master device, this register indicates the initial value of the Master Latency

Timer.

0Eh: Header Type

Read Only

Default: 00h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Header Type

b[7:0]..........Header Type

This register indicates the device type of DS-1L. This is hardwired to 00h.

10 - 13h: PCI Audio Memory Base Address

Read / Write

Default: 00000000h

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

MBA

b31 b30 b29 b28 b27 b26 b25 b24 b23 b22 b21 b20 b19 b18 b17 b16

b[31:15]......MBA: Memory Base Address

This register indicates the physical Memory Base address of the PCI Audio registers in DS-1L. T he base

address can be located anywhere in the 32-bit address space. Data in the DS-1L register is not

prefetchable.

DS-1L needs 32768-bytes of memory address space.

- - - - - - - - - - - - - - -

MBA (higher)

-12-

January 14, 1999

YMF740C

2C-2Dh: Subsystem Vendor ID

Read Only

Default: 1073h

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Subsystem Vendor ID

b[15:0]........Subsystem Vendor ID

This register contains the Subsystem Vendor ID. In genera l, this ID is used to distinguish adapters or

systems made by different IHVs using the same chip by the same vendor. This register is read only. To

write the IHV’s Vendor ID, use 44-45h (Subsystem Vendor ID Write Register).

The default value is the YAMAHA's Vendor ID, 1073h. IHVs must change this ID to their Vendor ID in

the BIOS POST routine.

2E-2Fh: Subsystem ID

Read Only

Default: 000Ch

Access Bus Width: 8, 16, 32-bit

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

Subsystem ID

b[15:0]........Subsystem ID

This register contains the Subsystem ID. In general, this ID is used to distinguish adapters or systems

made by different IHVs using the same chip by the same vendor. This register is read only. To write

the IHV's Device ID, use 46-47h (Subsystem ID Write Register).

The default value is the YAMAHA's Device ID, 000Ch. IHVs must change this ID to their ID in the

BIOS POST routine.

34h: Capability Register Pointer

Read Only

Default: 50h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Capability Register Pointer

b[7:0]..........Capability Register Pointer

This register indicates the offset address of the Capabilities register in the PCI Configuration register

when 58-59h: ACPI Mode register, ACPI bit is “0”. DS-1L provides PCI Bus Power Management

registers as the capabilities. The Power Management registers are mapped to 50h - 57h in the PCI

Configuration register, and this register indicates “50h”.

When ACPI bit is “1”, this register indicates “00h”.

-13-

January 14, 1999

YMF740C

3Ch: Interrupt Line

Read / Write

Default: 00h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Interrupt Line

b[7:0]..........Interrupt Line

This register indicates the interrupt channel that INTA# is assigned to.

3Dh: Interrupt Pin

Read Only

Default: 01h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Interrupt Pin

b[7:0]..........Interrupt Pin

DS-1L supports INTA# only. This register is hardwired to 01h.

3Eh: Minimum Grant

Read Only

Default: 05h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Minimum Grant

b[7:0]..........Minimum Grant

This register indicates the length of the burst period required by DS-1L.

This register is hardwired to 05h.

3Fh: Maximum Latency

Read Only

Default: 19h

Access Bus Width: 8, 16, 32-bit

b7 b6 b5 b4 b3 b2 b1 b0

Maximum Latency

b[7:0]..........Maximum Latency

This register indicates how often DS-1L generates the Bus Master Request.

This register is hardwired to 19h.

-14-

January 14, 1999

Loading...

Loading...