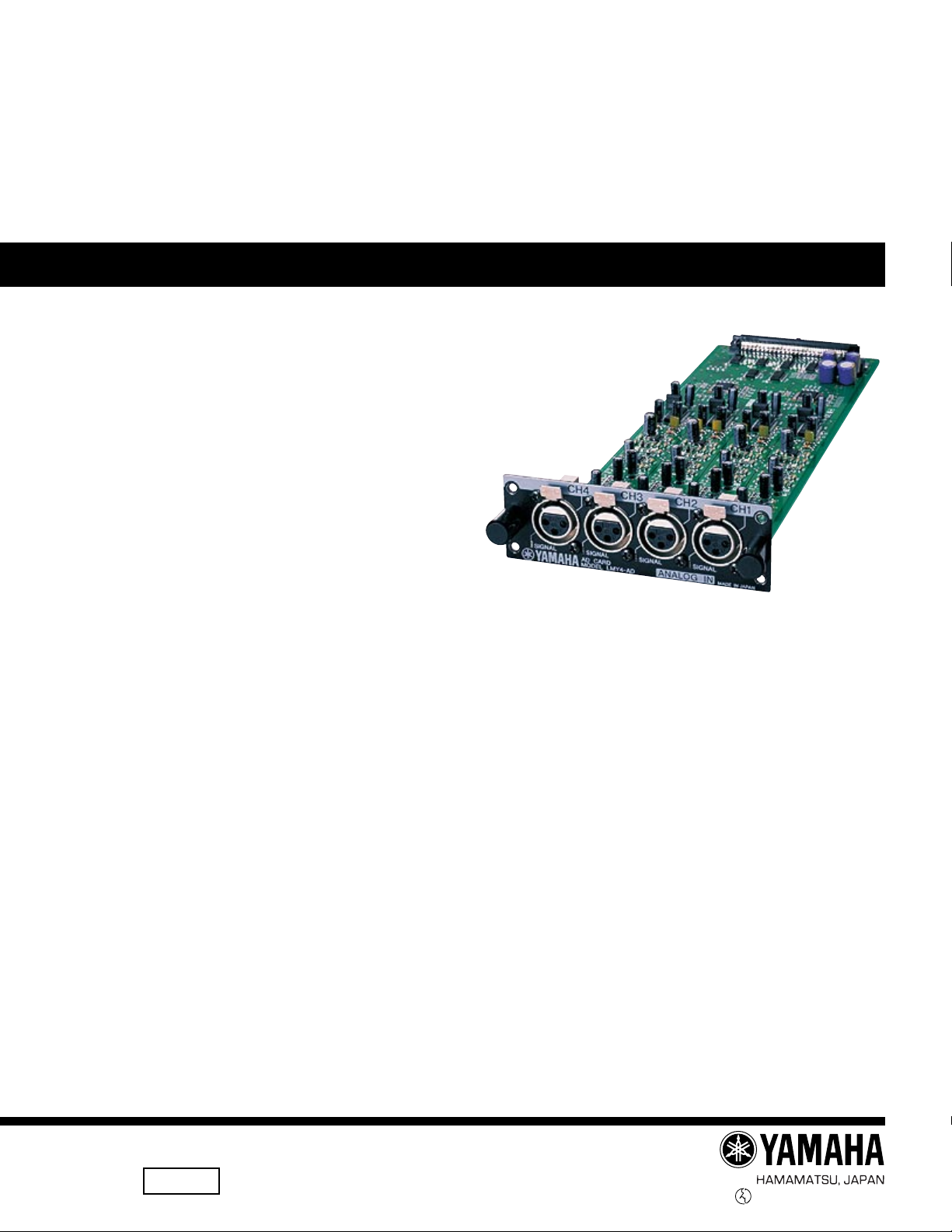

AD CARD

LMY4-AD

SERVICE MANUAL

PA

■ CONTENT

NOTICE OF CHANGES IN LMY4-AD S/M ............................... 3

SPECIFICATIONS .................................................................... 4

PANEL LAYOUT........................................................................ 4

DIMENSIONS ........................................................................... 4

BLOCK DIAGRAM .................................................................... 5

LSI PIN DESCRIPTION ............................................................ 6

IC BLOCK DIAGRAM................................................................ 8

CIRCUIT BOARD...................................................................... 9

TEST PROGRAM ................................................................... 11

PARTS LIST

CIRCUIT DIAGRAM

011503

*.**K-** K Printed in Japan '00.9

LMY4-AD

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed that

basic service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by the

users, and have therefore not been restated.

WARNING: Failure to follow appropriate service and safety procedures when servicing this product may result in personal injury,

destruction of expensive components, and failure of the product to perform as specified. For these reasons, we

advise all Yamaha product owners that all service required should be performed by an authorized Yamaha Retailer

or the appointed service representative.

IMPORTANT: The presentation or sale of this manual to any individual or firm does not constitute authorization, certification or

recognition of any applicable technical capabilities, or establish a principle-agent relationship of any form.

The data provided is believed to be accurate and applicable to the unit(s) indicated on the cover. The research, engineering, and

service departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable and

changes in specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to exist, please

contact the distributor's Service Division.

WARNING: Static discharges can destroy expensive components. Discharge any static electricity your body may have

accumulated by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to this bus).

IMPORTANT: Turn the unit OFF during disassembly and part replacement. Recheck all work before you apply power to the unit.

WARNING: CHEMICAL CONTENT NOTICE!

The solder used in the production of this product contains LEAD. In addition, other electrical/electronic and /or plastic (where applicable)

components may also contain traces of chemicals found by the California Health and Welfare Agency (and possibly other entities) to

cause cancer and/or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON WHATSOEVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose eyes to

solder/flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling food.

2

■ NOTICE OF CHANGES IN LMY4-AD S/M

IC BLOCK DIAGRAM

1. Losic IC HD74LV244AFPEL (IS024400) is changed to Losic IC TC74VHC244F (XT800A00)

2. Losic IC HD74LV245AFPEL (IS024500) is changed to Losic IC 74VHC245SJX (XY874A00)

TEST PROGRAM

Test program is newly provided. (Page 11)

LMY4-AD

3

LMY4-AD

■ SPECIFICATIONS

Input

Terminals

CH1-4

Actual Load

Impedance

10k ohm

* 0 dB is referenced to 0.775 Vrns.

** 1=GND, 2=HOT, 3=COLD

■ PANEL LAYOUT

For Use With

Nominal

600 ohm Lines

Input Level

Nominal

+10 dB (2.45 V)*

Maximum. Before Clip

+24 dB (12.3 V)*

Connector

XLR-3-31 type(Balanced)**

■ DIMENSIONS

66

4.5111

(4.5)

4

40

28

24.524

24

24

120

(23.5)

1

337

1

18

322.1

301.8

(1.3)

100

Unit: mm

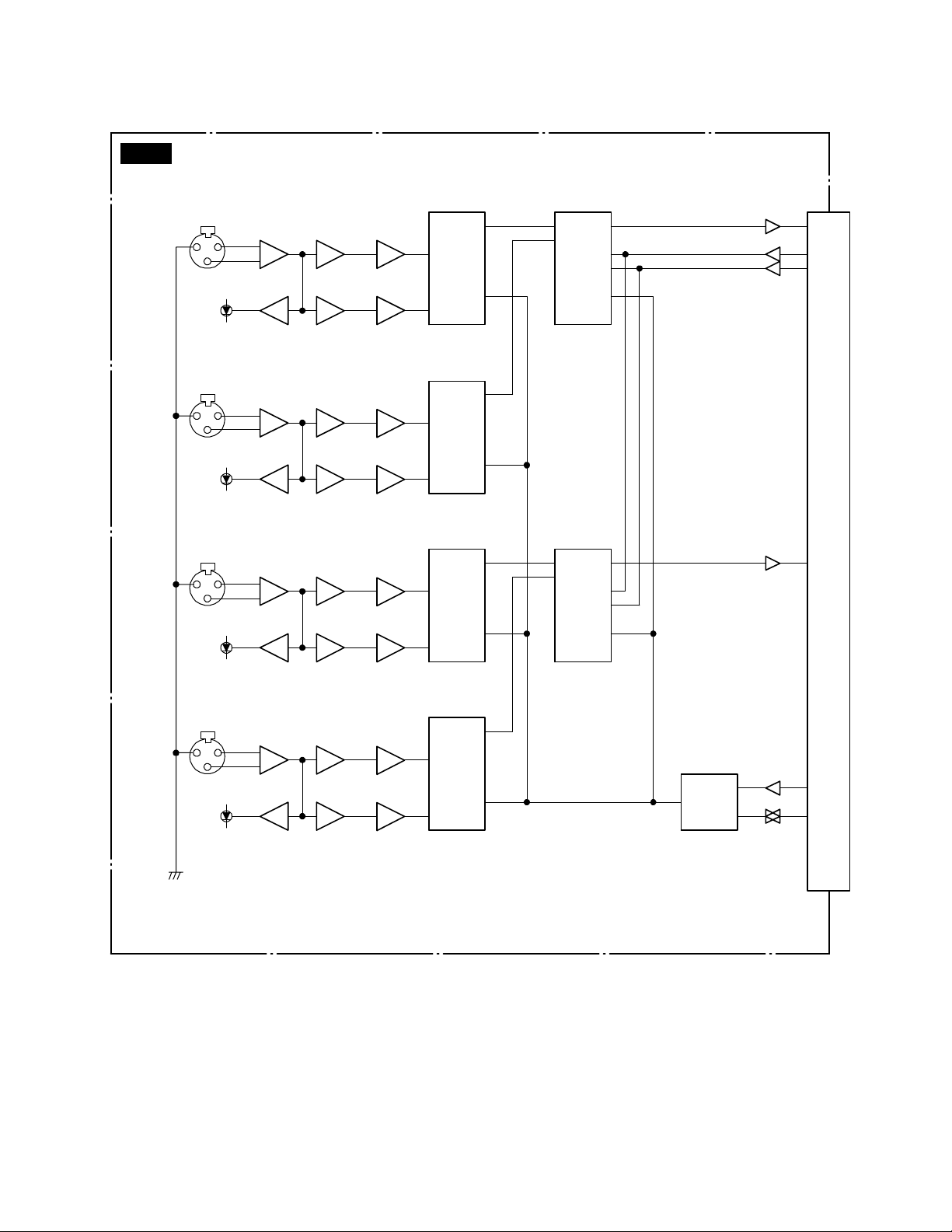

Amp

Amp

Amp

Amp

A/D

Amp

Amp

Amp

Amp

A/D

Amp

Amp

Amp

Amp

A/D

Amp

Amp

Amp

Amp

A/D

ADFC

ADFC

Reg.

I2 b/7

D00 a/34

D01 b/34

D02 a/35

D03 b/35

D04 a/36

D05 b/36

D06 a/37

D07 b/37

I1 a/7

SYNCM

b/15

256FS

a/19

A9 a/32

A8 b/31

A10 b/32

/RES

[CH1]

[SIGNAL]

[SIGNAL]

[SIGNAL]

[SIGNAL]

[CH2]

[CH3]

[CH4]

7

5

6

1

2

3

1

2

3

7

5

6

1

2

3

1

2

3

7

5

6

1

2

3

1

2

3

7

5

6

1

2

3

1

2

3

7

6

5

7

6

5

7

6

5

7

6

5

IC103

IC203

IC403

IC503

IC600

IC300

Amp

Amp

7

6

5

1

2

3

Amp

Amp

7

6

5

1

2

3

Amp

Amp

7

6

5

1

2

3

Amp

Amp

7

6

5

1

2

3

4

4

25

25

4

25

4

25

10

15

10

15

10

15

10

15 1

3

33

24

29

31

17

16

18 2

4

3

515

1-3

11-13

2-911-18

6

33

24

29

311

3

KEC-92518

IC100

IC101

IC102

IC100

IC201

IC202

IC400

IC401

IC402

IC400

IC501

IC502

1

2

3

1

2

3

1

2

3

1

2

3

IC301

IC301

IC303

IC302

AD2

IC304

■ BLOCK DIAGRAM

LMY4-AD

5

LMY4-AD

■ LSI PIN DESCRIPTION

YAC509 (XM167A00) ADFC AD1: IC300, 600

PIN

NAME I/O FUNCTION

No.

1

SI0 (L)

I

Input to Lch LO gain side (IMOD0=1)

Input to Lch (IMOD0=0)

2

SI1 (L)

3

SI0 (R)

I

Input to Lch HI gain side (IMOD0=1)

I

Input to Rch LO gain side (IMOD0=1)

Input to Rch (IMOD0=0)

4

5

6

7

IMOD0 (*)

SI1 (R)

WCKI

BCKI

I/O

I/O

I

Input to Rch HI gain side (IMOD0=1)

Word clock input/output of serial input

Bit clock input/output of serial input

I

Setting of serial input modes. "1" = parallel,

"0" = serial

8

IMOD1 (*)

I

Setting of serial input modes. "1" =

asynchronous, "0" = synchronous

9

10

11

12

13

14

ITM0 (*)

ITM1 (*)

GSEL0 (*)

GSEL1 (*)

DFC (*)

GCC (*)

I

Setting of input data timing

I

( " )

I

Setting of a floating gain

I

( " )

I

Digital filter ON/OFF ("1"=ON, "0"=OFF)

I

Automatic adjustment of floating gain

ON/OFF ("1"=ON, "0"=OFF)

15

HTC (*)

I

Quasi instantaneous cross fade bold time

ON/OFF ("1"=ON, "0"=OFF)

16

17

18

19

20

CFT0 (*)

CFT1 (*)

GND

VDD

Test1 (*)

I

Setting of cross fade time

I

( " )

GND

VDD(+5V)

I

Normally non-connected

21

22

Test2 (*)

Test3

I

O

"

"

ITM1

0

0

1

1

GSEL1

0

0

1

1

CFT1

0

0

1

1

Input timing (format)

ITM0

0

Move forward 20 bits closer

1

16 bits B.B format

0

18 bits B.B format

1

20 bits B.B format

Floating gain

GSEL0

12 dB (2 bits)

0

18 dB (3 bits)

1

24 dB (4 bits)

0

30 dB (5 bits)

1

Cross fade time

CFT0

0

1

0

1

0 ms

53 ms

106 ms

212 ms

PIN

NAME I/O FUNCTION

No.

23

XO

O

Connect X'tal OUT crystal oscillator or input

256fs clock to XI.

24

XI

I

Connect X'tal IN crystal oscillator or input

256fs clock to XI.

25

CK256A

O

Output clock which is inputted to 256fs OUT

XI.

26

27

MCK

BCKO

O

O

Output 128fs clock.

Output 64fs bit clock which divides MCK

(It rises at the head of SYNC).

28

WCKO

O

Output 1fs word clock which divides MCK

and of which the duty ratio is 50%.

29

SYNC

I/O

Input/output of 1fs synchronous clock (The

fall of SYNC makes the 6th rise of 256fs

the head of WC.)

30

31

32

SOR

SOL

CKSEL (*)

O

O

I

Output in order of Rch data and Lch data.

Output in order of Lch data and Rch data.

Switching of input or output of SYNC. "1" =

output, "0" = input.

33

34

35

RESET

MUTE (*)

OMD (*)

I

I

I

Internal reset at "0".

Output "0" for output mute all at "0".

SOL, SOR output (switching of "0"MBS

First/"1" LSB First).

36

37

38

39

40

41

NSC (*)

Test4

Test5

VDD

GND

DLSP0 (*)

I

O

O

Noise shooping ON/OFF. "1"=OFF, "0"=ON.

Normally non-connected.

"

VDD(+5V)

GND

I

Floating delay switching.

("1"=16 sample delay, "0"=0 sample delay)

42

FLSW (*)

I

Floating inhibiting SW.

"1"= floating, "0"= floating is inhibited.

ADC of output wave at HI level side.

43

44

Test6 (*)

Test7 (*)

I

I

Normally non-connected.

"

6

LMY4-AD

AK5392-VS-E2 (XV065A00) A/D CONVERTER

PIN

NAME I/O FUNCTION

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

VREFL

GNDL

VCOML

AINL+

AINLZCAL

VD

DGND

CAL

RST

SMODE2

SMODE1

LSCK

SCLK

O

O

O

I/O

I/O

L ch standard voltage output (+3.75V)

L ch standard grand (0 V)

L ch common voltage (+2.5 V)

I

L ch analog +input

I

L ch analog -input

I

Zero calibration

"L"=VCOML, VCOMR

"H": Analog input (AINLI,AINRI)

Power supply for digital

Ground for digital

Calibration status

I

Reset

I

Serial interface mode select

I

Clock for L/R ch select

Serial data clock

PIN

NAME I/O FUNCTION

No.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

SDATA

FSYNC

MCLK

CMODE

HPFE

TEST

B GND

A GND

AINR-

AINR+

VCOMR

GNDR

VREFR

VA

O

I/O

O

O

Serial data output

I

I

I

I

I

I

Frame synchronization clock

Master clock input

Master clock select

HPF enable pin

Test pin

Ground (0 V)

Ground for analog (0 V)

Power source for analog (5V)

Rch analog -input

Rch analog +input

R ch common voltage (2.5 V)

R ch standard glound (0 V)

R ch standard voltage output (3.75 V)

AD1: IC103, 203, 403, 503

7

Loading...

Loading...