Page 1

Zynq-7000 All Programmable SoC:

ZC702 Evaluation Kit

and

Video and Imaging Kit

(Vivado Design Suite 2013.3)

Getting Started Guide

UG926 (v6.0) December 17, 2013

This document applies to the following software versions: Vivado Design Suite 2013.3 and 2013.4This document applies to the following software versions: Vivado Design Suite 2013.3 and 2013.4This document applies to the following software versions: Vivado Design Suite 2013.3 and 2013.4This document applies to the following software versions: Vivado Design Suite 2013.3 and 2013.4

Page 2

Notice of Disclaimer

Send Feedback

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES

AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY,

NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including

negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with,

the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage

(inc luding l oss of data, profits, goodwil l, or any type of los s or dama ge suffe re d as a resul t of any act ion brough t by a t hi rd party) even if such

damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct

any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce,

modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions

of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm

terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application

requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps

Automotive Applications Disclaimer

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE

PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A

FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE

REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL

INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2012–2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands

included herein are trademarks of Xilinx in the United States and other countries. AMBA, AMBA Designer, ARM, ARM1176JZ-S, CoreSight,

Cortex, and PrimeCell are trademarks of ARM in the EU and other countries. PCI, PCIe, and PCI Express are trademarks of PCI-SIG and used

under license. HDMI, HDMI logo, and High-Definition Multimedia Interface are trademarks of HDMI Licensing LLC. All other trademarks are

the property of their respective owners.

.

; IP cores may be subject to warranty and support

2 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 3

Revision History

Send Feedback

The following table shows the revision history for this document.

Date Version Revision

05/25/2012 1.0

05/29/2012 1.1

06/21/2012 1.2

09/18/2012 2.0

Initial Xilinx release.

Added Figure 4-3 and the text just before and after it.

Chapter 1, Introduction: Added a “Reference Designs and Demonstrations” group to

section ZC702 Evaluation Kit Contents, page 8. Changed cable from Digilent USB

JTAG to Digilent USB-to-JTAG. Added that the SD MMC card contains bootable

configuration files for the Base TRD demo design files and Linux applications

platform. Updated USB JTAG interface information and added details to the clock

sources list in section For reference design files, documents, and board source files,

go to the Zynq-7000 AP SoC Video and Imaging Kit documentation page., page 10.

Changed FMC1 and FMC2 connector types to LPC I/O expansion connectors. Added

tables of default settings to the section Default Jumper and Switch Settings, page 11.

Chapter 2, ZC702 Evaluation Kit Built-In Self-Test: Updated switch settings in the

Introduction, page 15. Added bring-up details through the chapter. Settings were

added to section Run the BIST Application, page 22.

Added Chapter 3, Getting Started with the Base Targeted Reference Design.

Added Chapter 4, Using the AMS101 Evaluation Card.

Additional references were added through the book and to Appendix A, Additional

Resources.

The ZC702 evaluation kit now includes a USB Micro-B to female A adapter. Added

information about the Zynq-7000 AP SoC Video and Imaging Kit (ZVIK) to the

Overview, page 7 and a new section Zynq-7000 AP SoC Video and Imaging Kit

Contents, page 10. Photos are updated in Figure 1-3: Feature Callout for the ZC702

Board and Figure 2-2: ZC702 with the UART and Power Cable Attached. The TRD

Demonstration Procedure, page 30 adds information on how to demo the video

application using an external video source supporting use of the ZVIK. Added

Tab l e 3- 1 and Ta bl e 3 -2 . Added support for 720p video resolution in the video demo

application in Running the Video Demonstration for 720p Video Resolution, page 38.

11/12/2012 2.1

01/24/2013 3.0

ZC702 and ZVIK Getting Started Guide www.xilinx.com 3

UG926 (v6.0) December 17, 2013

Updated for ISE® Design Suite v14.3. Document and web site references changed

throughout the book. In BIST Setup Requirements, page 15, “A power adapter and

power cable for the ZC702 board” was removed. In ZC702 Evaluation Board Setup,

page 16, step 1 changed. In Install the USB-UART Driver, page 18,step 1 and step 2

changed. An introduction was added to Chapter 3. In Base TRD Key Features, page 27,

“1 GB DDR3 running at 533 MHz” was removed. In Base TRD Hardware Setup

Requirements, page 28, zImage and ramdisk8M.image.gz became uImage and

uramdisk8M.image.gz. The USB stick (or key) is not included in the kit. Instead,

download files from the ZC702 Product Page at www.xilinx.com/zc702

the Docs & Designs tab. Standoffs and a new Figure 3-3 showing mounting hardware

details were added to TRD Demonstration Procedure, page 30. Figure 3-6 and

Figure 3-7 were replaced to illustrate the QT-based GUI and minimized GUI mode.

USB key was removed from Chapter 4. Next Steps became Chapter 5.

Updated for ISE Design Suite 14.5. Revised eighth bullet on page 28 to replace

sentence ending in “to exercise the portions of the demo ...” to be “use the frame

buffer console terminal that will come up, once user exit the demo.” Added third note

on page 29. Revised Figure 3-6, page 33 and Figure 3-7, page 34.

and click on

Page 4

Date Version Revision

Send Feedback

02/12/2013 3.0.1

05/14/2013 4.0

08/12/13 5.0

Draft

10/21/13 6.0

Draft

Removed stray internal draft banner from the cover page, and from the first page in

each chapter and appendix.

Deleted “Key Features of the ZC702 Evaluation Board” section. The Base TRD Key

Features, page 27 were updated for the Programmable Logic (PL) to “One

Performance Monitor”. The required binaries in Base TRD Hardware Setup

Requirements, page 28 were updated to include “zynq-zc702-base-trd.dts“.

Port “P1” was labelled in Figure 3-2. Figure 3-6 and Figure 3-7 were replaced to

illustrate the QT-based GUI and minimized GUI mode. In Running the Video

Demonstration for 720p Video Resolution, page 38, the instructions were updated for

running QT based GUI in 720p mode and running the UART Menu based

Demonstration Application in 720p mode.

Updated document for Vivado Design Suite 2013.2. Added Command Line Application

block to Figure 3-1. Updated binaries under Base TRD Hardware Setup Requirements.

Updated commands under Running the Qt-Based GUI Application Demonstration,

Running the UART Menu-Based Demonstration Application, and Running the Video

Demonstration for 720p Video Resolution. Updated Figure 3-9 and Figure 4-1.

Updated Requirements to Get Started (modified steps 3 and 4 and deleted step 5).

Updated Evaluating AMS steps 2 and 3.

Updated document for Vivado Design Suite 2013.3. Updated Figure 3-6, Figure 3-7,

and Figure 3-9. Updated zynq> commands (changed sobel_qt to run_sobel.sh).

4 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 5

Table of Contents

Send Feedback

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Chapter 1: Introduction

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

ZC702 Evaluation Kit Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Zynq-7000 AP SoC Video and Imaging Kit Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Key Features of the ZVIK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Default Jumper and Switch Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Chapter 2: ZC702 Evaluation Kit Built-In Self-Test

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

BIST Setup Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Hardware BIST Board Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Hardware Bring-Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Run the BIST Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Chapter 3: Getting Started with the Base Targeted Reference Design

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Base TRD Key Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Base TRD Hardware Setup Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

TRD Demonstration Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Running the Qt-Based GUI Application Demonstration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Running the UART Menu-Based Demonstration Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Running the Video Demonstration for 720p Video Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Chapter 4: Using the AMS101 Evaluation Card

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Requirements to Get Started . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Evaluating AMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Chapter 5: Next Steps

Next Steps for the Zynq-7000 AP SoC Video and Imaging Kit (ZVIK) . . . . . . . . . . . . . . . . . . . . . . . . 45

ZC702 and ZVIK Getting Started Guide www.xilinx.com 5

UG926 (v6.0) December 17, 2013

Page 6

Appendix A: Additional Resources

Send Feedback

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Appendix B: Warranty

6 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 7

Introduction

UG926_c1_01_060712

Send Feedback

Overview

The Zynq®-7000 All Programmable SoC (AP SoC) ZC702 evaluation kit shown in Figure 1-1

is based on the XC7Z020 CLG484-1 AP SoC. For additional information, see the Zynq-7000

AP SoC Product Table [Ref 1]. A built-in self-test (BIST) is provided for the ZC702 evaluation

kit. The BIST provides a convenient way to test many of the board's features on power-up.

The tutorials and reference designs available on the Zynq-7000 AP SoC ZC702 Evaluation Kit

documentation page can be used to further explore the capabilities of the ZC702 board and

the Zynq-7000 AP SoC.

TIP: For the most up-to-date information on the content provided with the ZC702 evaluation kit, see

the Zynq-7000 AP SoC ZC702 Evaluation Kit product page

Concepts, Tools, and Techniques (UG873) [Ref 2] shows the basic hardware and software flow using the

ZC702 board. The Zynq-7000 AP SoC documentation page is also helpful.

Chapter 1

. Zynq-7000 All Programmable SoC:

X-Ref Target - Figure 1-1

Figure 1-1: ZC702 Evaluation Kit

ZC702 and ZVIK Getting Started Guide www.xilinx.com 7

UG926 (v6.0) December 17, 2013

Page 8

Chapter 1: Introduction

UG926_c1_02_110512

Send Feedback

The Zynq-7000 AP SoC Video and Imaging Kit (ZVIK) shown in Figure 1-2 is based on the

ZC702 evaluation kit and includes all of the components of the ZC702 kit with the

addition of components enabling HD video input from an High-Definition Multimedia

Interface (HDMI™) source or from the included HD image sensor. All of the information

presented in this guide related to the ZC702 evaluation kit applies to the ZVIK. For the

most current information on the content provided with the ZVIK, see the Zynq-7000 All

Programmable SoC Video and Imaging Kit product page.

X-Ref Target - Figure 1-2

Figure 1-2: Zynq-7000 AP SoC Video and Imaging Kit

This user guide also describes a Base Targeted Reference Design (TRD) based on Zynq-7000

AP SoC architecture. The Base TRD showcases various features and capabilities of the

Zynq Z-7020 AP SoC for the embedded domain in a single package.

TRDs are key components of the Xilinx Targeted Design Platform (TDP) strategy. TDPs from

Xilinx provide customers with basic scalable design platforms for the creation of

FPGA-based solutions in a wide variety of applications and industries.

Note:

as the ZC702 Evaluation Kit and the Zynq-7000 AP SoC Video and Imaging Kit is referred to as ZVIK.

In the remainder of this document, the Zynq-7000 AP SoC ZC702 evaluation kit is referred to

ZC702 Evaluation Kit Contents

The ZC702 evaluation kit includes the following items:

• ZC702 EK-Z7-ZC702-G evaluation board featuring the XC7Z020 CLG484-1

• Agile Mixed Signal (AMS) evaluation board

• Full Vivado design suite

8 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 9

Node-locked, device-locked to the Zynq-7000 XC7Z020 CLG484-1 device

Send Feedback

°

•Board design files

Schematics

°

Board layout files

°

Bill of materials

°

• Documentation

ZC702 Evaluation Kit and Video Imaging Kit Targeted Reference Design

°

Documentation Advisory

• Reference Designs and Demonstrations

BIST Utility and Demonstration

°

Targeted Reference Design (TRD), demonstrating a video processing pipeline.

°

ZC702 Evaluation Kit Contents

Note:

design, the user needs to register for an evaluation IP license for the Video IP.

AMS demonstration, providing an overview of the analog capabilities of the

°

The video demonstration contains the licensed IPs with no timeout. To recompile this

Zynq-7000 AP SoC devices.

• 12V AC adapter power supply

•Cables

RJ-45 Ethernet cable

°

HDMI cable

°

USB Type-A to USB Micro-B cable (Digilent USB-to-JTAG Programing Port)

°

USB Type-A to USB Mini-B cable (serial UART)

°

USB Micro-B to female A adapter (for connecting USB hub, keyboard, and mouse)

°

• Secure Digital Multimedia Card (SD MMC) (contains bootable configuration files for the

Base TRD demonstration design files and Linux platform applications)

The kit contains the software and reference designs, a demonstration, and documents to

help the user get started quickly.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 9

UG926 (v6.0) December 17, 2013

For reference design files, documents, and board source files, go to the Zynq-7000 AP SoC

ZC702 Evaluation Kit documentation page.

Page 10

Chapter 1: Introduction

Send Feedback

Zynq-7000 AP SoC Video and Imaging Kit Contents

The ZVIK contains all of the items included in the ZC702 evaluation kit plus the following

items. For more information on the HDMI input/output FMC module and ON Semiconductor

image sensor, refer to the Avnet product page [Ref 3].

• HDMI input/output FPGA mezzanine card (FMC) module

• ON Semiconductor VITA 2000 Color Image Sensor module

• Standard interchangeable

•Infrared (IR) cut filter

•Camera tripod

• Lens holder

•Cables

2

/3-inch 8 mm C-mount lens

Second HDMI cable

°

LCEDI image sensor cable

°

For reference design files, documents, and board source files, go to the Zynq-7000 AP

SoC Video and Imaging Kit documentation page.

Key Features of the ZVIK

Key features of the additional components of the Zynq-7000 AP SoC Video and Imaging kit

include:

•HDMI input/output FMC module

HDMI input

°

HDMI output

°

Video clock synthesizer

°

Interface for ON Semiconductor VITA image sensor module

°

• ON Semiconductor VITA 2000 color image sensor module

10 www.xilinx.com ZC702 and ZVIK Getting Started Guide

Supports up to WXGA resolution: 1920 (H) x 1200 (V) format

°

92 frames per second (fps) at full resolution

°

4.8 μ m x 4.8 μ m pixel size 2/3-inch optical format

°

Pipelined and triggered global shutter, rolling shutter

°

UG926 (v6.0) December 17, 2013

Page 11

X-Ref Target - Figure 1-3

FMC1 LPC

Connector

Xilinx XADC

Header

UG926_c1_03_111913

FMC2 LPC

Connector

8 User LEDs

User 2-Pole DIP Switch

Zynq-7000 AP SoC

Power Management System

(Bottom and Top of Board)

FPGA PROG Pushbutton

I2C Real-time Clock (RTC)

DDR3 Component

Memory (1 GB)

RGMII Ethernet

PHY Oscillator,

25,000 MHz

Quad SPI Flash Memory (1 Gb)

SD Card Interface Connector

Configuration Mode Select Switch

System Clock, 200 MHz,

2.5V LVDS

I2C Bus Switch

Power On/Off Slide Switch

CAN Bus Transceiver

HDMI Controller,

HDMI Video Connector

USB JTAG

Module with Integrated

USB Micro-B Connector

I2C Programmable User

Clock 3.3V LVDS

User Pushbuttons

Active High

Ethernet Status

LEDs

USB-to-UART Bridge,

USB Mini-B Connector

2x6 Male Header

Pins I/O Driven from

I2C Expander U80

USB 2.0 ULPI

Transceiver,

USB Micro-B

Connector

10/100/1000 MHz

Ethernet PHY,

RJ45 with Magnetics

2x6 and 1x6

PMOD I/O Header

12V Power Connector

PMBus Connector

(Bottom of board)

Send Feedback

Default Jumper and Switch Settings

Random programmable region of interest (ROI) readout

°

Automatic exposure control (AEC)

°

2

• Standard interchangeable

/3-inch, 8 mm C-mount lens

Default Jumper and Switch Settings

Figure 1-3 calls out the major features on the ZC702 board. See the ZC702 Evaluation Board

for the Zynq-7000 XC7Z020 All Programmable SoC User Guide (UG850) [Ref 4] for more

detailed information about the ZC702 board.

Default factory settings of jumpers and switches on the ZC702 board are highlighted in

Figure 1-4. Default switch and jumper settings are listed in Tab le 1- 1 and Ta bl e 1- 2.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 11

UG926 (v6.0) December 17, 2013

Figure 1-3: Feature Callout for the ZC702 Board

Page 12

Chapter 1: Introduction

UG926_c1_04_021213

1

8

9

7

SW11

Down/Off

2

3

4

6 5

1

8

9

7

SW11

Down/Off

2

3

4

6 5

Send Feedback

X-Ref Target - Figure 1-4

12 www.xilinx.com ZC702 and ZVIK Getting Started Guide

Figure 1-4: Default Jumper and Switch Settings on the ZC702 Board

UG926 (v6.0) December 17, 2013

Page 13

Table 1-1: Default Switch Settings

Send Feedback

Default Jumper and Switch Settings

Switch Position Setting

SW10

(JTAG chain input select two-position DIP switch)

SW12

(two-position DIP switch)

SW15

(two-position DIP switch)

SW16

(five-position DIP switch)

SW11

(power slide switch)

1Off

2On

1Off

2Off

1Off

2Off

1Right

2Right

3Right

4Right

5Right

Off

1Down

Figure 1-4

Callout

9

2

2

1

8

Default jumper positions are shown in Figure 1-4 and listed in Tabl e 1 - 2 .

Table 1-2: Default Jumper Settings

Jumper Function Default Position

HDR_1 X 2

J5 CFGBVS short to GND

J6 POR Master Reset

J7 USB 2.0 USB_VBUS_SEL

J8 XADC GND L3 Bypass

J9 XADC GND

J10 ARM HDR J41 pin 2 to VADJ

J11 UCD9248 U32 ADDR52 RESET_B

J12 FMC_VADJ_ON_B

J13 UCD9248 U33 ADDR53 RESET_B

J14 UCD9248 U34 ADDR54 RESET_B

J15 CAN BUS COMMON-MODE CANH HDR

J43 Ethernet PHY HDR

J44 USB 2.0 USB_RESET_B

J53 CAN BUS COMMON-MODE CANL HDR

OFF 4

OFF 1

ON 6

OFF 2

ON 2

OFF 7

OFF 4

ON 4

OFF 3

OFF 5

ON 7

ON 7

OFF 7

ON 7

Figure 1-4

Callout

ZC702 and ZVIK Getting Started Guide www.xilinx.com 13

UG926 (v6.0) December 17, 2013

J56 JTAG HDR J58 pin 2 3.3V SEL

J65 XADC_VCC5V0 = VCC5V0

OFF 9

ON 2

Page 14

Chapter 1: Introduction

Send Feedback

Table 1-2: Default Jumper Settings (Cont’d)

Jumper Function Default Position

HDR_1 X 3

J27 PS_SRST_B

J28 PS_POR_B

J30 Ethernet PHY HDR

J31 Ethernet PHY HDR

J32 Ethernet PHY HDR

J33 USB 2.0 Mode

J34 USB 2.0 J1 ID SEL

J35 USB 2.0 J1 VBUS CAP SEL

J36 USB 2.0 J1 GND SEL

J37 XADC_VREP SEL

J38 XADC_VCC SEL

J70 XADC_VREF Source SEL

1-2 1

1-2 1

1-2 7

NONE 7

NONE 7

2-3 6

1-2 7

1-2 6

1-2 7

1-2 2

2-3 2

2-3 2

Figure 1-4

Callout

14 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 15

Chapter 2

Send Feedback

ZC702 Evaluation Kit Built-In Self-Test

Introduction

The BIST tests many of the features offered by the ZC702 evaluation kit. The test is stored in

the onboard nonvolatile Quad SPI flash memory and configures the AP SoC when mode

switch SW16 is set to where SW1, 2, 3, and 5 are switched to the right and SW4 is switched

to the left, indicating QSPI configuration. This exercise of running the BIST demonstration

should take approximately 10 to 15 minutes.

Note:

Zynq-7000 XC7Z020 All Programmable SoC User Guide (UG850) [Ref 4].

For a description of all the features on the ZC702 board, see ZC702 Evaluation Board for the

BIST Setup Requirements

These are the prerequisites for running the BIST demonstration.

• Hardware setup:

ZC702 evaluation board with XC7Z020 CLG484-1 part

°

USB Type-A to Mini-B cable (for UART)

°

AC power adapter (12 VDC)

°

• Windows software and driver setup:

Tera Term Pro [Ref 5] (or similar) terminal program (might already be installed)

°

USB-UART driver from Silicon Labs [Ref 6] (might already be installed)

°

ZC702 and ZVIK Getting Started Guide www.xilinx.com 15

UG926 (v6.0) December 17, 2013

Page 16

Chapter 2: ZC702 Evaluation Kit Built-In Self-Test

UG926_c2_01_061212

Send Feedback

Hardware BIST Board Setup

This section describes the hardware setup and use of the terminal program for running the

BIST application. It contains step-by-step instructions for board bring-up.

ZC702 Evaluation Board Setup

The default jumper and switch settings of the ZC702 board are shown in Figure 1-4,

Tab le 1- 1 , and Tab le 1- 2.

1. Set the SW16 switch as shown in Figure 2-1, where position 1, 2, 3, and 5 are switched to

the right and position 4 is switched to the left for the BIST to boot from Quad SPI device

and run the system demonstration utility.

X-Ref Target - Figure 2-1

16 www.xilinx.com ZC702 and ZVIK Getting Started Guide

Figure 2-1: Settings for the Mode Switch to Boot from Quad SPI Mode

UG926 (v6.0) December 17, 2013

Page 17

Hardware Bring-Up

Send Feedback

Hardware Bring-Up

This section describes the steps for hardware bring-up.

1. Be sure to have the SW16 Mode switch settings set to those shown in Figure 2-1.

2. With the ZC702 board switched OFF (SW11 in the down position, as shown in

Figure 1-4), plug the USB Mini-B cable into the Mini USB port J17 labeled USB UART on

the ZC702 board and the other end into a open USB port on your PC (Figure 2-2).

X-Ref Target - Figure 2-2

12V Power

USB/UART

Init LED

UG926_c2_02_080212

Figure 2-2: ZC702 with the UART and Power Cable Attached

3. Connect the power cable.

4. Switch the ZC702 board’s power to ON (SW11 switched up as shown in Figure 1-4).

ZC702 and ZVIK Getting Started Guide www.xilinx.com 17

UG926 (v6.0) December 17, 2013

Page 18

Chapter 2: ZC702 Evaluation Kit Built-In Self-Test

UG926_c2_03_042513

Send Feedback

Install the USB-UART Driver

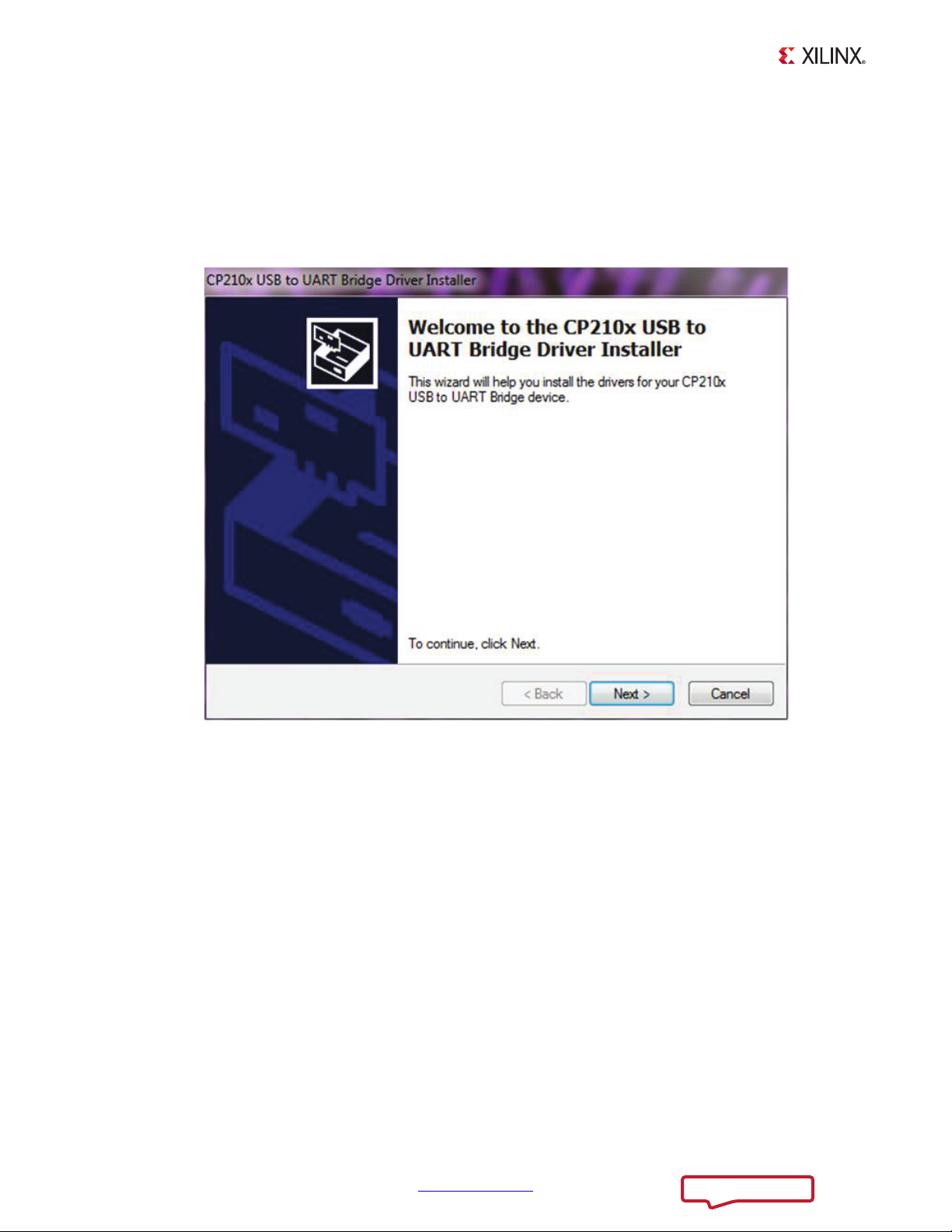

1. Run the downloaded executable UART-USB driver file, listed in BIST Setup Requirements,

page 15. Running the executable file enables USB-to-UART communications with a host

PC. This driver downloads and executes automatically when the board is powered up or

it can be downloaded from the Silicon Laboratories web site [Ref 6].

X-Ref Target - Figure 2-3

18 www.xilinx.com ZC702 and ZVIK Getting Started Guide

Figure 2-3: UART Cable Driver Installation

2. Set the USB-UART connection to a known COM Port and baud rate in the Device

Manager.

a. Left-click Start Menu and select Control Panel in Windows 7.

b. Select Device Manager on the left side.

c. Right-click the Silicon Labs device in the list and select Properties.

d. Click the Port Settings tab. Click the Advanced… button.

e. Select an open COM port between COM1 and COM4. This allows the computer to

remember the assignment and not reassign it each time the board serial UART port

is plugged in.

f. Select the baud rate = 115200, Data bits = 8, Parity = None, Stop Bits = 1, and Flow

control = None. Click OK.

Note:

Steps and diagrams refer to using a Windows XP or Windows 7 host PC.

UG926 (v6.0) December 17, 2013

Page 19

X-Ref Target - Figure 2-4

UG926_c2_04_061212

Send Feedback

Hardware Bring-Up

Figure 2-4 through Figure 2-6 show the steps for setting the USB-UART port.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 19

UG926 (v6.0) December 17, 2013

Figure 2-4: Configuring the Driver

Page 20

Chapter 2: ZC702 Evaluation Kit Built-In Self-Test

UG926_c2_05_061212

Send Feedback

X-Ref Target - Figure 2-5

20 www.xilinx.com ZC702 and ZVIK Getting Started Guide

Figure 2-5: UART Port Setting Tab

UG926 (v6.0) December 17, 2013

Page 21

X-Ref Target - Figure 2-6

UG926_c2_06_061212

Send Feedback

Hardware Bring-Up

Figure 2-6: Select a COM Port (between COM1 and COM4)

ZC702 and ZVIK Getting Started Guide www.xilinx.com 21

UG926 (v6.0) December 17, 2013

Page 22

Chapter 2: ZC702 Evaluation Kit Built-In Self-Test

Send Feedback

Run the BIST Application

1. Start Tera Term or a comparable installed terminal program. Configure it to have the

following settings:

Baud = 115200, Data = 8, Parity = None, Stop = 1 and Flow = None.

2. Press POR_B (SW1) located in the top left corner of the ZC702 board and view the BIST

output on the terminal window (Figure 2-7).

X-Ref Target - Figure 2-7

22 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926_c2_07_061412

Figure 2-7: BIST Main Menu

3. Select each relevant test and observe the test results.

For more information on the BIST software and additional tutorials, including how to restore

the default content of the onboard Quad SPI flash nonvolatile storage, see the ZC702 BIST

User Guide (ZC702 BIST PDF file, XTP180) on the Zynq-7000 AP SoC ZC702 Evaluation Kit

documentation page.

For more detailed information about these BIST tests, see the ZC702 Evaluation Board for

the Zynq-7000 XC7Z020 All Programmable SoC User Guide (UG850) [Ref 4].

UG926 (v6.0) December 17, 2013

Page 23

Run the BIST Application

Send Feedback

TIP: If any of the BIST tests fail, check the settings of the switches and jumpers as shown in Figure 1-4,

Table 1 - 1 , and Table 1-2. If these settings are correct and the test still fails, please contact Xilinx

Support to review your Support options.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 23

UG926 (v6.0) December 17, 2013

Page 24

Chapter 2: ZC702 Evaluation Kit Built-In Self-Test

Send Feedback

24 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 25

Chapter 3

Send Feedback

Getting Started with the Base Targeted

Reference Design

Introduction

This section provides step by step instructions for bringing up the board and running the

video Targeted Reference Design (TRD). In this design, the Zynq-7000 AP SoC performs

real-time processing of a 1080p60 video stream—either in Processing System (PS) software

or Programmable Logic (PL) hardware accelerator. The video processing path is

user-selectable through a graphical user interface (GUI) running on Linux in the Zynq-7000

AP SoC PS. The GUI also displays detailed information about system usage statistics and

system performance.

Figure 3-1 shows the system block diagram for Zynq-7000 AP SoC Base TRD.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 25

UG926 (v6.0) December 17, 2013

Page 26

Chapter 3: Getting Started with the Base Targeted Reference Design

Send Feedback

X-Ref Target - Figure 3-1

Linux User Space

Command Line Application

Linux Kernel

Kernel Libraries and Utilities Device Drivers

Processing

System

DDR Memory Controller

AMBA Switches

APU

AMBA Switches

Qt-Based Multithreaded Application

Programmable

Logic

Display Controller

Video Processing

(Sobel Filter)

Video Test Pattern

Generator

S_AXI3_HP 64 bit

M_AXI3_GP 32 bit

Video

Output

(Optional)

Video Input

with

Zynq-7000

Video and

Imaging Kit

UG926_c3_01_061213

Figure 3-1: Zynq-7000 AP SoC ZC702 and ZVIK Base TRD System Block Diagram

The Base TRD showcases various features and capabilities of the Zynq Z-7020 AP SoC for the

embedded domain in a single package. The Base TRD consists of two processing elements:

The Zynq-7000 AP SoC processing system (PS) and an interconnect logic-based video

accelerator. The AP SoC allows the user to implement a specific functionality either as a

software program running on the Zynq-7000 AP SoC PS or as a hardware design inside the

programmable logic (PL). The Base TRD demonstrates how the user can seamlessly switch

between a software or a hardware implementation, contributing to ease of use. The TRD also

demonstrates the value of offloading computation-intensive tasks onto PL, thereby freeing

the CPU resources to be available for user-specific applications.

The ZC702 evaluation kit and ZVIK come with an SD card loaded with binaries that enable

the user to run the video demonstration and software application. It also includes the

binaries necessary to configure and boot the Zynq-7000 AP SoC board.

Note:

provide general information only.

The screen captures in this document are conceptual representations of their subjects and

26 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 27

Base TRD Key Features

Send Feedback

Base TRD Key Features

The PS includes:

• Two ARM® Cortex™-A9 MPcore processors, each with a 32 KB instruction cache, a

32 KB data cache, and a NEON™ media processing engine and vector floating-point

processor (VFPv3).

• 512 KB of level 2 cache

• 256 KB of on-chip RAM

• ARM AMBA® AXI interconnect

• Multi-protocol, 32-bit DDR DRAM controller

• Standard peripheral interfaces including USB, Ethernet, UART, I2C, SD MMC, and GPIO

• Clocks and reset for PL

• High bandwidth interconnect between PS and PL

The PL includes:

• Two AXI interconnects, 64-bit wide at 150 MHz

• One AXI interconnect, 32-bit wide at 75 MHz

•AXI VDMA(s)

• A full HD video input (ZVIK) and output interface

• A Sobel accelerator

• One Performance Monitor

The software includes:

• Xilinx Zynq-7000 AP SoC standard Linux kernel (based on Open Source Linux version

3.x)

• Linux device drivers for TRD-specific IPs.

• A Qt-based Linux application demonstrating the video processing pipeline

• A command line menu-based Linux application demonstrating the video processing

pipeline

ZC702 and ZVIK Getting Started Guide www.xilinx.com 27

UG926 (v6.0) December 17, 2013

Note:

The video demonstration contains the licensed IPs with no timeout.

Page 28

Chapter 3: Getting Started with the Base Targeted Reference Design

Send Feedback

Base TRD Hardware Setup Requirements

These items are required to run and test the Base TRD and the video demonstration:

• The ZC702 evaluation board with the XC7Z020 CLG484-1 part

• USB Type-A to USB Mini-B cable (for UART communications) and a Tera Term Pro (or

similar) terminal program [Ref 5]

• USB-UART drivers from Silicon Labs [Ref 6]

• AC power adapter (12 VDC)

• An HDMI cable (two cables if using the ZVIK and the user desires to use an external

video source for the demonstration)

• SD MMC flash card containing TRD binaries formatted with FAT32

Note:

the first partition of the SD MMC card and include:

• USB Micro-B to female A adapter

• A USB hub is needed for connecting a keyboard and mouse (not included with the kit).

If a USB hub is not available, it is still possible to run the demonstration with only a USB

mouse, but the user will not be able use the frame buffer console terminal that will

come up once the user exits the demo.

• USB mouse and keyboard (optional—not included with the kit)

• An HDMI-compatible display monitor that supports full HD resolution: 1920 x 1080p

@ 60 Hz (not included with the kit). If the user wants to test at 720p video resolution,

the display monitor should support 720p resolution: 1280 x 720p @ 60 Hz. If an HDMI

monitor is not available, a DVI monitor can be used, but an HDMI to DVI-D

cable/connector adapter is required (not included with the kit). The connector adapter

can be easily obtained at most electronic retailers or through a variety of online

sources.

The included SD MMC is pre-loaded with required binaries. The binaries are loaded into

- BOOT.bin

- image.ub

- autostart.sh

Note:

Additionally, the binaries should be loaded at its root level. If the files are not loaded on the

SD card, copy the files from the ready_to_test directory to the SD card.

The default binary device tree configures the video-out resolution to 1080p.

28 www.xilinx.com ZC702 and ZVIK Getting Started Guide

Instructions for running the demonstration at 720p are provided in Running the Video

Demonstration for 720p Video Resolution, page 38.

Note:

display monitor. However, the example should work well with any HDMI-compatible display

device.

The example mentioned in this package has been tested with a Dell model #P2412H

UG926 (v6.0) December 17, 2013

Page 29

Base TRD Hardware Setup Requirements

Send Feedback

• For the ZVIK, if running with an external video input source is desired, use the

FMC-IMAGEON HDMI input/output FMC module to connect an external video source.

RECOMMENDED: An HDMI video source is required to provide the external video input. If an HDMI

source is not available, a DVI source can be used, but an HDMI to DVI-D cable/connector adapter is

required (not included with the kit). The connector adapter can be easily obtained at most electronic

retailers or through a variety of online sources. The external video source must be 1080P 60 Hz and

must not deliver content with copy protection or Digital Rights Management (DRM) enabled. Many DVD

and media players output content with DRM enabled even if the content is not DRM protected. A laptop

or other source is recommended.

IMPORTANT: This TRD does not support input from the camera provided in the ZVIK. Check the ZVIK

product page for additional designs and resources.

Note: When connecting an external video source to the FMC card:

• Connect the source only after the bit file is programmed. Connecting the source only

after system boot-up is recommended.

• Ensure that the source resolution is set to the same resolution used by the demo (1080p

or 720p). See Running the Video Demonstration for 720p Video Resolution, page 38 for

more details.

• Ensure that the refresh rate for the source is set to 60 Hz.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 29

UG926 (v6.0) December 17, 2013

Page 30

Chapter 3: Getting Started with the Base Targeted Reference Design

Keyboard and mouse

connected through USB hub

Video-In

Power

UG926_c3_02_041613

UART connector

J1

P1

Send Feedback

TRD Demonstration Procedure

This section provides a procedure for setting up the ZC702 board or ZVIK and running the

demonstration provided with the kit.

Board Setup

1. For customers using the ZVIK, assemble the FMC module to the ZC702 base board. The

FMC module and HDMI video input are not required for either kit to run the TRD, but

ZVIK customers can run the TRD demonstration using the external video input in

addition to the built-in Test Pattern Generator if the FMC card is installed. Two sets of

standoff hardware are in the box, which can be used to secure the FMC-IMAGEON FMC

module on the ZC702 base board and support the free end of the board. Assemble the

hardware as shown in Figure 3-3. Use the longer standoffs, screws, and rubber feet for

the free end of the board.

2. Connect the cables as shown in Figure 3-2 to prepare the ZC702 board to run the TRD

video demonstration.

X-Ref Target - Figure 3-2

Figure 3-2: ZC702 Board Setup for a Video Demonstration

a. Connect an LCD monitor to the HDMI out port P1 of the ZC702 board using an HDMI

cable.

b. Connect a keyboard and mouse to the USB hub, which is connected to the ZC702

board Micro-B USB connector J1 labeled USB ULPI through the USB Micro-B to

female A adapter. If a USB hub is not available, the mouse can be plugged directly

into the female USB connection of the USB Micro-B to female A adapter, but the user

30 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 31

X-Ref Target - Figure 3-3

UG926_c3_03_111012

Send Feedback

TRD Demonstration Procedure

will not be able to exercise the portions of the demonstration that require a

keyboard.

c. Connect the USB Mini-B cable into the Mini USB port J17 labeled USB UART on the

ZC702 board and the USB Type-A connector end of the cable into an open USB port

on the host PC for UART communications.

d. For customers using the ZVIK, mount the FMC-IMAGEON HDMI input/output FMC

module onto the FMC-2 slot present on the ZC702 board. Attach the FMC board to

the ZC702 carrier board using the two short standoffs and four short screws as

shown in Figure 3-3. Use the two long standoffs, four longer screws, and rubber feet

to support the free end of the board. Connect an external video source to the FMC

module HDMI input labeled HDMI IN with 1080p60 resolution. A 720p60 source can

also be used, but it requires adjustment to the system as described in the section

Running the Video Demonstration for 720p Video Resolution, page 38.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 31

UG926 (v6.0) December 17, 2013

Figure 3-3: ZVIK FMC Mounting Hardware Detail

e. Connect the power supply to the ZC702 board connector J60. Do not switch the

power on.

3. Insert the SD MMC, which contains the TRD binaries, into the SD slot on the ZC702

board.

Ensure the binary files are in the first partition of the FAT32-formatted SD MMC card

°

at its root level.

Page 32

Chapter 3: Getting Started with the Base Targeted Reference Design

UG926_c3_04_111012

Send Feedback

Note:

rdf0286-zc702-zvik-base-trd-2013.3/ready_to_test folder directly onto the

primary partition of the SD MMC card (which is formatted as FAT32) at the root level using an

SD MMC card reader. The files in the SD MMC card should match the list described in

SD MMC flash card containing TRD binaries formatted with FAT32, page 28.

If the evaluation kit design files were downloaded online, copy all the f iles within the

4. Make sure the switches are set as shown in Figure 3-4, which allows the ZC702 board to

boot from the

X-Ref Target - Figure 3-4

SD MMC card.

Figure 3-4: Switch Settings for the Mode Switch to Boot from the SD MMC Card

5. Make sure the display monitor is set for HDMI or DVI 1920 x 1080.

Running the Qt-Based GUI Application Demonstration

1. Power on the ZC702 board. The default binary Linux device tree configures and runs the

video demonstration for 1080p video-out resolution.

2. Start the installed UART terminal program on your host PC (e.g., Tera Term Pro on a

Windows PC, GtkTerm on a Linux PC).

Use the following UART configuration: Baud rate = 115200, bits = 8, parity = none, and

stop bits = 1.

Note:

Demonstration application.

This step is required to view debug information or to run the UART Menu-Based

32 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 33

Running the Qt-Based GUI Application Demonstration

Send Feedback

3. Wait for the ZC702 board to be configured and booted with Linux. The XILINX ZYNQ

banner appears on the display monitor after approximately two minutes as shown in

Figure 3-5.

X-Ref Target - Figure 3-5

UG926_c3_05_111012

Figure 3-5: Zynq Banner

X-Ref Target - Figure 3-6

4. The Qt-based video demonstration application starts. The GUI application shows up at

the bottom of the screen (see Figure 3-6).

ZC702 and ZVIK Getting Started Guide www.xilinx.com 33

UG926 (v6.0) December 17, 2013

UG926_c3_06_102813

Figure 3-6: Qt-Based GUI to Control the Video Pipeline

Page 34

Chapter 3: Getting Started with the Base Targeted Reference Design

UG926_c3_07_102813

Send Feedback

5. The Qt-based application allows the user to experience the Base TRD video

demonstration and is controlled through the mouse. The user can click Help for short

messages and information about the control window of the QT application. The GUI can

be minimized with the MIN button (See Figure 3-6) and can be brought back to the

original size with the MAX button. The user can also control transparency of the GUI with

the Transparency slider.

X-Ref Target - Figure 3-7

Figure 3-7: Minimized GUI Mode

6. Click Enable Video to start the internal Test Pattern Generator (TPG), which displays on

the monitor.

7. Exercise different options by pressing the buttons available in the GUI to evaluate the

different use cases mentioned in Tabl e 3 -1 .

Table 3-1: Zynq-7000 AP SoC Base TRD Video Demonstration Use Cases

Use Case Video Source Control Sobel Filter Control

1 TPG interference Sobel OFF

2 TPG interference Sobel - SW

3 TPG interference Sobel - HW

Additional ZVIK Options

4 External video Sobel OFF

5 External video Sobel - SW

6 External video Sobel - HW

34 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 35

Running the Qt-Based GUI Application Demonstration

Send Feedback

Video source control modes are explained as follows:

• TPG interference

The input video is generated by the TPG IP implemented in the PL.

°

• External video (available with the optional ZVIK FMC module)

The input video is supplied by an external video source and is connected through

°

the FMC-IMAGEON card.

Sobel filter modes are explained as follows:

Sobel OFF

• No processing done. Sobel filter is bypassed.

Sobel – SW

• Video processing (edge-detection filter) done by software code running on the PS.

• Observe CPU utilization going up to 100% for one of the two CPUs (this can be seen in

the CPU usage graph). In this mode, the frame rate of the video also drops to about

3 fps to 10 fps depending upon resolution.

Sobel – HW

• Video processing (edge-detection filtering) done by PL.

• Observe CPU utilization going down (to approximately 0%) and the frame rate jumping

to 60 fps.

Figure 3-8 shows the detected image edges of the video generated by the TPG, that is, case

1 versus case 2 or 3 of Tabl e 3 -1 .

ZC702 and ZVIK Getting Started Guide www.xilinx.com 35

UG926 (v6.0) December 17, 2013

Page 36

Chapter 3: Getting Started with the Base Targeted Reference Design

UG926_c3_08_041113

Send Feedback

X-Ref Target - Figure 3-8

Figure 3-8: Images with Sobel Filter On (Left) and with Sobel Filter Off (Right)

While exercising the modes described above, one can observe AXI bus bandwidth utilization

and CPU utilization on the graphs in the Qt GUI application.

8. Click Exit to quit the application and return the user to Linux console.

9. The application can be restarted by typing the following at the Linux command prompt:

zynq> run_sobel.sh -qt -res 1920x1080

Running the UART Menu-Based Demonstration Application

A command line based Linux application demonstration is also provided with the package.

This application presents the user with a command line menu-based UI to exercise different

modes of the video demonstration.

To run the menu-based UI application demonstration, the Qt-based GUI application which

was started (as explained in Running the Qt-Based GUI Application Demonstration, page 32)

needs to be quit as per step 8, page 36.

36 www.xilinx.com ZC702 and ZVIK Getting Started Guide

The following steps explain how to start the UART menu-based application demonstration

and exercise different application video use cases.

1. Go to the UART terminal started on your host PC as explained in step 2 from Running the

Qt-Based GUI Application Demonstration, page 32.

UG926 (v6.0) December 17, 2013

Page 37

X-Ref Target - Figure 3-9

UG926_c3_09_111913

Send Feedback

Running the UART Menu-Based Demonstration Application

2. Type these commands at the Linux command prompt into the host PC based terminal:

zynq> run_sobel.sh -cmd -res 1920x1080

The menu-based video application demonstration starts as shown in Figure 3-9.

Figure 3-9: Command Line Based UI Menu

Exercise different options by entering the use case number displayed in Tab l e 3-2 against

Enter your choice: on the terminal.

Table 3-2: Zynq-7000 AP SoC Base TRD Video Demonstration Use Cases

Use Case Video Source Control Sobel Filter Control

1 TPG interference Sobel OFF

2 TPG interference Sobel - SW

3 TPG interference Sobel - HW

Additional ZVIK Options

4 External video Sobel OFF

5 External video Sobel - SW

6 External video Sobel - HW

Video source control modes are explained as follows:

• TPG interference

The input video is generated by the TPG IP implemented in the PL.

°

ZC702 and ZVIK Getting Started Guide www.xilinx.com 37

UG926 (v6.0) December 17, 2013

Page 38

Chapter 3: Getting Started with the Base Targeted Reference Design

Send Feedback

• External video (available with the optional ZVIK FMC module)

The input video is supplied by an external video source and is connected through

°

the FMC-IMAGEON card.

Sobel Filter Modes are explained as follows:

Sobel OFF

• No processing done. Sobel filter is bypassed.

Sobel – SW

• Video processing (edge-detection filter) done by software code running on PS

Sobel On – HW

• Video processing (edge-detection filter) done by PL

Figure 3-8 shows the detected image edges of the video generated by the TPG, that is,

case 1 versus case 2 or 3 of Tabl e 3 - 2 .

3. Enter 0 to exit the application and return to the command prompt.

Running the Video Demonstration for 720p Video Resolution

Configure the display monitor to 720p60 resolution: 1280 x 720p @ 60 Hz. If using the ZVIK

with an external video source, configure the external video source to 1280 x 720 @ 60 Hz.

• Follow these steps for running QT based GUI demonstration application in 720p mode:

a. Exit any previously running applications.

b. Type these commands at the Linux command prompt into the host PC based

terminal:

zynq> run_sobel.sh -qt -res 1280x720

• Follow the steps for running UART Menu based Demonstration Application in 720p

mode:

a. Exit any previously running applications.

38 www.xilinx.com ZC702 and ZVIK Getting Started Guide

b. Type these commands at the Linux command prompt into the host PC based

terminal:

zynq> run_sobel.sh -cmd -res 1280x720

UG926 (v6.0) December 17, 2013

Page 39

Running the Video Demonstration for 720p Video Resolution

Send Feedback

For additional example designs, tutorials, software, and other information related to the

ZVIK, see Next Steps for the Zynq-7000 AP SoC Video and Imaging Kit (ZVIK), page 45.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 39

UG926 (v6.0) December 17, 2013

Page 40

Chapter 3: Getting Started with the Base Targeted Reference Design

Send Feedback

40 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 41

Using the AMS101 Evaluation Card

Send Feedback

Introduction

Each Xilinx Zynq-7000 AP SoC features two 1 MSPS, 12-bit, analog-to-digital converters

(ADCs) built into the device for everything from simple analog monitoring to more signal

processing-intensive tasks like linearization, calibration, over-sampling, and filtering. The

ZC702 evaluation kit includes the hardware and software to evaluate this ADC feature and to

determine its usefulness in the user’s end system.

For evaluation of Xilinx Agile Mixed Signal (AMS) capability, the following items in the kit are

needed:

• Access to the ZC702 XADC header

Chapter 4

• AMS101 evaluation card (see Figure 4-1)

• Design and software files, which can be downloaded from the web

• Zynq-7000 AP SoC design programming files

• USB-UART drivers from Silicon Labs

•Blank

SD MMC card

ZC702 and ZVIK Getting Started Guide www.xilinx.com 41

UG926 (v6.0) December 17, 2013

Page 42

Chapter 4: Using the AMS101 Evaluation Card

Reference

Buffer

for DAC

Jumpers to Select

DAC or External

Signal Source

Pins Allow for

External Analog

Input Signals

16-bit

DAC Sets

Analog Test

Voltage

Digital I/O

Level

Translators

UG926_c4_01_061913

Send Feedback

X-Ref Target - Figure 4-1

Figure 4-1: AMS101 Evaluation Card

Requirements to Get Started

1. The AMS101 evaluation requires a Windows host PC to install the National Instruments

LabVIEW Run-Time engine.

2. Verify the USB/UART Silicon Labs drivers are installed as described in Install the

USB-UART Driver, page 18.

3. Install the AMS Evaluator tool GUI.

Download the AMS Evaluator installer files (7 Series FPGA and Zynq AMS Evaluator

Installer for AMS Targeted Reference Design) at

www.xilinx.com/support/documentation/ams101_evaluation_card.htm

setup.exe file to install the National Instruments LabVIEW RunTime Engine needed to

host the AMS Evaluator tool.

The GUI itself has been built using National Instruments LabVIEW 2011 software. To

enable use of the GUI without the need for a LabVIEW license, Xilinx has bundled the

LabVIEW run-time engine with the GUI installer. During the installation process, the

run-time engine is installed on the PC.

4. Download the AMS design files from the Zynq-7000 AP SoC ZC702 Evaluation Kit

documentation page. Next, open the xadc_eval_design_zc702_vxx folder. Then, open the

ready_to_test folder and load the boot.bin file to the SD-MMC card.

. Click the

42 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 43

Evaluating AMS

UG926_c4_02_061212

Done LED

Send Feedback

Evaluating AMS

1. Connect and power the hardware.

a. Connect the ZC702 board to the AMS101 evaluation card, making sure the notch on

the XADC header lines up correctly with the AMS101 evaluation card. see Figure 4-2.

X-Ref Target - Figure 4-2

ZC702 and ZVIK Getting Started Guide www.xilinx.com 43

UG926 (v6.0) December 17, 2013

Figure 4-2: ZC702 Board with AMS101 Evaluation Card Plugged into XADC Header

2. Download the design to the Zynq-7000 AP SoC.

a. Plug the

SD MMC card into the ZC702 board.

b. Set the ZC702 board switch settings to boot from SD mode (Figure 3-4).

c. Power on the ZC702 board. After about 15 seconds, the Done LED (DS3) turns green,

indicating the design file on the

SD MMC card has properly loaded onto the

Zynq-7000 AP SoC.

3. Run the AMS101 Evaluator LabVIEW GUI executable file.

a. On the Host PC, open AMS101 Evaluator GUI V1.1.exe from the desktop.

The AMS Evaluator Tool allows designers to quickly evaluate the analog signals in the time

and frequency domain, display linearity, verify the XADC register settings, and measure the

internal temperature sensor and supply voltages.

Page 44

Chapter 4: Using the AMS101 Evaluation Card

Send Feedback

X-Ref Target - Figure 4-3

UG926_c4_03_061212

Figure 4-3: AMS101 Evaluator GUI

For a more extensive explanation of the AMS101 evaluation card, refer to the AMS101

Evaluation Card User Guide (UG886) [Ref 7]. For a more extensive explanation of the AMS

targeted reference design for ZC702, refer to the 7 Series FPGA AMS Targeted Reference

Design User Guide (UG960) [Ref 8].

44 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 45

Next Steps

Send Feedback

For more information on reference designs included in this kit, software, and additional

tutorials, including how to restore the default content of the onboard nonvolatile storage,

see the Zynq-7000 AP SoC ZC702 Evaluation Kit product page

Next Steps for the Zynq-7000 AP SoC Video and Imaging Kit (ZVIK)

For more information on additional example designs (including a camera design), tutorials,

software, and other information available for the ZVIK, see the Zynq-7000 All Programmable

SoC Video and Imaging Kit product page.

Chapter 5

Note:

Reference Design (XAPP794

Vivado Design Suite 2013.2 is required to implement the 1080p60 Camera Image Processing

).

ZC702 and ZVIK Getting Started Guide www.xilinx.com 45

UG926 (v6.0) December 17, 2013

Page 46

Chapter 5: Next Steps

Send Feedback

46 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 47

Additional Resources

Send Feedback

Xilinx Resources

For support resources such as Answers, Documentation, Downloads, and Forums, see the

Xilinx Support website

.

Appendix A

For continual updates, add the Answer Record to your myAlerts

For definitions and terms, see the Xilinx Glossary

.

.

Solution Centers

See the Xilinx Solution Centers for support on devices, software tools, and intellectual

property at all stages of the design cycle. Topics include design assistance, advisories, and

troubleshooting tips.

References

The most up to date information related to the ZC702 board and its documentation is

available on these websites:

Zynq-7000 AP SoC ZC702 Evaluation Kit product page

Zynq-7000 AP SoC ZC702 Evaluation Kit documentation page

ZC702 and ZVIK Getting Started Guide www.xilinx.com 47

UG926 (v6.0) December 17, 2013

Zynq-7000 AP SoC Video and Imaging Kit product page

Zynq-7000 AP SoC Video and Imaging Kit documentation page

Zynq-7000 SoC ZC702 Evaluation Kit Master Answer Record (AR 47864)

Page 48

Appendix A: Additional Resources

Send Feedback

These documents and sites provide supplemental material useful with this guide:

1. Zynq-7000 All Programmable SoC Product Table

2. Zynq-7000 All Programmable SoC: Concepts, Tools, and Techniques (UG873)

3. Avnet product page

4. ZC702 Evaluation Board for the Zynq-7000 XC7Z020 All Programmable SoC User Guide

(UG850

5. Tera Term home page

6. Silicon Labs USB-UART drivers page

7. AMS101 Evaluation Card User Guide (UG886)

)

8. 7 Series FPGA AMS Targeted Reference Design User Guide (UG960

9. Zynq-7000 All Programmable SoC ZC702 Base Targeted Reference Design User Guide

(UG925

10. Xilinx Application Notes, Reference Designs, Video IP and Development Kits

(a comprehensive listing of video and imaging application notes, white papers,

reference designs, and related IP cores)

11. Xilinx Zynq-7000 All Programmable SoC Boards and Kits page

)

)

48 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Page 49

Warranty

Send Feedback

THIS LIMITED WARRANTY applies solely to standard hardware development boards and standard

hardware programming cables manufactured by or on behalf of Xilinx (“Development Systems”). Subject

to the limitations herein, Xilinx warrants that Development Systems, when delivered by Xilinx or its

authorized distributor, for ninety (90) days following the delivery date, will be free from defects in material

and workmanship and will substantially conform to Xilinx publicly available specifications for such

products in effect at the time of delivery. This limited warranty excludes: (i) engineering samples or beta

versions of Development Systems (which are provided “AS IS” without warranty); (ii) design defects or

errors known as “errata”; (iii) Development Systems procured through unauthorized third parties; and

(iv) Development Systems that have been subject to misuse, mishandling, accident, alteration, neglect,

unauthorized repair or installation. Furthermore, this limited warranty shall not apply to the use of

covered products in an application or environment that is not within Xilinx specifications or in the event of

any act, error, neglect or default of Customer. For any breach by Xilinx of this limited warranty, the

exclusive remedy of Customer and the sole liability of Xilinx shall be, at the option of Xilinx, to replace or

repair the affected products, or to refund to Customer the price of the affected products. The availability of

replacement products is subject to product discontinuation policies at Xilinx. Customer may not return

product without first obtaining a customer return material authorization (RMA) number from Xilinx.

Appendix B

THE WARRANTIES SET FORTH HEREIN ARE EXCLUSIVE. XILINX DISCLAIMS ALL OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT

LIMITATION, ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE,

OR NON-INFRINGEMENT, AND ANY WARRANTY THAT MAY ARISE FROM COURSE OF DEALING,

COURSE OF PERFORMANCE, OR USAGE OF TRADE. (2008.10)

Do not throw Xilinx products marked with the “crossed out wheeled bin” in the trash. Directive

2002/96/EC on waste electrical and electronic equipment (WEEE) requires the separate collection of

WEEE. Your cooperation is essential in ensuring the proper management of WEEE and the protection of

the environment and human health from potential effects arising from the presence of hazardous

substances in WEEE. Return the marked products to Xilinx for proper disposal. Further information and

instructions for free-of-charge return available at: www.xilinx.com\ehs\weee.htm

.

ZC702 and ZVIK Getting Started Guide www.xilinx.com 49

UG926 (v6.0) December 17, 2013

Page 50

Appendix B: Warranty

Send Feedback

50 www.xilinx.com ZC702 and ZVIK Getting Started Guide

UG926 (v6.0) December 17, 2013

Loading...

Loading...