Page 1

0

R

XCR3384XL :

DS024 (v2.0) 2006 年 3 月 31 日

0

特長

• 低電力 3.3V で 384 個の マクロ セ ル CPLD

ピン間のロジッ ク遅延 : 7.0ns

•

最大システム周波数 : 135MHz

•

•384

•

•3.3V

•

• 高速 ISP プログ ラ ミ ング タイム

• 追加 I/O のポート イネーブル ピン

• インダスト リアル グレード電圧範囲で 2.7V 〜 3.6V

•

• セキ ュ リ ティ ビ ッ ト による不正ア クセス防止

• アーキテクチャの詳細は、『CoolRunner™ XPLA3 ファ ミ リ

個のマクロセル (9,000 個の利用可能なゲート )

小規模なフッ トプ リ ン ト パッケージ

-144 ピン TQFP (118 個のユーザー I/O)

-208

-256

-324

ピン PQFP (172 個の ユーザー I/O)

ボール FBGA (212 個のユーザー I/O)

ボール FBGA (220 個のユーザー I/O)

システム用に最適化

- 超低消費電力

- 標準スタンバイ電流 = 25℃ で 18µA

-3.3V

コア供給で 5V トレラント I/O ピン

- 高度な 0.35µ 5 層メ タル EEPROM プロセス

- Fast Zero Power™ (FZP) CMOS デザイン テクノロジ

-3.3V PCI 電気的仕様に準拠する出力 ( すべての入力

I/O に内部ク ランプ ダイオードはない )

または

高度なシステム機能

- インシステム プログ ラ ミ ング

-

入力レジス タ

- 予想可能な タ イ ミ ング モデル

- 各フ ァンクシ ョ ン ブロ ッ クに最大 23 クロック

- デザイン変更時の優れたピン固定機能

- IEEE 1149.1 バウンダリ スキ ャン (JTAG) を

完全サポー ト

-4 つの グ ロ ーバル クロック

- 各フ ァンクシ ョ ン ブロ ッ クに 8 個の P-term 制御項

各出力でスルー レートをプロ グ ラ ム可能

データシート』 (DS012) を参照

384

14

Product 製品仕様

個のマクロセル CPLD

フ ァ ミ リの概要

CoolRunner™ XPLA3 XCR3384XL デバイスは 3.3V で 384 個

のマ クロ セルを持つ

ジック ソ リ ューシ ョ ンを必要とする低電力 アプ リ ケーシ ョ ンを

ターゲッ ト とするデバイス です。

ロックでは、

延は、 最大システム周波数 135MHz で 7.0ns となります。

CPLD であ り 、 最先端のプロ グラマ ブル ロ

合計 24 個のフ ァン クション ブ

9,000 個 のゲー ト が 使用可能 です。 ピン間の伝播遅

Fast Zero Power を採用 し た TotalCMOS

デザ イン テク ノロジ

CoolRunner XPLA3 CPLD は、 プロセス テクノロジおよびデザ

テ クニッ クの両方において、 TotalCMOS™ ソリューション

イン

を提供し ます。

用するのではな く 、

ンプ リ メ ン ト し ます。 CMOS ゲー ト をこ の よ うに インプ リ メン

トすることにより、ザイ リンクスの

させるとパフォーマンスも低下するという概念を覆し、高パ

フ ォ ーマ ン ス と 低消費電力 が共に実現可能に な り ま し た。

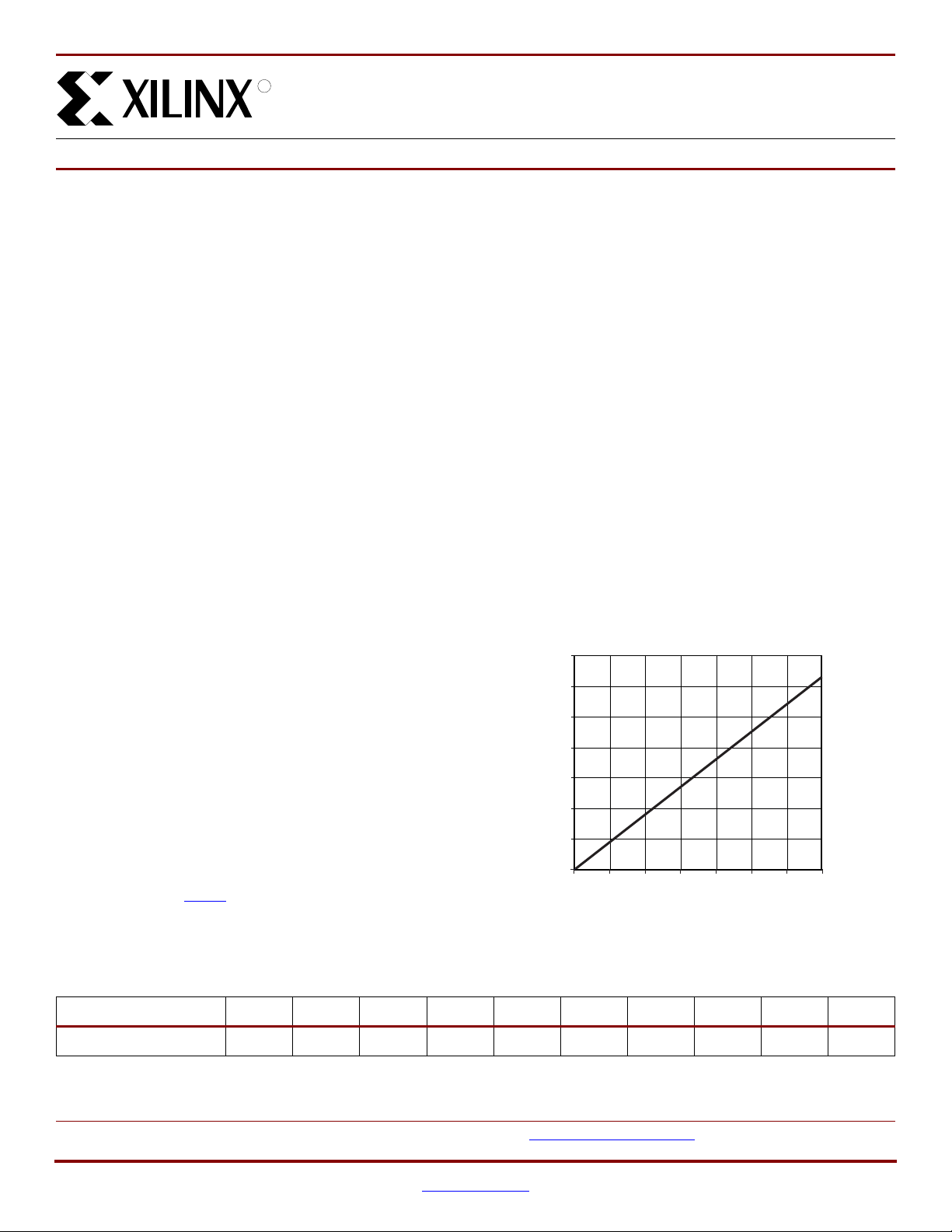

XCR3384XL TotalCMOS CPLD での周波数と ICC の関係 (3.3V

で 25℃ の場合で、 16 ビッ ト アップ/ダウン カウンタを使用した

) を示す図 1 および表 1 を参照して くだ さ い。

測定値

このフ ァ ミ リ は、 従来のよ う にセンス アンプを使

CMOS ゲート をカスケ ード接続して 積和をイ

CPLD では、消費電力を低下

280

240

200

(mA)

160

CC

120

Typical I

80

40

0

0 20 40 60 80 100 120 140

Frequency (MHz)

DS024_01_061802

図 1 : 標準的な I

表 1 : 標準的な I

周波数 (MHz)

標準的な I

© 2006 Xilinx, Inc. All rights reserved.すべての Xilinx の商標、 登録商標、 特許、 免責条項は、 http://www.xilinx.co.jp/legal.htmにリス トされています。 その他すべての

商標および登録商標は、 それ ぞれの所有者が所有し ています。 すべ ての仕様は通知なし に変更される可能性があります。

と周波数の関係 (VCC = 3.3V、 25℃)

CC

0 1 10 20 40 60 80 100 120 140

CC

(mA)

0.018 2.2 24.4 42.4 82.6 123.0 155.6 187.8 227.5 258.1

と周波数の関係 (VCC = 3.3V、 25℃)

CC

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 1

Product

製品仕様

Page 2

XCR3384XL : 384 個のマクロセル CPLD

0

0

0

0

30

0

50

60

0

80

90

00

0.51.52.5.54.5

s

)

)

)

2

R

推奨動作条件 での DC 電気特性

(1)

シンボル パラ メータ テス ト条件 標準 最小 最大 単位

(2)

V

OH

V

OL

I

IL

I

IH

I

CCSB

I

CC

(7)

最大出力電圧 V

最小出力電圧

入力漏洩電流 V

= 3.0V 〜 3.6V、IOH = -8mA

CC

= 2.7V 〜 3.0V、IOH = -8mA

V

CC

= -500µA - 90% V

I

OH

IOL = 8mA - - 0.4 V

= GND または VCC 〜 5.5V

IN

I/O が High-Z 時の漏洩電流 VIN = GND または VCC 〜 5.5V

スタンバイ電流

ダイナミ ッ ク電流

(4,5)

VCC = 3.6V 31.5 - 100 µA

f = 1MHz - - 5 mA

-2.4-V

-2.0-V

(3)

CC

--1010

--1010

-V

µA

µA

f = 50MHz - - 140 mA

C

C

C

IN

CLK

I/O

入力ピ ン キャパシタンス

ク ロ ッ ク入力キャパシタンス

I/O ピン キャパシタンス

(6)

(6)

メモ :

1. 推奨動作条件の詳細は、 『CoolRunner XPLA3 ファ ミ リ データシー ト』 (DS012) を参照し てくださ い。

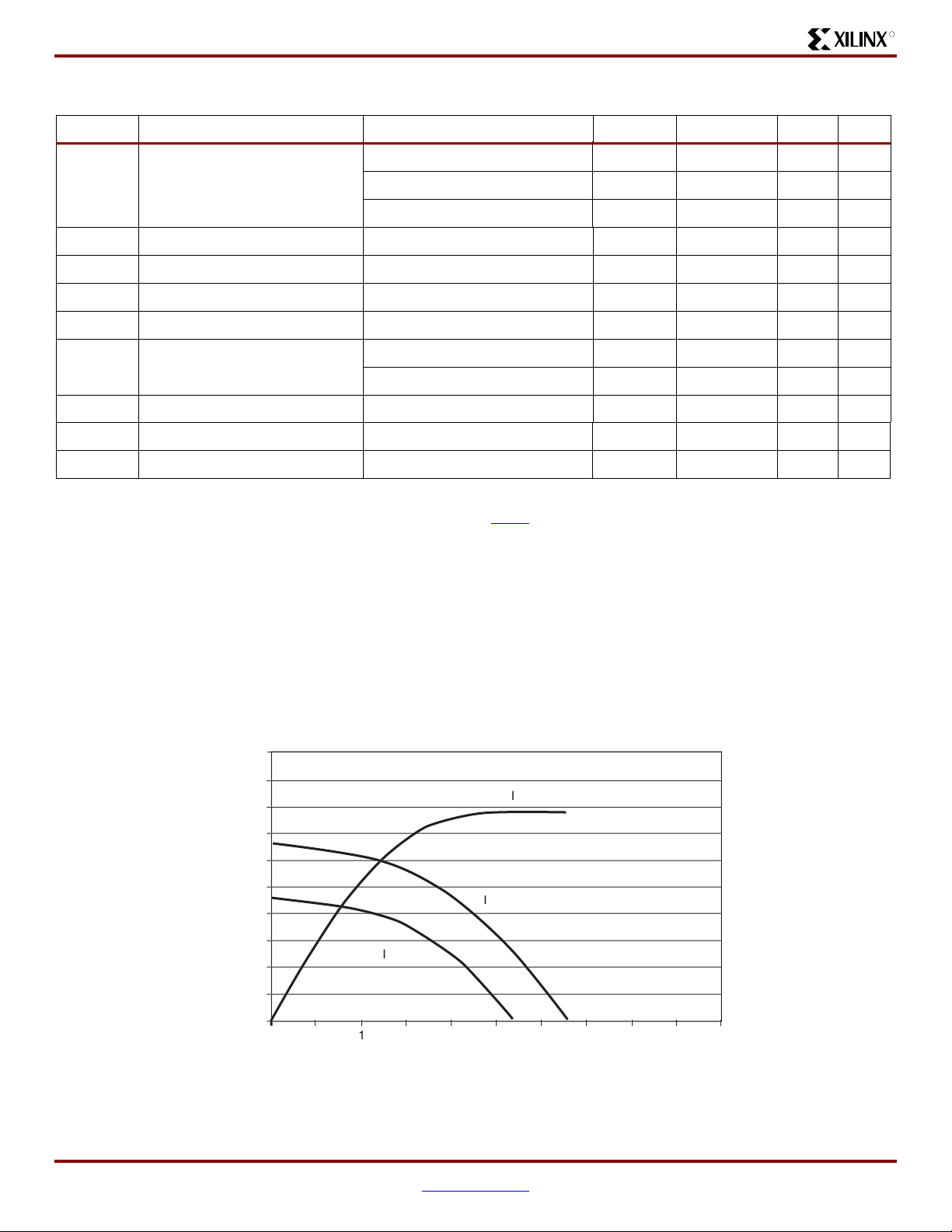

2. CoolRunner XPLA3 ファ ミ リの出力ドライブ特性は、 図 2 を参照して く だ さ い。

3. このパラ メ ータは、 テス ト によ る ものではな く 、 デザイ ンおよび特性評価によって保証されてお り ます。

4. 標準値は、 表 1 および図 1 を参照し てく ださ い。

5. このパラ メータは、 すべてのファ ンクシ ョ ン ブロ ッ クにロード された 16 ビッ トのリセット可能なアップ/ダウン カウンタで、 すべての出力を無

効および負荷がない状態で測定された ものです。

くデザインおよび特性評価に よって保証されてお り ます。

6. 標準値です (テス ト されていません)。

7. 70℃ の場合の標準値です。

f = 1MHz - - 8 pF

(6)

f = 1MHz - - 12 pF

f = 1MHz - - 10 pF

入力は、VCC またはグラ ンド に接続されています。 このパラ メータは、テス トによ るものではな

1

3.3V

L

7

3.3V

Volt

H

DS012_10_03180

4

2.7V

2

1

H

図 2 : CoolRunner XPLA3 フ ァ ミ リの標準 I/V 曲線 (25℃)

2 www.xilinx.co.jp DS024 (v2.0) 2006 年 3 月 31 日

Product 製品仕様

Page 3

R

XCR3384XL : 384 個のマクロセル CPLD

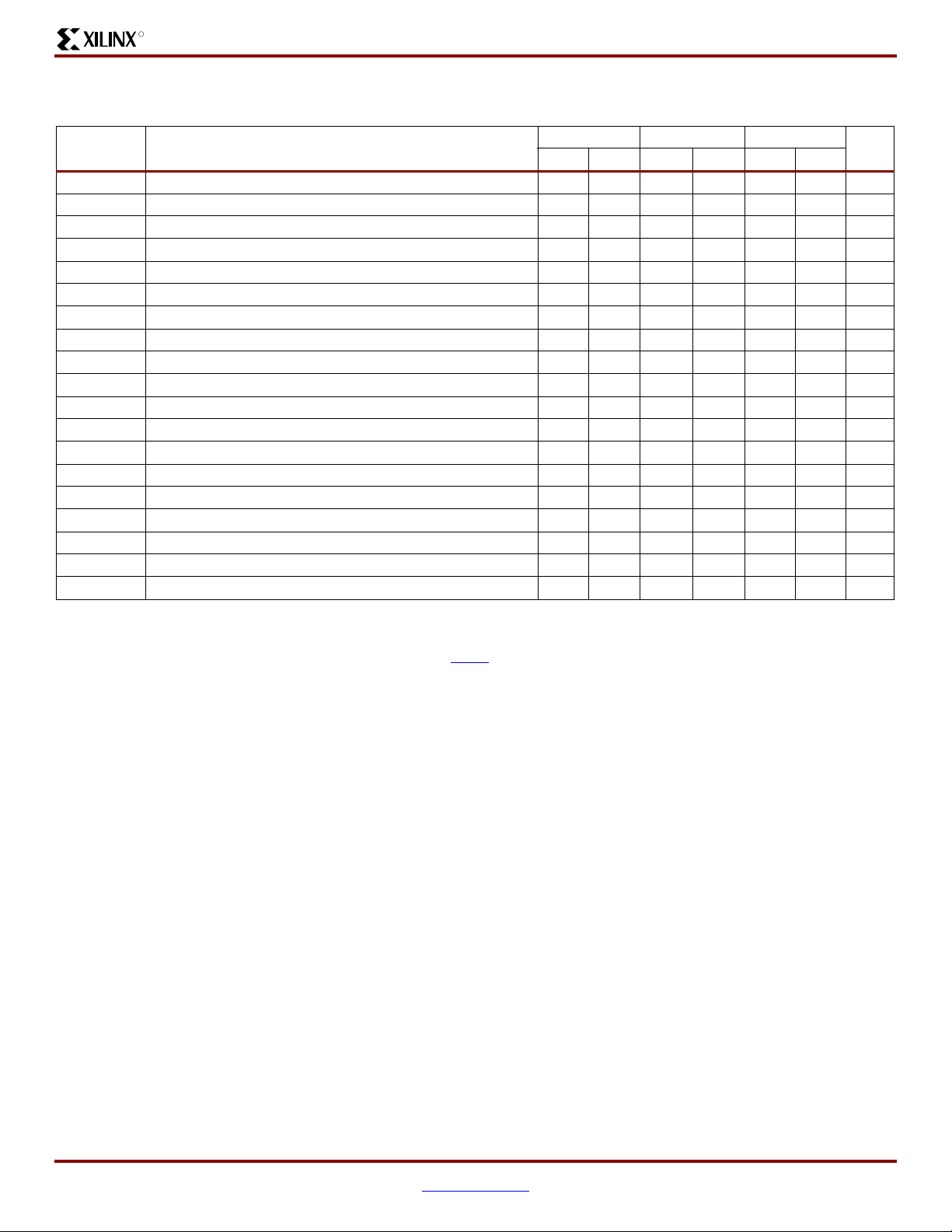

推奨動作条件 での AC 電気特性

(1、2)

-7 -10 -12

シンボル パラ メータ

T

PD1

T

PD2

T

CO

T

SUF

(4)

T

SU1

T

SU2

(4)

T

H

(4)

T

WLH

(4)

T

PLH

T

APRPW

(4)

T

R

(4)

T

L

f

SYSTEM

T

CONFIG

(4)

T

INIT

(4)

T

POE

(4)

T

POD

(4)

T

PCO

(4)

T

PAO

メモ :

1. 出力ス イ ッチング 1 回で測定した仕様です。

2.

推奨動作条件は、 『CoolRunner XPLA3 ファ ミ リ データシー ト』 (DS012) を参照し て く だ さ い。

3.

図 4 を参照し てく だ さ い。

4. これらのパラ メ ータは、 テス ト によ る ものではな くデザインおよび特性評価によ って保証されています。

5. コンフィギ ュレーシ ョ ン中に流れる標準的な電流は、 3.6V で 17mA です。

6. 出力 CL = 5 pF です。

伝播遅延時間 (シングル P-term)

伝播遅延時間 (OR アレ イ)

(3)

Clock to Out (グローバル同期ピン クロック)

セッ トアップ タイム (高速入力レジス タ)

セッ トアップ タイム (シングル P-term)

セッ トアップ タイム (OR アレ イ)

ホールド タイム

グローバル クロック パルス 幅 (High または Low)

P-term クロック パルス幅

非同期プ リ セ ッ ト / リセット パルス 幅 (High または Low)

入力立ち上が り時間

入力立ち下が り時間

(4)

最大システム周波数

(4)

コンフィ ギュレーシ ョン時間

(5)

ISP 初期化時間

P-term OE から出力が有効になるまでの時間

P-term OE から出力が無効になるまでの時間

P-term の Clock to Out

P-term のセ ッ ト/リ セッ トから有効な出力までの時間

(6)

-7.0-9.0-10.8ns

- 7.5 - 10.0 - 12.0 ns

- 4.5 - 5.8 - 6.9 ns

2.5 - 3.0 - 3.0 - ns

4.3 - 5.5 - 6.7 - ns

4.8 - 6.5 - 7.9 - ns

0-0-0-ns

3.0 - 4.0 - 5.0 - ns

4.5 - 6.0 - 7.5 - ns

4.5 - 6.0 - 7.5 - ns

-20-20-20ns

-20-20-20ns

- 135 - 102 - 83 MHz

- 200 - 200 - 200 µs

- 200 - 200 - 200 µs

- 9.0 - 11.0 - 13.0 ns

- 9.0 - 11.0 - 13.0 ns

- 8.0 - 10.3 - 12.4 ns

- 9.0 - 11.0 - 13.0 ns

単位最小 最大 最小 最大 最小 最大

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 3

Product

製品仕様

Page 4

XCR3384XL : 384 個のマクロセル CPLD

R

内部タイ ミ ング パラ メ ー タ

シンボル パラ メータ

バッ ファ遅延

T

IN

T

FIN

T

GCK

T

OUT

T

EN

内部レジスタおよび組み合わせ遅延

T

LDI

T

SUI

T

HI

T

ECSU

T

ECHO

T

COI

T

AOI

T

RAI

T

PTCK

T

LOGI1

T

LOGI2

入力バッ フ ァ遅延

高速入力バッ フ ァ遅延

グローバル クロック バッ ファ遅延

出力バッ フ ァ遅延

出力バッ フ ァ イネーブル/ディ スエーブル遅延

透過ラ ッチ遅延

レジスタ セッ ト アップ タイム

レジスタ ホールド タイム

レジスタ クロック イネーブル セッ トアップ タイム

レジスタ クロック イネーブル ホールド タイム

レジスタの Clock to Out 遅延

レジスタの非同期 S/R to Out 遅延

レジスタの非同期リ カバ リ時間

積項ク ロ ッ ク遅延

内部ロジッ ク遅延 (シン グル P-term)

内部ロジッ ク遅延 (PLA OR term)

(1、2)

-7 -10 -12

単位最小 最大 最小 最大 最小 最大

- 2.5 - 3.3 - 4.0 ns

- 2.7 - 3.3 - 3.3 ns

- 1.0 - 1.3 - 1.5 ns

- 2.5 - 3.2 - 3.8 ns

- 4.5 - 5.2 - 6.0 ns

- 1.3 - 1.6 - 2.0 ns

0.8 - 1.0 - 1.2 - ns

0.3 - 0.5 - 0.7 - ns

2.0 - 2.5 - 3.0 - ns

3.0 - 4.5 - 5.5 - ns

- 1.0 - 1.3 - 1.6 ns

- 2.0 - 2.0 - 2.2 ns

- 5.0 - 7.0 - 8.0 ns

- 2.0 - 2.5 - 3.0 ns

- 2.0 - 2.5 - 3.0 ns

- 2.5 - 3.5 - 4.2 ns

フィードバック遅延

T

F

追加遅延

T

LOGI3

T

UDA

T

SLEW

メモ :

1. これらのパラ メ ータは、 テス ト によ る ものではな くデザインおよび特性評価によ って保証されています。

2. タイミング モデルは、 『CoolRunner XPLA3 ファ ミ リ データ シー ト』 (DS012) を参照し て く だ さ い。

ZIA 遅延

NAND のフ ォール ドバ ッ ク遅延

ユニバーサル遅延

スルー レー ト 制限遅延

- 3.1 - 4.0 - 5.0 ns

- 2.0 - 2.5 - 3.0 ns

- 2.2 - 2.8 - 3.5 ns

- 4.0 - 5.0 - 6.0 ns

4 www.xilinx.co.jp DS024 (v2.0) 2006 年 3 月 31 日

Product 製品仕様

Page 5

R

スイッチ特性

V

IN

R2

S2

S1

XCR3384XL : 384 個のマクロセル CPLD

V

CC

Component Values

R1 390Ω

R1

C1

V

OUT

Note: For T

output level of V

R2 390Ω

C1 35 pF

Measurement S1 S2

T

POE

T

POE

(High)

(Low)

T

P

, C1 = 5 pF. Delay measured at

POD

+ 300 mV, VOH – 300 mV.

OL

Open Closed

Closed Open

Closed

Closed

DS023_03_102401

図 3 : AC 負荷回路

7.2

7.1

7.0

6.9

6.8

6.7

6.6

(ns)

6.5

6.4

6.3

6.2

6.1

6.0

124816

Number of Adjacent Outputs Switching

3.3V, 25°C

DS024_04_061802

図 4 : T

の軽減曲線

PD2

+3.0V

90%

0V

T

R

T

L

1.5 ns 1.5 ns

Measurements:

All circuit delays are measured at the +1.5V level of

inputs and outputs, unless otherwise specified.

DS017_05_042800

図 5 : 電圧波形

10%

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 5

Product

製品仕様

Page 6

XCR3384XL : 384 個のマクロセル CPLD

R

ピンについて

表 2 : XCR3384XL ユーザー I/O ピン

TQ144

ユーザー I/O

ピンの総数

メモ :

1. XCR3384XL TQ144 JTAG ピンは、 TQ144 パッケージのその他の

CoolRunner XPLA3 ファミ リ デバイスと は互換性はあ り ま せ ん 。

表 3 : XCR3384XL I/O ピン

ファン

クシ ョン

ブロッ ク

マクロ

セル

1 1 94 - E15 G22

12- -F13H20

13-13E16H21

14-15F14J19

1 5 93 16 F15 J21

16- --17- --18- --19- --110- - - 111- - - 112- - - 1139217G12J22

1 14 - 18 G15 K19

1 15 - 19 G13 K21

1169120F16K22

21-12E14G21

2 2 96 11 D16 G19

2 3 97 10 F12 F22

24989C16F21

2 5 99 8 E13 F20

26- --27- --28- --29- --210- - - 211- - - 212- - - 213100-D15E22

2141017D14E21

2 15 102 6 B16 F19

2 16 103 - C15 E20

31-21G14L19

32-22G16L20

(1)

PQ208 FT256 FG324

118 172 212 220

TQ144

(1)

PQ208 FT256 FG324

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

33- -H13L21

3490--M20

3 5 89 24 H12 M19

36- --37- --38- --39- --310- - - 311- - - 312- - - 3 13 - 25 H15 M22

3148826H14N22

315-27H16N21

3168728J14N19

4 1 104 4 A16 D22

421063E12C22

43107--B21

44110-C14B20

4 5 111 207 D13 C19

46- --47- --48- --49- --410- - - 411- - - 412- - - 4 13 112 206 A15 B19

4 14 113 205 B15 A20

4 15 114 204 B14 C18

4 16 116 203 C13 B18

51-29J15P22

5286

(1,2)

30

(2)

J13

(2)

P20

53-31J16P19

54- -L14R22

5 5 84 - K15 R21

56- --57- --58- --59- --510- - - 511- - - 512- - - 5 13 - 33 K14 R20

5148334K16T22

5158235K13T21

(2)

6 www.xilinx.co.jp DS024 (v2.0) 2006 年 3 月 31 日

Product 製品仕様

Page 7

R

XCR3384XL : 384 個のマクロセル CPLD

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

5168136L15T20

6 1 67 62 R13 AA16

62-61M11Y16

63-60T14W16

6 4 - 59 N12 AB17

6 5 - 58 R14 AA17

66- --67- --68- --69- --610- - - 611- - - 612- - - 613-57P13AB18

6 14 - 56 T15 AA18

61568-P14W17

6 16 69 - T16 AA19

7 1 80 37 K12 T19

7 2 79 38 L16 U22

7 3 78 39 M15 U21

7 4 77 40 N15 U20

75- -L13V22

76- --77- --78- --79- --710- - - 711- - - 712- - - 713- -M16U19

7 14 - 42 M14 V21

7157543N16V20

7 16 - 44 L12 W22

8 1 70 55 M12 Y18

8 2 71 51 R15 AA20

8 3 72 - N13 Y19

8 4 - - - AA21

85-49P16Y20

86- --87- --88- --89- --810- - - 811- - - 812- - - -

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

813-48N14Y21

8 14 - 47 R16 W20

8 15 - 46 M13 W21

8167445P15Y22

91122187D9C13

9 2 - 188 A9 D13

93121

(1,2)

189

(2)

C10

(2)

B14

9 4 - 190 A10 C14

9 5 120 - D10 D14

96- --97- --98- --99- --910- - - 911- - - 912- - - 913- -B11A15

914-192C11B15

915-193B12C15

9 16 - 194 E10 A16

10 1 - 178B8B11

10 2 - 177 D8 C11

10 3 131

(1,2)

176

(2)

A7

(2)

D11

10 4 132 175 C8 A10

10 5 - - - B10

10 6 - - - 10 7 - - - 10 8 - - - 10 9 - - - 10 10 - - - 10 11 - - - 10 12 - - 10 13 - - C7 C10

10 14 - 173 B7 D10

10 15 133 172 D7 A9

10 16 134 171 A6 B9

11 1 - - A14 A19

11 2 - 202 E11 D17

11 3 - 201 A13 A18

11 4 - - D12 C17

11 5 117 199 B13 B17

11 6 - - - 11 7 - - - 11 8 - - - 11 9 - - - -

(2)

(2)

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 7

Product

製品仕様

Page 8

XCR3384XL : 384 個のマクロセル CPLD

R

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

11 10 - - - 11 11 - - - 11 12 - - - 11 13 - 198 C12 A17

11 14 - 197 A12 D16

11 15 118 196 D11 C16

11 16 119 195 A11 B16

12 1 139 163 E6 D7

12 2 - 164 A4 C7

12 3 138 - C5 B7

12 4 137 - B5 A7

12 5 - 166 D6 C8

12 6 - - - 12 7 - - - 12 8 - - - 12 9 - - - 12 10 - - - 12 11 - - - 12 12 - - - 12 13 136 167 A5 B8

12 14 - 168 C6 A8

12 15 - 169 B6 D9

12 16 - 170 E7 C9

13 1 61 70 N10 W13

13 2 - 69 P11 AB14

13 3 62 68 M10 AA14

13 4 63 67 R11 Y14

13 5 - 66 T12 W14

13 6 - - - 13 7 - - - 13 8 - - - 13 9 - - - 13 10 - - - 13 11 - - - 13 12 - - - 13 13 - 65 R12 AB15

13 14 65 64 N11 AA15

13 15 - - T13 Y15

13 16 66 - P12 AB16

14 1 - 91 R6 AA8

14 2 47 92 M7 Y8

14 3 46 93 T5 AB7

14 4 - - T6 AA7

14 5 - - R5 Y7

14 6 - - - -

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

14 7 - - - 14 8 - - - 14 9 - - - 14 10 - - - 14 11 - - - 14 12 - - - 14 13 45 95 N6 W7

14 14 44 96 T4 AB6

14 15 - 97 P5 AA6

14 16 43 98 R4 Y6

15 1 - - T11 Y13

15 2 - - - AA13

15 3 60 71 R10 AB13

15 4 - 73 P10 W12

15 5 56 76 T10 AA12

15 6 - - - 15 7 - - - 15 8 - - - 15 9 - - - 15 10 - - - 15 11 - - - 15 12 - - - 15 13 55 77 N9 AB12

15 14 - 78 R9 Y11

15 15 - 79 P9 AA11

15 16 54 80 T9 W11

16 1 - 90 N7 AB8

16 2 48 89 T7 W9

16 3 - 88 P6 Y9

16 4 49 87 R7 AA9

16 5 - 86 P7 AB9

16 6 - - - 16 7 - - - 16 8 - - - 16 9 - - - 16 10 - - - 16 11 - - - 16 12 - - - 16 13 - - T8 W10

16 14 - - N8 Y10

16 15 - 84 R8 AA10

16 16 53 81 P8 AB11

17 1 - 147 E4 E2

17 2 - 148 D1 F3

17 3 6 149 F5 F4

8 www.xilinx.co.jp DS024 (v2.0) 2006 年 3 月 31 日

Product 製品仕様

Page 9

R

XCR3384XL : 384 個のマクロセル CPLD

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

17 4 5 150 C2 D1

17 5 4 151 D3 D2

17 6 - - - 17 7 - - - 17 8 - - - 17 9 - - - 17 10 - - - 17 11 - - - 17 12 - - - 17 13 - - C1 E3

17 14 - - - C2

17 15 2 153 B1 B2

17 16 1 154 B2 D3

18 1 7 146 D2 E1

18 2 8 145 E3 F2

18 3 9 144 E1 G4

18 4 10 - F4 G3

18 5 - - F1 G2

18 6 - - - 18 7 - - - 18 8 - - - 18 9 - - - 18 10 - - - 18 11 - - - 18 12 - - - 18 13 - 142 G5 H3

18 14 - 141 E2 H2

18 15 11 140 F3 H1

18 16 12 139 F2 J4

19 1 - 155 C3 C4

19 2 143 156 D4 B4

19 3 - - A2 C5

19 4 142 - A1 B5

19 5 141 158 B3 A4

19 6 - - - 19 7 - - - 19 8 - - - 19 9 - - - 19 10 - - - 19 11 - - - 19 12 - - - 19 13 - 159 C4 D6

19 14 - 160 A3 A5

19 15 140 161 D5 C6

19 16 - 162 B4 B6

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

20 1 14 138 G4 J3

20 2 - 137 G1 J2

20 3 - 136 G3 K4

20 4 15 135 H1 K3

20 5 - - H4 K2

20 6 - - - 20 7 - - - 20 8 - - - 20 9 - - - 20 10 - - - 20 11 - - - 20 12 - - - 20 13 - - G2 K1

20 14 16 133 H3 L4

20 15 - 132 J1 L3

20 16 18 131 J3 L2

21 1 - 99 M6 AB5

21 2 - 100 T3 W6

21 3 42 101 N5 AB4

21 4 41 102 R3 AA5

21 5 - 103 P4 Y5

21 6 - - - 21 7 - - - 21 8 - - - 21 9 - - - 21 10 - - - 21 11 - - - 21 12 - - - 21 13 40 104 T2 AA4

21 14 39 - - AB3

21 15 38 - R2 Y4

21 16 37 106 N4 AA3

22 1 19 - H2 M2

22 2 - 130 J5 M3

22 3 20 129 J2 M4

22 4 21 128 J4 N1

22 5 22

(1,2)

127

(2)

K1

(2)

22 6 - - - 22 7 - - - 22 8 - - - 22 9 - - - 22 10 - - - 22 11 - - - 22 12 - - - 22 13 23 126 K3 N3

N2

(2)

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 9

Product

製品仕様

Page 10

XCR3384XL : 384 個のマクロセル CPLD

表 3 : XCR3384XL I/O ピン (続き)

ファン

クシ ョン

ブロッ ク

マクロ

セル

TQ144

(1)

PQ208 FT256 FG324

22 14 - - - N4

22 15 - 124 K2 P1

22 16 25 123 L1 P2

23 1 36 108 M5 AA2

23 2 - 109 P2 Y3

23 3 - 1 10 P3 Y2

23 4 - 111 T1 W3

23 5 - - N3 W2

23 6 - - - 23 7 - - - 23 8 - - - 23 9 - - - 23 10 - - - 23 11 - - - 23 12 - - - 23 13 - - R1 W1

23 14 35 112 M4 V3

23 15 - 113 P1 U4

23 16 - 114 L5 V2

24 1 26 122 K4 P3

24 2 27 121 L3 P4

24 3 28 120 K5 R1

24 4 29 119 M1 R2

24 5 30 - L2 R3

24 6 - - - 24 7 - - - 24 8 - - - 24 9 - - - 24 10 - - - 24 11 - - - 24 12 - - - 24 13 31 118 M2 T2

24 14 32 117 L4 T3

24 15 - - M3 U2

24 16 34 115 N2 U3

メモ :

1. XCR3384XL TQ144 JTAG ピンは、 TQ144 パッケージのその他の

CoolRunner XPLA3 ファミ リ デバ イ ス とは互換性はあ り ません。

2. JTAG ピンです。

R

10 www.xilinx.co.jp DS024 (v2.0) 2006 年 3 月 31 日

Product 製品仕様

Page 11

R

表 4 : XCR3384XL グローバル、 JTAG、ポート イネーブル、 電源、 未接続ピン

ピン

タイプ

TQ144

(1)

PQ208 FT256 FG324

XCR3384XL : 384 個のマクロセル CPLD

IN0 / CLK0 128 181 B9 C12

IN1 / CLK1

IN2 / CLK2

IN3 / CLK3

TCK

TDI

TDO

TMS

PORT_EN

V

CC

24、 50、 51、 58、 73、 76、

95、 115、 123、 130、 144

127 182 A8 B12

126 183 C9 D12

125 184 B10 A12

(1)

86

131

121

22

33

(1)

(2)

(1)

(1)

、 23、 41、 63、 74、 83、

5

30 J13 P20

176 A7 D11

189 C10 B14

127 K1 N2

(2)

116

85、 107、 125,143、 165、

179、 186、 191

GND

未接続 108、 109 1、 2、 52、 53、 54、 105、

3、 13、 17、 52、 57、 59、

64、 85、 105、 124、 129、

135、

14、 32、 50、 72、 75、 82、

94、 134、 152、 174、 180、

185、 200

157、 208

(2)

N1

、 E9、 F7、 F8、 F9、

E8

F10、 G6、 G11、 H5、 H6、

H11、 J6、 J11、 J12、 K6、

K11、 L7、 L8、 L9、 L10、

M8、 M9

、 F6、 F11、 G7、 G8、

E5

G9、 G10、 H7、 H8、 H9、

H10、 J7、 J8、 J9、 J10、

K7、 K8、 K9、 K10、 L6、

L11

-

(2)

T4

、 A13、 D8、 D15、

A11

H4、 H19、 J10、 J11、 J12、

J13、 K9、 K14、 L9、 L14、

M1、 M9、 M14、 N9、

N14、 N20、 P10、 P11、

P12、 P13、 R4、 R19、

W8、 W15、 Y12、 AB10

D4

、 D5、 D18、 D19、 E4、

E19、 J9、 J14、 K10、

K11、 K12、 K13、 L10、

L11、 L12、 L13、 M10、

M11、 M12、 M13、 N10、

N11、 N12、 N13、 P9、

P14、 V4、 V19、 W4、

W5、 W18、 W19

、 A2、 A3、 A6、 A14、

A1

A21、 A22、 B1、 B3、

B13、 B22、 C1、 C3、

C20、 C21、 D20、 D21、

F1、 G1、 G20、 H22、 J1、

J20、 K20、 L1、 L22、

M21、 P21、 T1、 U1、 V1、

Y1、 Y17、 AA1、 AA22、

AB1、 AB2、 AB19、

AB20、 AB21、 AB22

メモ :

1. XCR3384XL TQ144 JTAG ピンは、 TQ144 パッ ケージのその他の CoolRunner XPLA3 ファミ リ デバイス と は互換性はあ り ま せ ん 。

2. JTAG ピンが I/O と し て使用される場合、 ポー ト イネーブルを High にし て JTAG ピン を有効に します。 詳細は、 デバイ ス ファミ リのデータシー

ト

(DS012) を参照 し てく ださ い。

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 11

Product

製品仕様

Page 12

XCR3384XL : 384 個のマクロセル CPLD

デバイスのマークおよび注文情報

R

R

Device Type

Package

Speed

Operating Range

1

Sample package with part marking.

デバイス番号および

パッケージ番号

スピード

(ピン間遅延)

パッケージ

シンボル ピ ン数 パッケージ タ イプ 動作範囲

XCR3384XL-7TQ144C 7.5ns TQ144

XCR3384XL-7TQG144C 7.5ns TQG144

XCR3384XL-7PQ208C 7.5ns PQ208

XCR3384XL-7PQG208C 7.5ns PQG208

XCR3384XL-7FT256C 7.5ns FT256

XCR3384XL-7FTG256C 7.5ns FTG256

XCR3384XL-7FG324C 7.5ns FG324

XCR3384XL-10TQ144C 10ns TQ144

XCR3384XL-10TQG144C 10ns TQG144

XCR3384XL-10PQ208C 10ns PQ208

XCR3384XL-10PQG208C 10ns PQG208

XCR3384XL-10FT256C 10ns FT256

XCR3384XL-10FTG256C 10ns FTG256

XCR3384XL-10FG324C 10ns FG324

XCR3384XL-10TQ144I 10ns TQ144

XCR3384XL-10TQG144I 10ns TQG144

XCR3384XL-10PQ208I 10ns PQ208

XCR3384XL-10PQG208I 10ns PQG208

XCR3384XL-10FT256I 10ns FT256

XCR3384XL-10FTG256I 10ns FTG256

XCR3384XL-10FG324I 10ns FG324

XCR3384XL-12TQ144C 12ns TQ144

XCR3384XL-12TQG144C 12ns TQG144

XCR3384XL-12PQ208C 12ns PQ208

XCR3384XL-12PQG208C 12ns PQG208

XCR3384XL-12FT256C 12ns FT256

XCR3384XL-12FTG256C 12ns FTG256

XCR3384XL-12FG324C 12ns FG324

XCR3384XL-12TQ144I 12ns TQ144

XCR3384XL-12TQG144I 12ns TQG144

XCR3384XL-12PQ208I 12ns PQ208

XCRxxxxXL

TQ144

7C

144

ピン

ピン Thin Quad Flat Pack (TQFP)、鉛フリー

144

208

ピン

208

ピン Plastic Quad Flat Pack (PQFP)、鉛フリー

ボール

256

256

ボール Fine-Pitch BGA (FT)、鉛フリー

324

ボール

ピン

144

144

ピン Thin Quad Flat Pack (TQFP)、鉛フリー

208

ピン

ピン Plastic Quad Flat Pack (PQFP)、鉛フリー

208

256

ボール

256

ボール Fine-Pitch BGA (FT)、鉛フリー

ボール

324

144

ピン

144

ピン Thin Quad Flat Pack (TQFP)、鉛フリー

ピン

208

208

ピン Plastic Quad Flat Pack (PQFP)、鉛フリー

256

ボール

256

ボール Fine-Pitch BGA (FT)、鉛フリー

324

ボール

ピン

144

144

ピン Thin Quad Flat Pack (TQFP)、鉛フリー

208

ピン

ピン Plastic Quad Flat Pack (PQFP)、鉛フリー

208

256

ボール

256

ボール Fine-Pitch BGA (FT)、鉛フリー

324

ボール

144

ピン

144

ピン Thin Quad Flat Pack (TQFP)、鉛フリー

ピン

208

This line not

related to device

part number

(1)

Thin Quad Flat Pack (TQFP) C

C

Plastic Quad Flat Pack (PQFP) C

C

Fine-Pitch BGA (FT) C

C

Fineline BGA Package (FG) C

Thin Quad Flat Pack (TQFP) C

C

Plastic Quad Flat Pack (PQFP) C

C

Fine-Pitch BGA (FT) C

C

Fineline BGA Package (FG) C

Thin Quad Flat Pack (TQFP) I

I

Plastic Quad Flat Pack (PQFP) I

I

Fine-Pitch BGA (FT) I

I

Fineline BGA Package (FG) I

Thin Quad Flat Pack (TQFP) C

C

Plastic Quad Flat Pack (PQFP) C

C

Fine-Pitch BGA (FT) C

C

Fineline BGA Package (FG) C

Thin Quad Flat Pack (TQFP) I

I

Plastic Quad Flat Pack (PQFP) I

12 www.xilinx.co.jp DS024 (v2.0) 2006 年 3 月 31 日

Product 製品仕様

Page 13

R

XCR3384XL : 384 個のマクロセル CPLD

デバイス番号および

パッケージ番号

XCR3384XL-12PQG208I 12ns PQG208

XCR3384XL-12FT256I 12ns FT256

XCR3384XL-12FTG256I 12ns FTG256

XCR3384XL-12FG324I 12ns FG324

メモ :

3. C = コマーシャル : TA = 0℃ ~ +70℃、 I = インダス ト リアル : TA = -40 ~ +85℃

スピード

(ピン間遅延)

パッケージ

シンボル ピ ン数 パッケージ タ イプ 動作範囲

208

ピン Plastic Quad Flat Pack (PQFP)、鉛フリー

ボール

256

256

ボール Fine-Pitch BGA (FT)、鉛フリー

324

ボール

Fine-Pitch BGA (FT) I

Fineline BGA Package (FG) I

I

I

保証免責条項

これらの製品は、 http://www.xilinx.co.jp/warranty.htm に記載する XILINX (以下 「ザイ リ ンクス」 とする) 限定保証に従 う もの と し ま

す。 当限定保証では、 該当時点での該当製品ザイ リ ン ク スデータシー ト に記載されている以外のアプ リ ケーシ ョ ンまたは環境での使用

については保証いたしません。 更に製品はフ ェ イルセーフ設計されたものではな く、身体的危害また

プ リ ケーシ ョ ンでの使用に対して、 ザイ リ ンクスは一切の保証責任を負いません。 かかる アプ リ ケーシ ョ ンでの使用は、 適応される法

律および規制に従い、 使用する側が一切の責任を負う ものと し ます。

は人命損失などの危険性のあるア

参考文献

CoolRunner XPLA3 デバイ ス関連資料

『パッ ケージ仕様』

『デバイ ス パッ ケージ ユーザー ガイ ド』

改訂履歴

次の表に、 この文書の改訂履歴を示します。

(1)

日付 バージ ョ ン 改訂内容

2001/02/08 1.0

2001/04/11 1.1

2001/04/19 1.2

2001/08/10 1.3

200/01/08 1.4

2003/01/06 1.5

2003/07/15 1.6

2003/08/21 1.7

2004/02/13 1.8

2005/04/08 1.9

初版リ リ ース

UMC

特性評価データを満たすため、 TSUF 仕様を変更。 標準的な I/V 曲線を追加 (図 2)。 表 2 の

ユーザー

ケージ情報の追加

標準的な I/V 曲線の変更 (図 2) 。電圧レベルの追加

AE

ソフトウェア タイ ミ ン グを満たすた め、 T

プ

変更。

より近くなるよう変更し、

Preliminary

10mA

I

IL

パッケージ デバイ スのピン 1 を示すマーキン グの変更

はんだ付け温度仕様の追加 とアプリ ケーシ ョ ン ノ ート、 データシー ト 、 およびパッ ケージへの リ ン

クの追加

標準 I

追加

I/O ピンの総数を変更し、 VOH 仕様を変更。 324 Ball Fineline BGA のピン配置 とパ ッ

電気特性の変更、 内部タイ ミ ング パラ メータ、 TQ144 パッケージおよびピン配置の追加

タイム (T

および I

SU1

T

仕様と T

INIT

へ移行。 各特性評価の AC および DC 仕様の変更。 AC 特性の メ モ 5 を変更 : 3.6V で

を 13mA へ変更。 T

のテ ス ト条件の変更

IH

および T

CCSB

) を追加し 、 OR アレ イ を通過するセ ッ ト ア ップ タイムのシンボル TSU を T

CONFIG

APRPW

仕様の変更。 T

T

遅延値のメモを追加。 ピン 34 と 35 の TQ144 ピ ン配置を変更

POD

の変更 (T

PCO

仕様の追加。 T

SUF

HI

PTCK

SOL

仕様を変更。 AC 特性表にシングル積項セ ッ ト アッ

SU2

仕様の修正。 AC 負荷回路図を実際のテス ト 条件に

の追加)。 注文情報のフォーマッ ト変更

仕様の削除。 鉛フ リー パッケージについてのメモを

に

2006/03/31 2.0

保証免責条項の追加。 鉛フ リー パッ ケージの注文情報の追加

DS024 (v2.0) 2006 年 3 月 31 日 www.xilinx.co.jp 13

Product

製品仕様

Loading...

Loading...