XILINX XCCACEM64BG388I, XCCACEM32BG388I, XCCACEM16BG388I Datasheet

DS087 (v1.0) September 25, 2001 www.xilinx.com 1

Advance Product Specification 1-800-255-7778

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademar ks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change with ou t not ice.

Summary of Features

• System level, high capacity, pre-configured solution for

Virtex and Spartan FPGAs

• Industry standard Flash memory die combined with

Xilinx controller technology in a single package

• Effortless density migration:

- XCCACEM16-BG388I (16 Megabit (Mb))

- XCCACEM32-BG388I (32 Mb)

- XCCACEM64-BG388I (64 Mb)

• All densities are available in the 388-pin Ball Grid Array

package

• VCC I/O: 1.8V, 2.5V, and 3.3V

• Configuration rates up to 152 Mb per second (Mb/s)

• Flexible configuration solution:

- SelectMAP (control up to four FPGAs)

-Slave-Serial

- Concurrent Slave-Serial (up to eight separate

chains)

• Patented compression technology (up to

2x compression)

• JTAG interface allows:

- Access to the standard Flash memory

- Boundary Scan testing

• Native interface to the standard Flash memory is

provided for:

- External parallel programming

- Processor access to unused Flash memory

locations

• Supports up to eight separate design sets (selectable

by mode pins or via JTAG), enabling systems to

reconfigure FPGAs for different functions

• Compatible with IEEE Standard 1532

• User-friendly software to format and program the

bitstreams into the standard Flash via the patented

Flash programming engine

• Internet Reconfigurable Logic (IRL) upgradable system

Description

The System ACE™ Multi-Package Module (MPM) solution

addresses the need for a space-efficient, pre-engineered,

high-density configuration solution in multiple FPGA systems. The System ACE technology is a ground-breaking

in-system programmable configuration solution that provides substantial savings in dev elopment eff ort and cost per

bit over traditional PROM and embedded solutions for high

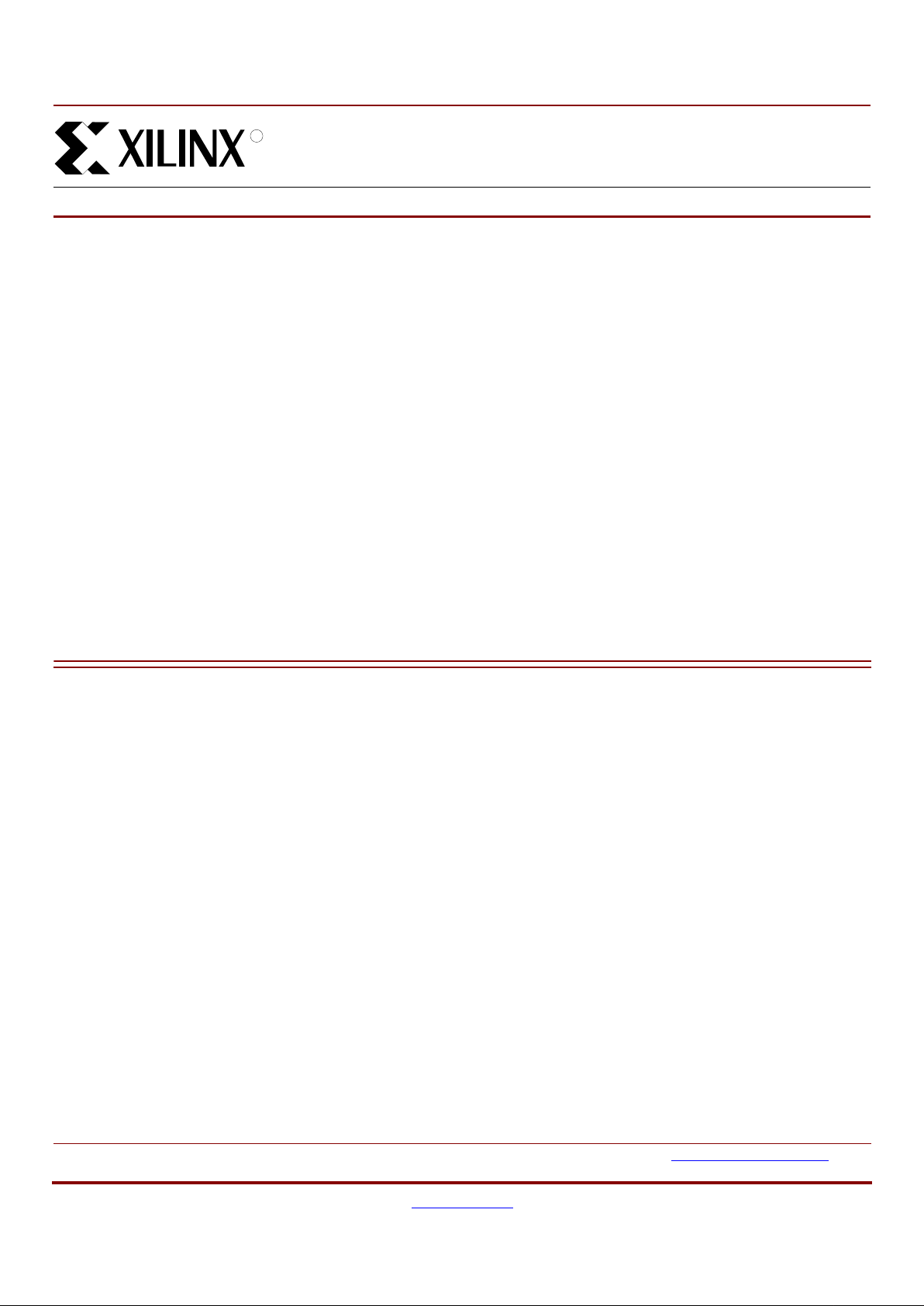

capacity FPGA systems. As shown in Figure 1, the System

ACE MPM solution is a multi-package module that includes

the System ACE MPM controller, a configuration PROM,

and an AMD Flash Memory.

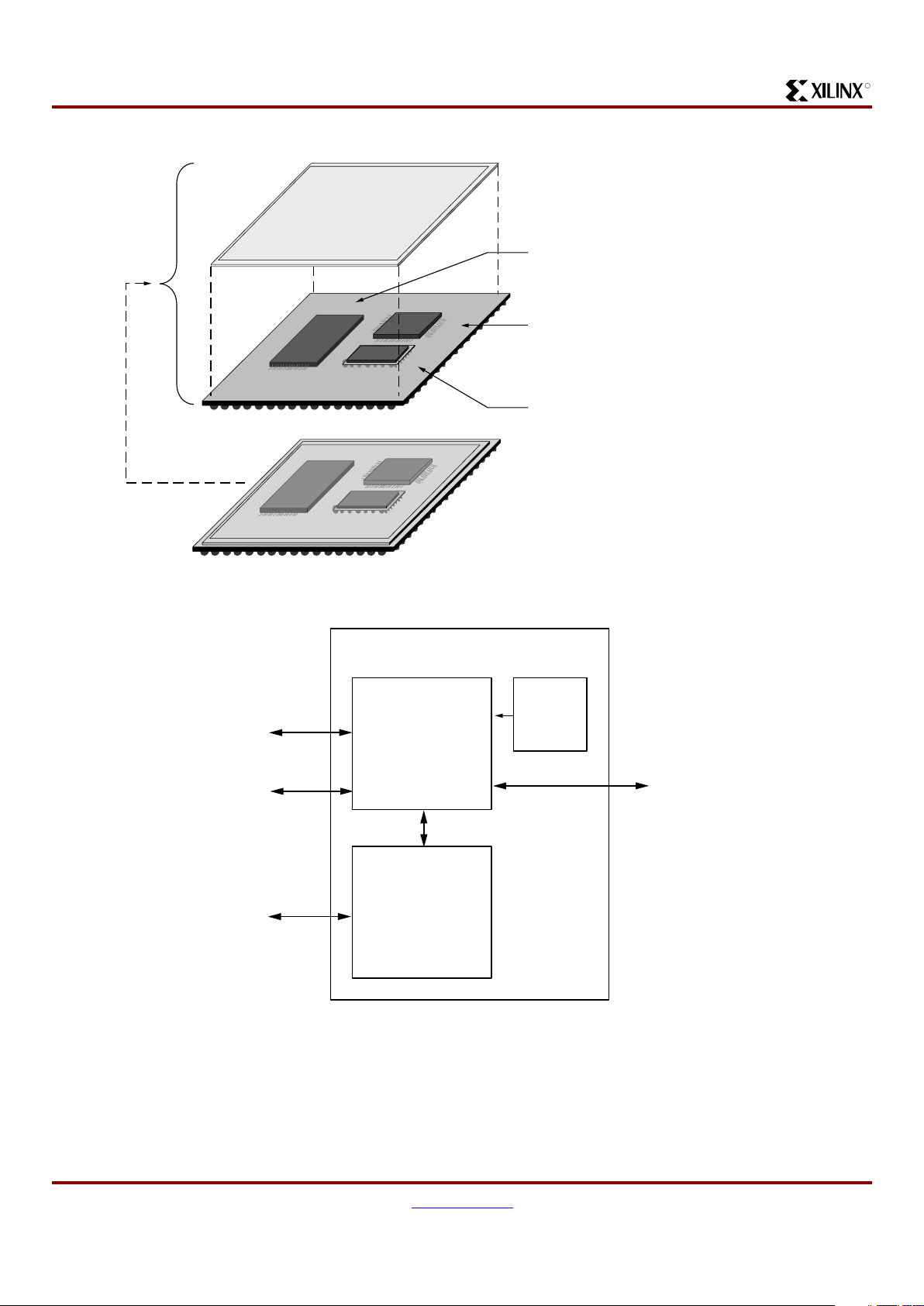

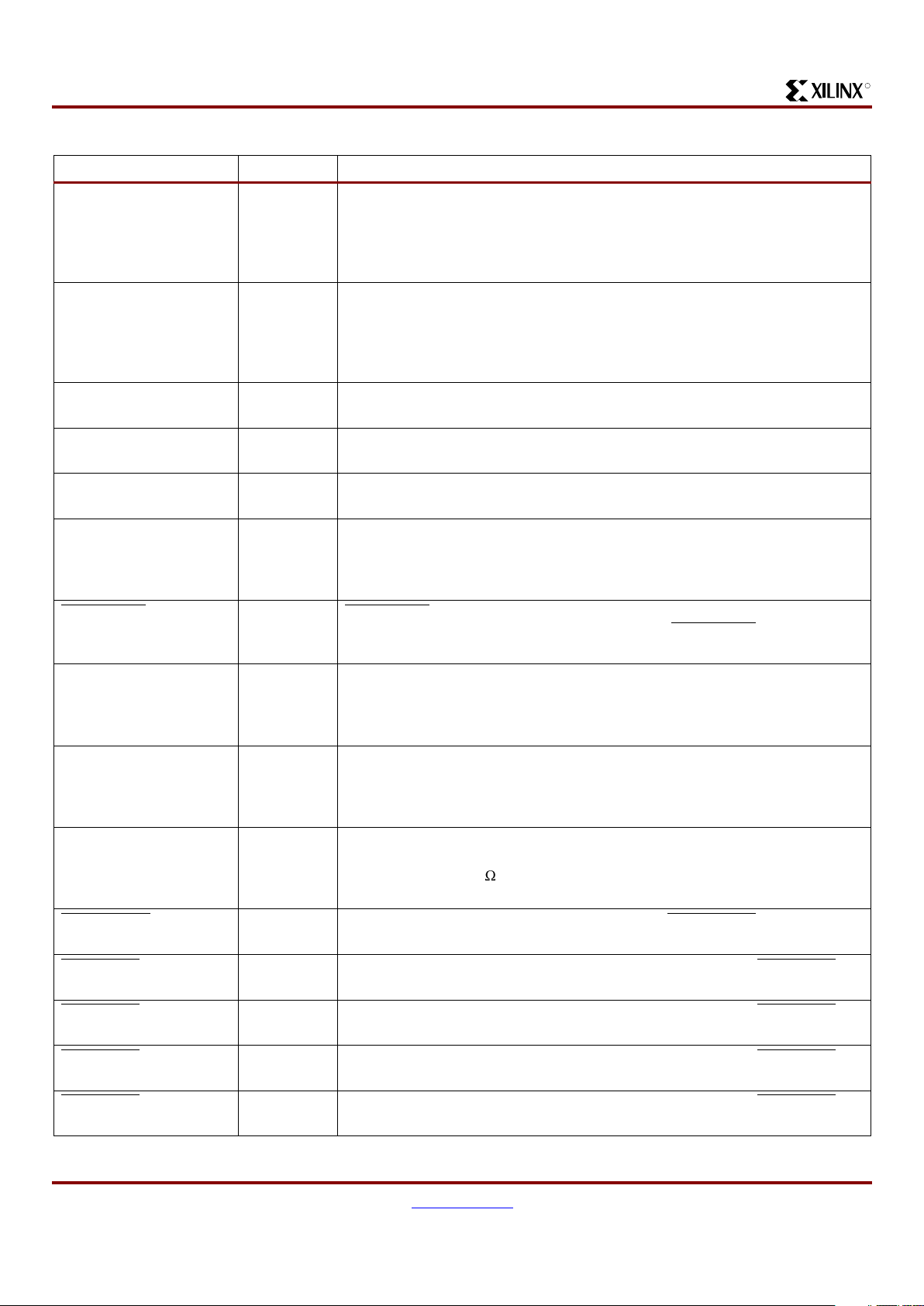

The System ACE MPM has four major interfaces. (See

Figure 2.) The boundary scan JT A G interface is prov ided for

boundary scan test and boundary-scan-based Flash memory programming. The system control interface provides an

input for the system clock, design set selection pins, system

configuration control signals, and system configuration status signals.

The native Flash memory interface provides direct read and

write access to the Flash memory unit. The target FPGA

interface provides the signals to configure target FPGAs via

the Slave-Serial, concurrent Slave-Serial, or SelectMAP

configuration modes.

Separate power pins provide voltage compatibility control

for the target FPGA configuration interfac e and for the system control/status interface.

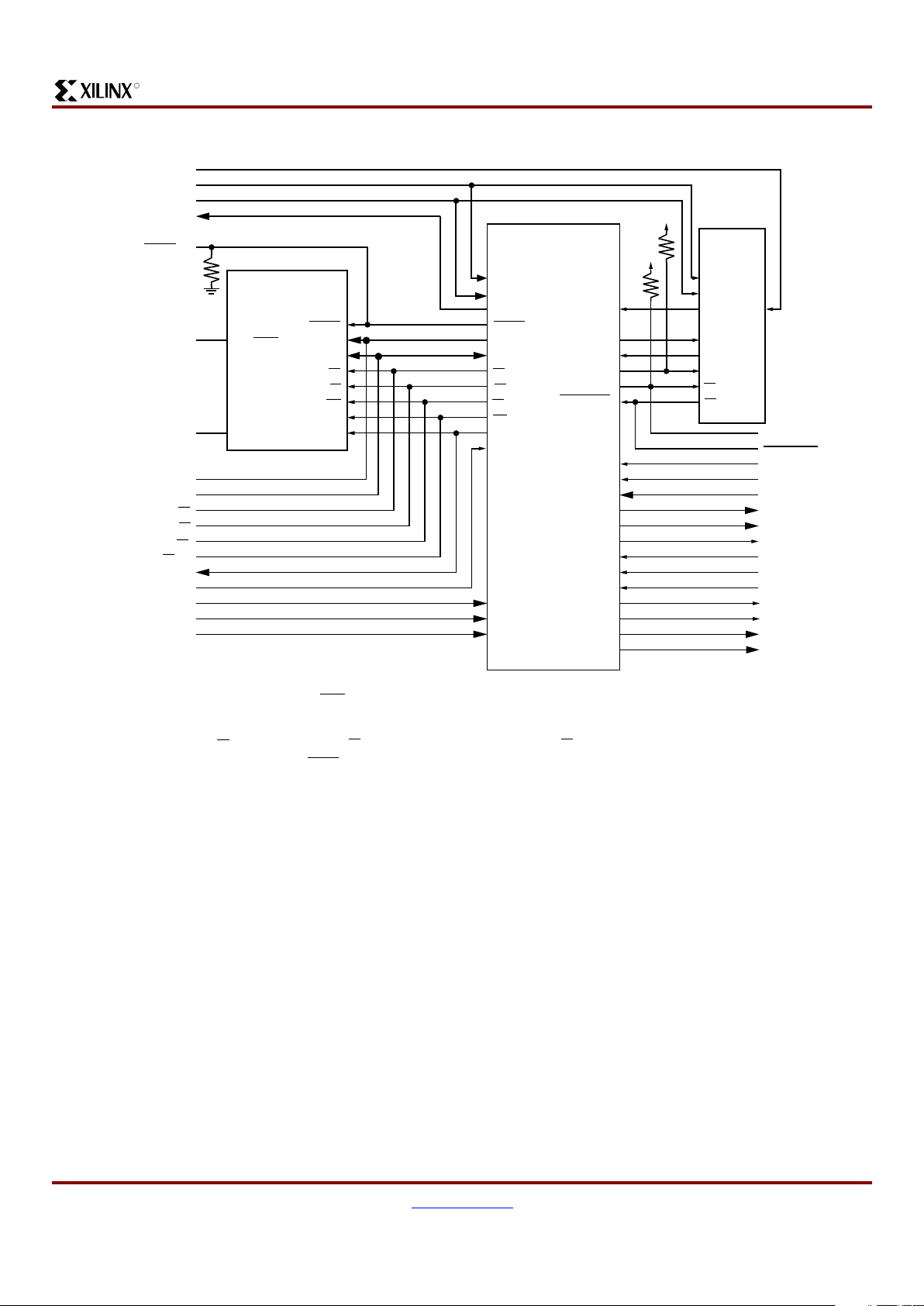

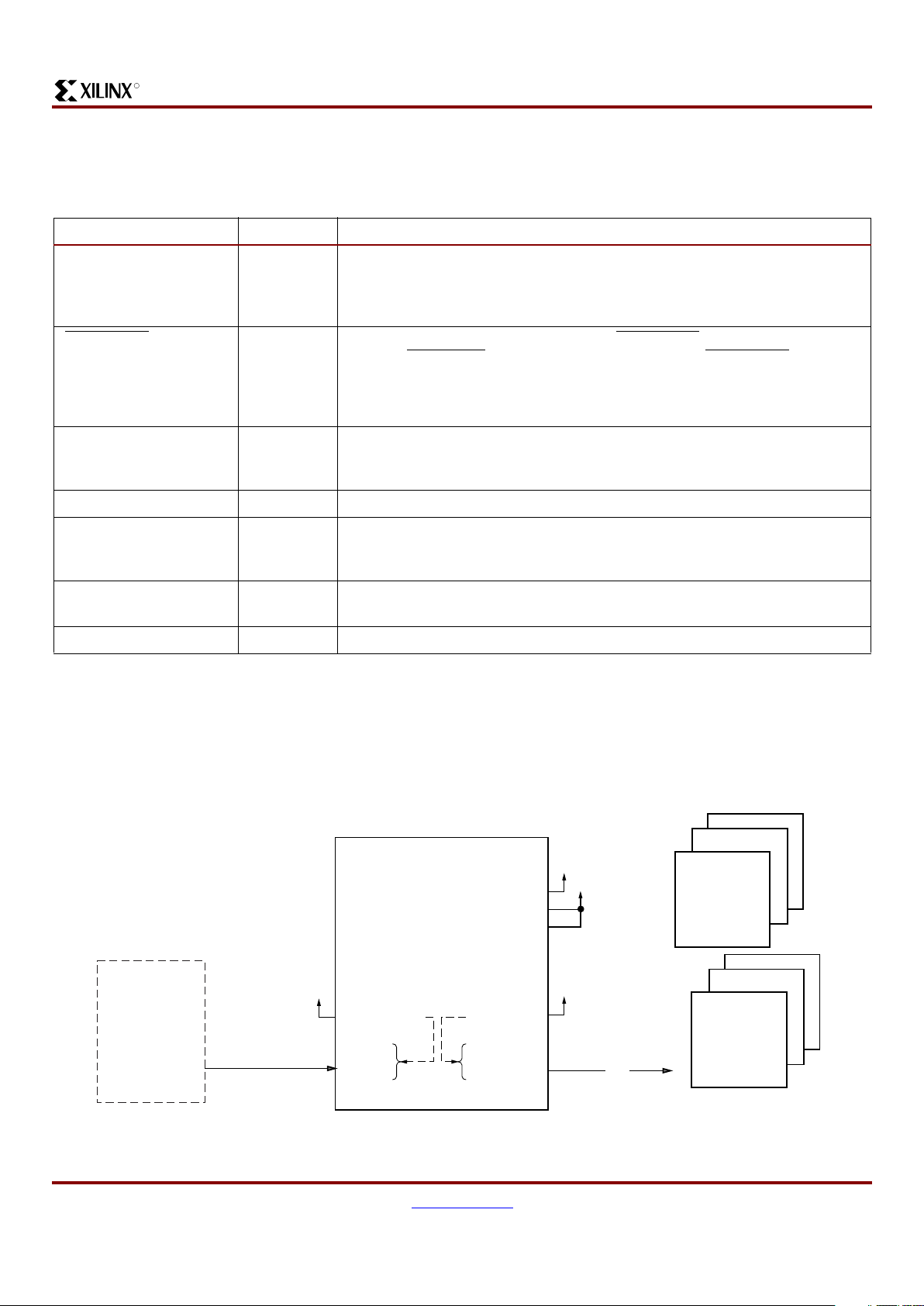

See Figure 3 for a complete view of the components and

schematic of the signals in the System ACE MPM.

0

System ACE MPM Solution

DS087 (v1.0) September 25, 2001

00

Advance Product Specification

R

System ACE MPM Solution

2 www.xilinx.com DS087 (v1.0) September 25, 2001

1-800-255-7778 Advance Product Specification

R

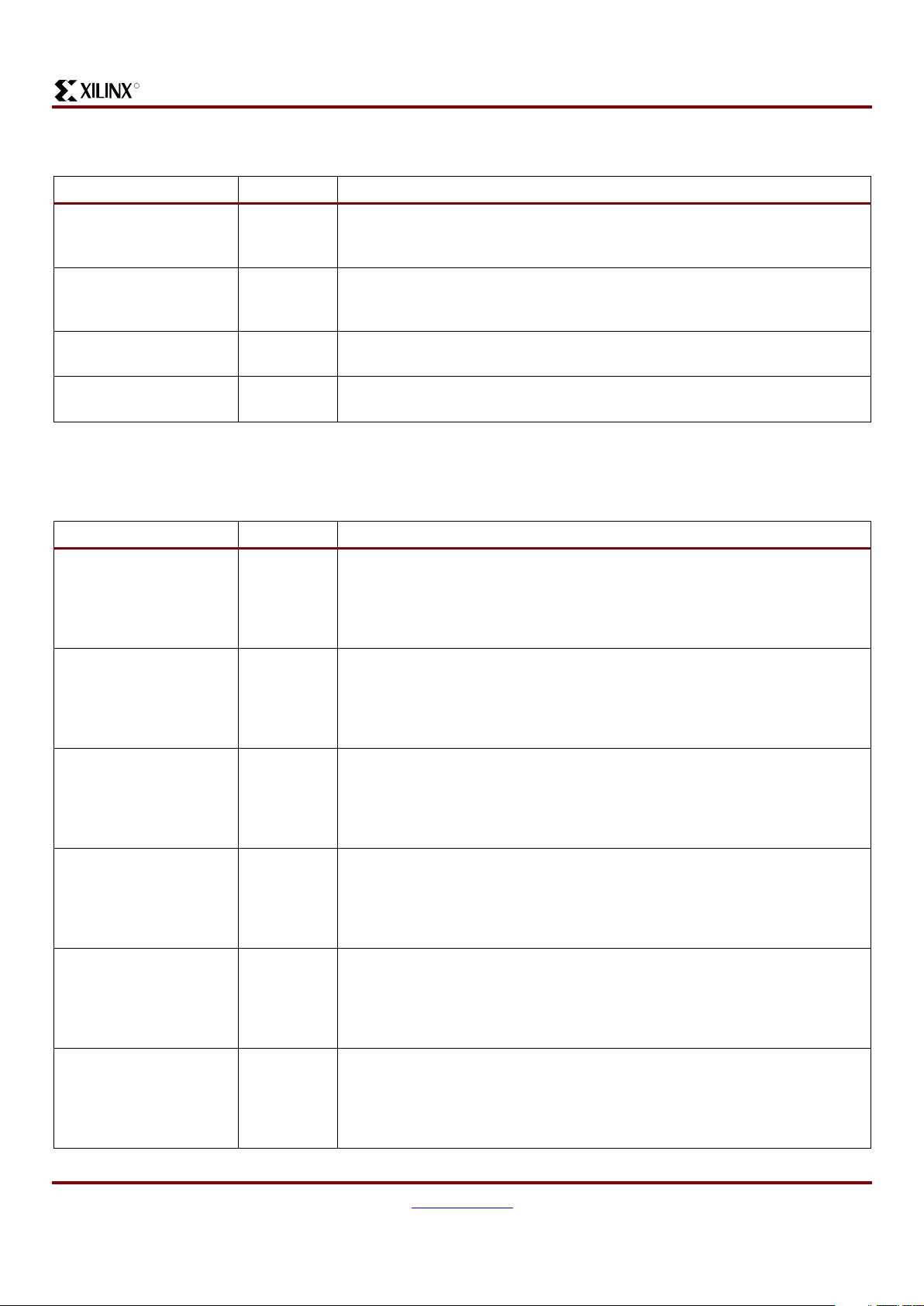

Figure 1: System ACE MPM Assembly

16/32/64 Mbit AMD Flash Memory

Package: 48 pin TSOP

Dimensions: 20 x 12 x 1.2 mm

PROM XC18V01

Package: VQ44

Dimensions: 12 x 12 x 1.2 mm

Virtex XCV50E Configuration Controller

Package: CS144

Dimensions: 12 x 12 x 1.2 mm

Metal Lid

MPM BGA Module

System ACE MPM BG388

Complete Assembly

Dimensions: 35 x 35 x 2.7 mm

DS087_01_081501

Figure 2: System ACE MPM Interfaces

System ACE MPM

PROM

Slave-Serial

or SelectMAP

AMD

Flash

Memory

Boundary

Scan

Interface

System

Control

Interface

Native

Flash

Memory

XCV50E

Configuration

Controller

Target

FPGA

Interface

ds087_02_091001

System ACE MPM So lution

DS087 (v1.0) September 25, 2001 www.xilinx.com 3

Advance Product Specification 1-800-255-7778

R

Figure 3: System ACE MPM schematic

AMD Flash

V

IO

/BYTE *

2

ACC *

4

RESET

A0-A21 *

1

DQ0-DQ15

OE

CE

WE

ACC/WP *

5

RY/BY *

3

TDI

TCK

TMS

TDO

RESET *

6

FLASH_IO_LEVEL*

2

ACC *

4

A0-A21 *

1

DQ0-DQ15

OE

CE

WE

WP *

5

RY/BY *

3

FCM_ENABLE

FLASH_VCCO

CFG_VCCO

CTRL_VCCO

XCV50E

TDI

CCLK

DIN

INIT

DONE

PROGRAM

SYSRESET

SYSCLK

BITSTRSEL[0-2]

STATUS[0-3]

CFG_MODE[0-2]

CFG_CLK

CFG_BUSY

CFG_INIT

CFG_DONE

CFG_PROG

CFG_WRITE

CFG_CS[0-3]

CFG_DATA[0-7]

TCK

TMS

TDO

RESET

A0-A21 *

1

DQ0-DQ15

OE

CE

WE

WP *

5

RY/BY *

3

FCM_ENABLE

VCCO

2,3,4,5

VCCO

6,7

VCCO

0,1

4.7k

*1

A21 for XCCACEM64 only; A20 for XCCACEM32 and XCCACEM64 only.

*2

V

IO

for XCCACEM64; BYTE for XCCACEM16 and XCCACE32.

*3

XCCACEM16 and XCCACEM32 only.

*4

XCCACEM64 only.

*5 WP on XCCACEM64; ACC/WP on XCCACEM32. Do not apply V to ACC/WP.

*6

Do not apply V

ID

to RESET.

XC18V01

TCK

TMS

TDO

CLK

D0

OE/Reset

CE

CF

TDI

300

4.7k

3.3v

3.3v

GND

System ACE MPM

DEVRDY

FCMRESET

SYSRESET

SYSCLK

BITSTRSEL[0-2]

STATUS[0-3]

CFG_MODE[0-2]

CFG_CLK

CFG_BUSY

CFG_INIT

CFG_DONE

CFG_PROG

CFG_WRITE

CFG_CS[0-3]

CFG_DATA[0-7]

DS087_03_091701

HH

System ACE MPM Solution

4 www.xilinx.com DS087 (v1.0) September 25, 2001

1-800-255-7778 Advance Product Specification

R

Pin Descriptions

This section provides native Flash interface, Boundary

Scan, and target FPGA configuration pinout information.

Native Flash Interface Pins

All of the native Flash memory pins are routed to pins on the

System ACE MPM ball-grid-array. Thus, the Flash memory

is available to the sy stem for direct read and write access

with a few restrictions. See Note 1 and Table 1 for descriptions of the restrictions.

Notes:

1. All of the native Flash memory interface pins are connected to

the System ACE MPM controller (except where explicitly

noted in the pin description). The FCM_ENABLE pin must be

held Low to externally access the Flash memory without

contention with the System ACE MPM controller.

Boundary Scan Pins

The System ACE MPM controller (Virtex-E XCV50E) and

the System ACE MPM controller PROM (XC18V01) are

both IEEE Standard 1149.1 compatible devices. The System ACE MPM connects these devices into an internal scan

chain comprised of the XC18V01 device followed by the

XCV50E device. The internal scan chain is accessible

through the boundary scan test access port (TAP) on the

BG388 package. See Table 2.

Table 1: Native Flash Memory Interface Pins

Pin Name Pin Type Description

A0-A21 I/O Flash memory address bus. A21 exists on the XCCACEM64 only. A20 exists

on the XCCACEM32 and XCCACEM64 only.

DQ0-DQ15 I/O Flash memory data bus. DQ15 becomes the A-1 pin in the XCCACEM16 and

XCCACEM32 when the BYTE

mode is active.

RESET

I/O Flash memory hardware reset. When asserted, all Flash operations are

immediately terminated and Flash is reset to read mode. When RESET

and CE

are held High, the Flash memory is put into standby mode. Do not apply V

ID

to

the RESET

pin. The RESET is connected to the System ACE MPM controller

that has a maximum tolerance of 3.6V.

CE

I/O Flash memory chip enable. When RESET and CE are held High, the Flash

memory is put into standby mode.

OE

I/O Flash memory output enable.

WE

I/O Flash memory write enable.

RY/BY Output Flash memory ready/busy signal. Open-drain output. When Low, the RD/BY

signal indicates that the Flash is actively erasing, programming, or resetting.

XCCACEM16 and XCCACEM32 only.

WP I/O Flash memory hardware write protect.

ACC Input Flash memory accelerated mode pin. Do not apply V

HH

to the XCCACEM32

WP/ACC pin. The XCCACEM32 WP/ACC pin is connected to the System ACE

MPM controller that has a maximum tolerance of 3.6V. The XCCACEM64 A CC

pin is independent of the rest of the System ACE MPM and may be used to put

the Flash memory into accelerated program operation.

FLASH_IO_LEVEL Input Flash memory V

IO

pin on the XCCACEM64 only. This pin must be connected

to 3.3V for compatibility with the System ACE MPM controller.

BYTE

Input Flash memory byte-wide data bus mode. XCCACEM16 and XCCACEM32

only . This pin must be connected to 3.3V for compatibility with the System ACE

MPM controller and thus only the 16-bit, word mode is av ailab l e for accessing

the Flash memory in the system.

System ACE MPM So lution

DS087 (v1.0) September 25, 2001 www.xilinx.com 5

Advance Product Specification 1-800-255-7778

R

Target FPGA Configuration Pins

Table 3 provides target FPGA configuration pins.

Table 2: IEEE 1149.1 Boundary Scan Pins

Pin Name Pin Type Description

TCK Input IEEE 1149.1 test clock pin. The System ACE MPM TCK pin is connected to the

XCV50E and XC18V01 TCK pins. By default, the XCV50E has an internal

pull-up resistor on its TCK pin.

TMS Input IEEE 1149.1 test mode select pin. The System ACE MPM TMS pin is

connected to the XCV50E and XC18V01 TMS pins which have internal pull-up

resistors.

TDI Input IEEE 1149.1 test data input pin. The System ACE MPM TDI is connected to

the XC18V01 TDI pin which has an internal pull-up resistor.

TDO Output IEEE 1149.1 test data output pin. The System A CE MPM TDO pin is connected

to the XCV50E TDO pin which by default has an internal pull-up resistor.

Table 3: Target FPGA Configuration Pins

Pin Name Pin Type Description

CFG_DATA[0] Output F or Sla ve-Serial configuration mode , CFG_D ATA[0] is the serial data signal for

Serial-Slave Chain 0 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 0. F or Slave-SelectMAP configuration m ode, CFG_DAT A [0]

is the data bit 0 on the SelectMAP bus and is connected to D0 on all target

FPGAs.

CFG_DATA[1] Output F or Sla ve-Serial configuration mode , CFG_D ATA[1] is the serial data signal for

Serial-Slave Chain 1 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 1. F or Slave-SelectMAP configuration m ode, CFG_DAT A [1]

is the data bit 1 on the SelectMAP bus and is connected to D1 on all target

FPGAs.

CFG_DATA[2] Output F or Sla ve-Serial configuration mode , CFG_D ATA[2] is the serial data signal for

Serial-Slave Chain 2 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 2. F or Slave-SelectMAP configuration m ode, CFG_DAT A [2]

is the data bit 2 on the SelectMAP bus and is connected to D2 on all target

FPGAs.

CFG_DATA[3] Output F or Sla ve-Serial configuration mode , CFG_D ATA[3] is the serial data signal for

Serial-Slave Chain 3 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 3. F or Slave-SelectMAP configuration m ode, CFG_DAT A [3]

is the data bit 3 on the SelectMAP bus and is connected to D3 on all target

FPGAs.

CFG_DATA[4] Output F or Sla ve-Serial configuration mode , CFG_D ATA[4] is the serial data signal for

Serial-Slave Chain 4 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 4. F or Slave-SelectMAP configuration m ode, CFG_DAT A [4]

is the data bit 4 on the SelectMAP bus and is connected to D4 on all target

FPGAs.

CFG_DATA[5] Output F or Sla ve-Serial configuration mode , CFG_D ATA[5] is the serial data signal for

Serial-Slave Chain 5 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 5. F or Slave-SelectMAP configuration m ode, CFG_DAT A [5]

is the data bit 5 on the SelectMAP bus and is connected to D5 on all target

FPGAs.

System ACE MPM Solution

6 www.xilinx.com DS087 (v1.0) September 25, 2001

1-800-255-7778 Advance Product Specification

R

Pin Name Pin Type Description

CFG_DATA[6] Output F or Sla ve-Serial configuration mode , CFG_D ATA[6] is the serial data signal for

Serial-Slave Chain 6 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 6. F or Slave-SelectMAP configuration m ode, CFG_DAT A [6]

is the data bit 6 on the SelectMAP bus and is connected to D6 on all target

FPGAs.

CFG_DATA[7] Output F or Sla ve-Serial configuration mode , CFG_D ATA[7] is the serial data signal for

Serial-Slave Chain 7 and is connected to DIN of the first FPGA in the

Slave-Serial Chain 7. F or Slave-SelectMAP configuration m ode, CFG_DAT A [7]

is the data bit 7 on the SelectMAP bus and is connected to D7 on all target

FPGAs.

CFG_MODE[0] Output The CFG_MODE pins set the configuration mode on the target FPGAs.

Connect CFG_MODE[0] to the M0 pin on all target FPGAs.

CFG_MODE[1] Output The CFG_MODE pins set the configuration mode on the target FPGAs.

Connect CFG_MODE[1] to the M1 pin on all target FPGAs.

CFG_MODE[2] Output The CFG_MODE pins set the configuration mode on the target FPGAs.

Connect CFG_MODE[2] to the M2 pin on all target FPGAs.

CFG_CCLK Output CFG_CCLK is the configuration clock source for the target FPGAs. The

CFG_CCLK is derived from the SYSCLK. The CFG_CCLK frequency is half

the SYSCLK frequency. Connect CFG_CCLK to the CCLK pin on all target

FPGAs.

CFG_PROG

Output CFG_PROG is pulsed Low at the beginning of the configuration download to

reset the configuration state of the target FPGAs. CFG_PROG

is connected to

the PROG_B pin on all target FPGAs.

CFG_INIT Input Target FPGA INIT monitor pin. At the start of the configuration process, the

System ACE MPM controller waits for INIT to go High bef ore initiating deliv ery

of configuration data through the CFG_DATA pins. CFG_INIT is connected to

the INIT pin on all target FPGAs.

CFG_BUSY Input When CFG_B USY is High, the CFG_DAT A outputs are held. If the target FP GA

configuration mode is Slave-SelectMAP and if the CFG_CCLK is greater than

50 MHz, connect the CFG_BUSY pin to the BUSY pin on all target FPGAs.

Otherwise, pull-down the CFG_BUSY pin to GND.

CFG_DONE Input CFG_DONE monitors the DONE status on all target FPGAs. Connect the

CFG_DONE to the DONE pin on all target FPGAs. DONE must be pulled High

with an external 330-8 pull-up resistor. The BitGen option DriveDONE should

be left in the default “NO” setting when generating bitstreams for Xilinx FPGAs.

CFG_WRITE

Output Slave-SelectMAP write-enable pin. Connect the CFG_WRITE pin to the

RDWR_B pin on all target FPGAs.

CFG_CS[0]

Output S lav e-SelectMAP chip-enab le f or target FPGA 0. Connect the CFG_CS[0] pin

to the CS_B pin on target FPGA 0.

CFG_CS[1]

Output S lav e-SelectMAP chip-enab le f or target FPGA 1. Connect the CFG_CS[1] pin

to the CS_B pin on target FPGA 1.

CFG_CS[2]

Output S lav e-SelectMAP chip-enab le f or target FPGA 2. Connect the CFG_CS[2] pin

to the CS_B pin on target FPGA 2.

CFG_CS[3]

Output S lav e-SelectMAP chip-enab le f or target FPGA 3. Connect the CFG_CS[3] pin

to the CS_B pin on target FPGA 3.

Table 3: Target FPGA Configuration Pins (Continued)

System ACE MPM So lution

DS087 (v1.0) September 25, 2001 www.xilinx.com 7

Advance Product Specification 1-800-255-7778

R

System Control and Status Pins

Table 4 provides system control and status pins.

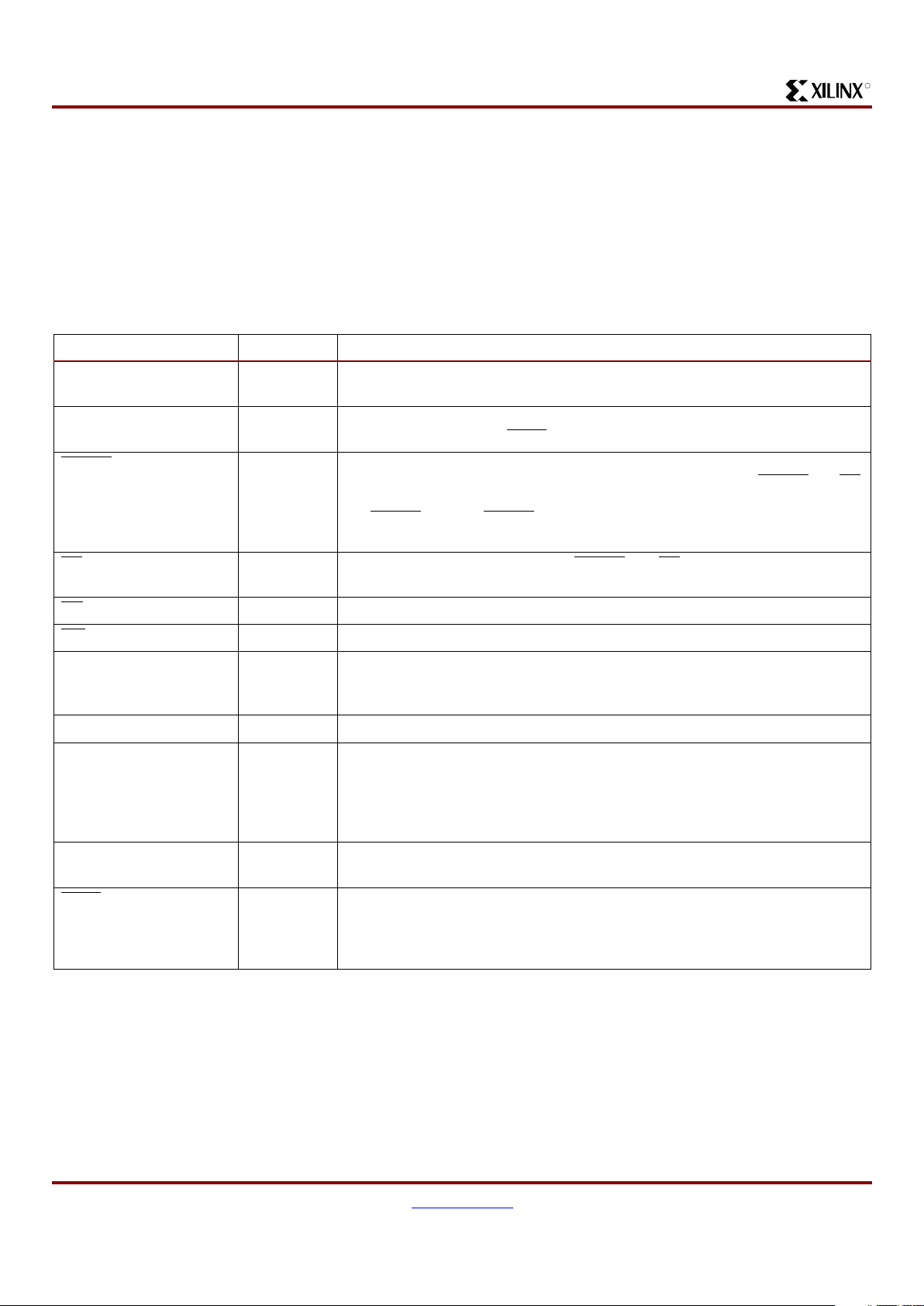

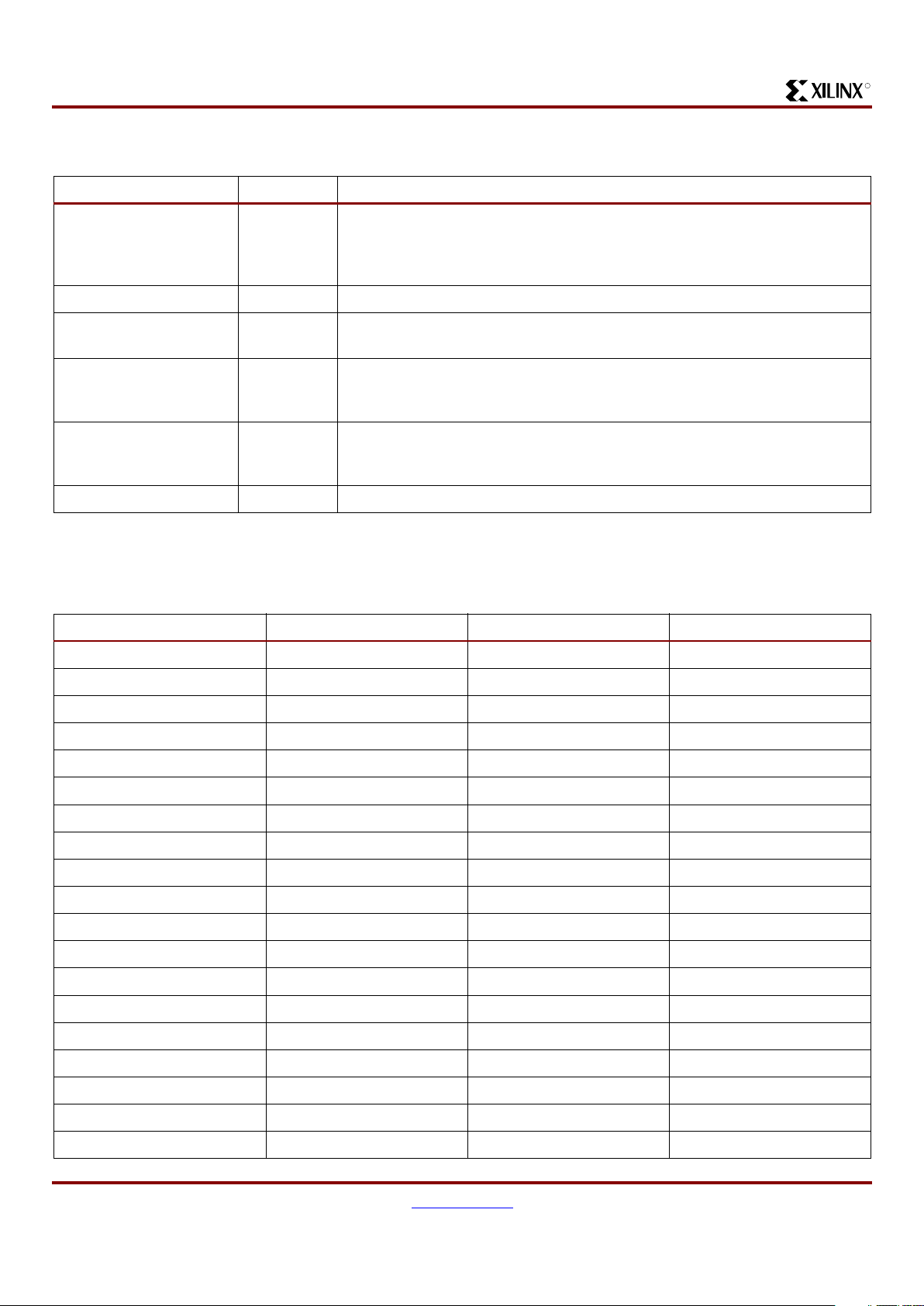

Power and Ground Pins

The System ACE MPM requires at least two power supplies: 1.8V supplies power to the System ACE MPM configuration controller (an XCV50E) core; and 3.3V supplies

power to the Flash memory and configuration controller

PROM (an XC18V01). Additional power supplies may be

required for the output voltage compatibility pins:

FLASH_VCCO, CFG_VCCO, and CTRL_VCCO. See

Figure 4 and Table 5 for a description of the System ACE

MPM power pins.

Table 4: System Control and Status Pins

Pin Name Pin Type Description

FCM_ENABLE Input System ACE MPM controller enable. When this pin is held Low, all of the

System ACE MPM controller (XCV50E) pins tied to the Flash memory are

3-stated allowing external peripherals access to Flash memory without

contention.

FCMRESET

Input System ACE MPM FPGA reset pin. The FCMRESET pin is connected to the

XCV50E PRO GR AM

pin. Applying a Low pulse to the FCMRESET resets the

XCV50E and forces the XCV50E to reconfigure itself from the XC18V01

PROM. (The XCV50E automatically configures itself from the XC18V01 PROM

at power-up.)

DEVRDY Output System ACE MPM FPGA DONE pin. The DEVRDY pin is connected to the

XCV50E DONE pin. When DEVRDY is High, the XCV50E is configured and

ready for operation.

SYSCLK Input SYSCLK is the system clock input for the System ACE MPM control logic.

SYSRESET Input Hold SYSRESET High for at least 10 SYSCLK cycles to reset the System ACE

MPM control logic. Upon release from the reset condition, the System ACE

MPM initiates the download procedure to the target FPGAs.

BITSTRSEL[2-0] Input The BITSTRSEL pins determine which of the eight configuration data streams

to download to the target FPGA.

STATUS[3-0] Output The STATUS pins indicate the status of the System ACE MPM control logic.

Figure 4: Power Pins

DS087_04_090601

System ACE

MPM

CFG_VCCO

Configuration

Signals

VCCint1

VCCint2

FLASH_VCCO

CTRL_VCCO

Control

Signals

Slave-Serial

or

Slave-SelectMAP

Control

Circuits

BITSTRSEL[0-2]

SYSCLK

SYSRESET

1.8v

3.3v

CFG_VCCO

Compatible with

Target FPGAs

CTRL_VCCO

Compatible with

Control Circuits

System Signals

XILINX

Virtex-II

XILINX

Spartan-II

XILINX

Virtex-II

XILINX

Virtex-II

System ACE MPM Solution

8 www.xilinx.com DS087 (v1.0) September 25, 2001

1-800-255-7778 Advance Product Specification

R

Pinout

Table 6 provides System ACE MPM pinout. Unlisted BGA sites are no connects.

Table 5: Power and Ground Pins

Pin Name Pin Type Description

VCC

INT1

Power 1.8V power supply pins for the Virtex-E XCV50E configuration controller cor e .

The 1.8V power supply should rise prior to or simultaneously to the

FLASH_VCCO, CTRL_VCCO, and CFG_VCCO power supplies.Otherwise,

the XCV50E device might draw excessive current.

VCC

INT2

Power 3.3V power supply pins for the AMD Flash memory and the XC18V01 PROM.

FLASH_VCCO Pow er 3.3V pow er supply for the I/O banks connecting the Virtex-E XCV50E controller

to the AMD Flash memory.

CFG_VCCO Pow er Configurable power supply f or the I/O banks on the target FPGA configuration

interface. Connect this power pin to a voltage that is compatible with the target

FPGA configuration pins.

CTRL_VCCO Pow er Configurable power supply for the I/O banks on the system interface . Connect

this power pin to a v oltage that is compatible with the system control a nd status

monitor signals.

GND Ground Ground.

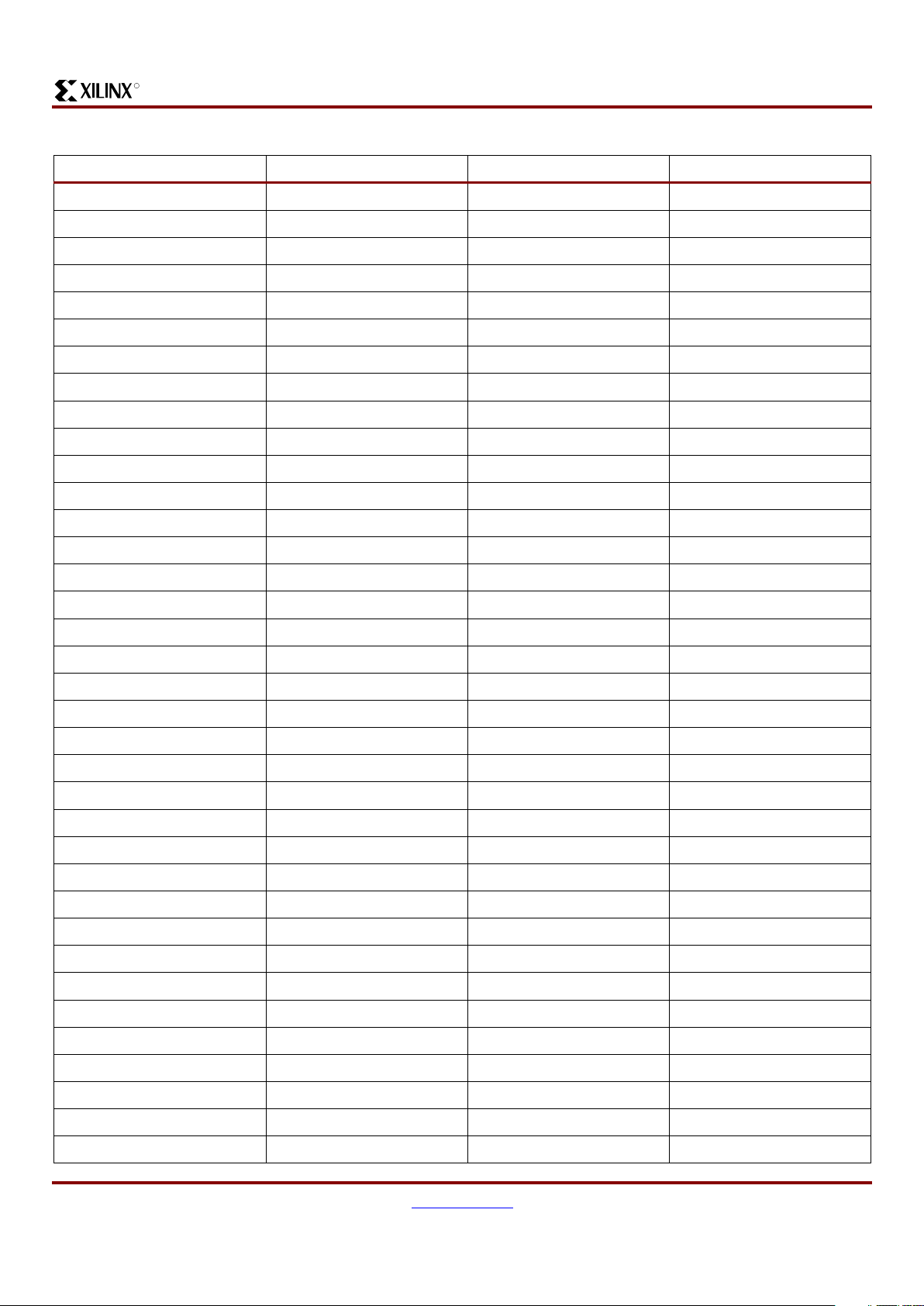

Table 6: System ACE MPM Pinout

Pin Name XCCACEM16-BG388I XCCACEM32-BG388I XCCACEM64-BG388I

A0 AF8 AF8 AF8

A1 AF4 AF4 AF4

A2 AF3 AF3 AF3

A3 AF2 AF2 AF2

A4 AE4 AE4 AE4

A5 AE3 AE3 AE3

A6 AE1 AE1 AE1

A7 AD2 AD2 AD2

A8 W1 W1 W1

A9 W2 W2 W2

A10V1V1V1

A11V2V2V2

A12 U1U1U1

A13 U2U2U2

A14 T1 T1 T1

A15 T2 T2 T2

A16 R25 R25 R25

A17 AD1 AD1 AD1

A18 AC2 AC2 AC2

System ACE MPM So lution

DS087 (v1.0) September 25, 2001 www.xilinx.com 9

Advance Product Specification 1-800-255-7778

R

Pin Name XCCACEM16-BG388I XCCACEM32-BG388I XCCACEM64-BG388I

A19Y1Y1AC1

A20 n/a Y2 Y2

A21 n/a n/a Y1

DQ0 AD26 AD26 AD26

DQ1 AC25 AC25 AC25

DQ2 AB26 AB26 AB26

DQ3 AA26 AA26 AA26

DQ4 Y26 Y26 Y26

DQ5 W26 W26 W26

DQ6 U26 U26 U26

DQ7 T26 T26 T26

DQ8 AD25 AD25 AD25

DQ9 AC26 AC26 AC26

DQ10 AB25 AB25 AB25

DQ11 AA25 AA25 AA25

DQ12 Y25 Y25 Y25

DQ13 W25 W25 W25

DQ14 U25 U25 U25

DQ15 T25 T25 T25

RESET AA2 AA2 AA2

CE AE23 AE23 AE23

OE AE26 AE26 AE26

WE AA1 AA1 AA1

RY/BY AC1 AC1 n/a

WP n/a AB2 AB2

ACC n/a n/a AB1

FLASH_IO_LEVEL R26 R26 R26

FCM_ENABLE B7 B7 B7

FCMRESET K26 K26 K26

DEVRDY N26 N26 N26

TCK G26 G26 G26

TMSA3A3A3

TDI F26 F26 F26

TDO A15 A15 A15

SYSCLK A9 A9 A9

SYSRESET B8 B8 B8

Table 6: System ACE MPM Pinout (Continued)

Loading...

Loading...