Page 1

5

4

3

2

1

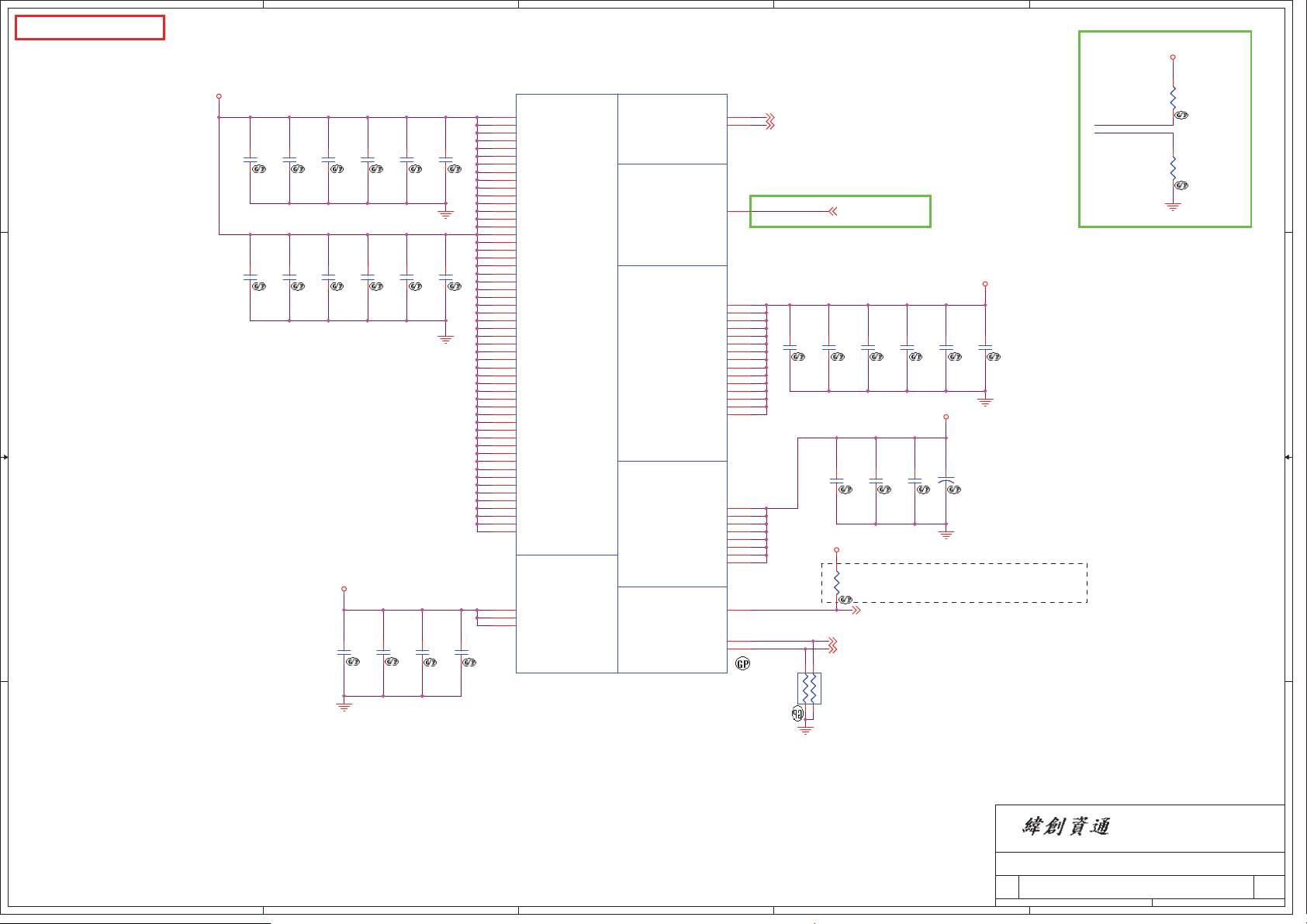

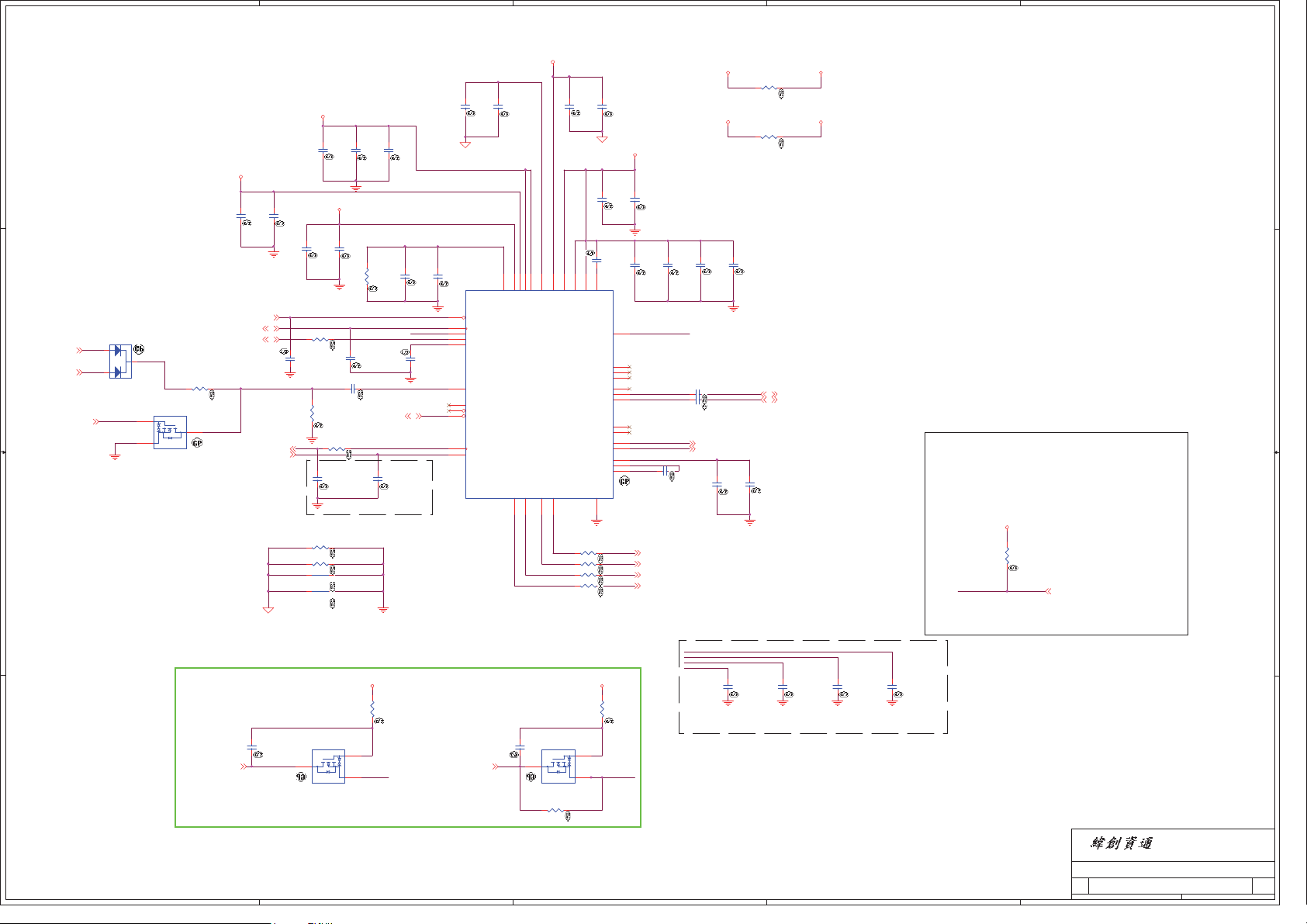

LLW-1/LGG-1 Schematics

D D

Sandy Bridge

Cougar Point

C C

2011-01-18

REV : -1

DY:None Installed

UMA:UMA platform installed only

B B

PX:Discrete(both Robson and Whistler) SKU installed

RBS:Robson SKU installed only

WTL:Whistler SKU installed only

SAMSUNG:Use SAMSUNG VRAM

Hynix:Use Hynix VRAM

VRAM_1G:Use 1G VRAM

VRAM_2G:Use 2G VRAM

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

1

of

194

of

194

of

194

-1

-1

-1

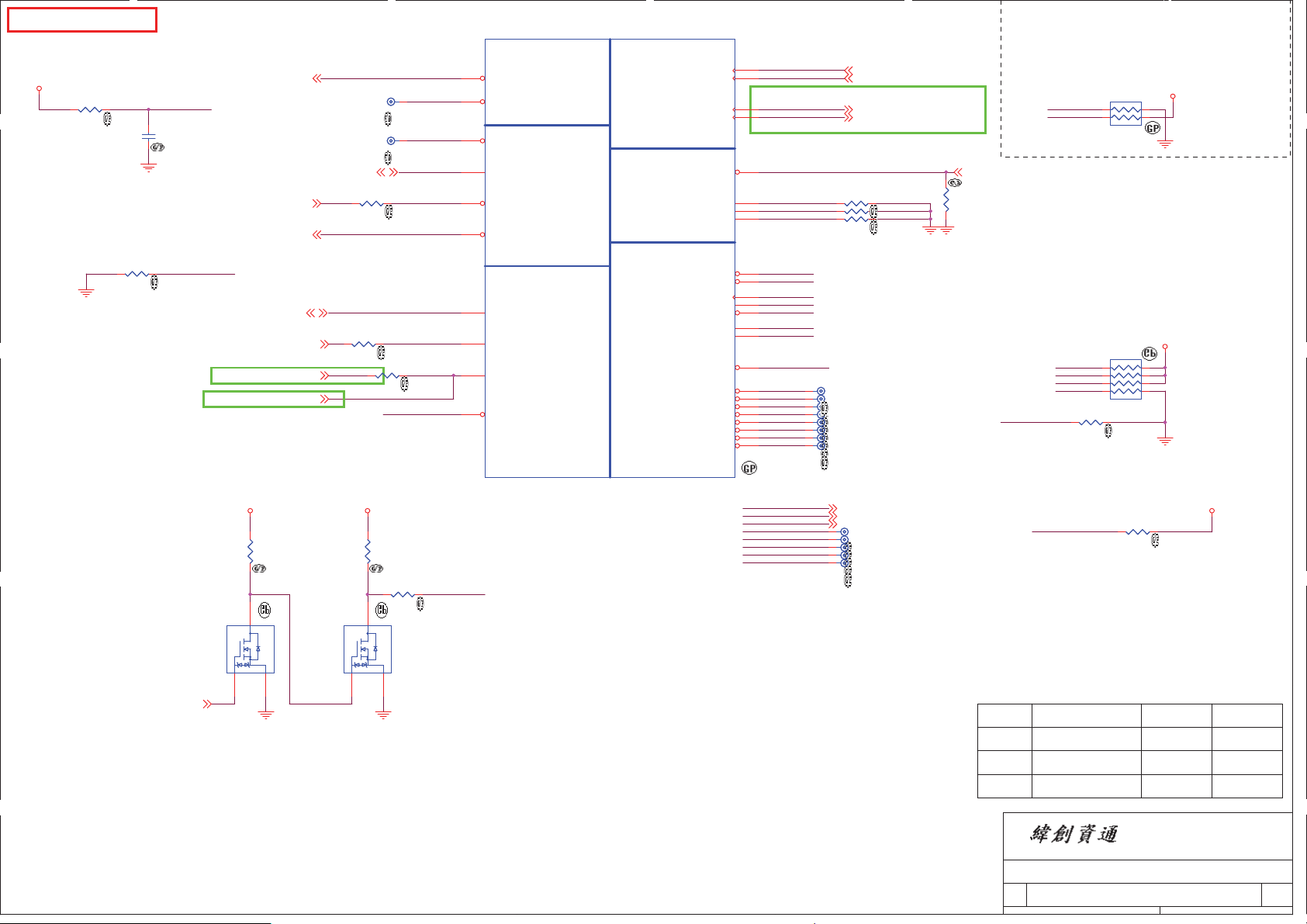

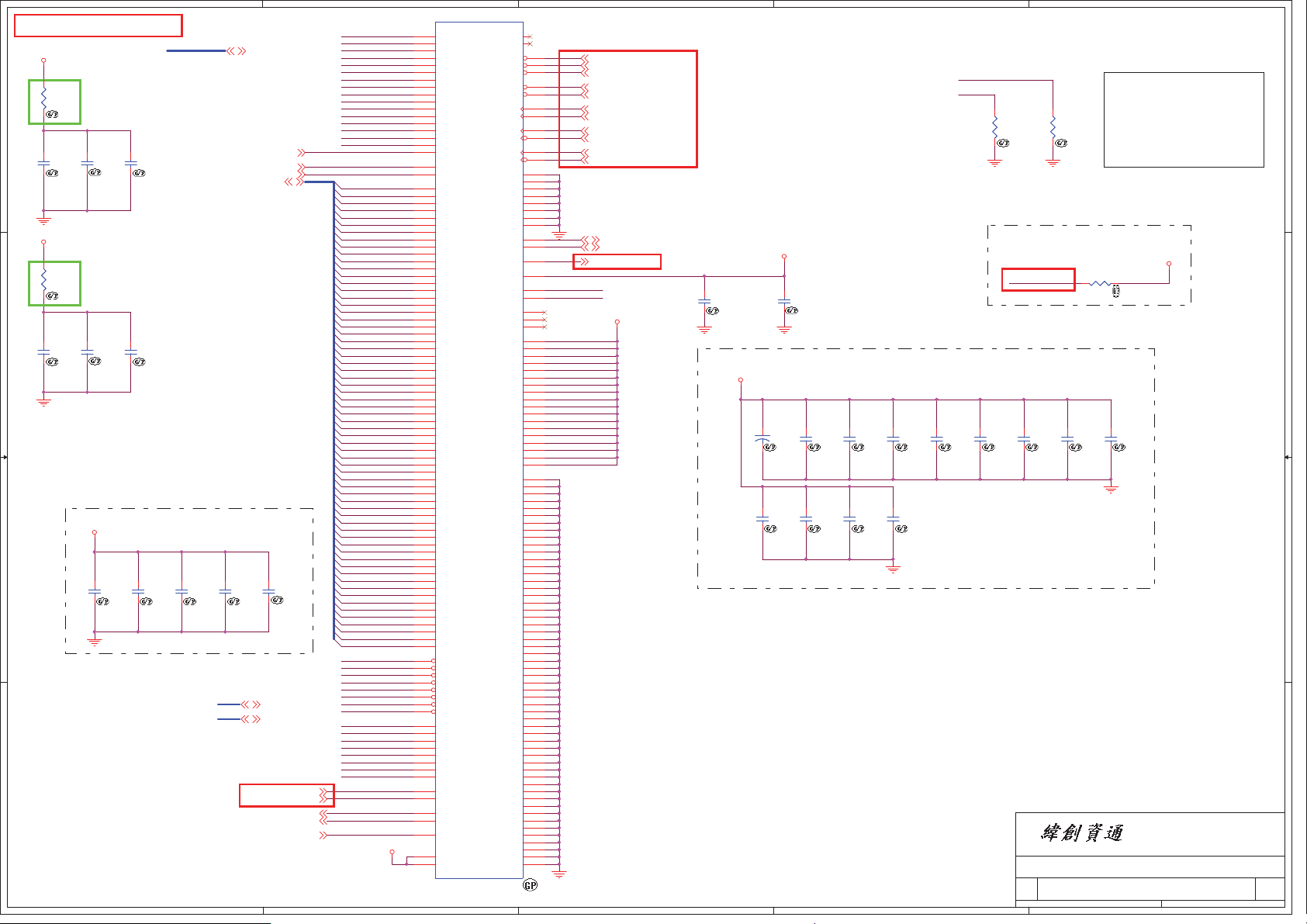

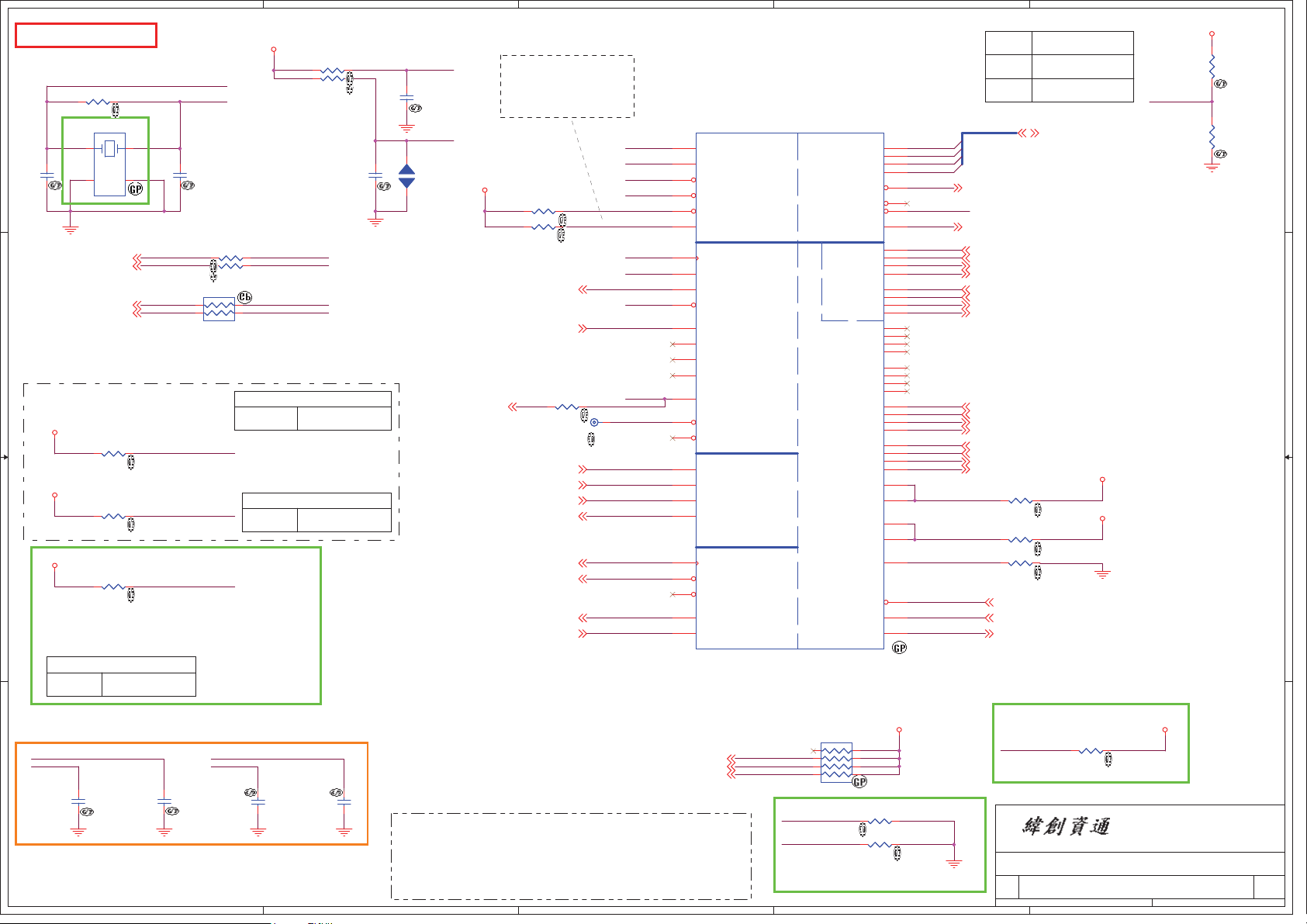

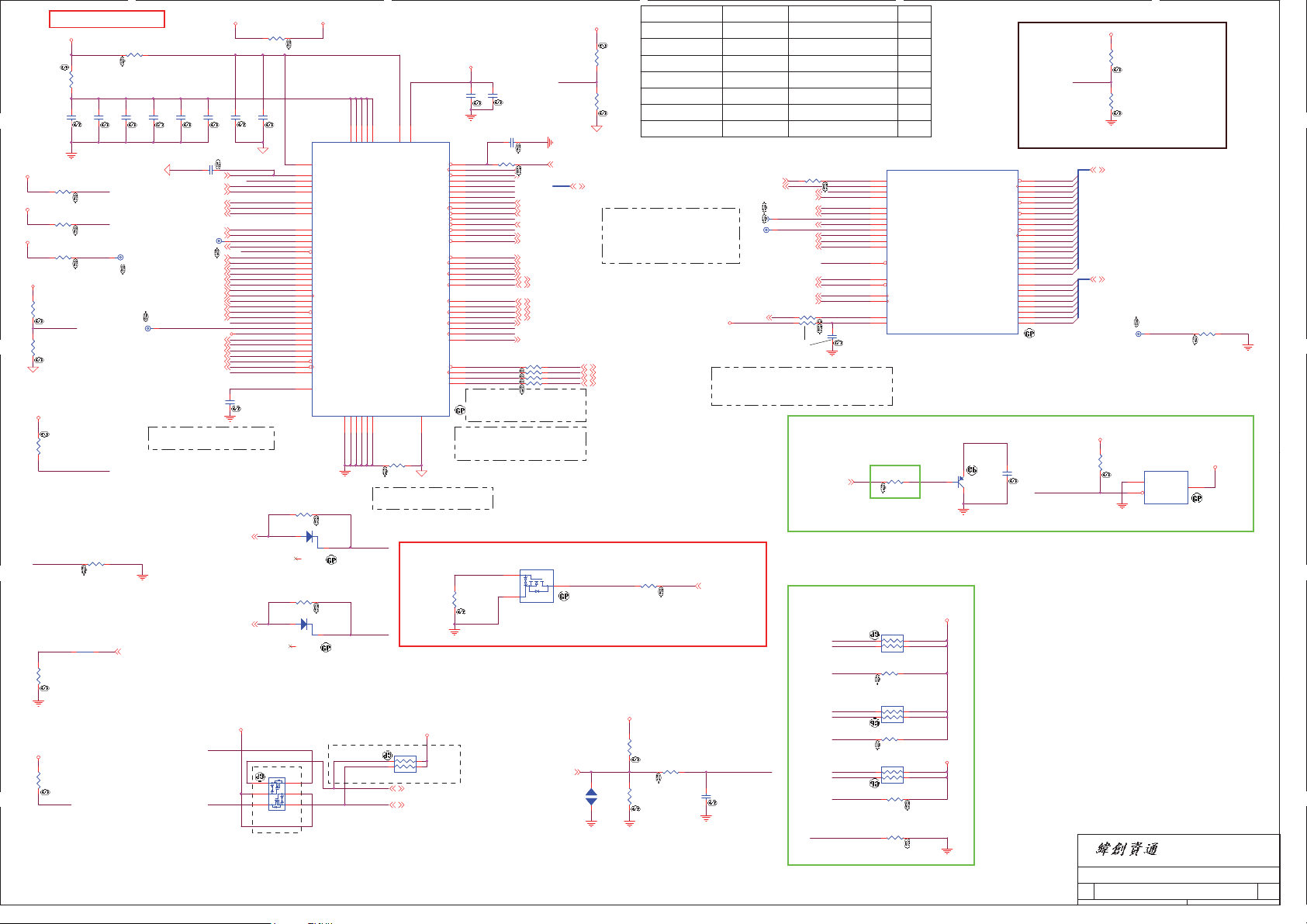

Page 2

PCB Layer Stackup

ThermalSensor

EMC2103

RFID

I2C/SM Bus Switch

14" HD

1366*768

VGA connector

AUDIO

COMBO Jack

58

28

80

49

50

SIM

Slot

USB 2.0

USB 2.0

Camera

##OnMainBoard

SM Bus

LVDS

VGA Port

66

PORT2

PORT1

LLW-1 / LGG-1 Block Diagram

VRAM

2GB/1GB

AMD GPU

Whistler-LP 1G/2G

Seymour-XT 1G

SATA CONN

ODD CONN

Mini PCI-E

WWAN Card

HD AUDIO CODEC

CX20671

eSATA Combo CN

eSATA

USB 2.0

CH1

61

CH9

61

CH12

49

DDR3

800MHz

PORT3

88~91

83~87

56

56

66

29

57

PEG x16

SATA Port 0

SATA Port 4

SATA

USB 2.0 CH4

Azalia bus

SATA Port5

CH8

USB 2.0

FingerPrint

Bluetooth

69

63

Intel CPU

Sandy Bridge

DDR3 1333MHz

DMI x4

Intel

PCH

USB 2.0 (14 ports)

AC97 2.3/Azalia Interface

Serial ATA 150MB/s

ACPI 2.0

LPC I/F

PCI Rev 2.3

PCI Express

INT. RTC

CH2

HDMI

USB 2.0

CH3

connector

4~10

FDI

17~25

Display Port

51

XDP

Conn.

Channel A

DDR3 1333

Channel B

DDR3 1333

USB 2.0 CH11

PCI Express 4

PCI Express 2

11

Project Code: 91.4MH01.001

PCB(Raw Card):10282

UNBUFFERED

DDR3 SODIMM

204-PIN DDR3 SODIMM

UNBUFFERED

DDR3 SODIMM

Mini PCI-E

WLAN Card

PCI Express 2

CONNCONN

82

PCI Express 3

USB 2.0 CH13

PCI Express 8

USB 2.0 CH10 USB 2.0 CH10

Media Card Reader

R5U220

PCI Express 8

82

LPC Bus / 33MHz

KBC

Nuvoton NPCE795

27

G-Sensor

SPI FLASH

79

Int.KB/Track point

Touch Pad

60

65

32

USB 2.0 CH13

LPC Debug

Board Conn

14

15

LOM

RTL8111E

NEW CARD

USB 2.0 PORT4

71

69

L1: TOP L5: VCC

L2: GND

L3: Signal

L4: Signal

L6: Signal

L7: GND

L8: BOTTOM

Battery Charger/Selector

BQ24745

OUTPUTSINPUTS

DCBATOUT BT+

System DC/DC

BD95280

PWR_3D3V_DCBATOUT

PWR_5V_DCBATOUT

3D3V_S5

5V_S5

CPU DC/DC

NCP6131

DCBATOUT

DCBATOUT_VCC_GFXCOREVCC_GFXCORE

42~44

VCC_CORE

1D05V_VTT

TPS51218

PWR_1D05V_DCBATOUT

1D05V_VTT

1D5V_S3

TPS51218

PWR_1D5V_DCBATOUT 1D5V_S3

0D75V

RJ45

RT9026

1D5V_S3

DDR_VREF_S3

0D75V_S0

1D8V_S0

RT8015

3D3V_S5

1D8V_S0

VCCSA

RT8208B

PWR_VCCSA_DCBATOUT

0D85V_S0

GFX CORE

RT8208B

PWR_DCBATOUT_VGA_COREVGA_CORE

1V_VGA

RT9025

1V_VGA_S01D5V_S3

1D8V_VGA

RT9025

3D3V_S5 1D8V_VGA_S0

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

of

of

of

294Tuesday, January 18, 2011

294Tuesday, January 18, 2011

294Tuesday, January 18, 2011

40

41

45

46

46

47

48

92

93

93

-1

-1

-1

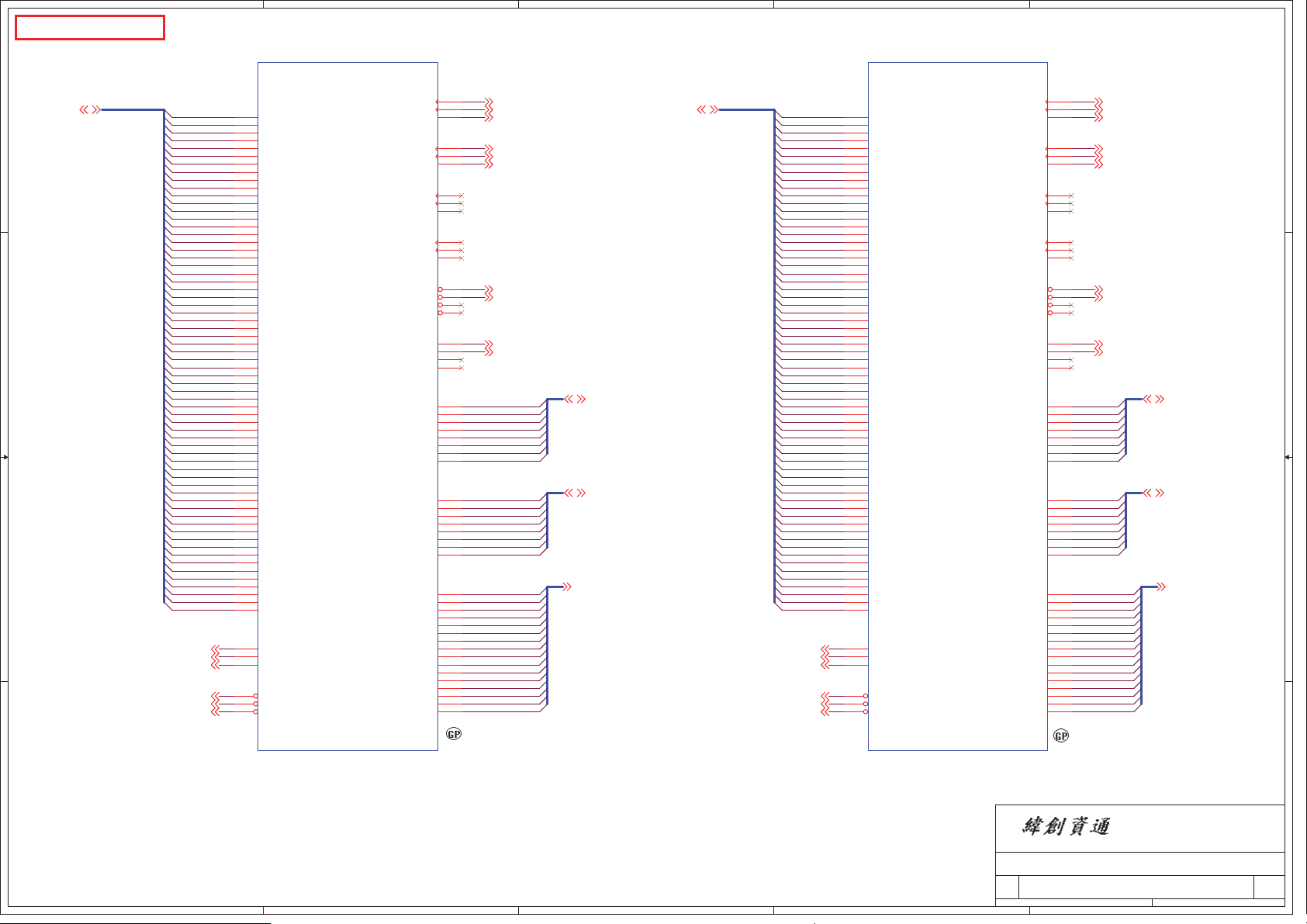

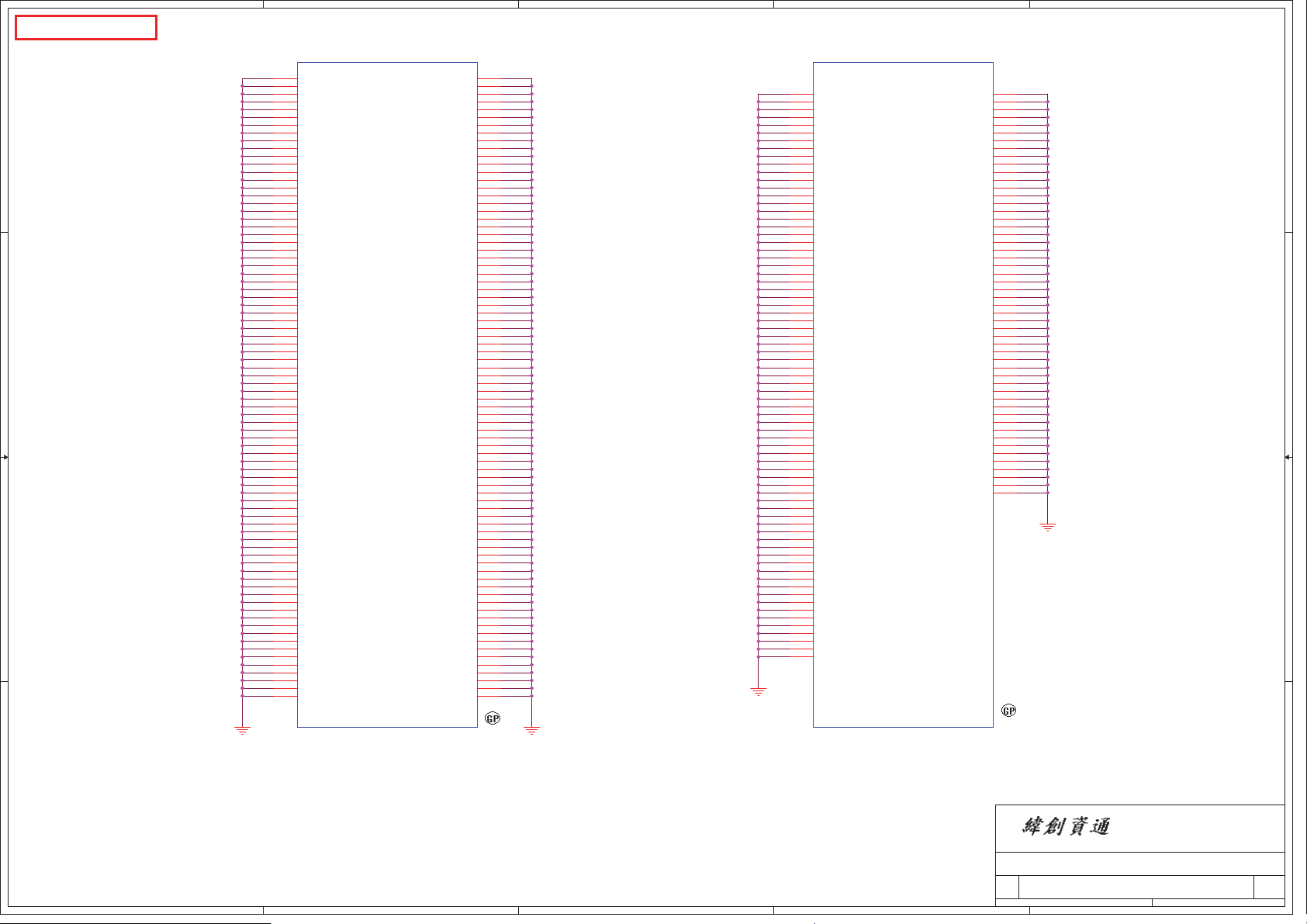

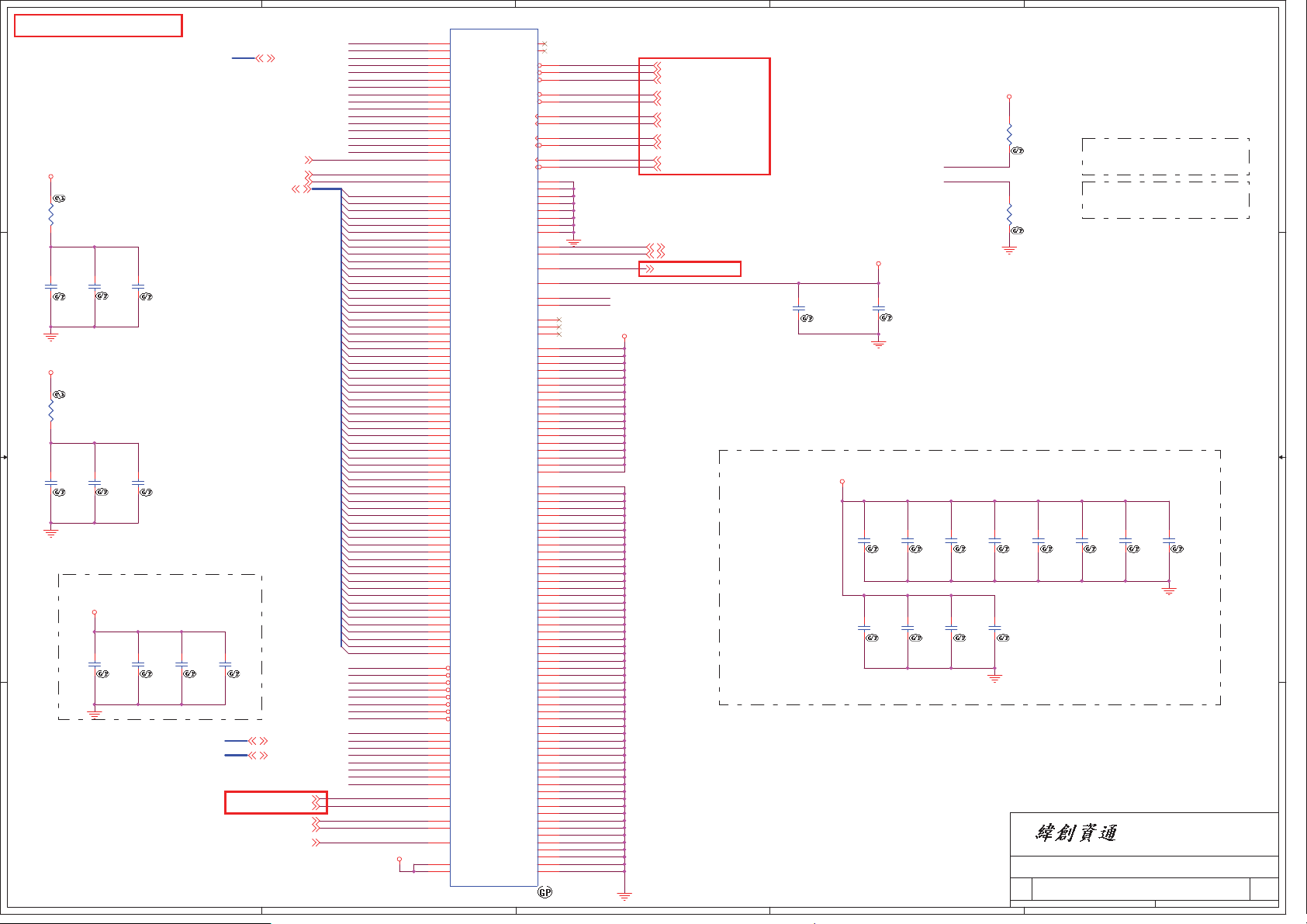

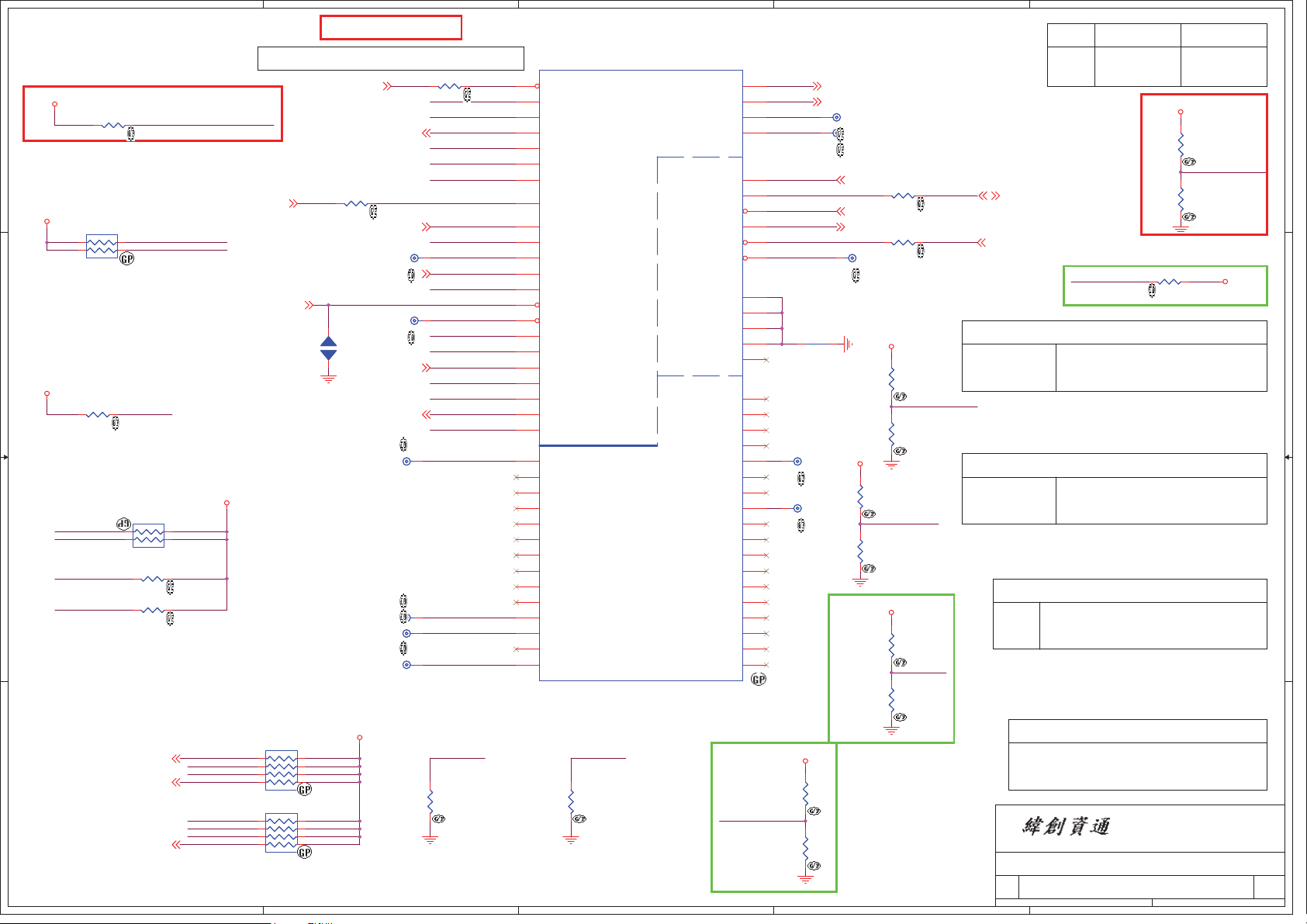

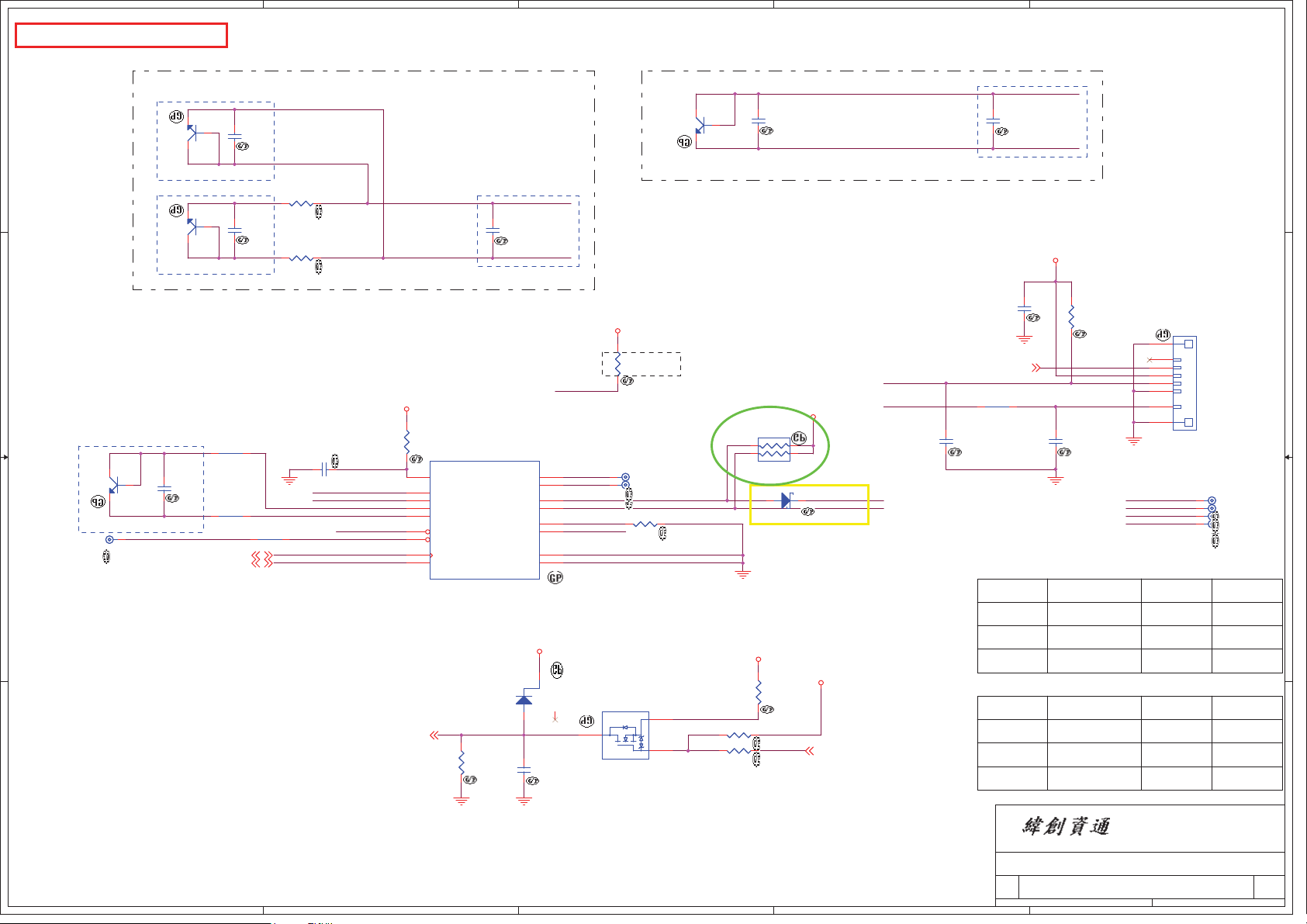

Page 3

A

PCH Strapping

Name Schematics Notes

SPKR

INIT3_3V# Weak internal pull-up. Leave as "No Connect".

GNT3#/GPIO55

4 4

GNT2#/GPIO53

GNT1#/GPIO51

SPI_MOSI

NV_ALE

Reboot option at power-up

Internal weak Pull-down.

Default Mode:

Connect to Vcc3_3 with 8.2-kȍ

No Reboot Mode with TCO Disabled:

- 10-kȍ weak pull-up resistor.

GNT[3:0]# functionality is not available on Mobile.

Mobile: Used as GPIO only

Pull-up resistors are not required on these signals.

If pull-ups are used, they should be tied to the Vcc3_3power rail.

Enable Danbury:

Disable Danbury:

Enable Danbury:

Disable Danbury:

Huron River Schematic Checklist Rev.0_7

Connect to Vcc3_3 with 8.2-k? weak pull-up resistor.

Left floating, no pull-down required.

Connect to +NVRAM_VCCQ with 8.2-kohm

weak pull-up resistor [CRB has it pulled up

with 1-kohm no-stuff resistor]

Leave floating (internal pull-down)

B

C

Processor Strapping

Pin Name Strap Description Configuration (Default value for each bit is

CFG[2]

PCI-Express Static

Lane Reversal

CFG[4]

CFG[6:5]

CFG[7]

PCI-Express

Port Bifurcation

Straps

PEG DEFER TRAINING

1 unless specified otherwise)

1:

Normal Operation.

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

0:

Disabled - No Physical Display Port attached to

1:

Embedded DisplayPort.

Enabled - An external Display Port device is

0:

connectd to the EMBEDDED display Port

11 : x16 - Device 1 functions 1 and 2 disabled

10 : x8, x8 - Device 1 function 1 enabled ;

function 2 disabled

01 : Reserved - (Device 1 function 1 disabled ;

function 2 enabled)

00 : x8, x4, x4 - Device 1 functions 1 and 2

enabled

1:

PEG Train immediately following xxRESETB de assertion

PEG Wait for BIOS for training

0:

D

Huron River Schematic Checklist Rev.0_7

Default

Value

1

0

11

1

E

NC_CLE DMI termination voltage. Weak internal pull-up. Do not pull low.

Low (0) - Flash Descriptor Security will be overridden. Also,

when this signals is sampled on the rising edge of PWROK

then it will also disable Intel ME and its features.

HAD_DOCK_EN#

/GPIO[33]

3 3

High (1) - Security measure defined in the Flash Descriptor will be enabled.

Platform design should provide appropriate pull-up or pull-down depending on

the desired settings. If a jumper option is used to tie this signal to GND as

required by the functional strap, the signal should be pulled low through a weak

pull-down in order to avoid asserting HDA_DOCK_EN# inadvertently.

Note: CRB recommends 1-kohm pull-down for FD Override. There is an internal

pull-up of 20 kohm for DA_DOCK_EN# which is only enabled at boot/reset for

strapping functions.

HDA_SDO Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

HDA_SYNC

GPIO15

GPIO8

2 2

GPIO27

Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

Low (1) - Intel ME Crypto Transport Layer Security (TLS) cipher suite with no

confidentiality High (1) - Intel ME Crypto Transport Layer Security (TLS) cipher

suite with confidentiality

Note : This is an un-muxed signal.

This signal has a weak internal pull-down of 20 kohm which is enabled when PWROK is low.

Sampled at rising edge of RSMRST#.

CRB has a 1-kohm pull-up on this signal to +3.3VA rail.

GPIO8 on PCH is the Integrated Clock Enable strap and is required to be pulled-down

using a 1k +/- 5% resistor. When this signal is sampled high at the rising edge of

RSMRST#, Integrated Clocking is enabled, When sampled low, Buffer Through Mode is

enabled.

Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

POWER PLANE

5V_S0

3D3V_S0

1D8V_S0

1D5V_S0

1D05V_VTT

0D85V_S0

0D75V_S0

VCC_CORE

VCC_GFXCORE

1D8V_VGA_S0

3D3V_VGA_S0

1V_VGA_S0

5V_USBX_S3

1D5V_S3

DDR_VREF_S3

BT+

DCBATOUT

5V_S5

5V_AUX_S5

3D3V_S5

3D3V_AUX_S5

3D3V_AUX_KBC

3D3V_AUX_S5

VOLTAGE DESCRIPTION

5V

3.3V

1.8V

1.5V

1.05V

0.95 - 0.85V

0.75V

0.35V to 1.5V

0.4 to 1.25V

1.8V

3.3V

1V

5V

1.5V

0.75V

6V-14.1V

6V-14.1V

5V

5V

3.3V

3.3V

3.3V3D3V_LAN_S5

3.3V

3.3V

Voltage Rails

ACTIVE IN

S0

CPU Core Rail

Graphics Core Rail

S3

AC Brick Mode only

All S states

WOL_EN

DSW, Sx ON for supporting Deep Sleep states

G3, Sx

Legacy WOL

Powered by Li Coin Cell in G3

and +V3ALW in Sx

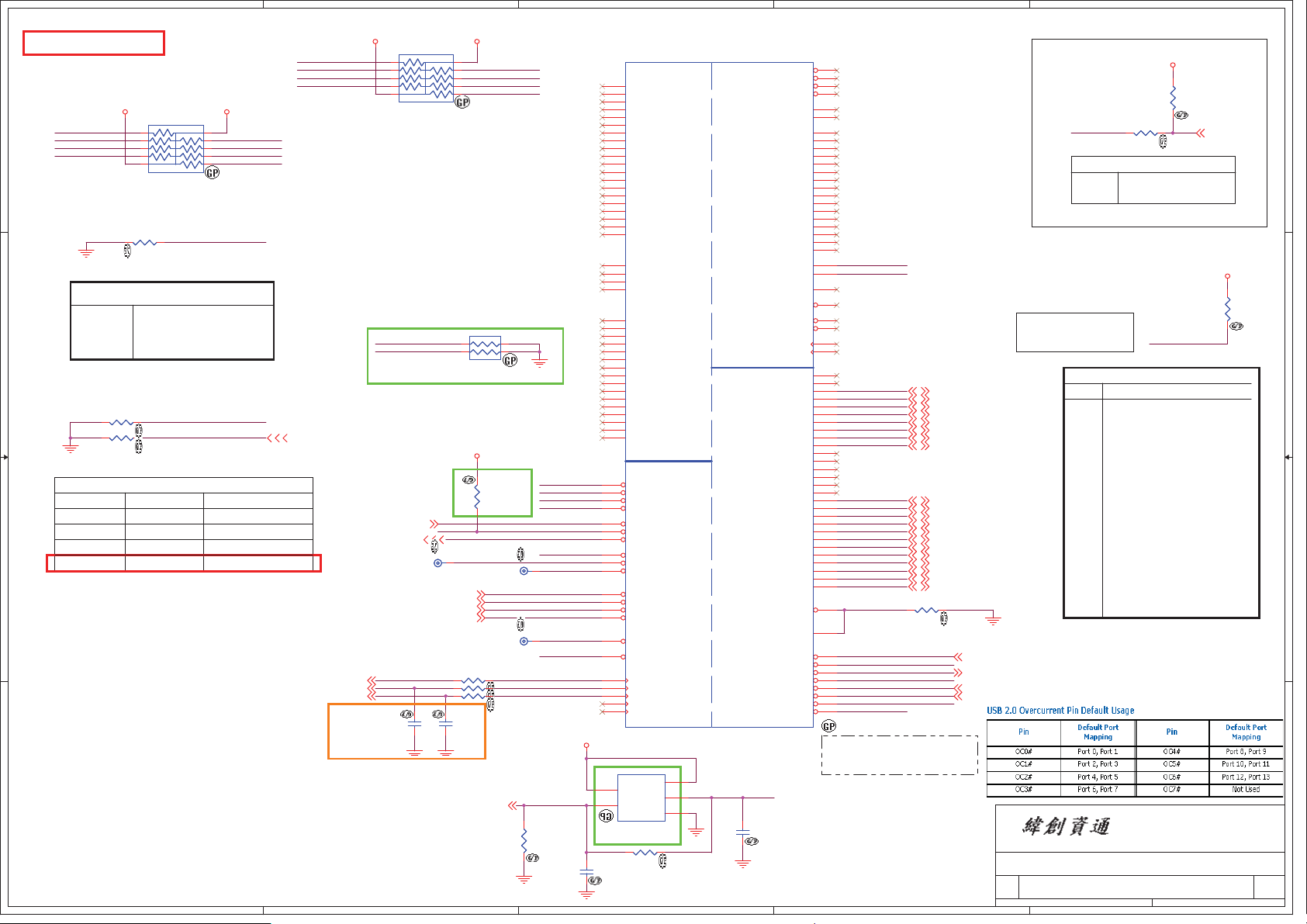

USB Table

Pair Device

X

PCIE Routing

LANE1

LANE2

LANE3

LANE4

1 1

LANE5

LANE6

LANE7

LANE8 NEW CARD

RESERVED

LAN

CARD READER

MiniCard WLAN

RESERVED

RESERVED

RESERVED

SATA Table

SATA

Pair

0

1

2

3

4

5

Device

HDD

mSATA

N/A

N/A

ODD

ESATA

0

USB2

1

FINGERPRINT

2

BLUETOOTH

3

Mini Card2 (WWAN)

4

X

5

X

6

X

7

ESATA1

8

USB1

9

USB Ext. port 4

10

Mini Card1 (WLAN)

11

CAMERA

12

New Card

13

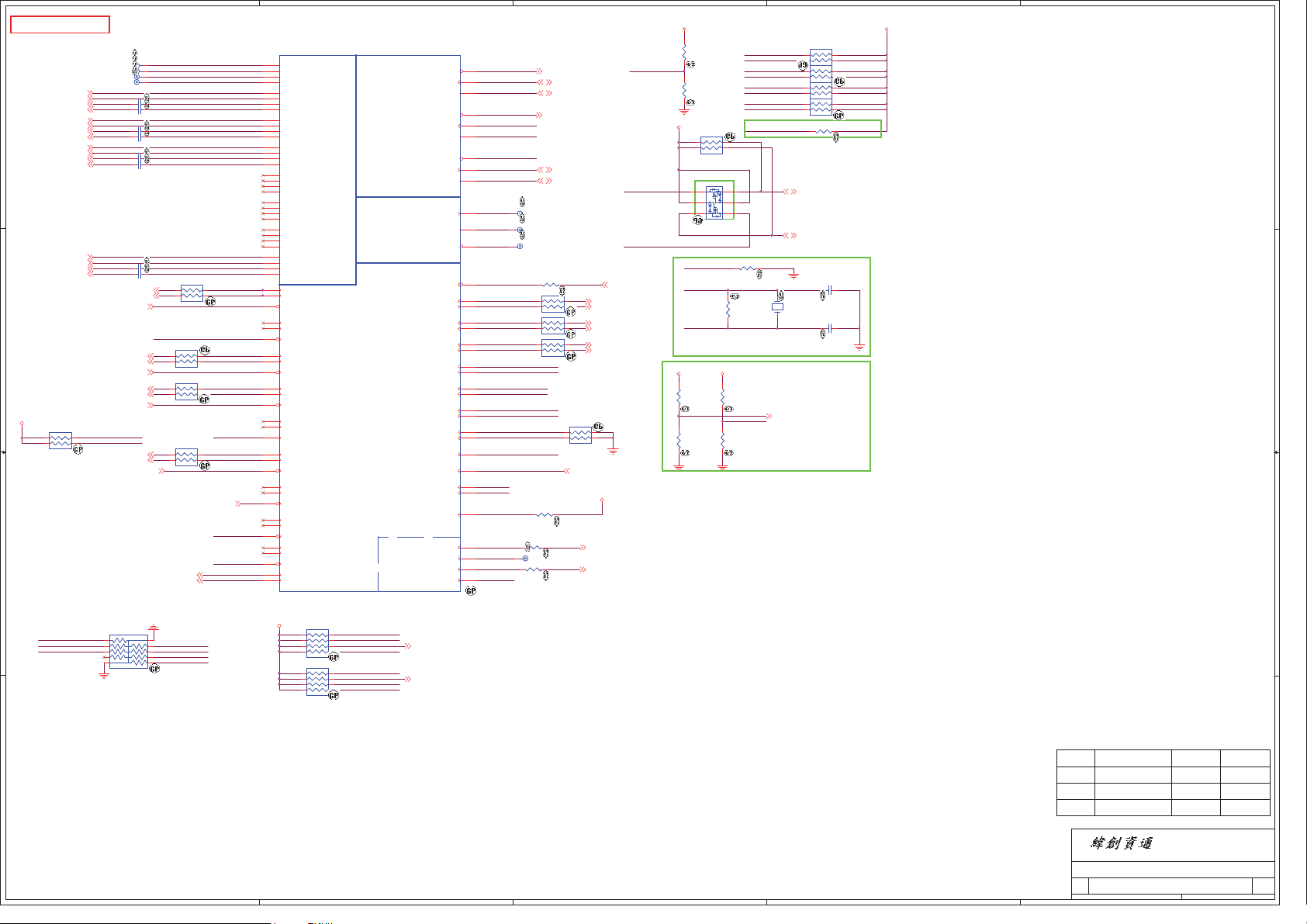

SMBus ADDRESSES

2

I C / SMBus Addresses

Device

EC SMBus 1

Battery

Capacity Board

EC SMBus 2

PCH

MXM

LCD

Thermal Sensor

PCH SMBus

CK505 Clock Generator

SO-DIMMA (SPD)

SO-DIMMB (SPD)

Digital Pot

HURON RIVER ORB

Address Hex Bus Ref Des

KBC_SDA1/KBC_SCL1

KBC_SDA1/KBC_SCL1

KBC_SDA2/KBC_SCL2

KBC_SDA2/KBC_SCL2

KBC_SDA2/KBC_SCL2

KBC_SDA2/KBC_SCL2

PCH_SMBDATA/PCH_SMBCLK

PCH_SMBDATA/PCH_SMBCLK

PCH_SMBDATA/PCH_SMBCLK

PCH_SMBDATA/PCH_SMBCLK

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Table of Content

Table of Content

Table of Content

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

of

394Tuesday, January 18, 2011

of

394Tuesday, January 18, 2011

of

394Tuesday, January 18, 2011

-1

-1

-1

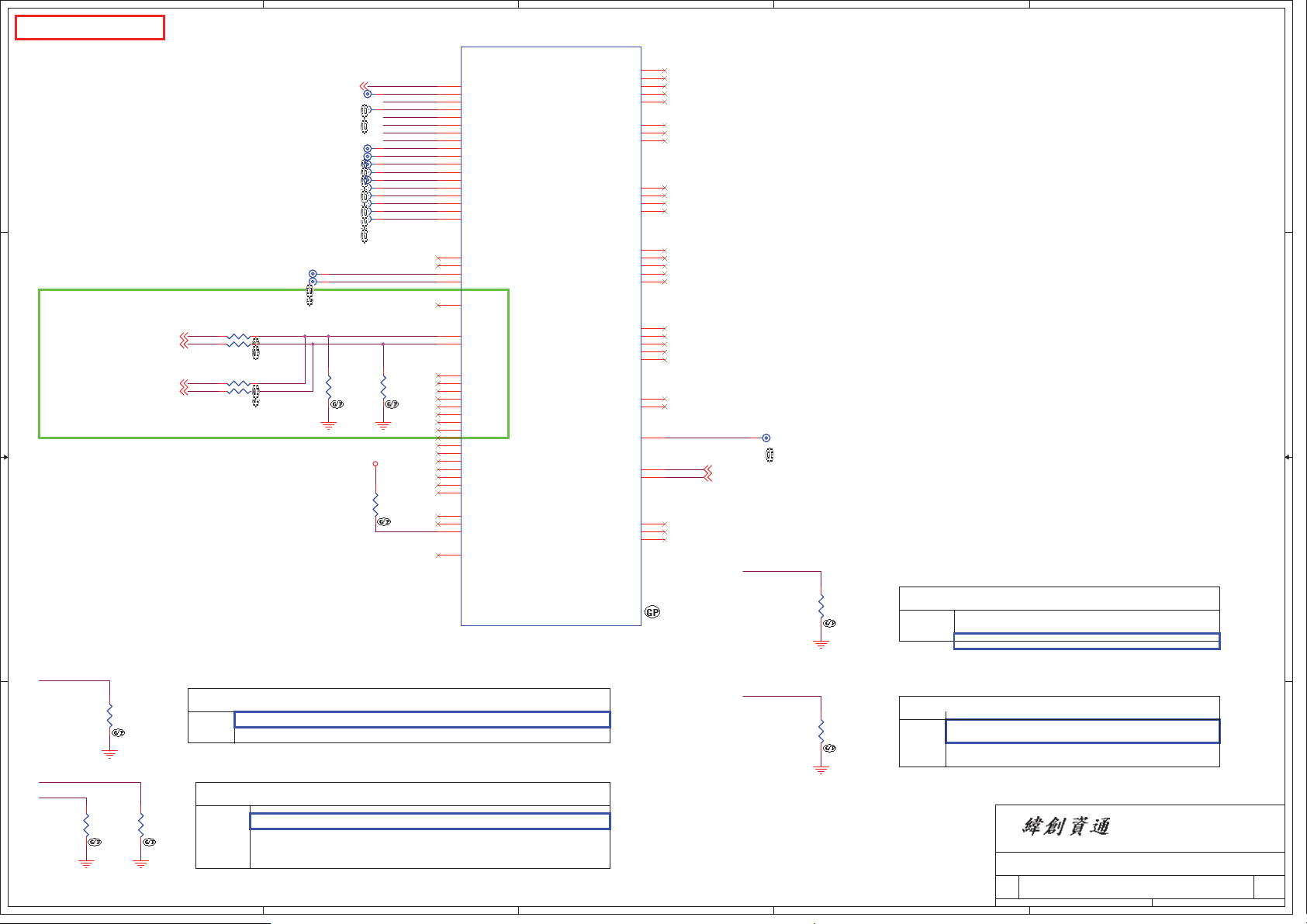

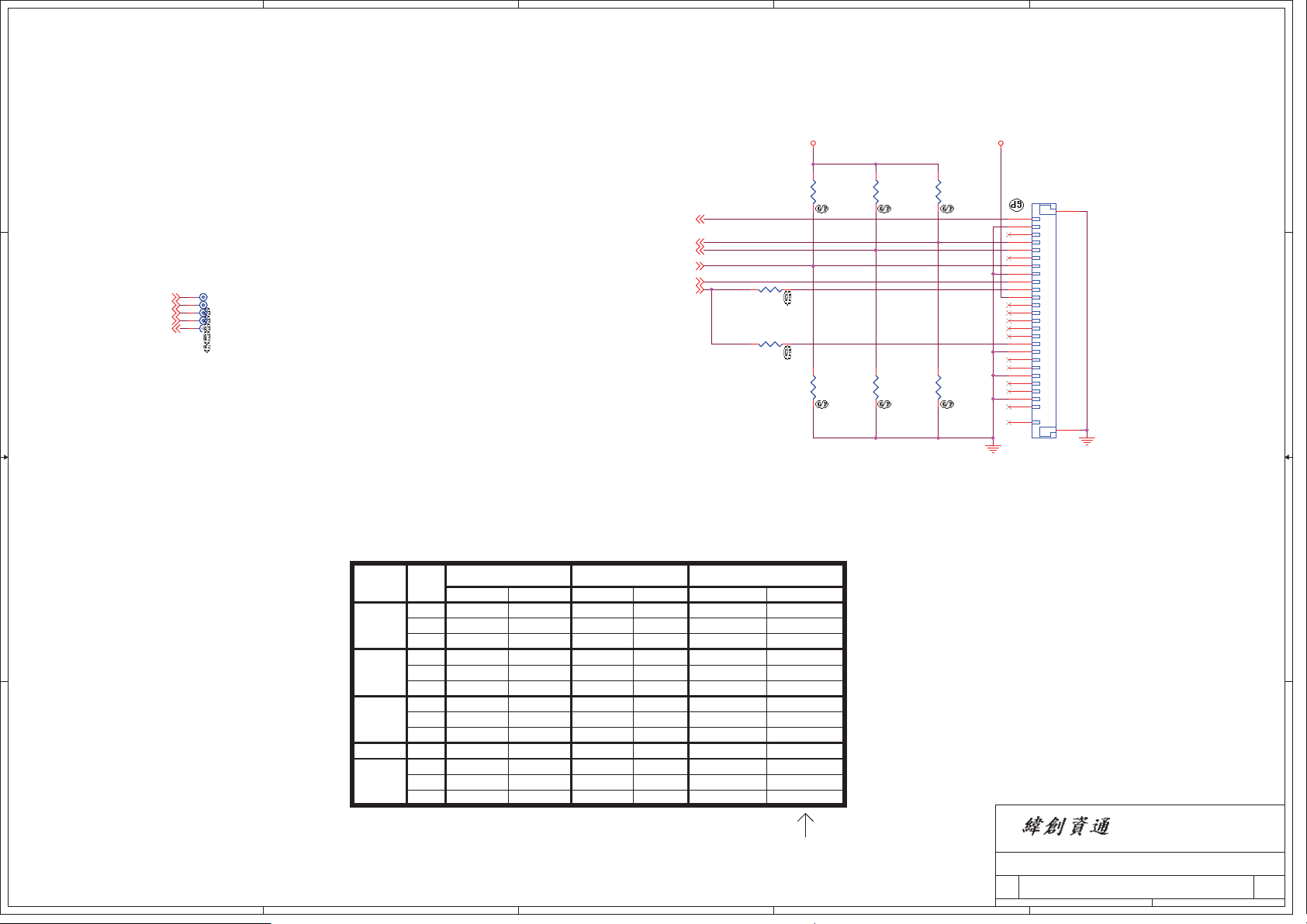

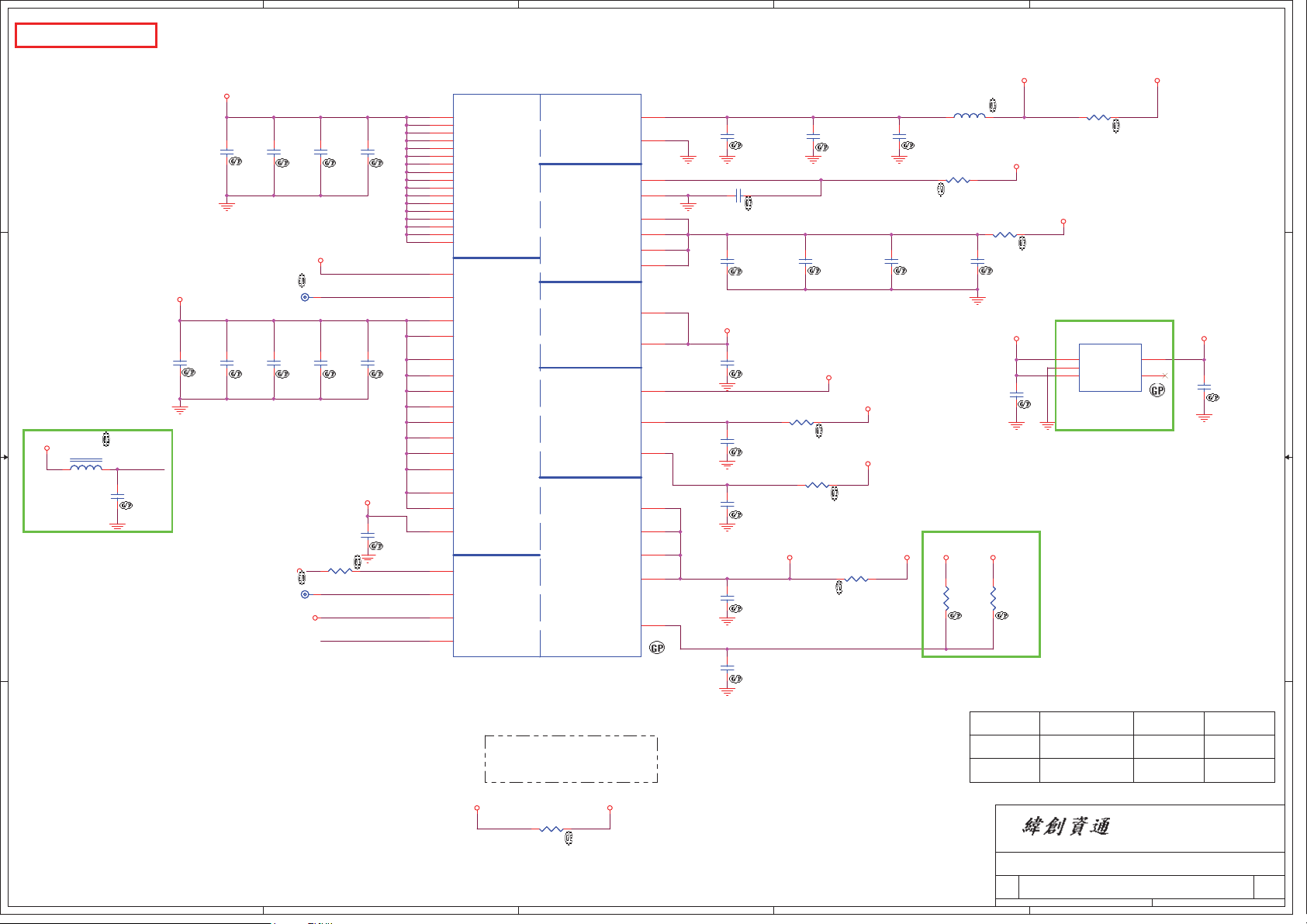

Page 4

5

4

3

2

1

SSID = CPU

Signal Routing Guideline:

PEG_ICOMPO keep W/S=12/15 mils and routing length less than 500 mils.

PEG_ICOMPI & PEG_RCOMPO keep W/S=4/15 mils and routing length less than 500 mils.

1 OF 9

CPU1A

CPU1A

D D

C C

B B

NOTE.

Processor strap CFG[4] should be pulled low to enable Embedded DisplayPort.

Note:

Intel DMI supports both Lane

Reversal and polarity inversion

but only at PCH side. This is

enabled via a soft strap.

Note:

Intel FDI supports both Lane

Reversal and polarity inversion

but only at PCH side. This is

enabled via a soft strap.

Note:

Lane reversal does not apply to

FDI sideband signals.

Signal Routing Guideline:

EDP_ICOMPO keep W/S=12/15 mils and routing

length less than 500 mils.

EDP_COMPIO keep W/S=4/15 mils and routing

length less than 500 mils.

DMI_TXN[3..0]19

DMI_TXP[3..0]19

DMI_RXN[3..0]19

DMI_RXP[3..0]19

FDI_TXN[7:0]19

FDI_TXP[7:0]19

FDI_FSYNC019

FDI_FSYNC119

FDI_INT19

FDI_LSYNC019

FDI_LSYNC119

1D05V_VTT

R402 24D9R2F-L-GPR402 24D9R2F-L-GP

1 2

R403 10KR2J-3-GP

R403 10KR2J-3-GP

1 2

DY

DY

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

DP_COMP

eDP_HPD

B27

B25

A25

B24

B28

B26

A24

B23

G21

E22

F21

D21

G22

D22

F20

C21

A21

H19

E19

F18

B21

C20

D18

E17

A22

G19

E20

G18

B20

C19

D19

F17

H20

H17

A18

A17

B16

C15

D15

C17

F16

C16

G15

C18

E16

D16

F15

J18

J17

J19

SANDY

SANDY

DMI_RX#0

DMI_RX#1

DMI_RX#2

DMI_RX#3

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

DMI_TX#0

DMI_TX#1

DMI_TX#2

DMI_TX#3

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI0_TX#0

FDI0_TX#1

FDI0_TX#2

FDI0_TX#3

FDI1_TX#0

FDI1_TX#1

FDI1_TX#2

FDI1_TX#3

FDI0_TX0

FDI0_TX1

FDI0_TX2

FDI0_TX3

FDI1_TX0

FDI1_TX1

FDI1_TX2

FDI1_TX3

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

EDP_COMPIO

EDP_ICOMPO

EDP_HPD

EDP_AUX

EDP_AUX#

EDP_TX0

EDP_TX1

EDP_TX2

EDP_TX3

EDP_TX#0

EDP_TX#1

EDP_TX#2

EDP_TX#3

SANDY

SANDY

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

1 OF 9

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_IRCOMP_R

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_C_TXN15

PEG_C_TXN14

PEG_C_TXN13

PEG_C_TXN12

PEG_C_TXN11

PEG_C_TXN10

PEG_C_TXN9

PEG_C_TXN8

PEG_C_TXN7

PEG_C_TXN6

PEG_C_TXN5

PEG_C_TXN4

PEG_C_TXN3

PEG_C_TXN2

PEG_C_TXN1

PEG_C_TXN0

PEG_C_TXP15

PEG_C_TXP14

PEG_C_TXP13

PEG_C_TXP12

PEG_C_TXP11

PEG_C_TXP10

PEG_C_TXP9

PEG_C_TXP8

PEG_C_TXP7

PEG_C_TXP6

PEG_C_TXP5

PEG_C_TXP4

PEG_C_TXP3

PEG_C_TXP2

PEG_C_TXP1

PEG_C_TXP0

R401 24D9R2F-L-GPR401 24D9R2F-L-GP

1 2

PEG_RXN[0..15]

C401 SCD1U6D3V1KX-GP

C401 SCD1U6D3V1KX-GP

1 2

PX

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

PX

C402 SCD1U6D3V1KX-GP

C402 SCD1U6D3V1KX-GP

C403 SCD1U6D3V1KX-GP

C403 SCD1U6D3V1KX-GP

C404 SCD1U6D3V1KX-GP

C404 SCD1U6D3V1KX-GP

C405 SCD1U6D3V1KX-GP

C405 SCD1U6D3V1KX-GP

C406 SCD1U6D3V1KX-GP

C406 SCD1U6D3V1KX-GP

C407 SCD1U6D3V1KX-GP

C407 SCD1U6D3V1KX-GP

C408 SCD1U6D3V1KX-GP

C408 SCD1U6D3V1KX-GP

C409 SCD1U6D3V1KX-GP

C409 SCD1U6D3V1KX-GP

C410 SCD1U6D3V1KX-GP

C410 SCD1U6D3V1KX-GP

C411 SCD1U6D3V1KX-GP

C411 SCD1U6D3V1KX-GP

C412 SCD1U6D3V1KX-GP

C412 SCD1U6D3V1KX-GP

C413 SCD1U6D3V1KX-GP

C413 SCD1U6D3V1KX-GP

C414 SCD1U6D3V1KX-GP

C414 SCD1U6D3V1KX-GP

C415 SCD1U6D3V1KX-GP

C415 SCD1U6D3V1KX-GP

C416 SCD1U6D3V1KX-GP

C416 SCD1U6D3V1KX-GP

C417 SCD1U6D3V1KX-GP

C417 SCD1U6D3V1KX-GP

C418 SCD1U6D3V1KX-GP

C418 SCD1U6D3V1KX-GP

C419 SCD1U6D3V1KX-GP

C419 SCD1U6D3V1KX-GP

C420 SCD1U6D3V1KX-GP

C420 SCD1U6D3V1KX-GP

C421 SCD1U6D3V1KX-GP

C421 SCD1U6D3V1KX-GP

C422 SCD1U6D3V1KX-GP

C422 SCD1U6D3V1KX-GP

C423 SCD1U6D3V1KX-GP

C423 SCD1U6D3V1KX-GP

C424 SCD1U6D3V1KX-GP

C424 SCD1U6D3V1KX-GP

C425 SCD1U6D3V1KX-GP

C425 SCD1U6D3V1KX-GP

C426 SCD1U6D3V1KX-GP

C426 SCD1U6D3V1KX-GP

C427 SCD1U6D3V1KX-GP

C427 SCD1U6D3V1KX-GP

C428 SCD1U6D3V1KX-GP

C428 SCD1U6D3V1KX-GP

C429 SCD1U6D3V1KX-GP

C429 SCD1U6D3V1KX-GP

C430 SCD1U6D3V1KX-GP

C430 SCD1U6D3V1KX-GP

C431 SCD1U6D3V1KX-GP

C431 SCD1U6D3V1KX-GP

C432 SCD1U6D3V1KX-GP

C432 SCD1U6D3V1KX-GP

1D05V_VTT

PEG_RXN[0..15] 83

PEG_RXP[0..15]

NOTE.

If PEG is not implemented, the RX&TX pairs can be left as No Connect

PEG Static Lane Reversal

PEG_RXP[0..15] 83

PEG_TXN15

PEG_TXN14

PEG_TXN13

PEG_TXN12

PEG_TXN11

PEG_TXN10

PEG_TXN9

PEG_TXN8

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP15

PEG_TXP14

PEG_TXP13

PEG_TXP12

PEG_TXP11

PEG_TXP10

PEG_TXP9

PEG_TXP8

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

PEG_TXN[0..15] 83

PEG_TXP[0..15] 83

Table 4.1- Central Processing Unit slot multi-source

Supplier

FOXCONN

TYCO

<Core Design>

<Core Design>

A A

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Description Lenovo P/N Wistron P/N

PZ98827-364B-41F

N/A 62.10055.421

N/A2-2013620-3

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (PCIE/DMI/FDI)

CPU (PCIE/DMI/FDI)

CPU (PCIE/DMI/FDI)

LLW-1 / LGG-1

LLW-1 / LGG-1

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

LLW-1 / LGG-1

494

494

494

62.10040.771

of

of

of

-1

-1

-1

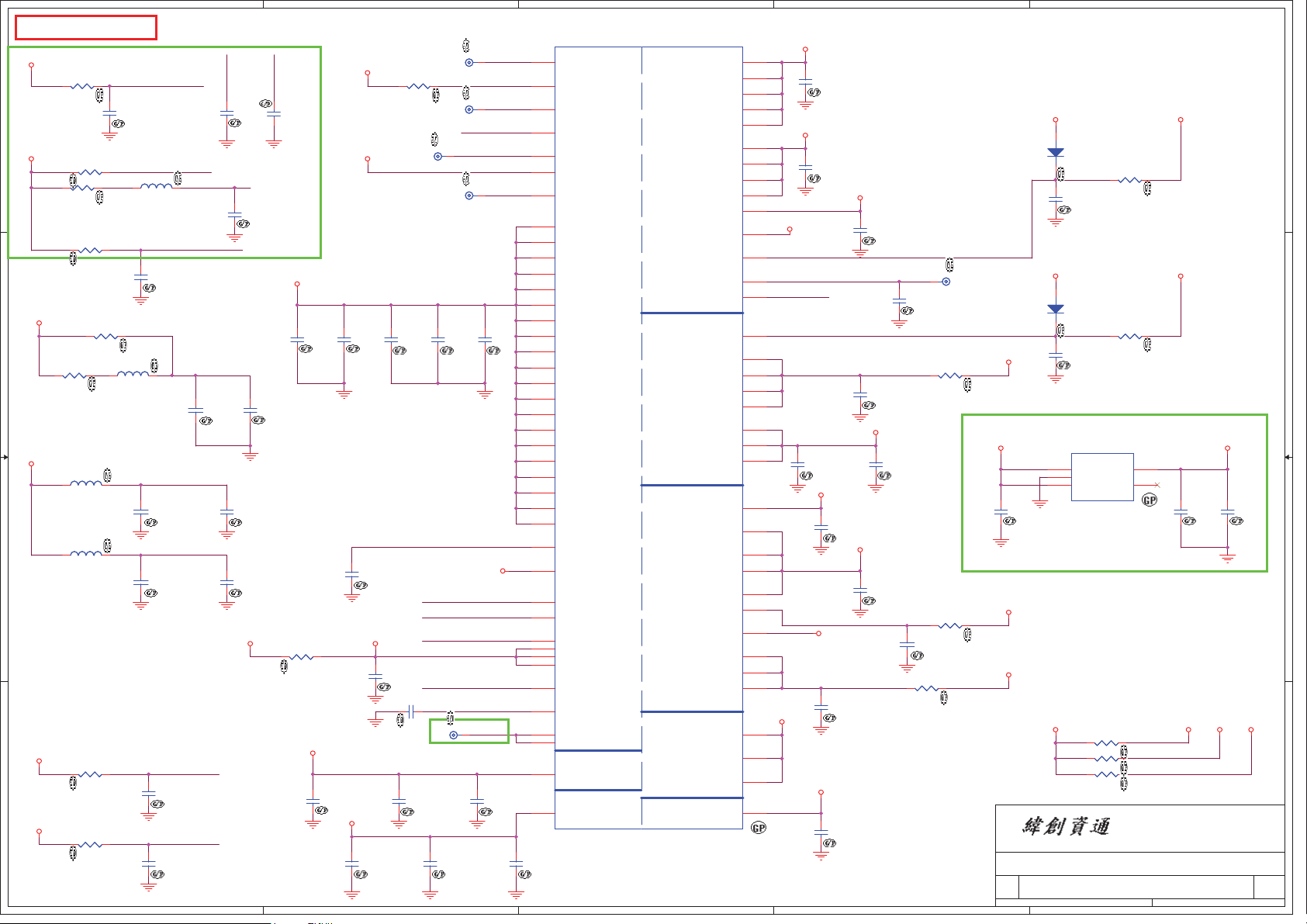

Page 5

SSID = CPU

5

1D05V_VTT

R501 62R2J-GPR501 62R2J-GP

1 2

D D

H_PROCHOT#

12

C502

C502

SC47P50V2JN-3GP

SC47P50V2JN-3GP

H_SNB_IVB#18

4

CPU1B

CPU1B

SANDY

SANDY

C26

SNB_IVB#

SKTOCC#_R

H_CATERR#

AN34

AL33

SKTOCC#

CATERR#

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

1

TP501TPAD14-GP TP501TPAD14-GP

1

TP502TPAD14-GP TP502TPAD14-GP

3

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

2 OF 9

2 OF 9

BCLK

BCLK#

A28

A27

A16

A15

CLK_DP_P_R

CLK_DP_N_R

CLK_EXP_P 20

CLK_EXP_N 20

CLK_DP_P_R 20

CLK_DP_N_R 20

2

Disabling Guidelines:

If motherboard only supports external graphics:

Connect DPLL_REF_SSCLK on Processor to GND through

1K +/- 5% resistor.

Connect DPLL_REF_SSCLK# on Processor to VCCP

through 1K +/- 5% resistorpower (~15 mW) may be

wasted.

RN502

CLK_DP_P_R

CLK_DP_N_R

RN502

1

2 3

SRN1KJ-11-GP-U

SRN1KJ-11-GP-U

DY

DY

1

1D05V_VTT

4

H_PECI22,27

R513

R513

H_PROCHOT#27,42

Connect EC to PROCHOT# through inverting OD buffer.

R506

R506

1 2

H_CPUPWRGD_R

10KR2J-3-GP

10KR2J-3-GP

C C

H_THERMTRIP#22,36,85

H_PM_SYNC19

H_CPUPWRGD22,36

PM_DRAM_PWRGD19,37

VDDPWRGOOD37

12

R502

R502

1KR2J-1-GP

1KR2J-1-GP

1 2

1 2

R504 0R2J-2-GPR504 0R2J-2-GP

R505

R505

1D05V_VTT3D3V_S0

B B

D

Q501

Q501

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2nd = 84.2N702.031

2nd = 84.2N702.031

S

G

PLT_RST#18,27,32,36,65,66,71,80,82,83

G

H_PROCHOT#_R

56R2J-4-GP

56R2J-4-GP

H_CPUPWRGD_R

DY

DY

VDDPWRGOOD XDP_TMS

1 2

12

D

0R2J-2-GP

0R2J-2-GP

BUF_PLT_RST#

R509

R509

75R2F-2-GP

75R2F-2-GP

R512

R512

43R2J-GP

43R2J-GP

1 2

Q502

Q502

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2nd = 84.2N702.031

2nd = 84.2N702.031

S

AN33

AL32

AN32

AM34

AP33

V8

AR33

BUF_PLT_RST#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

SANDY

SANDY

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

R8

SM_RCOMP_0

AK1

SM_RCOMP_1

A5

SM_RCOMP_2

A4

Signal Routing Guideline:

SM_RCOMP keep routing length less than 500 mils.

AP29

PRDY#

AP27

PREQ#

AR26

TCK

AR27

TMS

AP30

TRST#

AR28

TDI

AP26

TDO

AL35

DBR#

XDP_BPM0

AT28

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

XDP_BPM1

AR29

XDP_BPM2

AR30

XDP_BPM3

AT30

XDP_BPM4

AP32

XDP_BPM5

AR31

XDP_BPM6

AT31

XDP_BPM7

AR32

XDP_DBRESET#

XDP_PREQ#

XDP_PRDY#

XDP_TDO

XDP_TDI

XDP_TRST#

XDP_TCLK

XDP_TMS

R508 140R2F-GPR508 140R2F-GP

R507 25D5R2F-GPR507 25D5R2F-GP

R510 200R2F-L-GPR510 200R2F-L-GP

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_DBRESET#

1

1

1

1

1

1

1

1

1 2

1 2

1 2

TP503TP503

TP504TP504

TP505TP505

TP506TP506

TP507TP507

TP508TP508

TP509TP509

TP510TP510

XDP_DBRESET# 11,19

XDP_PREQ# 11

XDP_PRDY# 11

1

TP511TP511

1

TP512TP512

1

TP513TP513

1

TP514TP514

1

TP515TP515

SM_DRAMRST# 37

R503

R503

4K99R2F-L-GP

4K99R2F-L-GP

1 2

XDP_TDI

XDP_TDO

XDP_TCLK

XDP_TRST#

R511 51R2J-2-GPR511 51R2J-2-GP

1 2

XDP_DBRESET#

Table 5.1- N-Channel MOSFET multi-source

Supplier

PANJIT

Description Lenovo P/N Wistron P/N

2N7002K

DIODES

1D05V_VTT

RN501

RN501

4 5

3

6

2

7

1

8

SRN51J-1-GP

SRN51J-1-GP

R516 1KR2J-1-GPR516 1KR2J-1-GP

1 2

N/A 84.2N702.J31

N/A2N7002K

3D3V_S0

84.2N702.031

84.07002.I31NXP N/A2N7002BK

<Core Design>

<Core Design>

A A

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (Thermal/CLK/PM)

CPU (Thermal/CLK/PM)

CPU (Thermal/CLK/PM)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

of

594Tuesday, January 18, 2011

of

594Tuesday, January 18, 2011

of

594Tuesday, January 18, 2011

-1

-1

-1

Page 6

5

4

3

2

1

SSID = CPU

4 OF 9

3 OF 9

CPU1C

CPU1C

SANDY

SANDY

M_A_DQ[63:0]14 M_B_DQ[63:0]15

D D

C C

B B

M_A_DQ[63:0]

M_A_BS014

M_A_BS114

M_A_BS214

M_A_CAS#14

M_A_RAS#14

M_A_WE#14

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

C5

SA_DQ0

D5

SA_DQ1

D3

SA_DQ2

D2

SA_DQ3

D6

SA_DQ4

C6

SA_DQ5

C2

SA_DQ6

C3

SA_DQ7

F10

SA_DQ8

F8

SA_DQ9

SA_DQ10

G9

SA_DQ11

F9

SA_DQ12

F7

SA_DQ13

G8

SA_DQ14

G7

SA_DQ15

K4

SA_DQ16

K5

SA_DQ17

K1

SA_DQ18

J1

SA_DQ19

J5

SA_DQ20

J4

SA_DQ21

J2

SA_DQ22

K2

SA_DQ23

M8

SA_DQ24

SA_DQ25

N8

SA_DQ26

N7

SA_DQ27

SA_DQ28

M9

SA_DQ29

N9

SA_DQ30

M7

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

AJ5

SA_DQ38

AJ6

SA_DQ39

AJ8

SA_DQ40

SA_DQ41

AJ9

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

V6

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

3 OF 9

SA_CLK0

SA_CLK#0

SA_CKE0

SA_CLK1

SA_CLK#1

SA_CKE1

SA_CLK2

SA_CLK#2

SA_CKE2

SA_CLK3

SA_CLK#3

SA_CKE3

SA_CS#0

SA_CS#1

SA_CS#2

SA_CS#3

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_A_DIM0_CLK_DDR0 14

M_A_DIM0_CLK_DDR#0 14

M_A_DIM0_CKE0 14

M_A_DIM0_CLK_DDR1 14

M_A_DIM0_CLK_DDR#1 14

M_A_DIM0_CKE1 14

M_A_DIM0_CS#0 14

M_A_DIM0_CS#1 14

M_A_DIM0_ODT0 14

M_A_DIM0_ODT1 14

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#[7:0] 14

M_A_DQS[7:0] 14

M_A_A[15:0] 14

M_B_DQ[63:0]

M_B_BS015

M_B_BS115

M_B_BS215

M_B_CAS#15

M_B_RAS#15

M_B_WE#15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

CPU1D

CPU1D

SANDY

SANDY

C9

SB_DQ0

A7

SB_DQ1

SB_DQ2

C8

SB_DQ3

A9

SB_DQ4

A8

SB_DQ5

D9

SB_DQ6

D8

SB_DQ7

G4

SB_DQ8

F4

SB_DQ9

F1

SB_DQ10

G1

SB_DQ11

G5

SB_DQ12

F5

SB_DQ13

F2

SB_DQ14

G2

SB_DQ15

J7

SB_DQ16

J8

SB_DQ17

SB_DQ18

K9

SB_DQ19

J9

SB_DQ20

J10

SB_DQ21

K8

SB_DQ22

K7

SB_DQ23

M5

SB_DQ24

N4

SB_DQ25

N2

SB_DQ26

N1

SB_DQ27

M4

SB_DQ28

N5

SB_DQ29

M2

SB_DQ30

M1

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

R6

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

SB_BS1

SB_BS2

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

4 OF 9

SB_CLK0

SB_CLK#0

SB_CKE0

SB_CLK1

SB_CLK#1

SB_CKE1

SB_CLK2

SB_CLK#2

SB_CKE2

SB_CLK3

SB_CLK#3

SB_CKE3

SB_CS#0

SB_CS#1

SB_CS#2

SB_CS#3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

AE2

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

M_B_DIM0_CLK_DDR0 15

M_B_DIM0_CLK_DDR#0 15

M_B_DIM0_CKE0 15

M_B_DIM0_CLK_DDR1 15

M_B_DIM0_CLK_DDR#1 15

M_B_DIM0_CKE1 15

M_B_DIM0_CS#0 15

M_B_DIM0_CS#1 15

M_B_DIM0_ODT0 15

M_B_DIM0_ODT1 15

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQS#[7:0] 15

M_B_DQS[7:0] 15

M_B_A[15:0] 15

SANDY

SANDY

SANDY

A A

5

4

3

SANDY

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (DDR)

CPU (DDR)

CPU (DDR)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Date: Sheet

Date: Sheet

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

1

-1

-1

of

694

of

694

of

694

-1

Page 7

5

4

3

2

1

SSID = CPU

CFG011

TP701TP701

D D

TP714TP714

TP715TP715

TP702TP702

TP703TP703

TP704TP704

TP705TP705

TP706TP706

TP707TP707

TP708TP708

TP709TP709

TP710TP710

TP711TP711

TP712TP712

VCC_VALIDATION_SENSE

1

VSS_VALIDATION_SENSE

1

M3 - Processor Generated SO-DIMM VREF_DQ

DY

DY

R708 0R2J-2-GP

R708 0R2J-2-GP

M_VREF_DQ_DIMM014,37

C C

B B

M_VREF_DQ_DIMM115

M_VREF_CA_DIMM014

M_VREF_CA_DIMM115

1 2

R709 0R2J-2-GP

R709 0R2J-2-GP

1 2

DY

DY

DY

DY

R707 0R2J-2-GP

R707 0R2J-2-GP

1 2

R706 0R2J-2-GP

R706 0R2J-2-GP

1 2

DY

DY

12

R711

R711

1KR2F-3-GP

1KR2F-3-GP

CFG0

CFG1

1

CFG2

CFG3

1

CFG4

CFG5

CFG6

CFG7

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

1

CFG13

1

CFG14

1

CFG15

1

CFG16

1

CFG17

1

B4:VREF_DQ CHA

M_VREF_DQ_DIMM0_C

M_VREF_CA_DIMM0_CM_VREF_CA_DIMM0_C

D1:VREF_DQ CHB

12

R712

R712

1KR2F-3-GP

1KR2F-3-GP

3D3V_S5

20 mils

12

R710

R710

10KR2J-3-GP

10KR2J-3-GP

H_VCCP_SEL

AK28

AK29

AL26

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

AJ31

AH31

AJ33

AH33

AJ26

F25

F24

F23

D24

G25

G24

E23

D23

C30

A31

B30

B29

D30

B31

A30

C29

B18

A19

B4

D1

J20

J15

CPU1E

CPU1E

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

RSVD#AJ31

RSVD#AH31

RSVD#AJ33

RSVD#AH33

RSVD#AJ26

RSVD#B4

RSVD#D1

RSVD#F25

RSVD#F24

RSVD#F23

RSVD#D24

RSVD#G25

RSVD#G24

RSVD#E23

RSVD#D23

RSVD#C30

RSVD#A31

RSVD#B30

RSVD#B29

RSVD#D30

RSVD#B31

RSVD#A30

RSVD#C29

RSVD#J20

RSVD#B18

RSVD#A19

RSVD#J15

SANDY

SANDY

SANDY

SANDY

RESERVED

RESERVED

5 OF 9

5 OF 9

RSVD#L7

RSVD#AG7

RSVD#AE7

RSVD#AK2

RSVD#W8

RSVD#AT26

RSVD#AM33

RSVD#AJ27

RSVD#T8

RSVD#J16

RSVD#H16

RSVD#G16

RSVD#AR35

RSVD#AT34

RSVD#AT33

RSVD#AP35

RSVD#AR34

RSVD#B34

RSVD#A33

RSVD#A34

RSVD#B35

RSVD#C35

RSVD#AJ32

RSVD#AK32

RSVD#AH27

RSVD#AN35

RSVD#AM35

RSVD#AT2

RSVD#AT1

RSVD#AR1

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AH27

AN35

AM35

AT2

AT1

AR1

VCC_DIE_SENSE

PCIE_CLK_XDP_P 11,20

PCIE_CLK_XDP_N 11,20

1

CFG2

TP716TP716

12

PX

PX

R702

R702

1KR2J-1-GP

1KR2J-1-GP

PEG Static Lane Reversal

CFG2

1: Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

CFG7

12

DY

DY

R705

R705

1KR2J-1-GP

1KR2J-1-GP

CFG5

CFG6

A A

12

DY

DY

R701

R701

1KR2J-1-GP

1KR2J-1-GP

12

DY

DY

R704

R704

1KR2J-1-GP

1KR2J-1-GP

5

PEG DEFER TRAINING

CFG7

1: PEG Train immediately following xxRESETB de assertion

0: PEG Wait for BIOS for training

PCIE Port Bifurcation Straps

CFG[6:5]

11: x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

4

3

CFG4

12

DY

DY

R703

R703

1KR2J-1-GP

1KR2J-1-GP

Display Port Presence Strap

CFG4

2

1: Disabled; No Physical Display Port

attached to Embedded Display Port

0: Enabled; An external Display Port device is

connected to the Embedded Display Port

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU (RESERVED)

CPU (RESERVED)

CPU (RESERVED)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Date: Sheet

Date: Sheet

Date: Sheet

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

1

-1

-1

of

794

of

794

of

794

-1

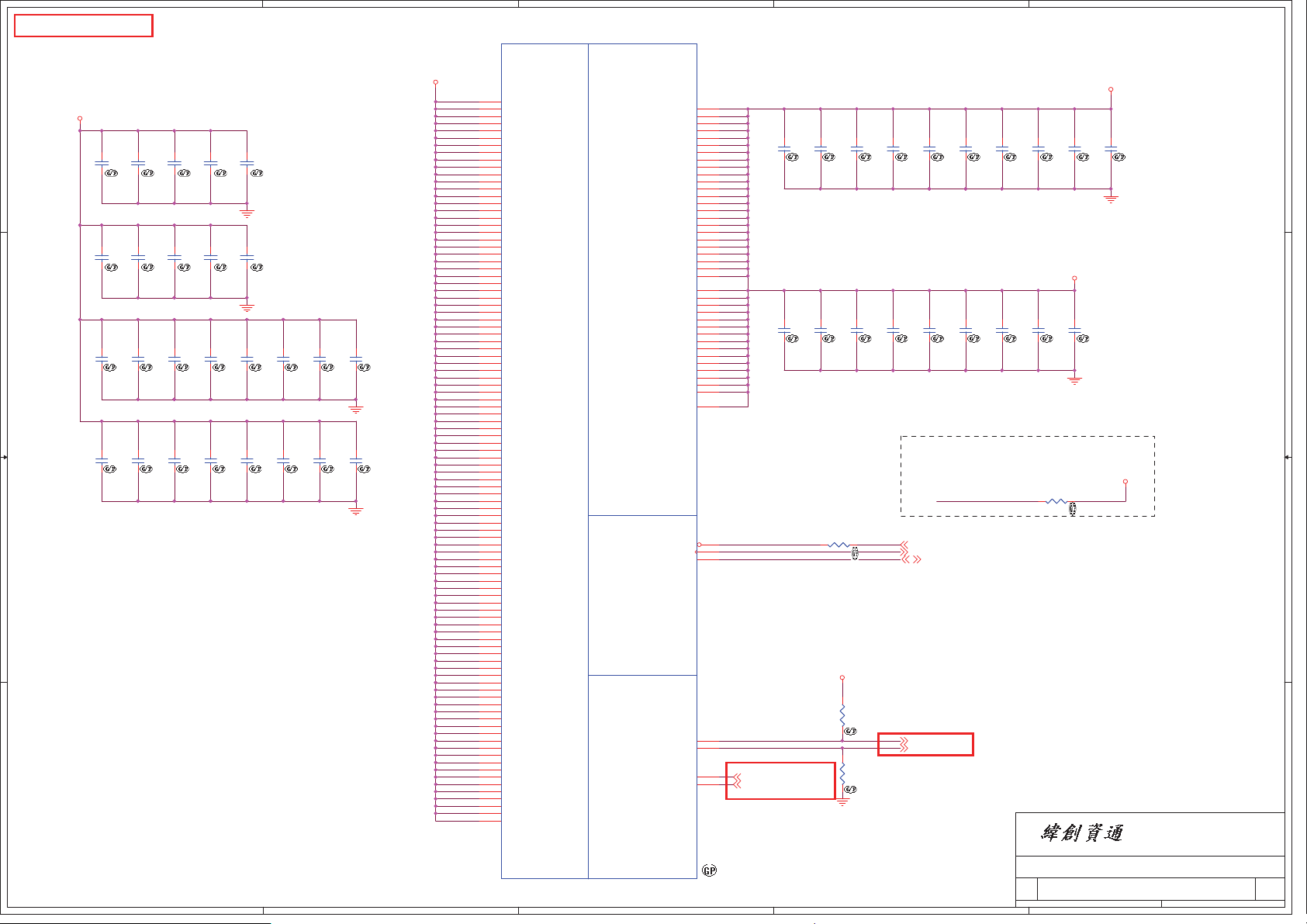

Page 8

5

SSID = CPU

PROCESSOR CORE POWER

53A

D D

C C

B B

A A

VCC_CORE

12

C801

C801

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C815

C815

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C816

C816

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C837

C837

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VCC Output Decoupling Recommendation:

4 x 470 uF at Bottom Socket Edge

8 x 22 uF at Top Socket Cavity

8 x 22 uF at Top Socket Edge

8 x 22 uF at Bottom Socket Cavity

12

12

C803

C803

C802

C802

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C818

C818

C817

C817

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C821

C821

C822

C822

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C836

C836

C835

C835

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

5

12

12

C804

C804

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C819

C819

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C823

C823

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C834

C834

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C811

C811

C820

C820

C824

C824

C833

C833

12

12

C826

C826

C825

C825

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C832

C832

C831

C831

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

4

POWER

CPU1F

CPU1F

VCC_CORE

AG35

VCC

AG34

VCC

AG33

VCC

AG32

VCC

AG31

VCC

AG30

VCC

AG29

VCC

AG28

VCC

AG27

VCC

AG26

VCC

AF35

VCC

AF34

VCC

AF33

VCC

AF32

VCC

AF31

VCC

AF30

VCC

AF29

VCC

AF28

VCC

AF27

VCC

AF26

VCC

AD35

VCC

AD34

VCC

AD33

VCC

AD32

VCC

AD31

VCC

AD30

VCC

AD29

VCC

AD28

VCC

AD27

VCC

AD26

VCC

AC35

VCC

AC34

VCC

AC33

VCC

AC32

VCC

12

C827

C827

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C828

C828

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

4

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y35

VCC

Y34

VCC

Y33

VCC

Y32

VCC

Y31

VCC

Y30

VCC

Y29

VCC

Y28

VCC

Y27

VCC

Y26

VCC

V35

VCC

V34

VCC

V33

VCC

V32

VCC

V31

VCC

V30

VCC

V29

VCC

V28

VCC

V27

VCC

V26

VCC

U35

VCC

U34

VCC

U33

VCC

U32

VCC

U31

VCC

U30

VCC

U29

VCC

U28

VCC

U27

VCC

U26

VCC

R35

VCC

R34

VCC

R33

VCC

R32

VCC

R31

VCC

R30

VCC

R29

VCC

R28

VCC

R27

VCC

R26

VCC

P35

VCC

P34

VCC

P33

VCC

P32

VCC

P31

VCC

P30

VCC

P29

VCC

P28

VCC

P27

VCC

P26

VCC

SANDY

SANDY

POWER

SANDY

SANDY

CORE SUPPLY

CORE SUPPLY

3

6 OF 9

6 OF 9

AH13

VCCIO

AH10

VCCIO

AG10

VCCIO

AC10

VCCIO

Y10

VCCIO

U10

VCCIO

P10

VCCIO

L10

VCCIO

J14

VCCIO

J13

VCCIO

J12

VCCIO

J11

VCCIO

H14

VCCIO

H12

VCCIO

H11

VCCIO

G14

VCCIO

G13

VCCIO

G12

VCCIO

F14

VCCIO

F13

VCCIO

F12

VCCIO

F11

VCCIO

E14

VCCIO

E12

VCCIO

E11

VCCIO

D14

VCCIO

D13

VCCIO

D12

VCCIO

D11

VCCIO

C14

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VIDALERT#

VIDSCLK

VIDSOUT

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

PEG AND DDR

PEG AND DDR

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

SENSE LINES SVID

SENSE LINES SVID

3

VCCIO Output Decoupling Recommendation:

2 x 330 uF (3 x 330 uF for 2012 capable designs)

5 x 22 uF & 5 x 0805 no-stuff at Bottom

7 x 22 uF & 2 x 0805 no-stuff at Top

12

12

C806

C806

C805

C805

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

No-stuff sites outside the socket may be removed.

No-stuff sites inside the socket cavity need to remain.

12

C812

C812

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

For CRB VIDSOUT need to pull high 130 ohm closr to CPU and IMVP7

For CRB VIDALERT# need to pull high 75 ohm close to CPU

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

R803 43R2J-GPR803 43R2J-GP

R801, R802 need to close to CPU

VCCIO_SENSE 45

VSSIO_SENSE 45

12

C813

C813

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1 2

VCC_CORE

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

R801

R801

100R2F-L1-GP-U

100R2F-L1-GP-U

12

R802

R802

100R2F-L1-GP-U

100R2F-L1-GP-U

2

1D05V_VTT

12

12

C807

C807

12

C814

C814

12

12

C808

C808

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C829

C829

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C809

C809

12

C830

C830

H_CPU_SVIDDAT

C810

C810

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C842

C842

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C839

C839

C838

C838

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1D05V_VTT

12

12

C844

C844

C843

C843

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

R804 130R2F-1-GPR804 130R2F-1-GP

1 2

12

C840

C840

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C845

C845

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1D05V_VTT

1

12

C841

C841

S-HS_20100610 V1.0

VR_SVID_ALERT# 42

H_CPU_SVIDCLK 42

H_CPU_SVIDDAT 42

VCCSENSE 42

VSSSENSE 42

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., H s ichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H s ichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H s ichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Date: Sheet

Date: Sheet

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

1

-1

-1

-1

of

894

of

894

of

894

Page 9

5

VAXG Output Decoupling Recommendation:

SSID = CPU

VCC_GFXCORE

2 x 470 uF at Bottom Socket Edge

2 x 22 uF at Top Socket Cavity

4 x 22 uF at Top Socket Edge

2 x 22 uF at Bottom Socket Cavity

4 x 22 uF at Bottom Socket Edge

PROCESSOR VAXG: 24A

D D

12

C901

C901

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C907

C907

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C C

Disabling Guidelines for External Graphics Designs:

Can connect to GND if motherboard only supports external

graphics and if GFX VR is not stuffed.

Can be left floating (Gfx VR keeps VAXG rail from floating)

B B

if the VR is stuffed

12

12

12

C903

C903

C902

C902

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C918

C918

C908

C908

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1D8V_S0

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VCCPLL Output Decoupling Recommendation:

1 x 330 uF

2 x 1 uF

1 x 10 uF

4

12

12

12

C904

C904

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C919

C919

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C905

C905

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C920

C920

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C906

C906

C921

C921

PROCESSOR VCCPLL: 1.2A

12

12

C925

C925

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C923

C923

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C922

C922

SC1U10V2KX-1GP

SC1U10V2KX-1GP

3

POWER

CPU1G

CPU1G

AT24

VAXG

AT23

VAXG

AT21

VAXG

AT20

VAXG

AT18

VAXG

AT17

VAXG

AR24

VAXG

AR23

VAXG

AR21

VAXG

AR20

VAXG

AR18

VAXG

AR17

VAXG

AP24

VAXG

AP23

VAXG

AP21

VAXG

AP20

VAXG

AP18

VAXG

AP17

VAXG

AN24

VAXG

AN23

VAXG

AN21

VAXG

AN20

VAXG

AN18

VAXG

AN17

VAXG

AM24

VAXG

AM23

VAXG

AM21

VAXG

AM20

VAXG

AM18

VAXG

AM17

VAXG

AL24

VAXG

AL23

VAXG

AL21

VAXG

AL20

VAXG

AL18

VAXG

AL17

VAXG

AK24

VAXG

AK23

VAXG

AK21

VAXG

AK20

VAXG

AK18

VAXG

AK17

VAXG

AJ24

VAXG

AJ23

VAXG

AJ21

VAXG

AJ20

VAXG

AJ18

VAXG

AJ17

VAXG

AH24

VAXG

AH23

VAXG

AH21

VAXG

AH20

VAXG

AH18

VAXG

AH17

VAXG

B6

VCCPLL

A6

VCCPLL

A2

12

C924

C924

VCCPLL

SANDY

SANDY

POWER

SANDY

SANDY

GRAPHICS

GRAPHICS

1.8V RAIL

1.8V RAIL

SENSE

SENSE

VREFMISC

VREFMISC

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

7 OF 9

7 OF 9

VAXG_SENSE

VSSAXG_SENSE

LINES

LINES

SM_VREF

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA_SENSE

FC_C22

VCCSA_VID1

AK35

AK34

VCC_AXG_SENSE 42

VSS_AXG_SENSE 42

Refer to the latest Huron River Mainstream PDG

(Doc# 436735) for more details on S3 power

reduction implementation.

+V_SM_VREF_CNT should have 10 mil trace width

+V_SM_VREF_CNT

AL1

Routing Guideline:

Power from DDR_VREF_S3 and +V_SM_VREF_CNT

should have 10 mils trace width.

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C909

C909

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

+V_SM_VREF_CNT 37

PROCESSOR VDDQ: 10A

C910

C910

PROCESSOR VCCSA: 6A

12

C916

C916

M27

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

RN901

RN901

SRN1KJ-7-GP

SRN1KJ-7-GP

VCCSA_SENSE

H_FC_C22

VCCSA_SEL

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

0D85V_S0

12

1

23

4

R902

R902

10R2J-2-GP

10R2J-2-GP

H_FC_C22 48

VCCSA_SEL 48

2

R906,R907 close to CPU

1D5V_S0

12

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C911

C911

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C915

C915

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C912

C912

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

0D85V_S0

12

C917

C917

R902 need be close to pin H23.

VCCSA_SENSE 48

12

12

12

C914

C914

C913

C913

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VDDQ Output Decoupling Recommendation:

1 x 330 uF

6 x 10 uF

TC903

TC903

ST330U2VDM-4-GP

ST330U2VDM-4-GP

VCCSA Output Decoupling Recommendation:

1 x 330 uF

2 x 10 uF at Bottom Socket Cavity

1 x 10 uF at Bottom Socket Edge

VCC_GFXCORE

VCC_AXG_SENSE

VSS_AXG_SENSE

S-HR_20100609 V1.0

1

12

12

R906

R906

100R2F-L1-GP-U

100R2F-L1-GP-U

R907

R907

100R2F-L1-GP-U

100R2F-L1-GP-U

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

1

of

994

of

994

of

994

-1

-1

-1

Page 10

5

4

3

2

1

SSID = CPU

9 OF 9

8 OF 9

CPU1H

CPU1H

AT35

VSS

AT32

VSS

AT29

VSS

AT27

VSS

AT25

VSS

AT22

VSS

D D

C C

B B

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SANDY

SANDY

VSS

VSS

8 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

M34

H33

H30

H27

H24

H21

H18

H15

H13

H10

G35

G32

G29

G26

G23

G20

G17

G11

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

L33

L30

L27

K35

K32

K29

K26

J34

J31

F34

F31

F29

CPU1I

CPU1I

SANDY

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P9

VSS

P8

VSS

P6

VSS

P5

VSS

P3

VSS

P2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L9

VSS

L8

VSS

L6

VSS

L5

VSS

L4

VSS

L3

VSS

L2

VSS

L1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H9

VSS

H8

VSS

H7

VSS

H6

VSS

H5

VSS

H4

VSS

H3

VSS

H2

VSS

H1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SANDY

VSS

VSS

9 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

SANDY

SANDY

SANDY

A A

5

4

3

SANDY

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Tuesday, January 18, 2011

Date: Sheet

Date: Sheet

2

Date: Sheet

CPU (VSS)

CPU (VSS)

CPU (VSS)

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

Taipei Hsien 221, Taiwan, R.O.C.

of

10 94

of

10 94

of

10 94

1

-1

-1

-1

Page 11

5

4

3

2

1

D D

12

DY

DY

R1110

R1110

200R2J-L1-GP

200R2J-L1-GP

PCH_TCK21

PCH_TMS21

PCH_TDI21

PCH_TDO21

XDP_DBRESET#5,19

PCIE_CLK_XDP_N7,20

PCIE_CLK_XDP_P7,20

XDP_PRDY#5

XDP_PREQ#5

C C

1

TP1101TP1101

1

TP1102TP1102

1

CFG07

TP1103TP1103

1

TP1104TP1104

1

TP1105TP1105

PM_RSMRST#19

R1124 1KR2J-1-GP

R1124 1KR2J-1-GP

1 2

DY

DY

R1123 1KR2J-1-GP

R1123 1KR2J-1-GP

1 2

DY

DY

12

DY

DY

R1116

R1116

100R2J-2-GP

100R2J-2-GP

12

DY

DY

R1111

R1111

200R2J-L1-GP

200R2J-L1-GP

12

DY

DY

R1117

R1117

100R2J-2-GP

100R2J-2-GP

12

12

DEBUG Interface for Processor.

CPU XDP SFF 26pin IF

Pin 1 OBSFN_A0 (PREQ#, I/O)

Pin 2 OBSFN_A1 (PRDY#, I/O)

Pin 3 GND

Pin 4 OBSDATA_A0 (Open, I/O)

B B

A A

Pin 5 OBSDATA_A1 (Open, I/O)

Pin 6 GND

Pin 7 OBSDATA_A2 (Open, I/O)

Pin 8 OBSDATA_A3 (Open, I/O)

Pin 9 GND

Pin 10 HOOK0 (PWRGD, In)

Pin 11 HOOK1 (BP_PWRGD_RST#, Out)

Pin 12 HOOK2 (CFG0, Out)

Pin 13 HOOK3 (vr_READYSYS_PWROK,Out)

Pin 14 HOOK4 (BCLK, In)

Pin 15 HOOK5 (BCLK#, In)

Pin 16 VCCOBS_AB (VCCP Voltage of CPU, In)

Pin 17 HOOK6 (RESET#, Out)

Pin 18 HOOK7 (DBR#, Out)

Pin 19 GND

Pin 20 TDO, In

Pin 21 TRST#, Out

Pin 22 TDI, Out

Pin 23 TMS, Out

Pin 24 TCK1 (Open)

Pin 25 GND

Pin 26 TCK0 ,Out

TABLE

PCH

PIN

TDO

TMS

TDI

TCK

TRST#

REF

DES

R1110

R1116

R2

R1112

R1118

R91

R1111

R1117

R90

R541

R953

R535

R103

PCH ES1 JTAG

Enable EnableDisable Disable

DY

DY

DY DY DY DY 51 Ohms

200 Ohms

DY DY

200 Ohms

100 Ohms

DY DY

51 Ohms 51 Ohms

20K Ohms

10K Ohms

DY DY

DY

DY

DY

DY

20K Ohms

10K Ohms

DY

DY

PCH ES2 JTAG

200 Ohms

100 Ohms

200 Ohms

100 Ohms100 Ohms

DY DY

200 Ohms

100 Ohms

51 Ohms 51 Ohms

DY

DY

DY DY

DY

DY

DY

DY

DY

DY

DYDY

DY

DY

PRODUCTION

Enable Disable

DY

DY

DY

DY

51 Ohms

DY

DY

51 Ohms

51 Ohms

DY

DY

DY

DY

DY

DY

DY

DY

DY

DY

DY

DY

51 Ohms

DY

DY

DY

3D3V_S53D3V_S5

DY

DY

R1112

R1112

200R2J-L1-GP

200R2J-L1-GP

DY

DY

R1118

R1118

100R2J-2-GP

100R2J-2-GP

XDP1102

XDP1102

28

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

27

MLX-CON26-8-GP

MLX-CON26-8-GP

DY

DY

DEBUG Interfac e for PCH.

PCH XDP SFF 26pin IF

Pin 1 OBSFN_A0 (Open), I/O)

Pin 2 OBSFN_A1 (Open, I/O)

Pin 3 GND

Pin 4 OBSDATA_A0 (Open, I/O)

Pin 5 OBSDATA_A1 (Open, I/O)

Pin 6 GND

Pin 7 OBSDATA_A2 (Open, I/O)

Pin 8 OBSDATA_A3 (Open, I/O)

Pin 9 GND

Pin 10 HOOK0 (RSMRST#, In)

Pin 11 HOOK1 (BP_PWRGD_RST#, Out)

Pin 12 HOOK2 (Open)

Pin 13 HOOK3 (Open)

Pin 14 HOOK4 (Open)

Pin 15 HOOK5 (Open)

Pin 16 VCCOBS_AB (3.3VSUS, In)

Pin 17 HOOK6 (RSMRST#, Out)

Pin 18 HOOK7 (DBR#, Out)

Pin 19 GND

Pin 20 TDO (JTAG, In)

Pin 21 TRST# (Open)

Pin 22 TDI (JTAG, Out)

Pin 23 TMS (JTAG, Out)

Pin 24 TCK1 (Open)

Pin 25 GND

Pin 26 TCK0 (JTAG, Out)

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

LOGIC

5

4

3

2

Title

Title

Title

XDP CONN

XDP CONN

XDP CONN

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

1

-1

-1

of

11 94Tuesday, January 18, 2011

of

11 94Tuesday, January 18, 2011

of

11 94Tuesday, January 18, 2011

-1

Page 12

5

D D

C C

4

3

2

1

BLANK

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

5

4

3

Date: Sheet

2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Reserved

Reserved

Reserved

LLW-1 / LGG-1

LLW-1 / LGG-1

LLW-1 / LGG-1

12 94Tuesday, January 18, 2011

12 94Tuesday, January 18, 2011

12 94Tuesday, January 18, 2011

1

-1

-1

-1

of

of

of

Page 13

A

4 4

3 3

B

C

D

E

BLANK

2 2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

1 1

Title

Title