Page 1

5

D D

C C

4

3

2

1

LF14M

Schematics Document

B B

A A

Eletro-X

5

4

3

2

M40

Tiiitllle

DocumentNumber

Siiize

A3

Wednesday, February 26,2014

Date:

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

CoverPage

LF14M

Sheet 1

1

Rev

-1

102

of

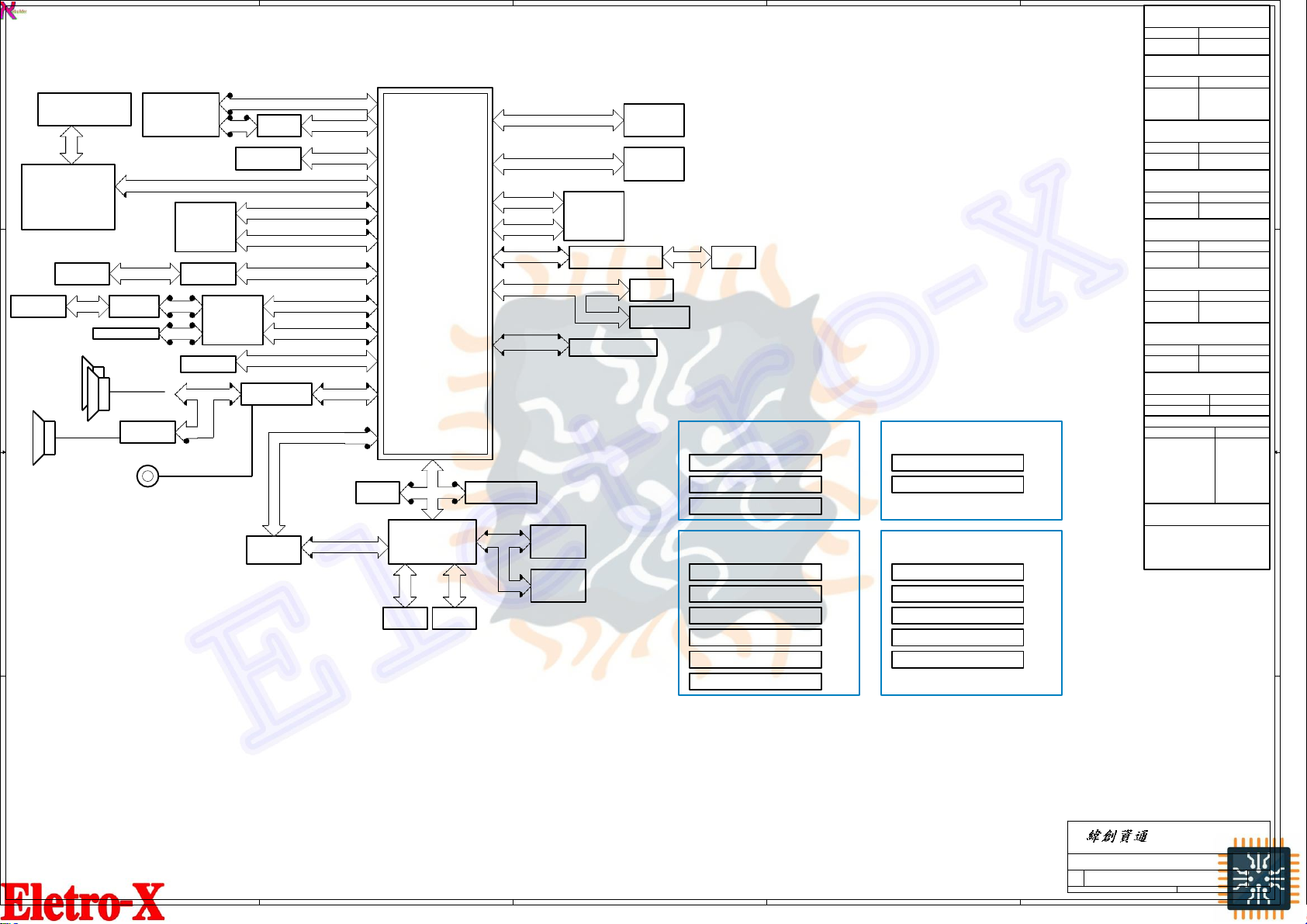

Page 2

5

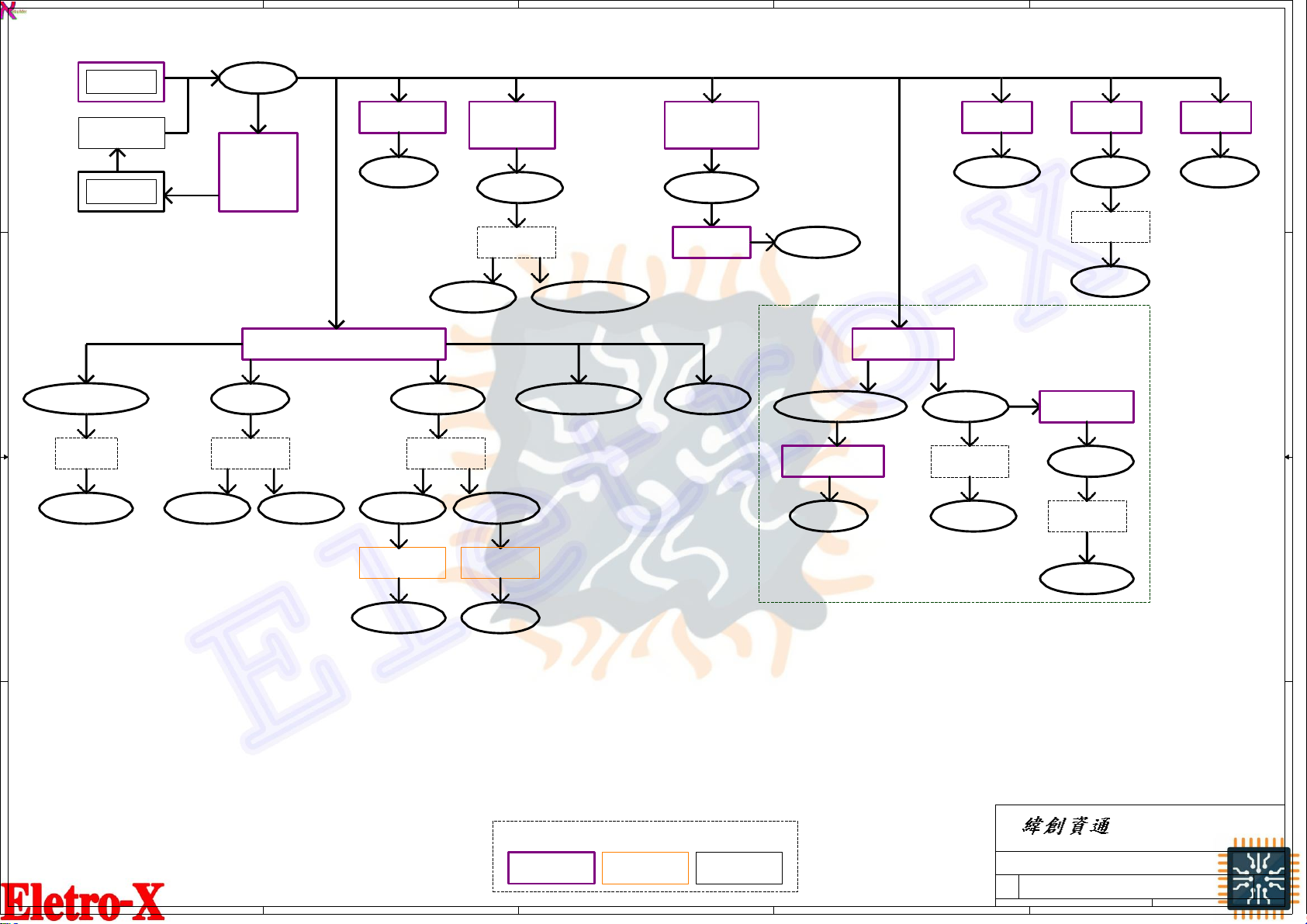

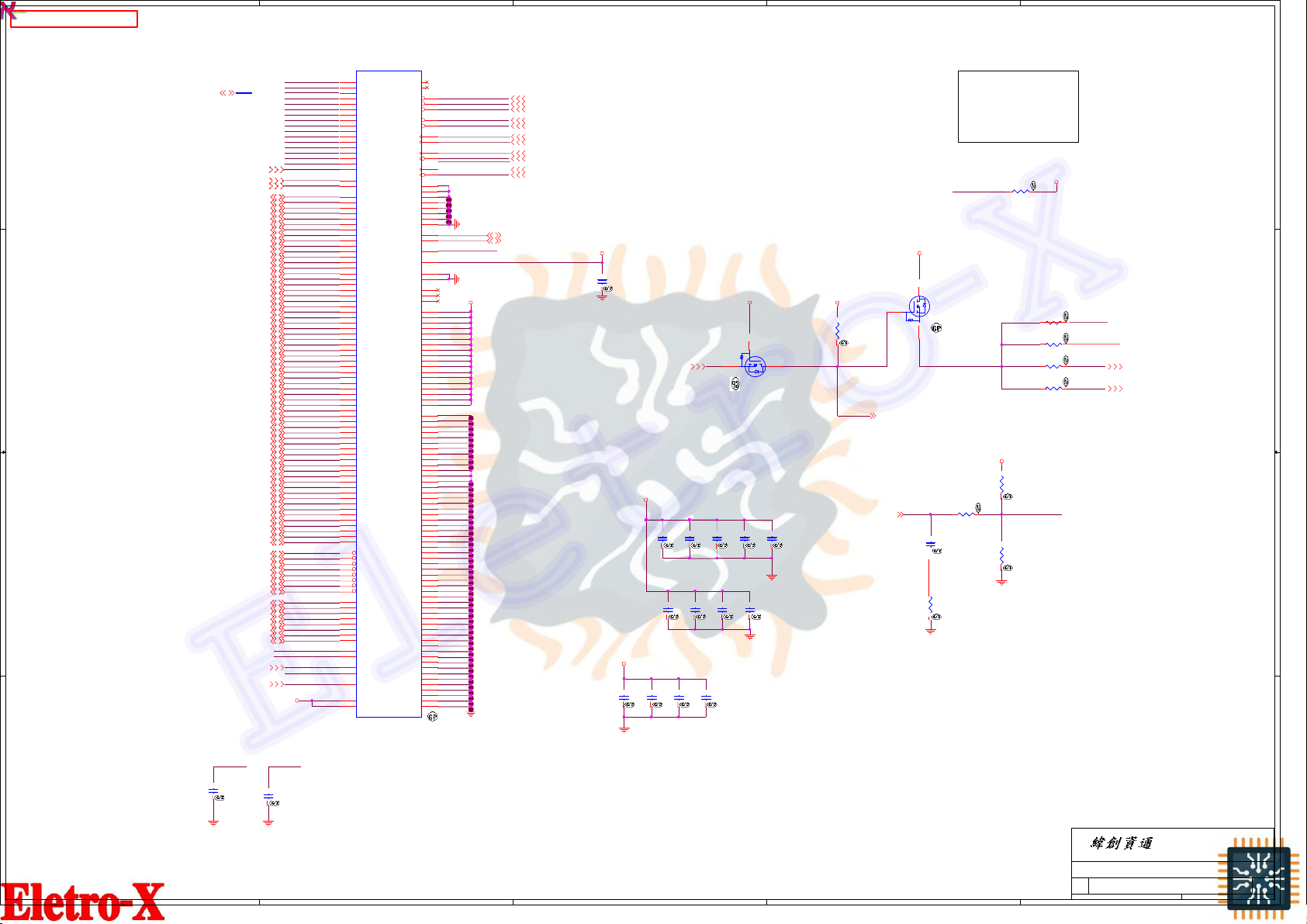

LF14M Board Block Diagram

VRAM

DDR3 1GB/2GB/4GB

D D

DDR3

900MHz

78~81

Touch LCDFHD

TOUCH

52

SENSOR

HDMI1.4a

GPU (DualRank)

N15V-GM(GT820M)

N15S-GT(GT840M)

73~77

USB3.0

34

SKT x1

CARDSKT

SDR104

C C

Card Reader

GL3213

USB2.0 SKTx2

2CH SPEAKER

SUB Woofer

U40/U50

Woofer AMP.

Internal ArrayDMIC

B B

DOCKINGBD

M50 only

USB Charger

Camera

28

63

34

IOBD

52

DDIx2

USB3.0 Port3,USB2.0Port6

USB3.0 Port1,USB2.0Port1

USB3.0Port2

USB2.0 Port2,USB2.0Port4

63

HD Audio Codec

ALC233

SPIFlash

8MB

eDPx2

USB2.0Port7

52

DDIx4

54

PEG x4

USB2.0Port3

HDA

29

25

SPI

TPM

SPI

4

Intel CPU

Broadwell

BGA1168

USB 3.0/2.0 ports (8)

ETHERNET(10/100/1000Mb)

High Definition Audio

SATA ports(3)

PCIe ports(5)

LPC I/F

5,6,7,8,9,10,

17,18,19,20,21,22,23,24,25

LPCBUS

88

KBC

NUVOTON

NPCE285G 24

TouchPad62Analog

G-Sensor

PCIEPort3

USB2.0Port5

PCIEPort4

USB2.0Port0

LPC debug port

SMBus

67

DDR3L 1333/1600 ChannelA

DDR3L/ 1.35V

DDR3L 1333/1600 ChannelB

NGFF WLAN

COMBO

65

Thermal

NCT7718W

Charger

BQ24715

44

Project code : 4PD00X010001

PCBP/N

Revision

58

LAN RTL8111GUS

SATAPort0

SATAPort1

Finger Print BD

26

3

DIMM

Slot 1

DIMM

Slot 2

30

HDD

ODD BD

64

:13281

: SC

12

13

MDI

RJ45

31

56

56

M40 Small BD & PCB P/N:

IO BD (13812-SA)

Sensor BD(13813-SA)

Fingerprint BD(Buy)

M50 Small BD & PCB P/N:

IO BD (13817-SA)

Sensor BD(13813-SA)

Volume Key BD (13819-SA)

ODD BD(13820-SA)

DOCKING BD (13818-SA)

Fingerprint BD(Buy)

2

1

CHARGER

BQ24715

INPUTS

DCBATOU T

SYSTEM DC/DC

TPS51275

INPUTS

DCBATOU T

CPU DC/DC

TPS51624

INPUTS

DCBATOU T VCC_CORE

SYSTEM DC/DC

SYS8208A

INPUTS

DCBATOU T 1D05V_VTT

SYSTEM DC/DC

RT8207

INPUTS OUTPUTS

DCBATOU T 1D35V_S3

OUTPUTS

BT+

OUTPUTS

5V_Charger

3D3V_S5

OUTPUTS

OUTPUTS

44

45

46-47

48

49

SYSTEM DC/DC

INPUTS OUTPUTS

SYSTEM DC/DC

TLV70215

INPUTS

RT8812A

INPUTS

DCBATOUT

Switches

Mybo14 Small BD & PCBP/N:

63

63

63

IO BD (13812-SA)

Sensor BD(13813-SA)

63

63

Mybo15 Small BD & PCB P/N:

63

63

63

63

63

63

IO BD (13814-SA)

Sensor BD(13813-SA)

Volume Key BD (13816-SA)

ODD BD(13820-SA)

Power BTN BD (13815-SA)

63

63

63

63

63

INPUTS

3D3V_S0

1D35V_S0

1D0 5V_V TT

PCB LAYER

L1:Top L4:Signal

L2:VCC L5:GND

L3:Signal L6:Bottom

OUTPUTS

1D5V_S0DCBATOU T

OUTPUTS

VGA_CORE

OUTPUTS

3D3V_VGA_S0

1D35V_VGA_S0

1D0 5V_V GA_S 0

51

82

83

A A

<Corrre Desiiign>

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,,Hsiiichiiih,,,

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

Block Diagram

LF14M

1

Rev

-1

Eletro-X

5

Tiiitttllle

DocumentttNumberrr

Siiize

A2

4

3

2

Dattte::: W ednesday,,, Febrrruarrry 26,,,2014 Sheettt 2 offf 102

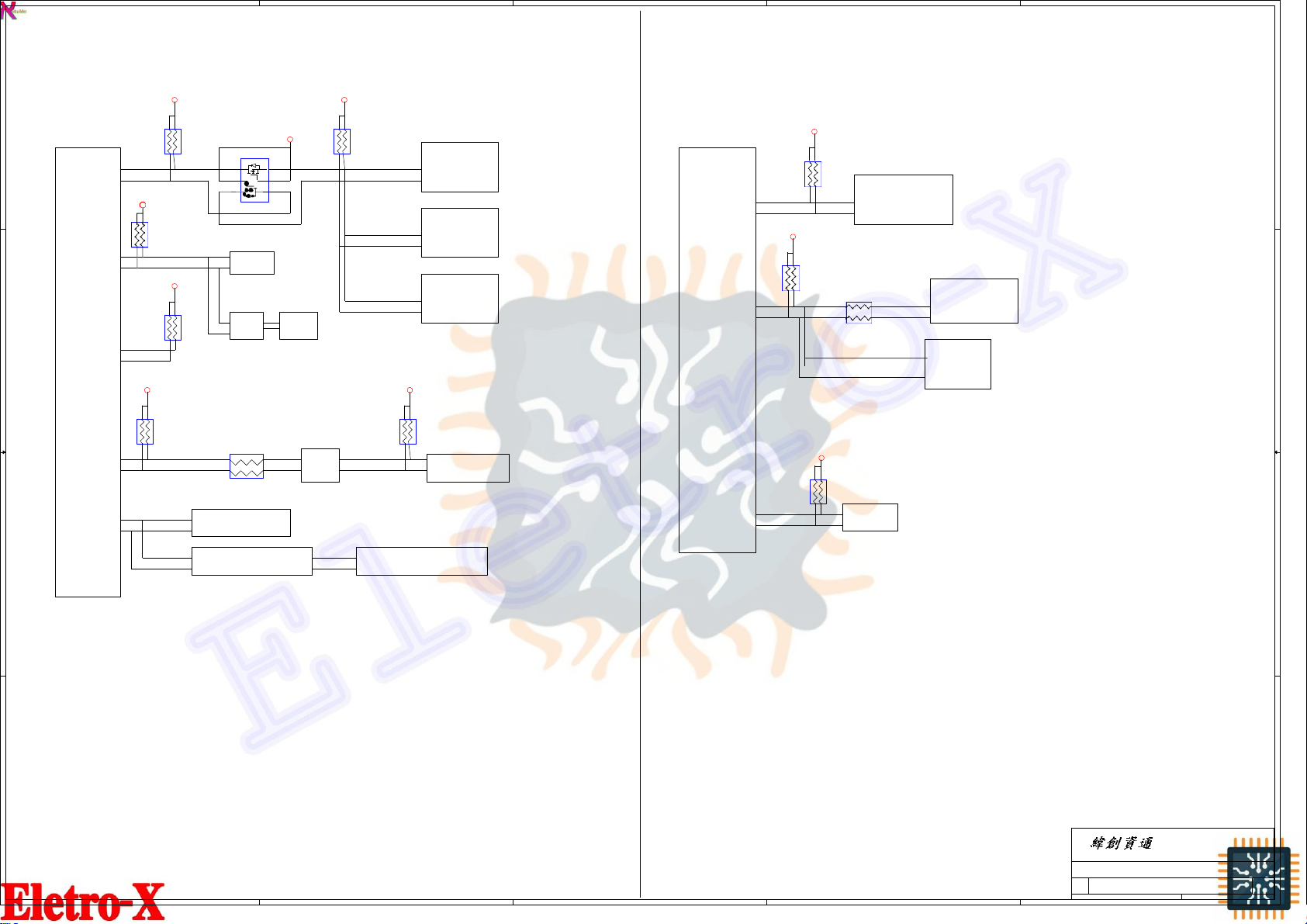

Page 3

A

B

C

D

E

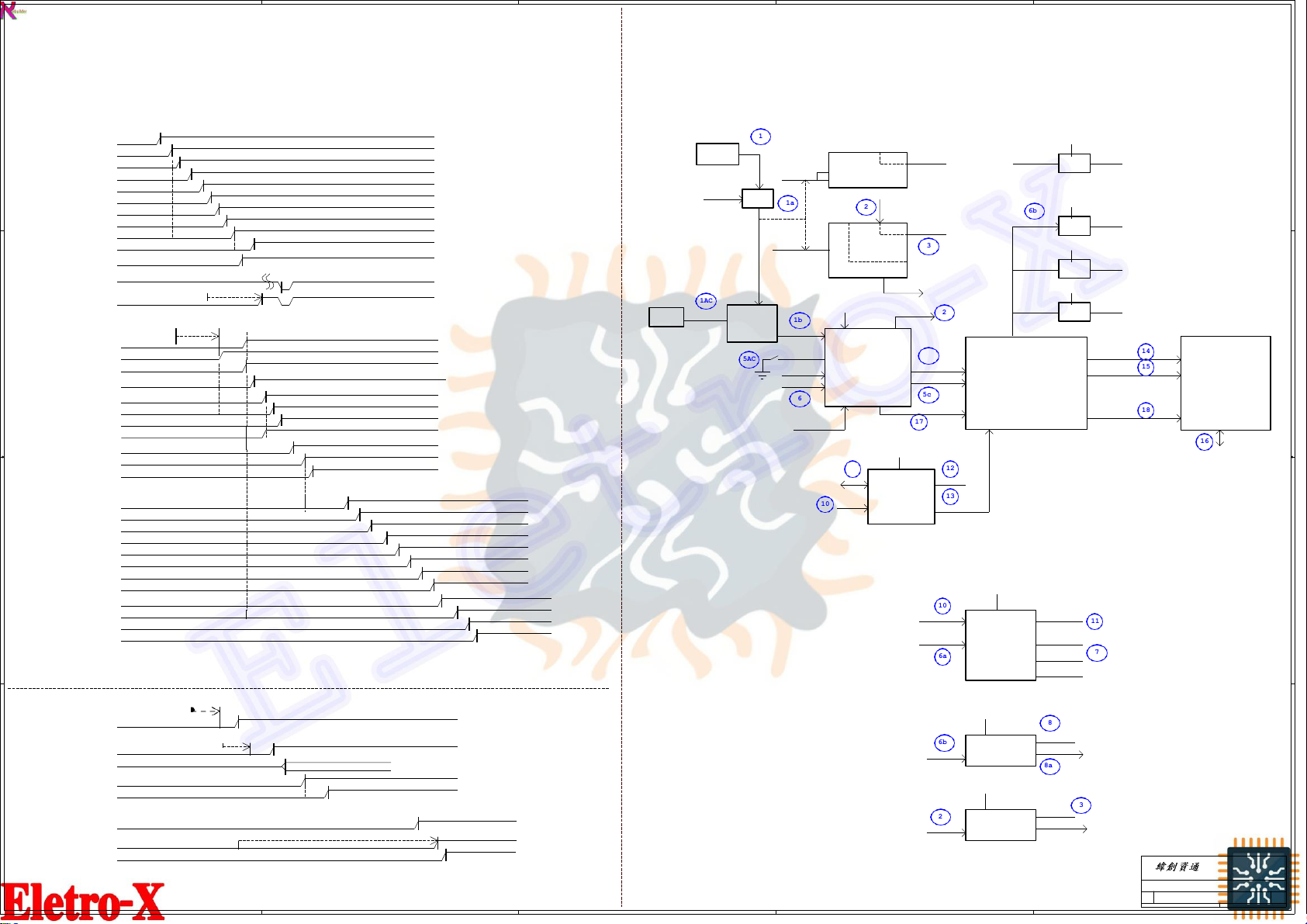

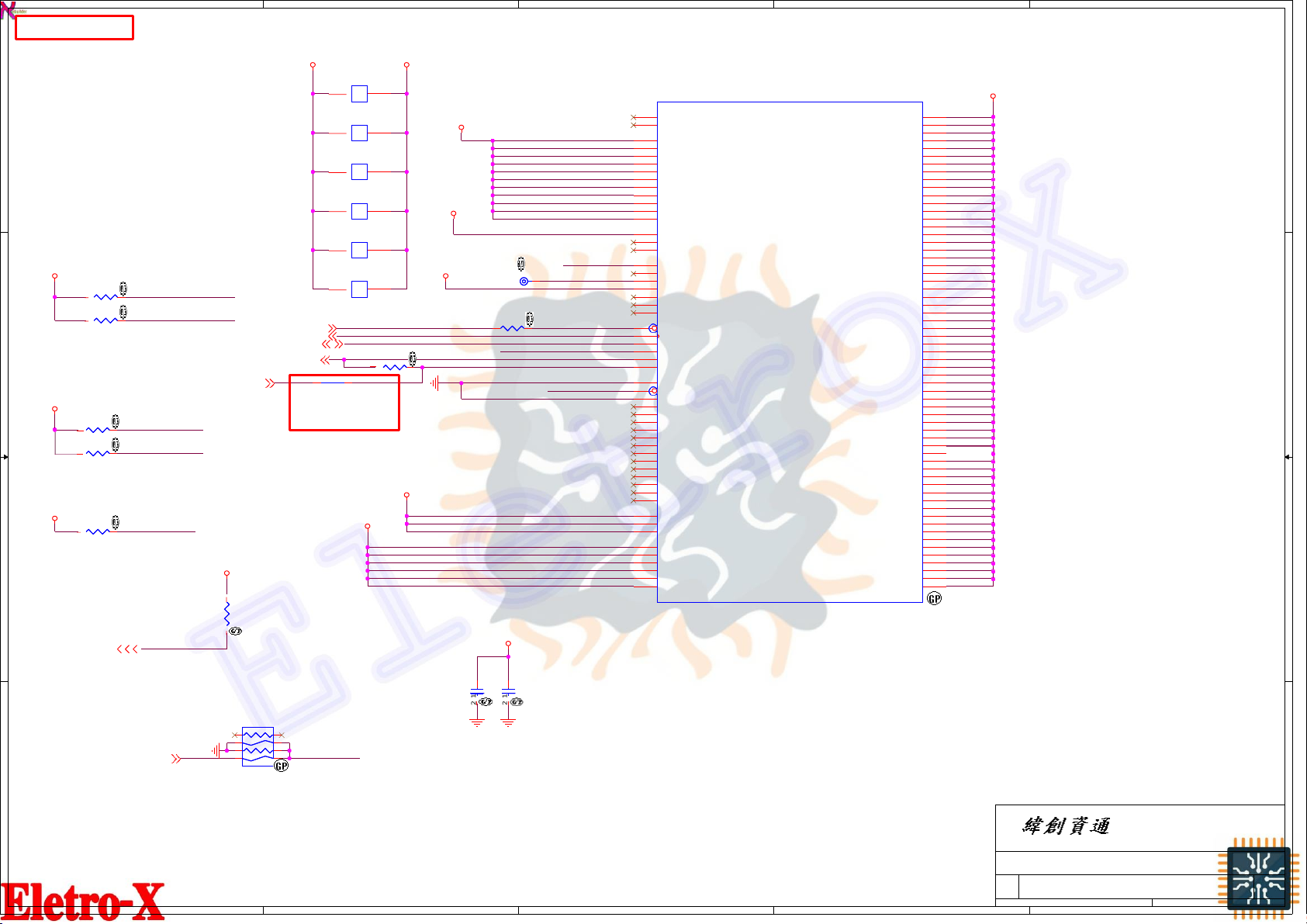

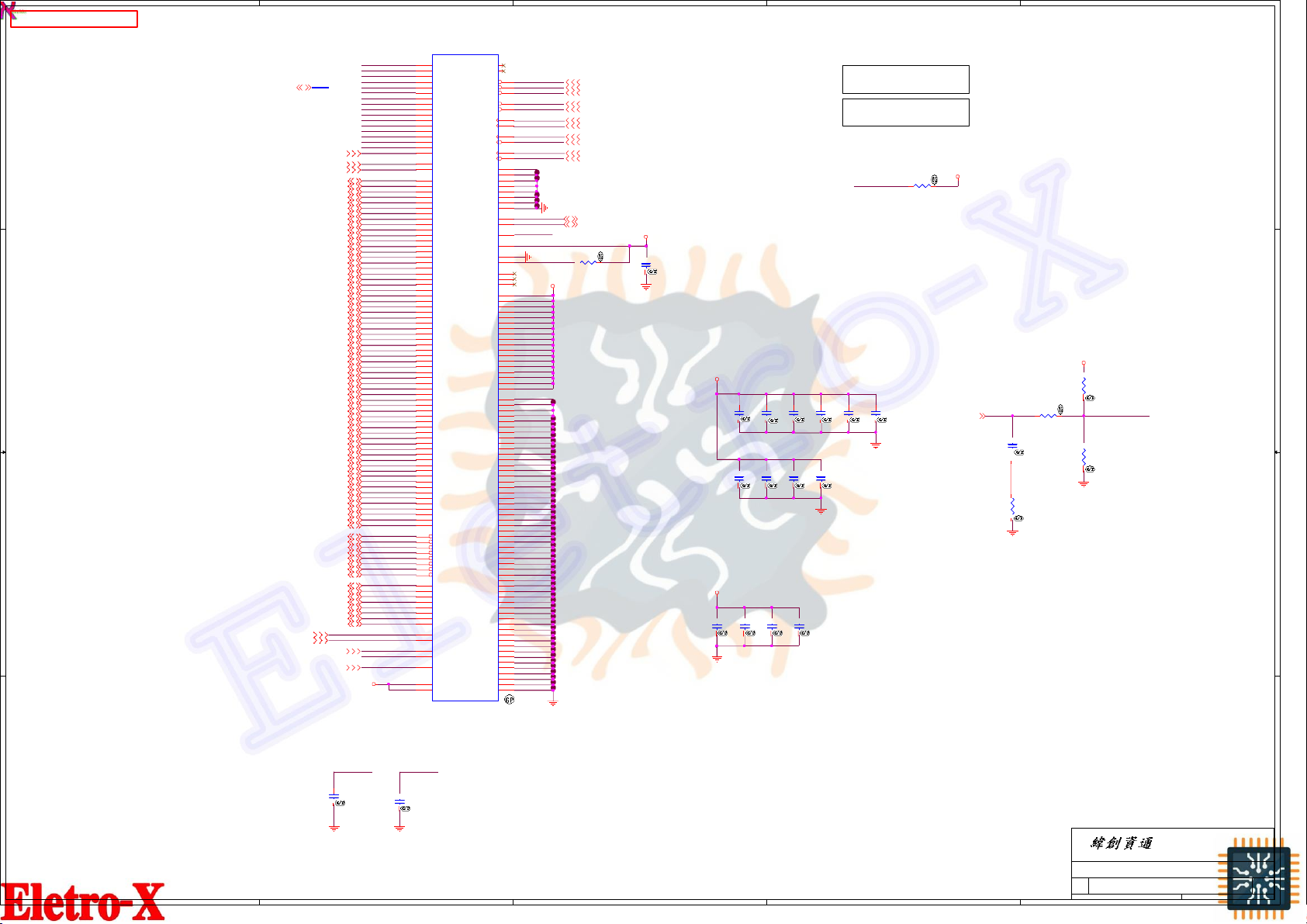

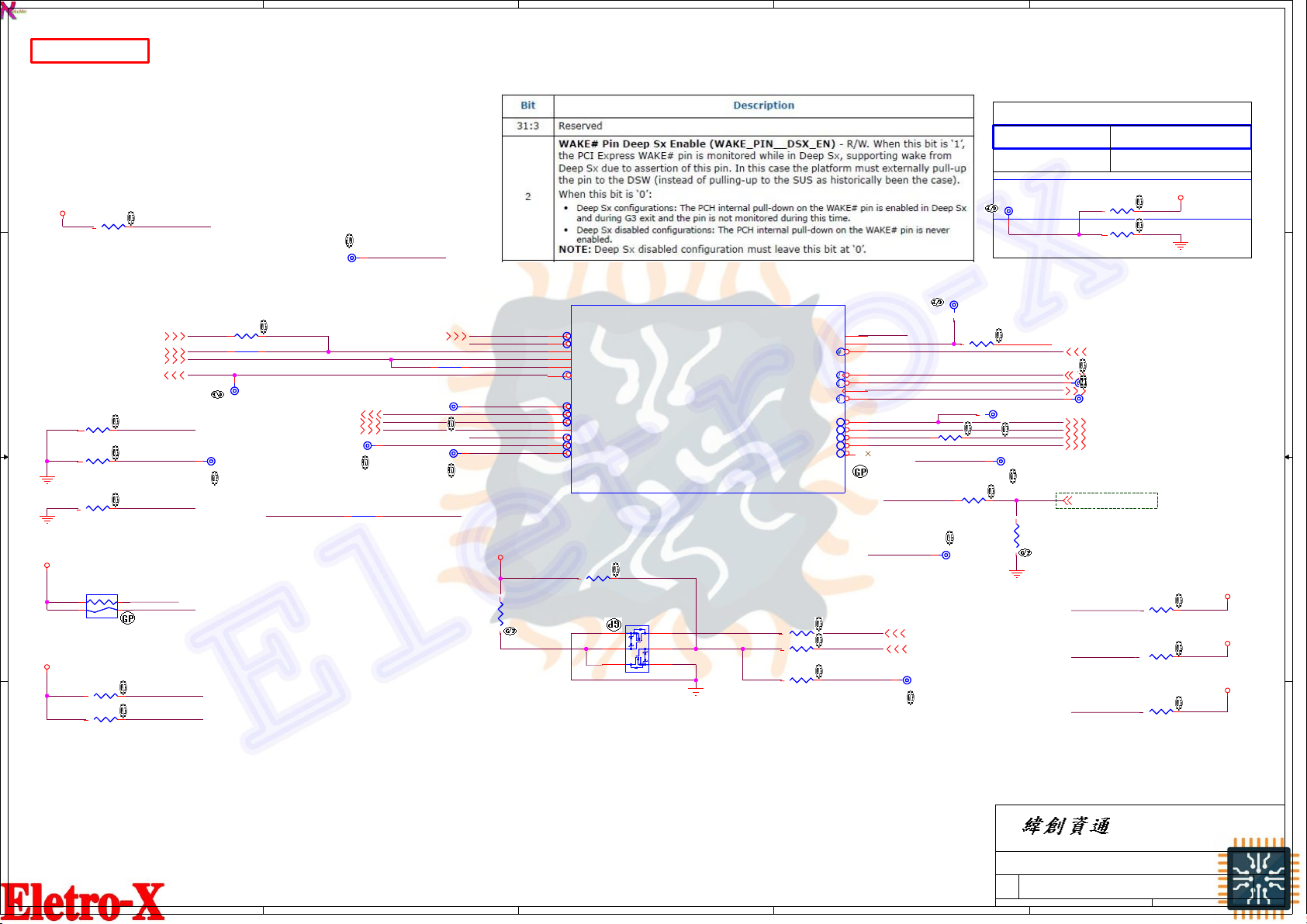

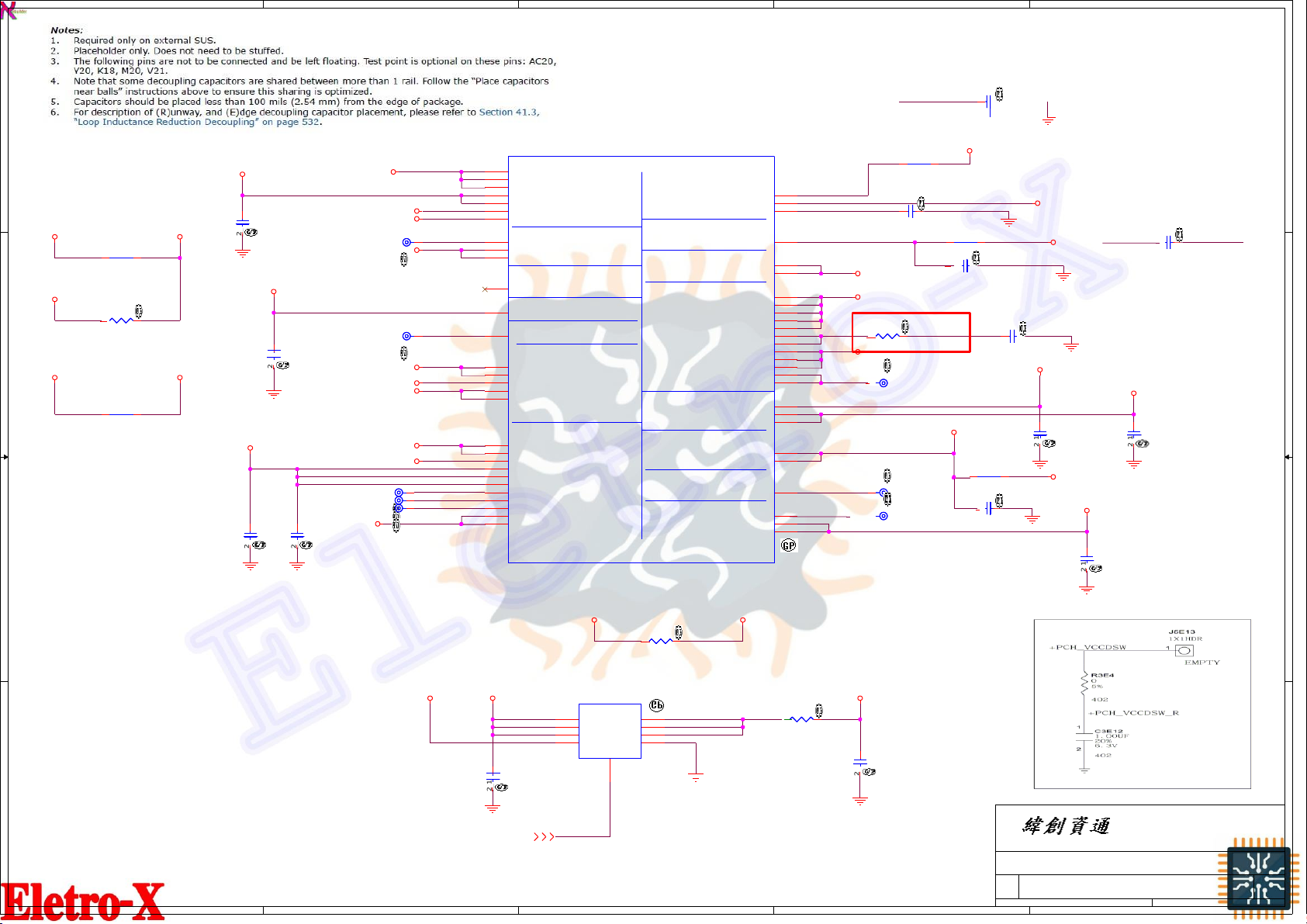

PCH SMBus Block Diagram

3D3V_S5

1 1

SMB_CL K

SMBCLK

SMB_DAT A

SMBDATA

3D3V_S5

SML0_C LK

SML0_D ATA

3D3V_S0

SML1_C LK

SML1_D ATA

3D3V_S5

SML1CLK

SML1DATA

2 2

SML0CLK

SML0DATA

2N7002SPT

To KBC

Level

Shift

3D3V_S0

Thermal

Sensor

CPU

DDPB_ CTRLCLK

DDPB_ CTRLDATA

PCH_ HDMI_C LK

PCH_ HDMI_D ATA

Level

Shift

3D3V_S0

DDC _CLK_ HDMI

DDC _DATA _HDMI

PCH_ SMBCLK

PCH_ SMBDAT A

PCH_ SMBCLK

PCH_ SMBDAT A

PCH_ SMBCLK

SCL

PCH_SMBDATA

5V_S0

RAM 1 & 2

SCL

SDA

RAM 3 & 4

SCL

SDA

TP

SDA

HDMI CONN

KBC SMBus Block Diagram

3D3V_S0

TouchPad Conn.

TPDATA

TPCLK

BATA_SC L_1

BATA_SD A_1

KBC

IT8587

PSDAT1

PSCLK1

SMCLK0

SMDAT0

TPDA TA

TPCL K

3D3V_AUX_S5

BAT_SCL

BAT_SDA

3D3V_S5

Battery Conn.

CLK_SMB

DAT_SMB

SMBus addres s:16

ISL9519

SCL

SDA

SMBus address:12

SML1_C LK

DDPC_C TRLCLK

DDPC_C TRLDATA

3 3

4 4

PA_A UX_P

PA_A UX_N THUNDERBOLT

Display Port Switch

AUX_CHP

AUX_CHN

THUNDERBOLT Conn.

Eletro-X

A

B

C

SMLCLK1

SMLDAT1

SML1_D ATA

SCL

SDA

PCH

M40

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,, Hsiiichiiih,,,

LF14M

E

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

Sheettt 101 offf 102Dattte:::

Rev

-1

Tiiitttllle

SMBUS BLOCK DIAGRAM

DocumentttNumberrr

Siiize

A2

D

Wednesday,,, Febrrruarrry 26,,,2014

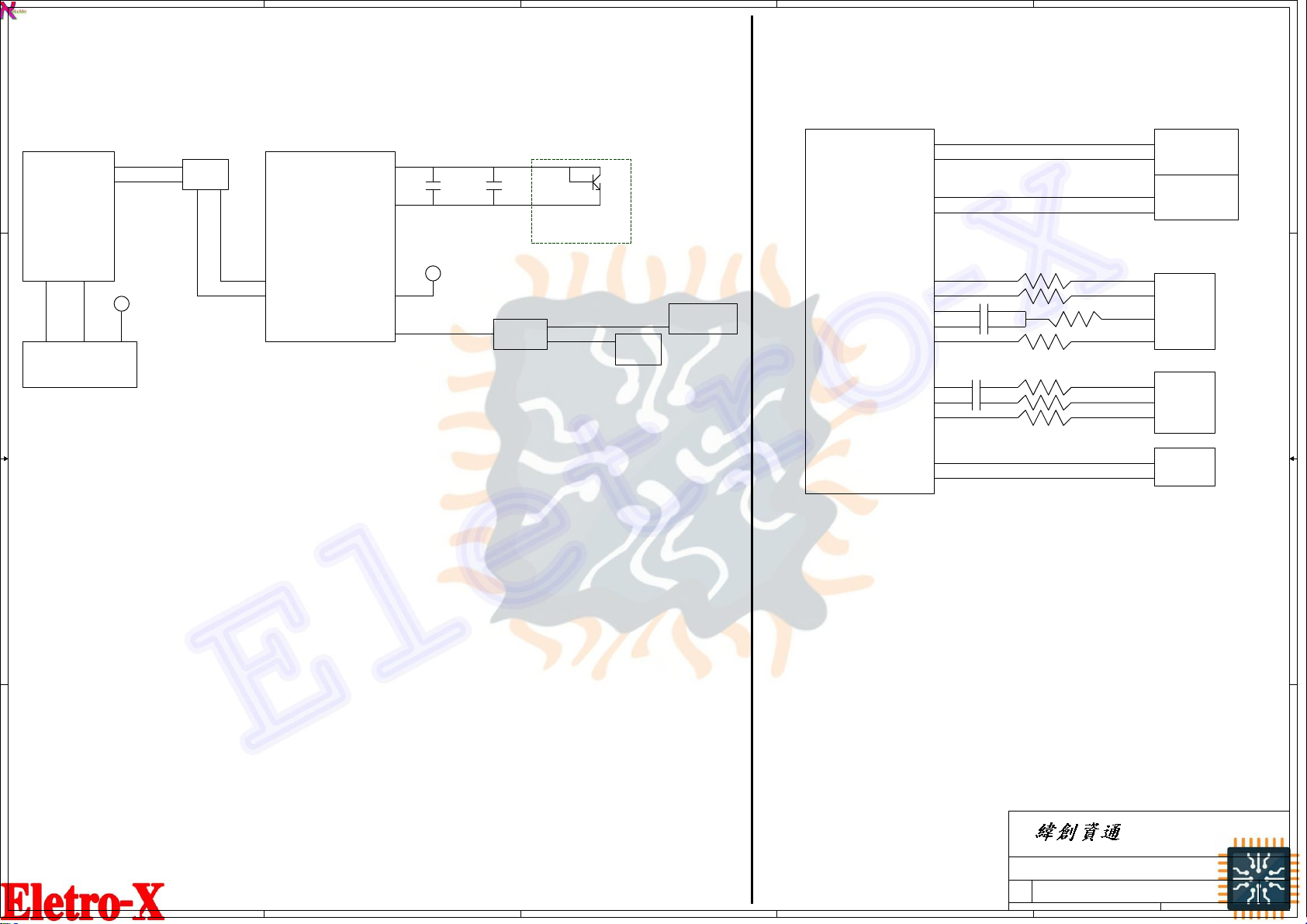

Page 4

A

B

C

D

E

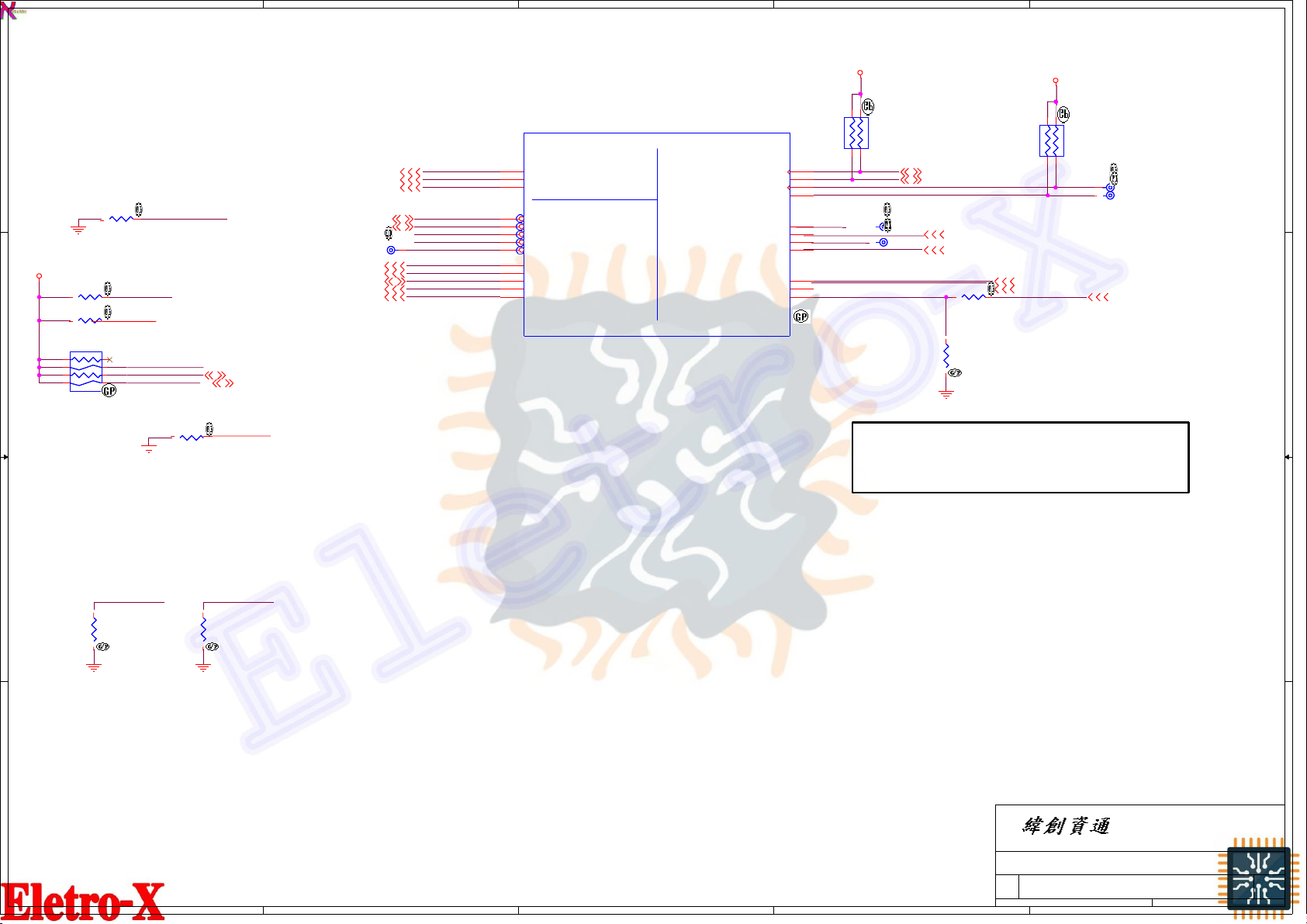

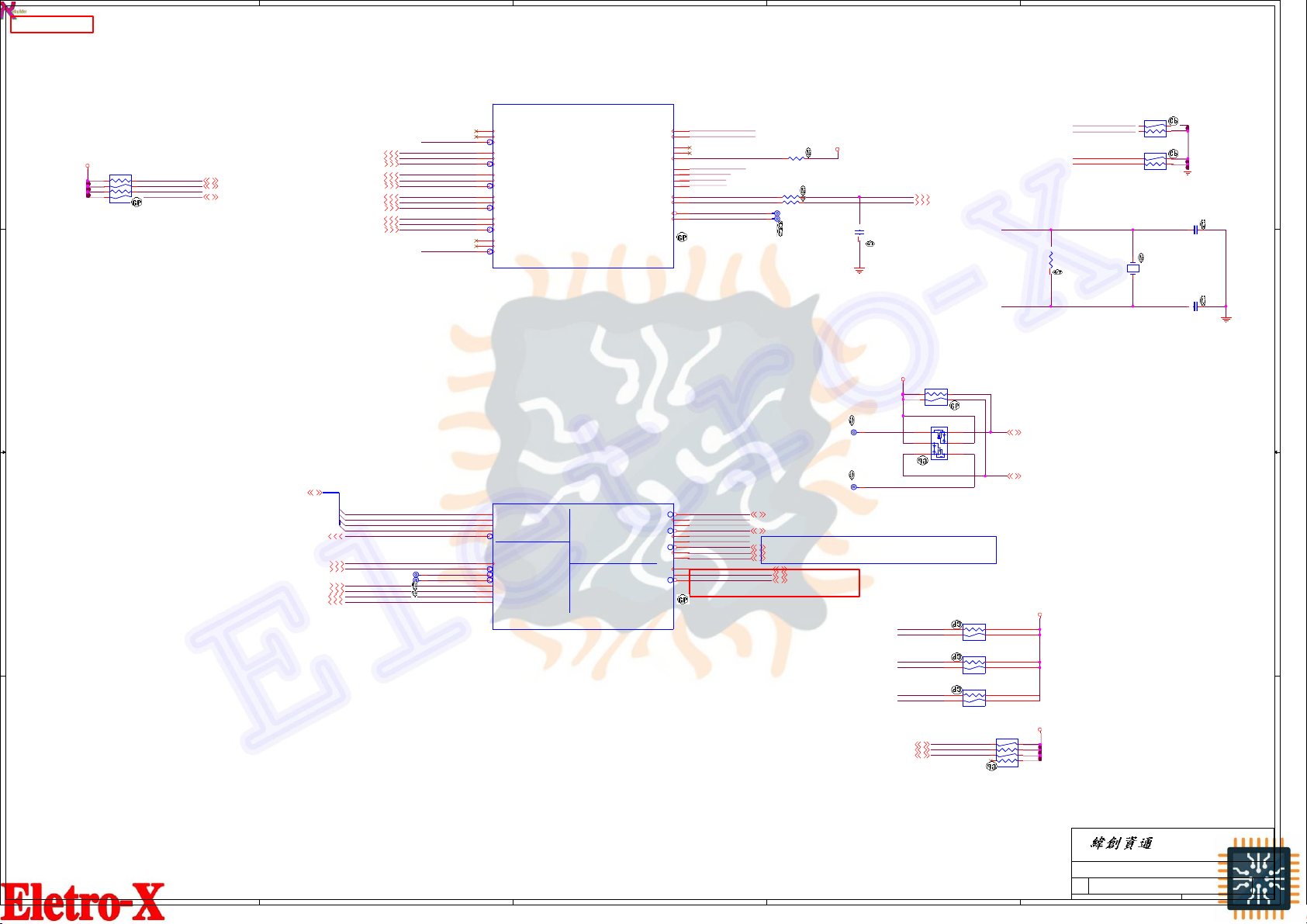

Thermal Block Diagram

1 1

SML1_CLK

KBC

IT8587

SCL1

SDA1

SML1_DA TA

LEVEL

SHIFT

NCT_CLK

System

NCT_DAT

A

Thermal

NCT7718W

PWM 4 GPD6

5V

FAN1_PW

M

FAN_TACH

2 2

1

VIN

SDA

SCL ALERT#

T_CRIT#

Put under CPU(T8 HW shutdown)

P2800_DXP

D+

D-

P2800_DXN

3D3V_S0

PH

THER M_SYS_SHDN#

Place near CPU

PWM CORE

2N7002 D

S G

PURE_HW_S HUTDOWN#

IMVP_PWR GD

PGO OD

VR

EN

3V/5V

Audio Block Diagram

SPK-OUT-LSPK-OUT-L+

SPK-OUT-RSPK-OUT-R+

Codec

ALC282

HPOUT-L/PORT-T-L

HPOUT-R/PORT-T-R

MIC2-L/PORT-F-L

MIC2-R/PORT-F-R

SENSE_A

SPEAKER

SPEAKER

HP

OUT

FAN Conn.

MIC1-L/PORT-B-L

MIC1-R/PORT-B-R

SENSE_A

DMIC-CLK

DMIC-DATA

MIC

IN

DMIC

3 3

4 4

Eletro-X

A

B

C

D

M40

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

Sheet 102 102Date:

E

of

Tiiitllle

THERMAL/AUDIO BLOCK DIAGRAM

Siiize Document Number

Custom

Wednesday, February 26, 2014

Rev

-1

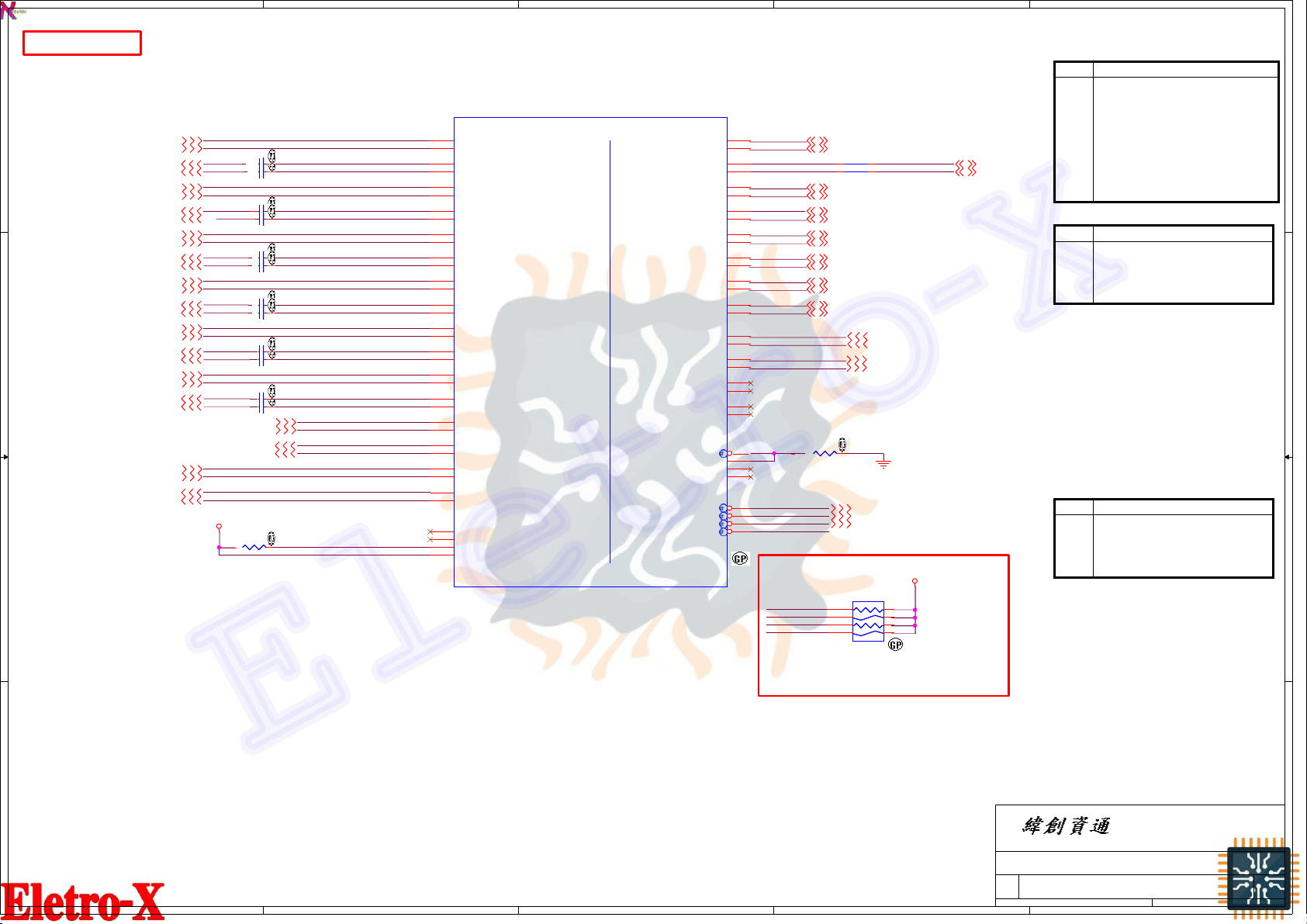

Page 5

5

4

3

2

1

Adapter

D D

FDS6679AZ

DCBATOUT

TPS51622

TPS51117 +

CSD86330Q

TPS51117 +

CSD86330Q

TPS62150

TPS62140

TPS51367

Charger

Battery

ISL9519

+AD

VCC_CORE

1D05V_M

1D2V_VDD

1D5V_S0

+V1.8U

1D2V_S0

TPS22965

QM3006S

TPS51206

0D6V_S0

+V1.8S

1D05V_VTT +V1.05DX_PHY

C C

V5A_WALKPORT

SY6288

USB30_VCCA

5V_DS3

TPS22965

5V_S5

TPS62130

3D3V_DSW

TPS22924

5V_S0 3D3V_S5

3D3V_S0

3D3V_WWAN_S0 3D3V_DX

PWR_VCC12V_IN

TPS61087DRCR

VCC12V0

TPS51275

3D3V_POC

SI7121DN

3D3V_LC

RT8078AZQW

1D05V_LC

SI4838BDY

USB Power

B B

G5244A31U

3D3V_DS3

RT9724GB

LCDVDD

1D05V_CIO

For Thunderbolt

For DS3

A A

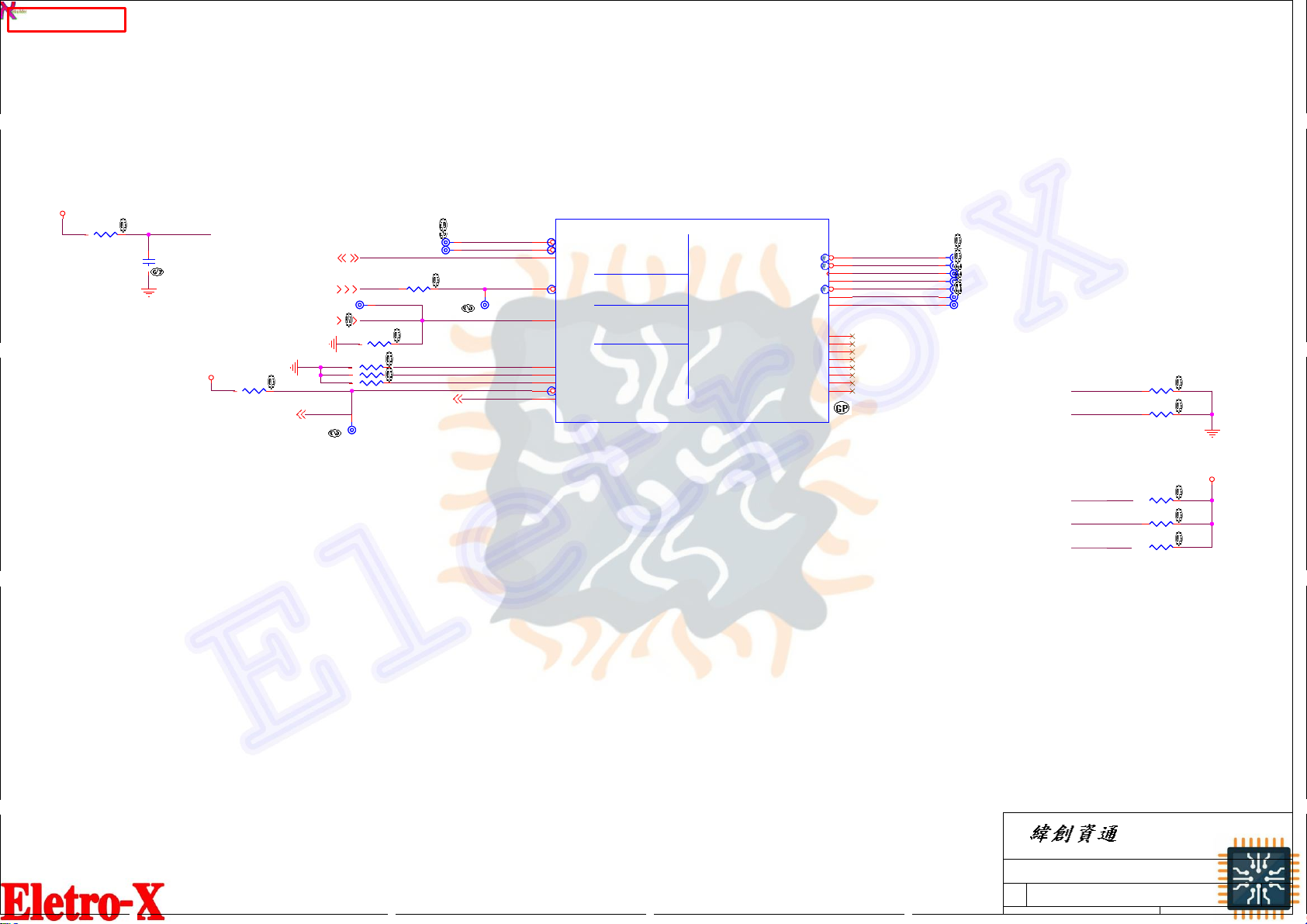

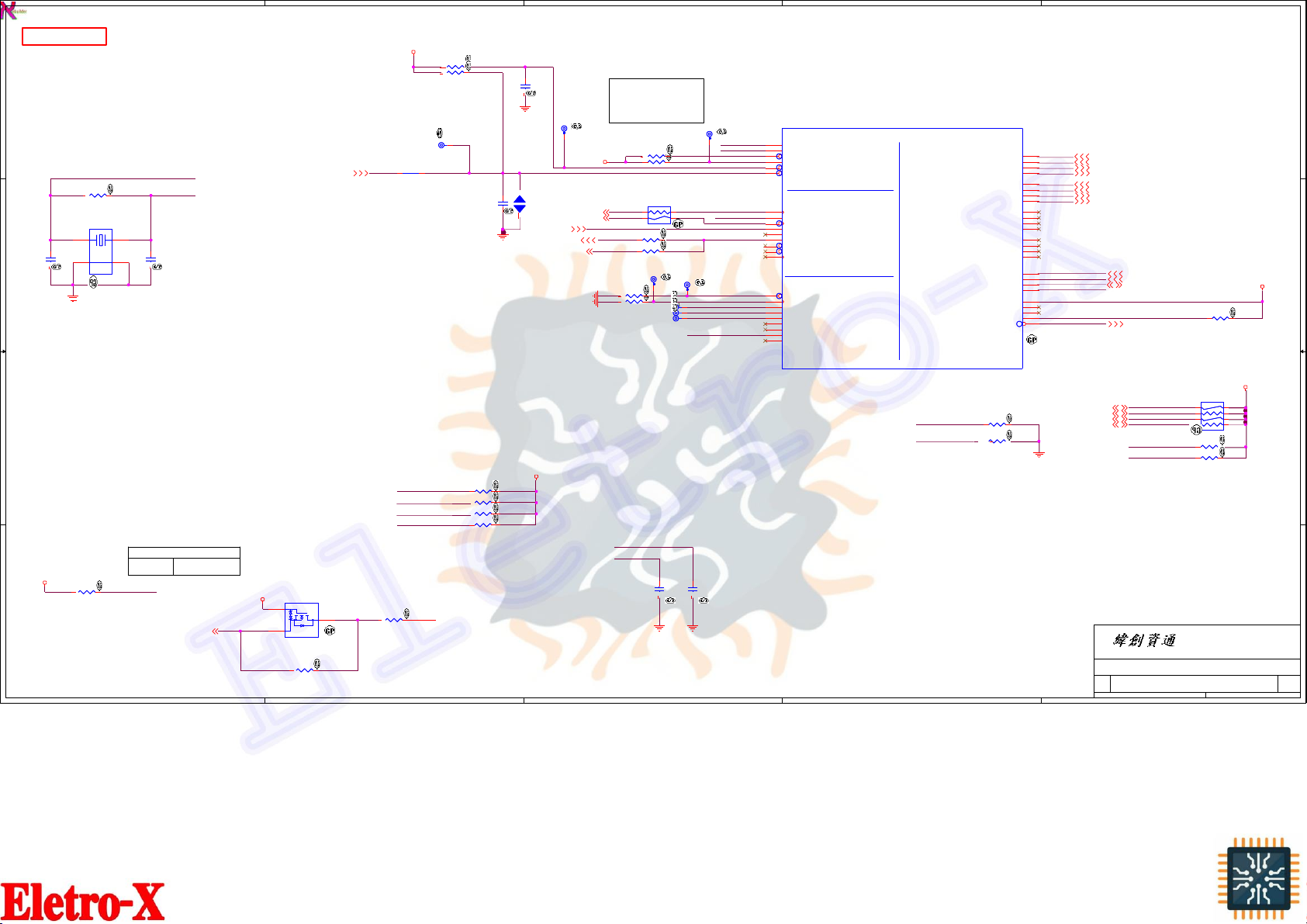

Power Shape

Eletro-X

5

4

Regulator LDO Switch

3

2

M40

Tiiitllle

Siiize

A3

Date:

Power Block Diagram

DocumentNumber

Wednesday, February 26,2014

LF14M

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

Rev

102

Sheet 100

1

of

-1

Page 6

5

4

3

2

1

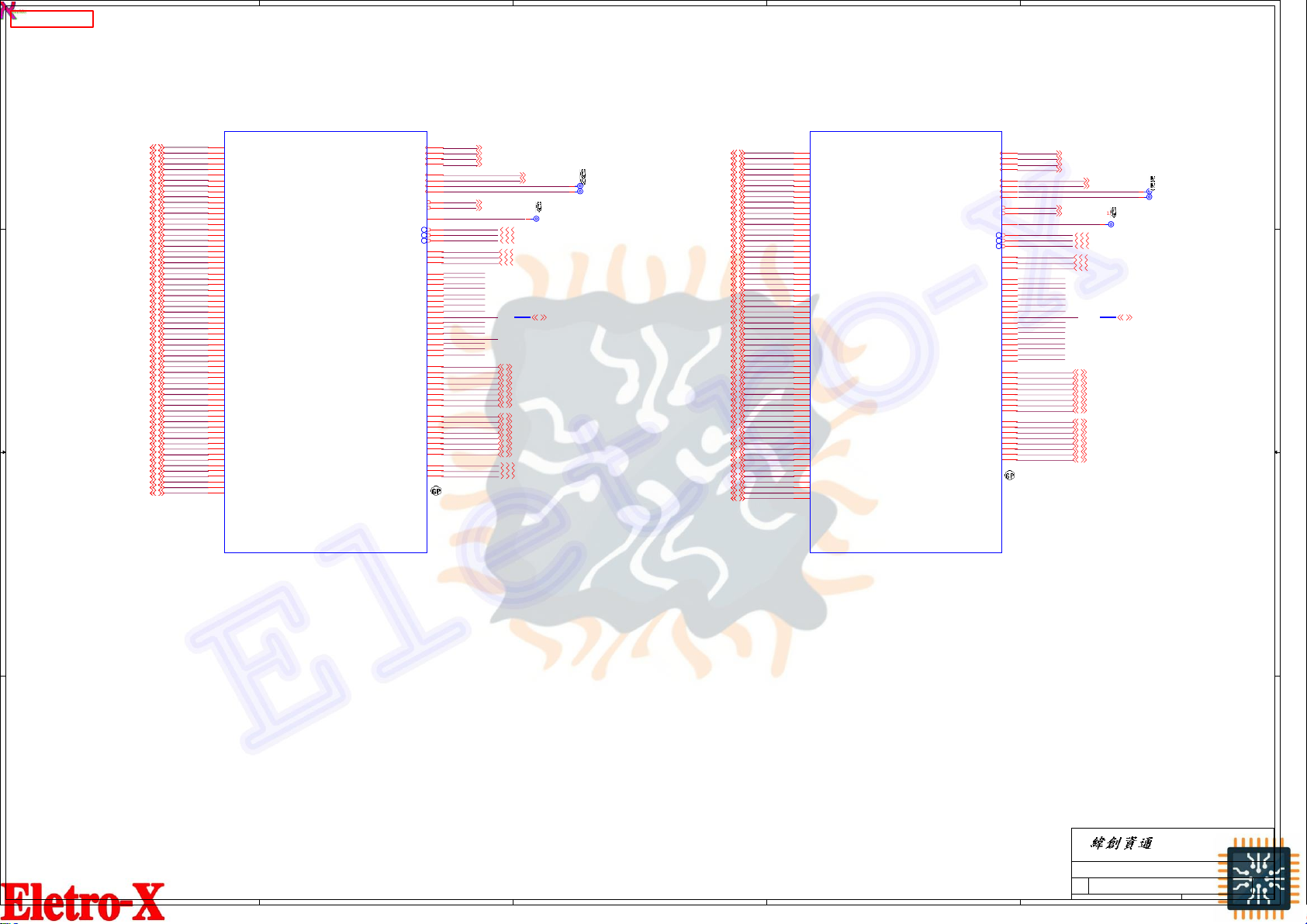

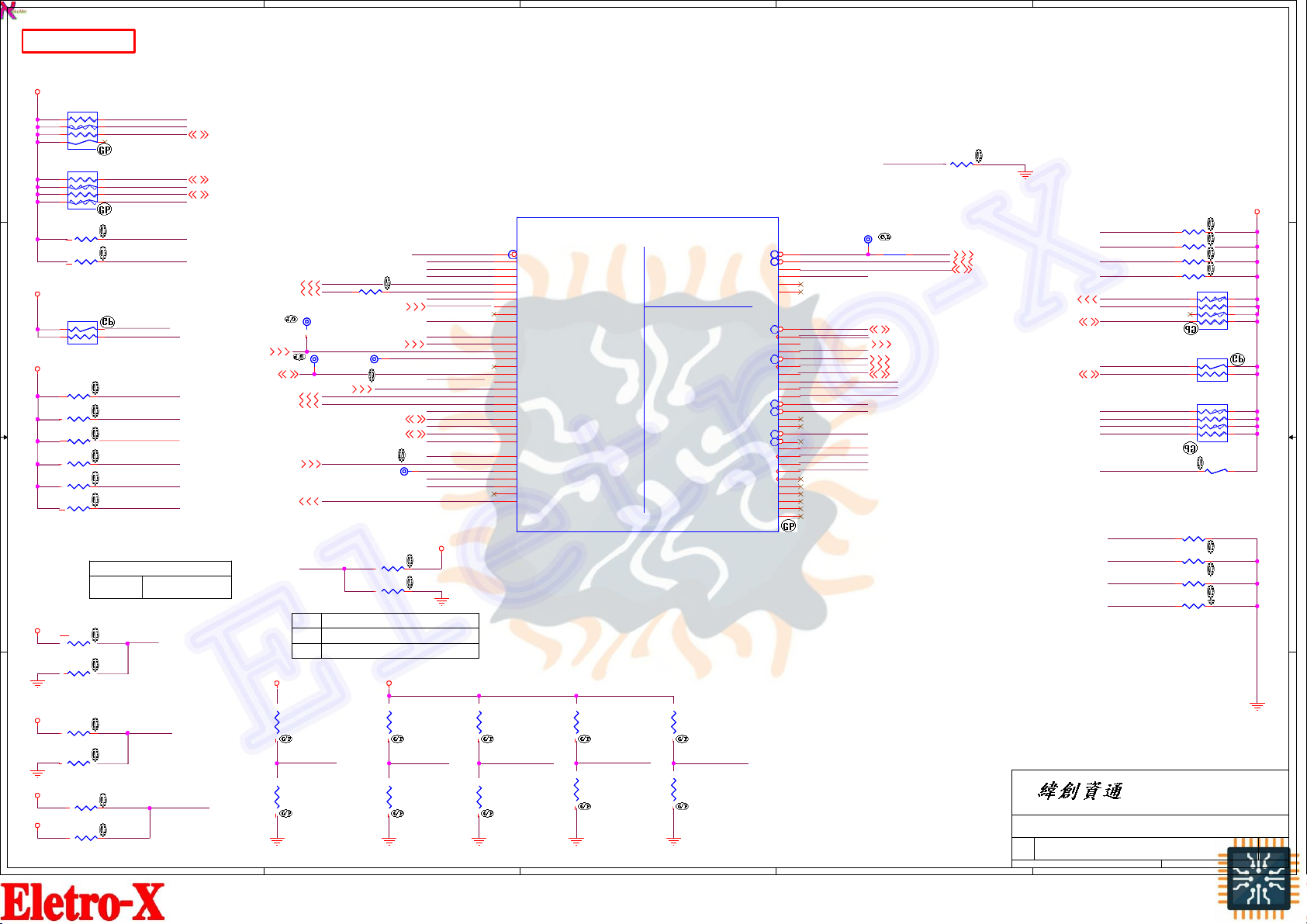

SHARK BAY POWER UP SEQUENCE DIAGRAM

Intel-Power Up Sequence

(AC mode)

D D

38

ISL9519

Charger

5AC

AD+

SWITCH

1

40

40

DCBATOUT

PM_SLP_S4#

PM_SLP_S3#

DCBATOUT

1a

1b

AC_IN

KBC_PWRBTN#

6

ALL_SYS_PWRGD

TPS62130

EN

(3D3V_DSW)

VIN

2

TPS62130

(5V)

VIN

3D3V_DSW

GPC4

GPE4

KBC

IT8587

GPD1

GPD0

Delay 99ms

GPI7

16

SVID

VR_EN

10

S5_ENABLE

EN

PGOOD

GPD5

SVID

VR_ON

41

41

3V_5V_POK

S5_ENABLE

GPE0

GPB7

GPG6

27

5V_S5

VIN

VR

TPS516 22

3D3V_DSW

5V_S5

3

2

5b

PM_RSMRST#

PM_PWRBTN#

5c

17

VCC_CORE

OUTPUT

PGOOD IMVP_PWRGD

10

DDR_PG_OUT

PM_SLP_S4#

6a

RSMRST#

PWRBTN#

SYS_PWROK

APWROK PWROK

12

13

S3 VTT

S5

46

DCBATOUT

VIN

TPS51117 +

TPS51206

RTC_AUX_S5

RTC_RST#

T1

3D3V_DSW

S5_ENABLE

3V_5V_EN

5V_DS3

1D05V_M

3V_5V_POK

PCH_RSMRST#

PM_SUSWARN#

AC_PRESENT

AC KBC_PWRBTN_EC#

AC PM_PWRBTN#

C C

B B

PM_SLP_A#

PM_SLP_S4#

PM_SLP_S3#

PM_MPWROK

1D2V_VDD

DDR_PG_CTRL

0D6V

1D8V_S0

5V_S0

3D3V_S0

1D5V_S0

GFX_CORE_EN(Discrete only)------Delay 5ms

+VGA_CORE(Discreteonly)

1.0V_RUN_VGA_EN(Discrete only)------Delay 4ms

+1.0V_RUN_VGA(Discreteonly)

1.8V_VGA_RUN_EN(Discrete only)------Delay 5ms

+1.8V_RUN_VGA(Discreteonly)

+3.3V_RUN_VGA_EN(Discrete only)-->DY reserved

+3.3V_RUN_VGA(Discrete only) -->Reserved forsequence

V1.5S_PWRGD

1D05V_VTT

1.05VTT_PWRGD

VCCST

AC PM_PWRBTN#

T2

3V_5V_POK

T13

T3

T4

T5

T6

T7

T12

DC

Battery

T14

T15

T17

T18

T19

+5V_RUN & +3.3V_RUN need meet 0.7Vdiff erence

T20

T21

T23

T24

T25

T26

T27

T28

T29

T30

T31

T32

T33

AC

Adapterin

AD_OFF_R

1AC

BT+

39

PM_SLP_S3#

PCH

VOUT

VTTREF

PGOOD

3D3V_DSW

3D3V_S5S5_ENABLE

SWITCH

36

5V_S5

6b

0D6V_S0

1D2V_VDD

VDDQ_VREF

DDR_VR_PWRGD

5V_S0

SWITCH

36

3D3V_S5

3D3V_S0

SWITCH

36

+V1.8U

+V1.8S

SWITCH

36

CLKOUT CLK

H_CPUPWRGD

PROCPWRGD

PLTRST# PLTRST#

11

7

14

15

PWRGOOD

Shark Bay

CPU

18

SVID

SVID

16

1.05VTT_PWRGD

ALL_SYSTEM_PWRGD

+VCC_CORE

CLK_CPU_BCLK

IMVP_PWRGD

A A

PCH_PWROK

H_CPUPWRGD

SYS_PWRGD

PLT_RST#

H_VR_EN

ALL_SYSTEM_PWRGD

<3ms

T36

T37

CLKIN_BCLK Stable

T38

To KBC GPI7 delay 99ms toPCH

CPU CORE Power

T39

T50

T51

T52

PM_SLP_S3#

S5_ENABLE

Eletro-X

5

4

3

2

DCBATOUT

VIN

6b

TPS62150

EN

DCBATOUT

VIN

2

TPS51117

EN

VOUT

PGOOD

VOUT

PGOOD

46

45

8

1D5V_S0

V1.5S_PWRGD

8a

1D05V_M

1D05V_M_PWR

3

M40

Tiiitttllle

DocumentttNumberrr

Siiize

A1

Wednesday,,, Febrrruarrry 26,,,2014

Dattte:::

1

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,,Hsiiichiiih,,,

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

PowerSequence

LF14M

Sheettt 99 offf 102

Rev

-1

Page 7

SSID = CPU

5

4

3

2

1

D D

1D05V_VTT

R401

1 2

C C

62R2J-GP

H_PROCHOT#

C402

SC47P50V2JN-3GP

2 1

VDDQ_CPU

24,44,46H_PROCHOT#

36 H_CPUPWRGD

R420

2

1

470R2F-GP

37 SM_DRAMRST#

24 H_PECI

AFTP405

R406

1 2

R407

1

R408

1

1

TP410

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

1

R403

1 2

10KR2J-L-GP

2

2

12 DDR_PG_CTRL

TP401

TP402

R413

1 2

56R2J-L1-GP

200R2F-L-GP

120R2F-GP

100R2F-L1-GP-U

SKTOCC#_R

1

H_CATERR#

1

H_PROCHOT#_R

1

TP411

TPAD14-OP-GP

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST#

CPU1B

D61

PROC_DETECT#

K61

CATERR#

N62

PECI

K63

PROCHOT# PROC_TRST#

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST#

AV61

SM_PG_CNTL1

HASWELL-6-GP-U

71.HASWE.G0U

CPU BOMCTRL

MIISC

THERMAL

PWR

DDR3L

HSW_ULT_DDR3L

JTAG

2 OF 19

PRDY#

PREQ#

PROC_TCK

PROC_TMS

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

TP403

TP404

TP405

TP406

TP407

TP408

TP409

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

XDP_TCK

XDP_TRST#

XDP_TDO R414

XDP_TDI

XDP_TMS R416

1

R415

1 DY2

1

1

DY

1 DY2

R412

R411

DY

2

51R2J-2-GP

2

51R2J-2-GP

1D05V_VTT

2

51R2J-2-GP

51R2J-2-GP

51R2J-2-GP

1

1

1

1

1

1

1

B B

A A

Eletro-X

<CoreDesiiign>

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Tiiitllle

CPU (THERMAL/CLOCK/PM)

DocumentNumber

Siiize

A3

Wednesday, February 26,2014

Date:

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

Sheet 4

Rev

-1

102

of

Page 8

SSID = CPU

5

4

3

2

1

D D

12 M_A_DQ0

12 M_A_DQ1

12 M_A_DQ2

12 M_A_DQ3

12 M_A_DQ4

12 M_A_DQ5

12 M_A_DQ6

12 M_A_DQ7

12 M_A_DQ8

12 M_A_DQ9

12 M_A_DQ10

12 M_A_DQ11

12 M_A_DQ12

12 M_A_DQ13

12 M_A_DQ14

12 M_A_DQ15

12 M_A_DQ16

12 M_A_DQ17

12 M_A_DQ18

12 M_A_DQ19

12 M_A_DQ20

12 M_A_DQ21

12 M_A_DQ22

12 M_A_DQ23

12 M_A_DQ24

12 M_A_DQ25

12 M_A_DQ26

12 M_A_DQ27

12 M_A_DQ28

12 M_A_DQ29

12 M_A_DQ30

C C

B B

12 M_A_DQ31

12 M_A_DQ32

12 M_A_DQ33

12 M_A_DQ34

12 M_A_DQ35

12 M_A_DQ36

12 M_A_DQ37

12 M_A_DQ38

12 M_A_DQ39

12 M_A_DQ40

12 M_A_DQ41

12 M_A_DQ42

12 M_A_DQ43

12 M_A_DQ44

12 M_A_DQ45

12 M_A_DQ46

12 M_A_DQ47

12 M_A_DQ48

12 M_A_DQ49

12 M_A_DQ50

12 M_A_DQ51

12 M_A_DQ52

12 M_A_DQ53

12 M_A_DQ54

12 M_A_DQ55

12 M_A_DQ56

12 M_A_DQ57

12 M_A_DQ58

12 M_A_DQ59

12 M_A_DQ60

12 M_A_DQ61

12 M_A_DQ62

12 M_A_DQ63

CPU1C

AH63

SA_DQ0 SA_CL K#0

AH62

SA_DQ1

AK63

SA_DQ2

AK62

SA_DQ3

AH61

SA_DQ4

AH60

SA_DQ5

AK61

SA_DQ6

AK60

SA_DQ7

AM63

SA_DQ8

AM62

SA_DQ9

AP63

SA_DQ1 0

AP62

SA_DQ1 1

AM61

SA_DQ1 2

AM60

SA_DQ1 3

AP61

SA_DQ1 4

AP60

SA_DQ1 5

AP58

SA_DQ1 6

AR58

SA_DQ1 7

AM57

SA_DQ1 8

AK57

SA_DQ1 9

AL58

SA_DQ2 0

AK58

SA_DQ2 1

AR57

SA_DQ2 2

AN57

SA_DQ2 3

AP55

SA_DQ2 4

AR55

SA_DQ2 5

AM54

SA_DQ2 6

AK54

SA_DQ2 7

AL55

SA_DQ2 8

AK55

SA_DQ2 9

AR54

SA_DQ3 0

AN54

SA_DQ3 1

AY58

SA_DQ3 2

AW5 8

SA_DQ3 3

AY56

SA_DQ3 4

AW5 6

SA_DQ3 5

AV58

SA_DQ3 6

AU58

SA_DQ3 7

AV56

SA_DQ3 8

AU56

SA_DQ3 9

AY54

SA_DQ4 0

AW5 4

SA_DQ4 1

AY52

SA_DQ4 2

AW5 2

SA_DQ4 3

AV54

SA_DQ4 4

AU54

SA_DQ4 5

AV52

SA_DQ4 6

AU52

SA_DQ4 7

AK40

SA_DQ4 8

AK42

SA_DQ4 9

AM43

SA_DQ5 0

AM45

SA_DQ5 1

AK45

SA_DQ5 2

AK43

SA_DQ5 3

AM40

SA_DQ5 4

AM42

SA_DQ5 5

AM46

SA_DQ5 6

AK46

SA_DQ5 7

AM49

SA_DQ5 8

AK49

SA_DQ5 9

AM48

SA_DQ6 0

AK48

SA_DQ6 1

AM51

SA_DQ6 2

AK51

SA_DQ6 3

HASWELL--6--GP--U

71.HASWE.G0U

CPU BOM CTRL

HSW_ULT_DDR3L

DDR CHANNEL A

3 OF19

SA_CL K0

SA_CL K#1

SA_CL K1

SA_CK E0

SA_CK E1

SA_CK E2

SA_CK E3

SA_CS #0

SA_CS #1

SA_ODT0

SA_RA S#

SA_W E#

SA_CA S#

SA_BA 0

SA_BA 1

SA_BA 2

SA_MA 0

SA_MA 1

SA_MA 2

SA_MA 3

SA_MA 4

SA_MA 5

SA_MA 6

SA_MA 7

SA_MA 8

SA_MA 9

SA_MA 10

SA_MA 11

SA_MA 12

SA_MA 13

SA_MA 14

SA_MA 15

SA_DQS N0

SA_DQS N1

SA_DQS N2

SA_DQS N3

SA_DQS N4

SA_DQS N5

SA_DQS N6

SA_DQS N7

SA_DQS P0

SA_DQS P1

SA_DQS P2

SA_DQS P3

SA_DQS P4

SA_DQS P5

SA_DQS P6

SA_DQS P7

SM_VR EF_CA

SM_VR EF_DQ0

SM_VR EF_DQ1

AW4 3

AY42

AY43

AP33

AR32

AP32

AY34

AW3 4

AU34

AU36

AR38

AU39

AR36

AW3 9

AU40

AW4 1

AU41

AR35

AU42

AU35

AV35

AY41

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW5 7

AW5 3

AL42

AL49

AP49

AR51

AP51

AU37

AV37

AW3 6

AY36

AU43

AY37

AP36

AV40

AY39

AP35

AV42

M_A_DIM0_CKE2

M_A_DIM0_CKE3

M_A_DIM0_ODT0_TP

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DIM0_CLK_DDR#012

M_A_DIM0_CLK_DDR0 12

M_A_DIM0_CLK_DDR#112

M_A_DIM0_CLK_DDR1 12

M_A_DIM0_CS#0 12

M_A_DIM0_CS#1 12

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_DIM0_CKE012

M_A_DIM0_CKE112

TPAD14--OP--GP

1

TP503

M_A_RAS# 12

M_A_WE# 12

M_A_CAS# 12

M_A_BS0 12

M_A_BS1 12

M_A_BS2 12

M_A_A[15:0]12

M_A_DQS_DN0 12

M_A_DQS_DN1 12

M_A_DQS_DN2 12

M_A_DQS_DN3 12

M_A_DQS_DN4 12

M_A_DQS_DN5 12

M_A_DQS_DN6 12

M_A_DQS_DN7 12

M_A_DQS_DP0 12

M_A_DQS_DP1 12

M_A_DQS_DP2 12

M_A_DQS_DP3 12

M_A_DQS_DP4 12

M_A_DQS_DP5 12

M_A_DQS_DP6 12

M_A_DQS_DP7 12

+V_SM_VREF_CNT 37

M_VREF_DQ_DIMM0_C 12

M_VREF_DQ_DIMM1_C 13

CPU1D

13 M_B_DQ0

13 M_B_DQ1

13 M_B_DQ2

13 M_B_DQ3

TPAD14--OP--GP

1

TP501

TPAD14--OP--GP

1

TP502

13 M_B_DQ4

13 M_B_DQ5

13 M_B_DQ6

13 M_B_DQ7

13 M_B_DQ8

13 M_B_DQ9

13 M_B_DQ10

13 M_B_DQ11

13 M_B_DQ12

13 M_B_DQ13

13 M_B_DQ14

13 M_B_DQ15

13 M_B_DQ16

13 M_B_DQ17

13 M_B_DQ18

13 M_B_DQ19

13 M_B_DQ20

13 M_B_DQ21

13 M_B_DQ22

13 M_B_DQ23

13 M_B_DQ24

13 M_B_DQ25

13 M_B_DQ26

13 M_B_DQ27

13 M_B_DQ28

13 M_B_DQ29

13 M_B_DQ30

13 M_B_DQ31

13 M_B_DQ32

13 M_B_DQ33

13 M_B_DQ34

13 M_B_DQ35

13 M_B_DQ36

13 M_B_DQ37

13 M_B_DQ38

13 M_B_DQ39

13 M_B_DQ40

13 M_B_DQ41

13 M_B_DQ42

13 M_B_DQ43

13 M_B_DQ44

13 M_B_DQ45

13 M_B_DQ46

13 M_B_DQ47

13 M_B_DQ48

13 M_B_DQ49

13 M_B_DQ50

13 M_B_DQ51

13 M_B_DQ52

13 M_B_DQ53

13 M_B_DQ54

13 M_B_DQ55

13 M_B_DQ56

13 M_B_DQ57

13 M_B_DQ58

13 M_B_DQ59

13 M_B_DQ60

13 M_B_DQ61

13 M_B_DQ62

13 M_B_DQ63

AY31

SB_DQ0

AW3 1

SB_DQ1

AY29

SB_DQ2

AW2 9

SB_DQ3

AV31

SB_DQ4

AU31

SB_DQ5

AV29

SB_DQ6

AU29

SB_DQ7

AY27

SB_DQ8

AW2 7

SB_DQ9

AY25

SB_DQ1 0

AW2 5

SB_DQ1 1

AV27

SB_DQ1 2

AU27

SB_DQ1 3

AV25

SB_DQ1 4

AU25

SB_DQ1 5

AM29

SB_DQ1 6

AK29

SB_DQ1 7

AL28

SB_DQ1 8

AK28

SB_DQ1 9

AR29

SB_DQ2 0

AN29

SB_DQ2 1

AR28

SB_DQ2 2

AP28

SB_DQ2 3

AN26

SB_DQ2 4

AR26

SB_DQ2 5

AR25

SB_DQ2 6

AP25

SB_DQ2 7

AK26

SB_DQ2 8

AM26

SB_DQ2 9

AK25

SB_DQ3 0

AL25

SB_DQ3 1

AY23

SB_DQ3 2

AW2 3

SB_DQ3 3

AY21

SB_DQ3 4

AW2 1

SB_DQ3 5

AV23

SB_DQ3 6

AU23

SB_DQ3 7

AV21

SB_DQ3 8

AU21

SB_DQ3 9

AY19

SB_DQ4 0

AW1 9

SB_DQ4 1

AY17

SB_DQ4 2

AW1 7

SB_DQ4 3

AV19

SB_DQ4 4

AU19

SB_DQ4 5

AV17

SB_DQ4 6

AU17

SB_DQ4 7

AR21

SB_DQ4 8

AR22

SB_DQ4 9

AL21

SB_DQ5 0

AM22

SB_DQ5 1

AN22

SB_DQ5 2

AP21

SB_DQ5 3

AK21

SB_DQ5 4

AK22

SB_DQ5 5

AN20

SB_DQ5 6

AR20

SB_DQ5 7

AK18

SB_DQ5 8

AL18

SB_DQ5 9

AK20

SB_DQ6 0

AM20

SB_DQ6 1

AR18

SB_DQ6 2

AP18

SB_DQ6 3

HASWELL--6--GP--U

71.HASWE.G0U

HSW_ULT_DDR3L

DDR CHANNEL B

4 OF19

SB_CK #0

SB_CK 0

SB_CK #1

SB_CK 1

SB_CK E0

SB_CK E1

SB_CK E2

SB_CK E3

SB_CS #0

SB_CS #1

SB_ODT0

SB_RA S#

SB_W E#

SB_CA S#

SB_BA 0

SB_BA 1

SB_BA 2

SB_MA 0

SB_MA 1

SB_MA 2

SB_MA 3

SB_MA 4

SB_MA 5

SB_MA 6

SB_MA 7

SB_MA 8

SB_MA 9

SB_MA 10

SB_MA 11

SB_MA 12

SB_MA 13

SB_MA 14

SB_MA 15

SB_DQS N0

SB_DQS N1

SB_DQS N2

SB_DQS N3

SB_DQS N4

SB_DQS N5

SB_DQS N6

SB_DQS N7

SB_DQS P0

SB_DQS P1

SB_DQS P2

SB_DQS P3

SB_DQS P4

SB_DQS P5

SB_DQS P6

SB_DQS P7

AU50

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AR40

AR42

AR45

AW4 6

AU46

AU47

AR46

AP46

AM38

AN38

AK38

AL38

AY49

AW4 9

AL35

AM36

AU49

AP40

AP42

AP45

AY46

AY47

AK36

AV47

AK33

AW3 0

AV26

AN28

AN25

AW2 2

AV18

AN21

AN18

AV30

AW2 6

AM28

AM25

AV22

AW1 8

AM21

AM18

M_B_DIM0_CKE2

M_B_DIM0_CKE3

M_B_DIM0_ODT0_TP

M_B_DIM0_CLK_DDR#013

M_B_DIM0_CLK_DDR0 13

M_B_DIM0_CLK_DDR#1 13

M_B_DIM0_CLK_DDR1 13

M_B_DIM0_CS#0 13

M_B_DIM0_CS#1 13

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DIM0_CKE0 13

M_B_DIM0_CKE113

1

TP506

M_B_RAS# 13

M_B_WE# 13

M_B_CAS# 13

M_B_BS0 13

M_B_BS1 13

M_B_BS2 13

M_B_DQS_DN0 13

M_B_DQS_DN1 13

M_B_DQS_DN2 13

M_B_DQS_DN3 13

M_B_DQS_DN4 13

M_B_DQS_DN5 13

M_B_DQS_DN6 13

M_B_DQS_DN7 13

M_B_DQS_DP0 13

M_B_DQS_DP1 13

M_B_DQS_DP2 13

M_B_DQS_DP3 13

M_B_DQS_DP4 13

M_B_DQS_DP5 13

M_B_DQS_DP6 13

M_B_DQS_DP7 13

1

1

TPAD14--OP--GP

M_B_A[15:0]13

TP504

TP505

TPAD14--OP--GP

TPAD14--OP--GP

CPU BOM CTRL

A A

M40

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,, Hsiiichiiih,,,

Eletro-X

5

Tiiitttllle

CPU (DDR)

DocumentttNumberrr

Siiize

A2

4

3

2

Wednesday,,, Febrrruarrry 26,,,2014

LF14M

1

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

Sheettt5 102Dattte:::

Rev

-1

offf

Page 9

SSID = CPU

5

4

3

2

1

D D

C C

B B

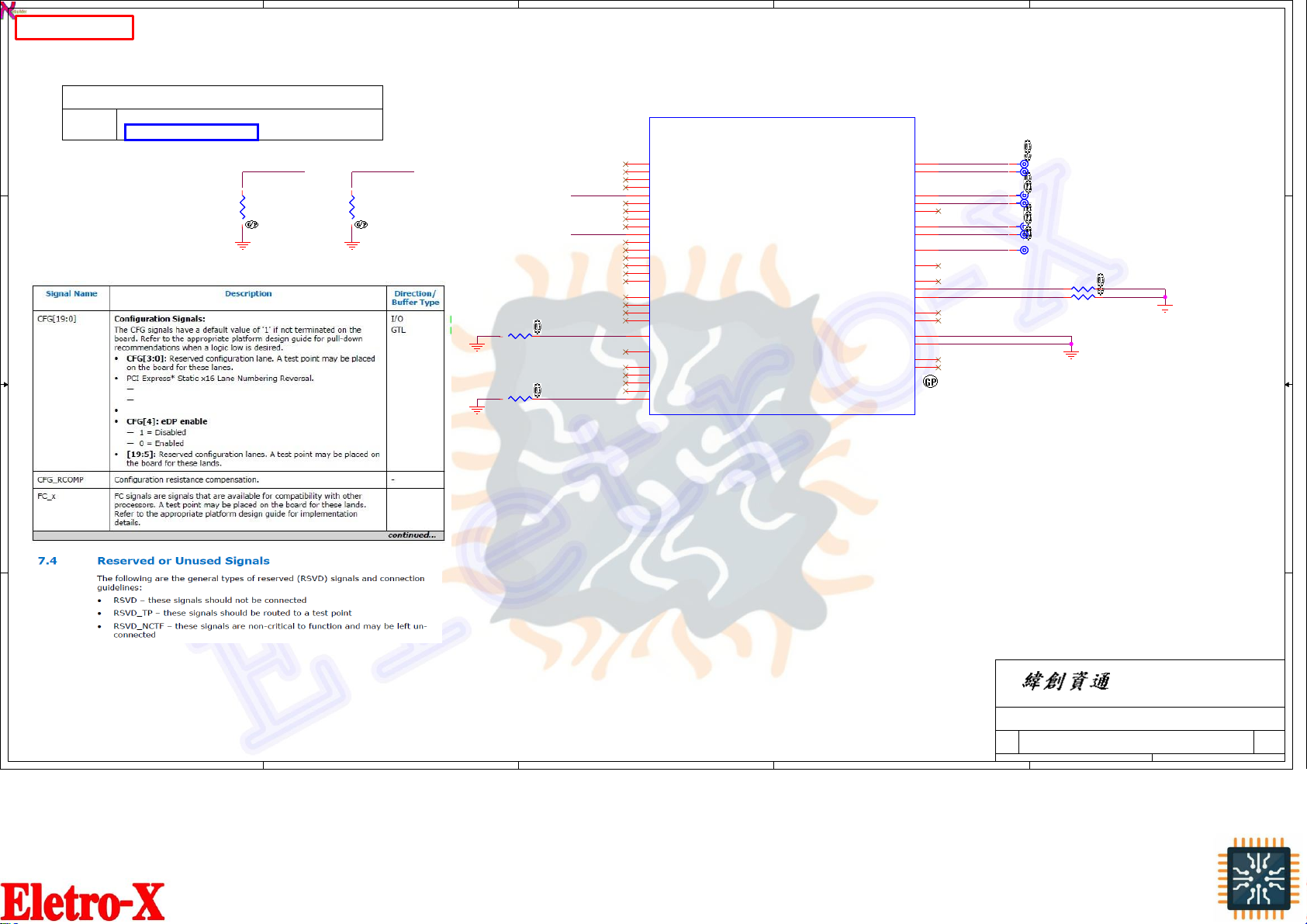

eDP Enable

CFG4

1:Disable

0:Enable

12

R601

1KR2J-L2-GP

CFG4

12

R602

1KR2J-L2-GP

DY

CFG9

R603

1 2

R604

1 2

49D9R2F-GP

8K2R2J-3-GP

CFG4

CFG9

CFG_RCOMP

TD_IREF

CPU1S

AC60

CFG0

AC62

CFG1

AC63

CFG2

AA63

CFG3

AA60

CFG4

Y62

CFG5

Y61

CFG6

Y60

CFG7

V62

CFG8

V61

CFG9

V60

CFG10

U60

CFG11

T63

CFG12

T62

CFG13

T61

CFG14

T60

CFG15

AA62

CFG16

U63

CFG18

AA61

CFG17

U62

CFG19

V63

CFG_RCOMP

A5

RSVD#A5

E1

RSVD#E1

D1

RSVD#D1

J20

RSVD#J20

H18

RSVD#H18

B12

TD_IREF

71.HASWE.G0U

HASWELL-6-GP-U

HSW_ULT_DDR3L

RESERVED

CPU BOMCTRL

19 OF 19

RSVD_TP#AV63

RSVD_TP#AU63

RSVD_TP#C63

RSVD_TP#C62

RSVD#B43

RSVD_TP#A51

RSVD_TP#B51

RSVD_TP#L60

RSVD#N60

RSVD#W23

RSVD#Y22

PROC_OPI_RCOMP

RSVD#AV62

RSVD#D58

VSS

VSS

RSVD#P20

RSVD#R20

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

RSVDAV63

RSVDAU63

RSVDC63

RSVDC62

RSVDA51

RSVDB51

RSVDL60

OPI_COMP3

OPI_COMP1

TP601

TP602

TP603

TP604

TP605

TP606

TP607

R605

R606

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

TPAD14-OP-GP

1

1

2

49D9R2F-GP

2

49D9R2F-GP

1

1

1

1

1

1

1

M40

A A

Tiiitllle

Siiize

Custom

5

4

3

2

Date:

CPU(CFG)

DocumentNumber

Wednesday, February 26,2014

LF14M

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

Rev

102

Sheet 6

1

of

-1

Eletro-X

Page 10

5 4 3 2 1

SSID = CPU

VDDQ_CPU1D35V_S3

PG701

1

2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

GAP-CLOSE-PWR

GAP-CLOSE-PWR

GAP-CLOSE-PWR

GAP-CLOSE-PWR

R712

1 2

0R0402-PAD

PG702

1

PG703

1

PG704

1

PG705

1

PG706

1

R711

VCC_CORE

2

2

2

2

2

1 DY2

1D05V_VTT

D D

1D05V_VTT VCOMP_OUT

Close to CPU

C C

1D05V_VTT

1

1

1D05V_VTT

1 2

B B

46 VCC_SENSE

R703

1 2

R704

1

R717

DY

10KR2J-L-GP

R710

DY

10KR2J-L-GP

R706

150R2F-4-L-GP

130R2F-1-GP

2

75R2F-2-GP

2

2

H_CPU_SVIDDAT

H_CPU_SVIDALRT#

17,26,36,46 IMVP_PWRGD

IMVP_PWRGD

VCCST_PWRGD

PWR_DEBUG

VCC_CORE

12

46 VR_SVID_ALERT#

46 H_CPU_SVIDCLK

46 H_CPU_SVIDDAT

46 H_VR_EN

R701

100R2F-L1-GP-U

R701 close to CPU

RN702

1

8

2

7

3

6

36,37,46,48 1.05VTT_PWRGD

A A

4 5

SRN10KJ-6-GP

VCCST_PWRGD

VCC_CORE

10KR2J-L-GP

VDDQ_CPU

SC22U6D3V5MX-L3-GP

TP702

TPAD14-OP-GP

R705

1

1D05V_VTT

C703

SC1U6D3V2KX-L-1-GP

2 1

VDDQ_CPU

VCC_SENSE

VCCIO_OUT

1

H_CPU_SVIDALRT#

2

43R2J-GP

VCCST_PWRGD

IMVP_PWRGD_R

PWR_DEBUG

C703,C715放放AC22 AE22 AE23

C715

DY

2 1

CPU1L

L59

RSVD#L59

J58

RSVD#J58

AH26

VDDQ

AJ31

VDDQ

AJ33

VDDQ

AJ37

VDDQ

AN33

VDDQ

AP43

VDDQ

AR48

VDDQ

AY35

VDDQ

AY40

VDDQ

AY44

VDDQ

AY50

VDDQ

F59

VCC

N58

RSVD#N58

AC58

RSVD#AC58

E63

VCC_SENSE

AB23

RSVD#AB23

A59

VCCIO_OUT

E20

VCCIOA_OUT

AD23

RSVD#AD23

AA23

RSVD#AA23

AE59

RSVD#AE59

L62

VIDALERT#

N63

VIDSCLK

L63

VIDSOUT

B59

VCCST_PWRGD

F60

VR_EN

C59

VR_READY

D63

VSS

H59

PWR_DEBUG#

P62

VSS

P60

RSVD_TP#P60

P61

RSVD_TP#P61

N59

RSVD_TP#N59

N61

RSVD_TP#N61

T59

RSVD#T59

AD60

RSVD#AD60

AD59

RSVD#AD59

AA59

RSVD#AA59

AE60

RSVD#AE60

AC59

RSVD#AC59

AG58

RSVD#AG58

U59

RSVD#U59

V59

RSVD#V59

AC22

VCCST

AE22

VCCST

AE23

VCCST

AB57

VCC

AD57

VCC

AG57

VCC

C24

VCC

C28

VCC

C32

VCC

HASWELL-6-GP-U

71.HASWE.G0U

CPU BOMCTRL

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

G35

G39

G43

G45

G49

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G37

G41

G47

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

Eletro-X

5 4 3 2 1

VCC_CORE

M40

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Tiiitllle

Siiize

A3

CPU(VCC_CORE)

DocumentNumber

Wednesday, February 26, 2014

Date: Sheet 7 of 102

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

Rev

-1

Page 11

5 4 3 2 1

SSID = CPU

D D

CPU1A

54 DDBP_DATA2#

C C

HDMI

DP to DOCKING

54 DDBP_DATA2

54 DDBP_DATA1#

54 DDBP_DATA1

54 DDBP_DATA0#

54 DDBP_DATA0

54 DDBP_DATA3#

54 DDBP_DATA3

63 PCH_DPC_N0

63 PCH_DPC_P0

63 PCH_DPC_N1

63 PCH_DPC_P1

C54

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

HASWELL-6-GP-U

71.HASWE.G0U

HSW_ULT_DDR3L

EDPDDII

1 OF19

EDP_T XN0

EDP_T XP0

EDP_T XN1

EDP_TXP1

EDP_T XN2

EDP_T XP2

EDP_T XN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_RCOMP

EDP_DISP

1

eDP_TXN0_CPU 52

eDP_TXP0_CPU 52

eDP_TXN1_CPU 52

eDP_TXP1_CPU 52

eDP_AUXN_CPU 52

eDP_AUXP_CPU 52

TP802

TPAD14-OP-GP

R801

1

VCOMP_OUT

2

24D9R2F-L-GP

CPU BOM CTRL

B B

A A

Eletro-X

5 4 3 2 1

M40

Wistron Corporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd., Hsiiichiiih,

Tiiitllle

CPU (DDI/EDP)

Document Number

Siiize

Custom

Wednesday, February 26, 2014

Date: Sheet 8 of 102

Taiiipeiii Hsiiien 221, Taiiiwan,R.O.C.

LF14M

Rev

-1

Page 12

SSID = CPU

5 4 3 2 1

CPU1P

D D

C C

D33

D34 J10

D35 J22

D37 J59

D38 J63

D39 K1

D41 K12

D42 L13

D43 L15

D45 L17

D46 L18

D47 L20

D49 L58

D5 L61

D50 L7

D51 M22

D53 N10

D54 N3

D55 P59

D57 P63

D59 R10

D62 R22

D8 R8

E11 T1

E17 T58

F20 U20

F26 U22

F30 U61

F34 U9

F38 V10

F42 V3

F46 V7

F50 W20

F54 W22

F58 Y10

F61 Y59

G18 Y63

G22

G3

G5

G6 AH46

G8 V23

H13 E62

HASWELL-6-GP-U

71.HASWE.G0U

HSW_ULT_DDR3L

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS

VSS

VSS

VSS VSS

VSS VSS

VSS VSS

VSS VSS_SENSE

CPU BOMCTRL

16 OF 19

VSS

VSS

H17

H57

V58

AH16

VSS_SENSE46

VSS_SENSE

R901 close to CPU

12

R901

100R2F-L1-GP-U

B B

A A

Eletro-X

5 4 3 2

M40

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Tiiitllle

Siiize Rev

A3

Date: Sheet 9

CPU(VSS)

DocumentNumber

Wednesday, February 26,2014

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

1

of

-1

102

Page 13

SSID = MEMORY

5 4 3 2 1

H = 4mm

DIIMM1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/A P

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/B A2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_D Q

30

RESET#

203

VTT1

204

VTT2

DDR3--204P--263--GP--U

SKT_DDR 204P SMD

RAS#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

EVENT#

VDDSP D

NC#1

NC#2

NC#/TES T

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

NP1

NP1

NP2

NP2

110

113

WE#

115

114

121

73

74

101

CK0

103

102

CK1

104

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

200

SDA

202

SCL

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

197

201

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

TS#_DIMM0_1

198

199

1D35V_S3

M_A_RAS# 5

M_A_WE# 5

M_A_CAS# 5

M_A_DIM0_CS#0 5

M_A_DIM0_CS#1 5

M_A_DIM0_CKE0 5

M_A_DIM0_CKE1 5

M_A_DIM0_CLK_DDR0 5

M_A_DIM0_CLK_DDR#0 5

M_A_DIM0_CLK_DDR1 5

M_A_DIM0_CLK_DDR#1 5

PCH_SMBDATA 13,18,62

PCH_SMBCLK 13,18,62

SCD1U16V2KX--L--GP

3D3V_S0

C1203

2 1

4 DDR_PG_CTRL

Q1201 Q120 2限限限84.05067.031

因因因因Vth因1V

1D35V_S3

C1204

SC10U6D3V3MX--L--GP

2 1

C1209

SC1U10V2KX--L1--GP

2 1

0D675V_S0

C1213 C1214 C1215C1216

SC1U10V2KX--L1--GP

2 1

SC1U10V2KX--L1--GP

SC1U10V2KX--L1--GP

2 1

Layout Note:

Place these Caps near

SO-DIMMA.

SODIMM A DECOUPLING

C1206

C1205

SC10U6D3V3MX--L--GP

SC10U6D3V3MX--L--GP

2 1

2 1

C1210

C1211

SC1U10V2KX--L1--GP

SC1U10V2KX--L1--GP

2 1

2 1

SC1U10V2KX--L1--GP

2 1

Place these caps

2 1

close to VTT1 and

VTT2.

SC10U6D3V3MX--L--GP

C1207

2 1

SC1U10V2KX--L1--GP

G

C1212

2 1

Q1202

DMN5L06K--7--GP

DS

84.05067.031

C1208

SC10U6D3V3MX--L--GP

2 1

1D35V_S3

3D3V_S51D35V_S3

R1206

220KR2J--L2--GP

2

1

5 M_VREF_DQ_DIMM0_C

G

DDR_PG_OUT 49

For Intel Recommend Close to DIMM

M_A_A0

M_A_A1

0D675V_S0

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DIM0_ODT0

M_A_DIM0_ODT1

VREF_CA

VREF_DQ0

5 M_A_A[15:0]

D D

5 M_A_BS2

5 M_A_BS0

5 M_A_BS1

5 M_A_DQ13

5 M_A_DQ8 5

M_A_DQ14 5

M_A_DQ10

5 M_A_DQ9 5

M_A_DQ12

5 M_A_DQ15

5 M_A_DQ11

5 M_A_DQ29

5 M_A_DQ28

5 M_A_DQ30

5 M_A_DQ31

5 M_A_DQ25

5 M_A_DQ24

5 M_A_DQ27

5 M_A_DQ26

5 M_A_DQ44

5 M_A_DQ41

5 M_A_DQ43

5 M_A_DQ47

5 M_A_DQ45

5 M_A_DQ40

5 M_A_DQ42

C C

B B

5 M_A_DQ46

5 M_A_DQ51

5 M_A_DQ50

5 M_A_DQ49

5 M_A_DQ48

5 M_A_DQ52

5 M_A_DQ53

5 M_A_DQ54

5 M_A_DQ55

5 M_A_DQ0

5 M_A_DQ1

5 M_A_DQ2

5 M_A_DQ6

5 M_A_DQ5

5 M_A_DQ4

5 M_A_DQ3

5 M_A_DQ7 5

M_A_DQ21 5

M_A_DQ20 5

M_A_DQ17 5

M_A_DQ16 5

M_A_DQ18 5

M_A_DQ19 5

M_A_DQ22 5

M_A_DQ23 5

M_A_DQ36 5

M_A_DQ33 5

M_A_DQ34 5

M_A_DQ38 5

M_A_DQ37 5

M_A_DQ32 5

M_A_DQ35 5

M_A_DQ39 5

M_A_DQ62 5

M_A_DQ58 5

M_A_DQ60 5

M_A_DQ61 5

M_A_DQ63 5

5 M_A_DQS_DN1

M_A_DQ59 5

5 M_A_DQS_DN3

M_A_DQ56 5

5 M_A_DQS_DN5

M_A_DQ57

5 M_A_DQS_DN6

5 M_A_DQS_DN0

5 M_A_DQS_DN2

5 M_A_DQS_DN4

5 M_A_DQS_DN7

5 M_A_DQS_DP1

5 M_A_DQS_DP3

5 M_A_DQS_DP5

5 M_A_DQS_DP6

5 M_A_DQS_DP0

5 M_A_DQS_DP2

5 M_A_DQS_DP4

5 M_A_DQS_DP7

13,37 VREF_CA

13,37 DDR3_DRAMRST#

Note:

If SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is0x30

If SA0 DIM0 = 1, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA2

SO-DIMMA TS Address is0x32

Thermal EVENT

TS#_DIMM0_1

DS

Q1201

DMN5L06K--7--GP

84.05067.031

M_A_B_DIM_ODT

R1208

1 2

C1217

SCD022U16V2KX--3GP

2 1

VREF_DIMM0

R1210

24D9R2F--L--GP

2 1

R1201

2

1

10KR2J--L--GP

ODT resistor must be 66.5 ohm

1 2

1 2

1 2

1 2

1D35V_S3

R1207

1K8R2F--GP

2

1

VREF_DQ0

2R2J--2--GP

R1209

1K8R2F--GP

2

1

3D3V_S0

R1202

66D5R2F--GP

R1203

66D5R2F--GP

R1204

66D5R2F--GP

R1205

66D5R2F--GP

M_A_DIM0_ODT0

M_A_DIM0_ODT1

M_B_DIM0_ODT0 13

M_B_DIM0_ODT1 13

62.10024.S61

VREF_CA VREF_DQ0

C1201

A A

SCD1U16V2KX--L--GP

2 1

C1202

SCD1U16V2KX--L--GP

2 1

Close RAM1 CA & DQ pin

Eletro-X

5 4 3 2

1ST =62.10024.S61

2ND =62.10024.M51

M40

Tiiitttllle

DDR3L-SODIMM1

Siiize DocumentttNumberrr

A2

Wednesday,,, Febrrruarrry 26,,,2014

Dattte:::

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,, Hsiiichiiih,,,

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

LF14M

1

Sheettt 12 offf

Rev

-1

102

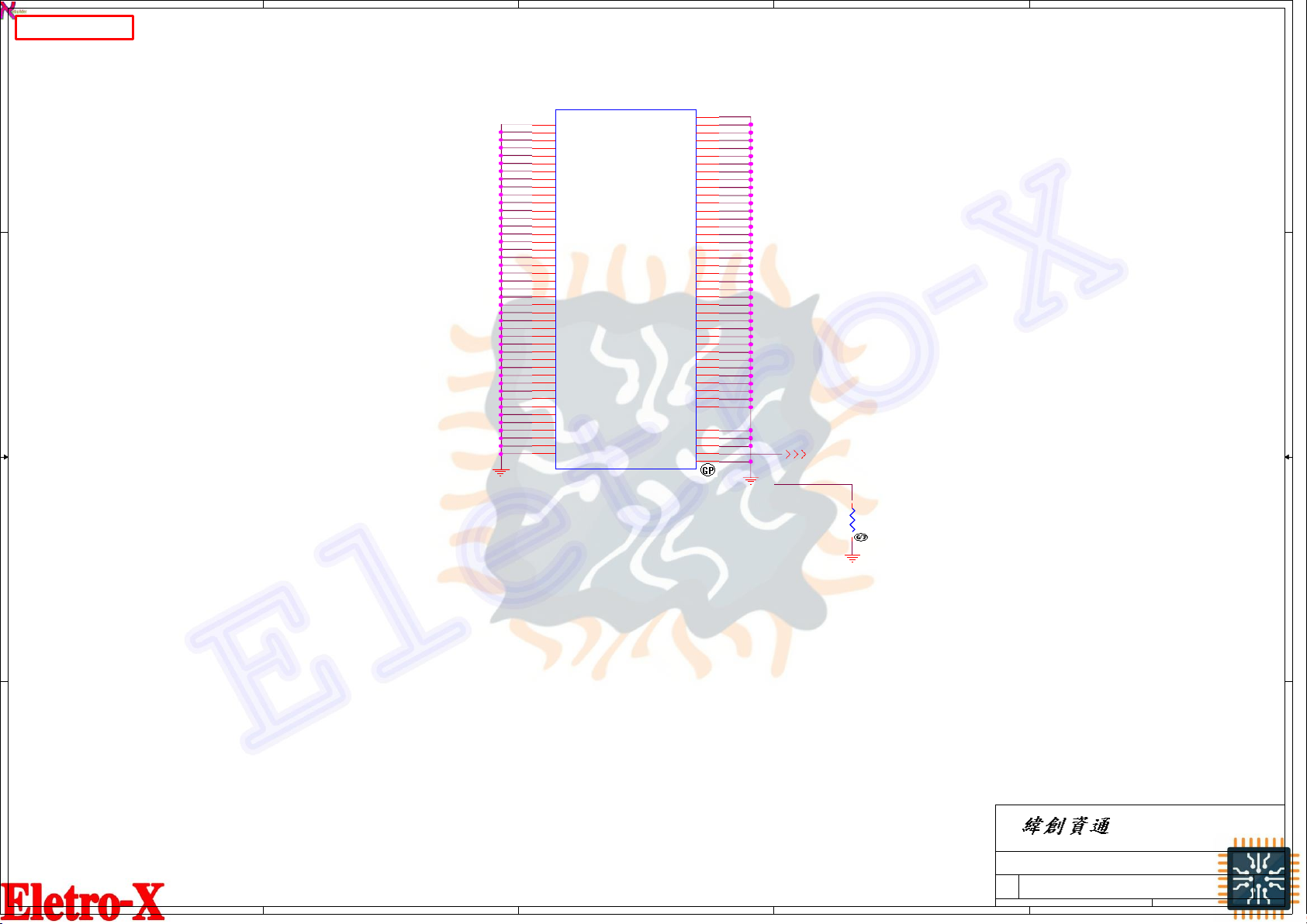

Page 14

SSID = MEMORY

5 4 3 2 1

M_B_A0

M_B_A1

M_B_A2

M_B_A3

0D675V_S0

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

VREF_CA

VREF_DQ1

5 M_B_A[15:0]

D D

5 M_B_BS2

5 M_B_BS0

5 M_B_BS1

5 M_B_DQ4

5 M_B_DQ1

5 M_B_DQ3

5 M_B_DQ7

5 M_B_DQ5

5 M_B_DQ0

5 M_B_DQ2

5 M_B_DQ6 5

M_B_DQ21 5

M_B_DQ20 5

M_B_DQ22 5

M_B_DQ23 5

M_B_DQ16 5

M_B_DQ17 5

M_B_DQ19 5

M_B_DQ18 5

M_B_DQ36 5

M_B_DQ33 5

M_B_DQ35 5

M_B_DQ39 5

M_B_DQ37 5

M_B_DQ32 5

M_B_DQ34 5

M_B_DQ38 5

M_B_DQ52 5

M_B_DQ49 5

M_B_DQ48 5

M_B_DQ53 5

C C

B B

12 M_B_DIM0_ODT0

12 M_B_DIM0_ODT1

M_B_DQ51 5

M_B_DQ55 5

M_B_DQ54 5

M_B_DQ50

5 M_B_DQ8 5

M_B_DQ14

5 M_B_DQ10

5 M_B_DQ11

5 M_B_DQ12

5 M_B_DQ9 5

M_B_DQ13 5

M_B_DQ15 5

M_B_DQ28 5

M_B_DQ29 5

M_B_DQ26 5

M_B_DQ27 5

M_B_DQ25 5

M_B_DQ24 5

M_B_DQ30 5

M_B_DQ31 5

M_B_DQ40 5

M_B_DQ41 5

M_B_DQ46 5

M_B_DQ42 5

M_B_DQ45 5

M_B_DQ44 5

M_B_DQ47 5

M_B_DQ43 5

M_B_DQ56 5

M_B_DQ57 5

M_B_DQ59 5

M_B_DQ58 5

M_B_DQ61 5

M_B_DQ60 5

M_B_DQ63 5

M_B_DQ62

5 M_B_DQS_DN0

5 M_B_DQS_DN2

5 M_B_DQS_DN4

5 M_B_DQS_DN6

5 M_B_DQS_DN1

5 M_B_DQS_DN3

5 M_B_DQS_DN5

5 M_B_DQS_DN7

5 M_B_DQS_DP0

5 M_B_DQS_DP2

5 M_B_DQS_DP4

5 M_B_DQS_DP6

5 M_B_DQS_DP1

5 M_B_DQS_DP3

5 M_B_DQS_DP5

5 M_B_DQS_DP7

12,37 VREF_CA

12,37 DDR3_DRAMRST#

DIIMM2

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/A P

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/B A2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_D Q

30

RESET#

203

VTT1

204

VTT2

DDR3--204P--262--GP--U

SKT_DDR 204P SMD

EVENT#

VDDSP D

NC#/TES T

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

NP1

NP2

RAS#

WE#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

SDA

SCL

SA0

SA1

NC#1

NC#2

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NP1

NP2

110

113

115

114

121

73

74

101

103

102

104

11

28

46

63

136

153

170

187

200

202

TS#_DIMM1_1

198

199

197

SA1_DIM1

201

77

122

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

1D35V_S3

M_B_RAS# 5

M_B_WE# 5

M_B_CAS# 5

M_B_DIM0_CS#0 5

M_B_DIM0_CS#1 5

M_B_DIM0_CKE0 5

M_B_DIM0_CKE1 5

M_B_DIM0_CLK_DDR0 5

M_B_DIM0_CLK_DDR#0 5

M_B_DIM0_CLK_DDR1 5

M_B_DIM0_CLK_DDR#1 5

PCH_SMBDATA 12,18,62

PCH_SMBCLK 12,18,62

R1302

1 2

10KR2J--L--GP

3D3V_S0

C1301

2 1

SCD1U16V2KX--L--GP

LayoutNote:

Place these Caps near

SO-DIMMB.

1D35V_S3

SODIMM B DECOUPLING

12

C1304

SC6P50V2CN-1GP

C1310

SC1U10V2KX--L1--GP

2 1

0D675V_S0

C1314 C1315

SC1U10V2KX--L1--GP

SC1U10V2KX--L1--GP

2 1

2 1

12

12

C1305

C1306

SC33P50V2JN-3GP

SC10U6D3V3MX--L--GP

C1311

C1312

SC1U10V2KX--L1--GP

SC1U10V2KX--L1--GP

2 1

2 1

C1316

C1317

SC1U10V2KX--L1--GP

SC1U10V2KX--L1--GP

2 1

2 1

Note:

SO-DIMMB SPD Address is 0xA4

SO-DIMMB TS Address is 0x34

SO-DIMMB is placed farther from

the Processor than SO-DIMMA

Thermal EVENT

TS#_DIMM1_1

12

12

C1307

SC10U6D3V3MX--L--GP

C1313

SC1U10V2KX--L1--GP

2 1

12

C1308

C1309

SC10U6D3V3MX--L--GP

SC10U6D3V3MX--L--GP

Place these caps

close to VTT1 and

VTT2.

3D3V_S0

R1301

1 2

10KR2J--L--GP

5 M_VREF_DQ_DIMM1_C

1 2

C1318

SCD022U16V2KX--3GP

2 1

VREF_DIMM1

R1306

24D9R2F--L--GP

2 1

For Intel Recommend Close to DIMM

R1304

2R2J--2--GP

1D35V_S3

2

2

1

1

R1303

1K8R2F--GP

R1305

1K8R2F--GP

VREF_DQ1

62.10024.S21

1ST =62.10024.S21

2ND =62.10024.M31

VREF_DQ1VREF_CA

A A

Eletro-X

5 4 3 2

C1302

SCD1U16V2KX--L--GP

2 1

Close RAM3 CA & DQ pin

C1303

SCD1U16V2KX--L--GP

2 1

M40

Tiiitttllle

DDR3L-SODIMM2

Siiize DocumentttNumberrr

A2

Wednesday,,, Febrrruarrry 26,,,2014

Dattte:::

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,, Hsiiichiiih,,,

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

LF14M

1

Sheettt 13 offf

Rev

-1

102

Page 15

5 4 3 2 1

3D3V_S0

4

3

D D

52 L_BKLT_CTRL

52 L_BKLT_EN

52 LVDS_VDD_EN

R1501

1

100KR2J-4-GP

3D3V_S0

R1509

1 2

R1510

1DY2

C C

RN1502

SRN10KJ-6-GP

1

2

3

4

INT_PIRQC#

10KR2J-L-GP

DGPU_PWR_EN#

10KR2J-L-GP

8

INT_PIRQD#

7

INT_SERIRQ

6

PCIE_CLK_LAN_REQ#

5

L_BKLT_EN

2

INT_SERIRQ 20,24

PCIE_CLK_LAN_REQ# 18,30

R1503

DGPU_PWR_EN#

1 2

10KR2J-L-GP

OPS

19 INT_PIRQA#

18 INT_PIRQB#

TPAD14-OP-GP TP1501

76 GPU_EVENT#

76 DGPU_HOLD_RST#

76 GC6_FB_EN_PCH

24,73,83 DGPU_PWROK

76,83 DGPU_PWR_EN#

INT_PIRQA#

INT_PIRQB#

INT_PIRQC#

INT_PIRQD#

MCP_PME

1

GPU_EVENT#

GC6_FB_EN_PCH

CPU1I

B8

EDP_BKLCTL

A9

EDP_BKLEN

eDP SIIDEBAND

EDP_VDDEN

PIRQA#/GPIO77

PIRQB#/GPIO78

PIRQC#/GPIO79

PIRQD#/GPIO80

PME#

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

HASWELL-6-GP-U

71.HASWE.G0U

AD4

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

CPU BOMCTRL

PCIIE

HSW_ULT_DDR3L

DIISPLAY

9 OF 19

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

DDPB_AUXN

C5

B6

DDPB_AUXP 1TP1503

B5

A6

C8

A8

D6

RN1503

SRN2K2J-5-GP

1

2

PCH_HDMI_CLK54

DDPC_CTRLCLK

DDPC_CTRLDATA

1

eDP_HPD_CPU

PCH_HDMI_DATA 54

TP1502TPAD14-OP-GP

TPAD14-OP-GP

PCH_DPC_AUXN 63

PCH_DPC_AUXP 63

1 2

R1504 1KR2J-1-GP

12

R1506

100KR2F-L1-GP

Wait Test new eDP_HPD method

3D3V_S0

4

3

RN1504

SRN2K2J-5-GP

DK

1

2

HDMI_PCH_DET54

DOCK_PCH_HPD63

TP1505 TPAD14-OP-GP

1

TP1506TPAD14-OP-GP

1

EMB_HPD 52

(Simulation HPD signal)

Reduce Cable Pin

B B

DGPU_HOLD_RST#

12

R1502

10KR2J-L-GP

OPS

A A

Eletro-X

5 4 3 2

GC6_FB_EN_PCH

12

R1505

10KR2J-L-GP

GC6

<CoreDesiiign>

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Tiiitllle

CPU(EDP SIDEBAND/GPIO/DDI)

Siiize DocumentNumber

A3

Wednesday, February 26,2014

Date: Sheet 15

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

1

Rev

-1

102

of

Page 16

5 4 3 2 1

2014/2/6

SSID = PCH

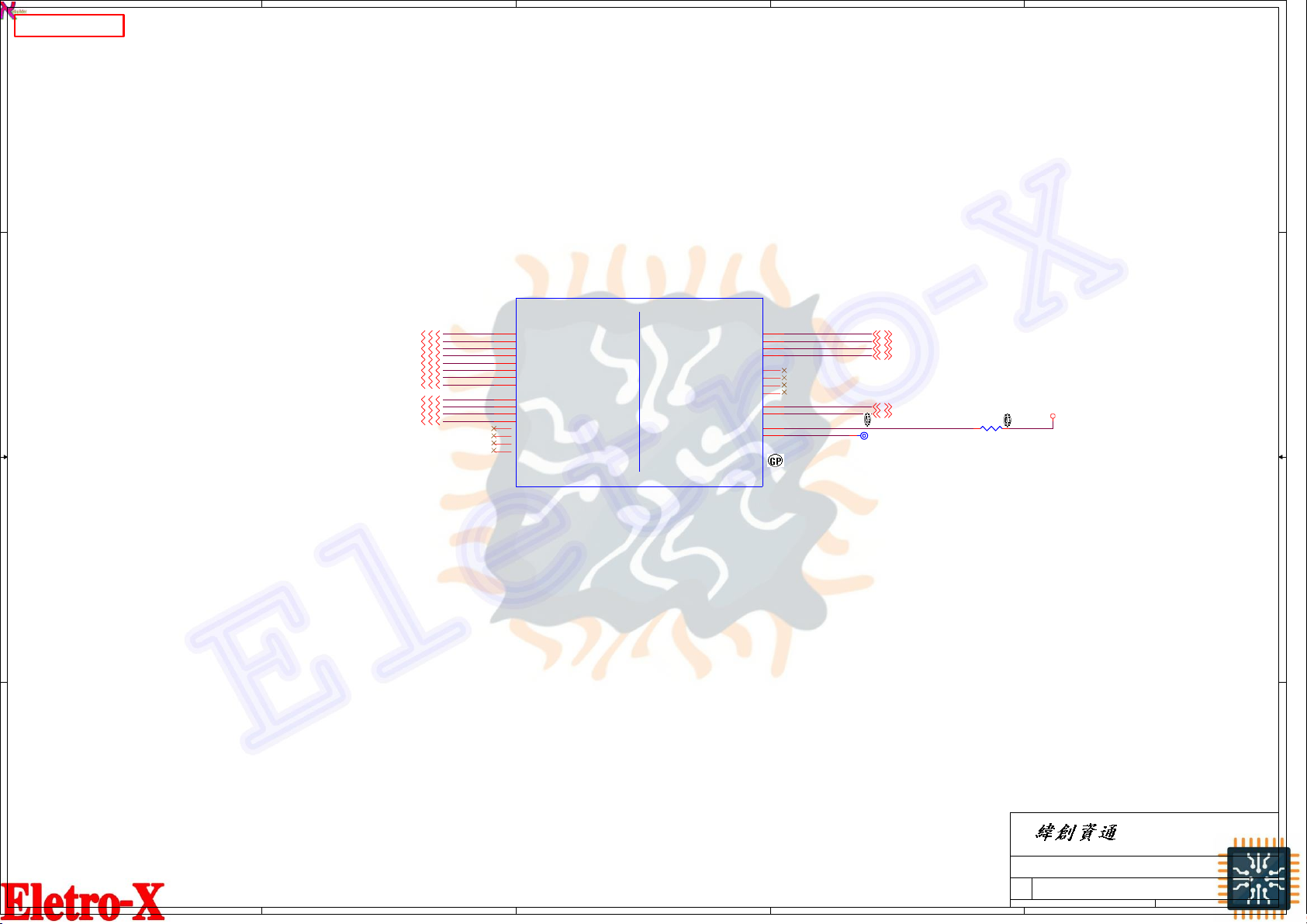

HSW_ULT_DDR3L

PCIIE USB

B29

A27

F10

E10

C23

C22

F8

E8

B23

A23

H10

G10

B21

C21

E6

F6

B22

A21

G11

F11

C29

B30

F13

G13

A29

G17

F17

C30

C31

F15

G15

B31

A31

E15

E13

RSVD#E13

B27

CPU1K

PERN5_L0

PERP5_L0

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD#E15

PCIE_RCOMP

PCIE_IREF

HASWELL-6-GP-U

D D

73 PEG_RXN0

73 PEG_RXP0

73 PEG_TXN0

73 PEG_TXP0

73 PEG_RXN1

73 PEG_RXP1

73 PEG_TXN1

GPU PEG BUS

C C

WLAN

LAN

73 PEG_TXP1

73 PEG_RXN2

73 PEG_RXP2

73 PEG_TXN2

73 PEG_TXP2

73 PEG_RXN3

73 PEG_RXP3

73 PEG_TXN3

73 PEG_TXP3

58 PCIE_RXN3

58 PCIE_RXP3

58 PCIE_TXN3

58 PCIE_TXP3

30 PCIE_RXN4

30 PCIE_RXP4

30 PCIE_TXN4

30 PCIE_TXP4

DOCKING

63 PCIE_RXN2

Card Reader

(PCIE/USB3.0)

B B

63 PCIE_RXP2

63 PCIE_TXN2

63 PCIE_TXP2

C1601

C1602

C1603

C1605

C1606

C1607

C1608

C1609

C1610

C1621

C1622

63 USB3_3_RX3_N

63 USB3_3_RX3_P

63 USB3_3_TX3_N

63 USB3_3_TX3_P

+V1.05S_AUSB3PLL

C1604

1

1 2

1

1

1

1

1

1

1 2

1 2

1 2

1 2

R1601

1

OPS

SCD1U16V2KX-L-GP PEG_TXN0_C

SCD1U16V2KX-L-GP PEG_TXP0_C

2

OPS

SCD1U16V2KX-L-GP PEG_TXN1_C

2

OPS

SCD1U16V2KX-L-GP PEG_TXP1_C

2

OPS

SCD1U16V2KX-L-GP PEG_TXN2_C

2

OPS

SCD1U16V2KX-L-GP PEG_TXP2_C

2

OPS

SCD1U16V2KX-L-GP PEG_TXN3_C

2

OPS

SCD1U16V2KX-L-GP PEG_TXP3_C

2

OPS

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

2

3K01R2F-3-GP

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_TXN4_C

PCIE_TXP4_C

PCIE_COMP

71.HASWE.G0U

CPU BOMCTRL

11 OF 19

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS#

USBRBIAS

RSVD#AN10

RSVD#AM10

OC0/GPIO40#

OC1/GPIO41#

OC2/GPIO42#

OC3/GPIO43#

USB_PP1/PN1改 改 改 USB2.0 Port 0

USB_PP0/PN0改 改 改 USB2.0 Port 1

NET維維維維

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

A33

AJ11

AN10

AM10

AT1

AH2

AV3

B33

AJ10

AL3

USB_PN0

USB_PP0

USB_RBIAS

USB_OC#0

USB_OC#1

USB_OC#2

USB_OC#3

USB_OC#0

USB_OC#1

USB_OC#3

USB_OC#2

1

USB_PN1 34,35

USB_PP1 34,35

R1620 2 0R0402-PAD

1

R1621 2 0R0402-PAD

1

USB_PN2 63

USB_PP2 63

USB_PN3 52

USB_PP3 52

USB_PN4 63

USB_PP4 63

USB_PN5 58

USB_PP5 58

USB_PN6 63

USB_PP6 63

USB_PN7 52

USB_PP7 52

R1602

2

22D6R2F-L1-GP

1 8

2 7

3 6

4 5

USB3_1_RX1_N 34

USB3_1_RX1_P 34

USB3_1_TX1_N 34

USB3_1_TX1_P 34

USB_OC#034,35

USB_OC#1 63

USB_OC#2 63

3D3V_SUS

RN1601

SRN10KJ-7GP

-7GP

USB3.0 SKT

USB_PN0_R 63,89

USB_PP0_R 63,89

USB2.0 Table

Pair Device

0

USB3.0 Port 1 (with Debug Function)

1

Fingerprint / USB3.0 Card Reader(DY)

2

USB2.0 Port 2

3

Camera

4

USB2.0 Port 3

5

WLAN(Bluetooth)

6

USB3.0 to DOCKING

7

Panel Touch

USB 3.0 Table

Pair Device

1

Combined with USB2.0 port1

2

Reserved

3

USB3.0 to DOCKING

4

USB 3.0 Card Reader

USB OverCurrent (OC#)

Pair Device

0C#0

USB3.0 port1

0C#1

USB2.0 port2

0C#2

USB2.0 port3

0C#3

Reserved

Need Test if not Stuff

A A

Eletro-X

5 4 3 2

M40

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Tiiitllle

Siiize DocumentNumber

A3

Date: Sheet 16

CPU(PCI/USB)

Wednesday, February 26,2014

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

1

Rev

-1

102

of

Page 17

SSID = PCH

5 4 3 2 1

D D

DSWODVREN - On Die DSW VR Enable

HIGH Enabled (DEFAUL T)

LOW Disabled

NonDS3

R1714

1

1

DY

R1716

DS3

TP1708

TP1707

TPAD14-OP-GP

1

DSWODVREN

PM_RSMRST#

2

0R2J-2-GP

AFTP1702

AFTP1705

1

2

0R2J-L-GP

12

DY

TPAD14-OP-GP

R1717

10KR2J-L-GP

1

1

PCIE_WAKE#58

PM_CLKRUN#_EC 24

TP1704

1

PCH_SUSCLK_KBC 58

1

TP1703

PM_SLP_S4# 24,49

PM_SLP_S3# 24

PM_SLP_A# 24

PM_SLP_SUS# 24,38

KBC_DPWROK 24

DS3

PM_SUSWARN#

PM_CLKRUN#_EC

PM_SUS_STAT#

DY

3D3V_S0

1

C C

B B

7,26,36,46 IMVP_PWRGD

24 S0_PWR_GOOD

24,30,36,58,63,65,76 PLT_RST#

R1705

1

DY

R1706

1

DY

R1707

1

3D3V_S5

RN1701

1

2

SRN10KJ-L-GP

3D3V_S5

R1724

1

R1723

1

R1701

2

10KR2J-L-GP

36 PCH_PWROK

2

10KR2J-L-GP

2

10KR2J-L-GP

2

10KR2J-L-GP

PM_PWRBTN#

4

BATLOW#

3

2

10KR2J-L-GP

2

10KR2J-L-GP

Follow Intel CRB

SYS_RESET#

S0_PWR_GOOD

PCH_PWROK

PCIE_WAKE#

AC_PRESENT

1

PM_RSMRST#

R1702

1 DY2

R1703 20R0402-PAD

1

1

TP1701

TPAD14-OP-GP

TP1706

TPAD14-OP-GP

PA

0R2J-L-GP

24 PM_SUSWARN#

24 PM_PWRBTN#

24 AC_PRESENT

TPAD14-OP-GP

TP1702

1

TPAD14-OP-GP

TPAD14-OP-GP

TP1720

TPAD14-OP-GP

R1708

1

0R0402-PAD

PCH_PWROK_R

24 PM_SUSACK#

TP1721

1

TP1719

PM_SUSACK#PM_SUSWARN#

2

R1704

1

0R0402-PAD

2

1

1

3D3V_AUX_KBC

PM_SUSACK#

SYS_RESET#

SYS_PWROK_R

PCH_PWROK_R

PM_RSMRST#

PM_SUSWARN#

BATLOW#

PM_SLP_S0#

SLP_WLAN#

12

R1710

100KR2J-4-GP

3V_5V_POK_#

CPU1H

AK2

SUSACK#

AC3

SYS_RESET#

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST#

AW6

RSMRST#

AV4

SUSWARN#/SUSPWRDNACK#/GPIO30

AL7

PWRBTN#

AJ8

ACPRESENT/GPIO31

AN4

BATLOW#/GPIO72

AF3

SLP_S0#

AM5

SLP_WLAN#/GPIO29

HASWELL-6-GP-U

71.HASWE.G0U

CPU BOMCTRL

NonRD17S093

1 2

100KR2J-4-GP

Q1701

5

6 1

2N7002KDW-GP

84.2N702.A3F

2ND =75.00601.07C

HSW_ULT_DDR3L

SYSTEM POWERMANAGEMENT

34

2

PM_RSMRST# R1711

3V_5V_POK_C

8 OF 19

DSWVRMEN

DPWROK

WAKE#

CLKRUN#/GPIO32

SUS_STAT#/GPIO61

SUSCLK/GPIO62

SLP_S5#/GPIO63

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS#

SLP_LAN#

2

1

R1712 1KR2J-L2-GP

2

1

0R2J-2-GP

R1713

2

1

DS3

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

Non DS3

PM_SLP_SUS#

0R2J-L-GP

DSWODVREN

PCH_DPWROK

PM_SUS_STAT#

PCH_SUSCLK_KBC

PM_SLP_S5#

SLP_A#

PM_SLP_SUS#

PCH_DPWROK

SLP_A#

TP1709

1

TP1705

TPAD14-OP-GP

1

R1715 20R2J-L-GP

1

PM_SLP_S3#

1

1

RSMRST#_KBC24

3V_5V_POK 45

TPAD14-OP-GP

R1721

2

330KR2J-L-GP

R1722

2

330KR2J-L-GP

TPAD14-OP-GP

TPAD14-OP-GP

1

1

1 2

RTC_AUX_S5

R1718

1KR2J-L2-GP

R1719

8K2R2J-3-GP

R1720

10KR2J-L-GP

3D3V_SUS

2

3D3V_S0

2

3D3V_SUS

A A

Eletro-X

5 4 3 2

<CoreDesiiign>

WistronCorporation

21F, 88, Sec.1, Hsiiin Taiii Wu Rd.,Hsiiichiiih,

Tiiitllle

Siiize DocumentNumber

A3

Date: Sheet 17

CPU(DMI/FDI/PM)

Wednesday, February 26,2014

LF14M

Taiiipeiii Hsiiien 221, Taiiiwan, R.O.C.

1

Rev

-1

102

of

Page 18

SSID = PCH

5

4

3

2

1

CPU1F

D D

CK_REQ

CK_REQ

3D3V_S0

Close to PCH

RN1801

SRN10KJ--6--GP

1

2

3

4

8

INT_PIRQB#

7

CK_REQ

6

HDD_LED#

5

MCP_GPIO36

PCIE Card Reader

MCP_GPIO36 19

INT_PIRQB# 15

HDD_LED#19,63

20,63 CLK_PCIE_CARD_REQ#

WLA N

20,58 CLK_PCIE_WLAN_REQ#

LAN

PCIE_CLK_LAN_REQ#

GPU PEG BUS

63 CLK_PCIE_CARD#

63 CLK_PCIE_CARD

58 CLK_PCIE_WLAN#

58 CLK_PCIE_WLAN

30 PCIE_CLK_LAN#

30 PCIE_CLK_LAN 15,30

73 CLK_PCIE_VGA#

73 CLK_PCIE_VGA

19,73 PEG_CLKREQ#

C43

CLKOUT_P CIE_N0

C42

CLKOUT_P CIE_P0

U2

PCIECL KRQ0#/GPIO1 8

B41

CLKOUT_P CIE_N1

A41

CLKOUT_P CIE_P1

Y5

PCIECL KRQ1#/GPIO1 9

C41

CLKOUT_P CIE_N2

B42

CLKOUT_P CIE_P2

AD1

PCIECL KRQ2#/GPIO2 0

B38

CLKOUT_P CIE_N3

C37

CLKOUT_P CIE_P3

N1

PCIECL KRQ3#/GPIO2 1

A39

CLKOUT_P CIE_N4

B39

CLKOUT_P CIE_P4

U5

PCIECL KRQ4#/GPIO2 2

B37

CLKOUT_P CIE_N5

A37

CLKOUT_P CIE_P5

T2

PCIECL KRQ5#/GPIO2 3

HASWELL--6--GP--U

71.HASWE.G0U

HSW_ULT_DDR3L

CLOCK

SIIGNALS

CPU BOM CTRL

C C

24,65 LPC_AD[0..3]

LPC_AD0

LPC_AD1

LPC_AD2

TP1807

TP1808

LPC_AD3

1

1

SPI_CS1#

SPI_CS2#

24,65 LPC_FRAME#

B B

24,25 SPI_CLK_R

24,25 SPI_CS0#_R

24,25 SPI_SI0_R

24,25 SPI_SO_R

25 SPI0_WP#

25 SPI_HOLD_0#

TPAD14--OP--GP

TPAD14--OP--GP

CPU1G

AU14

LAD0

AW1 2

LAD1

AY12

LAD2

AW1 1

LAD3

AV12

LFRAME #

AA3

SPI_CL K

Y7

SPI_CS 0#

Y4

SPI_CS 1#

AC2

SPI_CS 2#

AA2

SPI_MOS I

AA4

SPI_MIS O

Y6

SPI_IO2

AF1

SPI_IO3

HASWELL--6--GP--U

71.HASWE.G0U

HSW_ULT_DDR3L

LPC

SMBUS

SML1A LERT#/PCHHOT#/ GPIO73

C--LIINKSPII

CPU BOM CTRL

A A

6 OF19

XTAL24_ IN

XTAL24_ OUT

RSVD#K 21

RSVD#M 21

DIFFCLK _BIASREF

TESTLOW _C35

TESTLOW _C34

TESTLOW _AK8

TESTLOW _AL8

CLKOUT_L PC_0

CLKOUT_L PC_1

CLKOUT_ITP XDP#

CLKOUT_ITP XDP_P

7 OF19

SMBAL ERT#/GPIO11

SMBCL K

SMBDA TA

SML0A LERT#/GPIO60

SML0CL K

SML0DA TA

SML1CL K/GPIO75

SML1DA TA/GPIO74

CL_CLK

CL_DATA

CL_RST#

XTAL24_IN

A25

XTAL24_OUT

B25

K21

M21

DIFFCLK_BIAS

C26

C35

CLK_BUF_CKSSCD_P

C34

CLK_BUF_DOT96_P

AK8

CLK_BUF_DOT96_N

AL8

CLK_PCI_LPC_R

AN15

CLK_PCI_TPM_R

AP15

B35

PCIE_CLK_XDP_P

A35

MCP_GPIO11

AN2

AP2

AH1

MCP_GPIO60

AL2

AN1

AK1

MCP_GPIO73

AU4

AU3

AH3

AF2

AD2

AF4

CLK_BUF_CKSSCD_N

PCIE_CLK_XDP_N

SMB_CLK

SMB_DATA

SML0_CLK

SML0_DATA

CL_CLK_WLAN

CL_DATA_WLAN

CL_RST_WLAN#

R1801

R1803

1

R1804

1

1

1

MCP_GPIO11 20

MCP_GPIO60 20

MCP_GPIO73 20

SML1_CLK 24,26,52,76

SML1_DATA 24,26,52,76

Need Reserved Resistance

+V1.05S_AXCK_LCPLL

2

1

3K01R2F--3--GP

2

22R2J--2--GP

2

22R2J--2--GP

TP1803

TPAD14--OP--GP

TP1804

TPAD14--OP--GP

CL_CLK_WLAN 58

CL_DATA_WLAN 58

CL_RST_WLAN# 58

EC1802

SC10P50V2JN-L1--GP

DY

2 1

SMB_DATA

TP1805

TP1806

1

SMB_CLK

1

TPAD14--OP--GP

TPAD14--OP--GP

EC / Therma/ Digital G-sensor/ VGA

20 MCP_GPIO45

20 MCP_GPIO47

20 MCP_GPIO14

3D3V_S0

1

2 3

SRN2K2J--5--GP

4 3

2N7002KDW--GP

84.2N702.A3F

2nd =75.00601.07C

SMB_CLK

SMB_DATA

SML0_DATA

SML0_CLK

SML1_CLK

SML1_DATA

CLK_PCI_KBC 24

CLK_PCI_DB 65

RN1804

4

Q1801

1256

3 2

4 1

3 2

4 1

3 2

4 1

MCP_GPIO45

MCP_GPIO47

MCP_GPIO14

SRN2K2J--5--GP

RN1805

RN1806

SRN2K2J--5--GP

RN1807

SRN2K2J--5--GP

RN1808

8

7

6

5

SRN10KJ--6--GP

XTAL24_IN

XTAL24_OUT

PCH_SMBDATA 12,13,62

PCH_SMBCLK 12,13,62

3D3V_SUS

3D3V_SUS

1

2

3

4

R1805

1MR2J--L3--GP

2

1

CLK_BUF_CKSSCD_N

CLK_BUF_CKSSCD_P

CLK_BUF_DOT96_P

CLK_BUF_DOT96_N

Need very close to PC H

1 2

RN1802

2

1

SRN10KJ--L--GP

RN1803

2 3

1 4

SRN10KJ--L--GP

X1801

XTAL--24MHZ--74--GP

82.30004.781

3

4

C1801

1 2

SC12P50V2JN--3GP

C1802

1 2

SC12P50V2JN--3GP

Eletro-X

5

<Corrre Desiiign>

Wistron Corporation

21F,,, 88,,, Sec...1,,, Hsiiin Taiii Wu Rd...,,, Hsiiichiiih,,,

LF14M

1

Taiiipeiii Hsiiien 221,,, Taiiiwan,,,R...O...C...

Sheettt 18 offf 102Dattte:::

Rev

-1

Tiiitttllle

CPU (PCI-E/SMBUS/CLOCK/CL)

DocumentttNumberrr

Siiize

A2

4

3

2

Wednesday,,, Febrrruarrry 26,,,2014

Page 19

5

4

3

2

1

SSID = PCH

D D

R1901

1

2

10MR2J -L-GP

X1901

2

XTAL-32D768KHZ-67-GP

82.30001.G11

R1916

1 DY2

1KR2J-L2-GP

41

3

HDA_SD OUT

12

C C

B B

A A

C1901

SC4P5 0V2BN-GP

3D3V_A UDIO_SUS

RTC_X1

RTC_X2

12

C1902

SC4P5 0V2BN-GP

Flash Descriptor Security Overide

Low =Default

HDA_SDOUT

High= Enable

27 HDA_ CODEC_SYNC

5

24 KBC_R TCRST#

5V_S0 Q1902

2N7002K-2-GP

G

S

84.2N702.J31

2ND = 84.2N702.031

3RD = 84.2N702.W31

R1924

1 DY2

0R2J-2-GP

D

HDA_SY NC_R

RTC_AUX _S5

R1923

2

PCH_JTAG_TDI R191 2

TCK_JTAGX R1915

R1917

1 2

4

R1902

R1903

1

1 2

20KR2F -L3-GP

20KR2F -L3-GP

TP1901

1

TPAD14-OP-GP

1

0R0402-PAD

SC1U10V2KX-L1-GP

PCH_J TAG_TMS R1913

PCH_J TAG_TDO R1914

HDA_SY NC

33R2J-L1-GP

2

1

1

1

1

C1904

2 1

RTC Reset

2

51R2J -2-GP

2

51R2J -2-GP

2