Page 1

A

CLK GEN

3

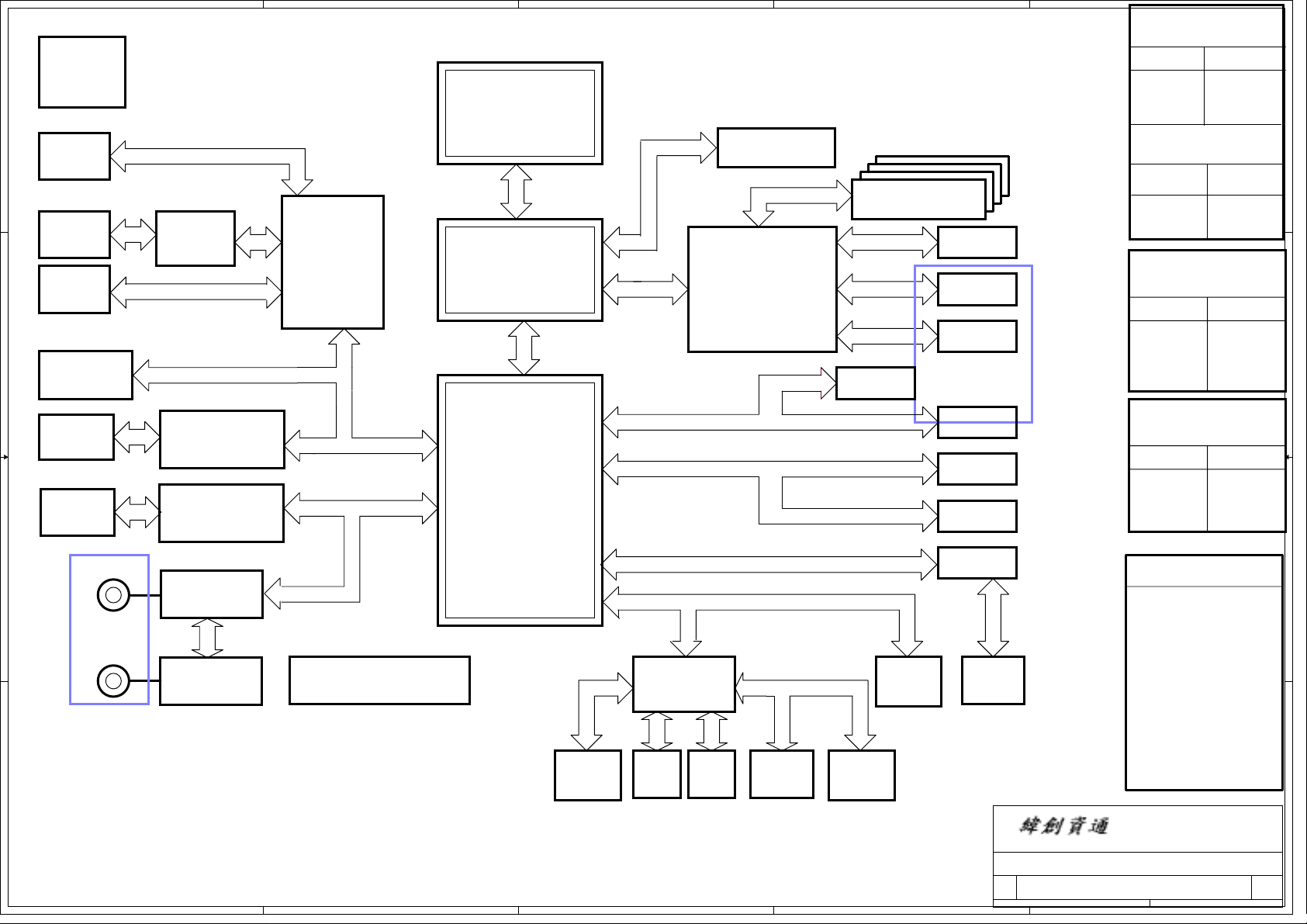

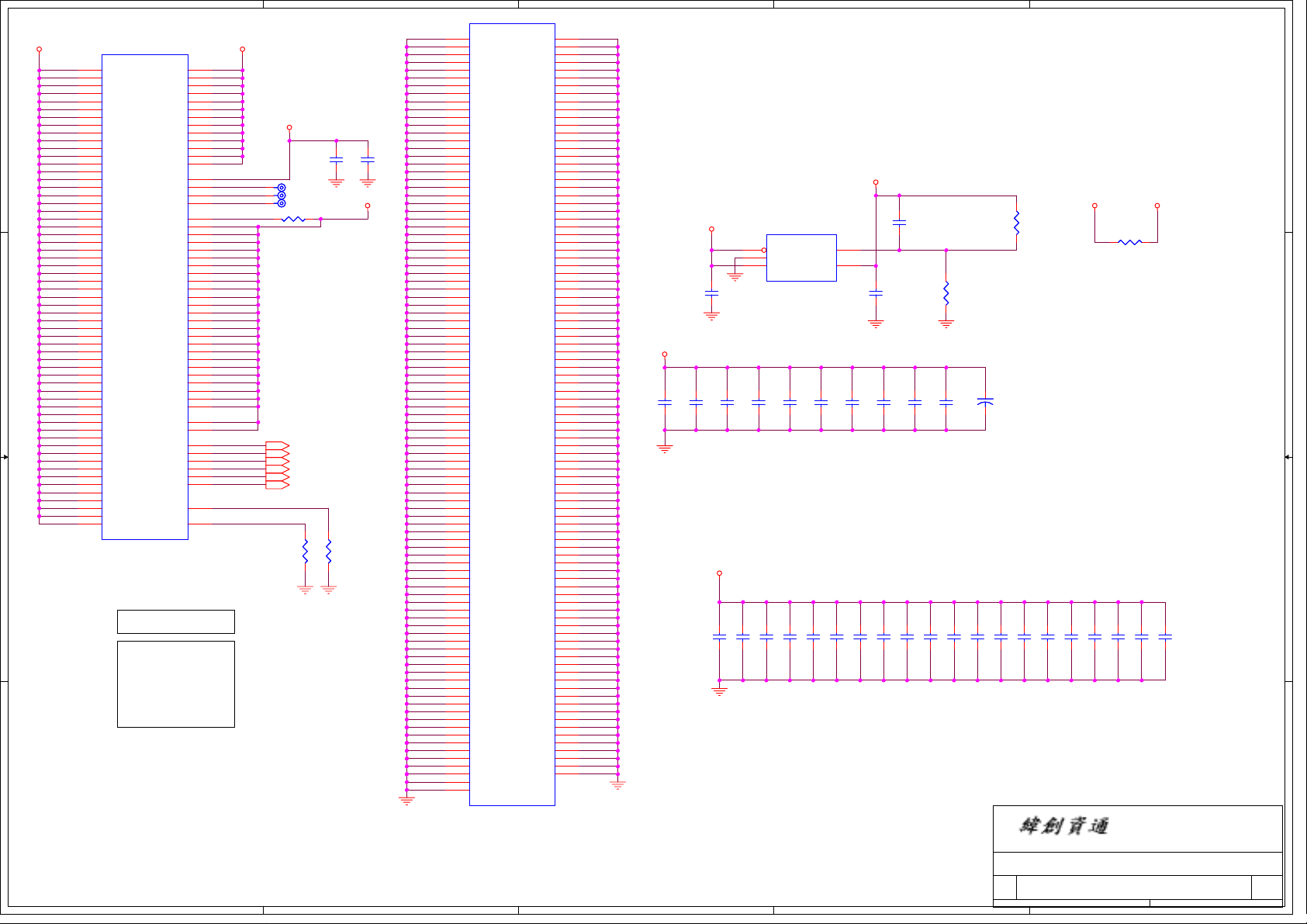

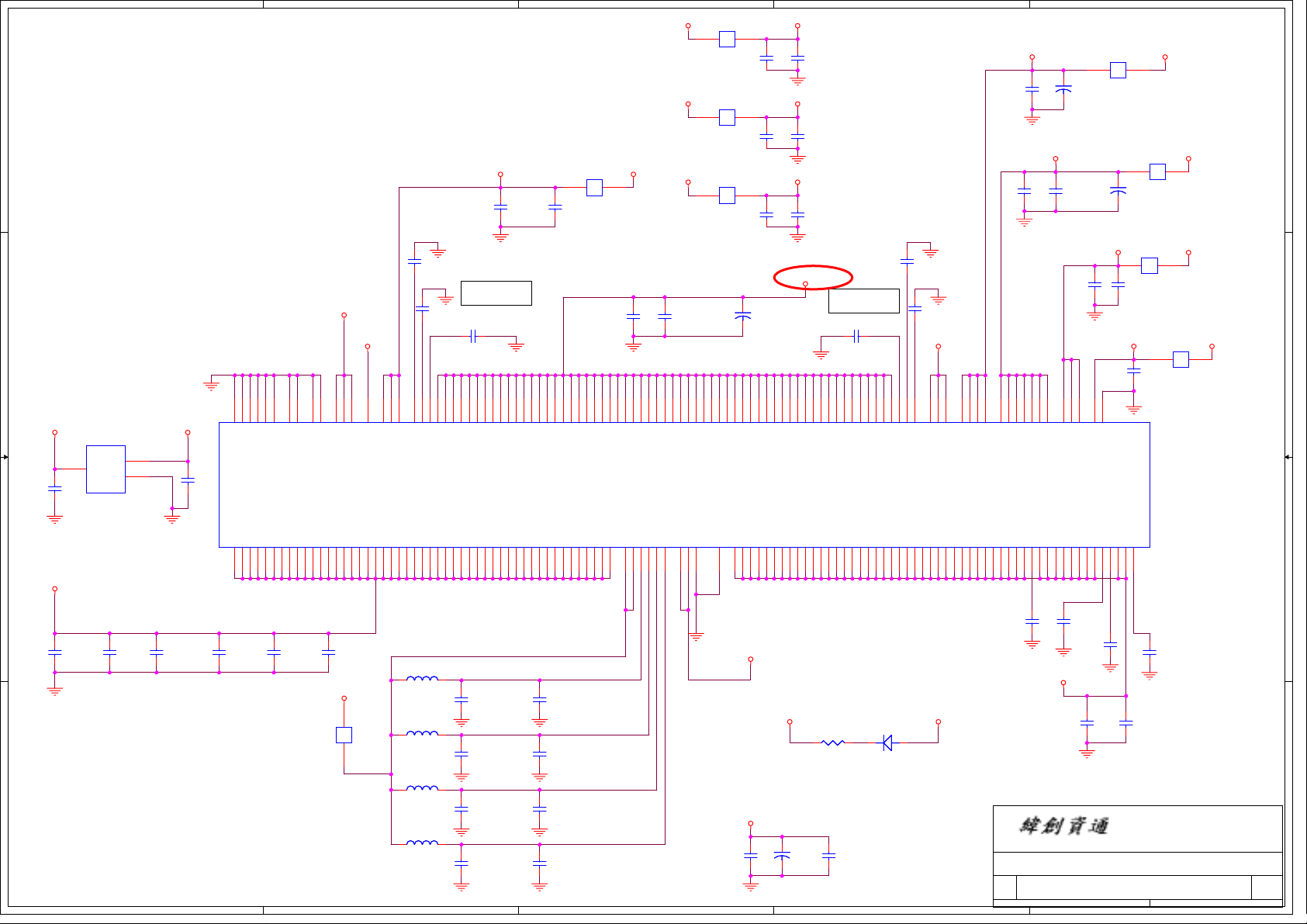

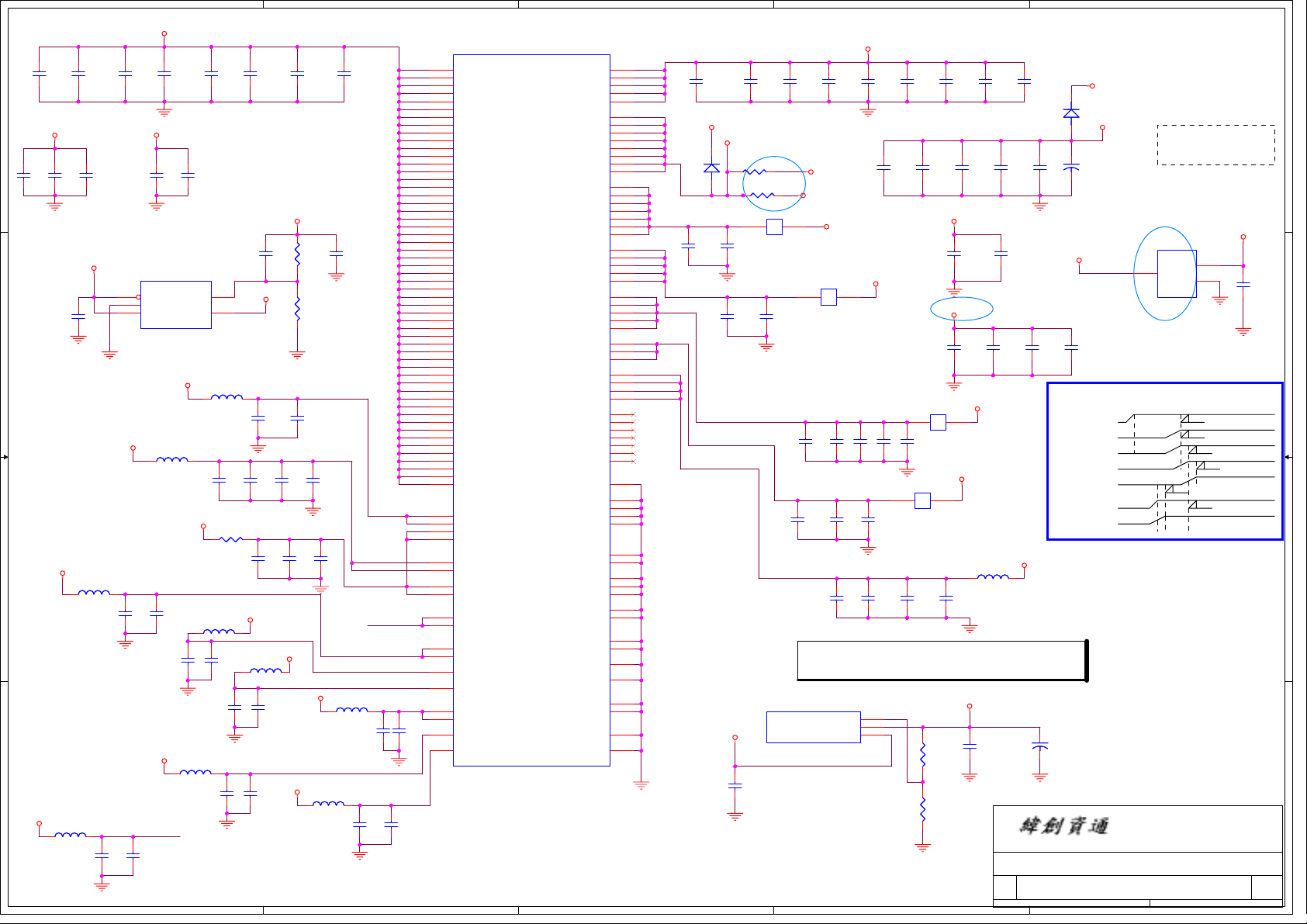

Leopard2 Block Diagram

ICS954206

4 4

31

1394

Conn

27,28

PCMCIA

1 SLOT

SD/MS

6 in 1

29 28

29

Power

Switch

TPS2220A

PCI 7411

CARDBUS

1394

SD/MS/MMC/SM

Card Slost

3 3

Mini-PCI

34

802.11a/b/g

RJ45

CONN

RJ11

CONN

31

10/100 RTL8100C

31

MODEM

MDC Card

30,31

PCI BUS

35

AC97-LINK

B

4,5

Mobile CPU

Dothan

Host BUS

400/533MHz

6,7,8,9,10

Alviso

DMI I/F

100MHz

21,22,23,24

ICH6-M

PEG

C

Project code: 91.4C701.001

PCB P/N : 48.4C701.011

REVISION : 05202 -1

DDRII*2

13,14,15

VGA

ATI M26P

USB 2.0

11,12

SVIDEO/COMP

BLUE THUMB

D

DDR-SDRAM

16,17

HY5DS573222F-28

LVDS

TVOUT

RGB CRT

DAUGHTER BOARD

USB x 2

USB x 2

P EIDE

HDD

LCD

CRT

E

SYSTEM DC/DC

42

45

19

18

40

TPS5130

INPUTS

DCBATOUT

OUTPUTS

1D8V_S3

5V_S3

3V_AUX

SYSTEM DC/DC

MAX8743

INPUTS

DCBATOUT

OUTPUTS

1D05V_S0

1D2V_VGA_S0

MAXIM CHARGER

MAX8725

INPUTS

OUTPUTS

BT+

DCBATOUT

35

26

CPU DC/DC

41

INPUTS

18V 4.0A

5V 100mA

MAX1907

OUTPUTS

VCC_CORE

S EIDE

DVD/

CD-RW

26

DCBATOUT

0.844~1.3V

27A

2 2

MIC IN

18

AC'97 CODEC

31

AD1981B

LINE OUT

OP AMP

G1420B

33

Docking

18

KBC

NS97551

PCI EXPRESS/ USB2.0

LPC Bus

36

LPC

Debug

Conn

EXPRESSCARD

38

DAUGHTER BOARD

Comsumer

35 3837

IR

1 1

A

B

37

Touch

Pad

C

Int.

KB

Thermal

& Fan

G768D

25

FlashRom

4Mb

(512kB)

D

26

PCB LAYER

Signal 1

L1:

GND

L2:

Signal 2

26

Power

Switch

TPS2231

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Block Diagram

Block Diagram

Block Diagram

L3:

Signal 3

L4:

VCC

L5:

Signal 4

L6:

GNDL7:

Signal 5L8:

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Leopard2

Leopard2

Leopard2

147Monday, July 11, 2005

147Monday, July 11, 2005

147Monday, July 11, 2005

E

-1

-1

of

of

of

-1

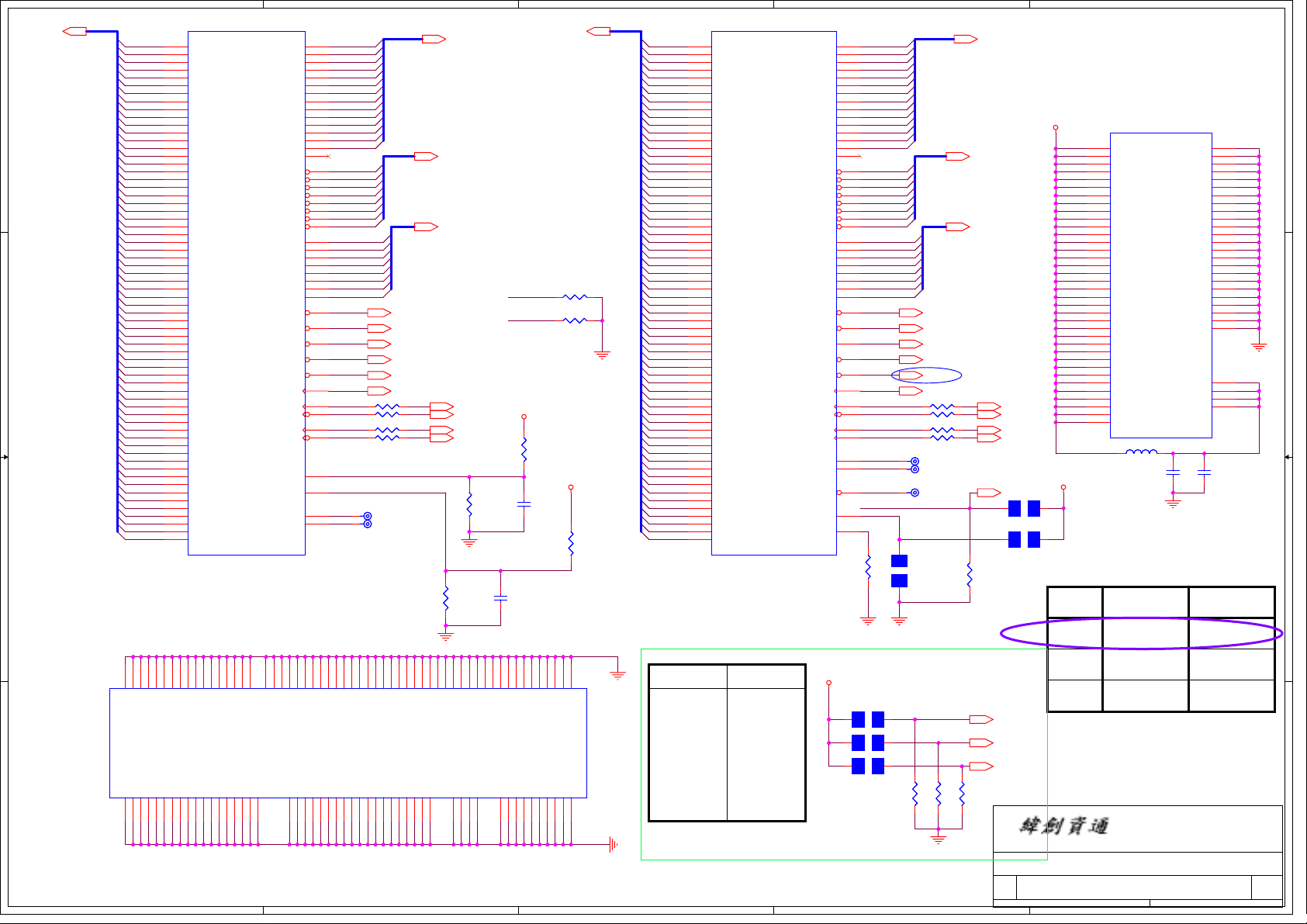

Page 2

A

B

C

D

E

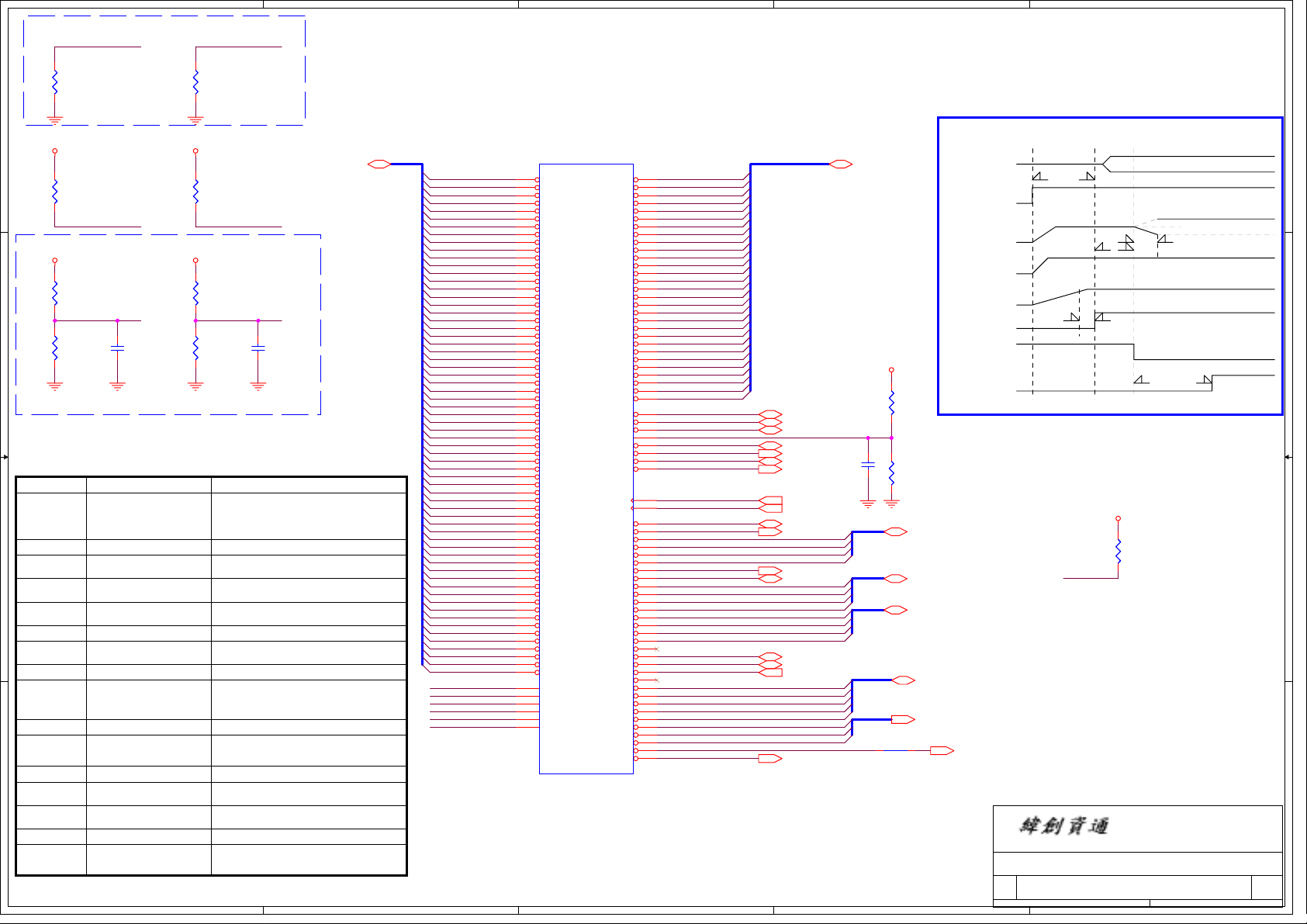

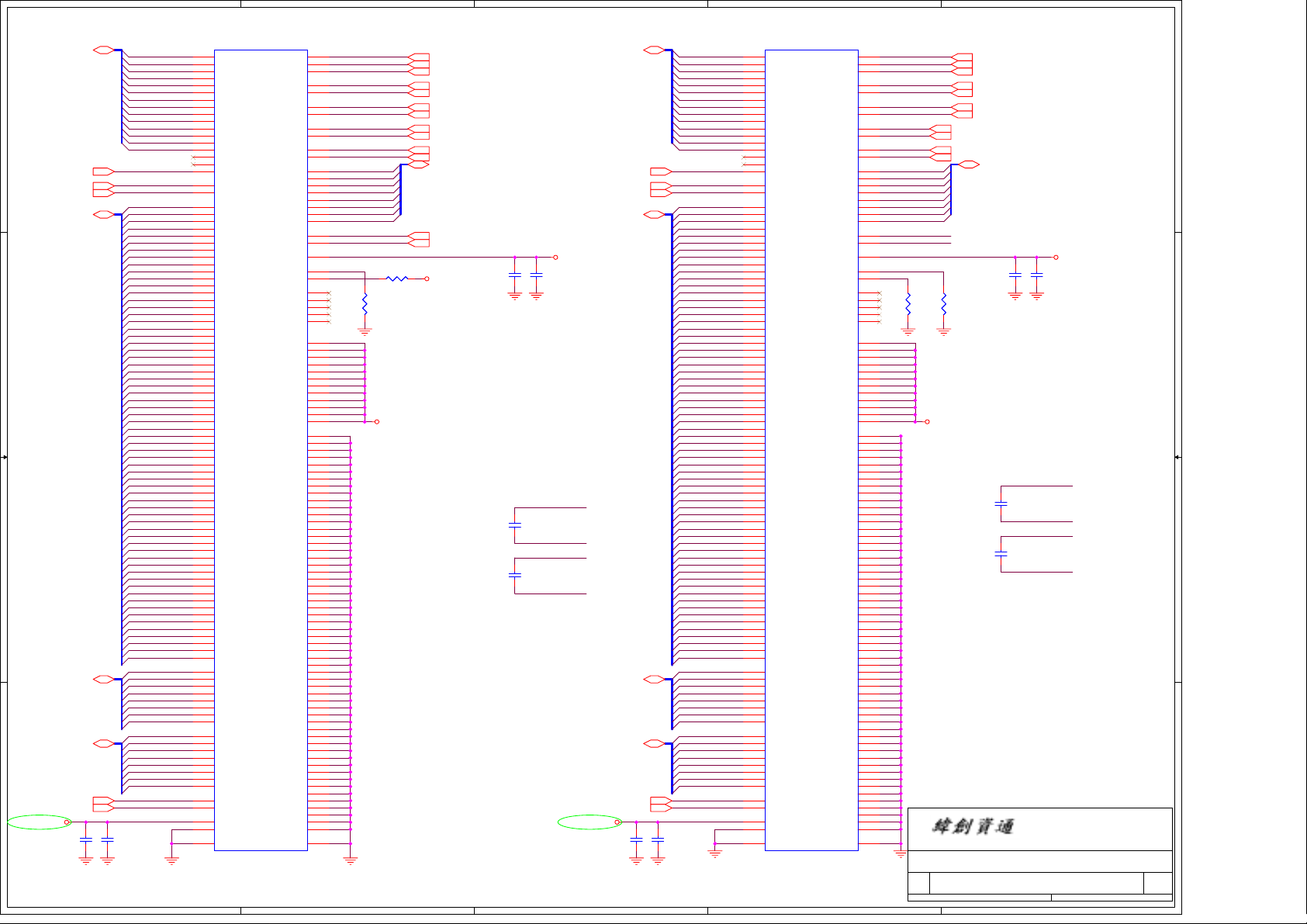

ICH6-M Integrated Pull-up

and Pull-down Resistors

ACZ_BIT_CLK,

EE_DOUT, EE_CS, GNT[5]#/GPO[17],

GNT[6]#/GPO[16],

4 4

LAD[3:0]#/FB[3:0]#, LDRQ[0],

PME#, PWRBTN#,

LAN_RXD[2:0]

ACZ_RST#, ACZ_SDIN[2:0], ACZ_SYNC,

ACZ_SDOUT,ACZ_BITCLK,

SPKR

USB[7:0][P,N]

DD[7],

LAN_CLK

3 3

ICH6-M IDE Integrated Series

DPRSLP#, EE_DIN,

TP[3]

SDDREQ

LDRQ[1]/GPI[41],

DPRSLPVR,

ICH6 internal 20K pull-ups

ICH6 internal 10K pull-ups

ICH6 internal 20K pull-downs

ICH6 internal 15K pull-downs

ICH6 internal 11.5K pull-downs

ICH6 internal 100K pull-downs

ICH6-M EDS 14308 0.8V1

Termination Resistors

DD[15:0],

DDACK#,

DCS3#,

IORDY,

IDEIRQ

DIOR#, DREQ,DIOW#,

DA[2:0],

DCS1#,

approximately 33 ohm

Power name description

5V_S0= 5 Voltage power up on system work(S0 state)

5V_S3= 5 Voltage suspend to RAM(S3 state)

5V_S5= 5 Voltage soft off(S5 state)

3D3V_S0= 3.3 Voltage power up on system work(S0 state)

3D3V_S3= 3.3 Voltage suspend to RAM(S3 state)

3D3V_S5= 3.3 Voltage soft off(S5 state)

LVDDR_2D8V= 2.8 Voltage power up on system work(S0 state)

1D8V_S3= 1.8 Voltage suspend to RAM(S3 state)

2D5V_S0= 2.5 Voltage power up on system work(S0 state)

VCC_CORE_S0= CPU VID Voltage power up on system work(S0 state)

1D5V_VCCA_S0= 1.5 Voltage power up on system work(S0 state)

1D5V_S0= 1.5 Voltage power up on system work(S0 state)

1D5V_S5= 1.5 Voltage soft off(S5 state)

DDR_VREF= 0.9 Voltage power up on system work(S0 state)

1D2V_VGA_S0= 1.2 Voltage power up on system work(S0 state) for VGA

VRAM_VDDQ= 1.8 Voltage power up on system work(S0 state) for VRAM

1D05V_S0= 1.05 Voltage power up on system work(S0 state)

CORE_GMCH_S0= 1.05 Voltage power up on system work(S0 state) for ALVISO core power

VCCP_GMCH_S0= 1.05 Voltage power up on system work(S0 state)for ALVISO BUSIO power

PCI RESOURCE TABLE

2 2

1 1

A

B

C

DEVICE IDSEL

Mini-PCI

Cardbus Controller

TI7411

LAN

Blue Thumb

D

AD21

AD22

AD23

AD24

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

PCI IRQ

P_INTE#

(CARBUS)P_INTG#

(1394)P_INTF#

(CARD READER)P_INTG#

P_INTE#

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

ITP

ITP

ITP

Leopard2

Leopard2

Leopard2

REQ# / GNT#

REQ0#/GNT0#

REQ1#/GNT1#

REQ2#/GNT2#

247Wednesday, July 06, 2005

247Wednesday, July 06, 2005

247Wednesday, July 06, 2005

E

-1

-1

of

of

of

-1

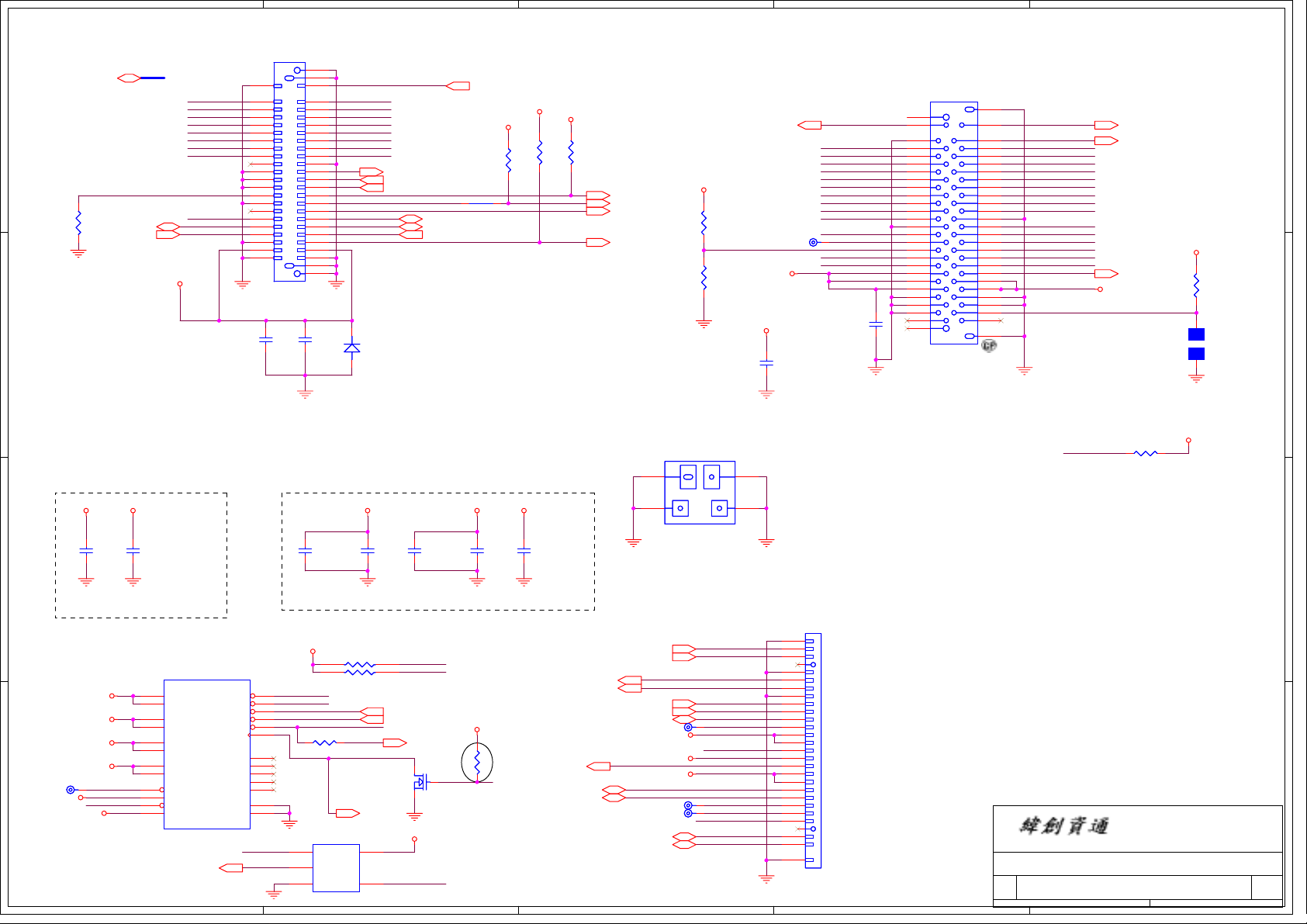

Page 3

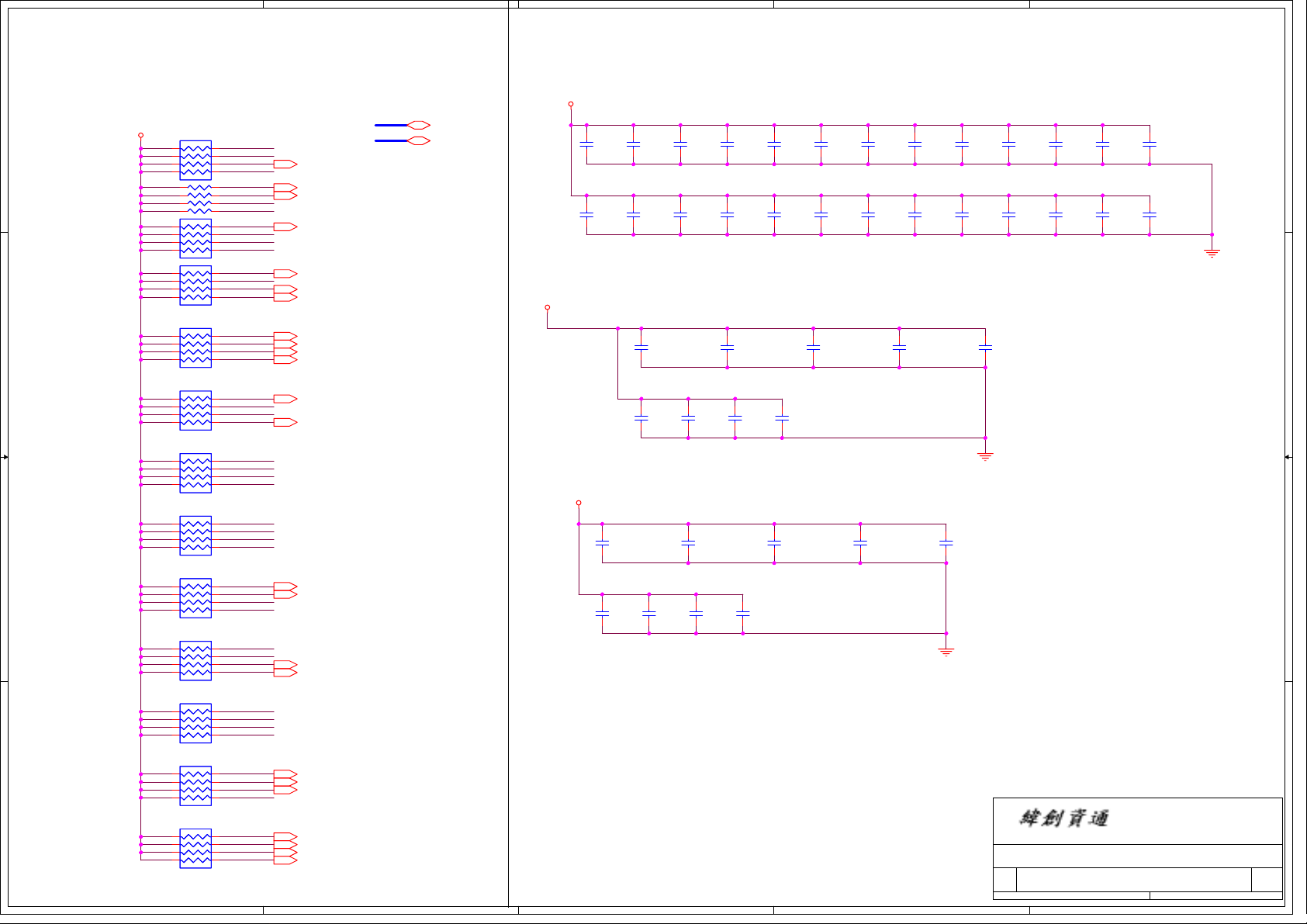

A

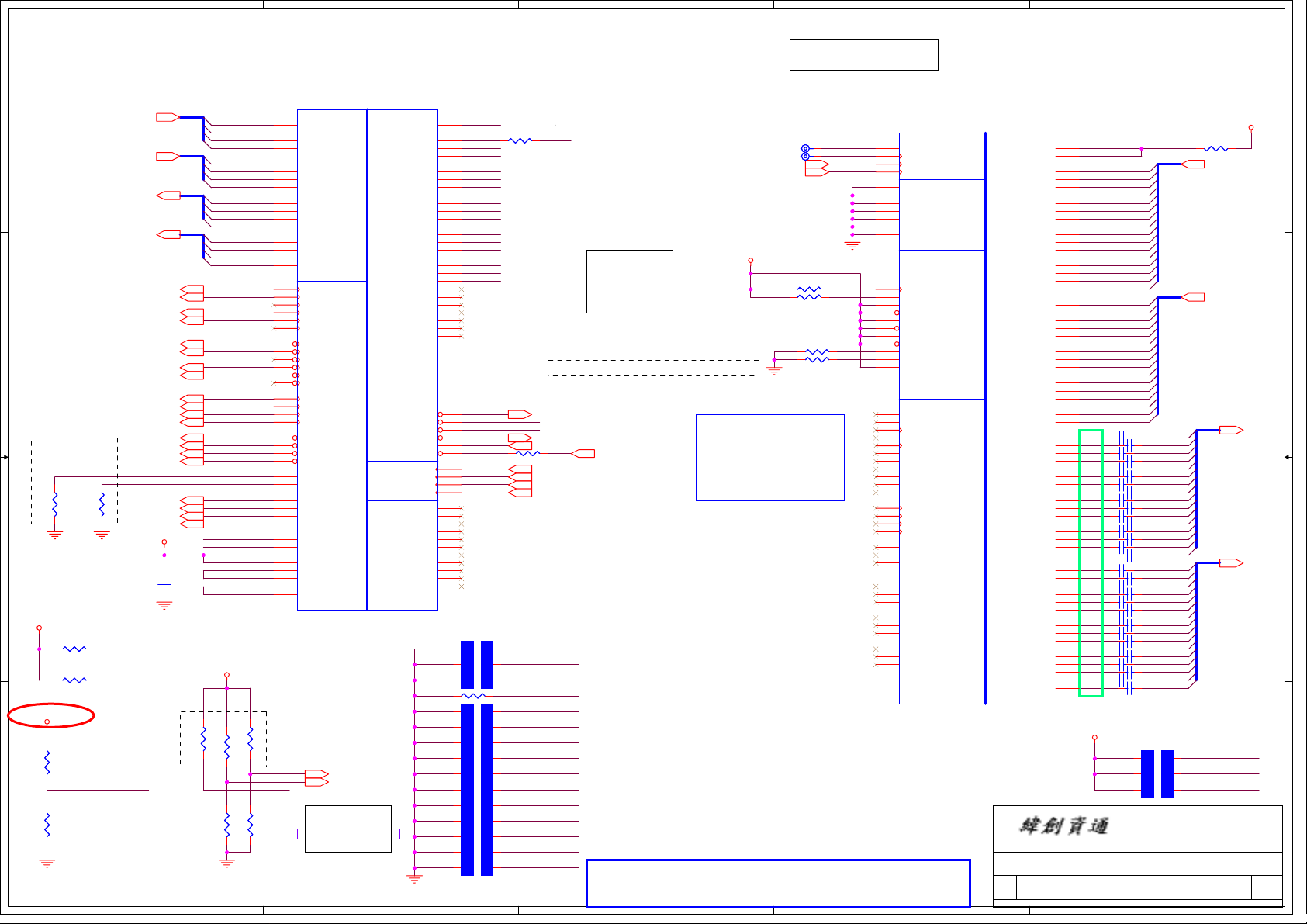

L17

L17

1 2

MLB-201209-11

MLB-201209-11

4 4

3D3V_S0

L38

L38

1 2

MLB-201209-11

MLB-201209-11

12

3D3V_APWR_S0 3D3V_48MPWR_S0

12

C519

C519

SC10U10V6ZY-U

SC10U10V6ZY-U

C199

C199

SC4D7U10V5ZY

SC4D7U10V5ZY

12

12

3D3V_CLKGEN_S0

C532

C532

SCD1U16V

SCD1U16V

C524

C524

SCD1U16V

SCD1U16V

DY

DY

12

C523

C523

SCD1U16V

SCD1U16V

B

3D3V_S03D3V_S0

1 2

4D7R3

4D7R3

R196

12

R196

C538

C538

SCD1U16V

SCD1U16V

12

12

C543

C543

SCD1U16V

SCD1U16V

C218

C218

SC4D7U10V5ZY

SC4D7U10V5ZY

12

DY

DY

12

C219

C219

SCD1U16V

SCD1U16V

DY

DY

C525

C525

SCD1U16V

SCD1U16V

12

DY

DY

C

C518

C518

SCD1U16V

SCD1U16V

12

DY

DY

C539

C539

SCD1U16V

SCD1U16V

3D3V_S0

12

12

R200

R200

10KR2

10KR2

R221

R221

10KR2

10KR2

DY

DY

ITP_EN

D

DummyR200(up side),Mounting R221(down side)

--SRC7 on

Mounting R200(up side),DummyR221(down side)

--CPU2_ITP on

E

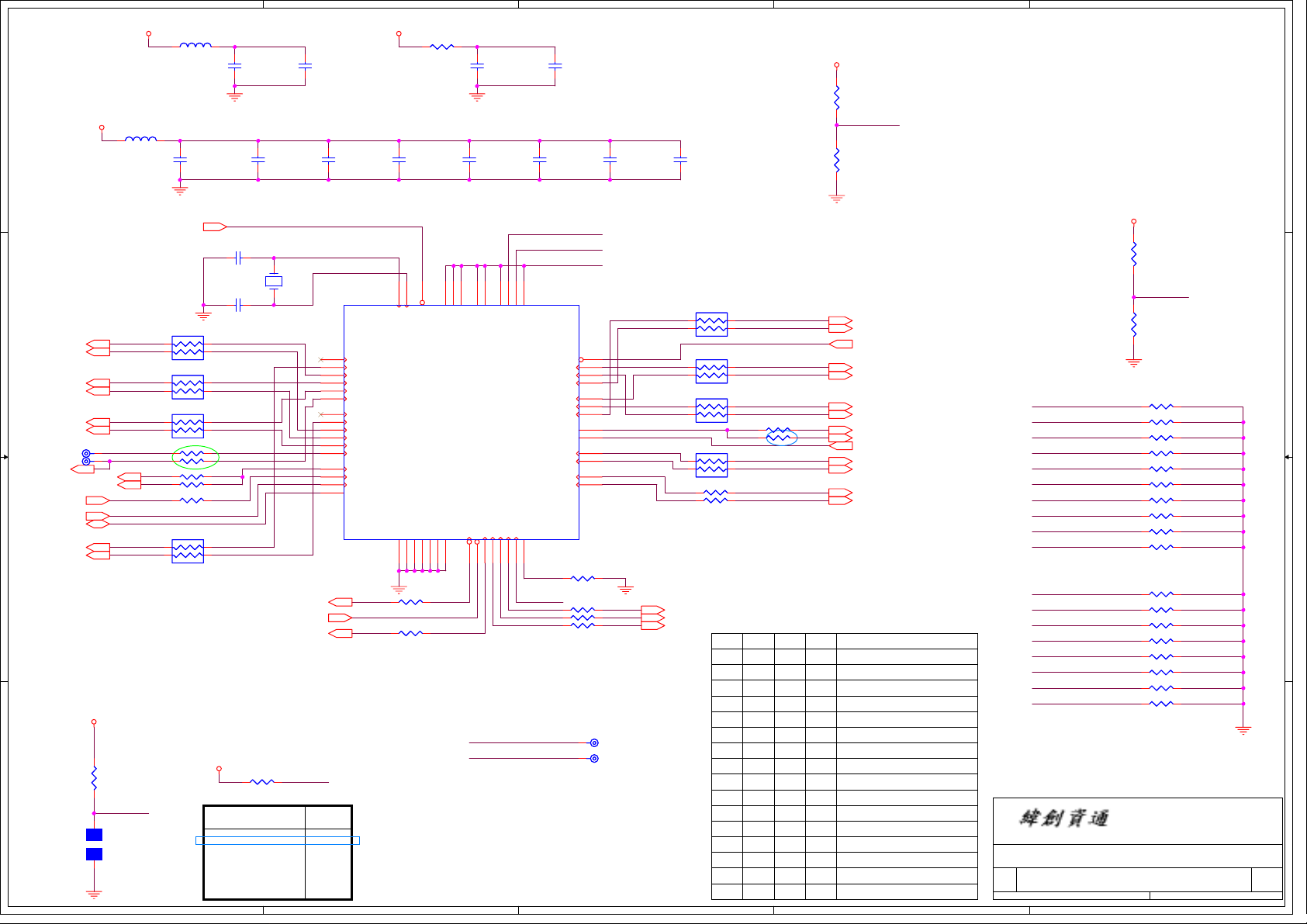

CLK_PWRGD#25,41

CPU

266M

133M

166M

400M

20

23

25

27

30

32

19

22

24

26

31

33

52

53

46

47

CLK_XOUT

CLK_XIN

49

X150X2

SRCCLKC1

SRCCLKC2

SRCCLKC3

SRCCLKC4_SATA

SRCCLKC5

SRCCLKC6

SRCCLKT1

SRCCLKT2

SRCCLKT3

SRCCLKT4_SATA

SRCCLKT5

SRCCLKT6

REF0

REF1/FSLC/TEST_SEL

SCLK

SDATA

51

1 2

R589

R589

1 2

R220

R220

B

10

22R2

22R2

33R2

33R2

VTT_PWRGD#/PD

34

GND2GND6GND13GND29GND45GND

GNDA

38

SS_SEL

VDDSRC21VDDSRC28VDDSRC

SEL100_96MHZ#/PCICLK_F1

9

ITP_EN

7

CPUCLKC2_ITP/SRCCLKC7

CPUCLKT2_ITP/SRCCLKT7

55

1 2

C544 SC22PC544 SC22P

1 2

C545 SC22PC545 SC22P

RN20

RN20

CLK_PCIE_NEW#26

3 3

CLK_PCIE_NEW26

CLK_MCH_3GPLL#7

CLK_MCH_3GPLL7

CLK_PCIE_ICH#22

CLK_PCIE_ICH22

TP_SRCC6 CLK_SRCT6

TP31TPAD30 TP31TPAD30

TP_SRCT6 CLK_SRCC6

TP30TPAD30 TP30TPAD30

PREQ2#26

CLK_ICH1422

CLK_CODEC32

CPU_SEL04,7

SMBC_ICH11,24

SMBD_ICH11,24

CLK_PCIE_PEG#13

CLK_PCIE_PEG13

2 2

3D3V_S0

12

R606

R606

10KR2

10KR2

1 1

12

REQSEL

R605

R605

DUMMY-R2

DUMMY-R2

4

SRN33-2-U2

SRN33-2-U2

RN18

RN18

4

SRN33-2-U2

SRN33-2-U2

RN19

RN19

4

SRN33-2-U2

SRN33-2-U2

SB

R584

R584

R568

R568

1 2

R602

R602

1 2

R601

R601

2K2R2

2K2R2

RN21

RN21

4

SRN33-2-U2

SRN33-2-U2

A

CLK_SRCC1

1

CLK_SRCT1

23

CLK_SRCC3

1

CLK_SRCT3

23

CLK_SRCC5

1

CLK_SRCT5

23

12

DY

DY

0R2-0

0R2-0

12

0R2-0

0R2-0

DY

DY

22R2

22R2

22R2

22R2

12

R222

R222

CLK_SRCC2

1

CLK_SRCT2

23

3D3V_CLKGEN_S0

R197

R197

FS_C

0

0

0

1

1 100M

1

1

X7

X7

X-14D31818M-17

X-14D31818M-17

1 2

CLK_REF14

PCLK_KBC36

PM_STPPCI#22

CLK_ICHPCI22

NEAR CLKGEN

1 2

FS_B

0

0

1

1

0

0

1

1

FS_A

10KR2

10KR2

FS_A

0

01200M

1

00333M

1

0

1 Reserved

3D3V_APWR_S0

3D3V_48MPWR_S0

3D3V_CLKGEN_S0

37

42

11

48

VDDA

VDD48

VDDPCI1VDDPCI

VDDREF

VDDCPU

CPU_STOP#

CPUCLKC0

CPUCLKC1

CPUCLKT0

CPUCLKT1

FSLA/USB_48MHZ

FSLB/TEST_MODE

96MHZ_SSC/SRCCLKC0

96MHZ_SST/SRCCLKT0

DOTC_96MHZ

DOTT_96MHZ

IREF

ITP_EN/PCICLK_F08PCI/SRC_STOP#

PCICLK256PCICLK33PCICLK44PCICLK5

5

39

CLK_IREF

475R2F

475R2F

REQSEL

CLK_PCI3

CLK_PCI4

CLK_PCI5

CLK_CPU_BCLK

CLK_CPU_BCLK#

close to CPU

U72

U72

33R2

33R2

33R2

33R2

33R2

33R2

54

43

40

35

44

41

36

12

16

18

17

15

14

ICS954206AG

ICS954206AG

12

R181

R181

12

R600

R600

12

R218

R218

12

R219

R219

TP33

TP33

TPAD30

TPAD30

TP32

TP32

TPAD30

TPAD30

CLK_CPUT1

CLK_CPUC1

CLK_CPUC2

CLK_CPUT2

CLK_CPUT0

CLK_CPUC0

FS_A

CLK_SRCC0

CLK_SRCT0

DOT96C

DOT96T

C

RN22

RN22

1

2 3

SRN33-2-U2

SRN33-2-U2

RN24

RN24

2 3

DY

DY

1

SRN33-2-U2

SRN33-2-U2

RN25

RN25

1

2 3

SRN33-2-U2

SRN33-2-U2

RN23

RN23

1

2 3

SRN33-2-U2

SRN33-2-U2

R199 33R2R199 33R2

R201 33R2R201 33R2

PCLK_PCM 27

PCLK_LAN 30

PCLK_MINI 34

SS3 SS2 SS1 SS0 Spread Amount%

000

0000

0

0

0

0

0

1 +-0.3

1

1

1

1

1

11

11

4

4

4

R592 10R2R592 10R2

1 2

R593 33R2R593 33R2

1 2

SC

4

12

12

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

PM_STPCPU# 22,41

CLK_XDP_CPU# 4

CLK_XDP_CPU 4

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK48_USB 22

CLK48_CARDBUS 27

CPU_SEL1 4,7

DREFSSCLK# 7

DREFSSCLK 7

DREFCLK# 7

DREFCLK 7

ICS954206AG Spread

Spectrum Select

1

0

1

0

0

1

0

1

1

1

11

0

0

00

001

1

0

1

0

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

-0.8

-1.0

-1.25

-1.5

-1.75

-2.0

-2.5

-3.0

+-0.4

+-0.5

+-0.6

+-0.8

+-1.0

+-1.25

+-1.5

D

DREFCLK

DREFCLK#

CLK_PCIE_NEW

CLK_PCIE_NEW#

CLK_XDP_CPU

CLK_XDP_CPU#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

DREFSSCLK

DREFSSCLK#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_PEG

CLK_PCIE_PEG#

CLK_PCIE_ICH

CLK_PCIE_ICH#

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Clock Generator (ICS954206AG )

Clock Generator (ICS954206AG )

Clock Generator (ICS954206AG )

3D3V_S0

12

R590

R590

10KR2

10KR2

H/L: 100/96MHz

SS_SEL

12

R591

R591

10KR2

10KR2

DY

DY

1 2

49D9R2F

49D9R2F

R202

R202

1 2

49D9R2F

49D9R2F

R198

R198

1 2

49D9R2F

49D9R2F

R582

R582

1 2

49D9R2F

49D9R2F

R580

R580

1 2

DY

DY

49D9R2F

49D9R2F

R603

R603

1 2

DY

DY

49D9R2F

49D9R2F

R594

R594

1 2

49D9R2F

49D9R2F

R596

R596

1 2

49D9R2F

49D9R2F

R595

R595

1 2

49D9R2F

49D9R2F

R585

R585

1 2

49D9R2F

49D9R2F

R586

R586

1 2

49D9R2F

49D9R2F

R194

R194

1 2

49D9R2F

49D9R2F

R195

R195

1 2

49D9R2F

49D9R2F

R566

R566

1 2

49D9R2F

49D9R2F

R567

R567

1 2

49D9R2F

49D9R2F

R581

R581

1 2

49D9R2F

49D9R2F

R583

R583

1 2

49D9R2F

49D9R2F

R569

R569

1 2

49D9R2F

49D9R2F

R570

R570

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Leopard2

Leopard2

Leopard2

347Monday, July 11, 2005

347Monday, July 11, 2005

347Monday, July 11, 2005

E

-1

-1

-1

Page 4

A

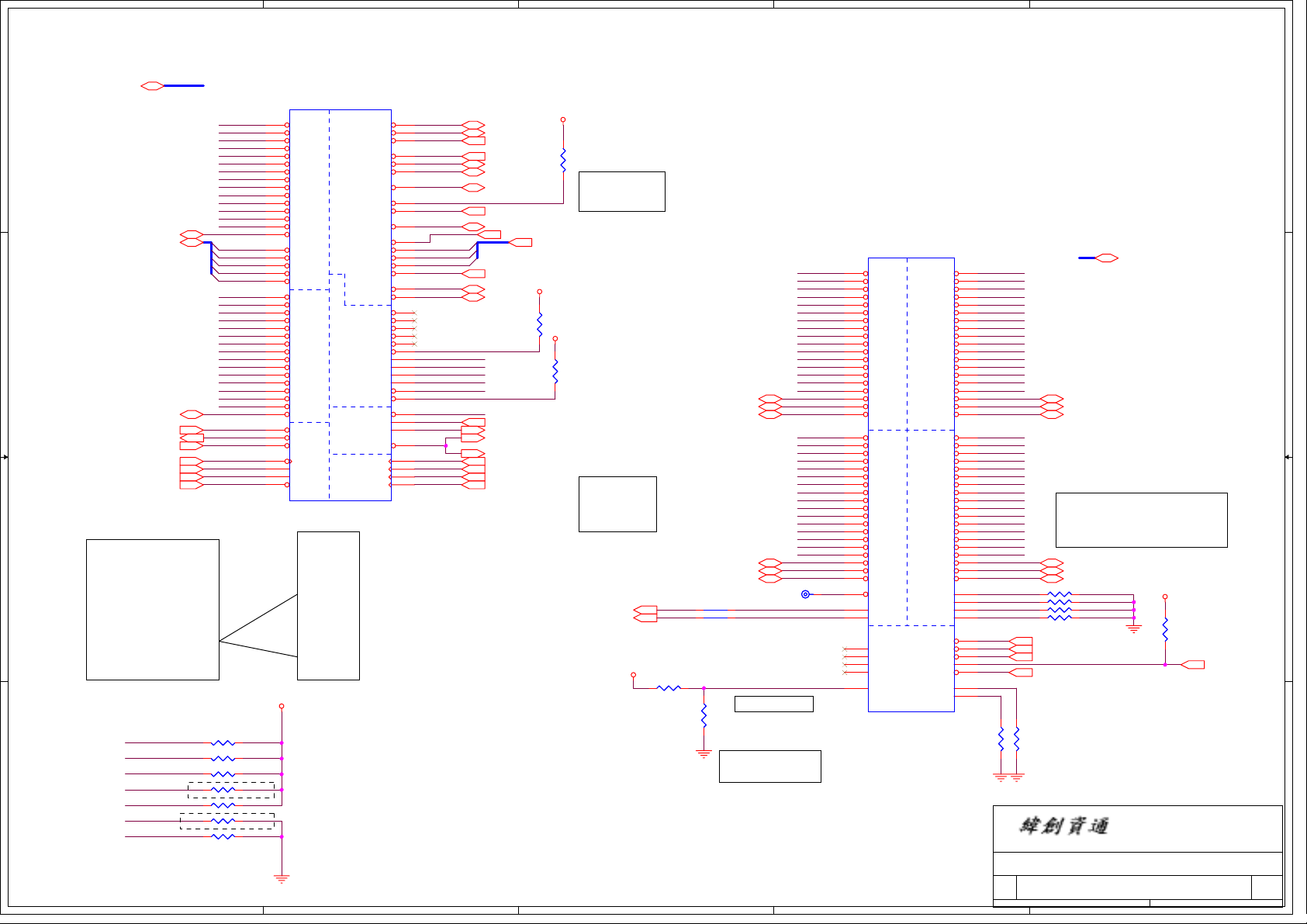

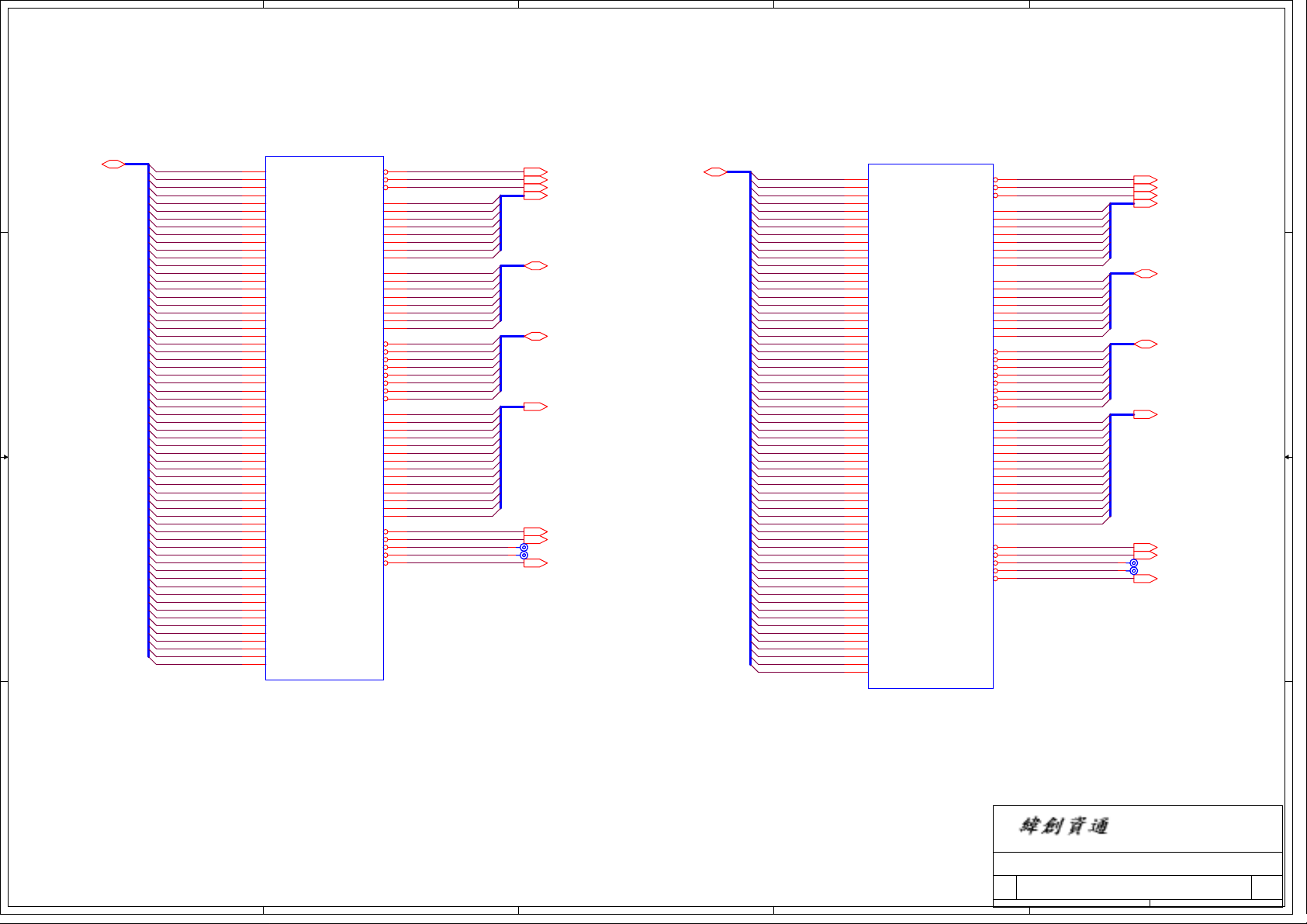

H_A#[31..3]6

U53A

U53A

62.10055.011

62.10055.011

PZ47903

4 4

H_ADSTB#06

H_REQ#[4..0]6

3 3

H_ADSTB#16

H_A20M#21

H_FERR#21

H_IGNNE#21

H_STPCLK#21

H_INTR21

H_NMI21

H_SMI#21

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

CPU

2 2

PZ47903

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

U3

ADSTB#0

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

AE5

ADSTB#1

C2

A20M#

D3

FERR#

A3

IGNNE#

C6

STPCLK#

D1

LINT0

D4

LINT1

B4

SMI#

ITP Conn.

ADDR GROUP 0

ADDR GROUP 1

THERMTRIP#

HCLK THERM XTP/ITP SIGNALS CONTROL

TCK(PIN 5)

TCK(PIN A13)

FBO(PIN 11)

VCCP_GMCH_S0

H_CPURST#

XDP_TDO

CPU_PROCHOT#

1 1

XDP_TDI

XDP_TMS

XDP_TRST#

XDP_TCK

R391

R391

R386

R386

R384

R384

1 2

R387

R387

1 2

R389

R389

1 2

R388

R388

1 2

R390

R390

12

54D9R2F

54D9R2F

12

54D9R2F

54D9R2F

12

56R2J

56R2J

150R2

150R2

39D2R2F

39D2R2F

680R2

680R2

27D4R2F

27D4R2F

All place within 2" to CPU

A

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

ITP_CLK1

ITP_CLK0

BCLK1

BCLK0

B

N2

L1

J3

L4

H2

M2

N4

A4

B5

J2

B11

H_RS#0

H1

H_RS#1

K1

H_RS#2

L2

M3

K3

K4

C8

B8

A9

C9

A10

XDP_BPM#5

B10

XDP_TCK

A13

XDP_TDI

C12

TDI

A12

C11

B13

A7

B17

B18

A18

C17

A15

A16

B14

B15

B

XDP_TDO

XDP_TMS

XDP_TRST#

DBR#

CPU_PROCHOT#

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_INIT# 21

H_LOCK# 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

THERMDP1 25

THERMDN 25

PM_THRMTRIP-A# 7,21

PM_THRMTRIP-I# 7,21

CLK_XDP_CPU# 3

CLK_XDP_CPU 3

CLK_CPU_BCLK# 3

CLK_CPU_BCLK 3

VCCP_GMCH_S0

H_IERR#

H_CPURST# 6

H_RS#[2..0] 6

VCCP_GMCH_S0

12

VCC_CORE_S0

R393

R393

56R2J

56R2J

12

12

R396

R396

56R2J

56R2J

R27

R27

150R2

150R2

Place testpoint on

H_IERR# with a GND

0.1" away

PM_THRMTRIP#

should connect to

ICH6 and Alviso

without T-ing

( No stub)

CPU_SEL03,7

CPU_SEL13,7

C

VCCP_GMCH_S0

1 2

R34

R34

C

R383

R383

R385

R385

1KR2F

1KR2F

H_DSTBN#06

H_DSTBP#06

H_DINV#06

H_DSTBN#16

H_DSTBP#16

H_DINV#16

1 2

1 2

12

R33

R33

2KR2F

2KR2F

0R0402-PAD

0R0402-PAD

0R0402-PAD

0R0402-PAD

BSEL[1:0] Freq.(MHz)

L H 100

L L 133

CPU_SEL0_CPU

CPU_SEL1_CPU

Layout Note:

0.5" max length.

TP2TP2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

GTLREF

PSI#

C20

D24

C26

C25

C23

C22

D25

H23

G25

M26

H24

G24

M23

N24

M25

H26

N25

C16

C14

AF7

AC1

AD26

A19

A25

A22

B21

A24

B26

A21

B20

B24

E24

B23

E23

L23

F25

K25

K24

L24

E26

J23

J25

L26

J26

E1

C3

D

U53B

U53B

PZ47903

PZ47903

62.10055.011

62.10055.011

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

DATA GRP 0DATA GRP 1

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

PSI#

BSEL0

BSEL1

MISC

RSVD2

RSVD3

RSVD4

RSVD5

GTLREF0

D

Y26

D32#

AA24

D33#

T25

D34#

U23

D35#

V23

D36#

R24

D37#

R26

D38#

R23

D39#

AA23

D40#

U26

D41#

V24

D42#

U25

D43#

V26

D44#

DATA GRP 2

Y23

D45#

AA26

D46#

Y25

D47#

W25

DSTBN2#

W24

DSTBP2#

T24

DINV2#

AB25

D48#

AC23

D49#

AB24

D50#

AC20

D51#

AC22

D52#

AC25

D53#

AD23

D54#

AE22

D55#

AF23

D56#

AD24

D57#

AF20

D58#

AE21

D59#

AD21

D60#

DATA GRP 3

AF25

D61#

AF22

D62#

AF26

D63#

AE24

DSTBN3#

AE25

DSTBP3#

AD20

DINV3#

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

G1

DPRSTP#

B7

DPSLP#

C19

DPWR#

SLP#

TEST1

TEST2

E4

A6

C5

F23

PWRGOOD

E

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

R402 27D4R2FR402 27D4R2F

COMP1

R403 54D9R2FR403 54D9R2F

COMP2

R35 27D4R2FR35 27D4R2F

COMP3

R36 54D9R2FR36 54D9R2F

TEST1

TEST2

12

12

R29

R29

1KR2

1KR2

DY

DY

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

1 2

1 2

1 2

1 2

H_DPRSLP# 21

H_DPSLP# 21

H_DPWR# 6

H_CPUSLP# 6,21

R392

R392

1KR2

1KR2

DY

DY

H_D#[63..0] 6

VCCP_GMCH_S0

12

R395

R395

200R2J

200R2J

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (1 of 2)

CPU (1 of 2)

CPU (1 of 2)

Leopard2

Leopard2

Leopard2

447Monday, July 11, 2005

447Monday, July 11, 2005

447Monday, July 11, 2005

E

H_PWRGD 21

of

-1

-1

-1

Page 5

A

VCC_CORE_S0 VCC_CORE_S0

4 4

3 3

2 2

1 1

AA11

AA13

AA15

AA17

AA19

AA21

AA5

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC9

AD10

AD12

AD14

AD16

AD18

AD8

AE11

AE13

AE15

AE17

AE19

AE9

AF10

AF12

AF14

AF16

AF18

AF8

D18

D20

D22

D6

D8

E17

E19

E21

E5

E7

E9

F18

F20

F22

F6

F8

G21

Layout Note:

U53C

U53C

PZ47903

PZ47903

62.10055.011

62.10055.011

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCCA0

VCCA1

VCCA2

VCCA3

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VID0

VID1

VID2

VID3

VID4

VID5

VCCSENSE

VSSSENSE

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

G5

H22

H6

J21

J5

K22

U5

V22

V6

W21

W5

Y22

Y6

F26

B1

N1

AC26

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L21

L5

M22

M6

N21

N5

P22

P6

R21

R5

T22

T6

U21

P23

W4

E2

F2

F3

G3

G4

H4

AE7

AF6

TP_VCCA1

TP_VCCA2

TP_VCCA3

CPU_D10

1D5V_VCCA_S0

1 2

R394

R394

TP_VCCSENSE

TP_VSSSENSE

54D9R2F

54D9R2F

C17

C17

SCD01U16V2KX

SCD01U16V2KX

TP1TP1

TP3TP3

TP20TP20

0R2-0

0R2-0

H_VID0 41

H_VID1 41

H_VID2 41

H_VID3 41

H_VID4 41

H_VID5 41

12

R40

R40

DY

DY

12

VCCP_GMCH_S0

12

R39

R39

54D9R2F

54D9R2F

DY

DY

B

12

C15

C15

SC10U10V6ZY-U

SC10U10V6ZY-U

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF11

AF13

AF15

AF17

AF19

AF21

AF24

A11

A14

A17

A20

A23

A26

AA1

AA4

AA6

AA8

AB3

AB5

AB7

AB9

AE3

AE6

AE8

AF2

AF5

AF9

B12

B16

B19

B22

B25

C10

C13

C15

C18

C21

C24

D11

U53D

U53D

A2

VSS0

A5

VSS1

A8

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

B3

VSS75

B6

VSS76

B9

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

C1

VSS83

C4

VSS84

C7

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

D2

VSS92

D5

VSS93

D7

VSS94

D9

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

PZ47903

PZ47903

62.10055.011

62.10055.011

C

VCCP_GMCH_S0

12

C21

C21

SCD1U10V2MX-1

SCD1U10V2MX-1

3D3V_S0

1

2

3

12

BC85

BC85

SC1U10V3ZY

SC1U10V3ZY

DY

DY

0.1u *10 150u *1

12

12

C20

C20

SCD1U10V2MX-1

SCD1U10V2MX-1

VCC_CORE_S0

C29

C29

SCD1U10V2MX-1

SCD1U10V2MX-1

12

12

C18

C18

C19

C19

SC10U6D3V5MX

SC10U6D3V5MX

12

SC10U6D3V5MX

SC10U6D3V5MX

I max = 120 mA

U52

U52

SHDN#

GND

IN

G913C-U

G913C-U

DY

DY

12

C30

C30

C25

C25

SCD1U10V2MX-1

SCD1U10V2MX-1

SCD1U10V2MX-1

SCD1U10V2MX-1

12

12

C23

C23

C24

C24

SC10U6D3V5MX

SC10U6D3V5MX

SC10U6D3V5MX

SC10U6D3V5MX

SET

OUT

12

C16

C16

SCD1U10V2MX-1

SCD1U10V2MX-1

12

12

C33

C33

C35

C35

SC10U6D3V5MX

SC10U6D3V5MX

1D5V_VCCA_S0

5

4

12

SC10U6D3V5MX

SC10U6D3V5MX

D

12

12

BC2

BC2

SC1U10V3ZY

SC1U10V3ZY

DY

DY

12

C28

C28

C31

C31

SCD1U10V2MX-1

SCD1U10V2MX-1

SCD1U10V2MX-1

SCD1U10V2MX-1

12

12

C42

C42

C36

C36

SC10U6D3V5MX

SC10U6D3V5MX

SC10U6D3V5MX

SC10U6D3V5MX

BC84

BC84

SC22P

SC22P

DY

DY

1D5V_VCCA_SET

12

C22

C22

SCD1U10V2MX-1

SCD1U10V2MX-1

12

12

C39

C39

C40

C40

DY

DY

SC10U6D3V5MX

SC10U6D3V5MX

12

R398

R398

49K9R2F

49K9R2F

DY

DY

12

C32

C32

SCD1U10V2MX-1

SCD1U10V2MX-1

12

12

C41

C41

C50

C50

DY

DY

SC10U6D3V5MX

SC10U6D3V5MX

SC10U10V5ZY-L

SC10U10V5ZY-L

12

TC1

TC1

ST100U6D3VM-U

ST100U6D3VM-U

12

C318

C318

DY

DY

SC10U10V5ZY-L

SC10U10V5ZY-L

<Core Design>

<Core Design>

<Core Design>

12

R397

R397

12K7R3F

12K7R3F

DY

DY

12

C319

C319

DY

DY

SC10U10V5ZY-L

SC10U10V5ZY-L

1D5V_VCCA_S0 1D5V_S0

12

12

C322

C322

C321

C321

DY

DY

DY

DY

SC10U10V5ZY-L

SC10U10V5ZY-L

SC10U10V5ZY-L

SC10U10V5ZY-L

R28

R28

12

C323

C323

DY

DY

SC10U10V5ZY-L

SC10U10V5ZY-L

1 2

12

C325

C325

DY

DY

DY

DY

SC10U10V5ZY-L

SC10U10V5ZY-L

SC10U10V5ZY-L

SC10U10V5ZY-L

0R2-0

0R2-0

12

C324

C324

E

12

C326

C326

DY

DY

SC10U10V5ZY-L

SC10U10V5ZY-L

SC10U10V5ZY-L

SC10U10V5ZY-L

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

A

B

C

D

Date: Sheet of

CPU (2 of 2)

CPU (2 of 2)

CPU (2 of 2)

Leopard2

Leopard2

Leopard2

SC

SC

547Sunday, July 03, 2005

547Sunday, July 03, 2005

547Sunday, July 03, 2005

E

of

SC

Page 6

A

B

C

D

E

Trace 10 mil wide with 20 mil spacing

H_XRCOMP

12

R97

R97

24D9R2F

24D9R2F

4 4

VCCP_GMCH_S0

R96

R96

54D9R2F

54D9R2F

1 2

H_XSCOMP

VCCP_GMCH_S0

12

R105

R105

221R3F

221R3F

H_XSWING

12

R95

R95

100R2F

3 3

100R2F

1 2

C95

C95

SCD1U16V

SCD1U16V

VCCP_GMCH_S0

VCCP_GMCH_S0

Trace 10 mil wide with 20 mil spacing

Alviso Strapping Signals

and Configuration

Pin Name

CFG[2:0]

CFG[4:3] Reserved

CFG5 DMI x2 Select

2 2

CFG6 Reserved 0 = DDR2

CFG7

CFG8

CFG9

CFG[11:10]

CFG[13:12]

CFG[15:14] Reversed

CFG16

CFG17

CFG18

1 1

CFG19

CFG20

SDVOCRTL

_DATA

All strap signals are sampled with respect to the leading

NOTE:

edge of the Alviso GMCH PWORK In signal.

Strap Description Configuration

CPU Strap

Reserved

PCI Express Graphics

Lane Reversal

Reserved

XOR/ALL Z test

straps

FSB Dynamic ODT

Reversed

GMCH core VCC

Select

CPU VTT Select

Reversed

SDVO Present

A

H_YRCOMP

12

R118

R118

24D9R2F

24D9R2F

R109

R109

54D9R2F

54D9R2F

1 2

H_YSCOMP

12

R116

R116

221R3F

221R3F

H_YSWING

12

R117

R117

100R2F

100R2F

001 = FSB533FSB Frequency Select

101 = FSB400

others = Reversed

0 = DMI x2

1 = DMI x4

1 = DDR1

0 = Reserved

1 = Dothan

0 = Reserve Lanes

1 = Normal

00 = Reserved

01 = XOR mode enabled

10 = All Z mode enabled

11 = Normal Operation

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

0 = 1.05V

1 = 1.5V

0 = 1.05V

1 = 1.2V

C128

C128

SCD1U16V

SCD1U16V

1 2

REV.NO. 1.0

REF. NO. 15577

(Default)

(Default)

(Default)

(Default)

(Default)

(Default)

0 = No SDVO device present

1= SDVO device present

U19A

H_D#[63..0]4 H_A#[31..3] 4

page 183

(Default)

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

(Default)

(Default)

ALVISO-GM:71.0GMCH.08U

ALVISO-PM:71.0GMCH.0BU

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

C1

C2

D1

T1

L1

P1

U19A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

ALVISO-GM

ALVISO-GM

HADSTB#0

HADSTB#1

HCPURST#

HOST

HOST

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HCPUSLP#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HVREF

HBNR#

HBPRI#

HBREQ0#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS0#

HRS1#

HRS2#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP#_GMCH

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_CPURST# 4

CLK_MCH_BCLK# 3

CLK_MCH_BCLK 3

H_DBSY# 4

H_DEFER# 4

H_DPWR# 4

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

VCCP_GMCH_S0

H_VREF

12

C384

C384

SCD1U10V2KX

SCD1U10V2KX

1 2

R54 0R0402-PADR54 0R0402-PAD

ALVISO-GML:71.0GMCH.0JU

B

C

12

R457

R457

100R2F

100R2F

12

R458

R458

200R2F

200R2F

H_DINV#[3..0] 4

H_DSTBN#[3..0] 4

H_DSTBP#[3..0] 4

H_REQ#[4..0] 4

H_RS#[2..0] 4

D

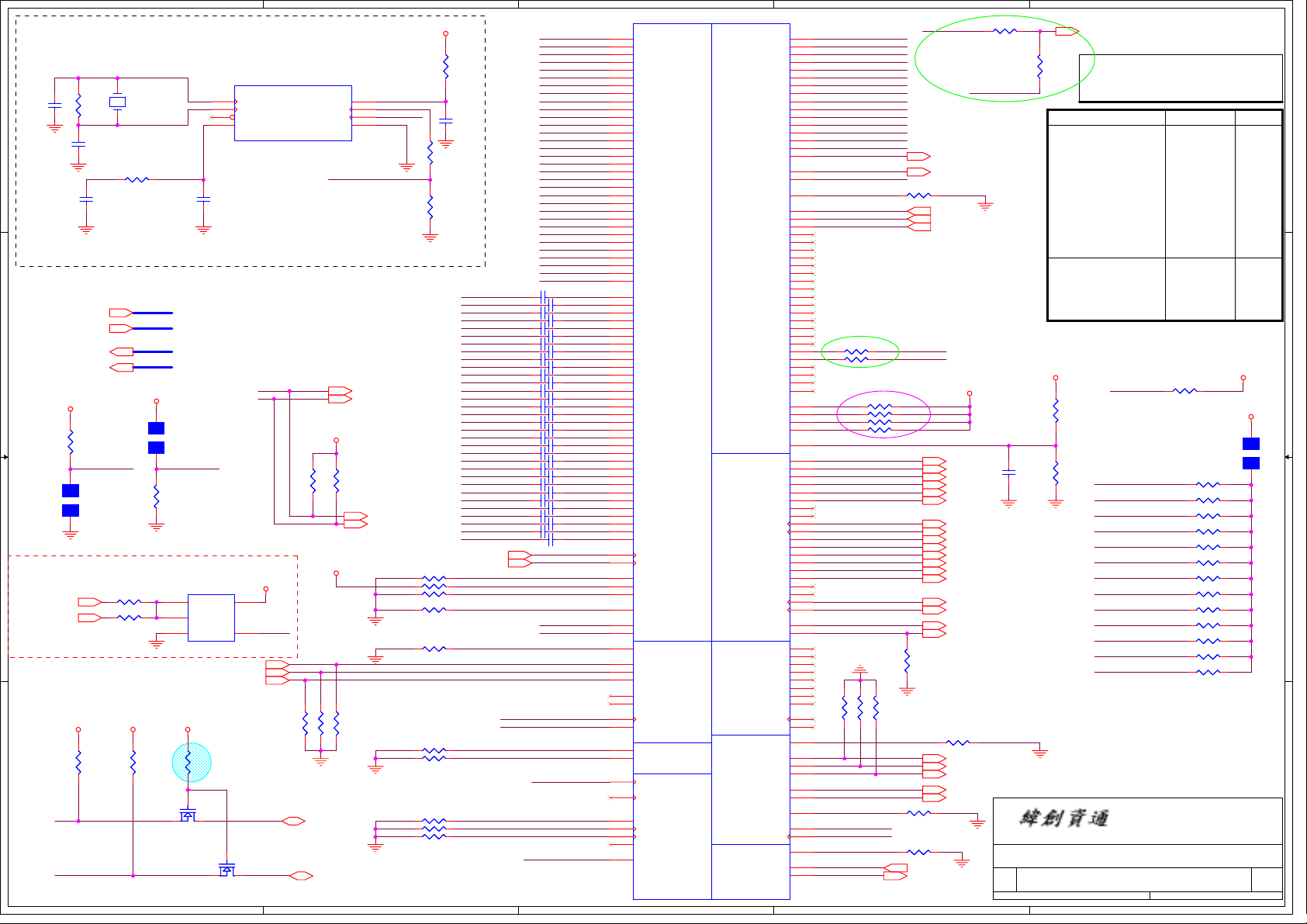

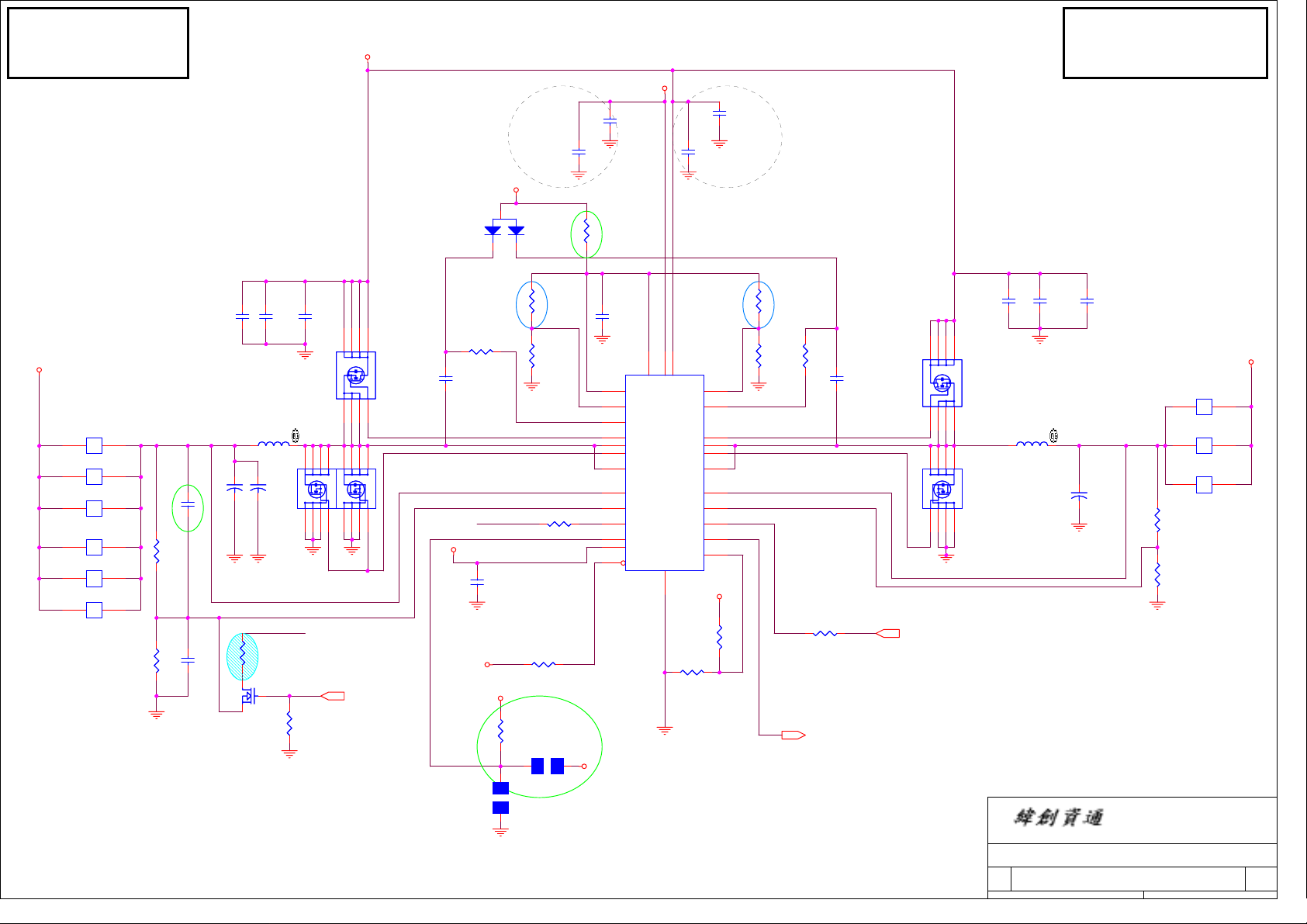

VID

VR_ON

Vcc_core

Vccp

Vcc_mch

MCH_PWERGD

CLK_ENABLE#

VGATE TO ICH6

H_CPUSLP# 4,21

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

Power On Sequencing

>3mS

Vboot Vvid

>100uS

3~10mS

647Monday, July 11, 2005

647Monday, July 11, 2005

647Monday, July 11, 2005

E

10~30uS

Vboot

<10uS

CORE_GMCH_S0

12

H_DPWR#

GMCH (1 of 5)

GMCH (1 of 5)

GMCH (1 of 5)

Leopard2

Leopard2

Leopard2

R519

R519

0R2-0

0R2-0

DY

DY

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

-1

-1

of

-1

Page 7

A

U19B

U19B

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

SMYSLEWIN

AF10

SMYSLEWOUT

ALVISO-GM

ALVISO-GM

Ref ALVISO EDS-1 Page 115

For Dothan-B

R420

R420

1KR2

1KR2

CFG2

CFG1

CFG0

R419

R419

CFG2=0(R419):133MHZ

CFG2=1(R420):100MHZ

CPU_SEL0 3,4

CPU_SEL1 3,4

CFG(2..1) FREQ.(MHz)

10 400

00 533

11 Reserved

R535

R535

40D2R2F

40D2R2F

10KR2

10KR2

10KR2

10KR2

FOR DDR2

R533

R533

80D6R2F

80D6R2F

M_RCOMPN

M_RCOMPP

R543

R543

80D6R2F

80D6R2F

DMI_TXN[3..0]22

DMI_TXP[3..0]22

DMI_RXN[3..0]22

DMI_RXP[3..0]22

12

R534

R534

40D2R2F

40D2R2F

PM_EXTTS#0

PM_EXTTS#1

M_CLK_DDR011

M_CLK_DDR111

M_CLK_DDR311

M_CLK_DDR411

M_CLK_DDR#011

M_CLK_DDR#111

M_CLK_DDR#311

M_CLK_DDR#411

M_CKE011,12

M_CKE111,12

M_CKE211,12

M_CKE311,12

M_CS#011,12

M_CS#111,12

M_CS#211,12

M_CS#311,12

M_OCDCOMP0

M_OCDCOMP1

M_ODT011,12

M_ODT111,12

M_ODT211,12

M_ODT311,12

DDR_VREF_S3

A

12

C154

C154

SCD1U10V2MX-1

SCD1U10V2MX-1

R465

R465

10KR2

10KR2

4 4

3 3

Layout Note:

Route as short

as possible

12

2 2

2D5V_S0

1 2

R498

R498

1 2

R471

R471

1D8V_S3

12

1 1

12

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

VCCP_GMCH_S0

12

12

R437

R437

10KR2

10KR2

12

R438

R438

4K7R2

4K7R2

DY

DY

12

12

4K7R2

4K7R2

DY

DY

B

CFG/RSVD

CFG/RSVD

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PM

PM

PWROK

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

CLK

CLK

DREF_SSCLKP

NC

NC

B

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSTIN#

DMI

DMI

DDR MUXING

DDR MUXING

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

CFG1

H13

G14

CFG3 PEG_COMP

F16

CFG4

F15

CFG5

G15

CFG6

E16

CFG7

D17

CFG8

J16

CFG9

D15

CFG10

E15

CFG11

D14

CFG12

E14

CFG13

H12

CFG14

C14

CFG15

H15

CFG16

J15

CFG17

H14

CFG18

G22

CFG19

G23

CFG20

D23

G25

G24

J17

A31

A30

D26

D25

J23

PM_EXTTS#0

J21

PM_EXTTS#1

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

CFG0

G16

When Low 2.2K Ohm

1 2

R441 DUMMY-R2R441 DUMMY-R2

1 2

R440 DUMMY-R2R440 DUMMY-R2

1 2

R464 DUMMY-R2R464 DUMMY-R2

1 2

R469 2K2R2R469 2K2R2

1 2

R442 DUMMY-R2R442 DUMMY-R2

1 2

R461 DUMMY-R2R461 DUMMY-R2

1 2

R439 DUMMY-R2R439 DUMMY-R2

1 2

R468 DUMMY-R2R468 DUMMY-R2

1 2

R69 DUMMY-R2R69 DUMMY-R2

1 2

R466 DUMMY-R2R466 DUMMY-R2

1 2

R459 DUMMY-R2R459 DUMMY-R2

1 2

R467 DUMMY-R2R467 DUMMY-R2

1 2

R463 DUMMY-R2R463 DUMMY-R2

1 2

R460 DUMMY-R2R460 DUMMY-R2

1 2

R462 DUMMY-R2R462 DUMMY-R2

RST1#

1 2

R52

R52

1 2

R536

R536

1KR2

1KR2

C

CFG2

Note:

CRT_RED,

CRT_GREEN,

CRT_BLUE, are

ground

referenced.

Place 150 Ohm termination resistors close to GMCH

PM_BMBUSY# 22

PM_THRMTRIP-A# 4,21

PWROK 25

100R2

100R2

DREFCLK# 3

DREFCLK 3

DREFSSCLK# 3

DREFSSCLK 3

PLT_RST1# 13,24,26

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

Strapping

CFG16

CFG17

Intel suggest NC Due to votusly DVO

Intel design guide suggest

Ref no.:14511

page 210

Note: Intel design guide

suggest(page 203)

If the LVDS interface is

not implementd, all

signals associated with

the interface can be left

as no connects.

CFG[17:3] have internal pullup resistors.

CFG[19:18] have internal pulldown

resistors

C

CLK_MCH_3GPLL#3

CLK_MCH_3GPLL3

CORE_GMCH_S0

Alviso will provide SDVO_CTRLCLK

and CTRLDATA pulldowns on-die

SDVO_DAT

TP22TPAD30 TP22TPAD30

SDVO_CLK

TP23TPAD30 TP23TPAD30

R494 0R2-0R494 0R2-0

1 2

R495 0R2-0R495 0R2-0

1 2

R493 0R2-0R493 0R2-0

1 2

R492 0R2-0R492 0R2-0

1 2

H24

H25

AB29

AC29

A15

C16

A17

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

J18

J20

D

U19G

U19G

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO-GM

ALVISO-GM

D

E

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

MISCTVVGALVDS

MISCTVVGALVDS

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

D36

D34

PEG_RXN0

E30

PEG_RXN1

F34

PEG_RXN2

G30

PEG_RXN3

H34

PEG_RXN4

J30

PEG_RXN5

K34

PEG_RXN6

L30

PEG_RXN7

M34

PEG_RXN8

N30

PEG_RXN9

P34

PEG_RXN10

R30

PEG_RXN11

T34

PEG_RXN12

U30

PEG_RXN13

V34

PEG_RXN14

W30

PEG_RXN15

Y34

PEG_RXP0

D30

PEG_RXP1

E34

PEG_RXP2

F30

PEG_RXP3

G34

PEG_RXP4

H30

PEG_RXP5

J34

PEG_RXP6

K30

PEG_RXP7

L34

PEG_RXP8

M30

PEG_RXP9

N34

PEG_RXP10

P30

PEG_RXP11

R34

PEG_RXP12

T30

PEG_RXP13

U34

PEG_RXP14

V30

PEG_RXP15

W34

TXN0

E32

TXN1

F36

TXN2

G32

TXN3

H36

TXN4

J32

TXN5

K36

TXN6

L32

TXN7

M36

TXN8

N32

TXN9

P36

TXN10

R32

TXN11

T36

TXN12

U32

TXN13

V36

TXN14

W32

TXN15

Y36

TXP0

D32

TXP1

E36

TXP2

F32

TXP3

G36

H32

TXP5

J36

TXP6

K32

TXP7

L36

M32

TXP9

N36

TXP10

P32

TXP11

R36

TXP12

T32

TXP13

U36

TXP14

V32

TXP15

W36

2D5V_S0

GMCH (2 of 5)

GMCH (2 of 5)

GMCH (2 of 5)

Leopard2

Leopard2

Leopard2

R473

R473

PEG_RXN[15..0] 13

PEG_RXP[15..0] 13

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PEG_TXN0

SCD1U16V

SCD1U16V

PEG_TXN1

SCD1U16V

SCD1U16V

PEG_TXN2

SCD1U16V

SCD1U16V

PEG_TXN3

SCD1U16V

SCD1U16V

PEG_TXN4

SCD1U16V

SCD1U16V

PEG_TXN5

SCD1U16V

SCD1U16V

PEG_TXN6

SCD1U16V

SCD1U16V

PEG_TXN7

SCD1U16V

SCD1U16V

PEG_TXN8

SCD1U16V

SCD1U16V

PEG_TXN9

SCD1U16V

SCD1U16V

PEG_TXN10

SCD1U16V

SCD1U16V

PEG_TXN11

SCD1U16V

SCD1U16V

PEG_TXN12

SCD1U16V

SCD1U16V

PEG_TXN13

SCD1U16V

SCD1U16V

PEG_TXN14

SCD1U16V

SCD1U16V

PEG_TXN15

SCD1U16V

SCD1U16V

PEG_TXP0

SCD1U16V

SCD1U16V

PEG_TXP1

SCD1U16V

SCD1U16V

PEG_TXP2

SCD1U16V

SCD1U16V

PEG_TXP3

SCD1U16V

SCD1U16V

PEG_TXP4TXP4

SCD1U16V

SCD1U16V

PEG_TXP5

SCD1U16V

SCD1U16V

PEG_TXP6

SCD1U16V

SCD1U16V

PEG_TXP7

SCD1U16V

SCD1U16V

PEG_TXP8TXP8

SCD1U16V

SCD1U16V

PEG_TXP9

SCD1U16V

SCD1U16V

PEG_TXP10

SCD1U16V

SCD1U16V

PEG_TXP11

SCD1U16V

SCD1U16V

PEG_TXP12

SCD1U16V

SCD1U16V

PEG_TXP13

SCD1U16V

SCD1U16V

PEG_TXP14

SCD1U16V

SCD1U16V

PEG_TXP15

SCD1U16V

SCD1U16V

C372

C372

C107

C107

C387

C387

C108

C108

C386

C386

C116

C116

C409

C409

C118

C118

C410

C410

C117

C117

C430

C430

C131

C131

C429

C429

C130

C130

C452

C452

C142

C142

C373

C373

C97

C97

C389

C389

C106

C106

C388

C388

C105

C105

C407

C407

C119

C119

C408

C408

C115

C115

C431

C431

C129

C129

C432

C432

C132

C132

C453

C453

C143

C143

When High 1K Ohm

1 2

R470 DUMMY-R2R470 DUMMY-R2

1 2

R497 DUMMY-R2R497 DUMMY-R2

1 2

R496 DUMMY-R2R496 DUMMY-R2

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

747Thursday, July 07, 2005

747Thursday, July 07, 2005

747Thursday, July 07, 2005

E

PEG_TXN[15..0]

PEG_TXP[15..0]

of

24D9R2F

24D9R2F

13

13

1D5V_S0

12

CFG18

CFG19

CFG20

-1

-1

-1

Page 8

A

4 4

U19C

M_A_DQ[63..0]11

3 3

2 2

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

U19C

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO-GM

ALVISO-GM

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_RCVENIN#

SA_RCVENOUT#

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_WE#

B

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

GMCH_TP48

GMCH_TP49

M_A_BS#0 11,12

M_A_BS#1 11,12

M_A_BS#2 11,12

M_A_DM[7..0] 11

M_A_DQS[7..0] 11

M_A_DQS#[7..0] 11

M_A_A[13..0] 11,12

M_A_CAS# 11,12

M_A_RAS# 11,12

TP29 TPAD30TP29 TPAD30

TP28 TPAD30TP28 TPAD30

M_A_WE# 11,12

C

M_B_DQ[63..0]11

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U19D

U19D

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO-GM

ALVISO-GM

D

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

GMCH_TP50

GMCH_TP51

E

M_B_BS#0 11,12

M_B_BS#1 11,12

M_B_BS#2 11,12

M_B_DM[7..0] 11

M_B_DQS[7..0] 11

M_B_DQS#[7..0] 11

M_B_A[13..0] 11,12

M_B_CAS# 11,12

M_B_RAS# 11,12

TP27 TPAD30TP27 TPAD30

TP26 TPAD30TP26 TPAD30

M_B_WE# 11,12

1 1

A

B

C

D

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

GMCH (3 of 5)

GMCH (3 of 5)

GMCH (3 of 5)

Leopard2

Leopard2

Leopard2

E

847Thursday, July 07, 2005

847Thursday, July 07, 2005

847Thursday, July 07, 2005

of

-1

-1

-1

Page 9

A

4 4

1D5V_DLVDS_S0

3 3

H17

B26

3D3V_S0 2D5V_S0

U59

U59

2

VOUT

3

12

C359

C359

SCD1U10V2MX-1

SCD1U10V2MX-1

VIN

1

GND

APL5308-25AC-TR

APL5308-25AC-TR

12

C63

C63

U19E

U19E

F17

E17

D18

C18

F18

E18

H18

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVBG

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

G18

VSSA_TVBG

D19

B25

VCCD_LVDS0

VCCD_TVDAC

VCCDQ_TVDAC

B

G10

G10

AE26

AP25

VCCSM15

12

AN25

AM25

VCCSM16

VCCSM17

1 2

C75

C75

SC10U10V5ZY-L

SC10U10V5ZY-L

AL25

AK25

AJ25

AH25

VCCSM18

VCCSM19

VCCSM20

VCCSM21

POWER

POWER

GAP-CLOSE-PWR

GAP-CLOSE-PWR

AG25

VCCSM22

VCCSM23

12

C76

C76

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C160

C160

SCD1U10V2MX-1

SCD1U10V2MX-1

Note: All VCCSM

C161

C161

SCD1U10V2MX-1

SCD1U10V2MX-1

V1.8_DDR_CAP5

AP29

AD28

AD27

AC27

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

pins shorted

internally

1 2

AP26

AN26

AM26

AL26

VCCSM6

VCCSM7

VCCSM8

VCCSM9

C165

C165

SCD1U10V2MX-1

SCD1U10V2MX-1

AK26

AJ26

AH26

AG26

AF26

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

12

V1.8_DDR_CAP1

V1.8_DDR_CAP2

A25

A35

VCCD_LVDS1

VCCD_LVDS2

AM37

AH37

B22

B21

A21

VCCHV0

VCCHV1

VCCHV2

VCCA_LVDS

VCCSM0

AF25

AE25

VCCSM24

2D5V_S02D5V_TVDAC_S0

AE24

AE23

VCCSM25

VCCSM26

C

12

C449

C449

SC10U10V5ZY-L

SC10U10V5ZY-L

AE22

AE21

AE20

AE19

VCCSM27

VCCSM28

VCCSM29

VCCSM30

1D5V_S0

2D5V_S0 2D5V_ALVDS_S0

2D5V_S0 2D5V_TXLVDS_S0

G11

G11

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

G13

G13

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

G12

G12

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

12

C79

C79

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C84

C84

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C81

C81

SCD1U10V2MX-1

SCD1U10V2MX-1

FOR DDR2

12

C447

C447

SC10U10V5ZY-L

SC10U10V5ZY-L

AE18

AE17

AE16

VCCSM31

VCCSM32

VCCSM33

AE15

AE14

VCCSM34

VCCSM35

12

TC9

TC9

ST100U4VBM-U

ST100U4VBM-U

DY

DY

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

1D5V_DLVDS_S0

12

C80

C80

SC10U10V5ZY-L

SC10U10V5ZY-L

12

C83

C83

SCD01U16V3KX

SCD01U16V3KX

12

C82

C82

SC4D7U10V5ZY

SC4D7U10V5ZY

1D8V_S3

Note: All VCCSM

AN12

AM12

AL12

AK12

AJ12

AH12

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

pins shorted

internally

C164

C164

1 2

SCD1U10V2MX-1

SCD1U10V2MX-1

AG12

AF12

AE12

AD11

AC11

AB11

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

AB10