Page 1

5

www.vinafix.vn

4

3

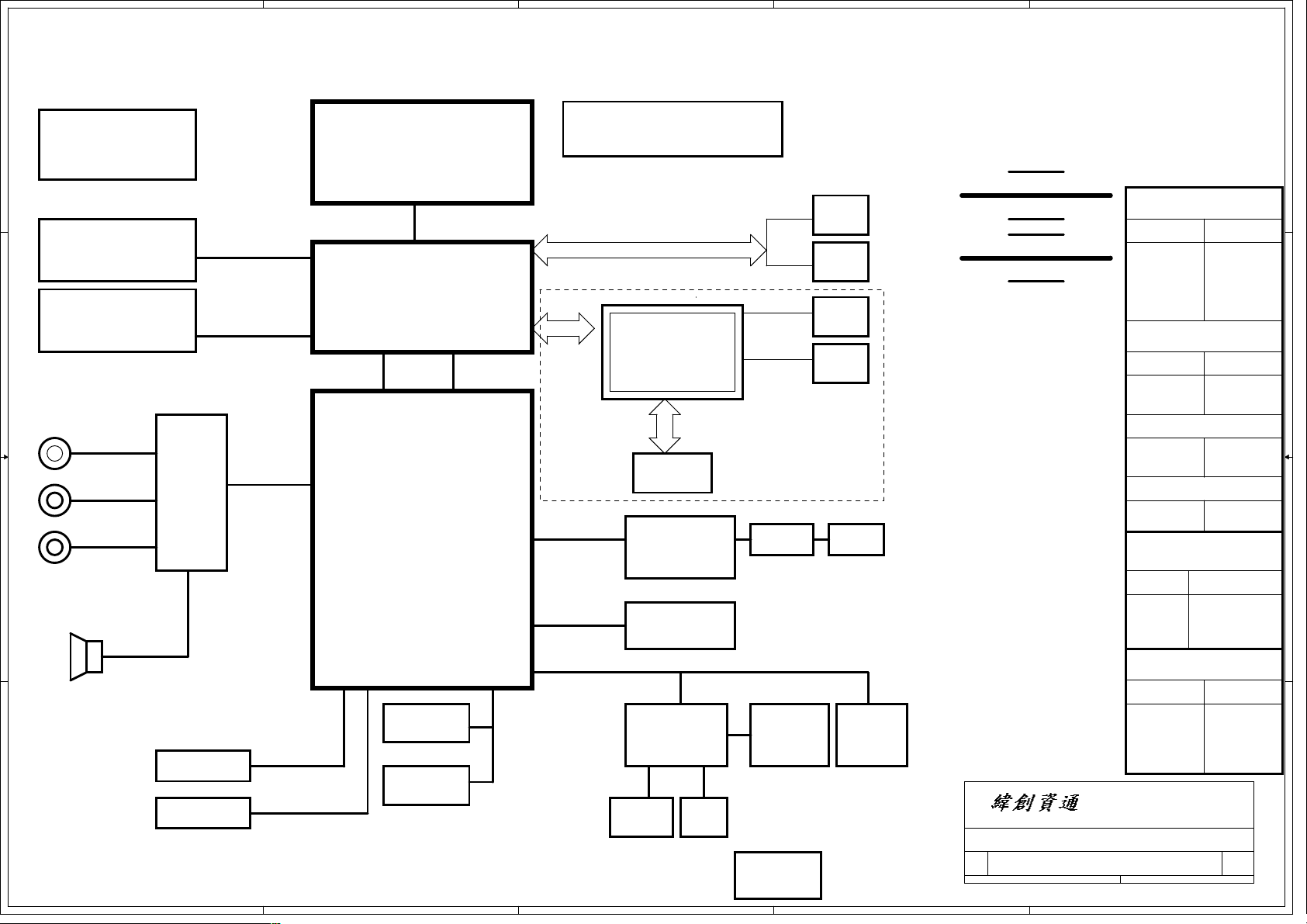

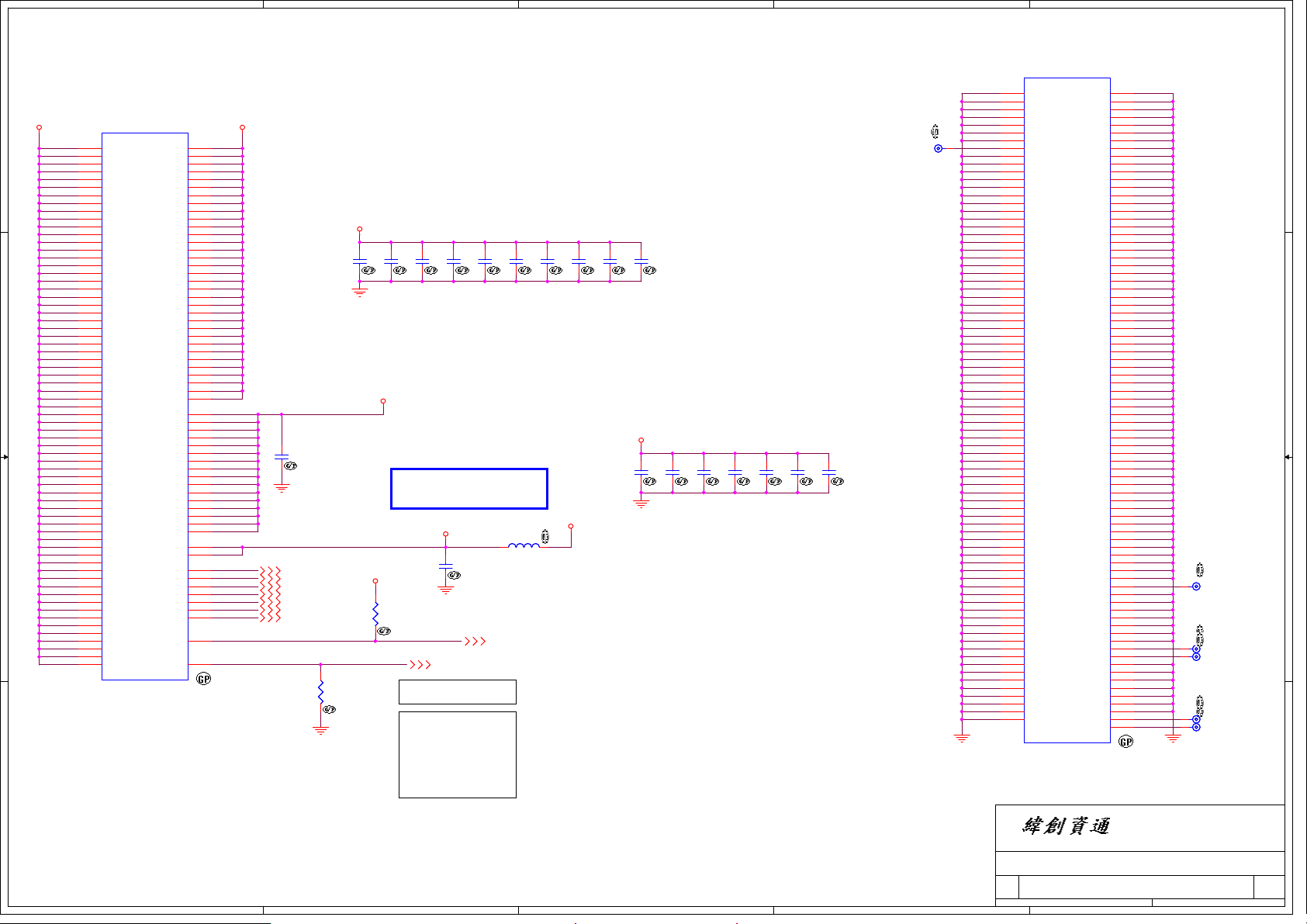

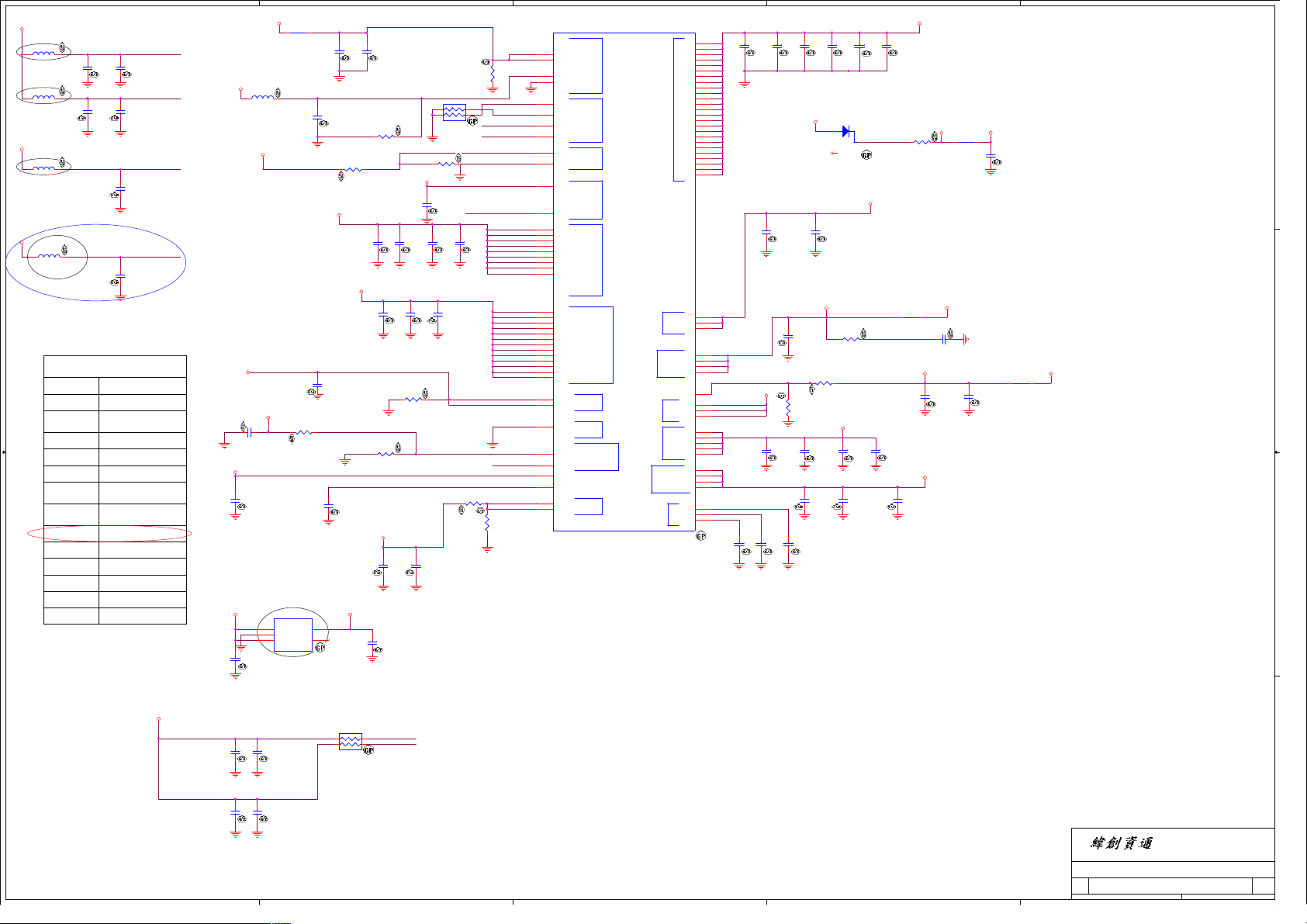

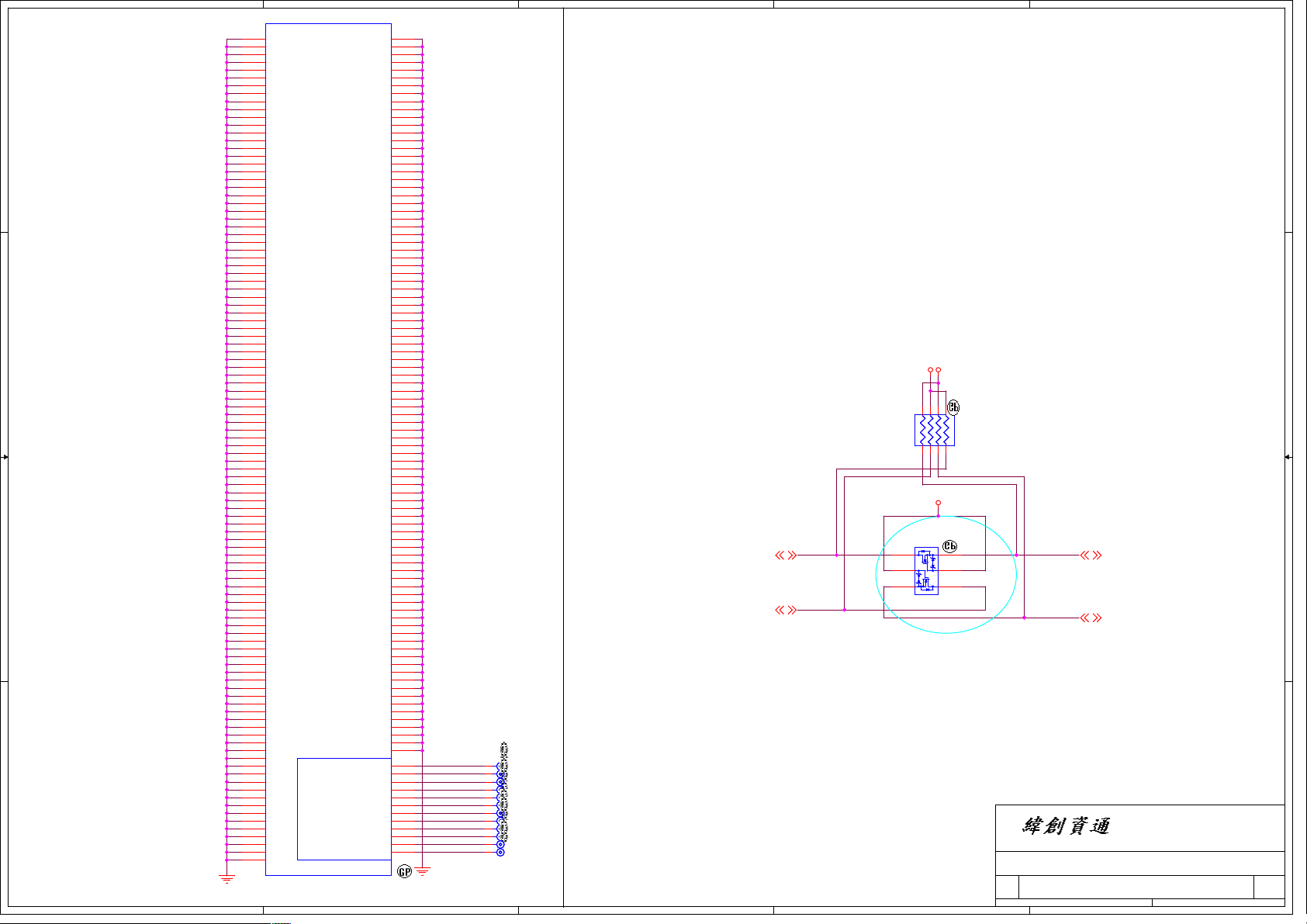

LB46E Block Diagram

2

1

Project code: 91.4HK01.A01

PCB P/N :

REVISION : 10307-sc

D D

Mobile CPU

CLK GEN.

3

Penryn 479

4, 5

HOST BUS 667/800/1067MHz@1.05V

DDR3 DIMM1

800/1066 MHz

DDR3 DIMM2

800/1066 MHz

C C

Line Out

(NO SPDIF)

25

MIC In AZALIA

25

Internal MIC

25

B B

25

INT.SPKR

A A

5

800/1066MHz

16

800/1066MHz

17

Codec

CX20671

25

HDD SATA

ODD SATA

Cantiga

AGTL+ CPU I/F

DDR Memory I/F

INTEGRATED GRAHPICS

LVDS, CRT I/F

6,7,8,9,10,11

X4 DMI

400MHz

C-Link0

ICH9M

6 PCIe ports

PCI/PCI BRIDGE

ACPI 2.0

4 SATA

12 USB 2.0/1.1 ports

ETHERNET (10/100/1000MbE)

High Definition Audio

LPC I/F

Serial Peripheral I/F

Matrix Storage Technology(DO)

Active Managemnet Technology(DO)

12,13,14,15

Camera

(USB)

18

SATA

20

SATA

21

USB

3 Port

4

22

USB

USB

THERMAL EMC2102

27

UMA

DIS

nVIDIA

PCIE x 16

PCIex1

PCIex1

LPC BUS

N11M-OP1

4X128MB

GDDRIII

52,53

LAN

RTL8111E

Mini Card

Kedron

a/b/g/n

KBC

KBC773L

Touch

Pad

INT.

KB

30 30

3

46~51

23

26

28

CRT

LCD

CRT

LCD

TXFM RJ45

24

BIOS

Winbond

W25X16

16M Bits

Power Board

29 34

31

19

18

19

18

LPC

DEBUG

CONN.

PCB STACKUP

TOP

VCC

S

S

GND

BOTTOM

SYSTEM DC/DC

TPS51125

INPUTS

DCBATOUT

OUTPUTS

5V_S5

3D3V_S5

37

SYSTEM DC/DC

TPS51218/RT9025

INPUTS OUTPUTS

DCBATOUT

TPS51116

DCBATOUT 1D5V_S3

TPS51116

1D5V_S3

1D05V_S0

1D8V_S0

0D75V_S0

39

38

38

CPU DC/DC

ISL6266A

153Monday, December 27, 2010

153Monday, December 27, 2010

153Monday, December 27, 2010

1

OUTPUTS

VCC_CORE_S0

0.35~1.5V

OUTPUTSINPUTS

BT+

DCBATOUT

INPUTS

DCBATOUT

CHARGER

BQ24745

DCBATOUT

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

1_BLOCK DIAGRAM

1_BLOCK DIAGRAM

1_BLOCK DIAGRAM

Taipei Hsien 221, Taiwan, R.O.C.

LB46E

LB46E

LB46E

SA

SA

SA

36

41

Page 2

A

www.vinafix.vn

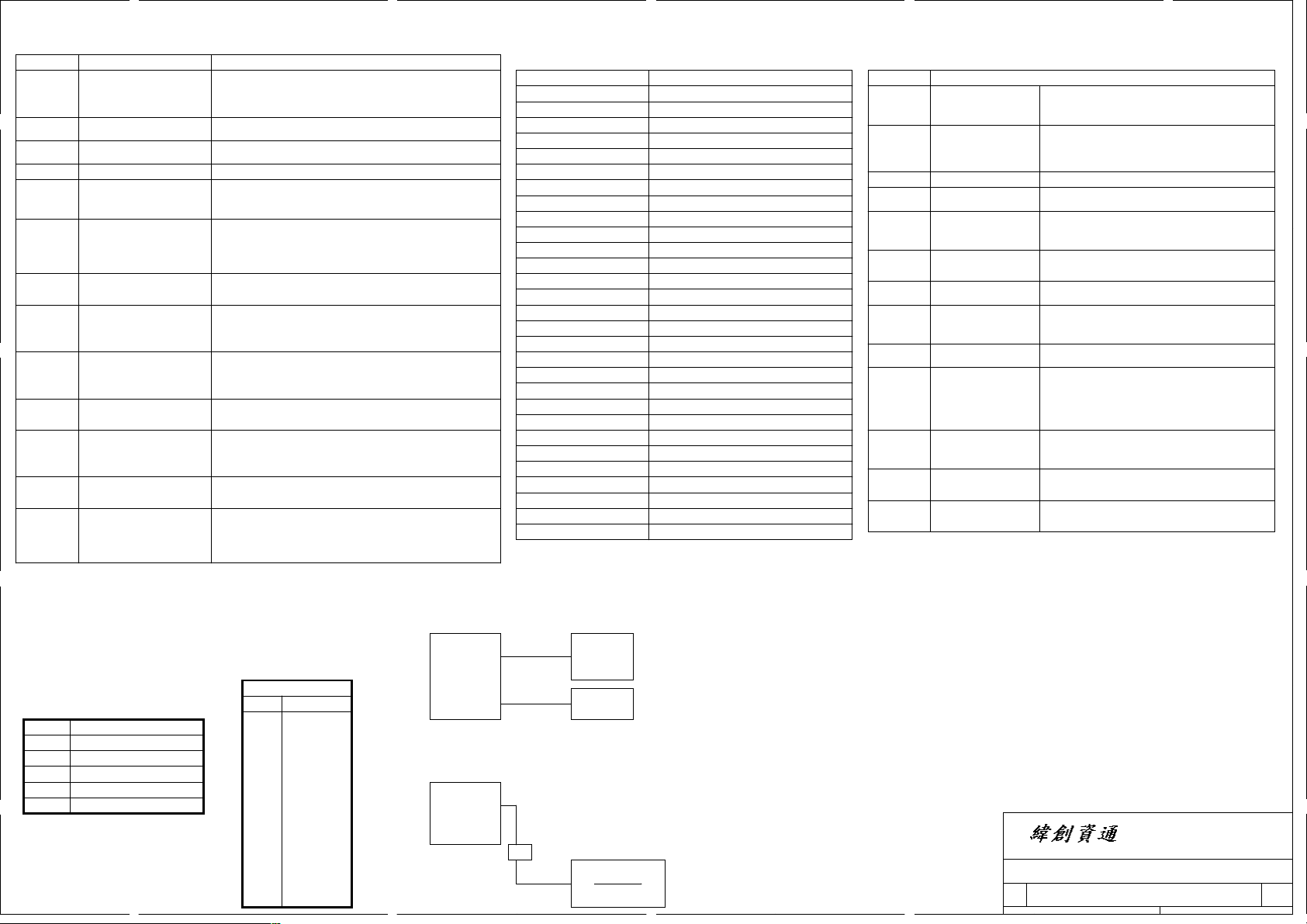

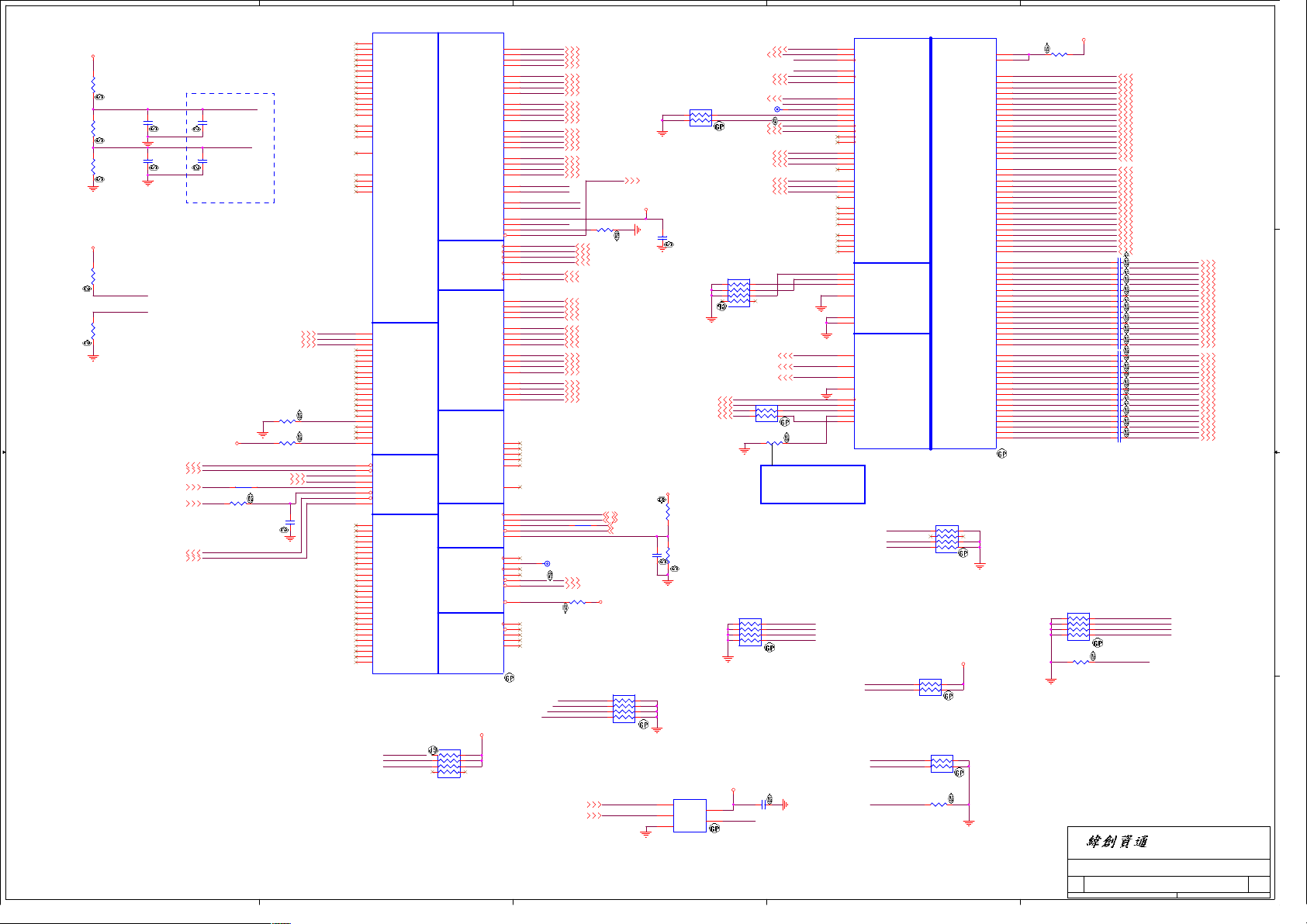

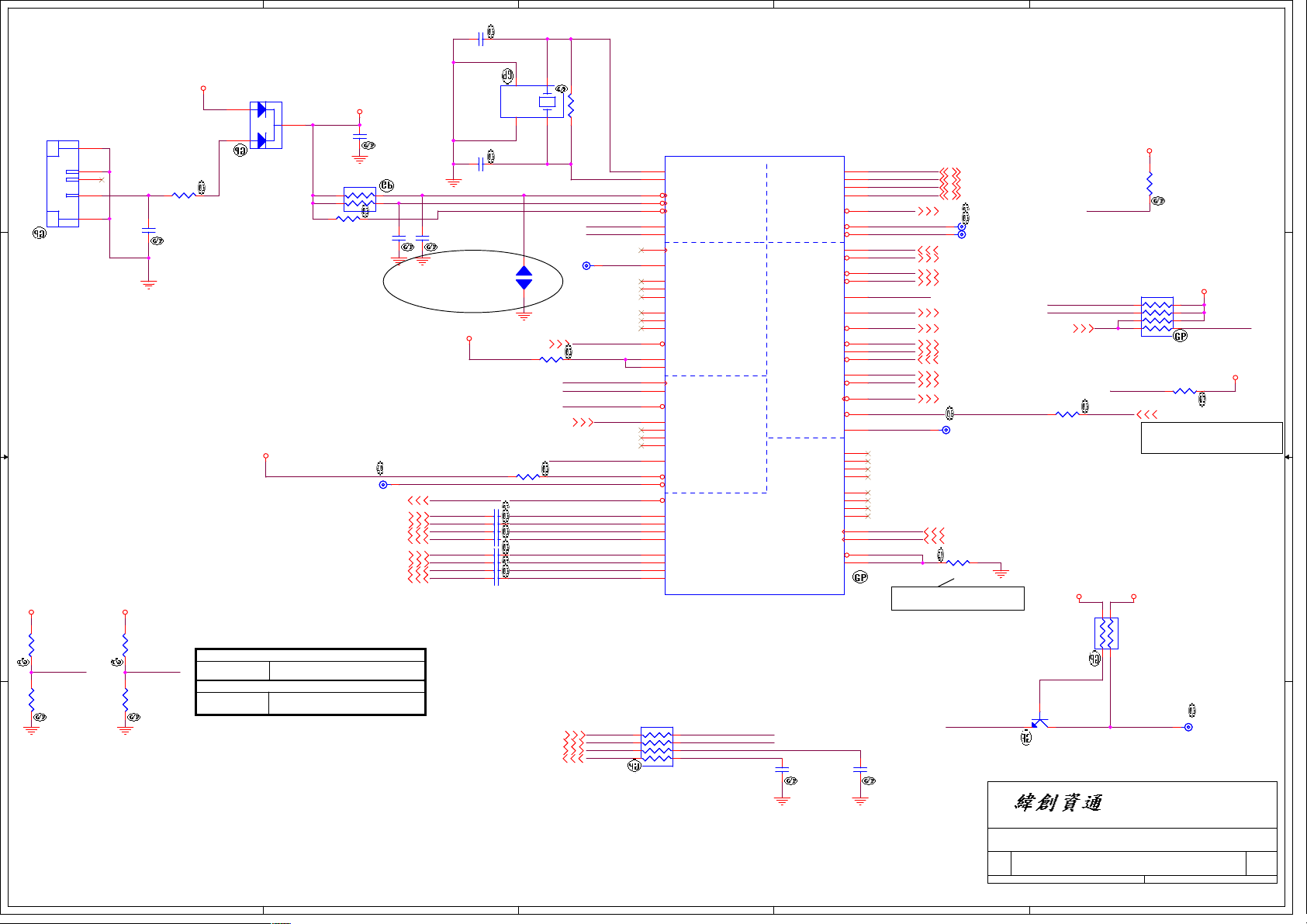

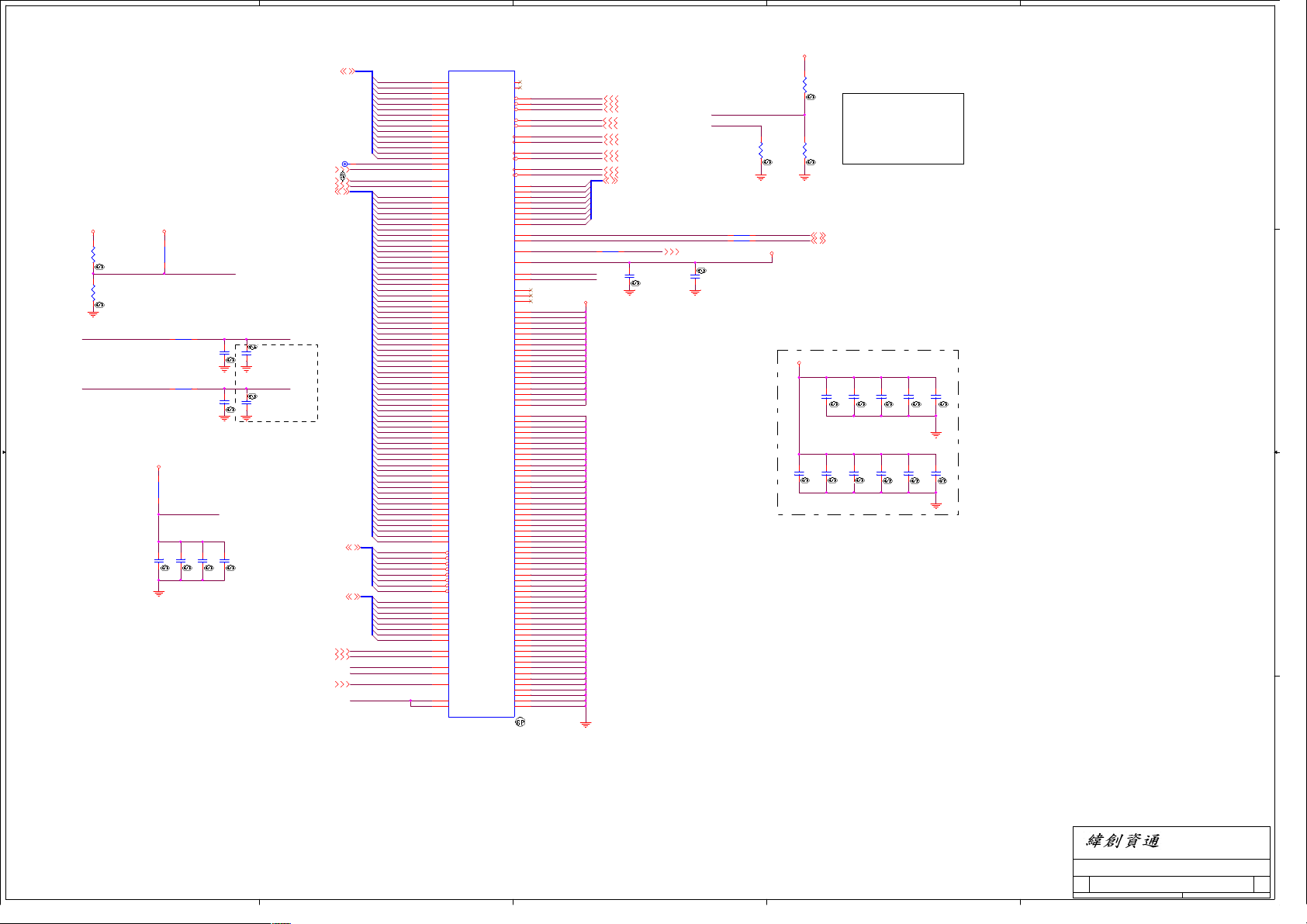

ICH9M Functional Strap Definitions

Signal

HDA_SDOUT

HDA_SYNC

4 4

GNT2#/

GPIO53

GPIO20

GNT1#/

GPIO51

GNT3#/

GPIO55

GNT0#:

SPI_CS1#/

GPIO58

SPI_MOSI

3 3

GPIO49

SATALED#

SPKR

TP3

GPIO33/

HDA_DOCK

_EN#

Usage/When Sampled

XOR Chain Entrance/

PCIE Port Config1 bit1,

Rising Edge of PWROK

PCIE config1 bit0,

Rising Edge of PWROK.

PCIE config2 bit2,

Rising Edge of PWROK.

Reserved

ESI Strap (Server Only)

Rising Edge of PWROK

Top-Block

Swap Override.

Rising Edge of PWROK.

Boot BIOS Destination

Selection 0:1.

Rising Edge of PWROK.

Integrated TPM Enable,

Rising Edge of CLPWROK

DMI Termination Voltage,

Rising Edge of PWROK.

PCI Express Lane

Reversal. Rising Edge

of PWROK.

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

Flash Descriptor

Security Override Strap

Rising Edge of PWROK

Allows entrance to XOR Chain testing when TP3

pulled low.When TP3 not pulled low at rising edge

of PWROK,sets bit1 of RPC.PC(Config Registers:

offset 224h). This signal has weak internal pull-down

This signal has a weak internal pull-down.

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

This signal has a weak internal pull-up.

Sets bit2 of RPC.PC2(Config Registers:Offset 0224h)

This signal should not be pulled high.

ESI compatible mode is for server platforms only.

This signal should not be pulled low for desttop

and mobile.

Sampled low:Top-Block Swap mode(inverts A16 for

all cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC.

Sample low: the Integrated TPM will be disabled.

Sample high: the MCH TPM enable strap is sampled

low and the TPM Disable bit is clear, the

Integrated TPM will be enable.

The signal is required to be low for desktop

applications and required to be high for

mobile applications.

Signal has weak internal pull-up. Sets bit 27

of MPC.LR(Device 28:Function 0:Offset D8)

If sampled high, the system is strapped to the

"No Reboot" mode(ICH9 will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.

This signal should not be pull low unless using

XOR Chain testing.

Sampled low:the Flash Descriptor Security will be

overridden. If high,the security measures will be

in effect.This should only be enabled in manufacturing

environments using an external pull-up resister.

ICH9 EDS 642879 Rev.1.5

Comment

2 2

B

ICH9M Integrated Pull-up

page 92

and Pull-down Resistors

SIGNAL Resistor Type/Value

CL_CLK[1:0]

CL_DATA[1:0]

CL_RST0#

DPRSLPVR/GPIO16

ENERGY_DETECT

HDA_BIT_CLK

HDA_DOCK_EN#/GPIO33

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GLAN_DOCK#

GNT[3:0]#/GPIO[55,53,51]

GPIO[20]

GPIO[49]

LDA[3:0]#/FHW[3:0]#

LAN_RXD[2:0]

LDRQ[0]

LDRQ[1]/GPIO23

PME#

PWRBTN#

SATALED#

SPI_CS1#/GPIO58/CLGPIO6

SPI_MOSI

SPI_MISO

SPKR

TACH_[3:0]

TP[3]

USB[11:0][P,N]

C

Cantiga chipset and ICH9M I/O controller

Hub strapping configuration

ICH9 EDS 642879 Rev.1.5

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

The pull-up or pull-down active when configured for native

GLAN_DOCK# functionality and determined by LAN controller

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 15K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 15K

D

Montevina Platform Design guide 22339 0.5

Pin Name

CFG[2:0]

CFG[4:3]

CFG8

CFG[15:14]

CFG[18:17]

CFG5

CFG6

CFG7

CFG9

CFG10 PCIE Loopback enable

CFG[13:12]

CFG16

CFG19

CFG20

SDVO_CTRLDATA

NOTE:

1. All strap signals are sampled with respect to the leading edge of

the (G)MCH Power OK (PWROK) signal.

2. iTPM can be disabled by a 'Soft-Strap' option in the

Flash-decriptor section of the Firmware. This 'Soft-Strap' is

activated only after enabling iTPM via CFG6.

Only one of the CFG10/CFG/12/CFG13 straps can be enabled at any time.

Strap Description

FSB Frequency

Select

Reserved

DMI x2 Select

iTPM Host

Interface

Intel Management

engine Crypto strap

PCIE Graphics Lane

XOR/ALL

FSB Dynamic ODT

DMI Lane Reversal

Digital Display Port

(SDVO/DP/iHDMI)

Concurrent with PCIe

SDVO Present

Local Flat Panel

(LFP) Present

Configuration

000 = FSB1067

011 = FSB667

010 = FSB800

others = Reserved

0 = DMI x2

1 = DMI x4

0= The iTPM Host Interface is enabled(Note2)

1=The iTPM Host Interface is disalbed(default)

0 = Transport Layer Security (TLS) cipher

suite with no confidentiality

1 = TLS cipher suite with

confidentiality (default)

0 = Reverse Lanes,15->0,14->1 ect..

1= Normal operation(Default):Lane

Numbered in order

0 = Enable (Note 3)

1= Disabled (default)

00 = Reserve

10 = XOR mode Enabled

01 = ALLZ mode Enabled (Note 3)

11 = Disabled (default)

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

0 = Normal operation(Default):

Lane Numbered in Order

1 = Reverse Lanes

DMI x4 mode[MCH -> ICH]:(3->0,2->1,1->2and0->3)

DMI x2 mode[MCH -> ICH]:(3->0,2->1)

0 = Only Digital Display Port

or PCIE is operational (Default)

1 =Digital display Port and PCIe are

operting simulataneously via the PEG port

0 =No SDVO Card Present (Default)

1 = SDVO Card Present

0 = LFP Disabled (Default)

1= LFP Card Present; PCIE disabledL_DDC_DATA

E

page 218

(Default)

(Default)

SMBus

EMC2102

Thermal

USB Table

USB

PCIE Routing

LANE1

LANE2

LANE3

LANE4

LANE5

LANE6

1 1

RTL8111E

MiniCard WLAN

NC

NC

NC

NC

Pair

Device

0

USB1

1

USB3

NC

2

3

MINIC1

WEBCAM

4

5

NC

6

NC

7

NC

8

NC

USB2

9

1011NC

NC

KBC

ICH9M

BAT_SCL

SMBC_ICH

BATTERY

9LPRS365BKLFT

DDR

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Reference

Reference

Reference

Taipei Hsien 221, Taiwan, R.O.C.

LB46E

LB46E

LB46E

253Monday, October 25, 2010

253Monday, October 25, 2010

253Monday, October 25, 2010

SB

SB

SB

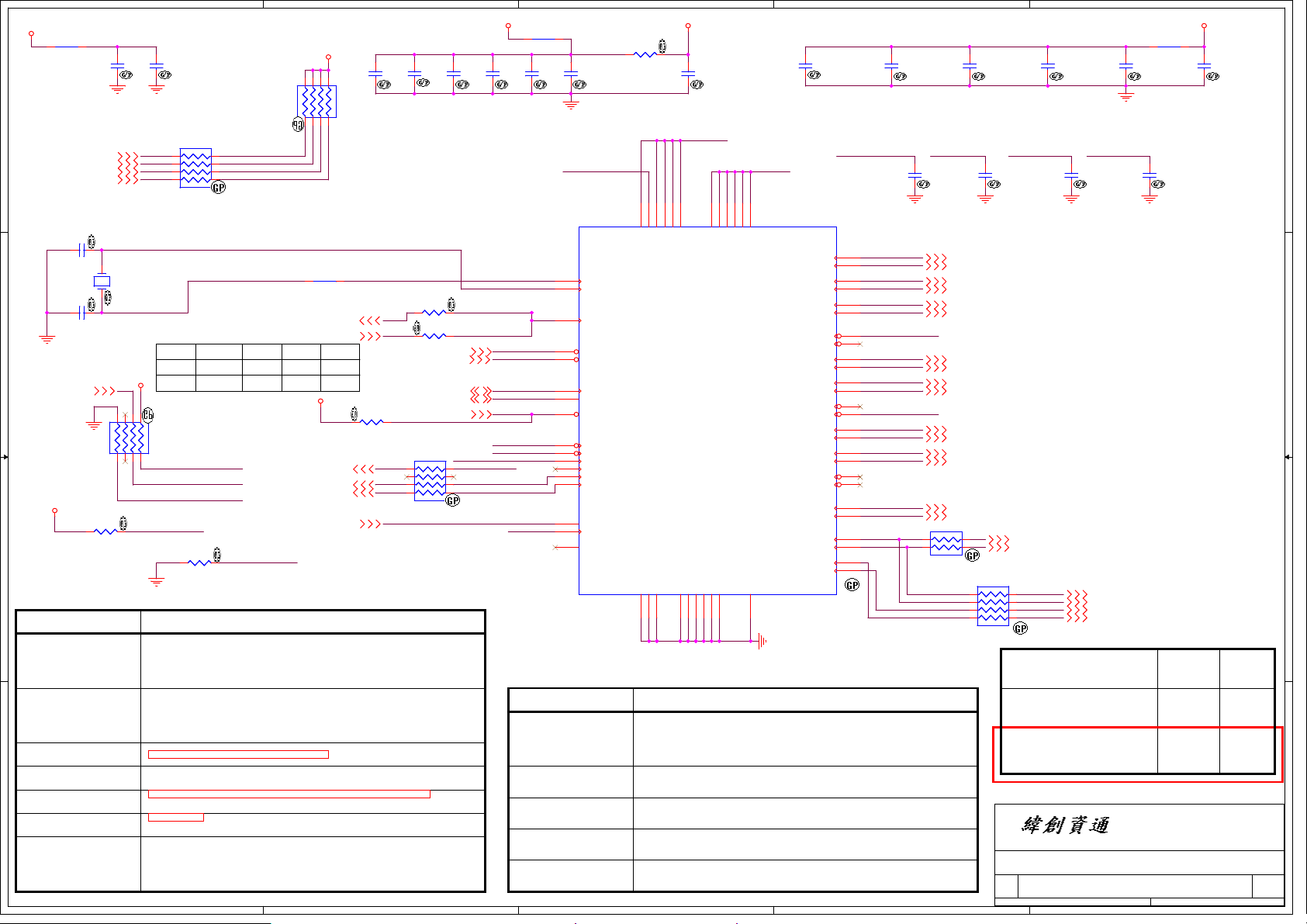

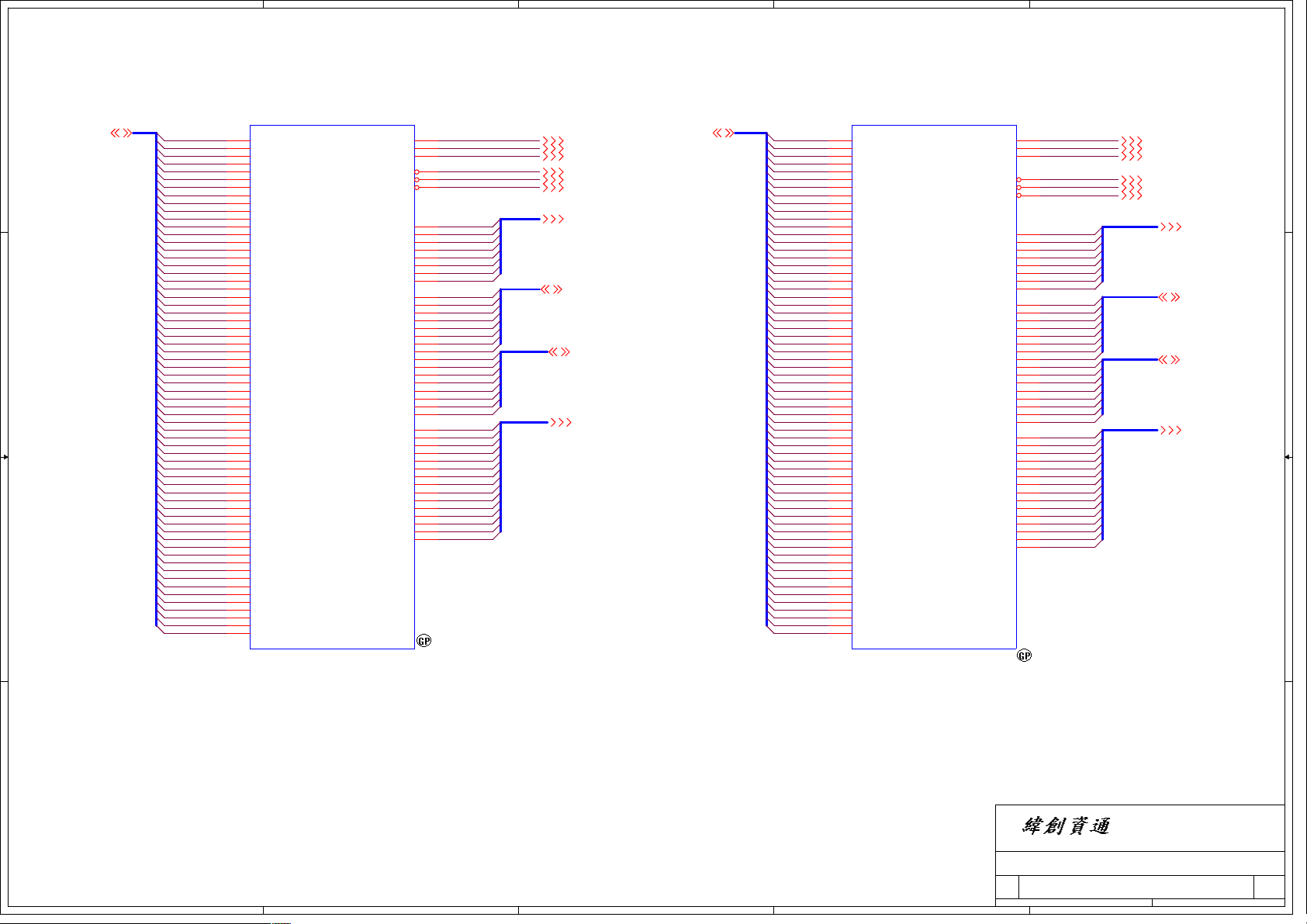

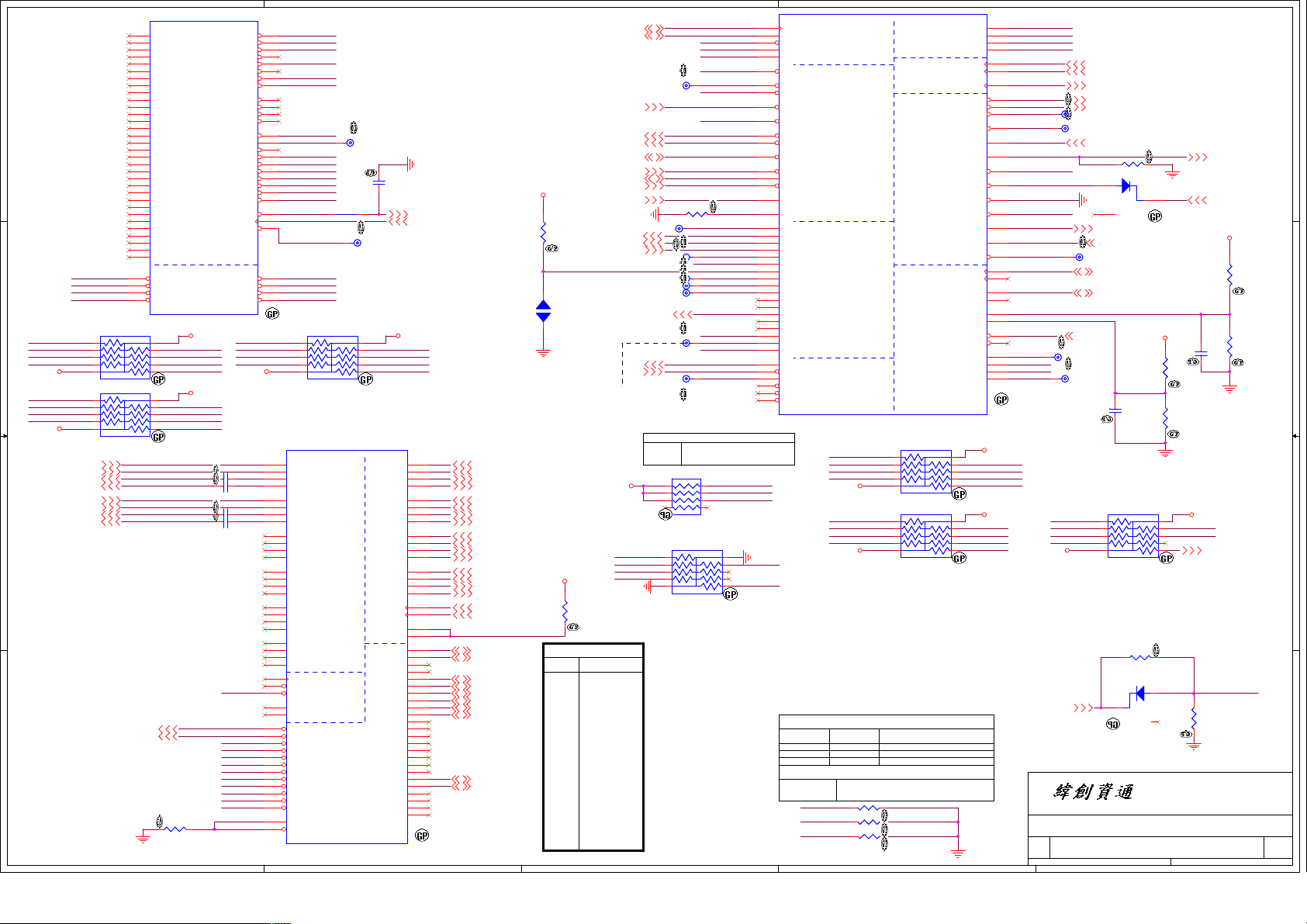

Page 3

A

www.vinafix.vn

3D3V_S0

R95

R95

1 2

0R0402-PAD

0R0402-PAD

DY

DY

4 4

PCIE_REQ_LAN#23

SATACLKREQ#13

PCIE_REQ_MINI#26

CLK_MCH_OE#7

CL=20pF

∮∮∮∮

0.2pF

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

C229

C229

1 2

78.27034.1FL

78.27034.1FL

12

78.27034.1FL

78.27034.1FL

GEN_XTAL_OUT_R

1 2

C230

C230

SC27P50V2JN-2-GP

3 3

2 2

SC27P50V2JN-2-GP

CPU_SEL24,7

3D3V_S0

R599

R599

1 2

DIS

DIS

10KR2J-L-GP

10KR2J-L-GP

12

12

C221

C221

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

GEN_XTAL_IN

X4

X4

X-14D31818M-35GP

X-14D31818M-35GP

82.30005.891

82.30005.891

3D3V_S0

678

RN28

RN28

SRN10KJ-6-GP

SRN10KJ-6-GP

123

4 5

PCLKCLK4

C227

C227

SC1U16V3ZY-GP

SC1U16V3ZY-GP

SRN10KJ-6-GP

SRN10KJ-6-GP

RN62

RN62

1

2

3

4 5

PCLKCLK4

0

1

PCIE_REQ_LAN#_R

8

PCLKCLK0

7

PCIE_REQ_MINI#_R

6

PCLKCLK1

SRN470J-3-GP

SRN470J-3-GP

24 25 20 21

27MHZ_NONSS 27MHZ_SS SRCT0 SRCC0

Pull high PCLKCLK4

For VGA Clock-0415

PCLKCLK2

CPU_SEL2_R

PCLKCLK5

R600

R600

1 2

UMA

UMA

10KR2J-L-GP

10KR2J-L-GP

PCLKCLK4

RN61

RN61

DOTT_96 DOTT_96SRCT1 SRCC1

3D3V_S0

123

45

678

R91

R91

1 2

0R0402-PAD

0R0402-PAD

CLK48_ICH13

CPU_SEL04,7

3D3V_S0

CLK_ICH1413

PCLK_KBC28

PCLK_ICH13

CPU_SEL14,7

ICS9LPRS365BKLFT setting table

PIN NAME DESCRIPTION

Byte 5, bit 7

0 = PCI0 enabled (default)

PCI0/CR#_A

PCI1/CR#_B

PCI2/TME

PCI3

1 1

PCI4/27M_SEL

PCI_F5/ITP_EN

SRCT3/CR#_C

1= CR#_A enabled. Byte 5, bit 6 controls whether CR#_A controls SRC0 or SRC2 pair

Byte 5, bit 6

0 = CR#_A controls SRC0 pair (default),

1= CR#_A controls SRC2 pair

Byte 5, bit 5

0 = PCI1 enabled (default)

1= CR#_B enabled. Byte 5, bit 6 controls whether CR#_B controls SRC1 or SRC4 pair

Byte 5, bit 4

0 = CR#_B controls SRC1 pair (default)

1= CR#_B controls SRC4 pair

0 = Overclocking of CPU and SRC Allowed

1 = Overclocking of CPU and SRC NOT allowed

3.3V PCI clock output

0 = Pin24 as SRC-1, Pin25 as SRC-1#, Pin20 as DOT96, Pin21 as DOT96#

1 = Pin24 as 27MHz, Pin25 as 27MHz_SS, Pin20 as SRC-0, Pin21 as SRC-0#

0 =SRC8/SRC8#

1 = ITP/ITP#

Byte 5, bit 3

0 = SRC3 enabled (default)

1= CR#_C enabled. Byte 5, bit 2 controls whether CR#_C controls SRC0 or SRC2 pair

Byte 5, bit 2

0 = CR#_C controls SRC0 pair (default),

1= CR#_C controls SRC2 pair

A

B

12

C165

C165

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

GEN_XTAL_OUT

1 2

R88 2K2R2J-2-GPR88 2K2R2J-2-GP

PM_STPCPU#13

12

DY

DY

R89 10KR2J-3-GP

R89 10KR2J-3-GP

1

2

3

4 5

SRN33J-7-GP

SRN33J-7-GP

B

3D3V_CLKPLL_S0

12

12

C149

C149

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

R597

R597

22R2J-2-GP

22R2J-2-GP

12

PM_STPPCI#13

SMBC_ICH15,16,17

SMBD_ICH15,16,17

CLK_PWRGD13

RN23

RN23

8

7

6

1D05V_S0

C176

C176

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

CPU_SEL2_R

PCLKCLK4

PCLKCLK5

C

3D3V_S0

R302

R302

1 2

0R0402-PAD

0R0402-PAD

12

12

C156

C156

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

PCLKCLK0

PCLKCLK1

PCLKCLK2

CPU_SEL2_R

2nd = 71.08513.003

2nd = 71.08513.003

3rd = 71.00875.C03

3rd = 71.00875.C03

12

C173

C173

C196

C196

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

3D3V_48MPWR_S0

U14

U14

3

X1

2

X2

CLK48

17

USB_48MHZ/FSLA

45

PCI_STOP#

44

CPU_STOP#

7

SCLK

6

SDATA

63

CK_PWRGD/PD#

8

PCI0/CR#_A

10

PCI1/CR#_B

11

PCI2/TME

12

PCI3

13

PCI4/27_SELECT

14

PCI_F5/ITP_EN

64

FSLB/TEST_MODE

5

REF0/FSLC/TEST_SEL

55

NC#55

ICS9 LPRS3 65BKL FT-GP -U

ICS9 LPRS3 65BKL FT-GP -U

71.09365.A03

71.09365.A03

DY

DY

R80

R80

1 2

0R2J-2-GP

0R2J-2-GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

3D3V_CLKGEN_S0

4

9

16

46

62

VDD48

VDDPCI

VDDREF

VDDSRC

VDDCPU

GNDREF

GNDPCI

GND48

1

15

18

PIN NAME DESCRIPTION

Byte 5, bit 1

0 = SRC3 enabled (default)

SRCC3/CR#_D

SRCC7/CR#_E

SRCT7/CR#_F

SRCC11/CR#_G

SRCT11/CR#_H

1= CR#_D enabled. Byte 5, bit 0 controls whether CR#_D controls SRC1 or SRC4 pair

Byte 5, bit 0

0 = CR#_D controls SRC1 pair (default)

1= CR#_D controls SRC4 pair

Byte 6, bit 7

0 = SRC7# enabled (default)

1= CR#_F controls SRC6

Byte 6, bit 6

0 = SRC7 enabled (default)

1= CR#_F controls SRC8

Byte 6, bit 5

0 = SRC11# enabled (default)

1= CR#_G controls SRC9

Byte 6, bit 4

0 = SRC11 enabled (default)

1= CR#_H controls SRC10

C

D

12

C204

12

C152

C152

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_CLKPLL_S0

19

23

27

33

43

52

56

VDDPLL3

VDD96_IO

VDDSRC_IO

VDDSRC_IO

VDDSRC_IO

VDDCPU_IO

VDDPLL3_IO

27MHZ_NONSS/SRCT1/SE1

27MHZ_SS/SRCC1/SE2

GND

GND

GNDSRC

GNDSRC

GNDSRC

GNDCPU

GND

22

26

30

36

49

59

65

C204

DY

DY

CPUT0

CPUC0

CPUT1_F

CPUC1_F

CPUT2_ITP/SRCT8

CPUC2_ITP/SRCC8

SRCT7/CR#_F

SRCC7/CR#_E

SRCT6

SRCC6

SRCT10

SRCC10

SRCT11/CR#_H

SRCC11/CR#_G

SRCT9

SRCC9

SRCT4

SRCC4

SRCT3/CR#_C

SRCC3/CR#_D

SRCT2/SATAT

SRCC2/SATAC

SRCT0/DOTT_96

SRCC0/DOTC_96

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

61

60

58

57

54

53

51

50

48

47

41

42

40

39

37

38

34

35

31

32

28

29

24

25

20

21

12

C179

C179

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SC5P50V2CN-2GP

SC5P50V2CN-2GP

12

PCIE_REQ_LAN#_R

PCIE_REQ_MINI#_R

1

2 3

DREFSSCLK#_R

DREFSSCLK_R

DREFCLK#_R

DREFCLK_R

SC5P50V2CN-2GP

SC5P50V2CN-2GP

EC31

EC31

DY

DY

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

CLK_PCIE_LAN 23

CLK_PCIE_LAN# 23

CLK_PCIE_ICH 13

CLK_PCIE_ICH# 13

CLK_PCIE_PEG 46

CLK_PCIE_PEG# 46

CLK_PCIE_MINI1 26

CLK_PCIE_MINI1# 26

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_PCIE_SATA 12

CLK_PCIE_SATA# 12

RN99

RN99

4

SRN0J-6-GP

SRN0J-6-GP

DIS

DIS

1

2

3

4 5

12

C226

C226

12

RN76

RN76

SRN0J-7-GP

SRN0J-7-GP

UMA

UMA

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

EC62

EC62

DY

DY

SEL2

FSC

12

SC5P50V2CN-2GP

SC5P50V2CN-2GP

(100 MHz)

VGA_XIN1 50

XTAL_SSIN1 50

8

7

6

1

0

3D3V_CLKGEN_S03D3V_48MPWR_S0

C224

C224

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

CLK48_ICHPCLK_ICHPCLK_KBCCLK_ICH14

12

EC66

EC66

DY

DY

CPU

NB

LAN

SB DMI

MINI1

NB CLK

SB SATA

DREFSSCLK# 7

DREFSSCLK 7

DREFCLK# 7

DREFCLK 7

SEL1

FSB

SEL0

FSA

01

01

0101

00 0

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Clock Generator

Clock Generator

Clock Generator

LB46E

LB46E

LB46E

E

3D3V_S0

R87

R87

1 2

0R0402-PAD

12

SC5P50V2CN-2GP

SC5P50V2CN-2GP

C155

C155

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

0R0402-PAD

12

EC33

EC33

DY

DY

12

C205

C205

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

(27 MHz)

CPU

FSB

100M

133M

166M

01

200M

533M

667M

800M

1066M266M

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

353Monday, December 27, 2010

353Monday, December 27, 2010

353Monday, December 27, 2010

E

X

SB

SB

SB

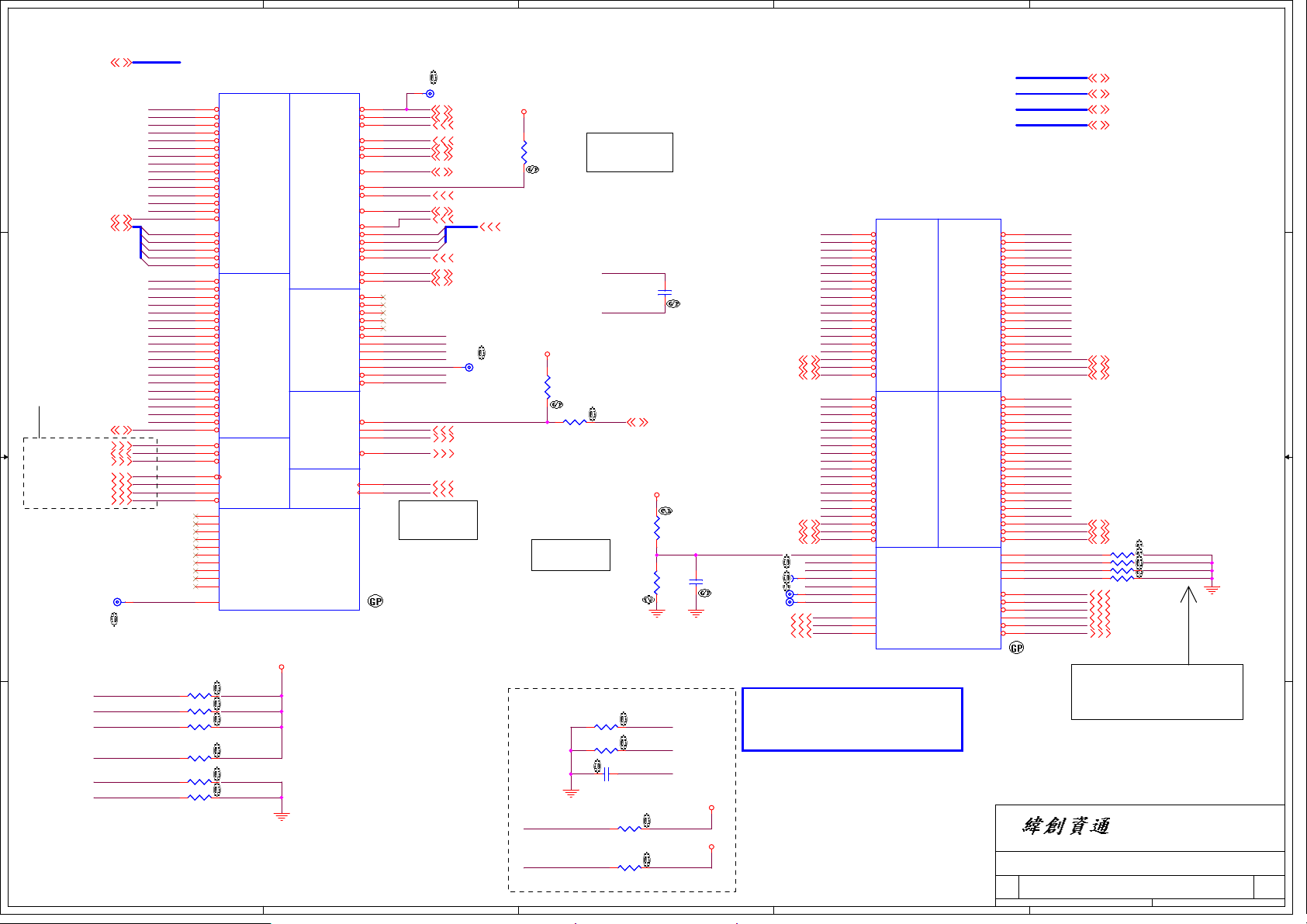

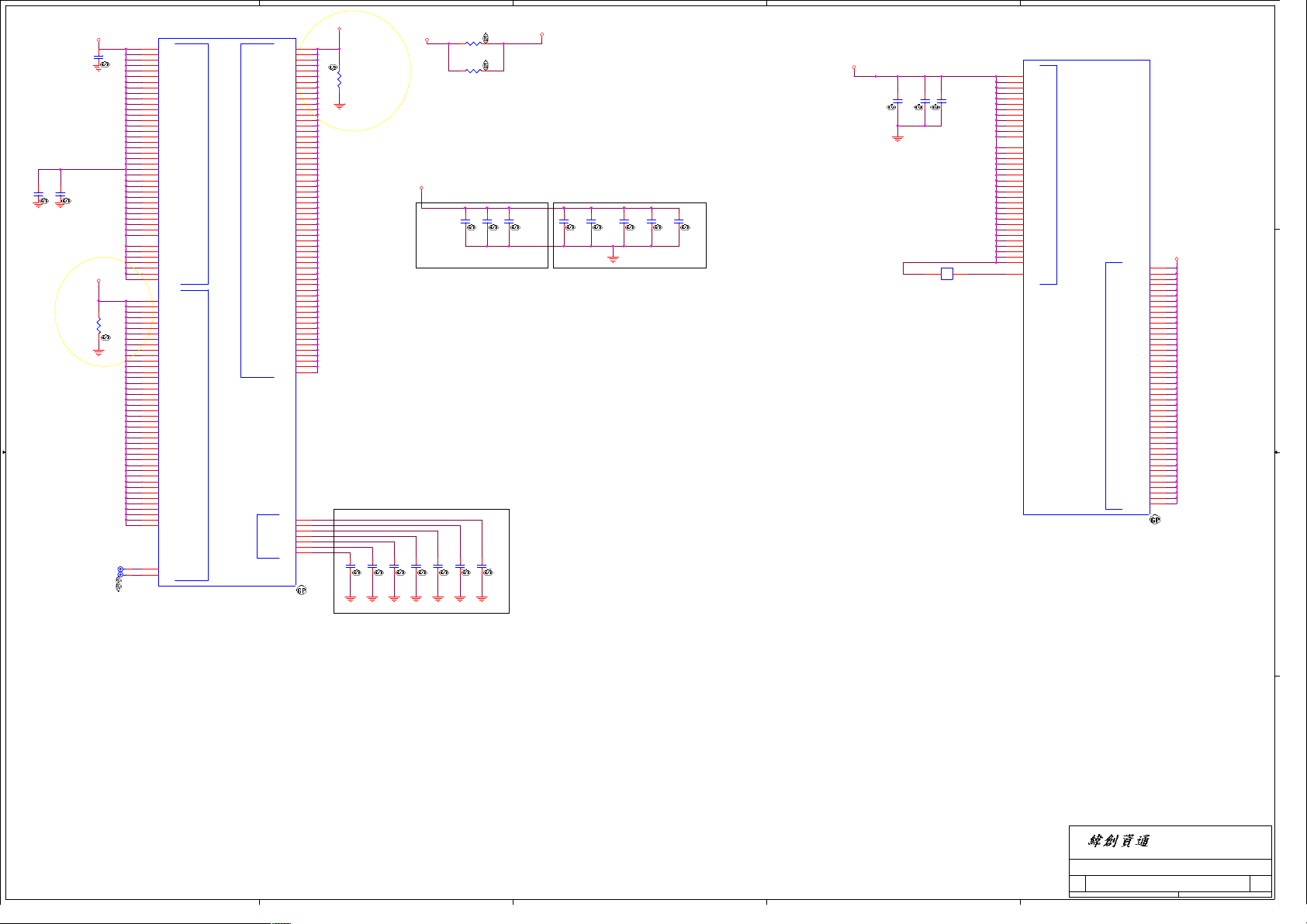

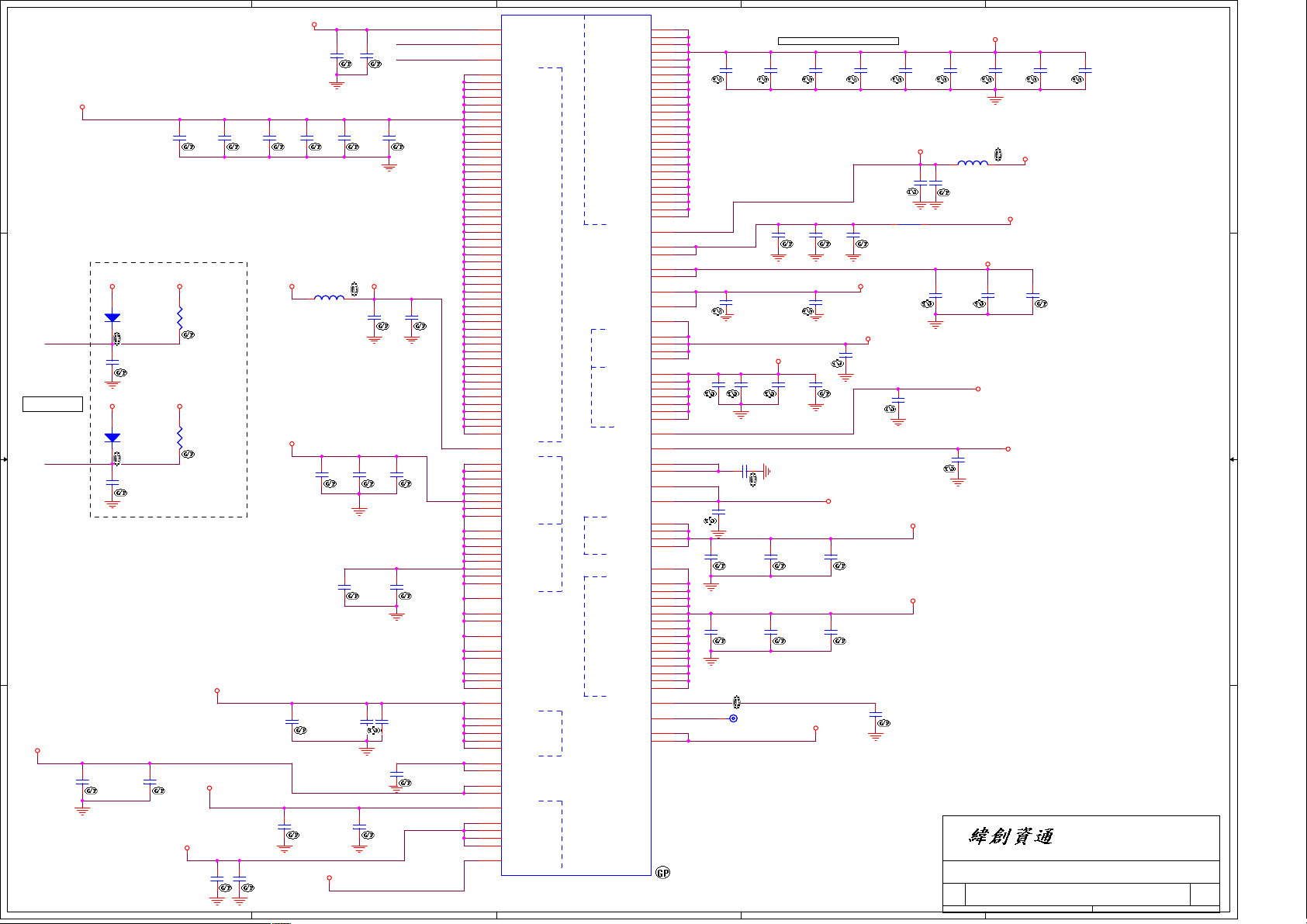

Page 4

A

www.vinafix.vn

B

C

D

E

H_A#[35..3]6

4 4

H_ADSTB#06

H_REQ#[4..0]6

3 3

Side Band

Non GTL

H_ADSTB#16

H_A20M#12

H_FERR#12

H_IGNNE#12

H_STPCLK#12

H_INTR12

H_NMI12

H_SMI#12

2 2

TP20TPAD14-GP TP20TPAD14-GP

XDP_TMS

XDP_TDI

XDP_BPM#5

H_CPURST#

XDP_TCK

1 1

XDP_TRST#

H_A#[35..3]

CPU1A

CPU1A

H_A#3

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

K3

H2

K2

J3

L1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

B1

2nd = 62.10053.581

2nd = 62.10053.581

1 2

1 2

1 2

DY

DY

R213

R213

1 2

51R2F-2-GP

51R2F-2-GP

1 2

1 2

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB0#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB1#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD#M4

RSVD#N5

RSVD#T2

RSVD#V3

RSVD#B2

RSVD#C3

RSVD#D2

RSVD#D22

RSVD#D3

RSVD#F6

KEY_NC

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

62.10079.001

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

1

R50 54D9R2F-L1-GPR50 54D9R2F-L1-GP

R48 54D9R2F-L1-GPR48 54D9R2F-L1-GP

R43 54D9R2F-L1-GPR43 54D9R2F-L1-GP

R41 54D9R2F-L1-GPR41 54D9R2F-L1-GP

R42 54D9R2F-L1-GPR42 54D9R2F-L1-GP

All place within 2" to CPU

A

1 OF 4

1 OF 4

ADDR GROUP 0

ADDR GROUP 0

ADDR GROUP 1

ADDR GROUP 1

ICH

ICH

RESERVED

RESERVED

3ND=62.10053.581,

62.10053.341,

62.10040.491,

62.10079.021,

62.10040.221

1D05V_S0

DEFER#

DRDY#

DBSY#

LOCK#

RESET#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALS CONTROL

XDP/ITP SIGNALS CONTROL

THERMAL

THERMAL

PROCHOT#

THRMDA

THRMDC

THERMTRIP#

HCLK

HCLK

BCLK0

BCLK1

ADS#

BNR#

BPRI#

BR0#

IERR#

INIT#

RS0#

RS1#

RS2#

HIT#

HITM#

TCK

TDO

TMS

DBR#

TDI

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

XDP_TDO

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

XDP_DBRESET#

C20

CPU_PROCHOT#

D21

A24

B25

C7

A22

A21

1

H_IERR#

PM_THRMTRIP#

should connect to

ICH9 and MCH

without T-ing

( No stub)

B

TP11 TPAD14-GPTP11 TPAD14-GP

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_INIT# 12

H_LOCK# 6

H_CPURST# 6,43

H_TRDY# 6

H_HIT# 6

H_HITM# 6

AFTP112

AFTP112

1

H_THERMDA 27

H_THERMDC 27

PM_THRMTRIP-A# 7,12,34

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

1D05V_S0

H_RS#[2..0] 6

AFTE14P-GP

AFTE14P-GP

12

R64

R64

56R2J-4-GP

56R2J-4-GP

1D05V_S0

12

Layout Note:

"CPU_GTLREF0"

0.5" max length.

R63

R63

68R2-GP

68R2-GP

DY

DY

1 2

R62

R62

0R2J-2-GP

0R2J-2-GP

Place testpoint on

H_IERR# with a GND

0.1" away

H_THERMDA

H_THERMDC

1KR2F-3-GP

1KR2F-3-GP

2KR2F-3-GP

2KR2F-3-GP

Follow Demo Circuit

1 2

DY

DY

R65 1KR2J-1-GP

R65 1KR2J-1-GP

1 2

DY

DY

R215 1KR2J-1-GP

R215 1KR2J-1-GP

12

C343 SCD1U10V2KX-4GP

C343 SCD1U10V2KX-4GP

DY

DY

R60

XDP_DBRESET#

XDP_TDO

R60

1 2

DY

DY

R47 54D9R2F-L1-GP

R47 54D9R2F-L1-GP

1 2

DY

DY

12

C438

C438

DY

DY

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

CPU_PROCHOT#_R 36

1D05V_S0

R179

R179

1 2

12

R181

R181

TEST1

TEST2

TEST4

1KR2J-1-GP

1KR2J-1-GP

C

12

DY

DY

3D3V_S0

1D05V_S0

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_DSTBN#06

H_DSTBP#06

H_DINV#06

H_DSTBN#16

H_DSTBP#16

H_DINV#16

CPU_GTLREF0

C352

C352

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

TP18TPAD14-GP TP18TPAD14-GP

TP44TPAD14-GP TP44TPAD14-GP

TP60TPAD14-GP TP60TPAD14-GP

CPU_SEL03,7

CPU_SEL13,7

CPU_SEL23,7

Net "TEST4" as short as possible,

make sure "TEST4" routing is

reference to GND and away other

noisy signals

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST1

TEST2

RSVD_CPU_12

1

TEST4

RSVD_CPU_13

1

RSVD_CPU_14RSVD_CPU_11

1

AD26

AF26

2 OF 4

2 OF 4

CPU1B

CPU1B

E22

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

62.10079.001

2nd = 62.10053.581

2nd = 62.10053.581

D

DATA GRP0 DATA GRP1

DATA GRP0 DATA GRP1

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

MISC

MISC

DPRSTP#

PWRGOOD

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

H_D#[63..0]

H_D#32

Y22

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPSLP#

DPWR#

SLP#

PSI#

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_DINV#[3..0] 6

H_DSTBN#[3..0] 6

H_DSTBP#[3..0] 6

H_D#[63..0] 6

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

R53 27D4R2F-L1-GPR53 27D4R2F-L1-GP

1 2

R51 54D9R2F-L1-GPR51 54D9R2F-L1-GP

1 2

R45 27D4R2F-L1-GPR45 27D4R2F-L1-GP

1 2

R44 54D9R2F-L1-GPR44 54D9R2F-L1-GP

1 2

H_DPRSTP# 7,12,36

H_DPSLP# 12

H_DPWR# 6

H_PWRGD 12,34

H_CPUSLP# 6

PSI# 36

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (1 of 2)

CPU (1 of 2)

CPU (1 of 2)

LB46E

LB46E

LB46E

453Monday, December 27, 2010

453Monday, December 27, 2010

453Monday, December 27, 2010

E

SB

SB

SB

Page 5

A

www.vinafix.vn

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

VCC_CORE

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

12

C84

C84

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

H_VID0 36

H_VID1 36

H_VID2 36

H_VID3 36

H_VID4 36

H_VID5 36

H_VID6 36

VCC_CORE

12

R39

R39

100R2F-L1-GP-U

100R2F-L1-GP-U

VCC_CORE

4 4

3 3

AA10

AA12

2 2

1 1

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

3 OF 4

3 OF 4

CPU1C

CPU1C

A7

VCC

A9

VCC

A10

VCC

A12

VCC

A13

VCC

A15

VCC

A17

VCC

A18

VCC

A20

VCC

B7

VCC

B9

VCC

B10

VCC

B12

VCC

B14

VCC

B15

VCC

B17

VCC

B18

VCC

B20

VCC

C9

VCC

C10

VCC

C12

VCC

C13

VCC

C15

VCC

C17

VCC

C18

VCC

D9

VCC

D10

VCC

D12

VCC

D14

VCC

D15

VCC

D17

VCC

D18

VCC

E7

VCC

E9

VCC

E10

VCC

E12

VCC

E13

VCC

E15

VCC

E17

VCC

E18

VCC

E20

VCC

F7

VCC

F9

VCC

F10

VCC

F12

VCC

F14

VCC

F15

VCC

F17

VCC

F18

VCC

F20

VCC

AA7

VCC

AA9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

62.10079.001

2nd = 62.10053.581

2nd = 62.10053.581

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCA

VCCA

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENSE

VSSSENSE

B

12

12

C92

C92

1D05V_S0

VCC_CORE

12

12

C70

C70

C90

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

C90

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

layout note: "1D5V_VCCA_S0"

as short as possible

1D5V_VCCA_S0

12

R38

R38

100R2F-L1-GP-U

100R2F-L1-GP-U

VSS_SENSE 36

Layout Note:

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

12

C429

C429

C61

C61

12

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C384

C382

C382

C384

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

1D5V_S0

C383

C383

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

L10

L10

1 2

PBY160808T-121Y-GP

PBY160808T-121Y-GP

68.00206.021

68.00206.021

2nd = 68.00230.041

2nd = 68.00230.041

VCC_SENSE 36

C

12

12

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

C48

C48

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

1D05V_S0

12

C62

C62

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C78

C78

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C69

C69

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C81

C81

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C83

C83

C82

C82

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C66

C66

C65

C65

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C381

C381

DY

DY

D

4 OF 4

CPU1D

CPU1D

A11

A14

A16

A19

A23

1

TP46TPAD14-GP TP46TPAD14-GP

AF2

B11

B13

B16

B19

B21

B24

C11

C14

C16

C19

C22

C25

D11

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G23

G26

H21

H24

K23

K26

L21

L24

M22

M25

N23

N26

G4

G1

J22

J25

M2

M5

4 OF 4

A4

VSS

A8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B6

VSS

B8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C5

VSS

C8

VSS

VSS

VSS

VSS

VSS

C2

VSS

VSS

VSS

D1

VSS

D4

VSS

D8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E3

VSS

E6

VSS

E8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F5

VSS

F8

VSS

VSS

VSS

VSS

VSS

F2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H3

VSS

H6

VSS

VSS

VSS

J2

VSS

J5

VSS

VSS

VSS

K1

VSS

K4

VSS

VSS

VSS

L3

VSS

L6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N1

VSS

N4

VSS

VSS

VSS

P3

VSS

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

62.10079.001

2nd = 62.10053.581

2nd = 62.10053.581

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

E

1

1

1

1

1

TP45TPAD14-GP TP45TPAD14-GP

TP48TPAD14-GP TP48TPAD14-GP

TP21TPAD14-GP TP21TPAD14-GP

TP61TPAD14-GP TP61TPAD14-GP

TP43TPAD14-GP TP43TPAD14-GP

A

B

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

C

D

Date: Sheet of

LB46E

LB46E

LB46E

Taipei Hsien 221, Taiwan, R.O.C.

CPU (2 of 2)

CPU (2 of 2)

CPU (2 of 2)

E

SB

SB

553Monday, December 27, 2010

553Monday, December 27, 2010

553Monday, December 27, 2010

SB

Page 6

5

www.vinafix.vn

H_SWING

1D05V_S0

12

R239

R239

221R2F-2-GP

221R2F-2-GP

12

R238

R238

100R2F-L1-GP-U

100R2F-L1-GP-U

H_RCOMP

D D

H_SWING routing Trace width and

Spacing use 10 / 20 mil

H_SWING Resistors and

Capacitors close MCH

500 mil ( MAX )

12

C478

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C C

H_RCOMP routing Trace width and

Spacing use 10 / 20 mil

C478

1 2

R226

R226

24D9R2F-L-GP

24D9R2F-L-GP

Place them near to the chip ( < 0.5")

B B

H_D#[63..0]4

1D05V_S0

1 2

12

4

R241

R241

1KR2F-3-GP

1KR2F-3-GP

H_AVREF

R240

R240

2KR2F-3-GP

2KR2F-3-GP

H_D#[63..0]

H_CPURST#4,43

H_CPUSLP#4

12

C479

C479

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

NB1A

NB1A

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

3

1 OF 10

1 OF 10

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

HOST

HOST

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

2

H_A#[35..3]

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 3

CLK_MCH_BCLK# 3

H_DPWR# 4

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

H_REQ#[4..0]

H_RS#[2..0]

1

H_A#[35..3] 4

H_DINV#[3..0] 4

H_DSTBN#[3..0] 4

H_DSTBP#[3..0] 4

H_REQ#[4..0] 4

H_RS#[2..0] 4

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Cantiga (1 of 6)_HOST

Cantiga (1 of 6)_HOST

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cantiga (1 of 6)_HOST

LB46E

LB46E

LB46E

Taipei Hsien 221, Taiwan, R.O.C.

653Monday, December 27, 2010

653Monday, December 27, 2010

653Monday, December 27, 2010

1

SB

SB

SB

Page 7

5

www.vinafix.vn

1D5V_S3

12

R251

R251

1KR2F-3-GP

1KR2F-3-GP

D D

12

12

R250

R250

3K01R2F-3-GP

3K01R2F-3-GP

R248

R248

1KR2F-3-GP

1KR2F-3-GP

12

C487

C487

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

12

C484

C484

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

SM_RCOMP_VOH

12

C489

C489

SC2D2U6D3V3MX-1-GP

SC2D2U6D3V3MX-1-GP

SM_RCOMP_VOL

12

C483

C483

SC2D2U6D3V3MX-1-GP

SC2D2U6D3V3MX-1-GP

layout take note

1D5V_S3

12

R247

R247

80D6R2F-L-GP

80D6R2F-L-GP

M_RCOMPP

M_RCOMPN

12

R246

R246

80D6R2F-L-GP

C C

B B

80D6R2F-L-GP

3D3V_S0

PM_SYNC#13

H_DPRSTP#4,12,36

PWROK13,34

PLT_RST1#13,23,26,28,46

PM_THRMTRIP-A#4,12,34

PM_DPRSLPVR13,36

R110 0R0402-PADR110 0R0402-PAD

1 2

R211 100R2J-2-GPR211 100R2J-2-GP

CPU_SEL03,4

CPU_SEL13,4

CPU_SEL23,4

R306 4K02R2F-GP

R306 4K02R2F-GP

1 2

R98 4K02R2F-GP

R98 4K02R2F-GP

1 2

PM_EXTTS#016

PM_EXTTS#117

12

C147

C147

SC100P50V2JN-3GP

SC100P50V2JN-3GP

DY

DY

DY

DY

12

DY

DY

PM_SYNC#

H_DPRSTP#

PWROK_GD

RSTIN#

PM_THRMTRIP-A#

PM_DPRSLPVR

Pin Name Strap Description Configuration

A A

CFG20

Digital DisplayPort

(SDVO/DP/HDMI)

Concurrent with

PCIE

5

Low = Only digital DisplayPort

(SDVO/DP/HDMI) or

PCIE is operational (default)

High = Digital DisplayPort

(SDVO/DP/HDMI) and

PCIE are operating simultaneously via the PEG port

CFG16

CFG20

NB1B

NB1B

M36

RESERVED#M36

N36

RESERVED#N36

R33

RESERVED#R33

T33

RESERVED#T33

AH9

RESERVED#AH9

AH10

RESERVED#AH10

AH12

RESERVED#AH12

AH13

RESERVED#AH13

K12

RESERVED#K12

AL34

RESERVED#AL34

AK34

RESERVED#AK34

AN35

RESERVED#AN35

AM35

RESERVED#AM35

T24

RESERVED#T24

B31

RESERVED#B31

B2

RESERVED#B2

M1

RESERVED#M1

AY21

RESERVED#AY21

BG23

RESERVED#BG23

BF23

RESERVED#BF23

BH18

RESERVED#BH18

BF18

RESERVED#BF18

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

CFG_17

P29

CFG_18

R28

CFG_19

T28

CFG_20

R29

PM_SYNC#

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

AT40

PWROK

AT11

RSTIN#

T20

THERMTRIP#

R32

DPRSLPVR

BG48

NC#BG48

BF48

NC#BF48

BD48

NC#BD48

BC48

NC#BC48

BH47

NC#BH47

BG47

NC#BG47

BE47

NC#BE47

BH46

NC#BH46

BF46

NC#BF46

BG45

NC#BG45

BH44

NC#BH44

BH43

NC#BH43

BH6

NC#BH6

BH5

NC#BH5

BG4

NC#BG4

BH3

NC#BH3

BF3

NC#BF3

BH2

NC#BH2

BG2

NC#BG2

BE2

NC#BE2

BG1

NC#BG1

BF1

NC#BF1

BD1

NC#BD1

BC1

NC#BC1

F1

NC#F1

A47

NC#A47

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

4

CLK_MCH_OE#

PM_EXTTS#0

PM_EXTTS#1

4

2 OF 10

2 OF 10

AP24

SA_CK_0

AT21

SA_CK_1

AV24

SB_CK_0

AU20

SB_CK_1

AR24

SA_CK#_0

AR21

SA_CK#_1

AU24

SB_CK#_0

AV20

SB_CK#_1

BC28

SA_CKE_0

AY28

SA_CKE_1

AY36

SB_CKE_0

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_VREF

SM_PWROK

SM_REXT

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

CL_PWROK

ICH_SYNC#

HDA_BCLK

HDA_RST#

HDA_SDO

HDA_SYNC

3D3V_S0

45

3

2

1

PEG_CLK

CL_CLK

CL_DATA

CL_RST#

CL_VREF

CLKREQ#

TSATN#

HDA_SDI

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

M_RCOMPP

M_RCOMPN

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_PWROK

SM_REXT

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CLPWROK_MCH

MCH_CLVREF

1

MCH_TSATN#

S3_PWRGD38

PM_SLP_S4#13,28,38

CLK_MCH_3GPLL 3

R111

R111

0R0402-PAD

0R0402-PAD

MCH_ICH_SYNC# 13

R242

R242

56R2J-4-GP

56R2J-4-GP

DREFSSCLK

DREFSSCLK#

DREFCLK#

DREFCLK

RSVD

RSVD

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_DRAMRST#

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLK

CLK

CFG

CFG

DMI

DMI

PM

PM

GRAPHICS VID

GRAPHICS VID

MEHDA

MEHDA

DDPC_CTRLCLK

DDPC_CTRLDATA

NC

NC

SDVO_CTRLCLK

SDVO_CTRLDATA

MISC

MISC

RN32

RN32

6

7

8

SRN10KJ-6-GP

SRN10KJ-6-GP

M_CLK_DDR0 16

M_CLK_DDR1 16

M_CLK_DDR2 17

M_CLK_DDR3 17

M_CLK_DDR#0 16

M_CLK_DDR#1 16

M_CLK_DDR#2 17

M_CLK_DDR#3 17

M_CKE0 16

M_CKE1 16

M_CKE2 17

M_CKE3 17

M_CS#0 16

M_CS#1 16

M_CS#2 17

M_CS#3 17

M_ODT0 16

M_ODT1 16

M_ODT2 17

M_ODT3 17

R243

R243

1 2

DREFCLK 3

DREFCLK# 3

DREFSSCLK 3

DREFSSCLK# 3

CLK_MCH_3GPLL# 3

DMI_TXN0 13

DMI_TXN1 13

DMI_TXN2 13

DMI_TXN3 13

DMI_TXP0 13

DMI_TXP1 13

DMI_TXP2 13

DMI_TXP3 13

DMI_RXN0 13

DMI_RXN1 13

DMI_RXN2 13

DMI_RXN3 13

DMI_RXP0 13

DMI_RXP1 13

DMI_RXP2 13

DMI_RXP3 13

12

PWROK 13,34

CL_RST#0 13

TP34TPAD14-GP TP34TPAD14-GP

CLK_MCH_OE# 3

12

1D05V_S0

RN75

RN75

1

2

3

4 5

SRN0J-7-GP

SRN0J-7-GP

DIS

DIS

3

DDR3_DRAMRST# 16,17

DDR_VREF_S3

499R2F-2-GP

499R2F-2-GP

CL_CLK0 13

CL_DATA0 13

C231

C231

8

7

6

3

RN98

RN98

1

2 3

SRN0J-6-GP

SRN0J-6-GP

UMA

UMA

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C250

C250

DIS=66.R0036.A8L

For Dis change RN to 0 ohm

GMCH_DDCCLK19

GMCH_DDCDATA19

GMCH_HSYNC19

GMCH_VSYNC19

1D05V_S0

R93

R93

1KR2F-3-GP

1KR2F-3-GP

1 2

12

12

R92

R92

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

511R2F-2-GP

511R2F-2-GP

FOR Cantiga:500 ohm

Teenah: 392 ohm

U18

U18

1

B

VCC

2

A

3

GND

74LVC1G08GW-1- GP

74LVC1G08GW-1- GP

73.01G08.L04

73.01G08.L04

2nd = 73.7SZ08.AAH

2nd = 73.7SZ08.AAH

3rd = 73.01G08.L03

3rd = 73.01G08.L03

5

4

Y

L_BKLTCTL18

GMCH_BL_ON28

CLK_DDC_EDID18

DAT_DDC_EDID18

GMCH_LCDVDD_ON18

TP76 TPAD14-GPTP76 TPAD14-GP

4

GMCH_TXACLK-18

GMCH_TXACLK+18

GMCH_TXAOUT0-18

GMCH_TXAOUT1-18

GMCH_TXAOUT2-18

GMCH_TXAOUT0+18

GMCH_TXAOUT1+18

GMCH_TXAOUT2+18

UMA/DIS

RN15

RN15

8

7

6

SRN75J-1-GP

SRN75J-1-GP

GMCH_BLUE_119

GMCH_GREEN_119

GMCH_RED_119

UMA

UMA

RN73

RN73

1

2

3

4 5

SRN0J-7-GP

SRN0J-7-GP

3D3V_S5

SM_PWROK

L_BKLTCTL

GMCH_BL_ON

LCTLA_CLK

LCTLB_DATA

CLK_DDC_EDID

DAT_DDC_EDID

GMCH_LCDVDD_ON

LIBG

L_LVBG

1

LVDS_VREFH

LVDS_VREFL

1

2

3

45

GMCH_BLUE_1

GMCH_GREEN_1

GMCH_RED_1

GMCH_DDCCLK

SRN33J-5-GP-U

SRN33J-5-GP-U

DIS

DIS

GMCH_DDCDATA

GMCH_HS

1

4

2 3

GMCH_VS

RN21

RN21

CRT_IREF

1 2

R299 1K02R2F-1-GP

R299 1K02R2F-1-GP

UMA

UMA

FOR Cantiga: 1.02k_1% ohm

Teenah: 1.3k ohm

CRT_IREF routing Trace

width use 20 mil

LCTLA_CLK

8

DAT_DDC_EDID

7

CLK_DDC_EDID

6

LCTLB_DATA

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

C379

C379

1 2

DY

DY

TVA_DAC

TVB_DAC

TVC_DAC

NB1C

NB1C

L32

L_BKLT_CTRL

G32

L_BKLT_EN

M32

L_CTRL_CLK

M33

L_CTRL_DATA

K33

L_DDC_CLK

J33

L_DDC_DATA

M29

L_VDD_EN

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

C41

LVDSA_CLK#

C40

LVDSA_CLK

B37

LVDSB_CLK#

A37

LVDSB_CLK

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

G29

CRT_IRTN

H32

CRT_DDC_CLK

J32

CRT_DDC_DATA

J29

CRT_HSYNC

E29

CRT_TVO_IREF

L29

CRT_VSYNC

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

LCTLB_DATA

LCTLA_CLK

2

GMCH_BLUE_1

GMCH_GREEN_1

GMCH_RED_1

DIS=66.R0036.A8L

For Dis change RN to 0 ohm

1

2 3

GMCH_BL_ON

GMCH_LCDVDD_ON

LIBG

2

3 OF 10

3 OF 10

PEG_CMP

T37

PEG_COMPI

T36

PEG_COMPO

Close to GMCH as 500 mils.

H44

PEG_RX#_0

J46

PEG_RX#_1

L44

PEG_RX#_2

L40

PEG_RX#_3

N41

PEG_RX#_4

P48

PEG_RX#_5

N44

PEG_RX#_6

T43

PEG_RX#_7

U43

PEG_RX#_8

Y43

PEG_RX#_9

Y48

PEG_RX#_10

Y36

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

AA43

AD37

AC47

AD39

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

J41

M46

M47

M40

M42

R48

N38

T40

U37

U40

Y40

AA46

AA37

AA40

AD43

AC46

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

GMCH_TXN0

GMCH_TXN1

GMCH_TXN2

GMCH_TXN3

GMCH_TXN4

GMCH_TXN5

GMCH_TXN6

GMCH_TXN7

GMCH_TXN8

GMCH_TXN9

GMCH_TXN10

GMCH_TXN11

GMCH_TXN12

GMCH_TXN13

GMCH_TXN14

GMCH_TXN15

GMCH_TXP0

GMCH_TXP1

GMCH_TXP2

GMCH_TXP3

GMCH_TXP4

GMCH_TXP5

GMCH_TXP6

GMCH_TXP7

GMCH_TXP8

GMCH_TXP9

GMCH_TXP10

GMCH_TXP11

GMCH_TXP12

GMCH_TXP13

GMCH_TXP14

GMCH_TXP15

LVDS

LVDS

TV VGA

TV VGA

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

UMA/DIS

RN16

RN16

1

8

2

7

3

6

4 5

SRN150F-1-GP

SRN150F-1-GP

3D3V_S0

UMA

UMA

RN81

RN81

4

SRN10KJ-5-GP

SRN10KJ-5-GP

RN22

RN22

1

4

2 3

SRN100KJ-6-GP

SRN100KJ-6-GP

UMA

UMA

R103

R103

1 2

2K37R2F-GP

2K37R2F-GP

UMA

UMA

1

1D05V_S0

R99

R99

12

49D9R2F-GP

49D9R2F-GP

PEG_RXN0 46

PEG_RXN1 46

PEG_RXN2 46

PEG_RXN3 46

PEG_RXN4 46

PEG_RXN5 46

PEG_RXN6 46

PEG_RXN7 46

PEG_RXN8 46

PEG_RXN9 46

PEG_RXN10 46

PEG_RXN11 46

PEG_RXN12 46

PEG_RXN13 46

PEG_RXN14 46

PEG_RXN15 46

PEG_RXP0 46

PEG_RXP1 46

PEG_RXP2 46

PEG_RXP3 46

PEG_RXP4 46

PEG_RXP5 46

PEG_RXP6 46

PEG_RXP7 46

PEG_RXP8 46

PEG_RXP9 46

PEG_RXP10 46

PEG_RXP11 46

PEG_RXP12 46

PEG_RXP13 46

PEG_RXP14 46

PEG_RXP15 46

C658 SCD1U10V2KX-5GP

C658 SCD1U10V2KX-5GP

1 2

DIS

DIS

C620 SCD1U10V2KX-5GP

C620 SCD1U10V2KX-5GP

1 2

DIS

DIS

C669 SCD1U10V2KX-5GP

C669 SCD1U10V2KX-5GP

1 2

DIS

DIS

C654 SCD1U10V2KX-5GP

C654 SCD1U10V2KX-5GP

1 2

DIS

DIS

C610 SCD1U10V2KX-5GP

C610 SCD1U10V2KX-5GP

1 2

DIS

DIS

C667 SCD1U10V2KX-5GP

C667 SCD1U10V2KX-5GP

1 2

DIS

DIS

C649 SCD1U10V2KX-5GP

C649 SCD1U10V2KX-5GP

1 2

DIS

DIS

C603 SCD1U10V2KX-5GP

C603 SCD1U10V2KX-5GP

1 2

DIS

DIS

C665 SCD1U10V2KX-5GP

C665 SCD1U10V2KX-5GP

1 2

DIS

DIS

C646 SCD1U10V2KX-5GP

C646 SCD1U10V2KX-5GP

1 2

DIS

DIS

C601 SCD1U10V2KX-5GP

C601 SCD1U10V2KX-5GP

1 2

DIS

DIS

C663 SCD1U10V2KX-5GP

C663 SCD1U10V2KX-5GP

1 2

DIS

DIS

C638 SCD1U10V2KX-5GP

C638 SCD1U10V2KX-5GP

1 2

DIS

DIS

C599 SCD1U10V2KX-5GP

C599 SCD1U10V2KX-5GP

1 2

DIS

DIS

C661 SCD1U10V2KX-5GP

C661 SCD1U10V2KX-5GP

1 2

DIS

DIS

C628 SCD1U10V2KX-5GP

C628 SCD1U10V2KX-5GP

1 2

DIS

DIS

C604 SCD1U10V2KX-5GP

C604 SCD1U10V2KX-5GP

1 2

DIS

DIS

C657 SCD1U10V2KX-5GP

C657 SCD1U10V2KX-5GP

1 2

DIS

DIS

C622 SCD1U10V2KX-5GP

C622 SCD1U10V2KX-5GP

1 2

DIS

DIS

C668 SCD1U10V2KX-5GP

C668 SCD1U10V2KX-5GP

1 2

DIS

DIS

C653 SCD1U10V2KX-5GP

C653 SCD1U10V2KX-5GP

1 2

DIS

DIS

C609 SCD1U10V2KX-5GP

C609 SCD1U10V2KX-5GP

1 2

DIS

DIS

C666 SCD1U10V2KX-5GP

C666 SCD1U10V2KX-5GP

1 2

DIS

DIS

C651 SCD1U10V2KX-5GP

C651 SCD1U10V2KX-5GP

1 2

DIS

DIS

C602 SCD1U10V2KX-5GP

C602 SCD1U10V2KX-5GP

1 2

DIS

DIS

C664 SCD1U10V2KX-5GP

C664 SCD1U10V2KX-5GP

1 2

DIS

DIS

C641 SCD1U10V2KX-5GP

C641 SCD1U10V2KX-5GP

1 2

DIS

DIS

C600 SCD1U10V2KX-5GP

C600 SCD1U10V2KX-5GP

1 2

DIS

DIS

C662 SCD1U10V2KX-5GP

C662 SCD1U10V2KX-5GP

1 2

DIS

DIS

C633 SCD1U10V2KX-5GP

C633 SCD1U10V2KX-5GP

1 2

DIS

DIS

C598 SCD1U10V2KX-5GP

C598 SCD1U10V2KX-5GP

1 2

DIS

DIS

C659 SCD1U10V2KX-5GP

C659 SCD1U10V2KX-5GP

1 2

DIS

DIS

RN74

RN74

GMCH_VS

1

8

GMCH_HS

2

7

GMCH_DDCDATA

3

6

GMCH_DDCCLK

4 5

SRN0J-7-GP

SRN0J-7-GP

DIS

DIS

R536

R536

1 2

0R2J-L-GP

0R2J-L-GP

DIS

DIS

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CRT_IREF

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cantiga (2 of 6)_DMI/PM/CFG

Cantiga (2 of 6)_DMI/PM/CFG

Cantiga (2 of 6)_DMI/PM/CFG

LB46E

LB46E

LB46E

1

753Monday, December 27, 2010

753Monday, December 27, 2010

753Monday, December 27, 2010

PEG_TXN0 46

PEG_TXN1 46

PEG_TXN2 46

PEG_TXN3 46

PEG_TXN4 46

PEG_TXN5 46

PEG_TXN6 46

PEG_TXN7 46

PEG_TXN8 46

PEG_TXN9 46

PEG_TXN10 46

PEG_TXN11 46

PEG_TXN12 46

PEG_TXN13 46

PEG_TXN14 46

PEG_TXN15 46

PEG_TXP0 46

PEG_TXP1 46

PEG_TXP2 46

PEG_TXP3 46

PEG_TXP4 46

PEG_TXP5 46

PEG_TXP6 46

PEG_TXP7 46

PEG_TXP8 46

PEG_TXP9 46

PEG_TXP10 46

PEG_TXP11 46

PEG_TXP12 46

PEG_TXP13 46

PEG_TXP14 46

PEG_TXP15 46

SB

SB

SB

Page 8

5

www.vinafix.vn

NB1D

D D

C C

B B

M_A_DQ[63..0]16

M_A_DQ[63..0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

NB1D

AJ38

SA_DQ_0

AJ41

SA_DQ_1

AN38

SA_DQ_2

AM38

SA_DQ_3

AJ36

SA_DQ_4

AJ40

SA_DQ_5

AM44

SA_DQ_6

AM42

SA_DQ_7

AN43

SA_DQ_8

AN44

SA_DQ_9

AU40

SA_DQ_10

AT38

SA_DQ_11

AN41

SA_DQ_12

AN39

SA_DQ_13

AU44

SA_DQ_14

AU42

SA_DQ_15

AV39

SA_DQ_16

AY44

SA_DQ_17

BA40

SA_DQ_18

BD43

SA_DQ_19

AV41

SA_DQ_20

AY43

SA_DQ_21

BB41

SA_DQ_22

BC40

SA_DQ_23

AY37

SA_DQ_24

BD38

SA_DQ_25

AV37

SA_DQ_26

AT36

SA_DQ_27

AY38

SA_DQ_28

BB38

SA_DQ_29

AV36

SA_DQ_30

AW36

SA_DQ_31

BD13

SA_DQ_32

AU11

SA_DQ_33

BC11

SA_DQ_34

BA12

SA_DQ_35

AU13

SA_DQ_36

AV13

SA_DQ_37

BD12

SA_DQ_38

BC12

SA_DQ_39

BB9

SA_DQ_40

BA9

SA_DQ_41

AU10

SA_DQ_42

AV9

SA_DQ_43

BA11

SA_DQ_44

BD9

SA_DQ_45

AY8

SA_DQ_46

BA6

SA_DQ_47

AV5

SA_DQ_48

AV7

SA_DQ_49

AT9

SA_DQ_50

AN8

SA_DQ_51

AU5

SA_DQ_52

AU6

SA_DQ_53

AT5

SA_DQ_54

AN10

SA_DQ_55

AM11

SA_DQ_56

AM5

SA_DQ_57

AJ9

SA_DQ_58

AJ8

SA_DQ_59

AN12

SA_DQ_60

AM13

SA_DQ_61

AJ11

SA_DQ_62

AJ12

SA_DQ_63

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

4

4 OF 10

4 OF 10

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS#

SA_CAS#

SA_WE#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

BD21

BG18

AT25

BB20

BD20

AY20

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_DM[7..0]

M_A_DQS[7..0]

M_A_DQS#[7..0]

M_A_A[14..0]

M_A_BS0 16

M_A_BS1 16

M_A_BS2 16

M_A_RAS# 16

M_A_CAS# 16

M_A_WE# 16

M_A_DM[7..0] 16

M_A_DQS[7..0] 16

M_A_DQS#[7..0] 16

M_A_A[14..0] 16

3

NB1E

M_B_DQ[63..0]17

M_B_DQ[63..0]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40