Page 1

www.RahasiaLaptop.com

A

B

C

D

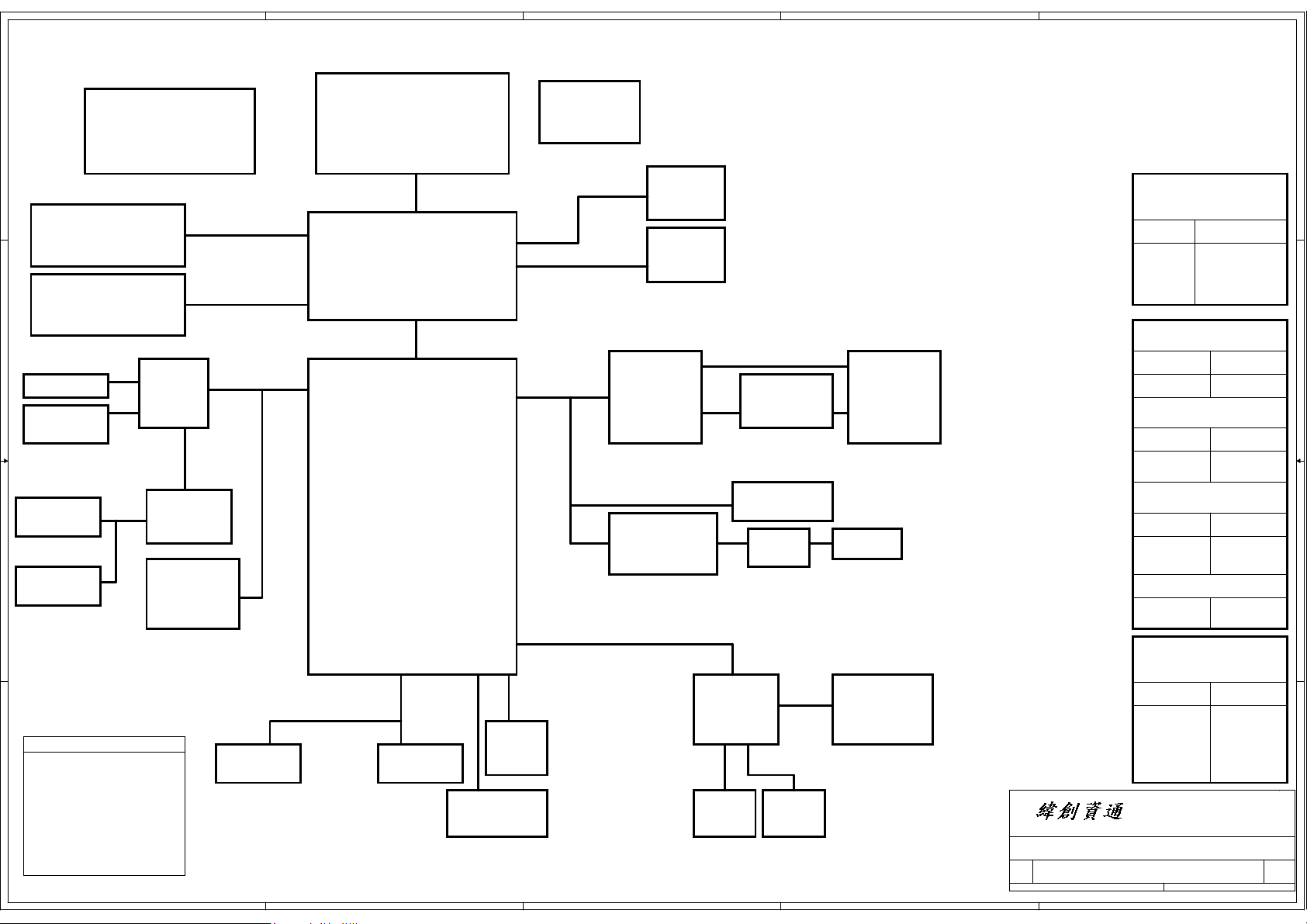

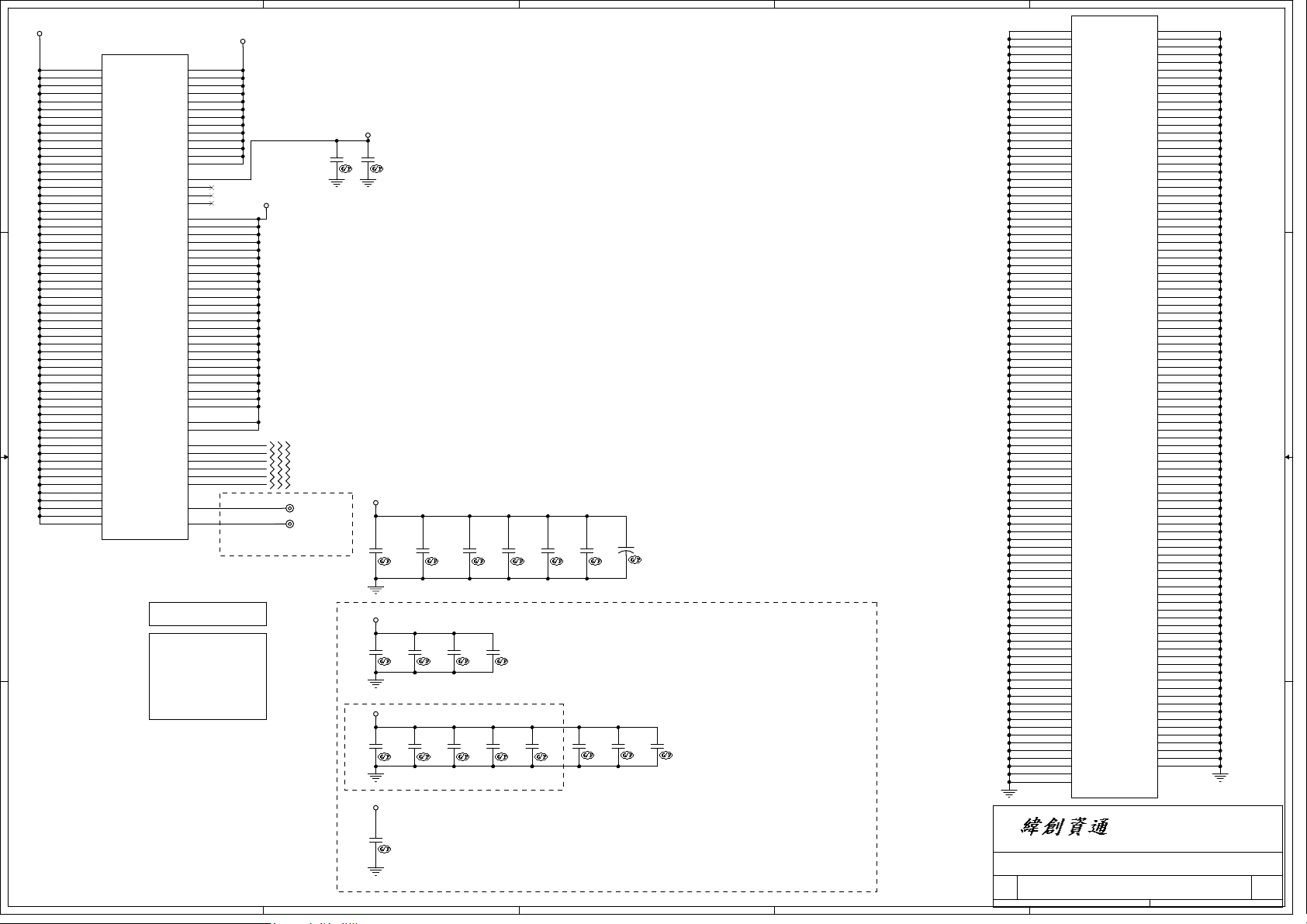

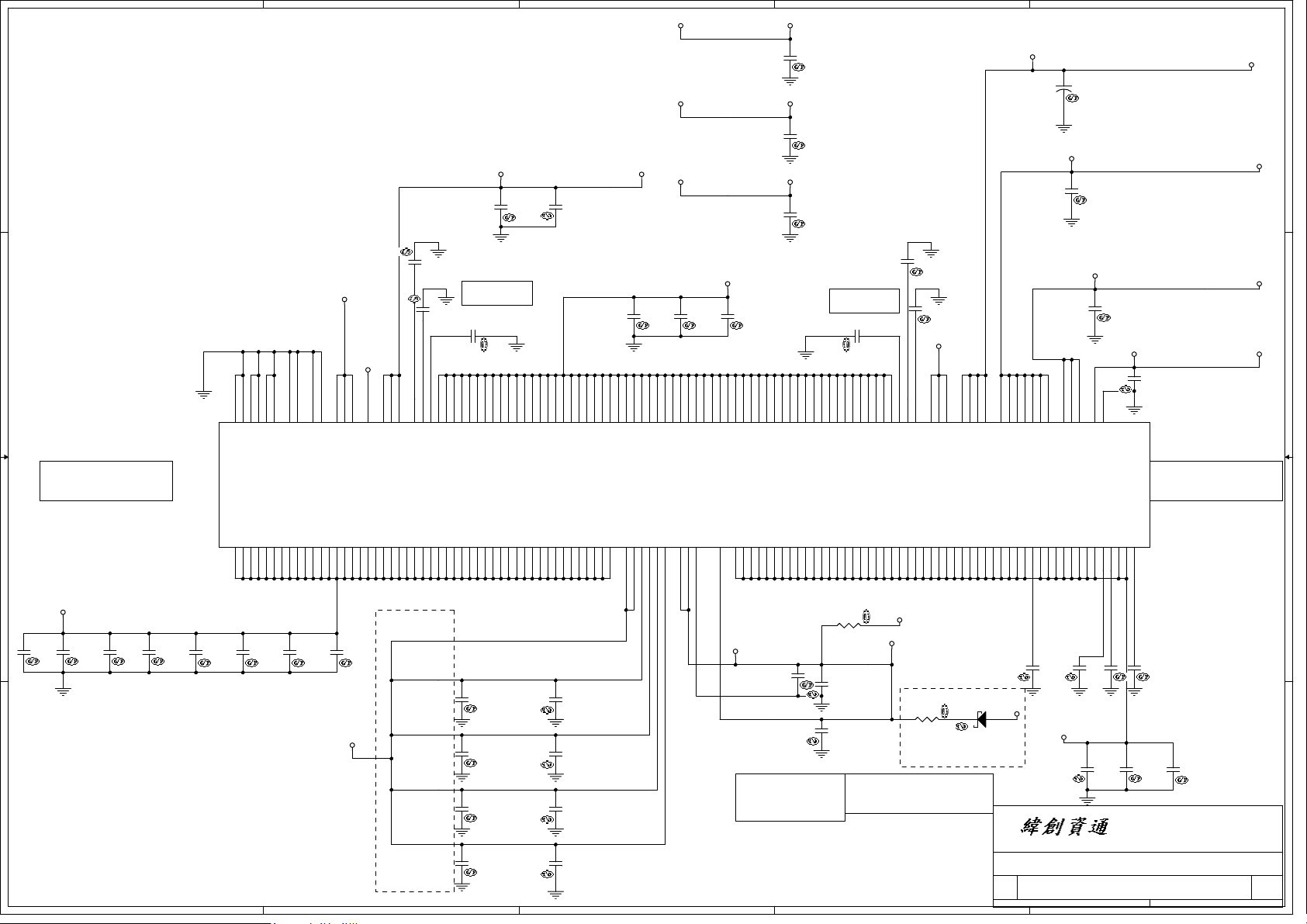

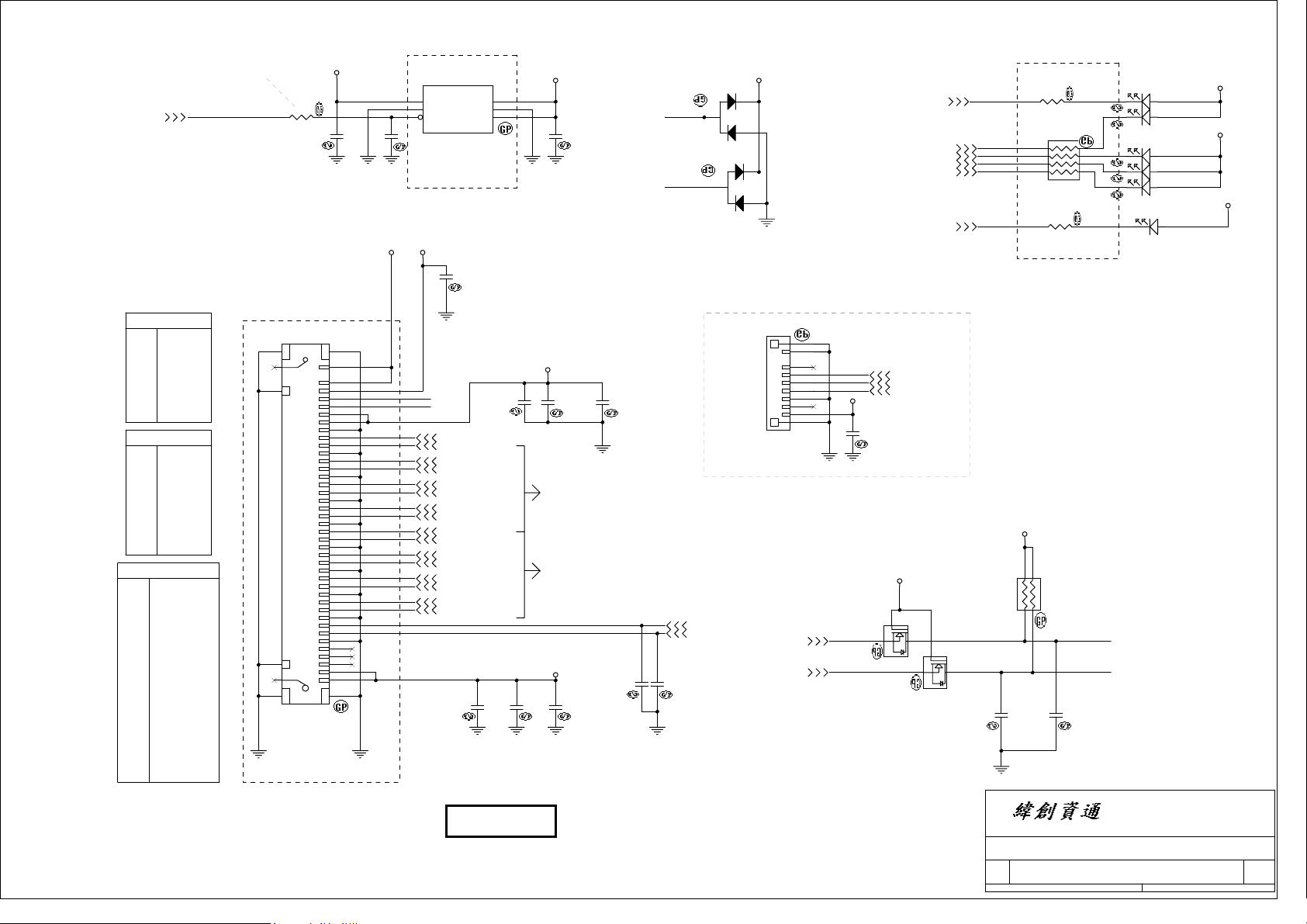

AG1(Alviso) Block Diagram 2005/11/01

E

CLK GEN.

4 4

DDR II

IDT CV125

34, 5

400MHz

400 MHz

11,12

DDR II

400MHz

400 MHz

11,12

3 3

Line In

Int.

MIC In

Line Out

27

Codec

ALC655

27

OP AMP

27

G1421B

ACLINK

26

27

Mobile CPU

Dothan

HOST BUS

400MHz

Intel 910GML

6,7,8,9,10

DMI I/F

100MHz

ICH6-M

G792

PCI BUS

19

RGB

LVDS

ENE

CB1410

10/100

CRT

CONN

LCD

XGA

24,25

LAN

RTL8110CL

2 2

INT.SPKR

27

MODEM

MDC Card

21

22, 23

LPC BUS

15,16,17,18

PATA

PCB Layer Stackup

L1: Signal 1

1 1

L2:VCC

L3: Signal 2

HDD

20

CD ROM

20

L4: Signal 3

L5: GND

USB

4 PORT

21

MINI USB

Blue-tooth

21

L6: Signal 4

A

B

C

Project Code:91.4G301.001

PCB:05223-01

14

13

Mini-PCI

802.11A/B/G

KBC

ENE KB3910

Pad

30 30

PWR SW

CP2211

25

28

TXFM

23

Xbus

INT_KBTouch

PCMCIA

ONE SLOT

RJ45

23

BIOS ROM

4M BITS

PM39LV040-70JCE

3129

25

<Core Design>

Title

Size Document Number Rev

Custom

Date: Sheet

D

INPUTS

DCBATOUT

INPUTS

APL5912-LAC

APL5308-25AC

INPUTS OUTPUTS

5V_S5

3D3V_S0 2D5V_S0

INPUTS OUTPUTS

DCBATOUT

5V_S5

DCBATOUT

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

BLOCK DIAGRAM

AG1(Alviso)

CPU DC/DC

ISL6218CV-T

OUTPUTS

VCC_CORE

0.844~1.3V

27A

SYSTEM DC/DC

TPS51120

DCBATOUT

SYSTEM DC/DC

ISL6227

TPS51100DGQ

CHARGER

ISL6255

140Tuesday, Novem ber 01, 2005

E

35

OUTPUTS

3D3V_S5

5V_S5

1D5V_S0

5V_S5

3D3V_S3

DDR_VREF

DDR_VREF_S3

OUTPUTSINPUTS

BT+

16.8V 3A

of

34

36

37

37

38

01

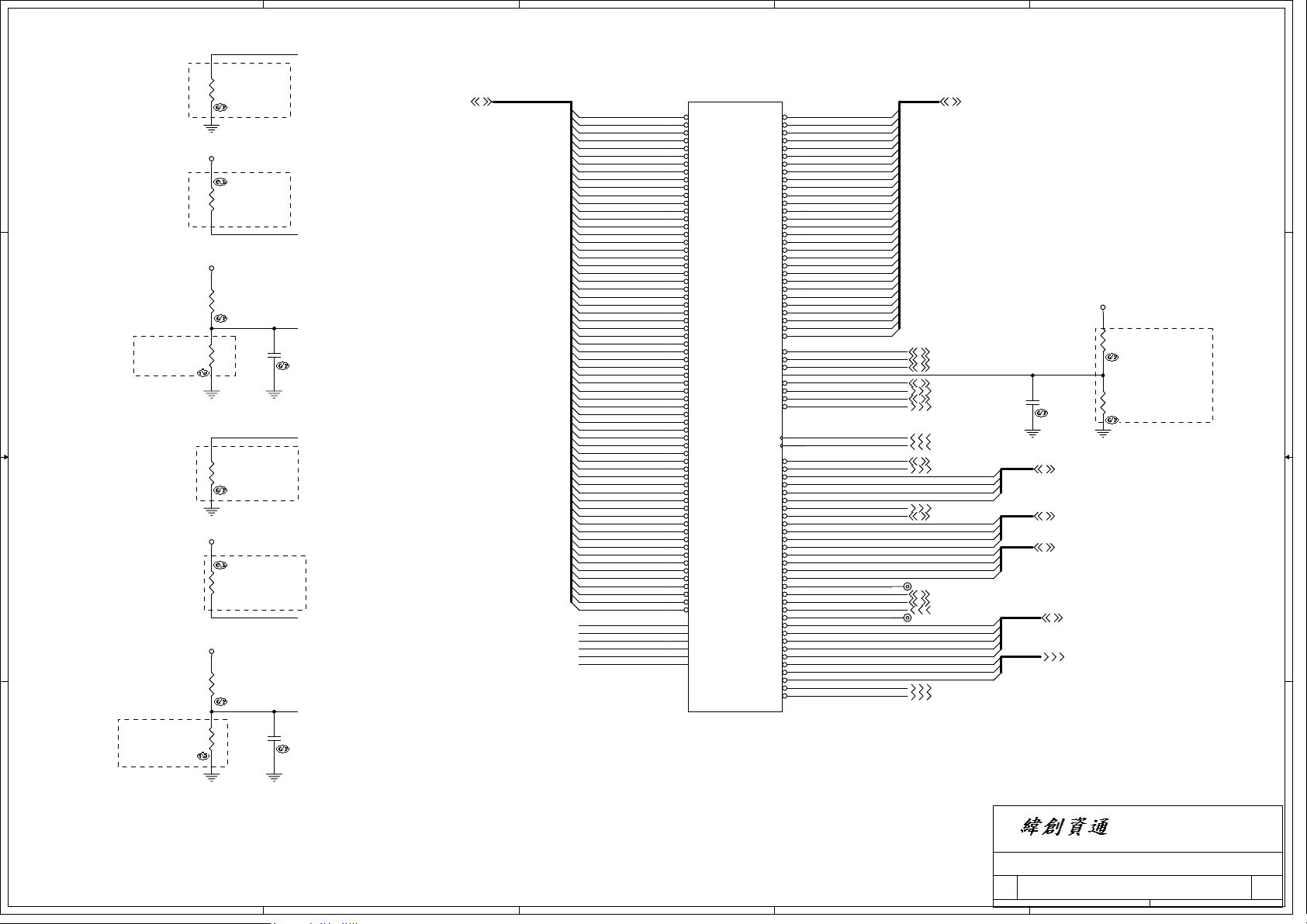

Page 2

www.RahasiaLaptop.com

A

B

C

D

E

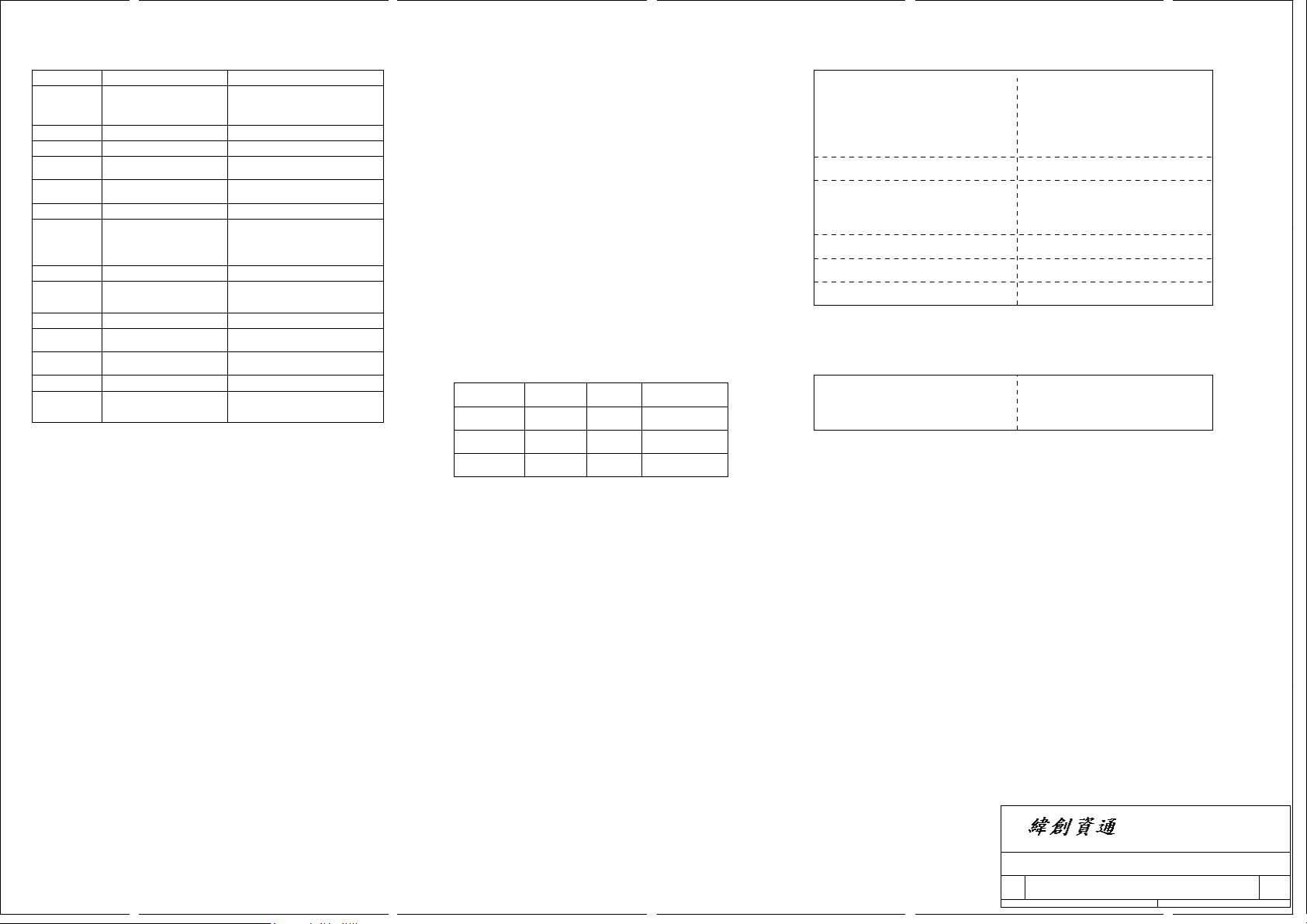

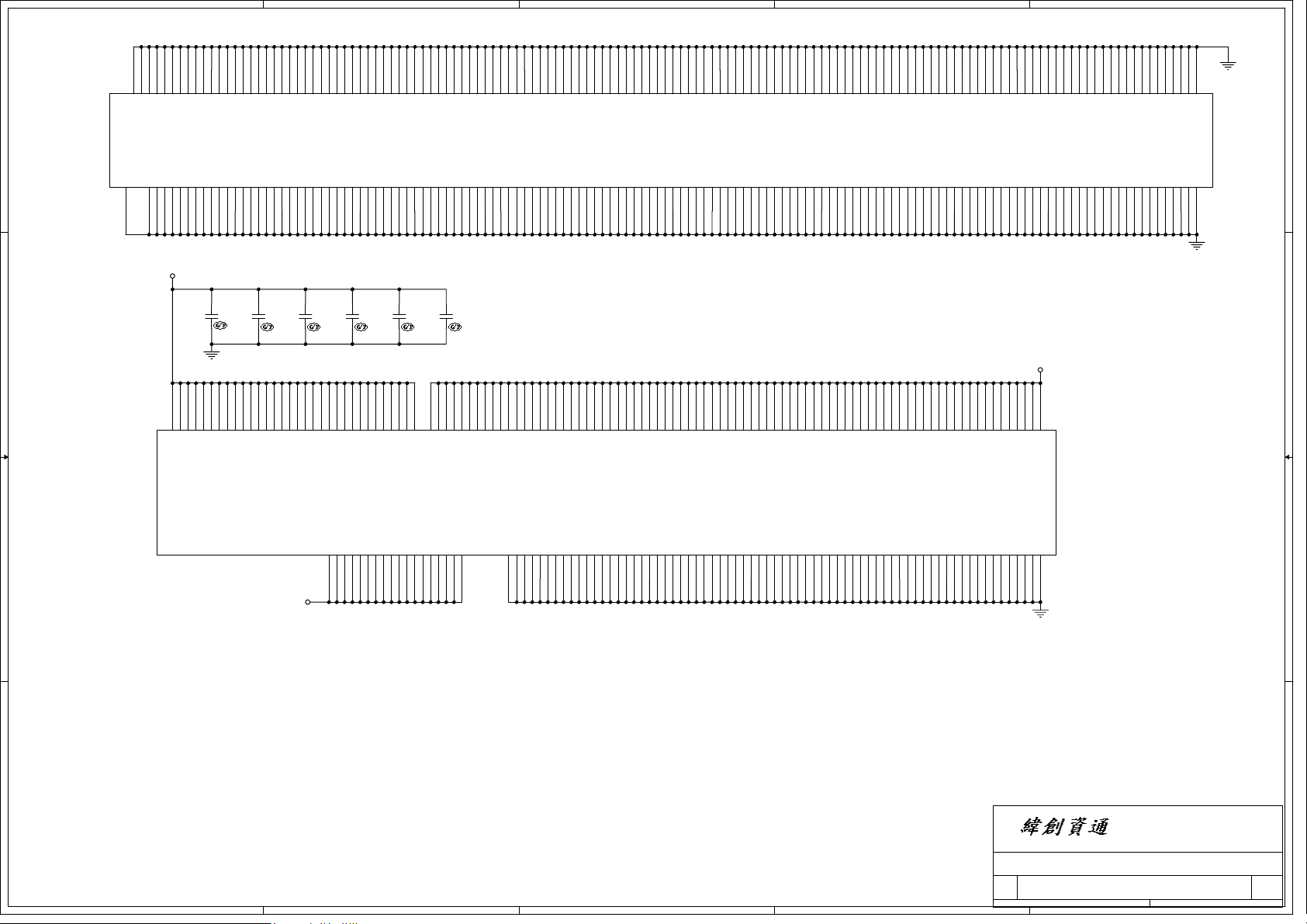

Alviso Strapping Signals

and Configuration

Pin Name

CFG[2:0]

4 4

CFG[3:4]

CFG5

CFG6

CFG7

CFG[8:11]

CFG[12:13]

CFG[14:15]

CFG16

CFG17

CFG18

3 3

CFG19

CFG20

SDVOCRTL

_DATA

All strap signals are sampled with respect to the leading

NOTE:

edge of the Alviso GMCH PWORK In signal.

Strap Description

FSB Frequency Select

Reversed

DMI x2 Select

DDR I / DDR II

CPU Strap

Reversed

XOR/ALL Z test

straps

Reversed

FSB Dynamic ODT 0 = Dynamic ODT Disabled

Reversed

CPU core VCC

Select

CPU VTT Select

Reversed

SDVO Present

Configuration

000 = Reserved

001 = FSB533

010 = FSB800

011-111 = Reversed

0 = DMI x2

1 = DMI x4

0 = DDR II

1 = DDR I

0 = Prescott

1 = Dothan

00 = Reserved

01 = XOR mode enabled

10 = All Z mode enabled

11 = Normal Operation

(Default)

1 = Dynamic ODT Enabled

(Default)

0 = 1.05V

1 = 1.5V

0 = 1.05V

1 = 1.2V

0 = No SDVO device present

(Default)

1= SDVO device present

(Default)

(Default)

(Default)

(Default)

page 7

PCI Routing

1410

MiniPCI

LAN

25

21

23

IRQ

B.F.G

F

E

REQ/GNTIDSEL

0

1

2

ICH6-M Integrated Pull-up

and Pull-down Resistors

ACZ_BIT_CLK,

EE_DOUT,

GNT[6]#/GPO[16],

LAD[3:0]#/FB[3:0]#, LDRQ[0],

PME#, PWRBTN#,

LAN_RXD[2:0]

ACZ_RST#, ACZ_SDIN[2:0],ACZ_SYNC,

ACZ_SDOUT,ACZ_BITCLK,

SPKR,

USB[7:0][P,N]

DD[7],

LAN_CLK

DPRSLP#, EE_DIN,

GNT[5]#/GPO[17],

TP[3]

EE_CS,

SDDREQ

LDRQ[1]/GPI[41],

DPRSLPVR,

ICH6 internal 20K pull-ups

ICH6 internal 10K pull-ups

ICH6 internal 20K pull-downs

ICH6 internal 15K pull-downs

ICH6 internal 11.5K pull-downs

ICH6 internal 100K pull-downs

ICH6-M EDS 14308 0.8V1

ICH6-M IDE Integrated Series

Termination Resistors

DD[15:0],

DDACK#,

DCS3#,

IORDY,

IDEIRQ

DIOR#, DREQ,DIOW#,

DA[2:0],

DCS1#,

approximately 33 ohm

2 2

1 1

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet

Memo

AG1(Alviso)

240Tuesday, November 01, 2005

of

01

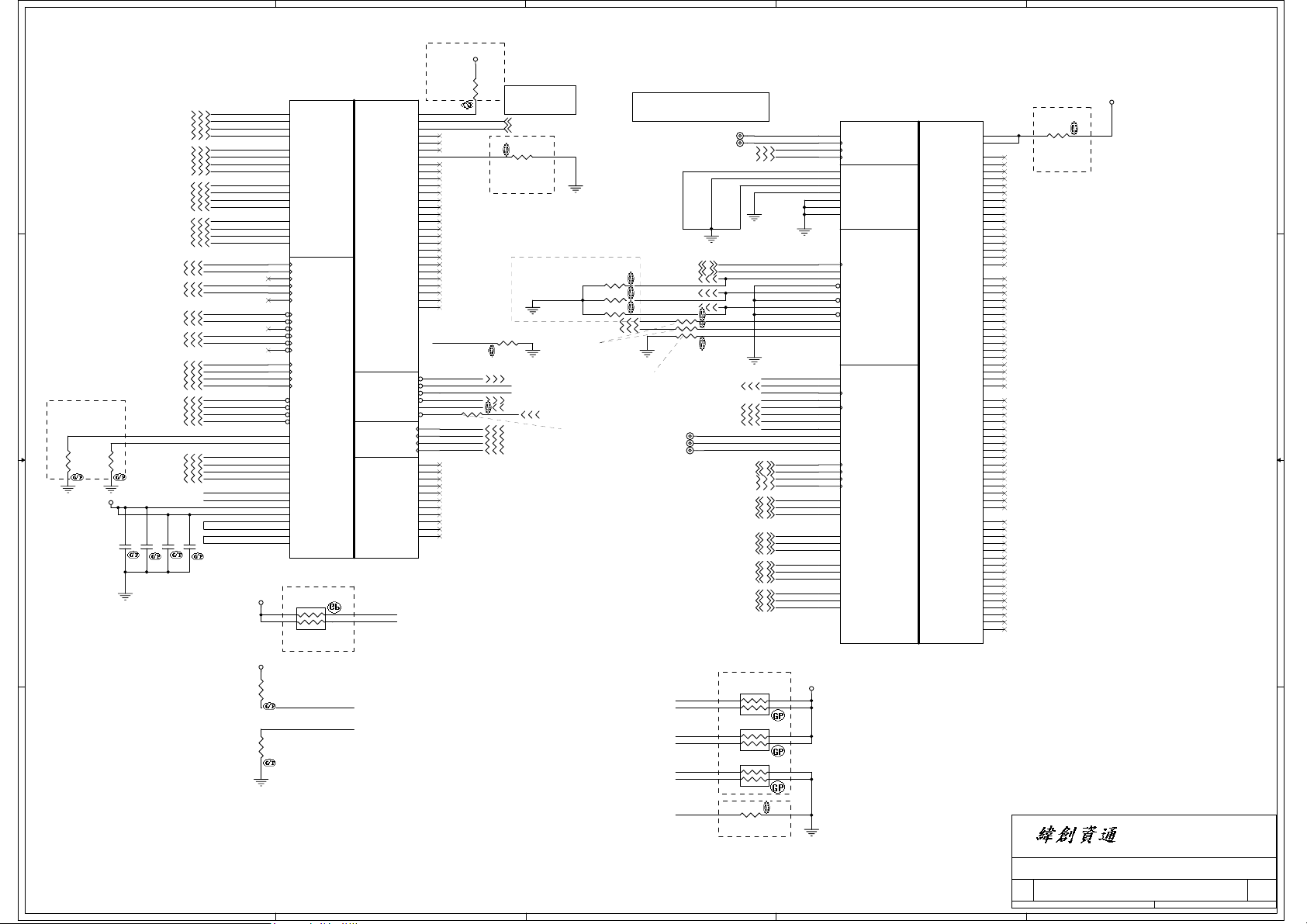

Page 3

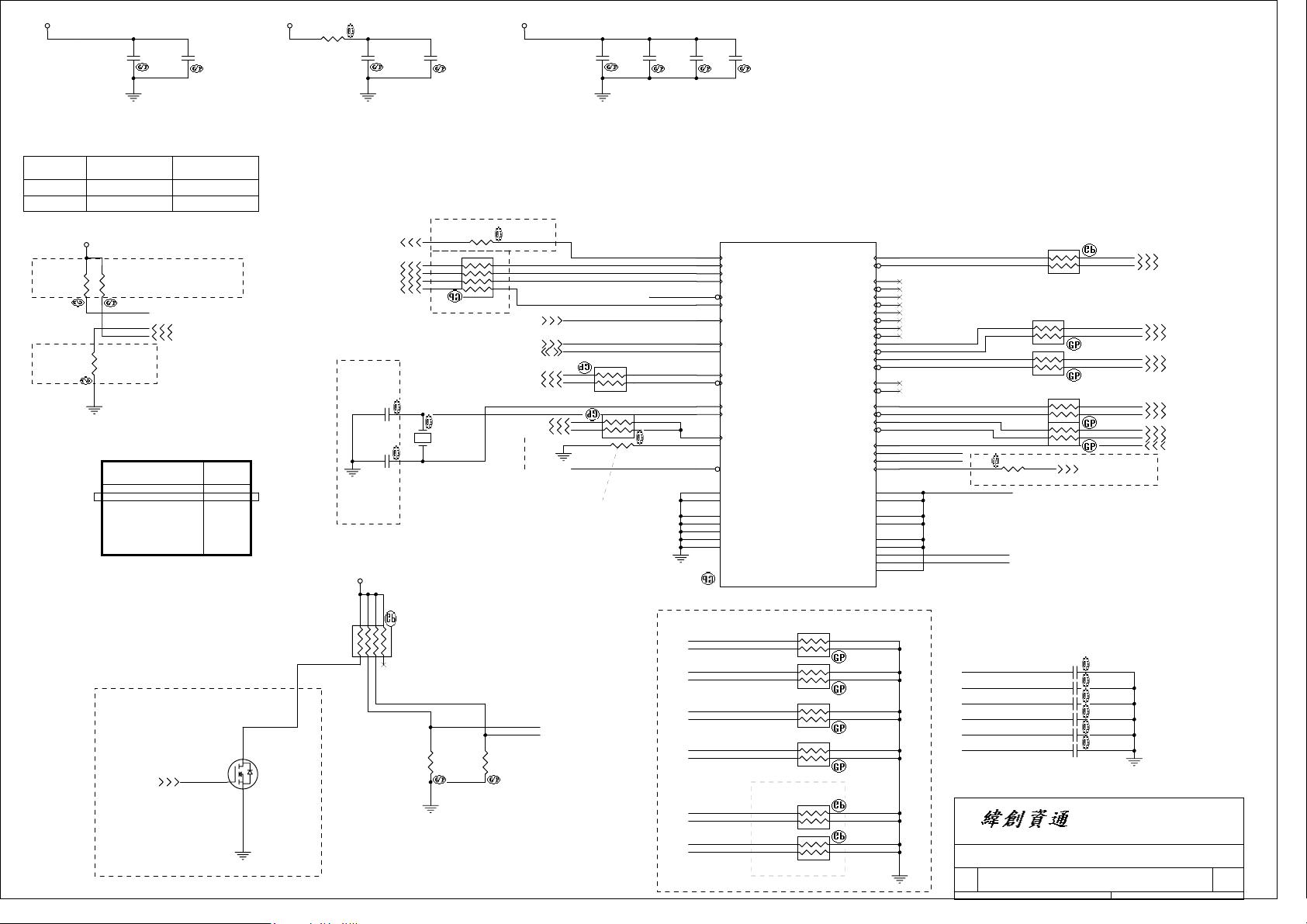

www.RahasiaLaptop.com

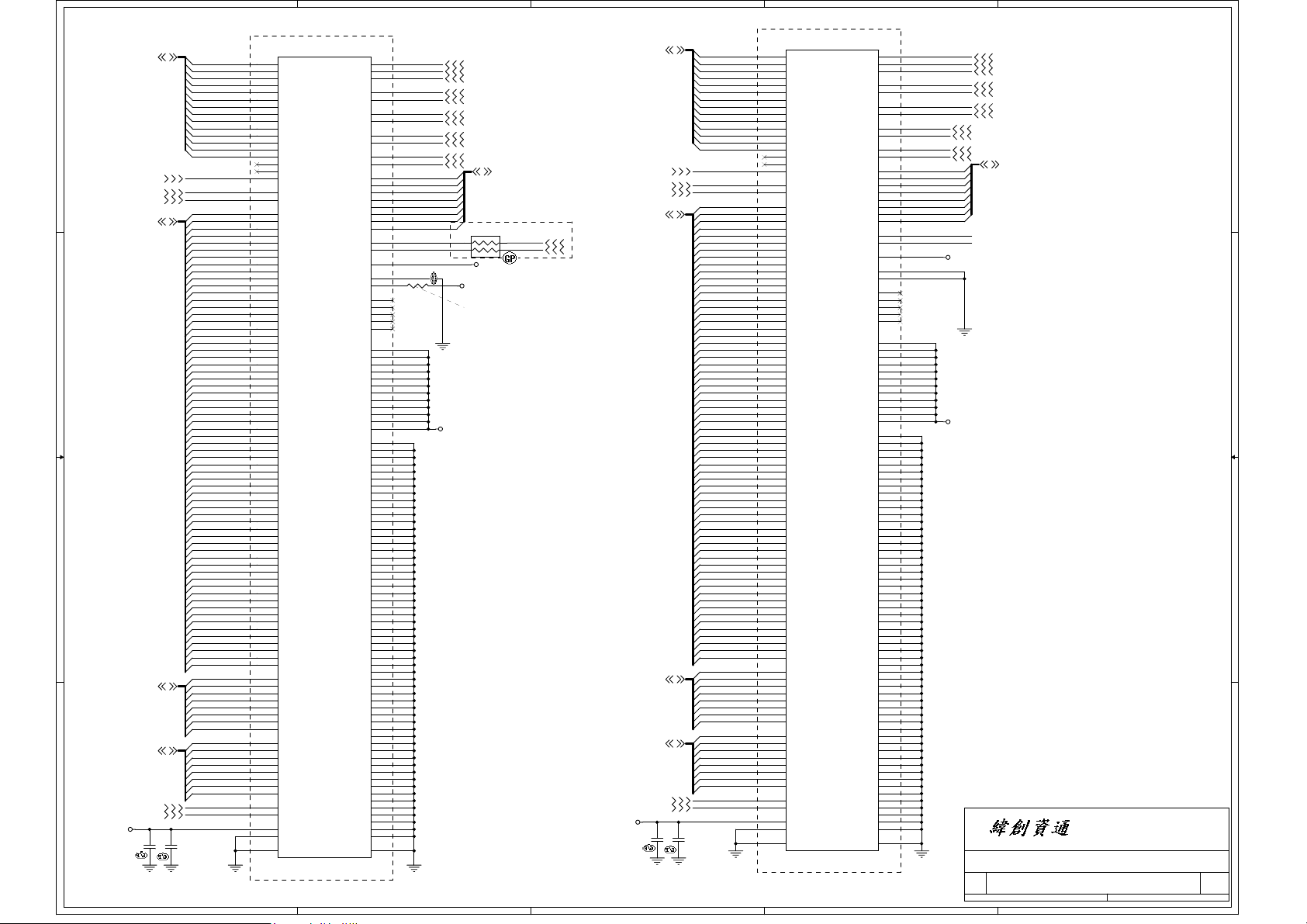

3D3V_S0 3D3V_S03D3V_S0

3D3V_APWR_S0 3D3V_CLKGEN_S03D3V_48MPWR_S0

R122

1 2

0R0603-PAD

12

C124

12

C295

SC4D7U10V5ZY-3GP

SCD1U16V2ZY-2GP

R105

1 2

2R3J-2-GP

R110

1 2

12

C104

12

C103

SC4D7U6D3V3KX-GP

SCD1U16V2ZY-2GP

0R0603-PAD

12

C108

12

SC10U10V5ZY-1GP

C109

12

12

C122

C105

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

IN

(3D3V_S0)

H

X

EN

(6218_PGOOD)

L

OUT

(VTT_PWRGD#)

H

Hi - ZH

AG1-910-01

3D3V_CLKGEN_S0

R98

1KR2J-1-GP

R102

1KR2J-1-GP

12

12

R369

1KR2J-1-GP

FS_A

12

FS_B

FS_C

0

0

0

0

1

1

0

0

1

1 100M

0

1

1

1

1

AG1-A-SA

6218_PGOOD32,34

AG1-910-01

CPU_SEL1 7

CPU_SEL0 4,7

FS_A

0

01200M

1

00333M

1

0

1 Reserved

PCLK_MINI28

PCLK_LAN22

PCLK_PCM24

PCLK_KBC29

CLK_ICHPCI16

AG1-910-SBAG1-910-01

SC22P50V2JN-4GP

C116

1 2

3D3V_S0

123

1 2

C120

SC27P50V2JN-2-GP

678

4 5

CPU

266M

133M

166M

400M

VTT_PWRGD#

D

Q23

1

G

2 3

S

2N7002PT-U

R251 33R2J-2-GP

AG1-A-SA

X1

X-14D31818M-31GP

1 2

CLK_ICH14 & CLK14_SIO

need equal length

RN64

SRN10KJ-4-GP

12

DY

R106

10KR2J-2-GP

1 2

8

7

6

RN7

SRN33J-4-GP

PM_STPPCI#16

SMBC_ICH11,18

SMBD_ICH11,18

DREFCLK7

DREFCLK#7

1

2

3

45

CLK_Audio26

CLK_ICH1416

ITP_EN

SS_SEL

12

DY

R104

10KR2J-2-GP

PCLK_MINI_1

PCLK_LAN_1

PCLK_PCM_1

PCLK_KBC_1

H/L: 100/96MHz

ITP_EN

H/L : CPU_ITP/SRC7

RN63 SRN33J-5-GP-U

4

4

RN13 SRN33J-5-GP-U

1 2

R252 475R2F-L1-GP

VTT_PWRGD#

23

1

23

1

SS_SEL

DREFCLK_1

DREFCLK#_1

XTAL_IN

XTAL_OUT

AG1-910-01

AG1-A-SA

56

3

4

5

9

8

55

46

47

14

15

50

49

52

39

10

2

6

51

45

38

13

29

IDTCV125PAG-GP

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_ICH

CLK_PCIE_ICH#

DREFSSCLK#

DREFSSCLK

DREFCLK#

DREFCLK

PCI0

PCI1

PCI2

PCI3

PCIF1/SEL100/96#

PCIF0/ITP_EN

PCI_STOP#

SCL

SDA

DOT96

DOT96#

XTAL_IN

XTAL_OUT

REF

IREF

VTT_PWRGD#/PD

VSS_PCI

VSS_PCI

VSS_REF

VSS_CPU

VSSA

VSS48

VSS_SRC

RN20 SRN49D9F-GP

1

2 3

RN19 SRN49D9F-GP

1

2 3

RN14 SRN49D9F-GP

1

2 3

RN9 SRN49D9F-GP

1

2 3

AG1-910-01

2 3

1

RN60 SRN49D9F-GP

2 3

1

RN61

CPU2_ITP/SRC7

CPU2_ITP#/SRC7#

CPU_STOP#

FSC/TEST_SEL

FSB/TEST_MODE

U28

LVDS

LVDS#

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC4

SRC4#

SRC5

SRC5#

SRC6

SRC6#

CPU0

CPU0#

CPU1

CPU1#

USB48/FSA

VDD_SRC

VDD_SRC

VDD_PCI

VDD_PCI

VDD_REF

VDD_CPU

VDDA

VDD48

VDD_SRC

4

4

4

4

4

4

SRN49D9F-GP

2nd

17

18

19

20

22

23

24

25

26

27

CLK_PCIE_ICH1

31

CLK_PCIE_ICH#1

30

CLK_MCH_3GPLL1

33

CLK_MCH_3GPLL#1

32

36

35

CLK_CPU_BCLK1

44

CLK_CPU_BCLK#1

43

CLK_MCH_BCLK1

41

CLK_MCH_BCLK#1

40

54

CPU_SEL0

53

CPU_SEL1

16

12

34

21

7

1

48

42

37

11

28

DREFSSCLK1

DREFSSCLK#1

FS_A

3D3V_CLKGEN_S0

3D3V_APWR_S0

3D3V_48MPWR_S0

RN10 SRN33J-5-GP-U

R103 22R2J-2-GP

2 3

1

4

RN62

SRN33J-5-GP-U

1

4

2 3

RN18 SRN47J-7-GP

1

4

2 3

RN12 SRN33J-5-GP-U

1

4

2 3

RN11 SRN33J-5-GP-U

1

4

2 3

12

CLK48_ICH 16

AG1-910-01

EMI capacitor

CLK_ICH14CLK_MCH_BCLK

PCLK_PCM

PCLK_MINI

PCLK_KBC

CLK_ICHPCI

CLK48_ICH

<Core Design>

Title

Size Document Number Rev

A3

Date: Sheet of

EC45 SC10P50V2JN-4GP

1 2

DY

EC41 SC10P50V2JN-4GP

1 2

DY

EC70 SC10P50V2JN-4GP

1 2

DY

EC42 SC10P50V2JN-4GP

1 2

DY

EC43 SC10P50V2JN-4GP

1 2

DY

EC39 SC10P50V2JN-4GP

1 2

DY

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Clock Gener ator - IDT125

AG1(Alviso)

340Friday, October 28, 2005

DREFSSCLK 7

DREFSSCLK# 7

CLK_PCIE_ICH 16

CLK_PCIE_ICH# 16

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

PM_STPCPU# 16, 34

01

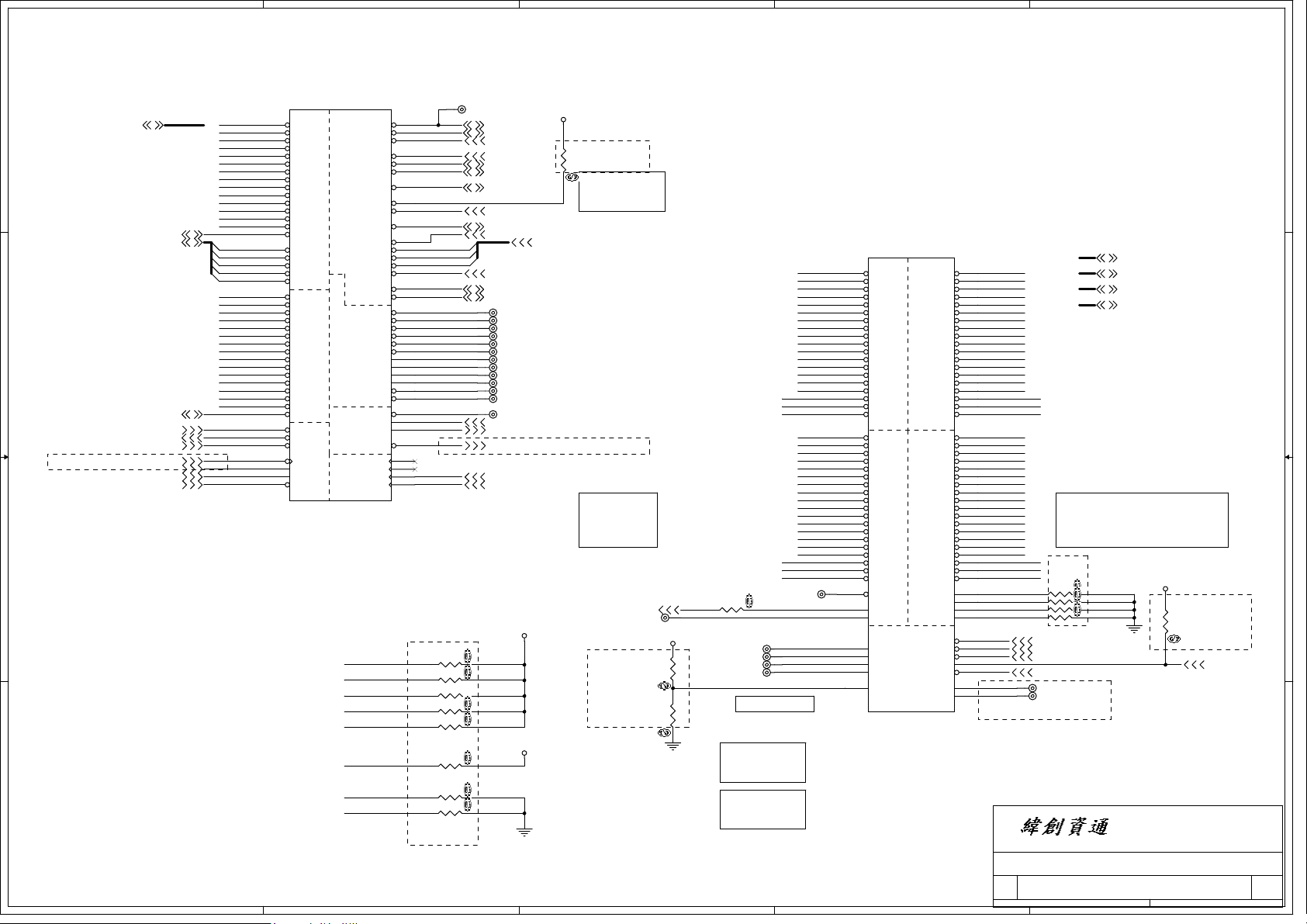

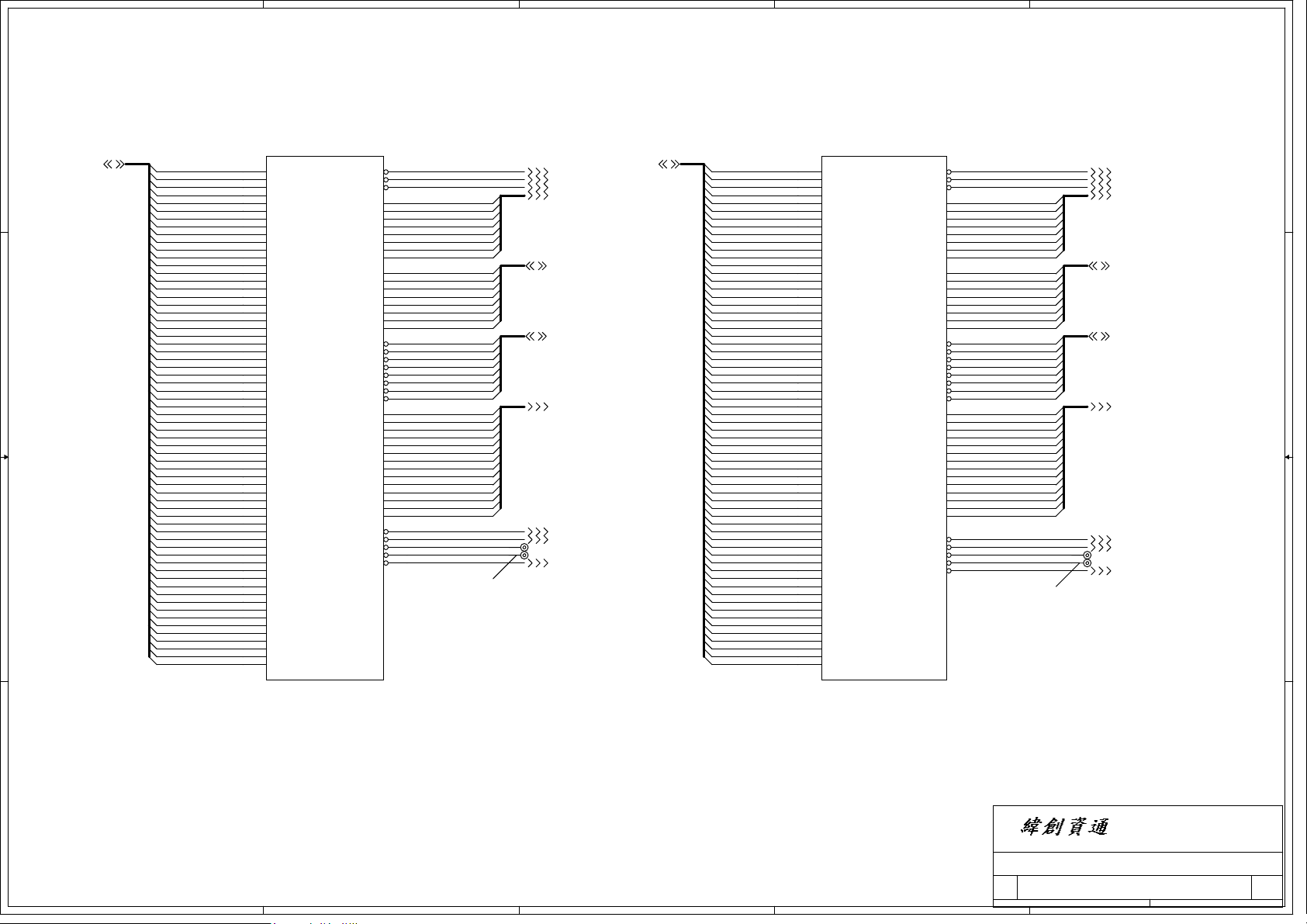

Page 4

www.RahasiaLaptop.com

A

B

C

D

E

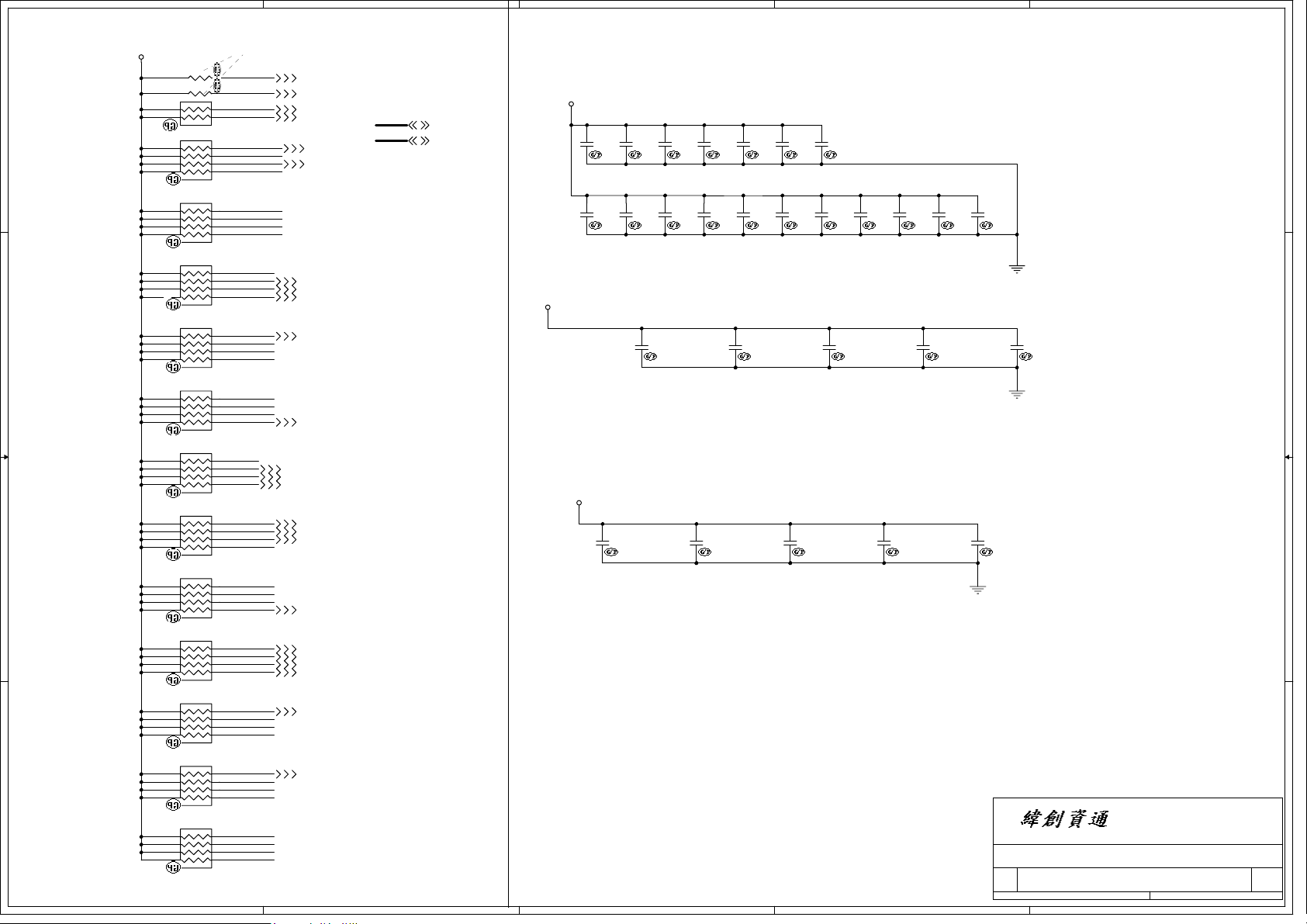

U41A

TUALA-SKT-1

H_A#3

4 4

3 3

H_A#[31..3]6

AG1-A-SA

H_ADSTB#06

H_REQ#[4..0]6

H_ADSTB#16

H_A20M#15

H_FERR#15

H_IGNNE#15

H_STPCLK#15

H_INTR15

H_NMI15

H_SMI#15

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

U3

ADSTB#0

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

AE5

ADSTB#1

C2

A20M#

D3

FERR#

A3

IGNNE#

C6

STPCLK#

D1

LINT0

D4

LINT1

B4

SMI#

62.10053.061

CONNECTOR Y

ADDR GROUP 0

ADDR GROUP 1

PROCHOT#

THERMTRIP#

HCLK THERM XTP/ITP SIGNALS CONTROL

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

THERMDA

THERMDC

ITP_CLK1

ITP_CLK0

BCLK1

BCLK0

N2

L1

J3

L4

H2

M2

N4

A4

B5

J2

B11

H1

K1

L2

M3

K3

K4

C8

B8

A9

C9

A10

B10

A13

C12

TDI

A12

C11

B13

A7

B17

B18

A18

C17

A15

A16

B14

B15

AG1_A-SA : 62.10079.001

2 2

CPU_PROCHOT#

XDP_TDI

XDP_TMS

XDP_TDO

H_CPURST#

XDP_DBRESET#

1 1

XDP_TCK

XDP_TRST#

All place within 2" to CPU

R262 56R2F-1-GP

R256 150R2F-1-GP

R259 39D2R3F-GP

R257 54D9R2F-L1-GP

R258 54D9R2F-L1-GP

R263 150R2F-1-GP

R255 27D4R2F-L1-GP

R260 680R3F-GP

AG1-910-01

A

B

TP53

TPAD28

H_RS#0

H_RS#1

H_RS#2

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

CPU_PROCHOT#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

H_IERR#

TP78TPAD28

TP87TPAD28

TP86TPAD28

TP77TPAD28

TP85TPAD28

TP76TPAD28

TP81TPAD28

TP82TPAD28

TP83TPAD28

TP84TPAD28

TP91TPAD28

TP88TPAD28

TP89TPAD28

1D05V_S0

H_RS#[2..0] 6

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_INIT# 15

H_LOCK# 6

H_CPURST# 6

H_TRDY# 6

H_HIT# 6

H_HITM# 6

H_THERMDA 19

H_THERMDC 19

PM_THRMTRIP-I# 7,15,19

CLK_CPU_BCLK# 3

CLK_CPU_BCLK 3

1D05V_S0

3D3V_S0

12

AG1-910-01

R261

56R2J-4-GP

Place testpoint on

H_IERR# with a GND

0.1" away

PM_THRMTRIP#

should connect to

ICH6 and Alviso

without T-ing

( No stub)

CPU_SEL03,7

AG1-910-01

AG1-A-SA

TP90 TPAD28

R283

1KR2F-3-GP

R282

2KR3F-L-GP

C

1D05V_S0

12

12

To V-CORE SWITCH

R264

1 2

DY

TP80 TPAD28

TP94 TPAD28

TP93 TPAD28

TP49 TPAD28

Layout Note:

0.5" max length.

BSEL[1:0] Freq.(MHz)

(A Stepping)

L L 100

L H 133

BSEL[1:0] Freq.(MHz)

(B Stepping)

L H 100

L L 133

TP92

TPAD28

0R3-0-U-GP

GTLREF0

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

C23

C22

D25

H23

G25

M26

H24

G24

M23

N24

M25

H26

N25

K25

K24

C16

C14

AF7

AC1

E26

AD26

L23

F25

J23

J25

L26

L24

J26

E1

C3

U41B

TUALA-SKT-1

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

DATA GRP 0DATA GRP 1

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

PSI#

BSEL0

BSEL1

MISC

RSVD2

RSVD3

RSVD4

RSVD5

GTLREF0

62.10053.061

CONNECTOR

Y

D

Y26

D32#

AA24

D33#

T25

D34#

U23

D35#

V23

D36#

R24

D37#

R26

D38#

R23

D39#

AA23

D40#

U26

D41#

V24

D42#

U25

D43#

V26

D44#

DATA GRP 2

Y23

D45#

AA26

D46#

Y25

D47#

W25

DSTBN2#

W24

DSTBP2#

T24

DINV2#

AB25

D48#

AC23

D49#

AB24

D50#

AC20

D51#

AC22

D52#

AC25

D53#

AD23

D54#

AE22

D55#

AF23

D56#

AD24

D57#

AF20

D58#

AE21

D59#

AD21

D60#

DATA GRP 3

AF25

D61#

AF22

D62#

AF26

D63#

AE24

DSTBN3#

AE25

DSTBP3#

AD20

DINV3#

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

G1

DPRSTP#

B7

DPSLP#

C19

DPWR#

SLP#

TEST1

TEST2

E4

A6

C5

F23

PWRGOOD

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

TEST1

TEST2

H_DSTBN#3

H_DSTBP#3

H_DINV#3

AG1-910-01

R281 27D4R2F-L1-GP

1 2

R279 54D9R2F-L1-GP

1 2

R287 27D4R2F-L1-GP

1 2

R284 54D9R2F-L1-GP

1 2

H_DPRSLP# 15

H_DPSLP# 15

H_DPWR# 6

H_CPUSLP# 6,15

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

TP79TPAD28

TP51TPAD28

H_D#[63..0] 6

H_DINV#[3..0] 6

H_DSTBN#[3..0] 6

H_DSTBP#[3..0] 6

1D05V_S0

12

R154

200R2F-L-GP

AG1-910-01

H_PW R GD 15,19

AG1-A-SA

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet

CPU (1 of 2)

AG1(Alviso) 01

440Monday, October 31, 2005

E

of

Page 5

www.RahasiaLaptop.com

A

VCC_CORE_S0

U41C

TUALA-SKT-1

AA11

VCC0

AA13

VCC1

AA15

VCC2

AA17

VCC3

AA19

VCC4

AA21

VCC5

AA5

VCC6

4 4

3 3

2 2

1 1

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC9

AD10

AD12

AD14

AD16

AD18

AD8

AE11

AE13

AE15

AE17

AE19

AE9

AF10

AF12

AF14

AF16

AF18

AF8

D18

D20

D22

D6

D8

E17

E19

E21

E5

E7

E9

F18

F20

F22

F6

F8

G21

Layout Note:

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

62.10053.061

CONNECTOR

Y

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCCA0

VCCA1

VCCA2

VCCA3

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VID0

VID1

VID2

VID3

VID4

VID5

VCCSENSE

VSSSENSE

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

G5

H22

H6

J21

J5

K22

U5

V22

V6

W21

W5

Y22

Y6

F26

B1

N1

AC26

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

K6

L21

L5

M22

M6

N21

N5

P22

P6

R21

R5

T22

T6

U21

P23

W4

E2

F2

F3

G3

G4

H4

AE7

AF6

VCC_CORE_S0

1D05V_S0

TP_VCCSENSE

TP_VSSSENSE

AG1-A-SA

SCD01U16V2KX-3GP

C311

H_VID0 34

H_VID1 34

H_VID2 34

H_VID3 34

H_VID4 34

H_VID5 34

1D5V_S0

12

TP58TPAD28

TP59TPAD28

VCC_CORE_S0

A

12

C161

SC10U10V5ZY-1GP

1D05V_S0

12

VCC_CORE_S0

12

12

DY

AG1-910-SB

VCC_CORE_S0

12

B

12

C178

C168

C167

C202

C187

DY

SCD1U16V2ZY-2GP

12

12

C169

SC10U6D3V5KX-1GP

12

12

C166

SCD1U16V2ZY-2GP

DY

SCD1U16V2ZY-2GP

SC10U6D3V5KX-1GP

SCD1U16V2ZY-2GP

SC10U6D3V5KX-1GP

B

12

12

C196

SC10U6D3V5KX-1GP

C209

SCD1U16V2ZY-2GP

C163

DY

C177

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C194

SC10U6D3V5KX-1GP

12

12

C213

SCD1U16V2ZY-2GP

DY

12

12

C180

SCD1U16V2ZY-2GP

12

C211

C200

SCD1U16V2ZY-2GP

C

12

C164

TC8

DY

SCD1U16V2ZY-2GP

ST100U6D3VBM-9GP

AG1-A-SA

12

12

C201

C203

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C

D

U41D TUALA-SKT-1

A2

VSS0

A5

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A17

VSS5

A20

VSS6

A23

VSS7

A26

VSS8

AA1

VSS9

AA4

VSS10

AA6

VSS11

AA8

VSS12

AA10

VSS13

AA12

VSS14

AA14

VSS15

AA16

VSS16

AA18

VSS17

AA20

VSS18

AA22

VSS19

AA25

VSS20

AB3

VSS21

AB5

VSS22

AB7

VSS23

AB9

VSS24

AB11

VSS25

AB13

VSS26

AB15

VSS27

AB17

VSS28

AB19

VSS29

AB21

VSS30

AB23

VSS31

AB26

VSS32

AC2

VSS33

AC5

VSS34

AC8

VSS35

AC10

VSS36

AC12

VSS37

AC14

VSS38

AC16

VSS39

AC18

VSS40

AC21

VSS41

AC24

VSS42

AD1

VSS43

AD4

VSS44

AD7

VSS45

AD9

VSS46

AD11

VSS47

AD13

VSS48

AD15

VSS49

AD17

VSS50

AD19

VSS51

AD22

VSS52

AD25

VSS53

AE3

VSS54

AE6

VSS55

AE8

VSS56

AE10

VSS57

AE12

VSS58

AE14

VSS59

AE16

VSS60

AE18

VSS61

AE20

VSS62

AE23

VSS63

AE26

VSS64

AF2

VSS65

AF5

VSS66

AF9

VSS67

AF11

VSS68

AF13

VSS69

AF15

VSS70

AF17

VSS71

AF19

VSS72

AF21

VSS73

AF24

VSS74

B3

VSS75

B6

VSS76

B9

VSS77

B12

VSS78

B16

VSS79

B19

VSS80

B22

VSS81

B25

VSS82

C1

VSS83

C4

VSS84

C7

VSS85

C10

VSS86

C13

VSS87

C15

VSS88

C18

VSS89

C21

VSS90

C24

VSS91

D2

VSS92

D5

VSS93

D7

VSS94

D9

VSS95

D11

<Core Design>

Title

Size Document Number Rev

A3

D

Date: Sheet

VSS96

CPU (2 of 2)

AG1(Alviso) 01

E

D13

VSS97

D15

VSS98

D17

VSS99

D19

VSS100

D21

VSS101

D23

VSS102

D26

VSS103

E3

VSS104

E6

VSS105

E8

VSS106

E10

VSS107

E12

VSS108

E14

VSS109

E16

VSS110

E18

VSS111

E20

VSS112

E22

VSS113

E25

VSS114

F1

VSS115

F4

VSS116

F5

VSS117

F7

VSS118

F9

VSS119

F11

VSS120

F13

VSS121

F15

VSS122

F17

VSS123

F19

VSS124

F21

VSS125

F24

VSS126

G2

VSS127

G6

VSS128

G22

VSS129

G23

VSS130

G26

VSS131

H3

VSS132

H5

VSS133

H21

VSS134

H25

VSS135

J1

VSS136

J4

VSS137

J6

VSS138

J22

VSS139

J24

VSS140

K2

VSS141

K5

VSS142

K21

VSS143

K23

VSS144

K26

VSS145

L3

VSS146

L6

VSS147

L22

VSS148

L25

VSS149

M1

VSS150

M4

VSS151

M5

VSS152

M21

VSS153

M24

VSS154

N3

VSS155

N6

VSS156

N22

VSS157

N23

VSS158

N26

VSS159

P2

VSS160

P5

VSS161

P21

VSS162

P24

VSS163

R1

VSS164

R4

VSS165

R6

VSS166

R22

VSS167

R25

VSS168

T3

VSS169

T5

VSS170

T21

VSS171

T23

VSS172

T26

VSS173

U2

VSS174

U6

VSS175

U22

VSS176

U24

VSS177

V1

VSS178

V4

VSS179

V5

VSS180

V21

VSS181

V25

VSS182

W3

VSS183

W6

VSS184

W22

VSS185

W23

VSS186

W26

VSS187

Y2

VSS188

Y5

VSS189

Y21

VSS190

Y24

VSS191

CONNECTOR Y

62.10053.061

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

540Monday, October 17, 2005

E

of

Page 6

www.RahasiaLaptop.com

A

H_XRCOMP

12

R290

24D9R2F-L-GP

AG1-910-01

4 4

1D05V_S0

54D9R2F-L1-GP

R291

AG1-910-01

1 2

H_XSCOMP

1D05V_S0

12

R288

221R2F-2-GP

H_XSWING

3 3

100R2F-L1-GP-U

AG1-910-01

R289

12

12

H_YRCOMP

R292

24D9R2F-L-GP

12

C331

SCD1U16V2ZY-2GP

AG1-910-01

1D05V_S0

2 2

1D05V_S0

R293

100R2F-L1-GP-U

AG1-910-01

54D9R2F-L1-GP

R295

1 2

H_YSCOMP

12

R294

221R2F-2-GP

12

AG1-910-01

H_YSWING

12

C335

SCD1U16V2ZY-2GP

B

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

C

U38A

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

C1

C2

D1

T1

L1

P1

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HOST

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

71.0GMCH.08U

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB#0

HADSTB#1

HVREF

HBNR#

HBPRI#

HBREQ0#

HCPURST#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_VREF

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

TP_H_EDRDY#

TP_H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

D

H_A#[31..3] 4H_D#[63..0]4

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_CPURST# 4

CLK_MCH_BCLK# 3

CLK_MCH_BCLK 3

H_DBSY# 4

H_DEFER# 4

H_DPWR# 4

H_DRDY# 4

TP57TPAD28

H_HIT# 4

H_HITM# 4

H_LOCK# 4

TP55TPAD28

H_CPUSLP# 4,15

H_TRDY# 4

12

C186

SCD1U16V2ZY-2GP

1D05V_S0

12

12

H_DINV#[3..0] 4

H_DSTBN#[3..0] 4

H_DSTBP#[3..0] 4

H_REQ#[4..0] 4

H_RS#[2..0] 4

E

R172

100R2F-L1-GP-U

R175

200R2F-L-GP

AG1-910-01

1 1

Place them near to the chip

A

B

C

D

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

Date: Sheet

GMCH (1 of 5)

AG1(Alviso) 01

640Tuesday, October 25, 2005

E

of

Page 7

www.RahasiaLaptop.com

A

U38B

DMI_TXN0

DMI_TXN016

M_CLK_DDR011

M_CLK_DDR111

M_CLK_DDR311

M_CLK_DDR411

M_CLK_DDR#011

M_CLK_DDR#111

M_CLK_DDR#311

M_CLK_DDR#411

12

DDR_VREF_S3

12

C304SC2D2U6D3V3MX-1-GP

DMI_TXN116

DMI_TXN216

DMI_TXN316

DMI_TXP016

DMI_TXP116

DMI_TXP216

DMI_TXP316

DMI_RXN016

DMI_RXN116

DMI_RXN216

DMI_RXN316

DMI_RXP016

DMI_RXP116

DMI_RXP216

DMI_RXP316

M_CKE011,12

M_CKE111,12

M_CKE211,12

M_CKE311,12

M_CS#011,12

M_CS#111,12

M_CS#211,12

M_CS#311,12

M_OCDCOMP0

M_OCDCOMP1

M_ODT011,12

M_ODT111,12

M_ODT211,12

M_ODT311,12

12

12

BC4SCD1U16V2ZY-2GP

C219SC2D2U6D3V3MX-1-GP

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

12

BC2SCD1U16V2ZY-2GP

4 4

3 3

Layout Note:

Route as short

as possible

12

R168

R155

40D2R2F-GP

40D2R2F-GP

2 2

1 1

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

2D5V_S0

1D8V_S3

12

12

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

SMYSLEWIN

AF10

SMYSLEWOUT

AG1-A-SA

2 3

1

R171

80D6R2F-L-GP

R173

80D6R2F-L-GP

71.0GMCH.08U

SRN10KJ-5-GP

4

RN24

M_RCOMPN

M_RCOMPP

DMI

DDR MUXING

PM_EXTTS#0

PM_EXTTS#1

A

CFG/RSVD

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PM

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

CLK

DREF_SSCLKP

NC

B

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

B

1D05V_S0

R166

10KR2J-3-GP

CFG0

G16

H13

G14

F16

F15

G15

CFG6

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

VGATE_PWRGD

J23

PM_EXTTS#0

J21

PM_EXTTS#1

H22

F5

AD30

AE29

1 2

R152 100R2J-2-GP

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

12

AG1-910-01

AG1-910-01

10KR2J-2-GP

DY

2K2R2J-2-GP

R254

CFG[2:0] Freq.(MHz)

101 400

001 533

CPU_SEL1 3

CPU_SEL0 3,4

R165

12

AG1-910-01

GMCH_VSYNC14

GMCH_HSYNC14

12

AG1-910-01

PM_BMBUSY# 16

PM_THRMTRIP-I# 4,15,19

VGATE_PWRGD 16,32

PLT_RST1# 16,18,29

DREFCLK# 3

DREFCLK 3

DREFSSCLK# 3

DREFSSCLK 3

AG1-910-01

C

Alviso will provide SDVO_CTRLCLK

and CTRLDATA pulldowns on-die

GMCH_DDCCLK14

GMCH_DDCDATA14

GMCH_BLUE14

R158150R2F-1-GP

1 2

GMCH_GREEN14

R157150R2F-1-GP

1 2

GMCH_RED14

R162150R2F-1-GP

1 2

R159 39R2J-L-GP

R156 39R2J-L-GP

AG1-910-SB

C

TP50 TPAD28

TP48 TPAD28

CLK_MCH_3GPLL#3

CLK_MCH_3GPLL3

1 2

1 2

1 2

R161

261R2F-GP

BL_ON29

CLK_DDC_EDID13

DAT_DDC_EDID13

GMCH_LCDVDD_ON13

TP42 TPAD28

TP44 TPAD28

TP46 TPAD28

GMCH_TXACLK-13

GMCH_TXACLK+13

GMCH_TXBCLK-13

GMCH_TXBCLK+13

GMCH_TXAOUT0-13

GMCH_TXAOUT1-13

GMCH_TXAOUT2-13

GMCH_TXAOUT0+13

GMCH_TXAOUT1+13

GMCH_TXAOUT2+13

GMCH_TXBOUT0-13

GMCH_TXBOUT1-13

GMCH_TXBOUT2-13

GMCH_TXBOUT0+13

GMCH_TXBOUT1+13

GMCH_TXBOUT2+13

LCTLA_CLK

LCTLB_DATA

CLK_DDC_EDID

DAT_DDC_EDID

BL_ON

LBKLT_CRTL

LIBG

SDVOC_CTRLDATA

SDVOC_CTRLCLK

AG1-A-SA

DY

RN21

1

2 3

SRN2K2J-1-GP

RN23

1

2 3

SRN2K2J-1-GP

1

2 3

SRN100KJ-6-GP

R271 1K5R2F-2-GP

1 2

AG1-910-01

HSYNC

CRTIREF

VSYNC

LBKLT_CRTL

LCTLA_CLK

LCTLB_DATA

CLK_DDC_EDID

DAT_DDC_EDID

LIBG

L_LVBG

L_VREFH

L_VREFL

2D5V_S0

4

4

RN22

4

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

U38G

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

71.0GMCH.08U

D

MISCTVVGALVDS

D

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

PCI-EXPRESS GRAPHICS

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

E

1D5V_PCIE_S0

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

R366

1 2

24D9R2F-L-GP

AG1-910-01

<Core Design>

Wistron Corporation

21F, 88, Sec .1, Hs in Ta i W u R d., Hs ichih,

Title

Size Document Number Re v

Custom

Date: Sheet

Taipei Hsi en 221, Taiwan, R.O.C .

GMCH (2 of 5)

AG1(Alviso) 01

740Tuesday, October 25, 2005

E

of

Page 8

www.RahasiaLaptop.com

A

4 4

B

C

D

E

M_A_DQ[63..0]11 M_B_DQ[63..0]11

3 3

2 2

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

U38C

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

AK15

SA_BS0#

AK16

SA_BS1#

AL21

SA_BS2#

AJ37

SA_DM0

AP35

SA_DM1

AL29

SA_DM2

AP24

SA_DM3

AP9

SA_DM4

AP4

SA_DM5

AJ2

SA_DM6

AD3

SA_DM7

AK36

SA_DQS0

AP33

SA_DQS1

AN29

SA_DQS2

AP23

SA_DQS3

AM8

SA_DQS4

AM4

SA_DQS5

AJ1

SA_DQS6

AE5

SA_DQS7

AK35

SA_DQS0#

AP34

SA_DQS1#

AN30

SA_DQS2#

AN23

SA_DQS3#

AN8

SA_DQS4#

AM5

SA_DQS5#

AH1

SA_DQS6#

AE4

SA_DQS7#

AL17

SA_MA0

AP17

SA_MA1

AP18

SA_MA2

AM17

SA_MA3

AN18

SA_MA4

AM18

SA_MA5

AL19

SA_MA6

DDR SYSTEM MEMORY A

SA_RCVENIN#

SA_RCVENOUT#

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_WE#

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

SA_RCVENIN#

SA_RCVENOUT#

Place Test PAD Near to Chip

as could as possible

M_A_BS#0 11,12

M_A_BS#1 11,12

M_A_BS#2 11,12

M_A_DM[7..0] 11

M_A_DQS[7..0] 11

M_A_DQS#[7..0] 11

M_A_A[13..0] 11,12

M_A_CAS# 11,12

M_A_RAS# 11,12

TP43 TPAD28

TP47 TPAD28 TP52 TPAD28

M_A_WE# 11,12

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AK9

AK6

AH5

AK8

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U38D

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

AJ9

SBDQ38

SBDQ39

AJ7

SBDQ40

SBDQ41

AJ4

SBDQ42

SBDQ43

SBDQ44

AJ8

SBDQ45

AJ5

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

DDR SYSTEM MEMORY B

SB_RCVENIN#

SB_RCVENOUT#

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_WE#

AJ15

AG17

AG21

M_B_DM0

AF32

M_B_DM1

AK34

M_B_DM2

AK27

M_B_DM3

AK24

M_B_DM4

AJ10

M_B_DM5

AK5

M_B_DM6

AE7

M_B_DM7

AB7

M_B_DQS0

AF34

M_B_DQS1

AK32

M_B_DQS2

AJ28

M_B_DQS3

AK23

M_B_DQS4

AM10

M_B_DQS5

AH6

M_B_DQS6

AF8

M_B_DQS7

AB4

M_B_DQS#0

AF35

M_B_DQS#1

AK33

M_B_DQS#2

AK28

M_B_DQS#3

AJ23

M_B_DQS#4

AL10

M_B_DQS#5

AH7

M_B_DQS#6

AF7

M_B_DQS#7

AB5

M_B_A0

AH17

M_B_A1

AK17

M_B_A2

AH18

M_B_A3

AJ18

M_B_A4

AK18

M_B_A5

AJ19

M_B_A6

AK19

M_B_A7

AH19

M_B_A8

AJ20

M_B_A9

AH20

M_B_A10

AJ16

M_B_A11

AG18

M_B_A12

AG20

M_B_A13

AG15

AH14

AK14

SB_RCVENIN#

AF15

SB_RCVENOUT#

AF14

AH16

Place Test PAD Near to Chip

ascould as possible

M_B_BS#0 11,12

M_B_BS#1 11,12

M_B_BS#2 11,12

M_B_DM[7..0] 11

M_B_DQS[7..0] 11

M_B_DQS#[7..0] 11

M_B_A[13..0] 11,12

M_B_CAS# 11,12

M_B_RAS# 11,12

TP54 TPAD28

M_B_WE# 11,12

71.0GMCH.08U

1 1

A

B

C

71.0GMCH.08U

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size Document Number Rev

A3

D

Date: Sheet

GMCH (3 of 5)

AG1(Alviso) 01

840Monday, October 17, 2005

E

of

Page 9

www.RahasiaLaptop.com

A

4 4

B

2D5V_TVDAC_S0

SCD1U16V2ZY-2GP

C313

C

1D5V_S0

R274

1 2

0R0603-PAD

2D5V_S0 2D5V_ALVDS_S0

R272

1 2

0R0603-PAD

2D5V_S0

R275

1 2

C312

12

0R0603-PAD

12

2D5V_S0 2D5V_TXLVDS_S0

R273

1 2

0R0603-PAD

1D5V_DLVDS_S0

12

C310

SC10U10V5ZY-1GP

12

C309

SCD01U16V2KX-3GP

12

C143

SC4D7U10V5ZY-3GP

D

1D5V_DDRDLL_S0

12

C315

ST100U6D3VBM-9GP

1D5V_PCIE_S0

12

C126

SC10U10V5ZY-1GP

E

1 2

1 2

R160

0R0603-PAD

R142

0R0603-PAD

1D5V_S0

1D5V_S0

12

AC11

VCCSM57

VCCSM58

VTT16

VTT17

R10

12

C216

SCD1U16V2ZY-2GP

12

C330

SCD1U16V2ZY-2GP

2D5V_TXLVDS_S0

V1.8_DDR_CAP4

V1.8_DDR_CAP3

V1.8_DDR_CAP6

B28

A28

AB11

AB10

VCCSM59

VCCSM60

VTT18

VTT19

P10

N10

2D5V_S0

AB9

M10

1D05V_S0

AP8

VCCSM61

VTT20

K10

AG1-910-SB

A27

AM1

AE1

VCCSM62

VCCSM63

VCCSM64

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VTT21

VTT22

VTT23Y9VTT24W9VTT25U9VTT26R9VTT27P9VTT28N9VTT29M9VTT30L9VTT31J9VTT32N8VTT33M8VTT34N7VTT35M7VTT36N6VTT37M6VTT38A6VTT39N5VTT40M5VTT41N4VTT42M4VTT43N3VTT44M3VTT45N2VTT46M2VTT47B2VTT48V1VTT49N1VTT50M1VTT51

J10

SCD47U10V3ZY-GP

R278

1 2

1KR2J-1-GP

DY

D

AE37

W37

U37

R37

N37

L37

VCC3G0

VCC3G1

VCC3G2

1D05V_S0

VCC3G3

VCC3G4

VCCP_GMCH_CAP1

12

J37

VCC3G5

VCC3G6

C325

1D05V_S0

AF20

AP19

AF19

AF18

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

C324

D27

2 1

SSM5818SLPT-GP

DY

SC4D7U10V5ZY-3GP

<Core Design>

Title

Size Document Number Rev

A3

Date: Sheet

C185

1D5V_3GPLL_S0

12

Y27

Y29

Y28

F37

VCCA_3GBG

VCCA_3GPLL2

VCCA_3GPLL0

VCCA_3GPLL1

SCD47U10V3ZY-GP

12

C328

12

C142

SC10U10V5ZY-1GP

2D5V_3GBG_S0 2D5V_S0

12

G37

VSSA_3GBG

G1

VCCP_GMCH_CAP3

VCCP_GMCH_CAP4

VCCP_GMCH_CAP2

12

12

SCD22U16V3ZY-GP

12

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

R153

1 2

0R0603-PAD

1 2

0R0603-PAD

C305

SCD1U16V2ZY-2GP

U38E

71.0GMCH.08U

Route ASSA3GBG gnd from GMCH to

decoupling cap groung lead and

then connect to the gnd plane

C329

SCD22U16V3ZY-GP

12

C210

SC2D2U6D3V3MX-1-GP

GMCH (4 of 5)

AG1(Alviso) 01

940Monday, October 17, 2005

E

1D5V_S0

R253

C184

SCD1U16V2ZY-2GP

of

SCD1U16V2ZY-2GP

C133

2D5V_ALVDS_S0

B22

B21

A21

VCCHV0

VCCHV1

VCCHV2

VCCA_LVDS

VCC17

VCC18

VCC19

VCC20

VCC21

T27

V27

U27

R27

AG1-910-SB

1 2

0R0805-PAD

1 2

0R0805-PAD

1 2

0R0805-PAD

1 2

0R0805-PAD

1 2

SCD1U16V2ZY-2GP

C131

1 2

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

AM37

AH37

AP29

AD28

VCCSM0

VCCSM1

VCCSM2

VCC22

VCC23

VCC24

VCC25

L27

P27

K27

N27

M27

R178

0R0805-PAD

L5

L3

L13

L12

Note: All VCCSM

pins shorted

internally

1 2

C151

SCD1U16V2ZY-2GP

AD27

AC27

AP26

AN26

AM26

AL26

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

J27

J25

K26

K25

H27

H26

12

12

C141

SC10U10V5ZY-1GP

12

C136

SC10U10V5ZY-1GP

12

C226

SC10U10V5ZY-1GP

12

C225

SC10U10V5ZY-1GP

1D5V_DLVDS_S0 1D8V_S3

3 3

H17

D19

G18

F18

E18

F17

E17

D18

C18

H18

VSSA_TVBG

N29

VCCA_TVDACB0

VCC2

C195

M29

VCCA_TVDACB1

VCC3

VCCA_TVBG

VCCA_TVDACC0

VCC4

K29

SCD1U16V2ZY-2GP

VCCD_TVDAC

VCCA_TVDACC1

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

J29

T28

V28

P28

U28

R28

N28

12

C144

SCD1U16V2ZY-2GP

Route ASSATVBG gnd from GMCH to

decoupling cap groung lead and

then connect to the gnd plane

VCC 1D05_S0 for low speed

graphic clock.1D5V_S0 for

high speed clock.default

12

use 1D05V_S0

1D05V_S0

12

C157

SC4D7U6D3V3KX-GP

12

12

C176

SC4D7U6D3V3KX-GP

C172

C145

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

2 2

1 1

VCCA_TVDACA0

VCCA_TVDACA1

VCC0

VCC1

T29

R29

12

12

C154

SCD1U16V2ZY-2GP

VCCDQ_TVDAC

VCC11

M28

B26

VCC12

L28

12

B25

VCCD_LVDS0

VCCD_LVDS1

VCC13

VCC14

K28

C162

1D5V_S0

A25

VCCD_LVDS2

VCC15

J28

H28

SCD1U16V2ZY-2GP

A35

VCC16

G28

AK26

K24

AJ26

VCCSM10

VCC33

K23

AH26

VCCSM11

VCC34

K22

AG26

VCCSM12

VCC35

K21

AF26

VCCSM13

VCC36

W20

AE26

VCCSM14

VCC37

U20

SC10U10V5ZY-1GP

AP25

VCCSM15

VCC38

T20

AN25

VCCSM16

VCC39

K20

VCCSM17

VCC40

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

POWER

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

T18

V19

K19

V18

K18

U19

12

C150

SCD1U16V2ZY-2GP

12

C135

SCD1U16V2ZY-2GP

12

C334

SCD1U16V2ZY-2GP

12

C333

SCD1U16V2ZY-2GP

K17

W18

1D5V_HMPLL_S0

1D5V_DPLLA_S0

1D5V_DPLLB_S0

1D5V_HPLL_S0

1D5V_MPLL_S0

AE24

VCCSM25

VCC48

Note: All VCCSM

SCD1U16V2ZY-2GP

AM12

AL12

AK12

AJ12

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VTT7

VTT8

VTT9

VTT10

L11

P11

N11

M11

12

12

SCD1U16V2ZY-2GP

12

SCD1U16V2ZY-2GP

pins shorted

internally

C323

AH12

AG12

AF12

AE12

AD11

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VTT11

VTT12

VTT13

VTT14

VTT15

T10

K11

V10

U10

W10

R276

1 2

DY

0R3-0-U-GP

R277

1 2

0R0603-PAD

C314

C319

Route VSSA_CRTDAC gnd from GMCH to

decoupling cap ground lead and then

connect to the gnd plane.

12

AE23

AE22

VCCSM26

VCCSM27

VCCH_MPLL1

AC2

AC1

12

C316

SC10U10V5ZY-1GP

AE21

AE20

AE19

AE18

AE17

AE16

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCH_MPLL0

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

F19

B23

C35

AA1

AA2

C317

SC10U10V5ZY-1GP

AE15

AE14

AP13

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

E19

G19

12

C321

SC10U10V5ZY-1GP

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCC_SYNC

VTT0

VTT1

VTT2

VTT3

VTT4

J13

K13

K12

H20

GMCH_VCC_SYNC

SC4D7U6D3V3KX-GP

V11

U11

W11

2D5V_CRTDAC_S0

C318

R163

1 2

0R0402-PAD

Layout Notes: VSSA_CRTDAC

Route caps within 250mil

of Alviso. Route FB

within 3" of Alviso.

AP12

VCCSM46

VTT5

T11

AN12

VCCSM47

VTT6

R11

DY

A

B

C

Page 10

www.RahasiaLaptop.com

A

H29

G29

F29

E29

D29

A29

AC28

AB28

AA28

W28

E28

AN27

AL27

AJ27

AG27

AF27

AB27

AA27

W27

G27

E27

B27

J26

G26

E26

A26

AN24

U38F

4 4

AL24

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

B

V31

U31

T31

R31

P31

N31

M31

L31

K31

J31

H31

G31

F31

E31

D31

AP30

AE30

AC30

AB30

AA30

Y30

C30

AM29

AJ29

AG29

AD29

AA29

W29

V29

U29

P29

L29

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

W31

C

C34

AL33

AF33

AD33

W33

V33

U33

T33

R33

P33

N33

M33

L33

K33

J33

H33

G33

F33

E33

D33

AN32

AJ32

AD32

AC32

AB32

AA32

Y32

C32

A32

AL31

AG31

AD31

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

D

AF36

AE36

AD36

AC36

AB36

AA36

C36

AE35

Y35

W35

V35

U35

T35

R35

P35

N35

M35

L35

K35

J35

H35

G35

F35

E35

D35

B35

AN34

AH34

AD34

AC34

AB34

AA34

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

E

AG37

Y37

V37

T37

P37

M37

K37

H37

E37

AN36

AL36

AJ36

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS

VSS196

VSS195

VSS194

VSS193

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

J24

F24

B24

D24

AJ24

AG24

B36

71.0GMCH.08U

VSS259P2VSS258T2VSS257V2VSS256

VSS255

VSS254

VSS253

VSS252

VSS251A3VSS250C3VSS249

VSS248

VSS247

VSS246

AA3

AB3

AC3

VSS245C4VSS244H4VSS243L4VSS242P4VSS241U4VSS240Y4VSS239

AJ3

VSSALVDS

VSS260L2VSS268J2VSS269G2VSS270D2VSS271

Y1

AL2

AE2

AD2

AH2

AN2

AF4

VSS238

VSS237E5VSS236W5VSS235

VSS234

VSS233B6VSS232J6VSS231L6VSS230P6VSS229T6VSS228

AL5

AP5

AN4

AA6

VSS227

VSS226

VSS225

VSS224G7VSS223V7VSS222

VSS221

VSS220

VSS219

VSS218C8VSS217E8VSS216L8VSS215P8VSS214Y8VSS213

VSS212A9VSS211H9VSS210K9VSS209T9VSS208V9VSS207

AJ6

AE6

AA7

AC6

AK7

AN7

AG7

AL8

AA9

VSS206

VSS205

VSS204

VSS203

VSS202

VSS201

VSS200

VSS199

VSS198

VSS197

J12

L10

F11

Y11

Y10

D10

AE9

AC9

AH9

AN9

H11

AA11

AA10

B12

AJ11

AL11

AF11

AN11

AG11

D12

J14

F14

A14

B14

K14

K15

A16

K16

C15

D16

AJ14

AL14

AG14

H16

AN14

AL16

C17

G17

A18

AJ17

AF17

AN17

J19

U18

T19

C19

H19

W19

AL18

B18

F20

A20

E20

V20

D20

AN19

AG19

G20

C21

AK20

J22

F21

A22

E22

D22

H23

AF21

AN21

AL22

AF23

AH22

1D8V_S3

12

3 3

AD13

AC13

AB13

AD12

AC12

U38H

2 2

71.0GMCH.08U

AB12

VCCSM_NCTF27

VCCSM_NCTF28

VCCSM_NCTF29

VCCSM_NCTF30

VCCSM_NCTF31

12

C322

C181

SC10U10V5ZY-1GP

AD17

AC17

AD16

AC16

AD15

AC15

AD14

AC14

VCCSM_NCTF19

VCCSM_NCTF20

VCCSM_NCTF21

VCCSM_NCTF22

VCCSM_NCTF23

VCCSM_NCTF24

VCCSM_NCTF25

VCCSM_NCTF26

1D05V_S0

Place these Hi-Freq decoupling caps near GMCH

VCCSM_NCTF8

VTT_NCTF14

AC23

R12

VCCSM_NCTF7

VTT_NCTF13

C152

AD23

T12

SCD1U16V2ZY-2GP

VCCSM_NCTF6

VTT_NCTF12

AC24

U12

AD24

VCCSM_NCTF5

VTT_NCTF11

V12

VCCSM_NCTF4

VTT_NCTF10

AC25

W12

12

AD25

VCCSM_NCTF3

VTT_NCTF9

L13

12

SCD1U16V2ZY-2GP

AD19

AC19

AD18

AC18

VCCSM_NCTF15

VCCSM_NCTF16

VCCSM_NCTF17

VCCSM_NCTF18

12

C175

SCD1U16V2ZY-2GP

AD22

AC22

AD21

AC21

AD20

AC20

VCCSM_NCTF9

VCCSM_NCTF10

VCCSM_NCTF11

VCCSM_NCTF12

VCCSM_NCTF13

VCCSM_NCTF14

VTT_NCTF17

VTT_NCTF16

VTT_NCTF15

L12

P12

N12

M12

VCCSM_NCTF2

VTT_NCTF8

AC26

M13

VCCSM_NCTF1

VTT_NCTF7

12

C188

AD26

N13

VCCSM_NCTF0

VTT_NCTF6

C160

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

L18

W17

V17

U17

T17

P17

N17

M17

L17

VCC_NCTF71

VCC_NCTF72

VCC_NCTF73

VCC_NCTF74

VCC_NCTF75

VCC_NCTF76

VCC_NCTF77

VCC_NCTF78

VTT_NCTF5

VTT_NCTF4

VTT_NCTF3

VTT_NCTF2

VTT_NCTF1

VTT_NCTF0

T13

P13

V13

R13

U13

W13

VCC_NCTF70

M18

VCC_NTTF69

N18

Y12

1D05V_S0

W26

V26

U26

T26

R26

P26

N26

M26

L26

P18

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

U21

T21

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF48

P22

N22

M22

L22

W21

V21

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

R22

M23

L23

W22

V22

U22

T22

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

V23

U23

T23

R23

P23

N23

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

W23

T24

R24

P24

N24

M24

L24

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

N25

M25

L25

W24

V24

U24

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

P21

N21

M21

L21

Y20

R20

P20

N20

M20

L20

Y19

R19

P19

N19

M19

L19

Y18

R18

W25

V25

U25

T25

R25

P25

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

NCTF

VSS_NCTF68

VSS_NCTF67

VSS_NCTF66

VSS_NCTF65

VSS_NCTF64

VSS_NCTF63

VSS_NCTF62

VSS_NCTF61

VSS_NCTF60

VSS_NCTF59

VSS_NCTF58

VSS_NCTF57

VSS_NCTF56

VSS_NCTF55

VSS_NCTF54

VSS_NCTF53

VSS_NCTF52

VSS_NCTF51

VSS_NCTF50

VSS_NCTF49

VSS_NCTF48

VSS_NCTF47

VSS_NCTF46

VSS_NCTF45

VSS_NCTF44

VSS_NCTF43

VSS_NCTF42

VSS_NCTF41

VSS_NCTF40

VSS_NCTF39

VSS_NCTF38

VSS_NCTF37

VSS_NCTF36

VSS_NCTF35

VSS_NCTF34

VSS_NCTF33

VSS_NCTF32

VSS_NCTF31

VSS_NCTF30

VSS_NCTF29

VSS_NCTF28

VSS_NCTF27

VSS_NCTF26

VSS_NCTF25

VSS_NCTF24

VSS_NCTF23

VSS_NCTF22

VSS_NCTF21

VSS_NCTF20

VSS_NCTF19

VSS_NCTF18

VSS_NCTF17

VSS_NCTF16

VSS_NCTF15

VSS_NCTF14

VSS_NCTF13

VSS_NCTF12

VSS_NCTF11

VSS_NCTF10

VSS_NCTF9

VSS_NCTF8

VSS_NCTF7

VSS_NCTF6

VSS_NCTF5

VSS_NCTF4

VSS_NCTF3

VSS_NCTF2

VSS_NCTF1

VSS_NCTF0

L14

M14

N14

T14

P14

R14

Y13

AA12

AA13

U14

L15

V14

Y14

W14

AA14

AB14

M15

N15

T15

P15

R15

U15

L16

V15

Y15

W15

AA15

AB15

M16

N16

T16

P16

V16

Y16

R16

U16

W16

Y17

R17

AA16

AB16

AA17

AB17

AA18

AB18

Y21

Y22

Y23

Y24

Y25

R21

AA19

AB19

AA20

AB20

AA21

AB21

AA22

AB22

AA23

AB23

Y26

AA24

AB24