winbond W78958B Technical data

IPME

查询W78958B供应商

W78958B

8-BIT EMULATION MICROCONTROLLER

GENERAL DESCRIPTION

The W78958B is an 8-bit emulation microcontroller that supports emulation for the Winbond W78C51

family of products, including the W78C31, W78C32, W78C51, W78C52, W78C154*, W78C58,

W78C438, and W78C458. It is designed to support real-time (up to 40 MHz) emulation tools, such as

in-circuit emulators (ICEs).

The W78958B is packaged in a 100-pin PQFP and is available in two different types, standard and

advanced. The standard type supports the functions of the W78C31, W78C32, W78C51, W78C52,

W78C154*, and W78C58. The advanced type supports the functions of the W78C438 and W78C458.

Both types can be operated in two modes, normal and emulation. In normal mode, the W78958B runs

freely, like the W78C51 family of products. In emulation mode, which is entered by driving the

ICESET pin high asynchronously, the W78958B stays in the S2 state of the next instruction. In this

mode, the W78958B allows direct access (read/write) to the special function registers (SFRs), the

program counter (PC), and the internal RAM. Also, it allows ICE makers to access the external

program and data memory easily, thereby eliminating the need for glue logic. Moreover, it provides

several signals to facilitate ICE design, including

switching between "internal" and external ROM, ESEL (Emulation address space Select), for

combining the emulation program and data memory in a 128 KB SRAM, and CLKS1 (internal S1

state clock timing signal), for creating the emulation control signals. Once the ICESET pin goes low,

the W78958B will release its internal clock and return to its normal operating mode.

(Internal Program Memory Enable), for

For detailed specifications concerning the W78C31, W78C32, W78C51, W78C52, W78C154*,

W78C58, W78C438, and W78C458, refer to the Functional Description below or to the Winbond

product specifications.

Notes for all W78C154*:

1. W78958B will emulate W78C154 except port1.6 & port1.7 as output mode:

W78958B port1.6 & port1.7 pull-ups

W78C154 port1.6 & port1.7 open drain

2. The specification of W78C154 is exclusive, therefore, the DC characteristics is not fully compatible with W78958B, however

the emulation function is still the same as W78958B.

Publication Release Date: September

1997 - 1 - Revision A3

W78958B

FEATURES

• 8-bit CMOS emulation microcontroller

• Real-time emulation at up to 40 MHz

• Convenient emulation chip for ICE market

• Two types: standard type and advanced type

• Standard type supports emulation for the W78C31, W78C32, W78C51, W78C52, W78C154*, and

W78C58

• Advanced type supports emulation for the W78C438, and W78C458

• In emulation mode, allows direct access to SFRs/PC and internal RAM

• Allows ICE makers to access external program/data memory easily

• Supports switching signals between "internal" and external ROM

• Supports combined emulation program and data memory in a 128 KB SRAM

• Provides internal S1 state clock timing signal for easy creation of the emulation control signals

• Fully static design

• 256-byte on-chip scratchpad RAM

• 64 KB program memory address space in standard type; 1 MB extended program memory address

space in advanced type

• 64 KB data memory address space in standard type; 1 MB extended data memory address space in

advanced type

• Boolean processor

• Six-source, two-level interrupt capability in standard type; eight-source, two-level interrupt capability

in advanced type

• Three 16-bit timer/counters

• One full duplex serial channel

• Built-in power management

• Four 8-bit bidirectional and bit-addressable I/O ports in standard type; four 8-bit bidirectional and

bit- addressable I/O ports and one 8-bit bidirectional but parallel I/O port in advanced type

• Packaged in 100-pin PQFP

− W78958BF-40

- 2 -

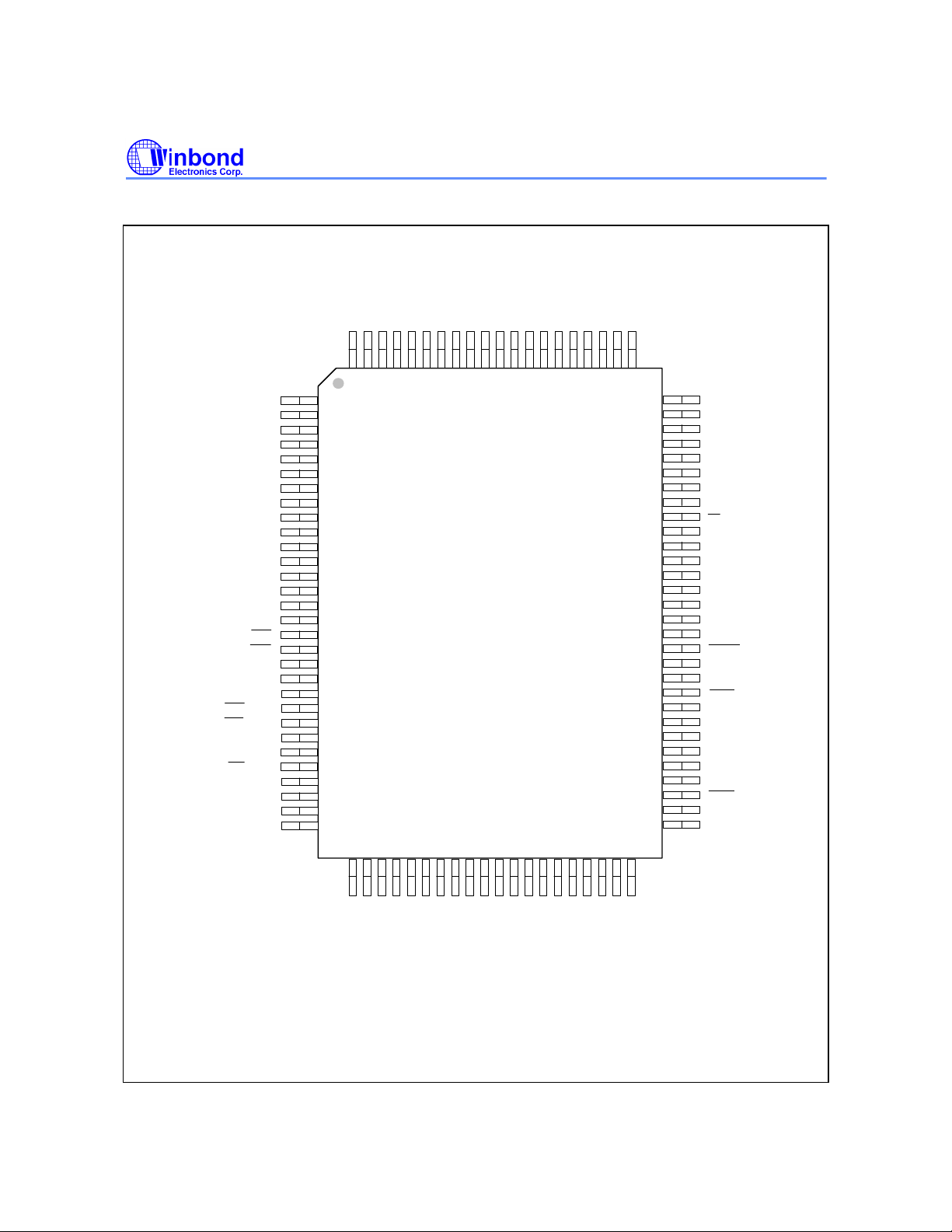

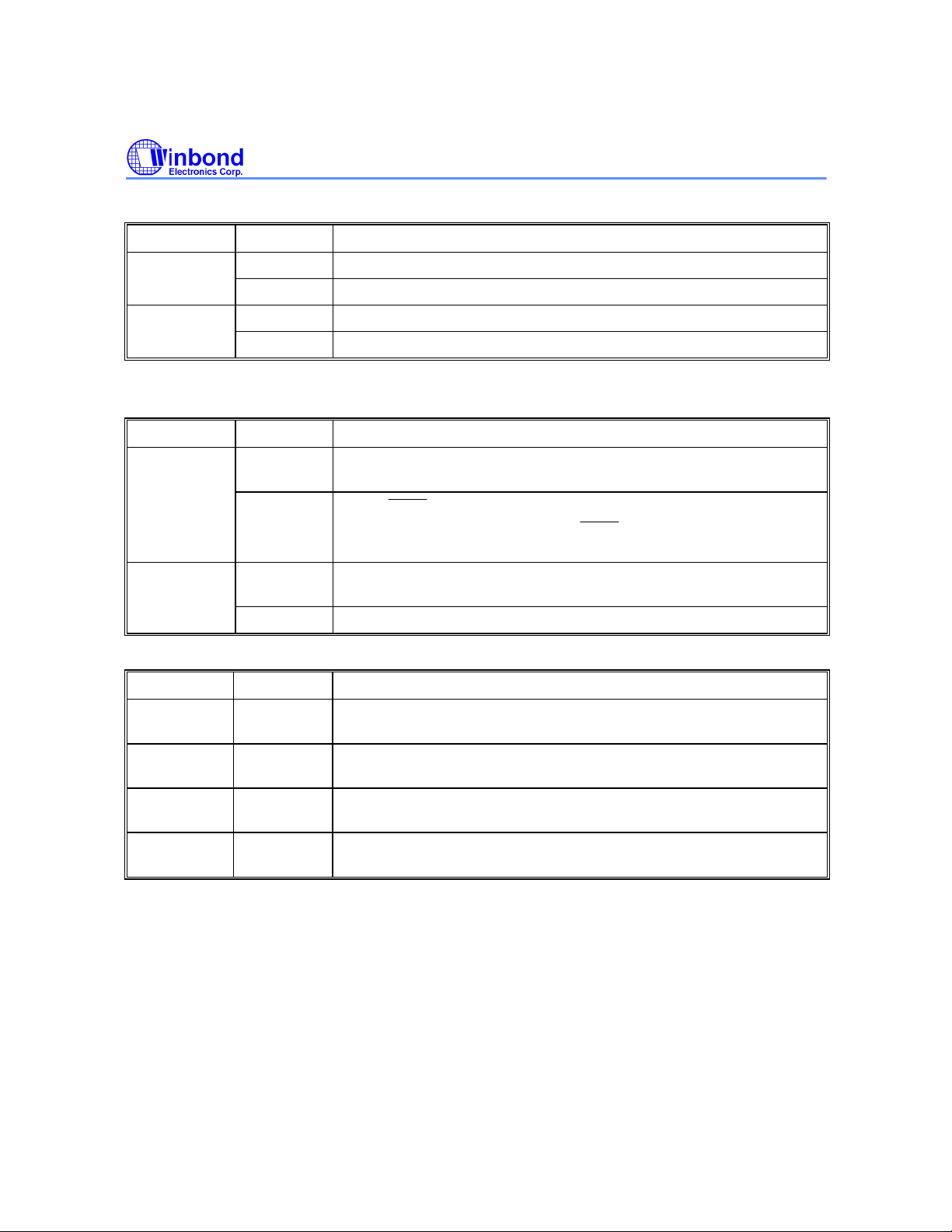

PIN CONFIGURATION

R

3

DNC

NC

NC

W78958B

T

2

T

E

2

X

,

,

P

P

P

P

P

1

N

.

4

C

1

1

1

1

.

.

.

.

0

2

3

1

D

D

D

D

P

P

P

P

4

4

4

4

.

.

.

.

4

5

6

7

D

D

D

D

P

P

4

4

.

.

2

3

P

P

P

P

4

4

.

.

1

0

P

P

0

0

0

V

D

0

.

.

.

.

0

2

1

NC

ICESET

NC

NC

P1.5

P1.6

P1.7

RESET

ROMS0, P8.0

ROMS0, P8.1

P8.2

P8.3

P8.4

P8.5

P8.6

P8.7

INT3

INT2

RXD, P3.0

VDD

TXD, P3.1

INT0, P3.2

INT1, P3.3

T0, P3.4

T1, P3.5

WR, P3.6

NC

NC

EMU

NC

0

0

1

2

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

3 3 3

3 4 5

3 3 363

456789

(100-pin PQFP)

7 8

9

3

W78958BF

3 3

4

4

4 4 4 4 4 4 4 4 5

9 0

1 2 3 4 5 6 7 8

89012

7

6 5 12

8888888889999999991

4

3

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

9

01 2

CLKS1

NC

P0.4

P0.5

P0.6

P0.7

EA

AP5.0

AP5.1

AP5.2

AP5.3

AP5.4

AP5.5

AP5.6

AP5.7

ENSTD

VSS

ALE

PSEN

P2.7

P2.6

P2.5

P2.4

NC

NC

ESEL

NC

P2.3

A

A

A

A

A

A

A

A

A

P

X

3

T

.

A

7

L

,

2

/

R

D

A

X

N

V

P

P

P

P

P

P

T

C

S

7

7

7

A

S

.

.

.

L

1

2

1

3

,

,

,

/

/

/

C

C

C

S

S

S

2

1

3

,

,

,

/

/

/

I

E

I

P

R

P

M

D

S

E

E

N

P

7

6

6

6

.

.

.

.

0

7

6

5

,

/

C

S

0

,

/

E

W

A

A

P

P

P

P

P

P

6

6

6

6

.

.

.

.

4

3

2

1

P

P

2

2

2

6

.

.

.

.

0

1

2

0

Publication Release Date: September 1997

- 3 - Revision A3

W78958B

PSEN

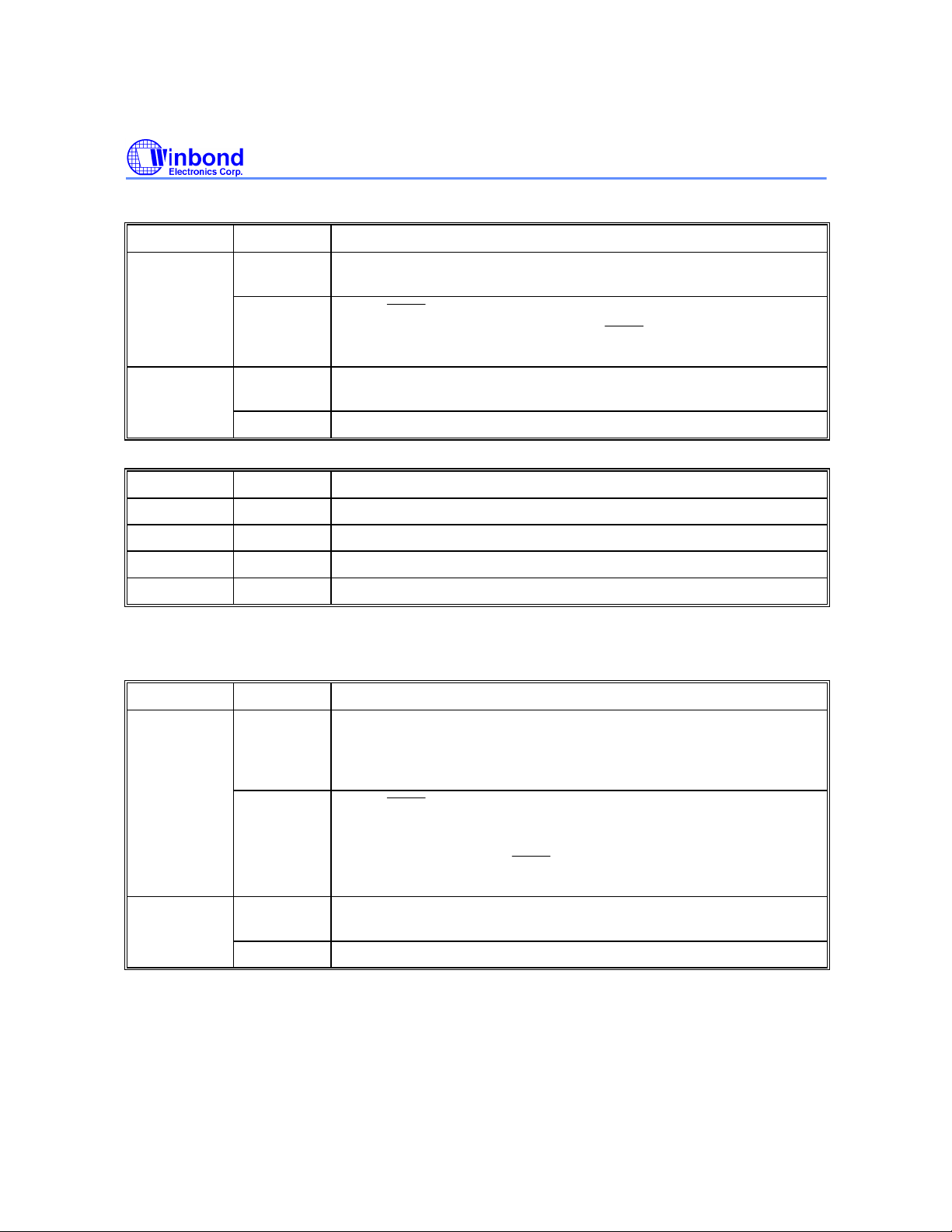

PIN DESCRIPTION

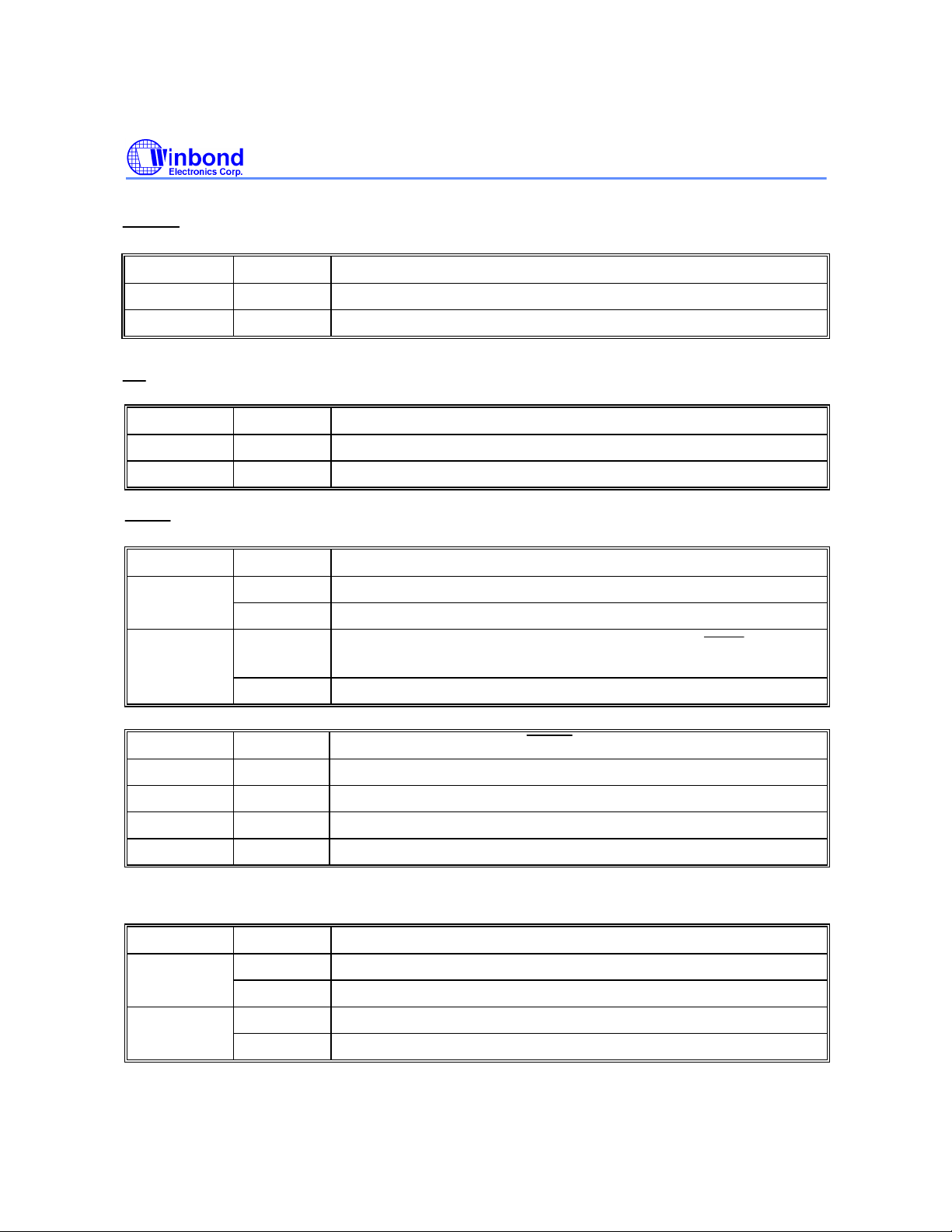

ENSTD Enable Standard Type, Input, Active Low

TYPE MODE DESCRIPTION

Advanced - Default status is pulled high by internal pull-up resistor.

Standard - A low on this pin enables the standard type.

Note: "-" in "Mode" column means that the function description is valid in both modes, normal and emulation.

EA External Address, Input

TYPE MODE DESCRIPTION

Advanced - Functions same as in W78C438.

Standard - Functions same as in W78C51, W78C52, W78C154* or W78C58.

PSEN

TYPE MODE DESCRIPTION

Advanced Normal Functions same as in W78C438.

Emulation In high impedance state.

Standard Normal

Emulation In high impedance state.

ROMS1 ROMS0 FUNCTION of

0 0 Same as in the W78C51 (verify 4K ROM).

0 1 Same as in the W78C52 (verify 8K ROM).

1 0 Same as in the W78C154* (verify 16K ROM).

1 1 Same as in the W78C58 (verify 32K ROM).

Pins ROMS1 and ROMS0 determine the function of

details, see Table D1 below.

PSEN

Table D1.

ALE

TYPE MODE DESCRIPTION

Advanced Normal Functions same as in W78C32.

Emulation In high impedance state.

Standard Normal Functions same as in W78C52.

. For

, PORT 0, AND PORT 2

Emulation In high impedance state.

- 4 -

W78958B

ESEL

ESEL

RST, XTAL1, XTAL2

TYPE MODE DESCRIPTION

Advanced - Functions same as in W78C32.

Standard - Functions same as in W78C52.

P0.7−P0.0 Port 0, Bits 7−0

TYPE MODE DESCRIPTION

Advanced Normal Functions are the same as those in the W78C32, except that a

multiplexed address/data bus is not provided during accesses to

external memory.

Emulation Frozen in the original state.

Standard Normal

Emulation

Pins ROMS1 (P8.1) and ROMS0 (P8.0) determine functions of P0.7−

P0.0. For details, see Table D1.

When

is held at "H" level, P0.7−P0.0 are floating.

P1.7−P1.0 Port 1, Bits 7−0

TYPE MODE DESCRIPTION

Advanced Normal Functions are the same as those in the W78C32.

Emulation Frozen in the original state.

Standard Normal Functions are the same as those in the W78C52.

Emulation Frozen in the original state.

P2.7−P2.0 Port 2, Bits 7−0

TYPE MODE DESCRIPTION

Advanced Normal Functions are the same as those in the W78C32, except that a high-

byte address bus is not provided during accesses to external

memory.

Emulation Frozen in the original state.

Standard Normal

Pins ROMS1 and ROMS0 determine functions of P2.7−P2.0. For

details, see Table D1.

Emulation

When

the MP2 (Mask Port 2) register. At this time, if the bit content of MP2

is 0, the corresponding pin of Port 2 maintains in the original state;

otherwise, the corresponding pin of Port 2 is in high impedance state.

is held at "H" level, the states of P2.7−P2.0 depend on

Publication Release Date: September 1997

- 5 - Revision A3

P3.7−P3.0 Port 3, Bits 7−0

ESEL

ESEL

TYPE MODE DESCRIPTION

Advanced Normal Functions are the same as those in the W78C32.

Emulation Frozen in the original state.

Standard Normal Functions are the same as those in the W78C52.

Emulation Frozen in the original state.

DP4.7−DP4.0 Address/Data Bus, Bits 7−0

TYPE MODE DESCRIPTION

Advanced Normal DP4 provides a multiplexed low-byte address/data bus during

accesses to external memory.

W78958B

Emulation

Standard Normal Pins ROMS1 and ROMS0 determine functions of DP4. For details,

Emulation Same as in the advanced type.

ROMS1 ROMS0 FUNCTIONS OF DP4

0 0 Provides a multiplexed low-byte address/data bus during accesses to

0 1 Provides a multiplexed low-byte address/data bus during accesses to

1 0 Provides a multiplexed low-byte address/data bus during accesses to

1 1 Provides a multiplexed low-byte address/data bus during accesses to

When

SFR/PC and internal RAM. When

in high impedance state.

see Table D2.

external 4 KB EPROM.

external 8 KB EPROM.

external 16 KB EPROM.

external 32 KB EPROM.

is held at "L" level, DP4 is the data input/output of the

Table D2.

is held at "H" level, DP4 is

- 6 -

W78958B

ESEL

ESEL

ESEL

ESEL

AP5.7−AP5.0 Address Bus, Bits 7−0

TYPE MODE DESCRIPTION

Advanced Normal AP5<7:0> output the <7:0> address of the external ROM multiplexed

with the <7:0> address of the external data RAM.

Emulation

Standard Normal Pins ROMS1 and ROMS0 determine functions of AP5. For details,

Emulation Same as in the advanced type.

ROMS1 ROMS0 FUNCTIONS of AP5

0 0 AP5 output the <7:0> address of the external 4K EPROM.

0 1 AP5 output the <7:0> address of the external 8K EPROM.

1 0 AP5 output the <7:0> address of the external 16K EPROM.

1 1 AP5 output the <7:0> address of the external 32K EPROM.

When

the SFR/PC and internal RAM. When

is in high impedance state.

see Table D3.

is held at "L" level, AP5 is the low-byte address input for

Table D3.

is held at "H" level, AP5

AP6.7−AP6.0 Address Bus, Bit 15−8

TYPE MODE DESCRIPTION

Advanced Normal AP6<7:0> output the <15:8> address of the external ROM

multiplexed with the <15:8> address of the external data RAM.

During the execution of "MOVX @Ri," AP6's output comes from the

HB register, which is the page register for the high byte address.

Emulation

Standard Normal Pins ROMS1 and ROMS0 determine functions of AP6. For details,

Emulation Same as in the advanced type.

When

accesses to the SFR/PC and internal RAM. At this time, if AP6<0> =

0, the SFR/PC can be accessed; if AP6<0> = 1, the internal RAM

can be accessed. When

impedance state.

see Table D4.

is held at "L" level, AP6<0> is the address input for the

is held at "H" level, AP6 is in high

Publication Release Date: September 1997

- 7 - Revision A3

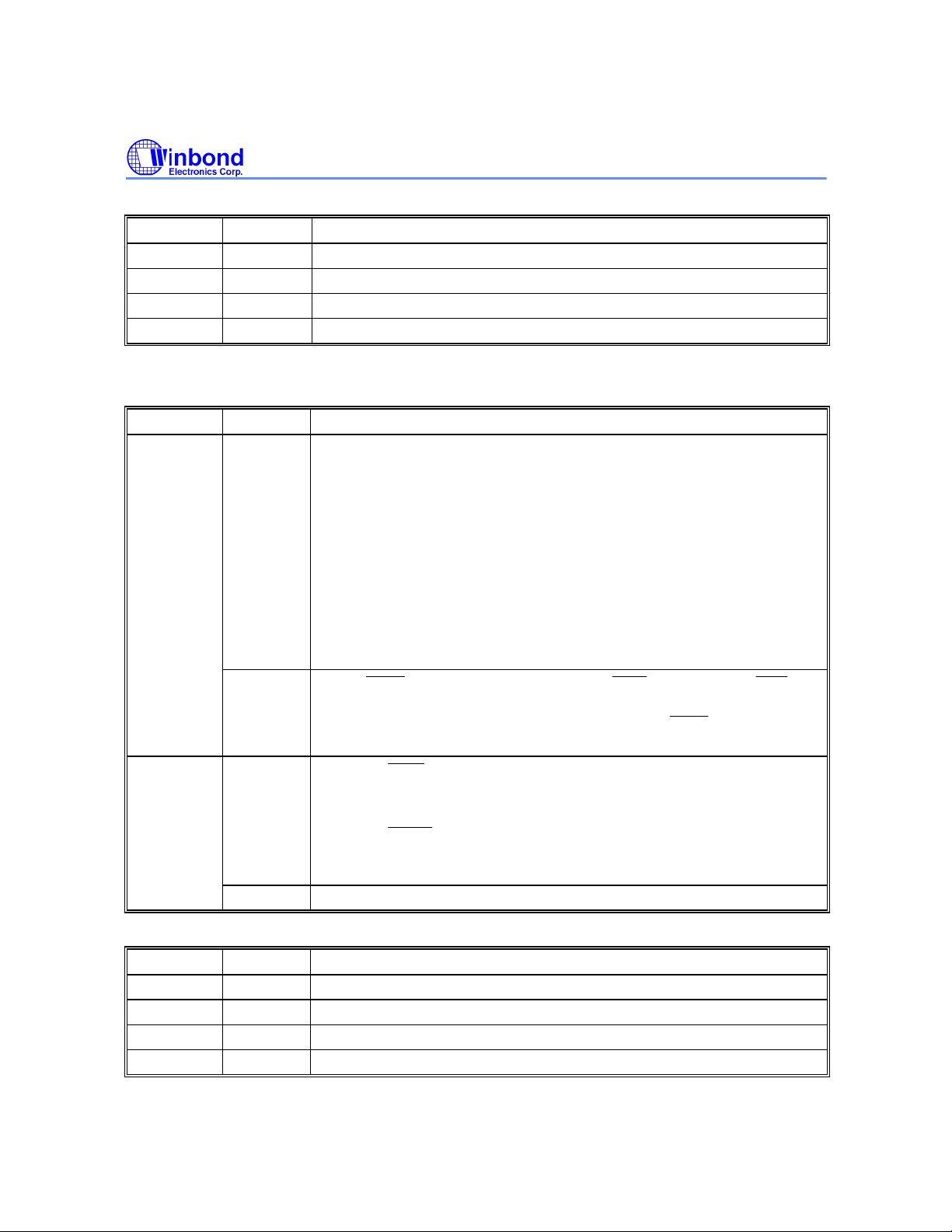

ROMS1 ROMS0 FUNCTIONS OF AP6

ESEL

EWR

ERD

ESEL

IPME

IPSEN

0 0 AP6<3:0> output the <11:8> address of the external 4K EPROM.

0 1 AP6<4:0> output the <12:8> address of the external 8K EPROM.

1 0 AP6<5:0> output the <13:8> address of the external 16K EPROM.

1 1 AP6<6:0> output the <14:8> address of the external 32K EPROM.

Table D4.

AP7.3−AP7.0 Address Bus, Bit 3−0, Input/Output, Dual-purpose

TYPE MODE DESCRIPTION

Advanced Normal Bit 7 of EPMA (Extended Program Memory Address) register

determines functions of AP7<3:0>.

When this bit is "0" (default value), AP7 outputs the <19:16> address of

the external ROM from bits <3:0> of EPMA register during the

execution of "MOVC A,@A+DPTR" to read the external ROM data, the

execution of "MOVX A,@DPTR" to read the external RAM data, or the

execution of "MOVX @DPTR,A" to write the external RAM data.

Excluding those times, AP7<3:0> output 0H.

When this bit is "1," AP7<3:0> (CS3−0) are the output pins to support

memory-mapped peripheral chip select, and only one of them is active

low at any time. These pins are decoded by AP6<7:6>. For details, see

Table D5.

Emulation

Standard Normal

When

are the write and read control input signals, respectively, for the

accesses to the SFR/PC and internal RAM. When

state, AP7<3:0> are in high impedance state.

AP7<2> (

outputs "0" to indicate that the access buses are DP4, AP5 and AP6. It

outputs "1" to indicate that the access buses are Port 0 and Port 2.

is held in "L" state, AP7<0> (

) is the "internal" program memory enable signal. It

) and AP7<1> (

W78958B

)

is held in "H"

AP7<3> (

outputs "0" to enable the "internal" program memory onto the DP4

address/data bus during fetch and MOVC operations.

Emulation Same as in the advanced type.

AP6.7 AP6.6 DESCRIPTION

0 0 AP7.0: low; others: high

0 1 AP7.1: low; others: high

1 0 AP7.2: low; others: high

1 1 AP7.3: low; others: high

) is the "internal" program store output enable signal. It

Table D5.

- 8 -

W78958B

INT 3

INT

3

INT

3

INT 2

INT 2

INT 2

P8.7−P8.0 Port 8, Bits 7−0, Input/Output

TYPE MODE DESCRIPTION

Advanced Normal Functions are the same as those of Port 1 in the W78C31, except

that they are mapped by the P8 register and not bit-addressable. The

P8 register is not a standard register in the W78C32. Its address is at

0A6H.

Emulation Frozen in the original state.

Standard Normal P8.1 (ROMS1, standard type ROM size Select 1) and P8.0 (ROMS0)

are the input pins that determine which of four different ROM sizes is

being used: 4K, 8K, 16K, or 32K bytes. For details, see Table D1−

D4.

Emulation Frozen in the original state.

INT2 and INT3 External Interrupt 2 and 3, Input

TYPE MODE DESCRIPTION

Advanced Normal Functions are similar to those of external interrupt 0 and 1 in the

W78C31, except that the functions/status of these interrupts are

determined/shown by the bits in the XICON (External Interrupt

Control) register. For details, see Table D6. The XICON register is

bit-addressable but is not a standard register in the W78C32. Its

address is at 0C0H. The interrupt vector addresses and the priority

polling sequence within the same level are shown in Table D7.

Emulation Frozen in the original state.

Standard - Not supported.

BIT ADDR. NAME FUNCTION

7 0C7H PX3

6 0C6H EX3

5 0C5H IE3 If IT3 is "1," IE3 is set/cleared automatically by hardware when

4 0C4H IT3

3 0C3H PX2

2 0C2H EX2

1 0C1H IE2 If IT2 is "1," IE2 is set/cleared automatically by hardware when

0 0C0H IT2

High/low priority level for

set/cleared by software.

Enable/disable interrupt from

software.

interrupt is detected/serviced.

is falling-edge/low-level triggered when this bit is set/cleared by

software.

High/low priority level for

set/cleared by software.

Enable/disable interrupt from

software.

interrupt is de0tected/serviced.

is falling-edge/low-level triggered when this bit is set/cleared

by software.

Table D6. Functions of XICON Register.

- 9 - Revision A3

is specified when this bit is

when this bit is set/cleared by

is specified when this bit is

when this bit is set/cleared by

Publication Release Date: September 1997

Loading...

Loading...