WELTREND WT8043N24, WT8043N20P8, WT8043N20P7, WT8043N20P4, WT8043N20P1 Datasheet

...

WT8043

Synchronous Signal discriminator

for Multi-Sync Display Monitor

Jan. 30, 1996

Description

The WT8043 is a silicon monolithic circuit designed for synchronous signal

processing of multi-sync display monitors capable of coping with many kinds of PC's

and workstations. It can be applied to display monitors supporting standard IBM

VGA, VESA super VGA and IBM 8514/A video modes. It can also be used in other

high-end display monitors supporting non-standard video modes with user-defined

horizontal/vertical frequency ranges.

WT8043 incorporates many functional circuits, horizontal/vertical frequency

discrimination, display mode selection, and synchronous pulse polarity detection, into

a single chip. Therefore, by using WT8043, monitor makers can shrink the PC board

size, reduce the material cost with fewer components, and reduce labor cost as well.

Features

• Accepting separate H&V Synchronous signals with any polarities

• Support VESA VGA (640x480, 640x400, 640x350), VESA SVGA (800x600),

European SVGA (800x600), VESA new SVGA (800x600), XGA (1024x768)

and 1280x1024.

• Also including NEC (24K) mode, 3 VESA New 75Hz timing modes and Apple

MAC II (35k) mode.

• Capable of processing horizontal frequency from 25KHz to 80KHz

• Capable of processing vertical frequency from 50Hz to 120Hz

• Standard IBM video mode control outputs (1024x768, 640x480, 640x400,

640x350)

• Six non-standard horizontal frequency control outputs with predefined frequency

range. (users can define their own horizontal frequency range)

• Fixed polarity horizontal and vertical synchronous signals output

• Power supply voltage: 5V, but mode select control output and frequency

discrimination control output, these open collector outputs can be combined with

pull high resistor, pull up to 12V.

Application

• Auto size control for Multi-Sync Display Monitors

Weltrend Semiconductor, Inc.

2F., No. 24, Industry E. 9th Rd.

Science-Based Industrial Park

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-35-780241

Fax: 886-35-770419

1

WT8043

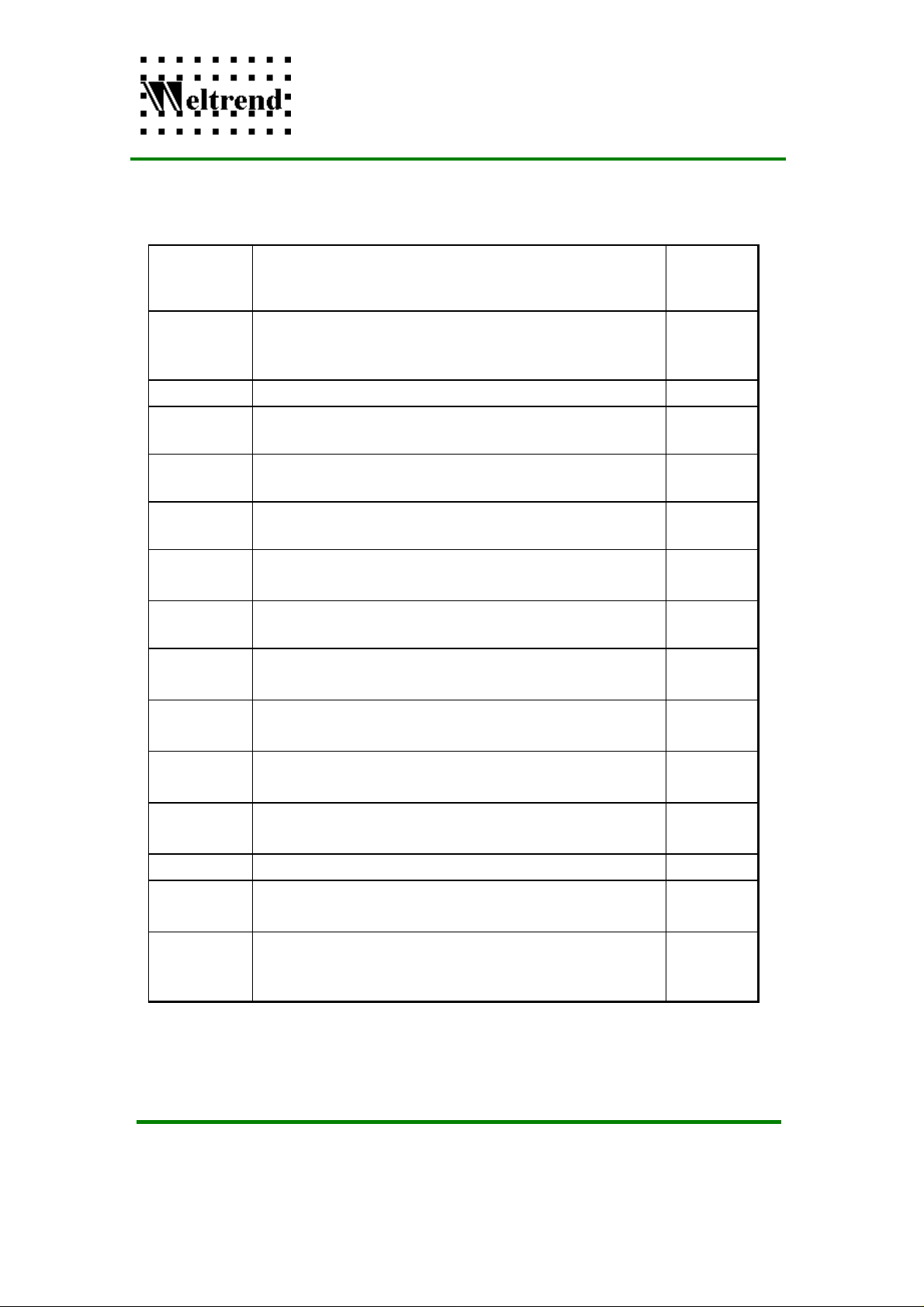

Ordering Information

Part No.

WT8043N16 WT8043N20P1 WT8043N20P4 WT8043N20P7 WT8043N20P8 WT8043N24

Package P-DIP 16L P-DIP 20L P-DIP 20L P-DIP 20L P-DIP 20L

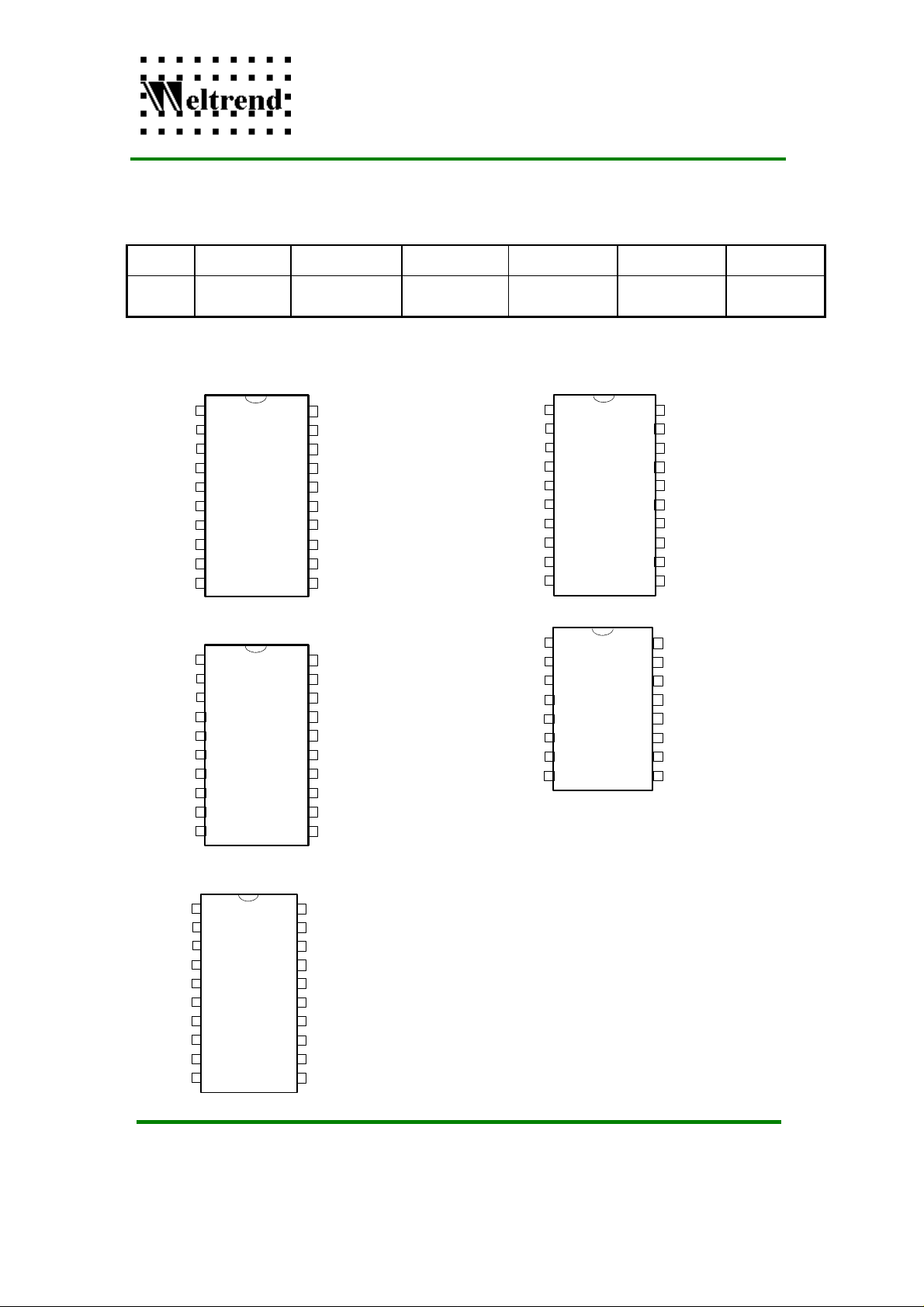

Pin Configuration

HSin

VSin

F45K

F36K

Vss

F33K

HSin

VSin

F36K

Vss

WT8043N20P8

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

WT8043N16

1

2

3

4

5

6

7

8 9

16

15

14

13

12

11

10

VDD

1024x768(60K,75)

1024x768(57K)

1024x768(I)

800x600(48K)

800x600(46.8K,75)

800x600(37.5K)

640x480

640x400

640x350

VDD

1024x768 (I)

800x600(37.5K)

800x600(35K)

640x480

640x400

640x350

F33K

OSCin

OSCout

HSin

VSin

H_out

V_out

F52K

F45K

F36K

Vss

OSCin

OSCout

HSin

VSin

H_out

V_out

F45K

F36K

Vss

F33K

WT8043N20P1

1

2

3

4

5

6

7

8

9

10 11

20

19

18

17

16

15

14

13

12

WT8043N20P4

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

14

12

11

15

13

VDD

1024x768(57K)

1024x768 (NI)

1024x768 (I)

800x600(48K)

800x600(37.5K)

800x600(35K)

640x480

640x400

640x350

VDD

1024x768(57K)

1024x768 (NI)

1024x768 (I)

800x600(48K)

800x600(37.5K)

800x600(35K)

640x480

640x400

640x350

OSCin

OSCout

H_out

V_out

OSCin

OSCout

H_out

V_out

P-DIP 24L

(skinny type)

OSCin

OSCout

HSin

VSin

H_out

V_out

F52K

F45K

F36K

Vss

WT8043N20P7

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VDD

1024x768(57K)

1024x768 (NI)

1024x768 (I)

800x600(48K)

800x600(37.5K)

800x600(35K)

640x480

640x400

NEC

Weltrend Semiconductor, Inc.

2F., No. 24, Industry E. 9th Rd.

Science-Based Industrial Park

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-35-780241

Fax: 886-35-770419

2

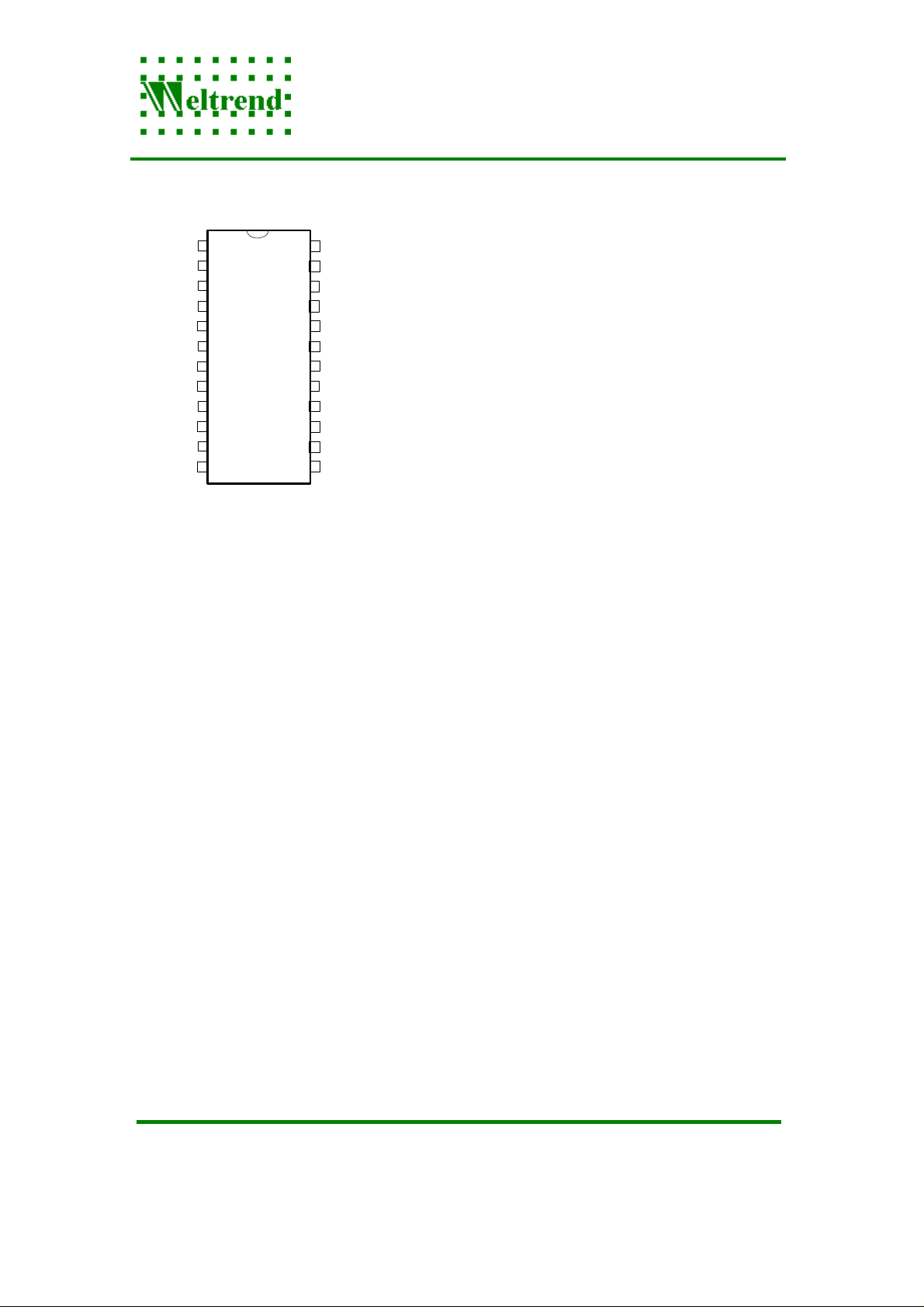

WT8043

WT8043N24

OSCin

OSCout

HSin

VSin

H_out

1280x1024

(64k)

V_out

F60K

F52K

F45K

F36K

Vss F33K

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VDD

F72K

1024x768(57K)

1024x768 (NI)

1024x768 (I)

800x600(48K)

800x600(37.5K)

800x600(35K)

640x480

640x400

640x350

Weltrend Semiconductor, Inc.

2F., No. 24, Industry E. 9th Rd.

Science-Based Industrial Park

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-35-780241

Fax: 886-35-770419

2

WT8043

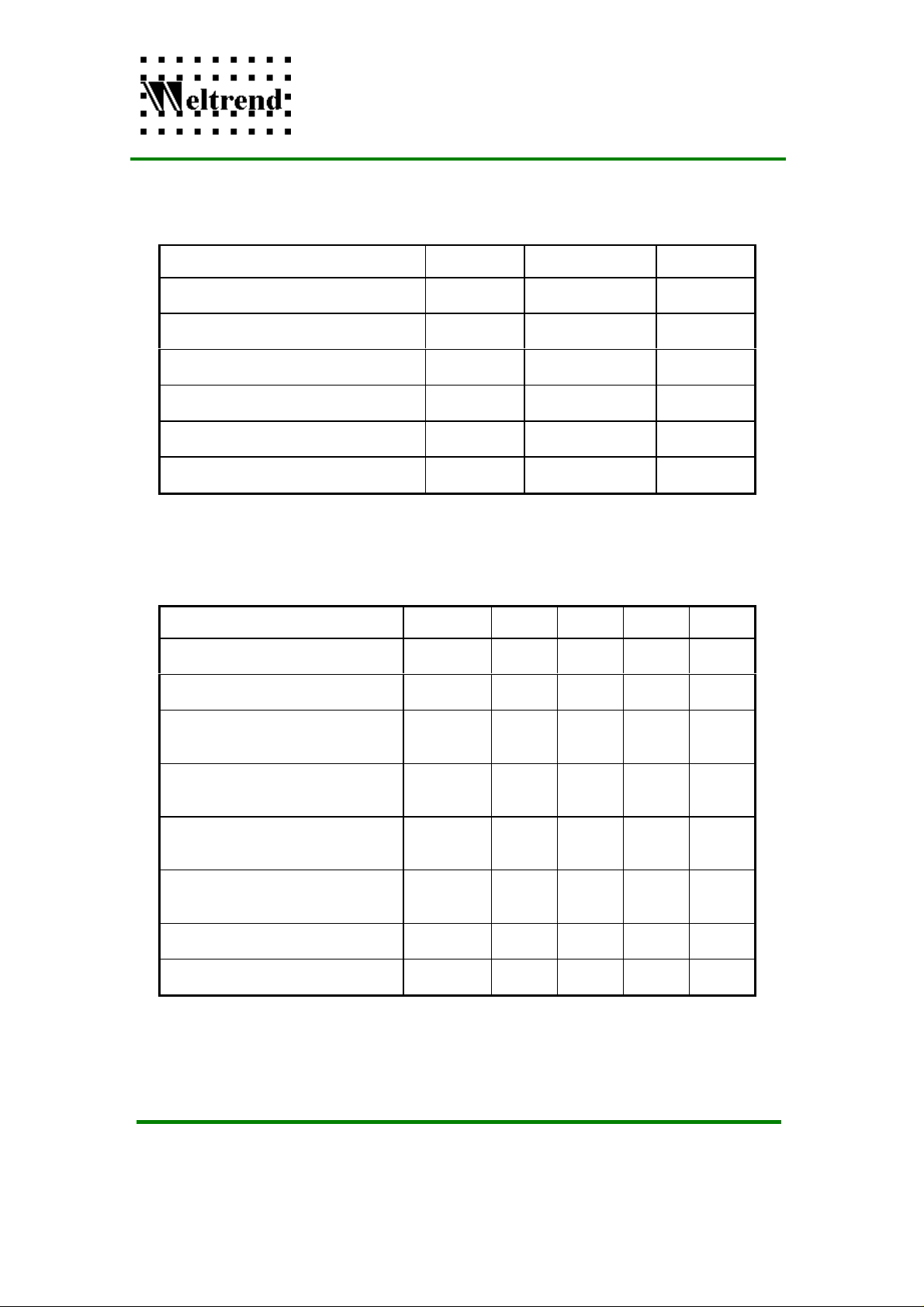

Absolute Maximum Ratings

Item Symbol Value Unit

Digital Supply Voltage V

Horizontal Sync. Input Voltage

DD

V

Vertical Sync. Input Voltage V

Power Dissipation P

Operating Temperature Range

Storage Temperature Range T

T

OPT

STG

Recommended Operating Conditions

Item Symbol Min. Typ. Max. Unit

Digital Supply Voltage V

Supply Current (Oscillator on) I

Synchronous Input Voltage

Low

(5) 4.5 5 5.5 V

DD

P

V

IL

HS

VS

D

5.5 V

VDD(5)+0.3

V

VDD(5)+0.3 V

300 mW

0~70

-40~125

°C

°C

0.8 V

mA

Synchronous Input Voltage

High

Horizontal Synchronous

Frequency Range

Vertical Synchronous

Frequency Range

Crystal Clock Frequency

F

Open Drain Pull High Voltage V

Weltrend Semiconductor, Inc.

2F., No. 24, Industry E. 9th Rd.

Science-Based Industrial Park

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-35-780241

Fax: 886-35-770419

V

IH

F

H

F

V

CLK

OH

2.4 4 5.0 V

25 - 80 KHz

50 - 120 Hz

3.5764 3.58 3.5836 MHz

8 12 V

3

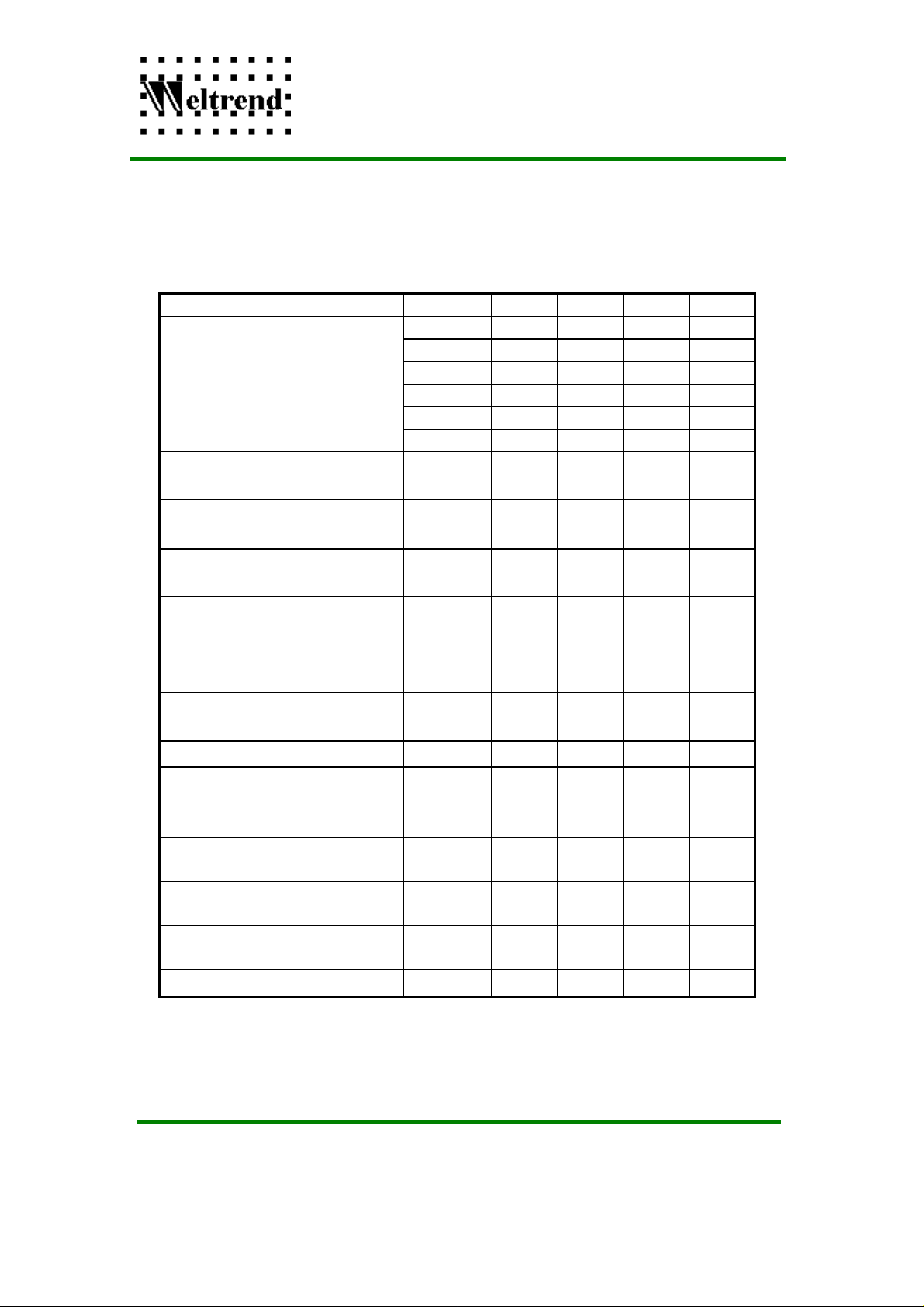

WT8043

Electrical Characteristics

(VDD=5V, T

=25°C, Crystal=3.58MHz)

OPT

Item Symbol Min. Typ. Max. Unit

F33K 32.95 - 33.05 KHz

F36.2K 36.15 - 36.25 KHz

Discrimintaion of H. F45K 44.95 - 45.05 KHz

Synchronous Frequency F52K 51.95 - 52.05 KHz

F62K 61.95 - 62.05 KHz

F72K 71.95 - 72.05 KHz

Output Low (H-out, V-out)

When I

OL

= 4mA

Output High (H-out, V-out)

When I

= -400µA

OH

Open Collector Output Low

When I

OL

= 6mA

Output Sink Current (H-out,

V-out) When V

OL1

= 0.4V

Output Drive Current (H-out,

V-out) When V

OH1

= 2.4V

Open Drain Sink Current

When V

OL2

= 0.4V

Input H_SYNC Pulse Width W

Input V_SYNC Pulse Width W

H_SYNC, Output Pulse delay,

V

OL1

V

OH1

V

OL2

I

OL1

¡ýI

OH1

I

OL2

H_SYNC

V_SYNC

T

DHS

0.4 V

2.4 V

0.4 V

4 mA

¡ý 400

6 mA

0.56 4

0.56 833

60 nS

respect to Hsin

V_SYNC, Output Pulse delay,

T

VHS

60 nS

respect to Vsin

Upper Trigger Input Point

V

UTP

2.0 V

(H_IN, V_IN)

Lower Trigger Input Point

V

LTP

0.8 V

(H_IN, V_IN)

Noise Margin (H_IN, V_IN)

V

NM

1.75 V

µA

µS

µS

Weltrend Semiconductor, Inc.

2F., No. 24, Industry E. 9th Rd.

Science-Based Industrial Park

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-35-780241

Fax: 886-35-770419

4

WT8043

Application Information

Structure

Name Function of

Terminal

OSCin A clock generating circuit is built into the chip. So if

a resonator is connected to OSCin / OSCout, a clock

signal can be obtained

OSCout

HSin Input terminal of horizontal synchronous Signal I, TTL

VSin Input terminal of vertical synchronous Signal I, TTL

H_out Output pin, active low, fixed polarity of original

1280 x 1024 1280x1024 mode control output O,

V_OUT

Referent to OSCin pin

H_sync signal w/ same pulse width

Output pin, active low, fixed polarity of original

V_sync signal w/ same pulse width

Compatible

Compatible

O, TTL

Compatible

open drain

O, TTL

Compatible

I

F60K H, frequency input 60k discrimination > 60k then

active low, < 60k then high

O,

open drain

F52K > 52k then active low, < 52k then high O,

open drain

F45K > 45k then active low, < 45k then high O,

open drain

F36K > 36k then active low, < 36k then high O,

open drain

Vss Ground

F33K > 33k then active low, < 33k then high O,

open drain

640 x 350 Mode seclect control output, if IBM VGA 640x350

mode, or VESA VGA 640x350 mode, then active

O,

open drain

low, else high state output

Weltrend Semiconductor, Inc.

2F., No. 24, Industry E. 9th Rd.

Science-Based Industrial Park

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-35-780241

Fax: 886-35-770419

5

Loading...

Loading...