Weltrend WT7525-N140, WT7525-N160, WT7525-N161, WT7525-N180, WT7525-N181 Schematic [ru]

...

偉詮電子股份有限公司

Weltrend Semiconductor, Inc.

`

WT7525

PC POWER SUPPLY SUPERVISOR

Data Sheet

REV. 0.40 Preliminary release

February 21, 2005

The information in this document is subject to change without notice.

Weltrend Semiconductor, Inc. All Rights Reserved.

新竹市科學工業園區工業東九路24號2樓

2F, No. 24, Industry E. 9th RD., Science-Based Industrial Park, Hsin-Chu, Taiwan

TEL:886-3-5780241 FAX:886-3-5794278.5770419

Email:support@weltrend.com.tw

WT7525 Preliminary release

Rev. 0.40

GENERAL DESCRIPTION

The WT7525 provides protection circuits, power good output (PGO), fault protection latch (FPOB),

and a protection detector function (PSONB) control. It can minimize external components of switching

power supply systems in personal computer.

The Over / Under Voltage Detector (OVD / UVD) monitors V33, V5, V12A, V12B and V12C input

voltage level. The Over Current Detector (OCD) monitor IS33, IS5, IS12A, IS12B and IS12C input

current sense. When OVD or UVD or OCD detect the fault voltage level, the FPOB is latched HIGH and

PGO go low. The latch can be reset by PSONB go HIGH. There is 3.5 ms delay time for PSONB turn

off FPOB.

When OVD and UVD and OCD detect the right voltage level, the power good output (PGO) will be

issue.

FEATURES

• The Over/Under Voltage Detector (OVD / UVD) monitors V33, V5, V12A, V12B and V12C input

voltage.

• The Over Current Detector (OCD) monitors IS33, IS5, IS12A, IS12B and IS12C input current sense.

• Both of the power good output (PGO) and fault protection latch (FPOB) are Open Drain Output.

• 75 / 300 ms time delay for UVD.

• 300 ms time delay for PGO.

• 38 ms for PSONB input signal De– bounce.

• 73 us for PGI/OVD/UVD internal signal De– glitches.

• 1.2 ms for OCD internal signal De–glitches.

• 3.5 ms time delay for PSONB turn-off FPOB.

Weltrend Semiconductor, Inc.

Page 2

WT7525 Preliminary release

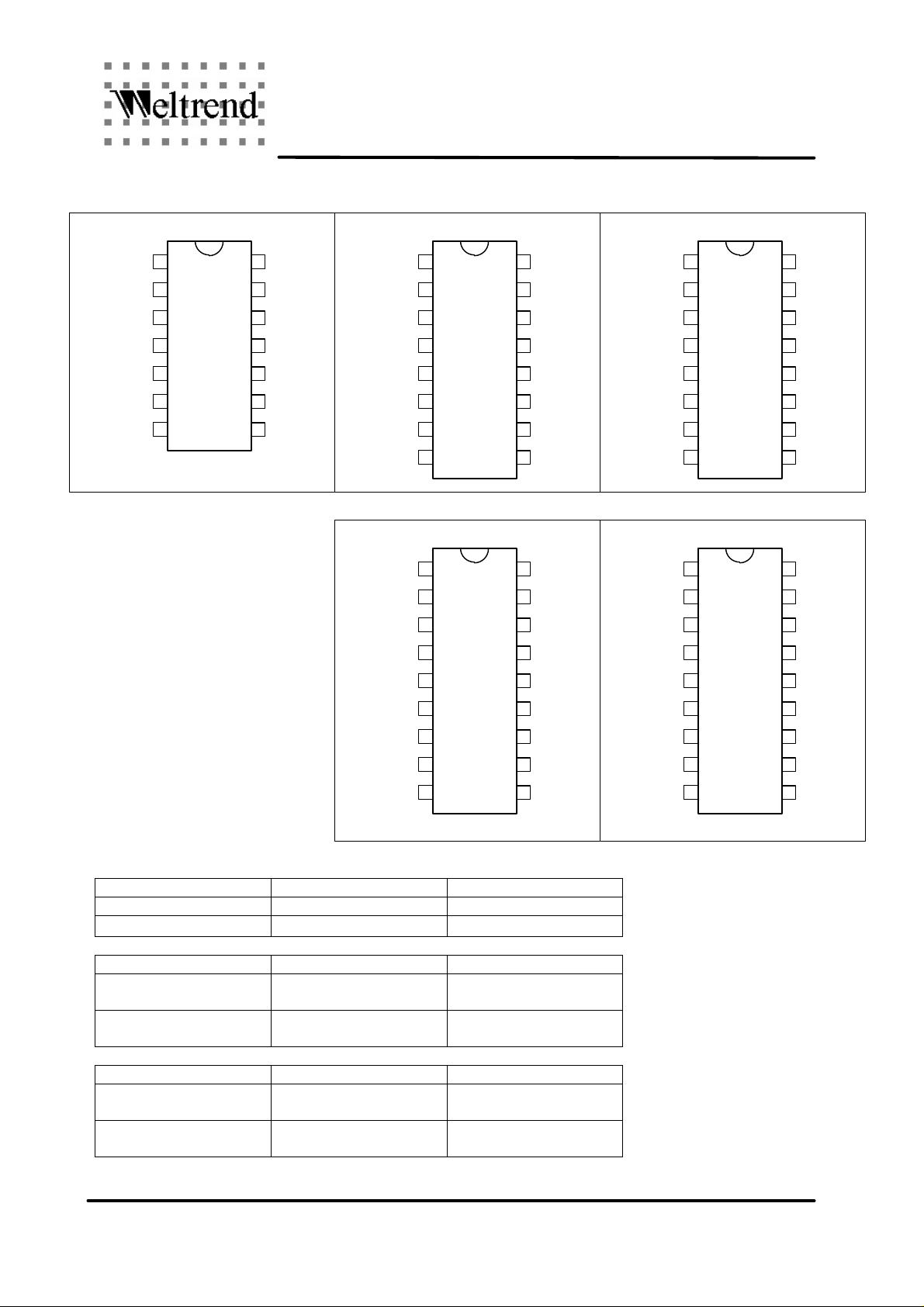

ORDERING INFORMATION

PGI

GND

FPOB

PSONB

ARINC

V12B

15 14 13 12 11 10

2 3 4 5 6 7

WT7525

-

160

PGI

GND

FPOB

PSONB

ABRIV12B

1413121110981 2 3 4 5 6

WT7525

-

140

PGI

GND

FPOB

PSONB

ARII5

V12B

15 14 13 12 11 10

2 3 4 5 6 7

WT7525

-

161

PGI

GND

FPOB

PSONB

A

RII5

V12B

V12C

17 16 15 14 13 12 11

2 3 4 5 6 7 8

WT7525

-

181

I

GND

FPOB

PSONB

ARINC

V12B

V12C

17 16 15 14 13 12 11

2 3 4 5 6 7 8

WT7525

-

180

Rev. 0.40

PIN ASSIGNMENT AND PACKAGE TYPE

16

I12

PGO

VCC

V5

V33

V12A

I33

7

I5

I12

1

9

8

PGO

VCC

V5

V33

V12A

I33

I5

I12B

I12

16

1

9

8

PGO

VCC

V5

V33

NC

V12A

I33

I12B

18

PG

I12

PACKAGE 14–Pin Plastic DIP 14–Pin Plastic SOP

WT7525–N140 WT7525–S140

Lead–Free(Pb)

PACKAGE 16–Pin Plastic DIP 16–Pin Plastic SOP

Lead–Free(Pb)

PACKAGE 18–Pin Plastic DIP 18–Pin Plastic SOP

Lead–Free(Pb)

※ The Top-Side Marking would be added a dot(●)in the right side for lead-free package.

WT7525–N140 Pb WT7525–S140 Pb

WT7525–N160

WT7525–N161

WT7525–N160 Pb

WT7525–N161 Pb

WT7525–N180

WT7525–N181

WT7525–N180 Pb

WT7525–N181 Pb

1

10

9

WT7525–S160

WT7525–S161

WT7525–S160 Pb

WT7525–S161 Pb

WT7525–S180

WT7525–S181

WT7525–S180 Pb

WT7525–S181 Pb

PGO

VCC

V5

V33

V12A

I33

I5

I12B

I12C

I12

1

9

18

10

PGO

VCC

V5

V33

NC

V12A

I33

I12B

I12C

Weltrend Semiconductor, Inc.

Page 3

WT7525 Preliminary release

Rev. 0.40

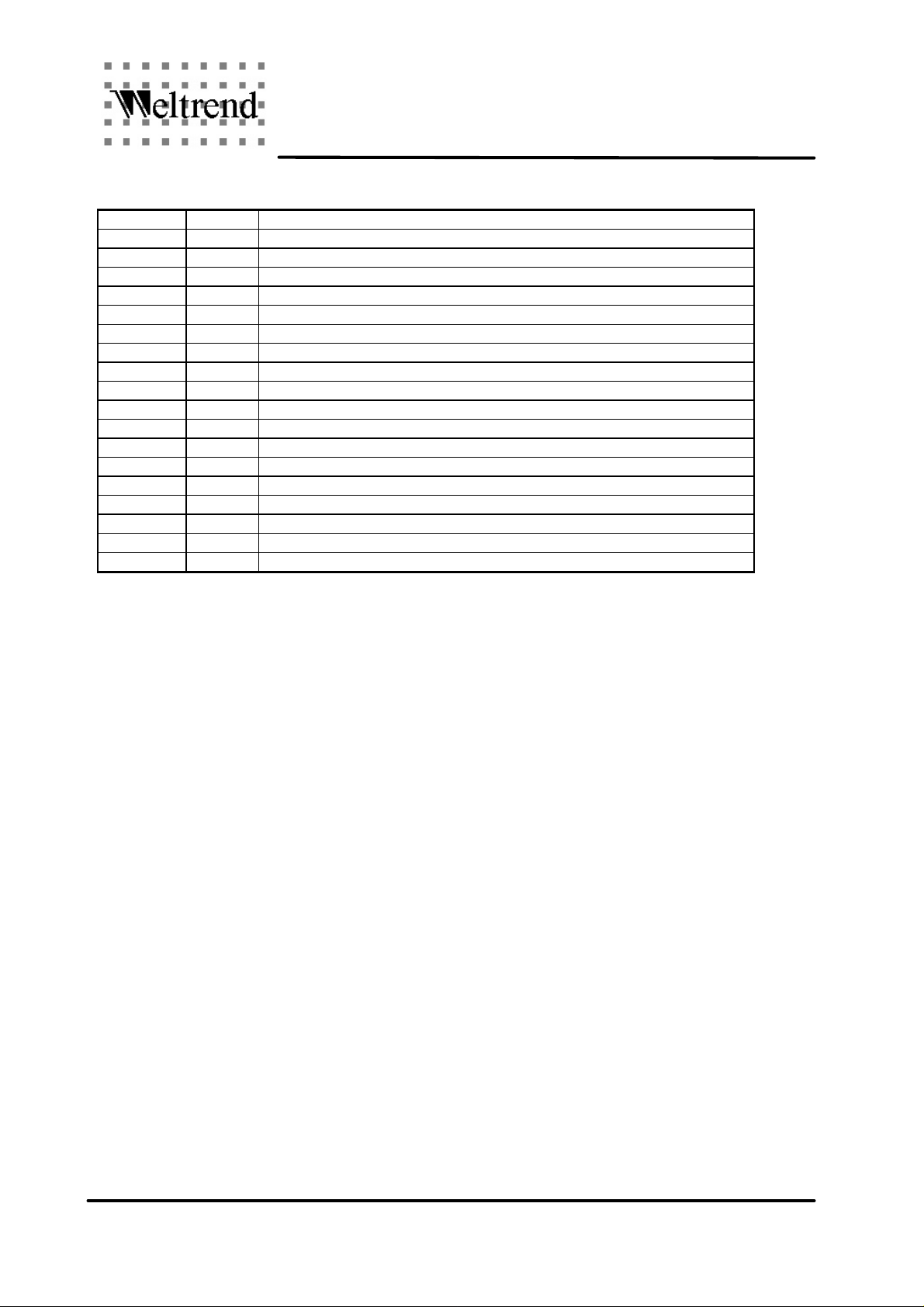

PIN DESCRIPTION

Pin Name TYPE Description

PGI I

GND P

FPOB O

PSONB I

I12A I

I12AB I

RI I

V12B I

V12C I

I12C I

I12B I

I5 I

I33 I

V12A I

V33 I

V5 I

VCC I

PGO O

Power good input signal pin

Ground

Fault protection output pin, open drain output

On/Off switch input

12VA over current protection sense input

12VA / 12VB over current protection sense input (only for 140)

Current sense adjust input

12VB over/under voltage input pin

12VC over/under voltage input pin

12VC over current protection sense input

12VB over current protection sense input

5V over current protection sense input

3.3V over current protection sense input

12VA over/under voltage input pin

3.3V over/under voltage input pin

5V over/under voltage input pin

Power supply

Power good output signal pin, open drain output

Weltrend Semiconductor, Inc.

Page 4

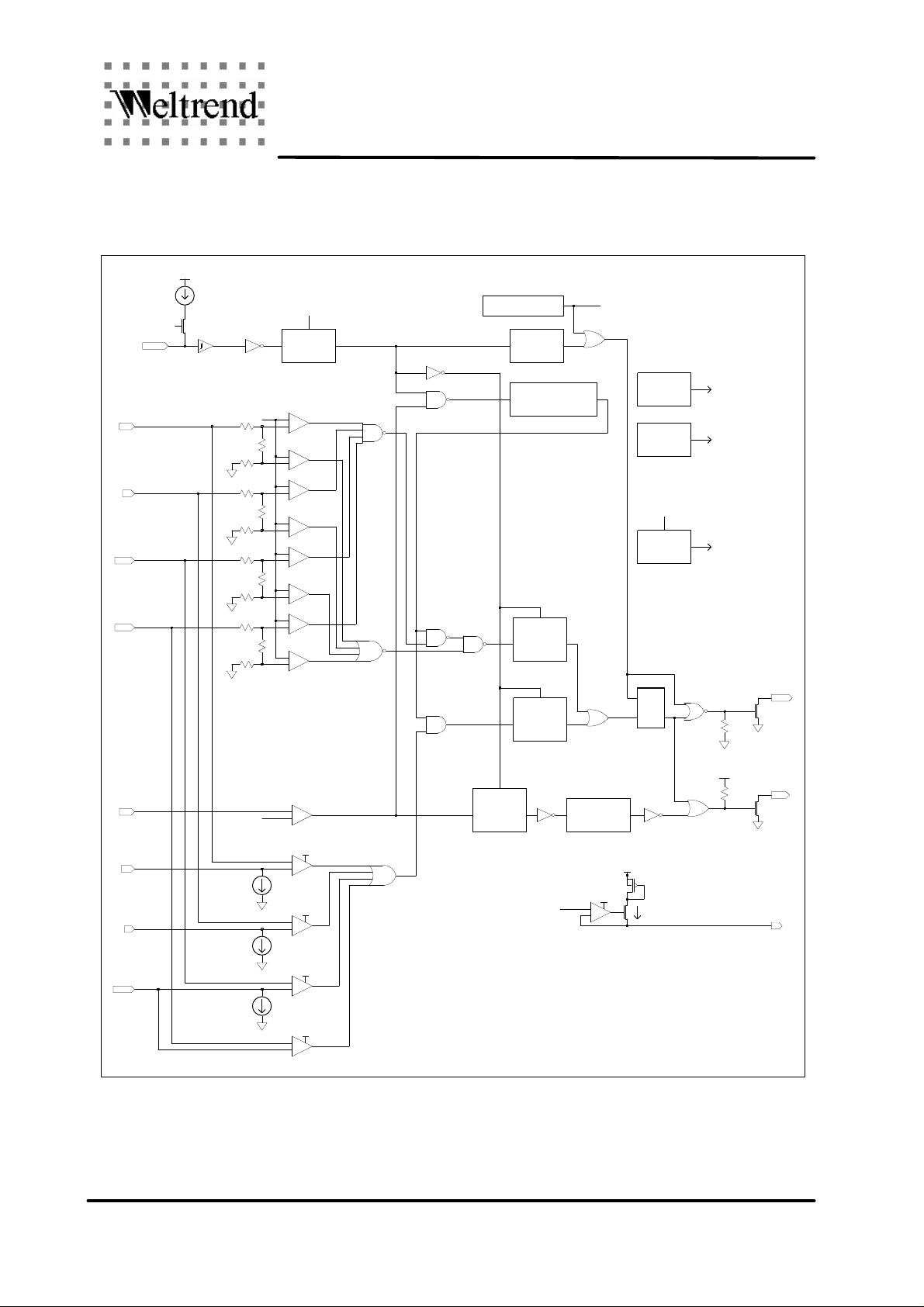

WT7525C-140 BLOCK DIAGRAM

BLOCK DIAGRAM

WT7525-140

VCC

WT7525 Preliminary release

Rev. 0.40

V12A

V12B

PWR

VCCI

PSONB

1.2V ~ 1.8V

V33

V5

VREF = 1.2V

38ms

debounce

-

UN

+

-

OV

+

-

UN

+

Power On Reset

3.5ms

clr

delay

75ms / 300ms

clr

delay

PWR

Bandgap

Reference

Internal

Power

VREF = 1.2V

VCCI = 3.6V

PWR

-

OV

+

-

UN

+

-

OV

+

-

UN

+

-

OV

+

clr

73us

debounce

clr

1.2ms

OSC

R

S Q

CLK

FPOB

debounce

IREF * 8

IREF * 8

IREF * 8

+

UN

-

V12A

-

+

V12A

-

+

V12A

-

+

V12A

-

+

I12AB

PGI

I33

I5

VREF = 1.2V

Weltrend Semiconductor, Inc.

clr

73us

debounce delay

VREF = 1.2V

300ms

clr

V12A

+

-

PGO

V12A

IREF=VREF / RI

RI

Page 5

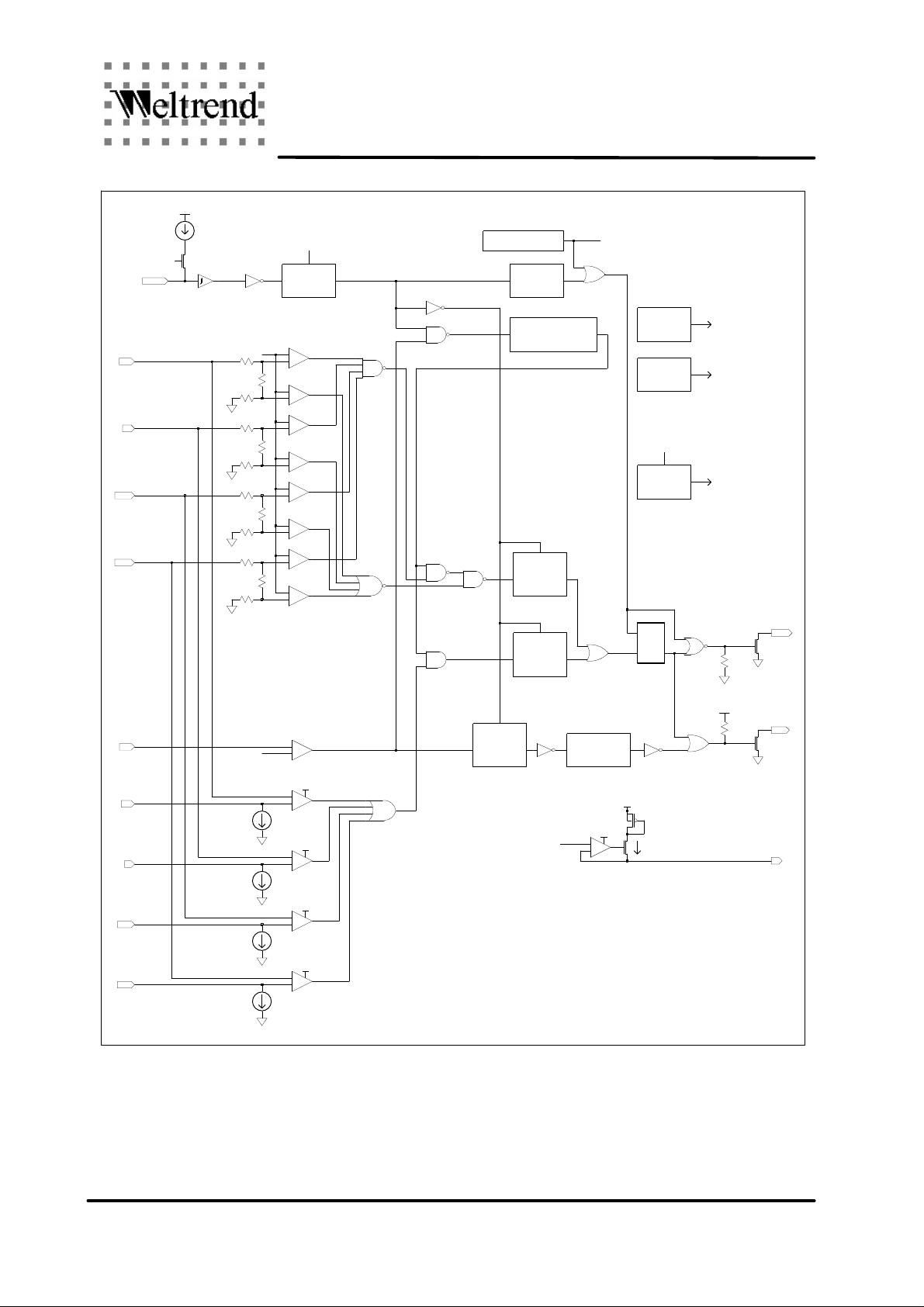

WT7525C-160 BLOCK DIAGRAM

WT7525-160 / 161

VCC

WT7525 Preliminary release

Rev. 0.40

V12A

V12B

PWR

VCCI

PSONB

1.2V ~ 1.8V

V33

V5

VREF = 1.2V

38ms

debounce

-

UN

+

-

OV

+

-

UN

+

Power On Reset

3.5ms

clr

delay

75ms / 300ms

clr

delay

PWR

Bandgap

Reference

Internal

Power

VREF = 1.2V

VCCI = 3.6V

PWR

-

OV

+

-

UN

+

-

OV

+

-

UN

+

-

OV

+

clr

73us

debounce

clr

1.2ms

OSC

R

S Q

CLK

FPOB

debounce

clr

73us

debounce delay

VREF = 1.2V

IREF * 8

IREF * 8

IREF * 8

IREF * 8

+

UN

-

V12A

-

+

V12A

-

+

V12A

-

+

V12A

-

+

PGI

I33

I5

I12A

I12B

VREF = 1.2V

300ms

clr

V12A

V12A

+

-

IREF=VREF / RI

PGO

RI

Weltrend Semiconductor, Inc.

Page 6

Loading...

Loading...