Vision VV5430 Datasheet

VISION VV5430 Monolithic Sensor

Integrated CMOS Image Sensor with support

for ADC and external control via serial interface

PRODUCT DATASHEET

DISTINCTIVE CHARACTERISTICS

•• Complete Video Camera on a single chip

• EIA/CCIR standard compatible

• Low power operation (250mW Typical)

• Integral 75Ω driver

• Frame & line timing signals for external ADC

• Optional image output in four quarters, with output driver tristate option for multiplexing

GENERAL DESCRIPTION

The VV5430 is a high ly -integrated VLSI

camera dev ice based on VISION ’s unique

CMOS sensor technology. It is suitable for

applicat ions requir ing minimum ex t ernal

circuitry , digitisation of the video signal or

externa l m ic roprocess or control.

The dev ic e inc orporate s a 388 x 295 pixel

image se ns or and all the necessary s upport

circuits to g enerate composite video into a 75Ω

load. Additional control signals support pix el

locked digit is ation of the vi deo signal.

• Automatic Exposure and Gain Control

• Automatic Black Level Calibration

• Linear or Gamma corrected output option

• Control options pin selectable for ease of use

• External control/configuration via serial interface

• Industry standard 48 pin LCC package

y

A bi-direct ional serial in t erf ac e and inter nal

register set allow full con t rol and monitoring of

all camera fu nc t ions. Automatic control of

exposure , gain and blac k lev el give a wide

range of operating conditions. All major control

functions are pin selectable giving maximum

flexibility with ease of use.

The VV5430 offers a complete camera system

ideally suited for integration into digital imaging

systems.

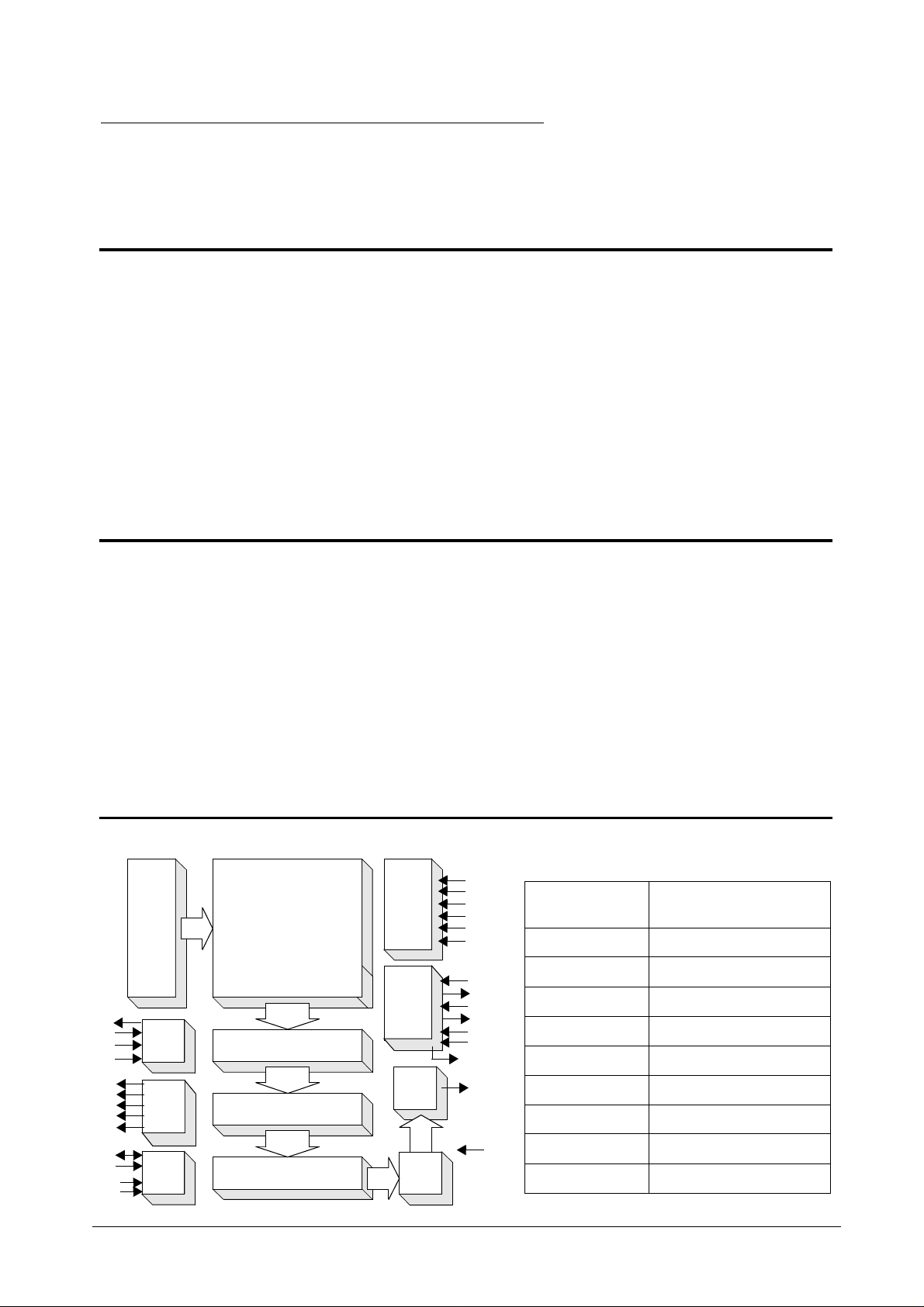

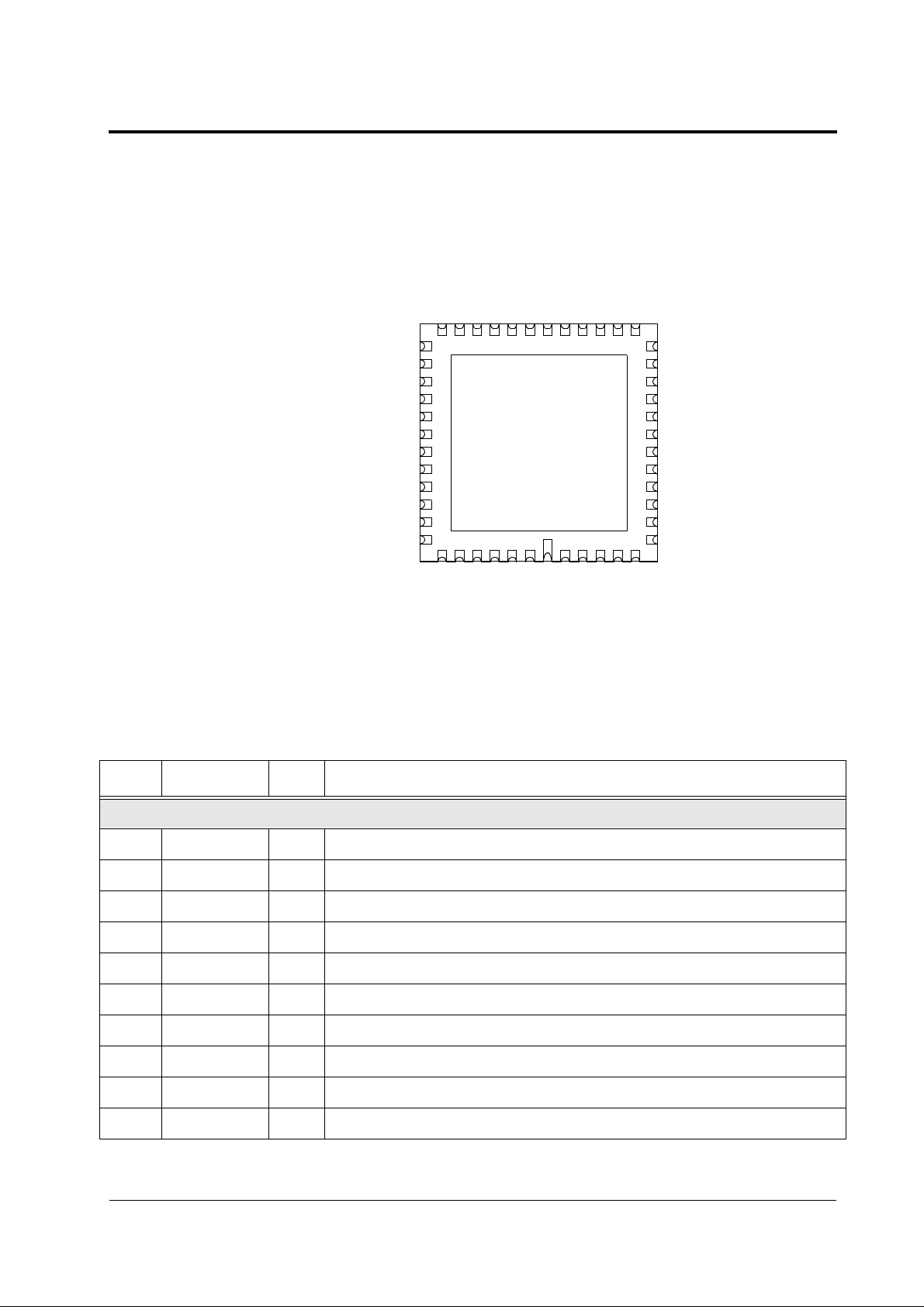

BLOCK DIAGRAM

AGC

VERTICAL

SHIFT

REGISTER

CKOUT

CKIN

SIN

CPE

FST

LST

PV

PVB

ODD

SDA

SCL

SAB0

SAB1

cd27033c.fm 1

CLOCK

CIRCUIT

IMAGE

CAPTURE

SERIAL

I/F

PHOTO DIODE ARRAY

COLUMN SENSE AMPLIFIERS

SAMP LE & H O LD

HORIZONTAL SHIFT REGISTER

Preliminar

DIGITAL

CONTROL

LOGIC.

ANALOG

VOLTAGE

REFS.

VIDEO

BUFFER

VIDEO

AMP

AEC

RESETB

LIN

BKLIT

CCIR

VRT

Vbloom

VOFF

VBG

EBCK

EVWT

2V7

AVO

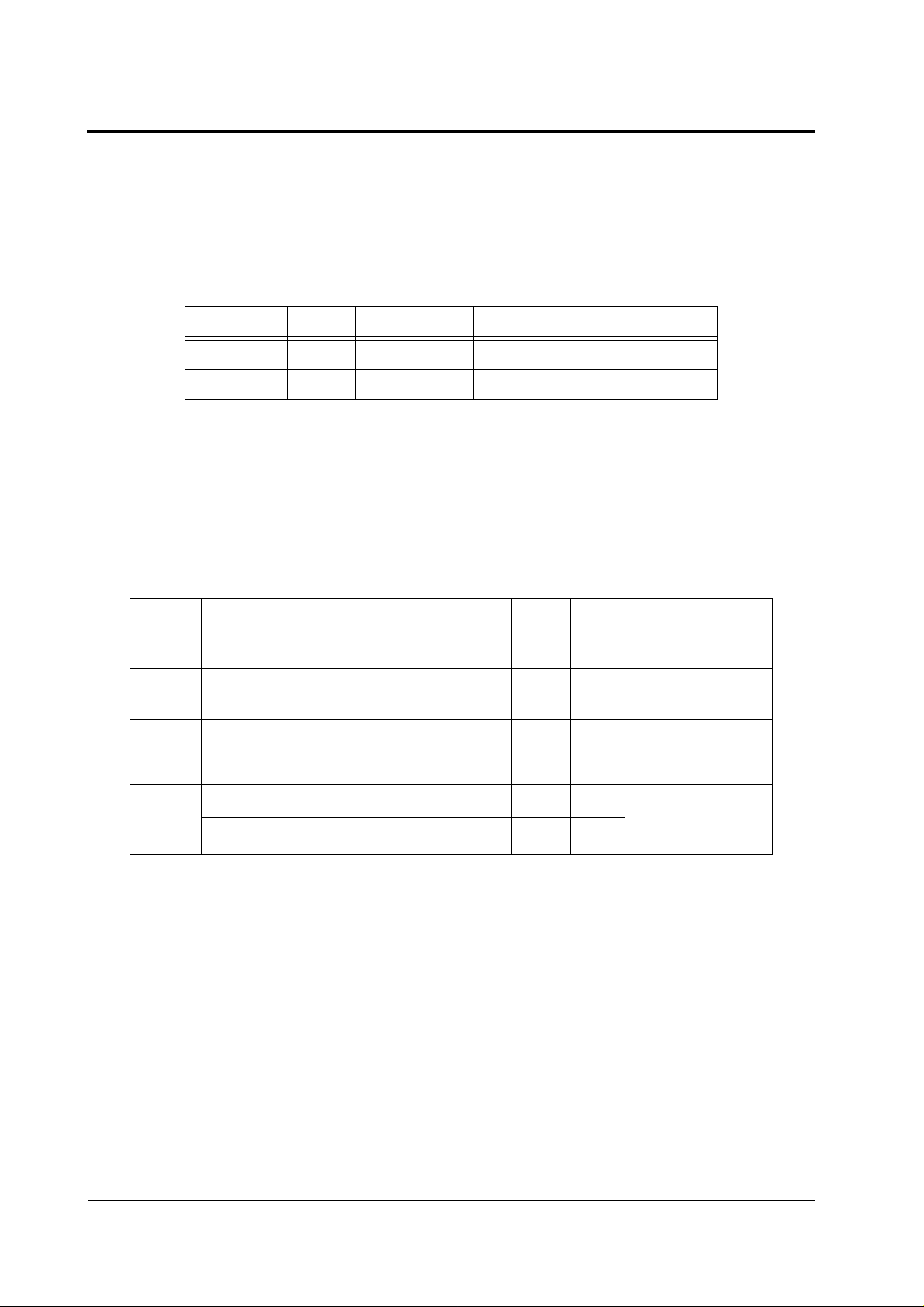

Pixel Format 384 x 287 (CCIR)

320 x 243 (EIA)

Pixel Size 12µm x 12µm

Array Size 4.66mm x 3.54mm

Min. illumination 0.5 lux (Standard Clock)

S/N Typ ically 52dB

Exposure control Automatic (to 1460 00:1)

Gain Control Up to +20dB

Power Supply 5v ±5%

Power < 300 mW

5V

Temperature 0

o

C - 40oC

VISION VV 5430 Sensor

MAIN FEATURES

The VV5430 deliver s a fu lly -f ormatted

composit e m onochro m e v ideo signal . S ta ndards optio ns inc lude EIA (3 20 x 244) and

CCIR (384 x 287). On chip signal conditioning

allows user-selecti on of linear or g am m acorrected output.

Different operationa l m odes can be s elected

dynamically via the e xternal inter fa c e or

configur ed at power up by tying the appropriate pins. Extensive use of automated operation and on chip references means that only

a small number of passive components are

needed to realise a com plete video camera.

Video Output

The integrated 75Ω driver eliminates the need

for additio nal active com ponents t o drive

standard loads, inclu ding double t erm inated

lines.

The video sig nal can also be inhibited by

setting the output to a high impedance state

(‘Tristate d’), which en ables multip lexing of a

number of different sensors. This, together

with vertical and horiz ontal ‘shuffle’ modes,

means that four sensor images can be shown

simultaneously on one display.

Frame, line and pixel timing signals are

provided t o f ac ilit ate pixel loc k ed digitisat ion

of the analo g v ideo data. In addition to th e

these outputs a synchronisation input (SIN) is

also provided to allow the start of frame to be

synchronised to an ex t ernal event.

elimina

Pr

Automatic Exposure and Gain Control

The VV5430 features autom at ic ex posure

control that allows a single fixed-aperture lens

to be use d, and incorpo rat es N ormal and

Backlit m odes to give operation over a wide

range of scene types. The system clock

frequency can also be reduced to provide

increased sensitivity.

Seri al Int e rf a ce

A bi-dire c tio nal serial interface allow s an

externa l c ontroller to s et operationa l parameters and co nt rol exposure and gain v alues

directly. T he host can al so int errogate

VV543 0 v ia t he serial interface to de te rm ine

the camera’s oper at ing modes and current

state. This allows alternative automatic exposure and other control algorithms to be run in

an external controller if the integrated

version s are not suitab le.

The VV5430 recei ve s and transm its c ontrol

and parametric data via a full duplex, two-wire

serial int erf ac e. The hos t is c om municat ions

master, with the camera either a slave

receiver or transmitter. Messages consist of

either three or five bytes of 8-bit data, with a

maximum serial clock frequency of 100kHz.

Since th e s erial clock is generated by th e

host, the host determines the data transfer

rate.

y

r

Contents

page

Main Features 2

Specifications 3

Pin List 7

Video Standards 9

Image Digitisation 12

Shuffle Modes 14

Exposure Control 17

Serial Com m unication 19

Read Data from Camera 21

Write to Camera 22

Example Support Circ uit 31

2 09/04/97

SPECIFICATIONS

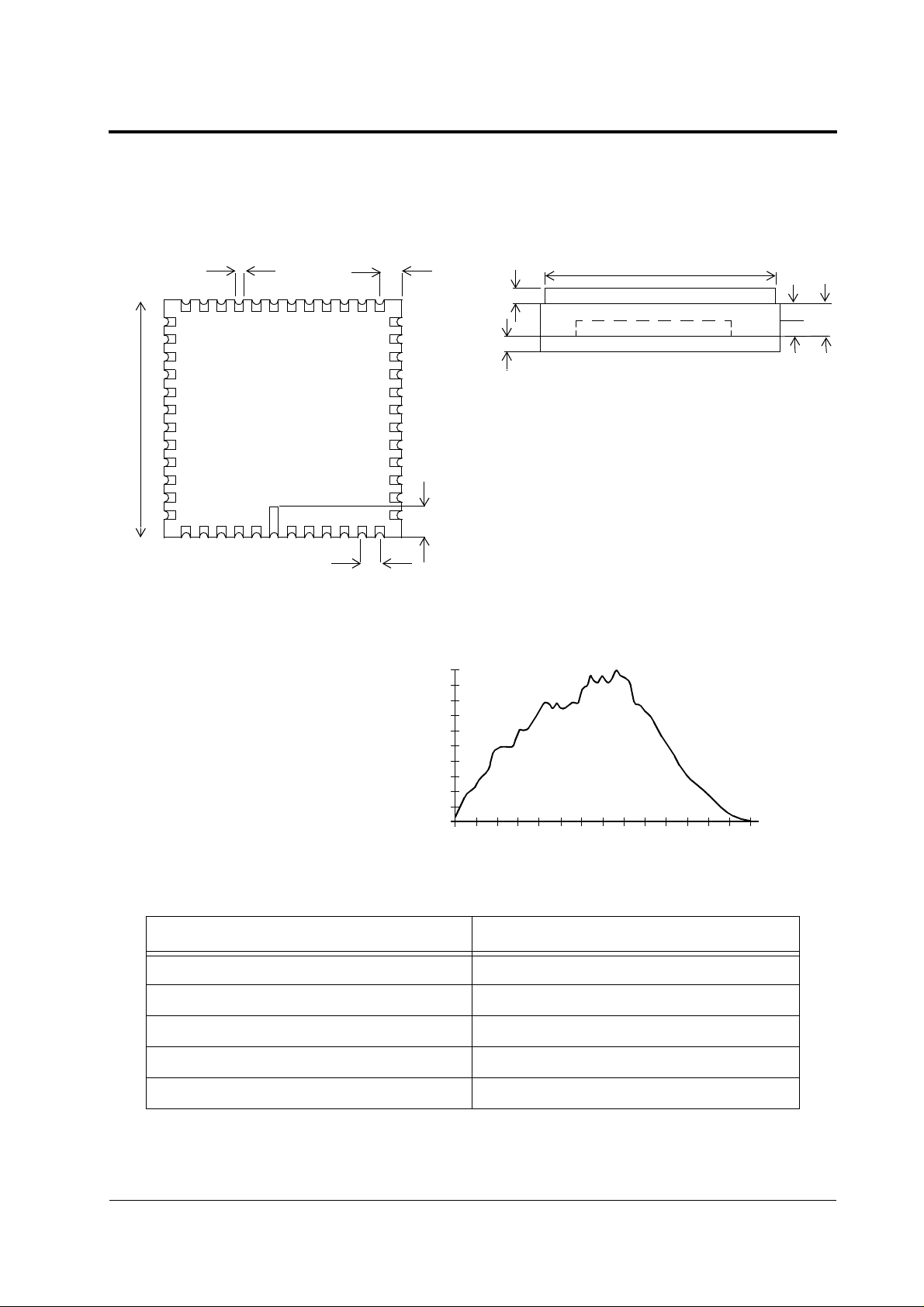

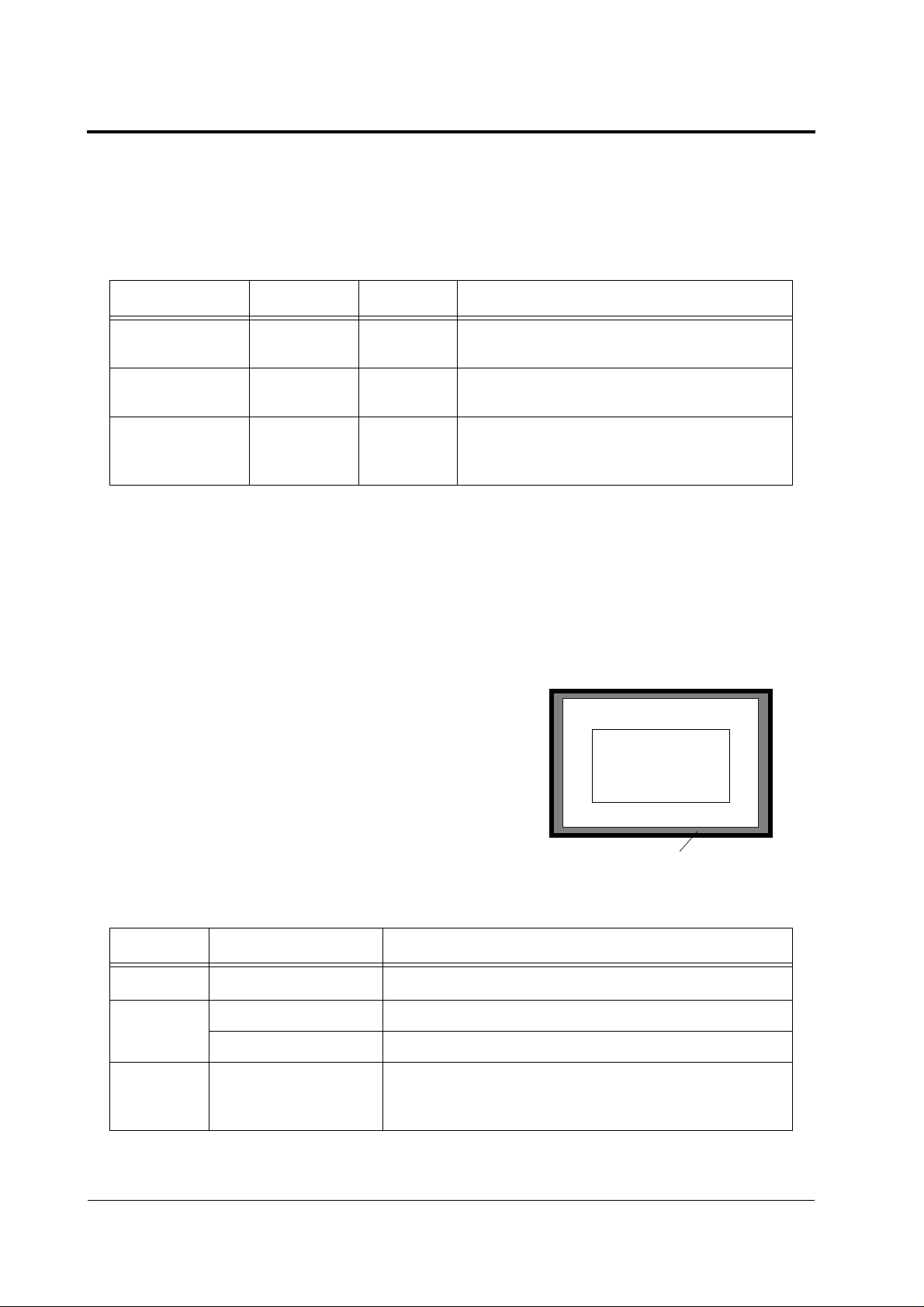

Package Details

Specifications

14.22

Viewed from below

Spectral Response

0.51

TYP

1.016 PITCH TYP

1.56 TYP

2.16

PIN 1

1.0

0.8

13.7

0.55

0.53

The optical array is ce nt red within th e

package to a tolerance of ± 0.2 mm, and

rotated n o m ore than ± 0.5

Toleranc es on package dimensions ±10%

Glass lid p lac ement is controlled so t hat no

packag e ov erhang ex is ts.

All dimens ions in millim et res

Glass Lid

Die

Base

Viewed from side

o

0.5

0.86

0.6

0.4

0.2

Normalised Response

0

400

500

600

700

800

900

1000

Preliminary

Wavel ength nm

1100

Absolute Maximum Ratings

Parameter Val ue

Supply Voltage -0.5 to +7.0 volts

Voltage on other input pins -0.5 to V

o

Temperature under bias -15

Storage Temperature -30

Maximum DC TTL output Current Magnitude 10mA (per o/p, one at a time, 1sec. duration)

Note: Stresses exceeding the Absolute Maximum Ratings may induce failure. Exposure to absolute

maximum ratings for extended periods may reduce reliability . Functionality at or above these

conditions is not implied.

C to 85oC

o

C to 125oC

+ 0.5 volts

DD

09/04/97 3

VISION VV 5430 Sensor

DC Operating Conditions

Symbol Parameter Min. Typ. Max. Uni ts Notes

V

DD

V

IH

V

IL

T

A

Operating supply voltage 4.75 5.0 5.25 Volts

Input Voltage Logic “1” 2.4 VDD+0.5 Volts

Input Voltage Logic “0” -0.5 0.8 Volts

Ambient Operating Temperature 0 70

AC Operating Conditions

Symb ol Par ameter Min. Typ. Max. Units No tes

CKIN

CKIN

SCL

1. Pixel Clock =

2. Serial Interface clock must be generated by host processor.

EIA Crystal frequency 12.0000 MHz 1

CCIR Crystal frequency 14.7456 MHz 1

Serial Data Clock 100 KHz 2

CKIN

/

2

Electrical Characteristics

y

o

C S t ill air

Symbol Parameter Min. Typ. Max. Units Notes

I

DCC

I

ADD

I

DD

V

REF2V7

V

BG

V

OH

V

OL

I

ILK

1. Digital and Analogue outputs unloaded - add output current.

Digital supply current

Analog su pply current

Overall s upply current

Internal voltage reference 2.700 Volts

Pr

Internal bandgap reference 1.22 Volts

Output Voltage Logic “1” 2.4 Volts I

Output Voltage Logic “0” 0.6 Volts I

Input Le ak age curren t

T ypical conditions, V

liminar

e

-1 µA

DD

10 mA 1

25 mA 1

35 mA 1

1 µA

= 5.0 V, TA = 27oC

= 2mA

OH

= -2mA

OL

VIH on

input

VIL on

input

4 cd27033c.fm

Specifications

Operating Characterist ics

Parameter min. typ. max. units Note

Dark Current Signal 50 mV/Sec Modal pixel voltage due to photodiode leak-

age under zero illumination with Gain=1

= (Vt1 - Vt2)/(t1-t2), calculated over

(V

dark

two different frames

Sensitivity 6 V/Lux·Sec V

Min. Illumination 0.5 Lux Standard CCIR clock

Shading TBA % Variance of V

Random Noise -52 dB RMS variance of all pixels, at 66% satura-

Smear TBA % Ratio of V

Flicker TBA % Variation of V

Lag TBA % Average residual signal with no illumination

Blooming TBA Ratio of spot illumination level that produces

/Lux·10ms, where Lux gives 50% satu-

Ave

ration with Gain=1 and Exposure=10ms

over eight equal blocks at

66% satu r ati o n lev e l illuminati on

tion, over four frames

25 lines high illuminated at 500xV

to V

Ave

at 66% saturation level illumination

in the field following one field of 66% sat.

illumina tion

0.1xV

sat

spot to the V

hole target)

ave

of the area outside a rectangle

ave

of the rectangle

of one line from field to field

ave

output from immediately around the

spot illumination level (pin-

sat

50%

level

Note: Devices are normaly not 100% tested for the above characterisation parameters, other than

Dark Current Signal (see Blemish Specification below).

Preliminary

All voltage (VA, V

blemish es are excluded (see Blemish Specific at ion below ). V

of saturation, that is peak white.

T est Conditions

The sensor is tested us ing the exam ple support

circuit illus t rat ed later in this document . Sta ndard

imaging conditions used for optical tests employ a

tungsten halogen lamp to unif orm ly illuminate t he

sensor (to better tha n 0. 5%), or to illum inate

specific areas. A neut ral density filt er is us ed to

control the level of illum ination where require d.

09/04/97 5

ave

, V

sat

, V

) measurements are referenced to the black level, V

xx%

Illumination Colour T emp. 3200o K

Clock Frequency Std. CCIR

Exposure Maximum

Gain x1

Auto. Gain Control (AGC) Off

Correction mode Linear

refers to the output that is xx%

xx%

, and sp ot

black

VISION VV 5430 Sensor

Blemish Specification

A Blemish is an area of pixels t hat produces output sig nif ic antly differe nt fro m it s su rrounding

pixels for the same illumination level. The definition of a Blemish Pixel varies according to testing

conditio ns as fo llows:

Test Exposure Illumination Blemish Pixel output definition

1 - Black Frame Minimum Black Differing more than ± 100 mV. from modal

value.

2 - Dark Current Maximum B lack Output more than three times the modal value

(see Dark Current Signal above).

3 - Pixel Variation Mid range 66% Sat. Differing more than ±35mV from modal value.

Note: The mode of pixel values must be within

±70 mV of 66% of V

for all devices.

sat

Note: Gain is set to Minimum and Correction set to Linear for all tests; measurement of blemishes for

Test 3 is conducted under standard illumination (see above), set to produce average output of

66% saturation level.

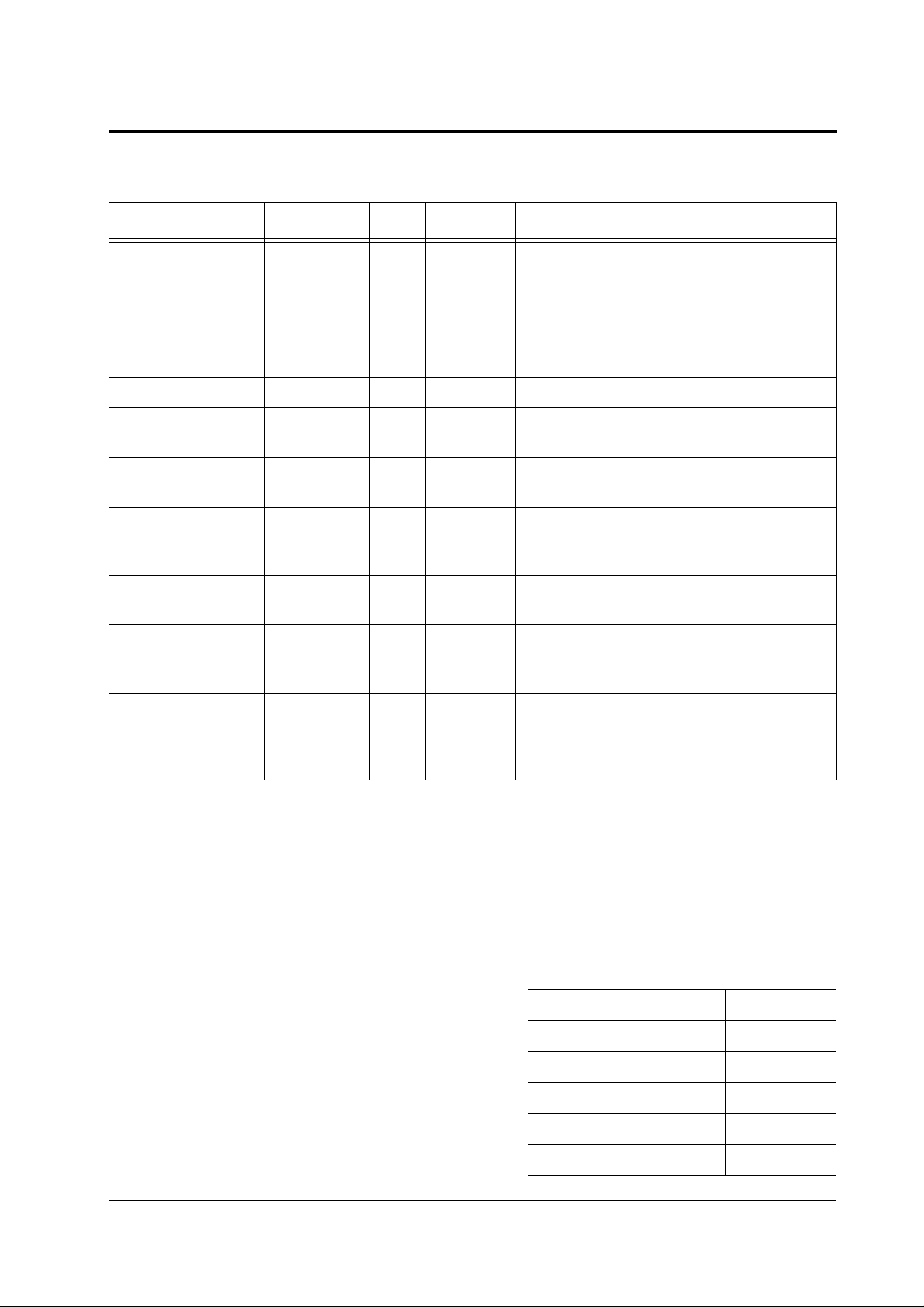

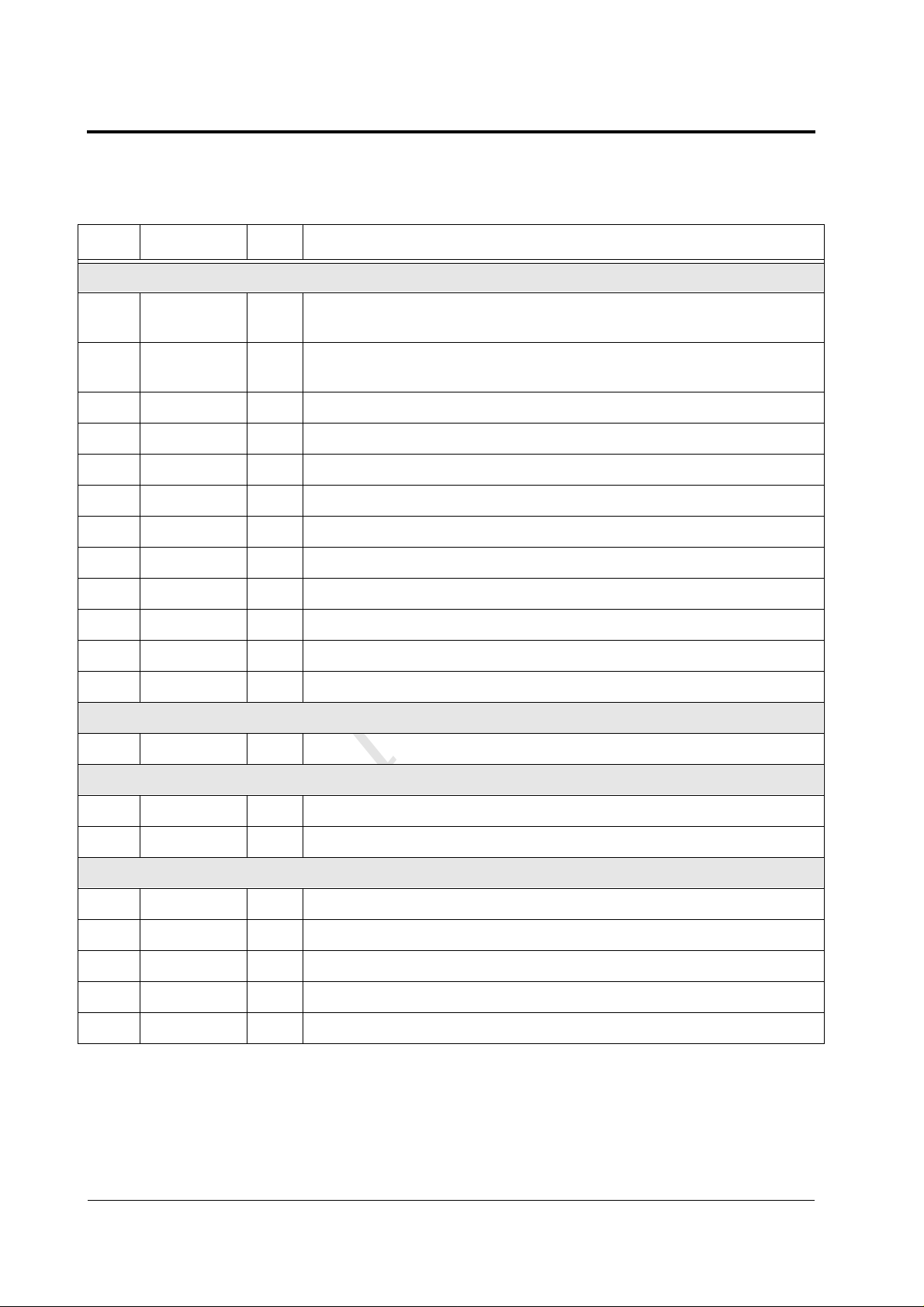

The pixel area of the sensor is divided into the following areas to qualify the blemish specification:

Area A is the central area of the array as defined

by the bo x wi th si des 50% of the linear height

and 50% of th e linear width of the array .

Area C is 10 vertical pixels by 10 horizontal pixels

aroun d th e edge of the array.

Area B is the remaining area of the array .

liminar

e

y

Area A

Area B

Area C

Pr

The blem is h s pecification is then def ined as follows :

Image Area Max. No. of Blemishes Notes

Area A 0 This is the most critical image area

4 Unconnected single pixels

Area B

Area C Any num ber Blemishes in this area are not significant, but the device

6 cd27033c.fm

1 Of up to four connected pixels (2x2 max.)

shall, however, have no row or column (>50% of row or

column) faults in any area.

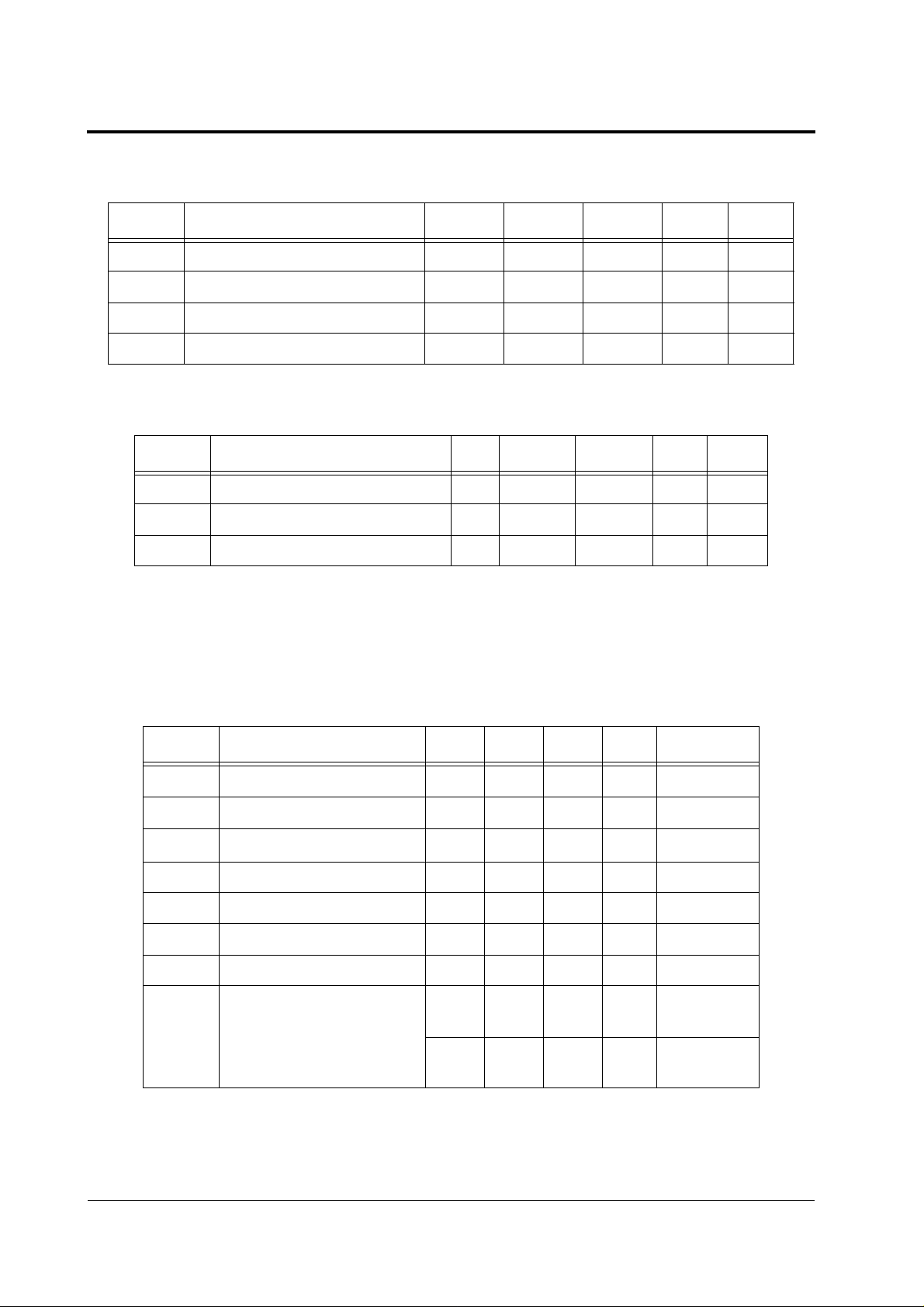

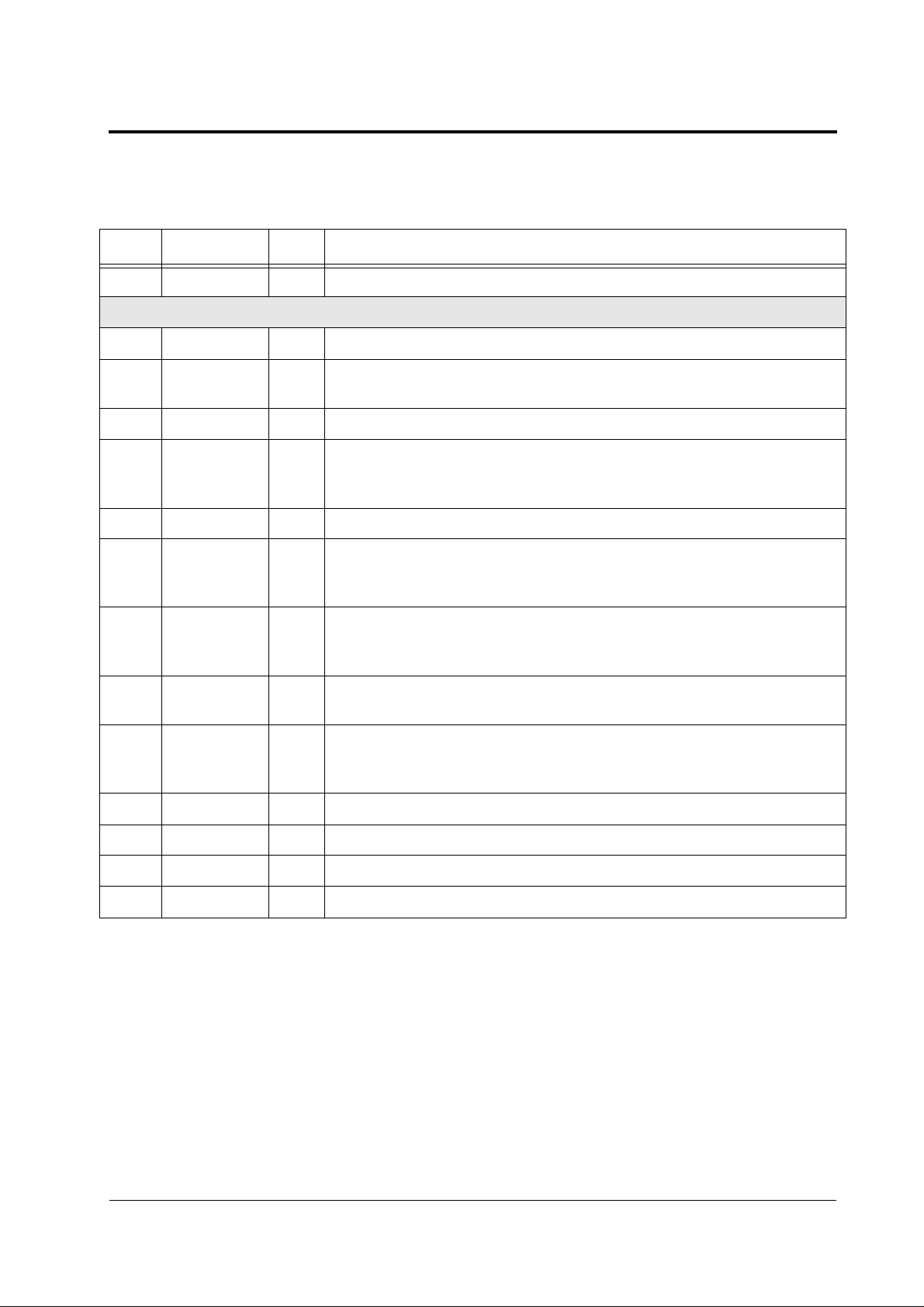

Pinout Diagram

48 Pin LCC

Viewed from top of package

VSS

PV

PVB

VDD

CPE

FST

ODD

SCI

SCL

SDA

VDD

VSS

31

32

33

34

35

36

37

38

39

40

Pin List

CKOUT

CKIN

VDD

BKLIT

RESETB

LST

41

42

VSS

AGC

CCIR

24 23 22 21 20 1930 29 28 27 26 25

LIN

AEC

SAB0

18

SCE

17

SIN

SAB1

16

15

VGND

14

AVO

13

VVDD

12

AMP2

11

AMP1

10

AVSS

9

EVWT

8

EBCK

7

AVDD

12345643 44 45 46 47 48

VRT

VBLWT

VCM

VBLOOM

VREF2V7

VBG

VPED

AVCC

AGND

VOFF/

DNC

DEC2V2

DEC2V7

PIN LIST

Pin Name Type Description

POWER SUPPLIES

1 AVCC PWR Core analogue power and reference supplies.

7 AV DD PWR output stage power. AVDD3 output stage logic.

10 AVSS GND Output stage ground. AVSS3 output stage logic.

13 VVDD PWR 75ohm buffer supply .

15 VGND GND 75ohm buffer ground.

24,31 VSS GND Digital padring & logic ground.

Preliminary

27,34 VDD PWR Digital padring & logic power.

41 DVDD PWR Core digital power.

42 DVSS GND Core digital ground.

48 AGND GND Core analogue ground and reference supplies.

09/04/97 7

VISION VV 5430 Sensor

Pin Name Type Description

ANALOGUE VOLTAGE REFERENCES

2 VBG OA Internal bandgap reference voltage (1.22V nominal). Requires external

0.1uF capacitor.

3 VOFF/VPED IA Pedestal DAC & offset comp. DAC bias. Connect to VBG or external ref-

erence.

4 DEC2V2 OA Decouple 2.2V reference. Requires external 0.1uF capacitor.

5 DEC2V7 OA Decouple 2.7V reference. Requires external 0.1uF capacitor.

6 - DNC Do NOT connect - for test use only

8 EBCK IA External black level bias. Internally generated. Decouple to VGND

9 EVWT IA E xte rnal white pixel threshold for exposure control. Decouple to VGND

43 VBLWT IA De fines white level for clamp circuitry. Requires external 0.1uF capacitor.

y

44 VBLOOM OA Anti-blooming voltage reference. Requires external 0.1uF capacitor.

45 VRT IA Pixel reset voltage. Connect to VREF2V7 or external reference.

46 VCM IA O ffset DAC common mode input. Connect to VREF2V7.

47 VREF2V7 OA Internally generated 2.7V reference. Requires external 4.7uF capacitor.

ANALOGUE OUTPUTS

14 AVO OA Buffered Analogue video out. Can drive a doubly terminated 75ohm load.

SYSTEM CLOCKS

25 CKOUT OD Oscillator output. Connect Crystal for standard timing.

26 CKIN ID Oscillator input. Connect Crystal for standard timing.

IMAGE CAPTURE TIMING SIGNALS

30 LST OD Line start. Active high pulse (start of active video lines).

32 PV OD Pixel sample clock. Qua lifies video output for external image capture.

33 PVB OD Pixel sample clock bar. Inverse of PV.

35 CPE ID↓ P ixel sample clock enable. Default CPE = 0 i.e. PV/PVB disabled.

36 FST OD Field start. Synchronises external image capture.

Pr

liminar

e

8 cd27033c.fm

Pin List

Pin Name Type Description

37 ODD OD Odd/even field signal. (ODD = 1 for odd fields, ODD = 0 for even)

DIGITAL CONTROL SIGNALS

16 SAB1 ID↓ Higher bit of two least significant bits of device address on serial interface.

17 SIN ID↓ Used to reset video timing control logic without resetting any other part of

VV5430. Resets video logic on the falling edge of the SIN pulse.

18 SCE ID↓ Scan mode enable - only relevant to test mode.

19 LIN ID↓ Gamma corrected or Linear output. LIN = 0, gamma corrected output,

LIN = 1, linear output. Default is gamma. LIN = 0 can be overridden via

serial interface.

20 SAB0 ID↓ Lower bit of two least significant bits of device address on serial interface.

21 AEC ID↑ Automatic exposure control. AEC = 1, auto exposure is enabled; AEC = 0

auto exposure and auto gain control are disabled. AEC = 1 can be overrid-

den via serial interface.

22 AGC ID↑ Aut om atic gain control enable. AGC = 1, auto-gain is enabled (if AEC =

1); AGC = 0, auto-gain is disabled. AGC can be overridden via serial

interface.

23 CCIR ID↑ Select default video mode for power-on. CCIR = 1 for CCIR video. EIA

video mode is selected when CCIR = 0. Default is CCIR if unconnected

28 BKLIT ID↓ No rmal or Backlit exposure contro l mode. BKLIT = 0, normal mode.

BKLIT = 1, backlit mode. Default is normal. BKLIT state can be overrid-

den via serial interface. See Exposure Control for details.

29 RESETB ID↑ Active low camera reset. All camera systems are reset to power-on state.

38 SCI ID↓ Scan chain input - only relevant to test mode.

39 SCL ID↑ Serial bus clock (input only). Must be generated by comms. host.

40 SDA BI↑ Serial bus data (bidirectional, open drain).

Key:

Preliminary

OA - Analogue output IA - Analogue input

OD - Digital output ID - Digital input

OD↓ - Digital out put with internal pull-down ID↑ - Digital input with internal pull-up

BI - Bidirectional

09/04/97 9

VISION VV 5430 Sensor

VIDEO STANDA RDS

The VV5430 has 2 different video format modes, producing CCIR or EIA standard composite

Monoch rom e video ou tp ut . Line standards and frequ encies are as f ollows:

Video Mode Format Image (Pixels) Crystal Frequency CCIR pin

CCIR 4:3 384 x 287 14.7456 MHz 1

EIA 4:3 320 x 243 12.0000 MHz 0

VV5430 Video Modes

Video signal Characteristics

The following table summaris es th e c om posite video output lev els (AVO) for t he two standards,

which are graphically illustrated on the following pages:

y

Symbol Parameter Min. Typ. Max. Units Notes

V

V

V

V

Sync

blank

black

Sat

CCIR, EIA Sync. level

CCIR, EIA Blanking

level

CCIR Black level

EIA Blac k lev el

CCIR Saturation level

e

EIA Sat uration level

liminar

0.3 V

0.9 V

0.9 V

1.0 V

2.3 V

2.4 V

DC reference

level

Peak Whi te ;

AVO clipped at

this level

Pr

Note: All measurements are made with AVO driving one 75Ω load.

10 cd27033c.fm

Loading...

Loading...