Vision VV6404C001, VV6404C001-B2, VV6301B001, VV5404C001, STV6404E-001 Datasheet

...

®

Mono and Colour Digital Video CMOS Image Sensors

CD5404-6404F-A

1/54

VV5404 & VV6404

DESCRIPTION

VV5404 and VV6404 are highly integrated CMOS VLSI

sensors which enables high standards of performance and

image quality at a very cost-effective price point. The 356 x

292 monochrome device offers one of the simplest routes

currently available to design-in of imaging applications, while

the colour device is ideal for low cos t PC camera applicati ons.

Both devices incorporat e a comprehens ive range of on-boar d

controls eliminating th e need for addition al support chips . Onchip A/D conversion provides 8 bit digital output and the

device set up i s fully automati c via th e built-in automati c black

level calibration algorithm.

Exposure and gain set tings are programma ble an d o peration

is controlled via a serial interface.

This sensors offer v ariabl e fram e rates of up to 30 fram es p er

second and a 4 wire digital video bus. The digital interface

also provides a t ri-stateable data qualification clock and fram e

synchronisation si gnal.

Hand-held products, in applications such as PDAs, bar code

scanning or autom atic me ter reading , will bene fit from th e low

power requirements and from the inbuilt sleep and power

down modes.

The price and performance standards introduced with the

VV5404 and VV6404 enable use of an imaging solution

where previously it may not have been practicable on cost

grounds.

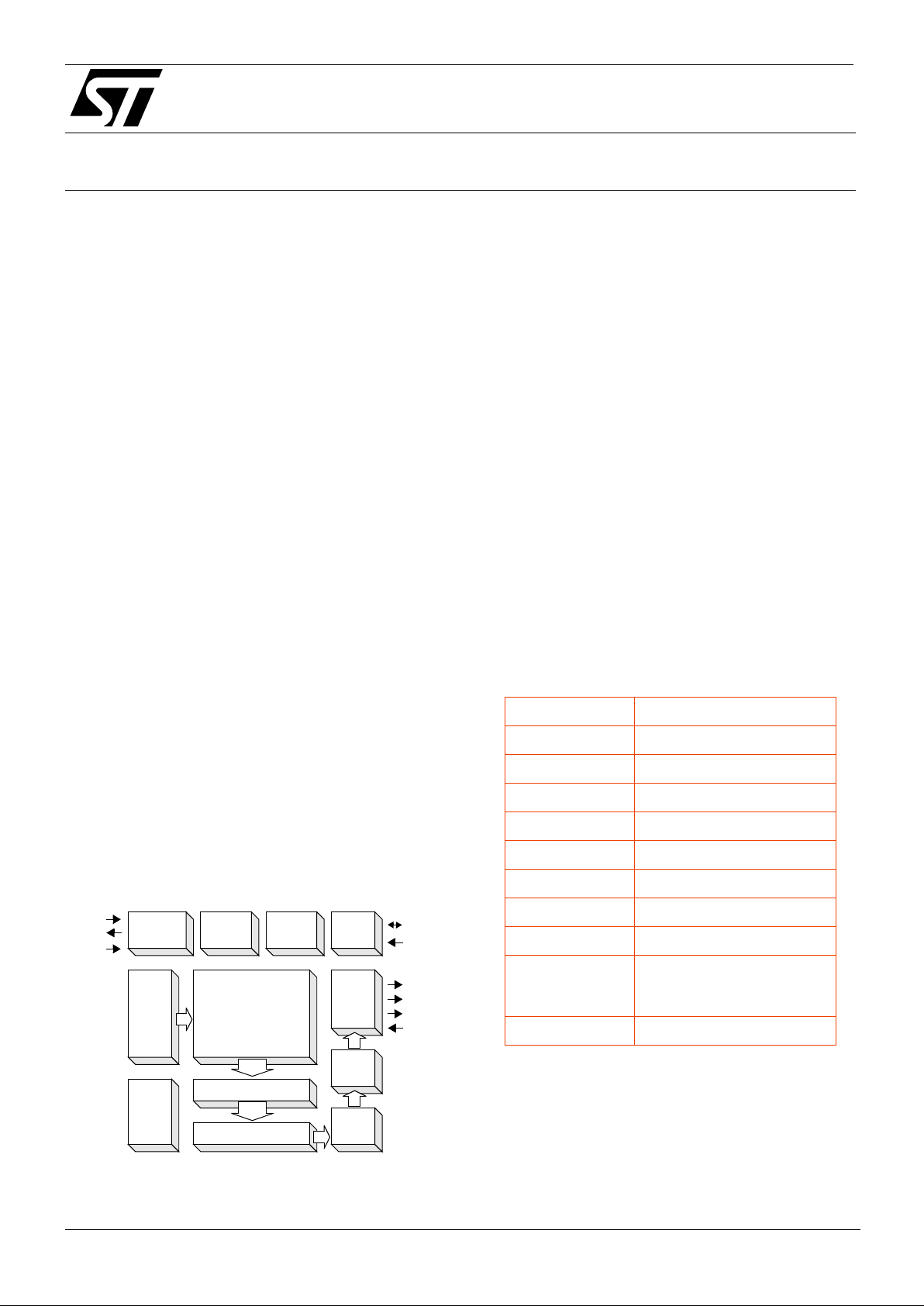

BLOCK DIAGRAM

FEATURES

• CIF Format mono or colour pixel array

• Up to 30 frames per second operation

• On-chip 8 bit analogue to digital converter

• Low power consumption

• Up to 356 x 292 pixel image size

• Automatic exposure and gain control

• Serial interface control

• Programmable exposure and gain values

• Automatic black level calibration

• 4-wire digital video bus

• Evaluation kit available

APPLICATIONS

• PC Cameras

• Biometrics

• Inspection Systems

SPECIFICATIONS

Important:

1. A colour co-processor is required to convert the VV6404 sensor’s video

data stream of raw colourised pixel data into either a CIF or QCIF format RGB or YUV colour image.

2. VV5404 and VV6404 do NOT have any form of automatic exposure

control. This must be performed externally.

SAMPLE & HOLD

HORIZONTAL SHIFT

PHOTO DIODE

ANALOG

VOLTAGE

REFS.

SDA

SCL

D[3:0]

VERTICAL

SHIFT

REGISTER

CLKO

8-bit

ADC

ARRAY

REGISTER

SERIAL

INTER-

FACE

OUTPUT

FORMAT

GAIN

IMAGE

FORMAT

BLACK

CALIBRATION

EXPOSURE

REGISTERS

STAGE

OEB

FST

QCK

SIN

CLKI

Pixel resolution

356 x 292 (CIF)

Array size

4.272mm x 3.212mm

Pixel size

12.0 µm x 1 1.0 µm

Min. illumination

0.1 lux

Exposure control

Automatic (to 25000:1)

Gain control

Automatic (to +20dB)

Signal/Noise ratio

46dB

Supply voltage

5.0v DC

+/−

5%

Supply curren t

<75mA

Operating

temperature

(ambient)

0

o

C - 40oC

(for extended temp. info please contact STMicroelectronics)

Package type

48LCC

VV5404 & VV6404

CD5404-6404F-A

2/54

Table of Contents

1. Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

2. Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

2.1 Image Read-out Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

2.2 Frame Rate Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

3. Exposure Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

4. Digital Video Interface Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4.1 General description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4.2 Embedded control data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4.2.1 The combined escape and sync character . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4.2.2 The command word. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

4.2.3 Supplementary Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

4.3 Video timing reference and status/configuration data. . . . . . . . . . . . . . . . . . . . . . . . . .13

4.3.1 Blank lines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.3.2 Bla ck line timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.3.3 Valid video line timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.3.4 Start of frame line timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.3.5 End of frame line timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.4 Detection of sensor using data bus state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.5 Resetting the Sensor Via the Serial Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

4.6 Power-up, Low-power and Sleep modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

4.6.1 Power-Up/Down (Figure 12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 8

4.6.2 Low-Power Mode (Figure 10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

4.6.3 Sleep Mode (Figure 11). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

4.6.4 Application of the system clock during sensor low-power modes . . . . . . . . . . . . . . . 22

4.7 Qualification of Output Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

4.7.1 Using the External Clock signal applied to CKI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.7.2 Data Qualification Clock, QCK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

4.7.3 Frame Start Signal, FST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

5. Serial Control Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2 7

5.1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

5.2 Serial Communication Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

5.3 Data Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

5.4 Message Interpretation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

5.5 The Programmers Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

5.5.1 DeviceH [000_00002] and DeviceL [000_ 00012]. . . . . . . . . . . . . . . . . . . . . . . . . . .31

5.5.2 Status0 [000_00102] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

5.5.3 Line_count_H [000_00112] & Line_count_L [000_01002]. . . . . . . . . . . . . . . . . . . . .31

5.5.4 Setup0 [001_00002] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

5.5.5 Setup1 [001_00012] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

5.5.6 Setup2 [001_00102] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

5.5.7 Setup4 [001_01002] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

5.5.8 Setup5 [001_01012] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

5.5.9 Expos ure Control Reg isters [010_00002] - [010_10012] . . . . . . . . . . . . . . . . . . . . . . 35

5.5.10 ADC Setup Register AS0 [111_01112] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

5.6 Types of messages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

5.6.1 Single location, single data write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

VV5404 & VV6404

CD5404-6404F-A

3/54

5.6.2 Single location, single data read.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

5.6.3 No data write followed by same location read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

5.6.4 Same location multiple data write.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

5.6.5 Same location multiple data read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

5.6.6 Multiple location write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

5.6.7 Multiple location read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

5.7 Serial Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 1

6. Clock Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

6.8 Synchronising 2 or More Cameras. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

7. Detailed specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

7.1 General. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

7.2 DC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

8. Physical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

8.1 Pinout Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

8.2 Signal Names. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

8.3 48LCC Mechanical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

8.4 VV6404 Sensor Support Circuit Schematic Diagram. . . . . . . . . . . . . . . . . . . . . . . . . .50

8.5 Sensor Support Circuit Component List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

9. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

VV5404 & VV6404

CD5404-6404F-A

4/54

1. Introduction

VV5404 and VV6404 are CIF format CMOS image sensors capable of outputing digital pixel data at frame rates, of

upto 30 frames per second. The VV5404 is a monochrome part, while the VV6404 has a colour filter applied over the

sensor array.

Important:

The VV6404 sensor’s video data stream only contains raw colourised pixel data. A colour co-processor

is required to generate for example either a CIF or a QCIF format YUV colour image.

The 356 x 292 pi xel senso rs have an on-chip 8-bi t analogue to digital con verter (F igure 1). T he sensors offer very

flexible digital interface, the main components of which are listed below:

1. A tri-stateable 4-wire data bus (D[3:0]) for sending both video data and embedded timing references.

2. A data qualification clock, QCK, which can be programmable via the serial interface to behave in a number of

different ways (Tri-stateable).

3. A frame start signal, FST (Tri-stateable).

4. A 2-wire serial interface (SDA,SCL) for controlling and setting up the device.

5. The ability to synchronise the operation of multiple cameras - synchronisation input, SIN.

An 8-bit pixel value is transmitted across the 4 wire tri-stateable databus as series pair of 4-bit nibbles, most significant

nibble first. Along within the pixel data, codes representing the start and end frames and the start and end of lines are

embedded within the video data strea m to allow the video processor to synchronise with video dat a the camera

module is generating. Section 4. defines the format for the output video datastream.

To complemen t the embedded control sequences a data qualification clock, QCK, and a frame start signal are also

available. QCK can be set-up to either be:

1. Disabled

2. Free-running.

3. Qualify onl y the con tr ol se quen ce s and the pixel data.

4. Qualify the pixel data only

There is also the choice of two different QCK frequencies, where one is twice the frequency of the other.

SAMPLE & HOLD

HORIZONTAL SHIFT

PHOTO DIODE

ANALOG

VOLTAGE

REFS.

SDA

SCL

D[3:0]

VERTICAL

SHIFT

REGISTER

CLKO

8-bit

ADC

ARRAY

REGISTER

SERIAL

INTER-

FACE

Figure 1 : Block Diagram of VV5404 and VV6404 Image Sensors

OUTPUT

FORMAT

GAIN

IMAGE

FORMAT

BLACK

CALIBRATION

EXPOSURE

REGISTERS

STAGE

OEB

FST

QCK

SIN

CLKI

VV5404 & VV6404

CD5404-6404F-A

5/54

1. Fast QCK: the falling edge of the clock qualifies the nibble data irrespective of whether it is the most or the least

significant nibble.

2. Slow QCK: the rising edge of the clock qualifies the most significant nibbles while the falling edge of the clock

qualifies the leas t sign ificant nibbles.

The FST can be enabled/disabled via the serial interface.

OEB tri-states all 4 databus lines, D[3:0], the qualification clock, QCK and the frame start signal, FST.

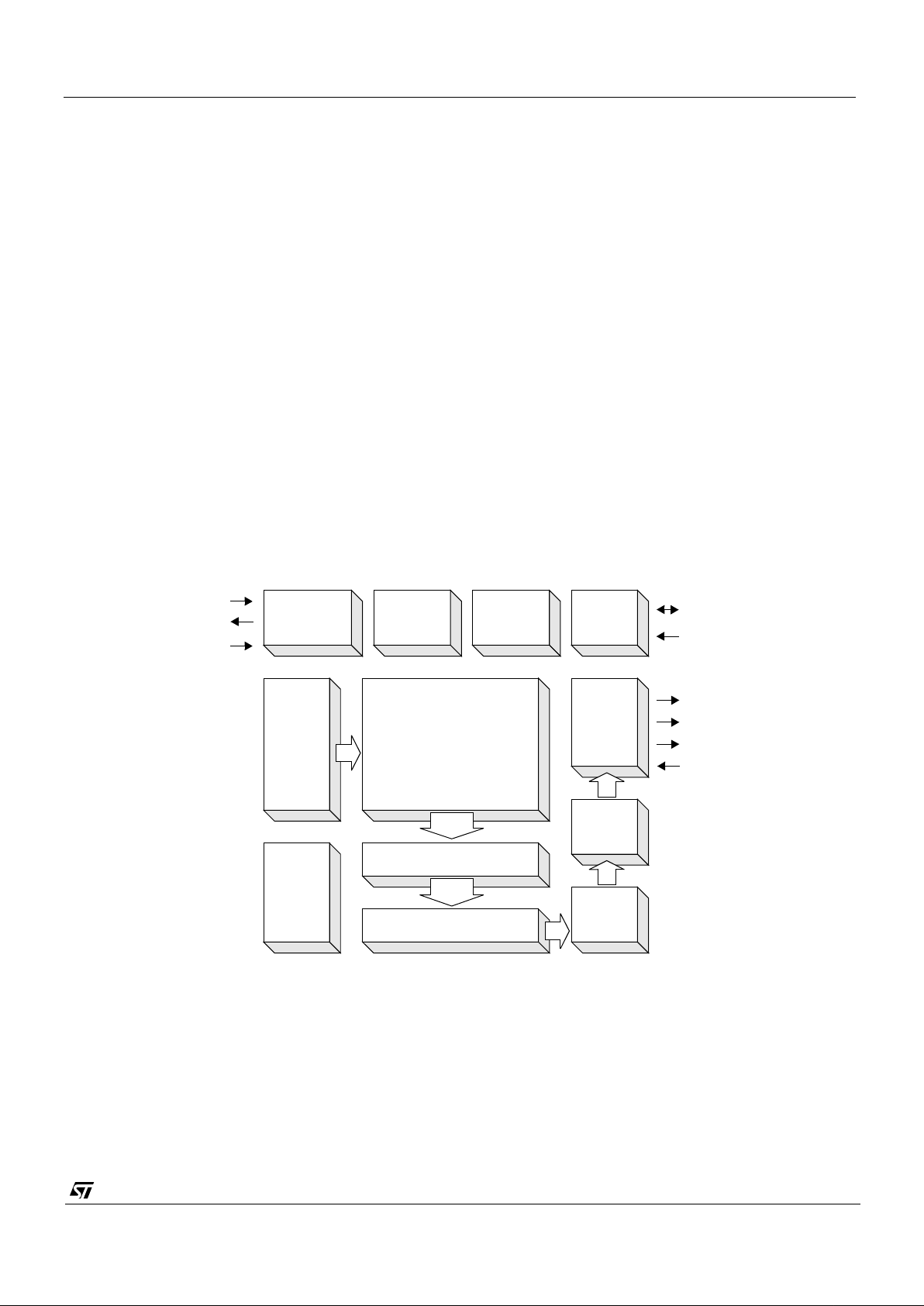

There are 3 main ways of interfacing to the VV5404 or VV6404 sensor based on the above signals:

1. The processor capturing the data (or colour co-processor for VV6404) supplies the sensor clock, CKI, and uses

the embedded control sequences to synchronise with the frame and line level timings. Thus the processor and

sensor are running off derivatives of the same fundamental clock (4 fsc - 14.31818 MHz). To allow the receiver

to determ ine the bes t sam pli ng pos ition of the video data, durin g its power-up sequen ce the sensor outputs a

101010... sequence on each of its databus lines for the video processor to lock on to.

2. The video processor uses a free-running QCK supplied by the sensor to sample the incoming video data

stream. The embedded control sequences are used to synchronise the frame and line level timings. A crystal is

used to generate the clock for the sensor.

3. The video processor uses FST and the data only mode for QCK to synchronise to the incoming video data. Primarily intended for interfacing to frame grabbers.

The 2-wire serial interface provides complete control over how the sensor is setup and run. Exposure and gain values

are programmed via this interface. Section 5. defines the communications protocol and the register map of all the

locations which can be accessed via the serial interface.

Using the first two interface options outlined above it is possible to control the sensor and receive video data via a 9wire cable between the sensor and the video processor/colour-processor.

1. A 4-wire data bus (D[3:0]) for sending both vide o data and embedded ti m ing r eferences.

2. A 2-wire serial interface (SDA,SCL).

3. The clock for the sensor or QCK from the sensor.

4. VCC and GND power lines.

The various image read-out and frame rate options are detailed in Sections 2 and 3 respectively.

Figure 2 : Interfacing Options

SDA

SCL

D[3:0]

CLKI

Sensor

Colour

Co-processor

(processor)

SDA

SCL

D[3:0]

QCK

Sensor

Colour

Co-processor

(processor)

FST

VV5404 & VV6404

CD5404-6404F-A

6/54

2. Operating Modes

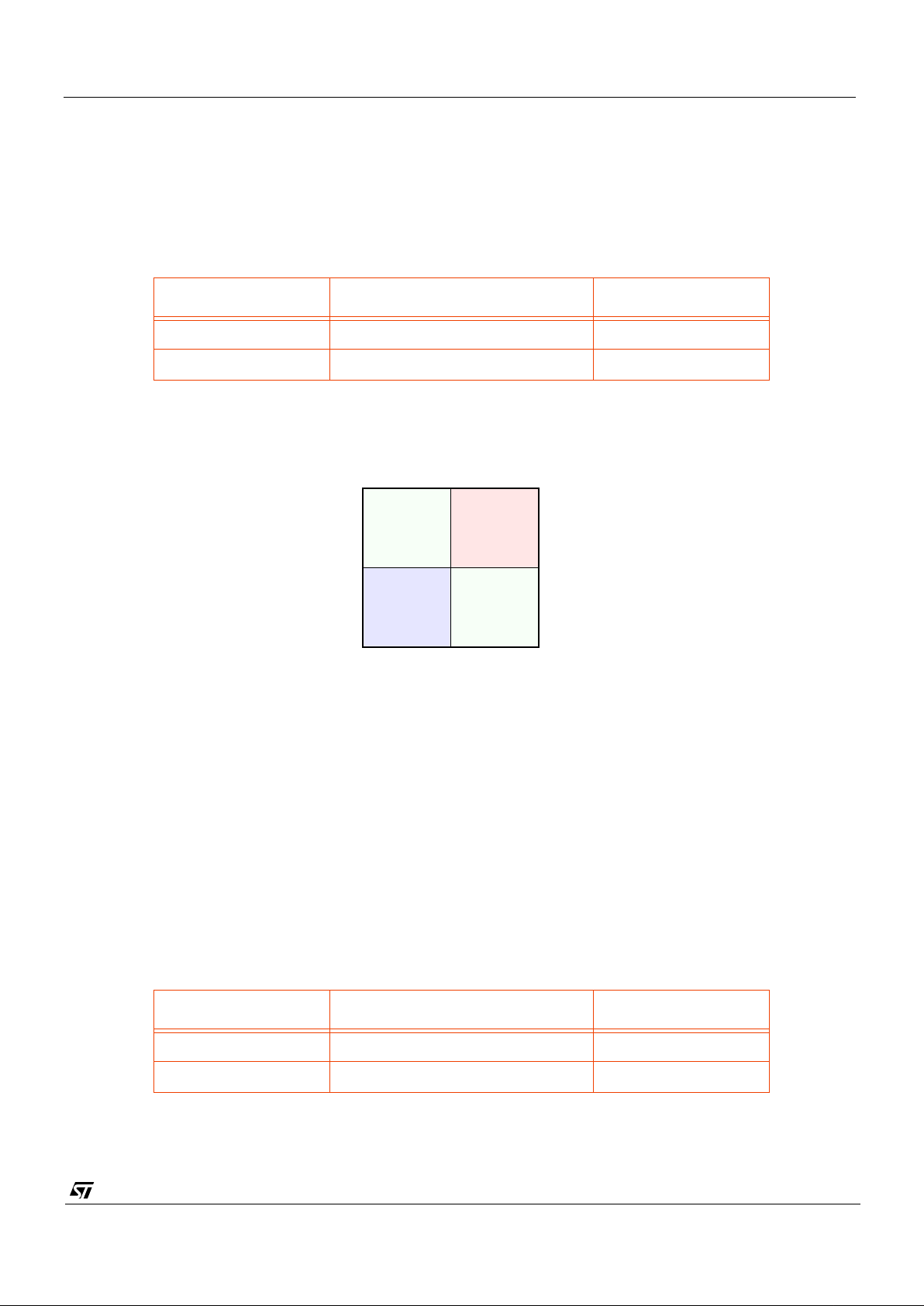

2.1 Image Read-out Options

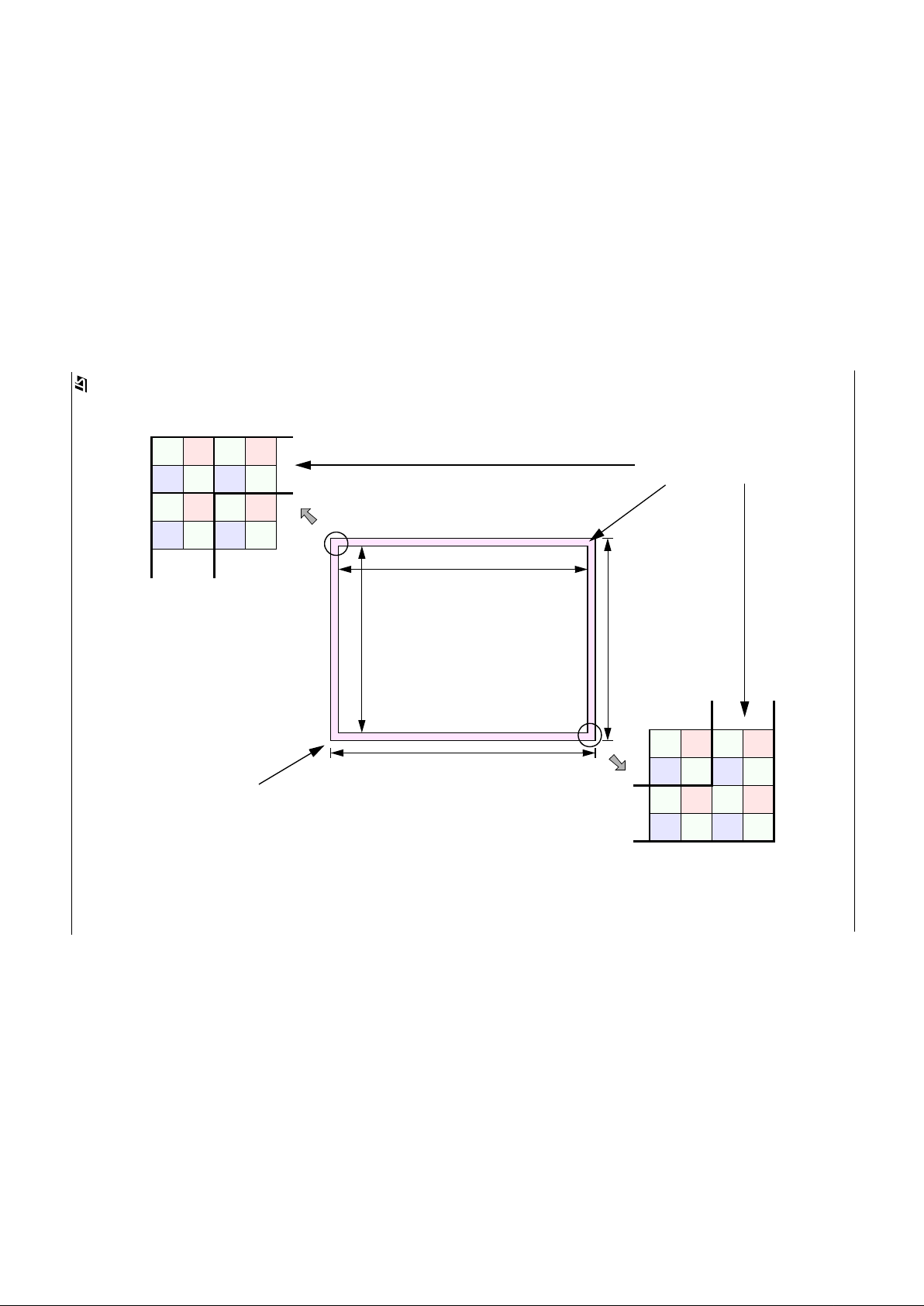

The output image format is CIF (352 x 288 pixel array). To provide the colour co-processor with the extra information

it needs for interpolation at the edges of the VV6404 pixel array, an optional border 2 pixels deep on all 4 sides of the

array can be enabled (Figure 4). The resulting image size of 356 x 292 pixels is the default power up state for this

camera module. The border option is programmable via the s erial interface.

Image read-out is either non-i nte rlac ed raster scan, or ‘shuffled’ non-interlaced rast er s ca n.

The shuffled raster scan order differs from a conventional raster in that the pixels of individual rows are re-ordered,

with the odd pixels within a row read-out first, followed by the even pixels.

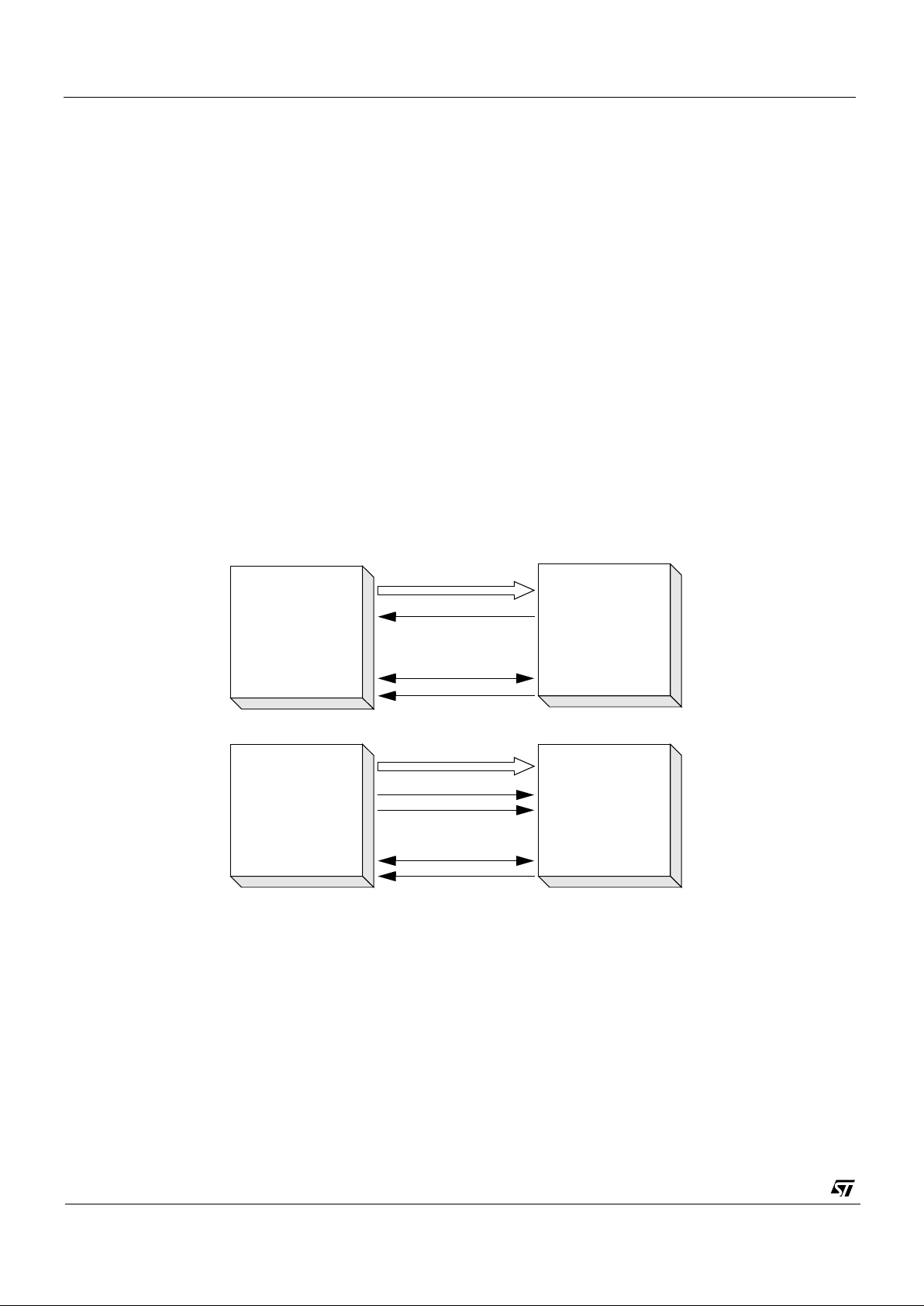

This ‘shuffled’ read-out within a line, is useful in the VV6404 device as it groups pixels of the same colour (according

to the Bayer pattern - Figure 3) together, reducing cross talk between the colour channels.

NOTE:

This option is on by def ault in both VV5404 and VV6404 sensors and is controllable via the serial interface.

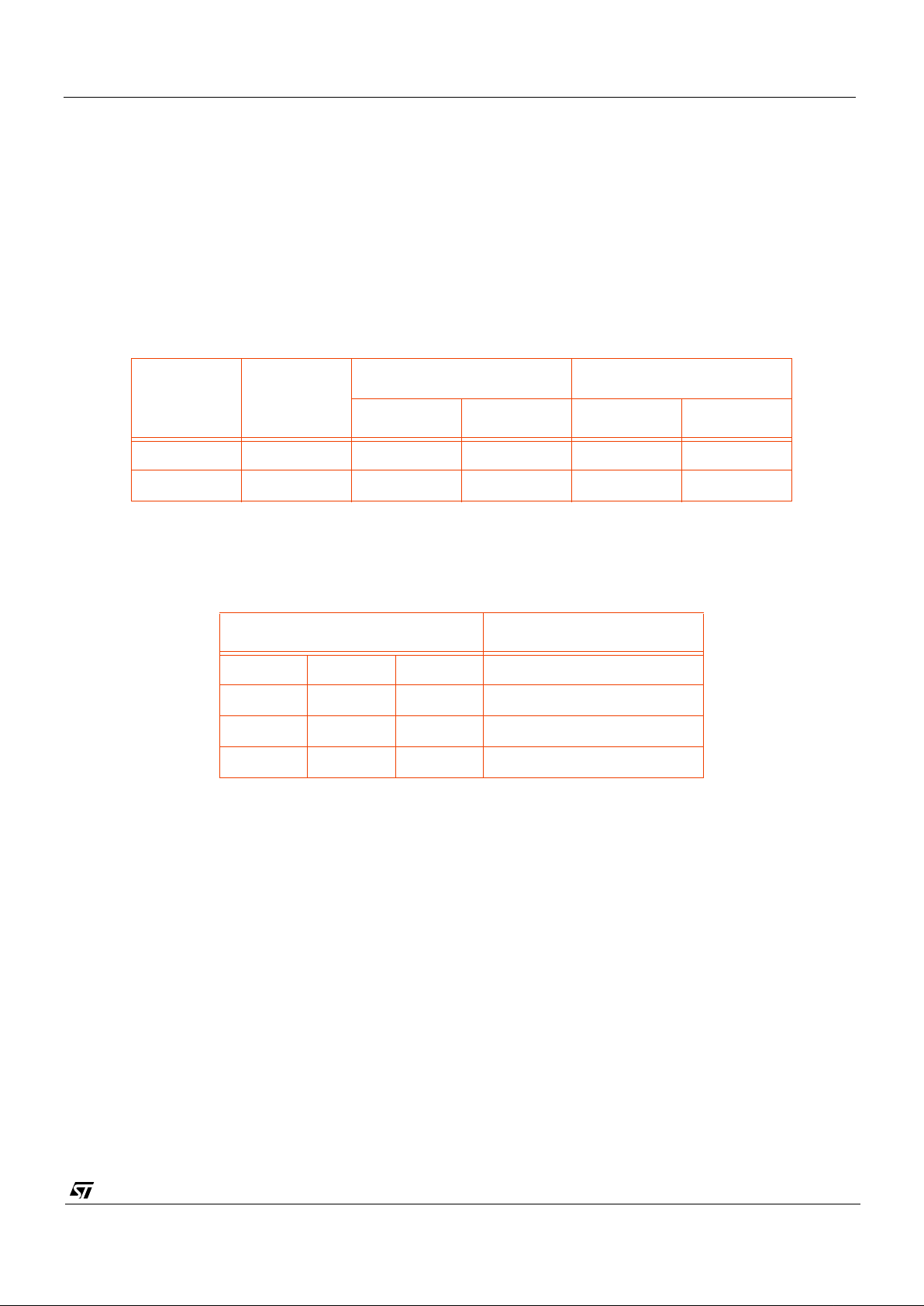

2.2 Frame Rate Options

Two options: 30 fps or 25 fps (Assuming a 7.15909 MHz input clock and the default clock divider setting). The number

of video lines in for each frame rate is the same (304), the slower frame rate is implemented by extending the line

period from 393 pixel periods to 471 pixel periods. 30 fps is the default option, the frame rate is programmable via the

serial interface.

Border Image size (column x row)

Disabled 352 x 288

Enabled 356 x 292 Default

Table 1 : Image Format Selection.

F rame Rate (fps) Fr ame Timing (Pixels x Lines)

25 471 x 304

30 393 x 304 default

Table 2 : Frame Rate Selection

Blue Green

Green Red

Even

Columns

(0, 2, 4,...)

Odd

Columns

(1, 3, 5,...)

Even

Rows

(0, 2, 4,...)

Odd

Rows

(1, 3, 5,...)

Figure 3 : Bayer Colourisation Pattern. (VV6404 only)

VV5404 & VV6404

CD5404-6404F-A

7/54

Blue Green

Green Red

Blue Green

Green Red

Blue Green

Green Red

Blue Green

Green Red

Blue Green

Green Red

Blue Green

Green Red

Blue Green

Green Red

Blue Green

Green Red

355354353

352

289

291

290

288

1

3

2

0

321

0

Figure 4 : VV6404 Colourised Image Format

352 Pixels

288 Pixels

292 Pixels

356 Pixels

0, 1, 2, 3,... ... 352, 353, 354, 355

0, 1, 2, 3,... ... 288, 289, 290, 291

Border Rows and Columns

Pixel Array

VV5404 & VV6404

CD5404-6404F-A

8/54

3. Exposure Control

The exposur e time for a pixel and the gain of the input amplifier to the 8-bit ADC are programmable via the serial

interface. The explanation below assumes that the gain and exposure values are updated together as part of a 5 byte

serial interface auto- incr em ent seq uence.

The exposure is divided into 2 components - coarse and fine. The coarse exposure value sets the number of lines a

pixel exposes for, while the fine exposure sets the number of additional pixel clock cycles a pixel integrates for. The

sum of the two gives the overall exposure time for the pixel array.

30 fps mode: Exposure Time = (Clock Divisor) x (Coarse x 393 + Fine) x (CKI clock period)/

25 fps mode: Exposure Time = (Clock Divisor) x (Coarse x 471 + Fine) x (CKI clock period)

If an exposure value is loaded outwith the valid ranges listed in the above table the value is clipped to lie within the

above ranges.

Exposure and gain values are re-timed within the sensor to ensure that a new set of values is only applied to the

sensor array at the start of each frame. Bit 0 of the Status Register is set high when a new exposure value is written

via the serial interface but has not yet been applied to the sensor array.

There is a 1 frame latency between a new exposure value being applied to the sensor array and the results of the

new exposure value being read-out. The same latency does not exist for the gain value. To ensure that the new

exposure and gain values are aligned up correctly the sensor delays the application of the new gain value by one

frame relative to the application of the new exposure value.

To eliminate the possibi li ty of the sensor array seeing only part of the new exposure and gain setting, if the serial

interface communications extends over a frame boundary, the internal re-timing of exposure and gain data is disabled

while writing data to any lo cation in t he Exposure page of the s erial interface register map. Thus if the 5 bytes of

exposure and gain data is sent as an auto-increment sequence, it is not possible for the sensor to consume only part

of the new exposure and gain data.

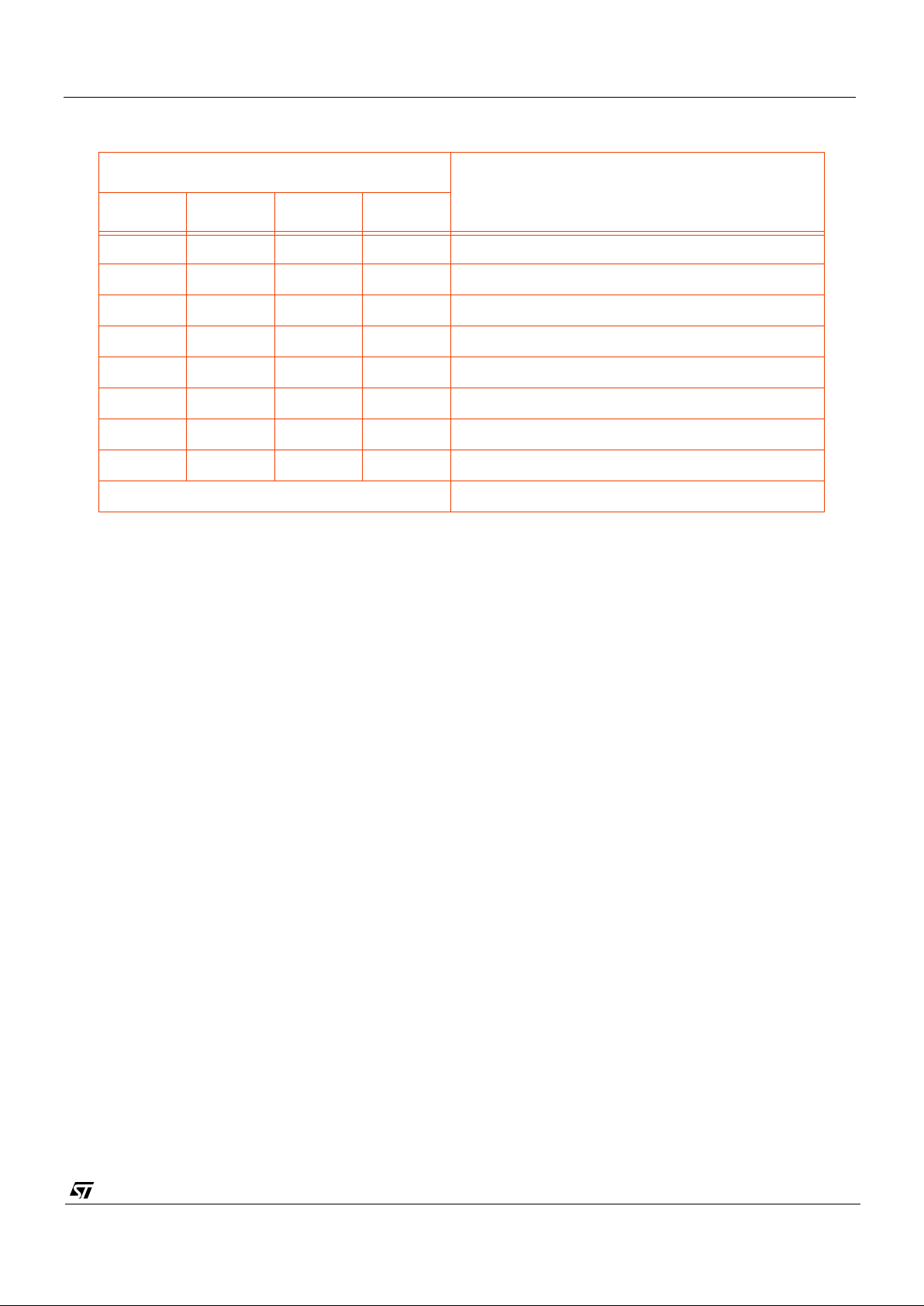

Value Units

30 fps mode 25 fps mode

Min. Max. Min. Max.

Coarse Video Lines 0 302 0 302

Fine Pixel Clocks 0 356 0 434

Table 3 : Coarse and Fine Exposure Ranges.

Gain Code, G[2:0] Amplifier Gain

000 1

001 2

011 4

111 8

Table 4 : Main Gain Steps.

VV5404 & VV6404

CD5404-6404F-A

9/54

4. Digital Video Interface Format

4.1 General descriptio n

The video interface consists of a unidirectional, tri-stateable 4-wire databus. The nibble transmission is synchronised

to the rising edge of the system clock (Figure 13).

Digital video data is 8 bits per sample, transmitted as serial pairs of parallel 4-bit nibbles (most significant nibble first)

on 4 wires.

Multiplexed with the sampled pixel data is control information including both video timing references and sensor

status/configuration data. Video timing reference information takes the form of field start characters, line start

characters, end of line characters and a line counter.

Where hexadecimal values are us ed, they ar e ind ic ate d by a subscri pt H, such as FF

H

; other values are decimal.

4.2 Embedded control data

To distinguish the control data from the sampled video data all control data is encapsulated in embedded control

sequences. These are a mi nim um of 6 words long and incl ude s a combined escape/sync character, 1 contro l word

(the ‘command byte’) and 2 words of supplementary data.

To minimise the susceptibility of the embedded control data to random bit errors redundant coding techniques have

been used to allow single bit errors in the embedded control words to be corrected. However, more serious corruption

of control words or the corruption of escape/sync characters cannot be tolerated without loss of sync to the data

stream. To ensure that a loss of sync is detected a simple set of rules has been devised. The four exceptions to the

rules are outl ined below:

1. Data containing a command words that has two bit errors.

2. Data containing two ‘end of line’ codes that are not separated by a ‘start of line’ code.

3. Data preceding an ‘end of frame’ code before a start of frame’ code has been received.

4. Data containing line that do not have sequential line numbers (excluding the ‘end of frame’ line).

If the video processor detects one of these violations then it should abandon the current frame of video.

4.2.1 The combined escape and sync character

Each embedded control sequence begins with a combined escape and sync character that is made up of three words.

The first two of these are FF

H

FFH- constituting two words that are illegal in normal data. The next word is 00H guarantee ing a cl e ar sig nal tran siti on tha t all ows a vid eo pr oc esso r to d eter mi ne t he posi tio n of the word boundaries

in the serial stream of nibbles. Combined escape and sync characters are always followed by a command word making up the four word minimum embedded control sequence.

4.2.2 The command word

The word that follows the combined escape/sync characters defines the type of embedded control data. Three of the

8 bits are used to carry the control information, four are ‘parity bits’ that allow the video processor to detect and correct

a certain level of errors in the transmission of the command words, the remaining bit is always set to 1 to ensure that

the command word is never has the value 00

H

. The coding scheme used allows the correction of single bit errors (in

the 8-bit sequence) and the detection of 2 bit errors. The three data bits of the command word are inte rpreted as

shown in Figure 5.

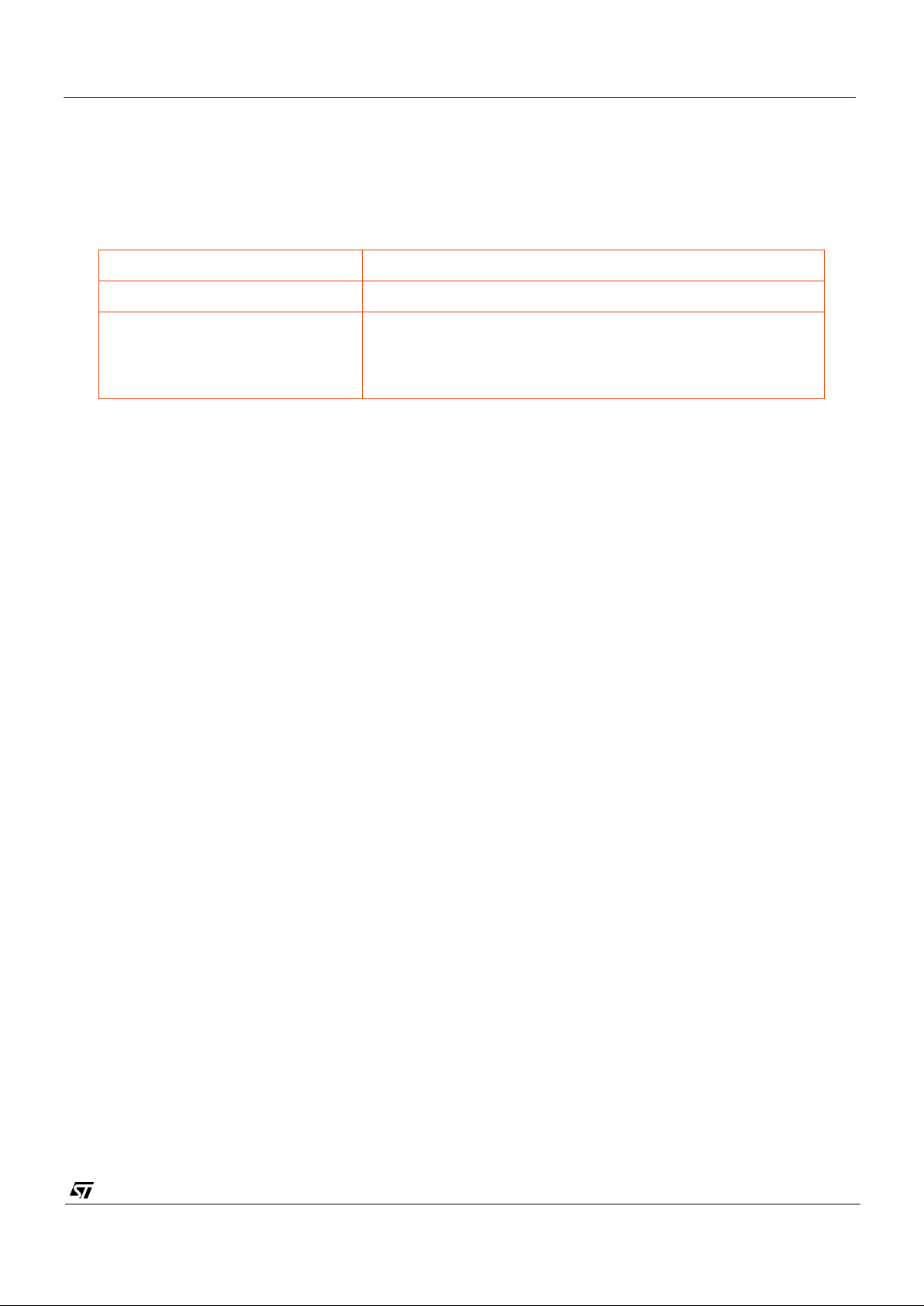

Read-out Order Progressive Scan (Non-interlaced)

Form of encoding Uniformly quantised, PCM, 8 bits per sample

Correspondence between video

signal levels and quantisation

levels:

Internally valid pixel data is clipped to ensure that 00

H

and FFH

values do not occur when pixel data is being output on the data

bus. This gives 254 possible values for each pixel (1 - 254). The

video black level co rre sp onds to code 16.

Table 5 : Video encoding parameters

VV5404 & VV6404

CD5404-6404F-A

10/54

Figure 5 : Embedded Control Sequence

(i) Line Number (L11 MSB)

(Line Code)

Escape/Sync Sequence

Bit

76543210

Odd word parity

FHF

H

FHF

H

0H0

H

YHX

H

D

2D3

D

0D1

P2P

3

P1P

0

or (ii) If Line Code = End of Line then

Nibble X

H

Nibble Y

H

Nibble D

3

Nibble D

2

Nibble D

1

Nibble D

0

Nibble D3 = F

H

Nibble D1 = F

H

Nibble D2 = F

H

Nibble D0= F

H

Line Code

Nibble X

H

Nibble Y

H

1 C2 C1 C

0

P3 P2 P1 P

0

End of Line 10002 (8H)0000

2

(0H)

Blank Line (BL) 1001

2 (9H

) 11012 (DH)

Black line (BK) 10102 (AH) 10112 (BH)

Visible Line (VL) 1011

2 (BH

)0110

2

(6H)

Start of Frame (SOF) 1100

2 (CH

)0111

2

(7H)

End of Frame (EOF) 11012 (DH) 10102 (AH)

Reserved 1110

2 (EH

) 11002 (CH)

Reserved 1111

2 (FH

)0001

2

(1H)

Bit

76543210

C

2

1

C1C

0

L7L

8

L6PL

11

0

L10L

9

L1L

2

L0PL

5

0

L4L

3

11 1111 11

11 1111 11

Supplementary Data

Command

4-wire nibble output mode

VV5404 & VV6404

CD5404-6404F-A

11/54

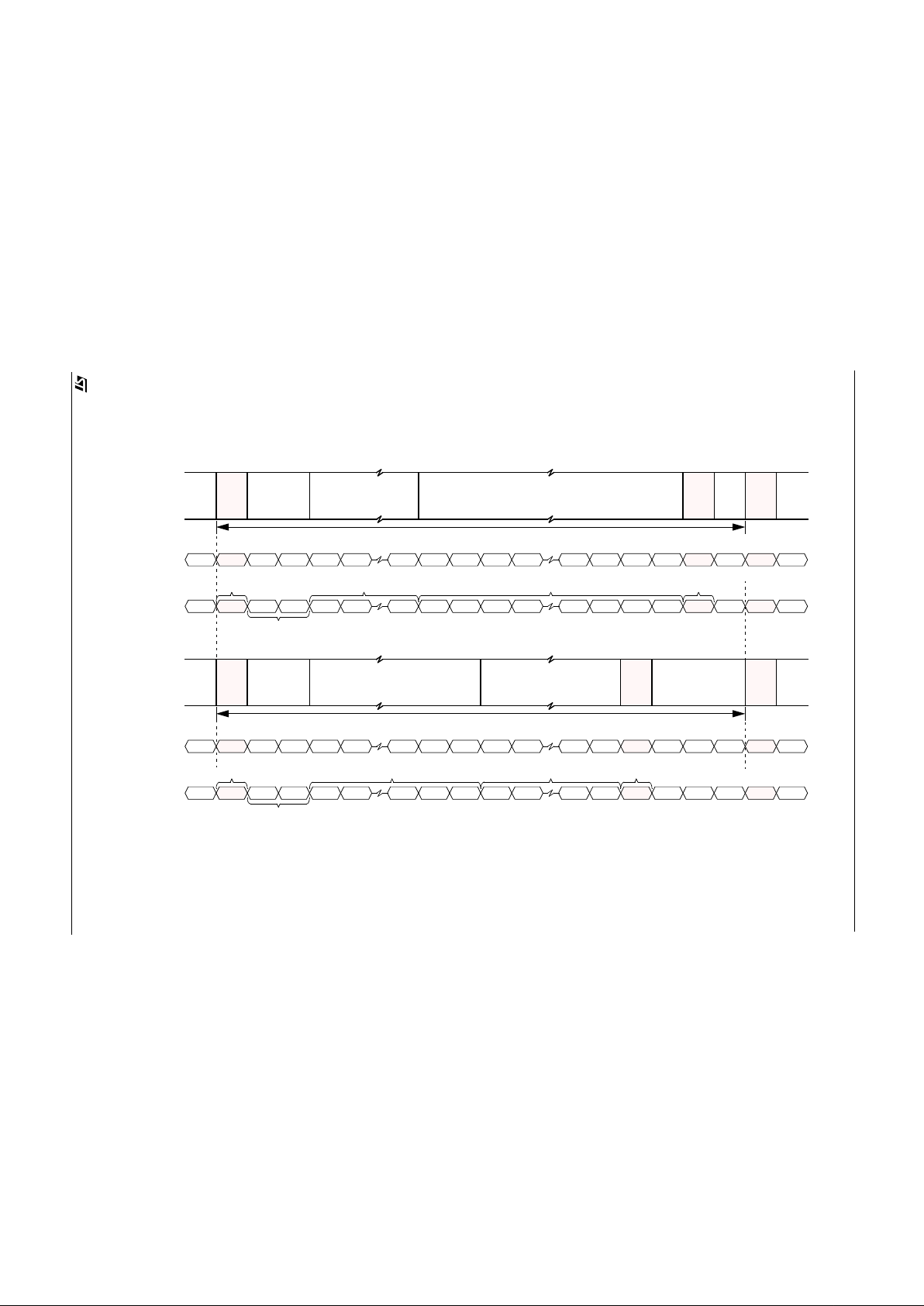

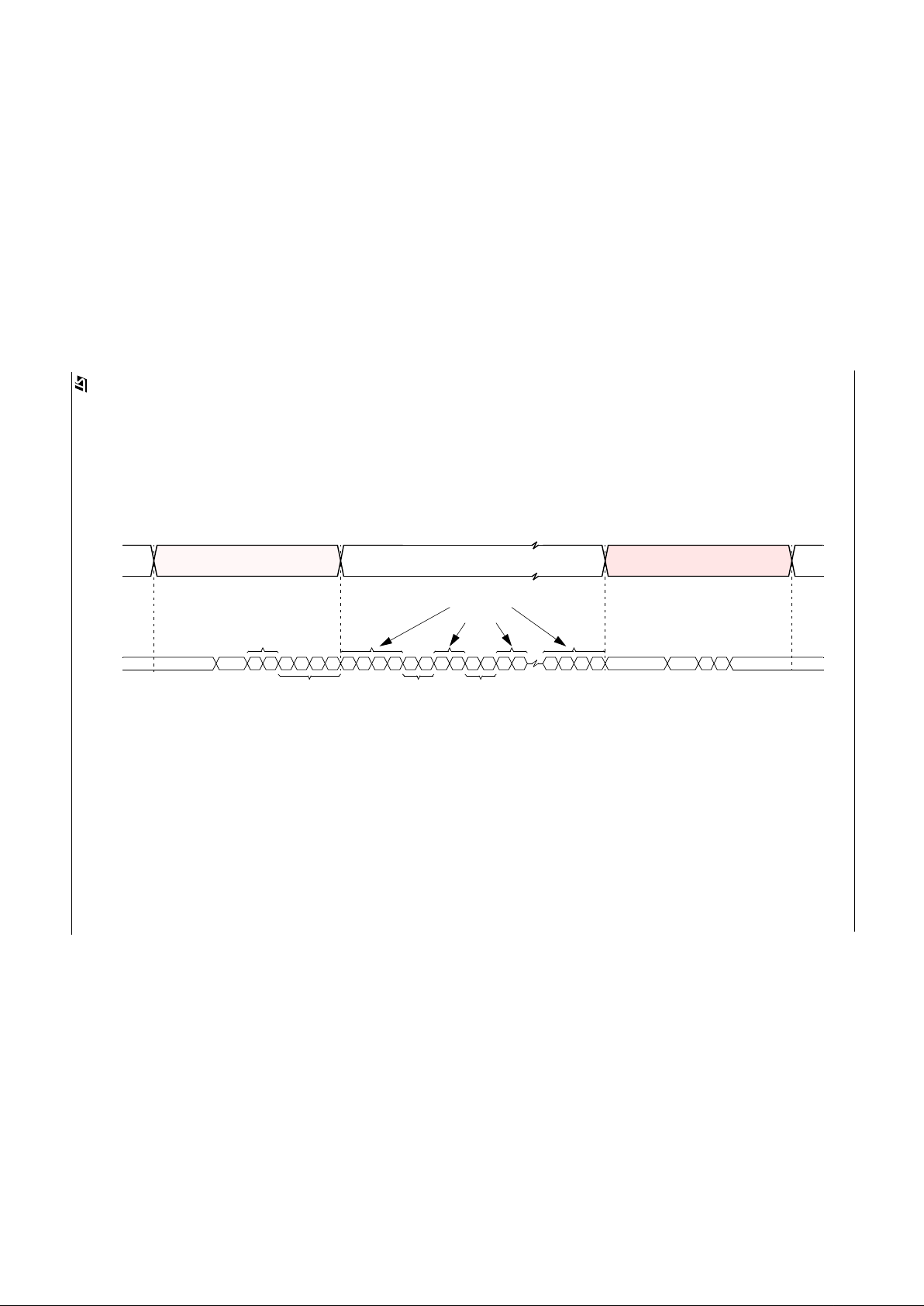

SOF

Line

2 Black Lines (BK)

7 Blank Lines (BL) 292 Visible Lines (VL)Start of Image (SOF)

BK BK BL BL BL VL VL VL VL VL VL VL VL SOF BKEOF BL

303

1234 9101112

13 299298 300 301 1303

Number

Line

Code

Figure 6 : Frame Formats

Start of

Blanking

End of

Image Data

Frame

Frame

Start of

Frame

Frame Period (304 Lines)

BL

Lines

Black

Lines

0 0302

Blanking

Line

End of Image (EOF)

Start of

Blanking

End of

Image Data

Frame

Frame

Start of

Frame

Lines

Black

Lines

Blanking

Lines

SOF

2 Black Lines (BK)

9 Blank Lines (BL) 288 Visible Lines (VL)Start of Image (SOF)

BK BK BL BL BL VL VL VL VL SOF BKEOF BL

303

1234 9101112

13 299298 300 301 1303

Frame Period (304 Lines)

BL

0 0302

End of Image (EOF)

BL BLBL BL

Frame Format (Border rows and columns enabled - Default) :

Frame Format (Border rows and columns disabled)) :

Line

Number

Line

Code

VV5404 & VV6404

CD5404-6404F-A

12/54

Start of Active Video (SAV)

Line

Figure 7 : Line Data Format.

End of Active Video (EAV)

Video Data

178 Odd Pixels 178 Even Pixels

0HY

H

D1D

0

D3D

2

PMP

L

PMP

L

PMP

L

PMP

L

F

H

Line Format

PMP

L

PMP

L

Number

SAV

Line Period (393 Pixel Periods - 30 fps, 471 Pixel Periods - 25 fps)

1

3 355 0 352 354

356 Pixels

Pixel Number (Shuffled Pixel Data)

F

H

F

H

FHFHFHFH0H0H8H0

H

0HX

H

Line

Code

Escape/Sync

Sequence

Null

Characters

Line

Code

Escape/Sync

Sequence

4-wire Nibble Output Mode, D[3:0]

0

1 177 178 354 355

Pixel Number (Unshuffled Pixel Data)

P

M

= Pixel Value - Most Significant Nibble, PL = Pixel Value - Least Significant Nibble, P = 8-bit Pixel Value

(i)

(ii)

(iii)

(iv)

(v)

Blanking Line (BL)

Black Line (BK)

Visible Line (VL)

Start of Frame (SOF)

End of Frame (EOF)

P = Blanking Level (07

H

)

P = Valid Black Pixel Da ta

P = Valid Pixel Data

P = Sensor Status Data

P = Blanking Level (07

H

)

VV5404 & VV6404

CD5404-6404F-A

13/54

The even parity bits are based on the following relationships:

1. An even number of ones in the 4-bit sequence (C

2

, C1, C0 and P0).

2. An even number of ones in the 3-bit sequence (C

2

, C1, P1).

3. An even number of ones in the 3-bit sequence (C

2

, C0, P2).

4. An even number of ones in the 3-bit sequence (C

1

, C0, P3).

Table 6 shows how the parity bits maybe used to detect and correct 1-bit errors and detect 2-bit errors.

4.2.3 Supplementary Data

The last 2 bytes of the embedded control sequence contains supplementary data. This normally contains the current

line number except if the line code is the end of line, the 2 bytes are padded out using null characters (FF

H

). The 12

bit line number is packaged up by splitting it into two 6-bit values. Each 6-bit values is then converted into an 8-bit

value by adding a zero to the start and an odd word parity bit at the end.

4.3 Video timing reference and status/configuration data

The video sequence is made up of lines of data. Each field of data is constructed of the following data lines:

1. A start of frame line

2. 2 of ‘black lines’ (used for black level calibration)

3. 7 (9) of blank lines

4. 292 (288) active video lines

5. An end of frame line

6. 1 (3) blank lines

The numbers given in () are for when the bor de r rows and columns are not output on the databus.

Each line of data starts with an embedded control sequence that identifies the line type (as outlined in Table 3). The

control sequ enc e is the n fol low ed by two by tes that, excep t in th e cas e of the end-of-frame line, conta in a coded line

number. The line number sequences starts with the start-of-frame line at 00

H

and increments one per line up until the

end-of-frame line. Each line is terminated with an end-of-line embedded control sequence. The line start embedded

sequences must be used to recognise data lines as a number of null bytes may be inserted between data lines.

Parity Checks

Comment

P

3

P

2

P

1

P

0

1 1 1 1 Code word un-corrupted

1110P

0

corrupted, line code OK

1101P

1

corrupted, line code OK

1011P

2

corrupted, line code OK

0111P

3

corrupted, line code OK

0010C

0

corrupted, invert sense of C

0

0100C

1

corrupted, invert sense of C

1

1000C

2

corrupted, invert sense of C2

All other codes 2-bit error in code word.

Table 6 : Detection of 1-bit and 2-bit errors in the Command Word

VV5404 & VV6404

CD5404-6404F-A

14/54

4.3.1 Blank lines

In addition to padding between data lines, actual blank data lines may appear in the positions indicated above. These

lines begin with start-of-blank-line embedded control sequences and are constructed identically to active video lines

except that they will contain only blank bytes (07

H

).

4.3.2 Black line timing

The black lines (which are used for black level calibration) are identical in structure to valid video lines except that

they begin with a start-of-black line sequence and contain either information from the sensor ‘black lines’ or blank

bytes (07

H

).

4.3.3 Valid video line timing

All valid video data is contained on active video lines. The pixel data appears as a continuous stream of bytes within

the active lines. The pixel data may be separated from the line header and end-of-line control sequence by a number

of ‘blank’ bytes (07

H

), e.g. when the border lines and pixels are disabled 07H is output in place of pixels 0, 1, 354 and

355.

4.3.4 Start of frame line timing

The start of frame line which begins each video field contains no video data but ins tead contains the contents of all

the serial interface registers. This information follows the start-of-line header immediately and is terminated by an

end-of-line control sequence. To ensure that no escape/sync characters appear in the sensor status/configuration

informati on the code 0 7

H

is output after each serial interface value. Thus it takes 256 pixel clock periods (512 system

clocks) to output all 128 of the serial interface registers. The remainder of the 356 pixel periods of the video portion

of the line is padded out using 07

H

values. The first two pixel locations are also padded with 07H characters (Figure 8)

If a serial interface register location is unused then 07

H

is output. The read-out order of the registers is independent

of whether the pixel read-out order is shuffled or un-shuffled.

4.3.5 End of frame line timing

The end of frame line which begins each video field contains no video data. Its sole purpose is to indicate the end of

a frame.

4.4 Detection of sensor using data bus state

The video processor device must have internal pull-down terminations on the data bus. On power-up a sensor will

pull all data lines high for a guaranteed period. This scheme allows the presence of a sensor on the interface to be

detected by the video processor on power-up, and the connection of a sensor to an already power-up interface (a

‘hot’ connection).

The absence of a sens or is detected by the vide o pr ocessor seeing more than 32 consecutive nibbles of 0

H

on the

data bus. On detecting the absence of a sensor, CKI, should be disabled (held low).

The presence of a sensor is detecte d by the video processor seeing more than 32 consecutive nibbles of F

H

on the

data bus. On detecting the presence of a sensor, CKI, should be enabled.

4.5 Resetting the Sensor Via the Serial Interface

Bit 2 of setup register 0 allows the VV6404 sensor to be reset to its power-on state via the 2-wire serial interface.

Setting this “Soft Reset” bit causes all of the serial interface registers including the “Soft Reset” bit to be reset to their

default values. This “Soft Reset” leaves the sensor in low-power mode and thus an “Exit Low-Power Mode” command

(Section 4.6.2) must be issued via the serial interface before the sensor will start to generate video data (Figure 9).

4.6 Power-up, Low-power and Sleep modes

To clarify the state of the interface on power-up and in the case of a ‘hot’ connection of the interface cable the powerup state of the bus is defined below.

VV5404 & VV6404

CD5404-6404F-A

15/54

Start of Active Video

Figure 8 : Status Line Data Format.

End of Active Video

Serial Interface Register Values

0H1

H

0H1

H

0H7

H

F

H

F

H

F

H

Output Databus, D[3:0]

1H9

H

(SAV) (EAV)

CH7

H

0H7

H

0H7H4H0

H

0H7

H

0H7

H

0H7

H

8H0

H

0

H

0

H

Start of Frame

Line Code

Line

Number 0

DeviceH

(Register 0)

DeviceL

(Register 1)

Padding

Characters

VV5404 & VV6404

CD5404-6404F-A

16/54

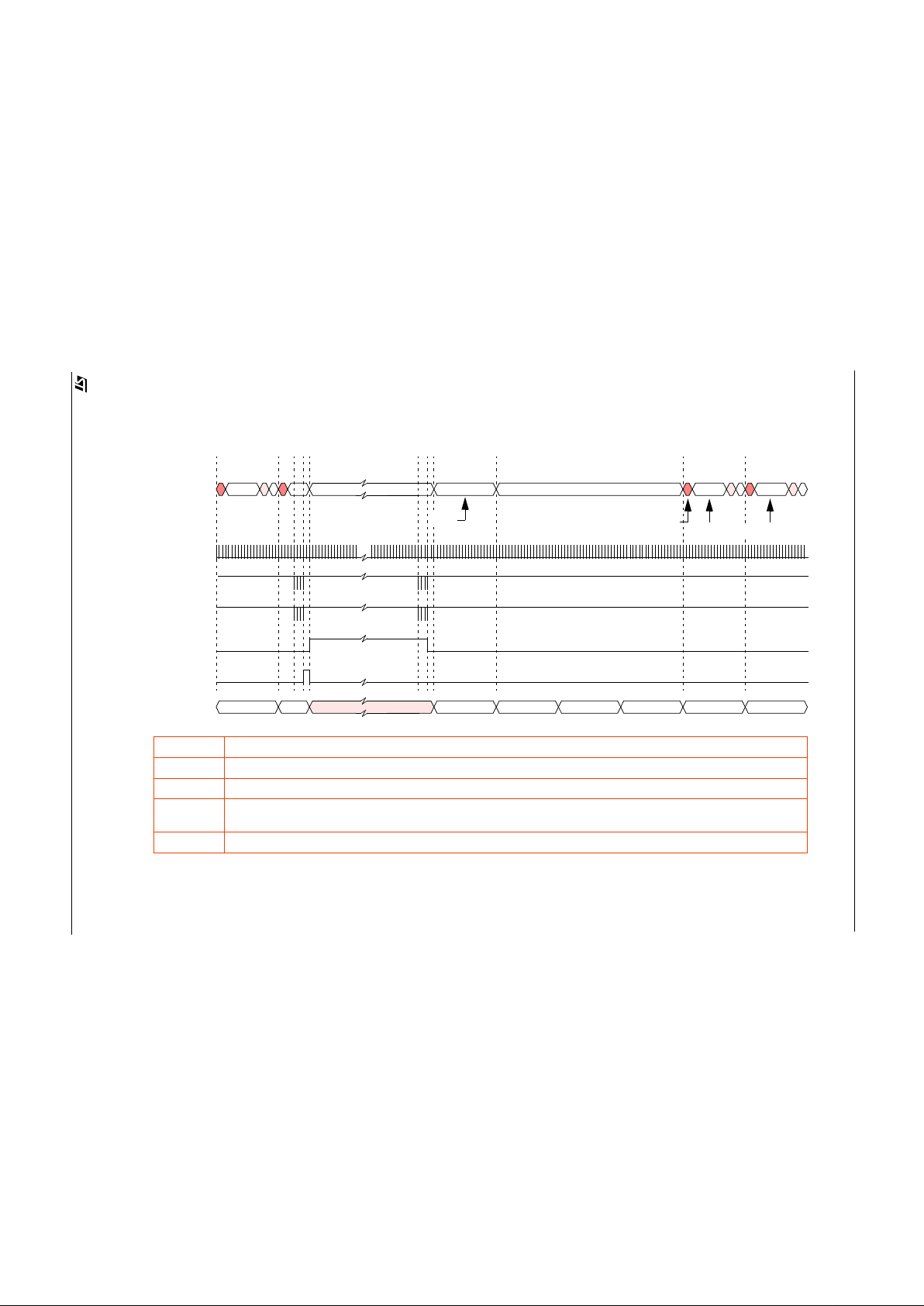

Figure 9 : Resetting the VV6404 Sensor via the Serial Interface.

F

H

9H,6H,9H,6H...

N 0 1

D[3:0]

CLKI

Frame

Number

SDA

SCL

2 3 4 5

Start of Frame Line for the 1st

frame of valid video data.

Valid Video data.

SR0

SR1

SR2

SR6

SR7

setup0[2]

SR0-SR1 “Soft-Reset” Command. At the end of the command the sensor is reset and enters low-power mode.

SR2 The sensor enters low-power mode.

SR3-SR4 “Exit Low Power Mode” Command. Powers-up analogue circuits and initiates the VM6404 sensor’s 4-frame start-up sequence

SR5-SR6 1 Frame of alternating 9

H

& 6H data on D[3:0] for the video processor to determine the best sampling phase for the nibble data

(D[3:0]).

SR7-SR8 4 Frames after the “Exit Low-Power mode” command, the sensor starts outputing valid video data.

One frame of 9H & 6H data.

F

H

SR3

SR4

SR5

SR8

setup0[0]

VV5404 & VV6404

CD5404-6404F-A

17/54

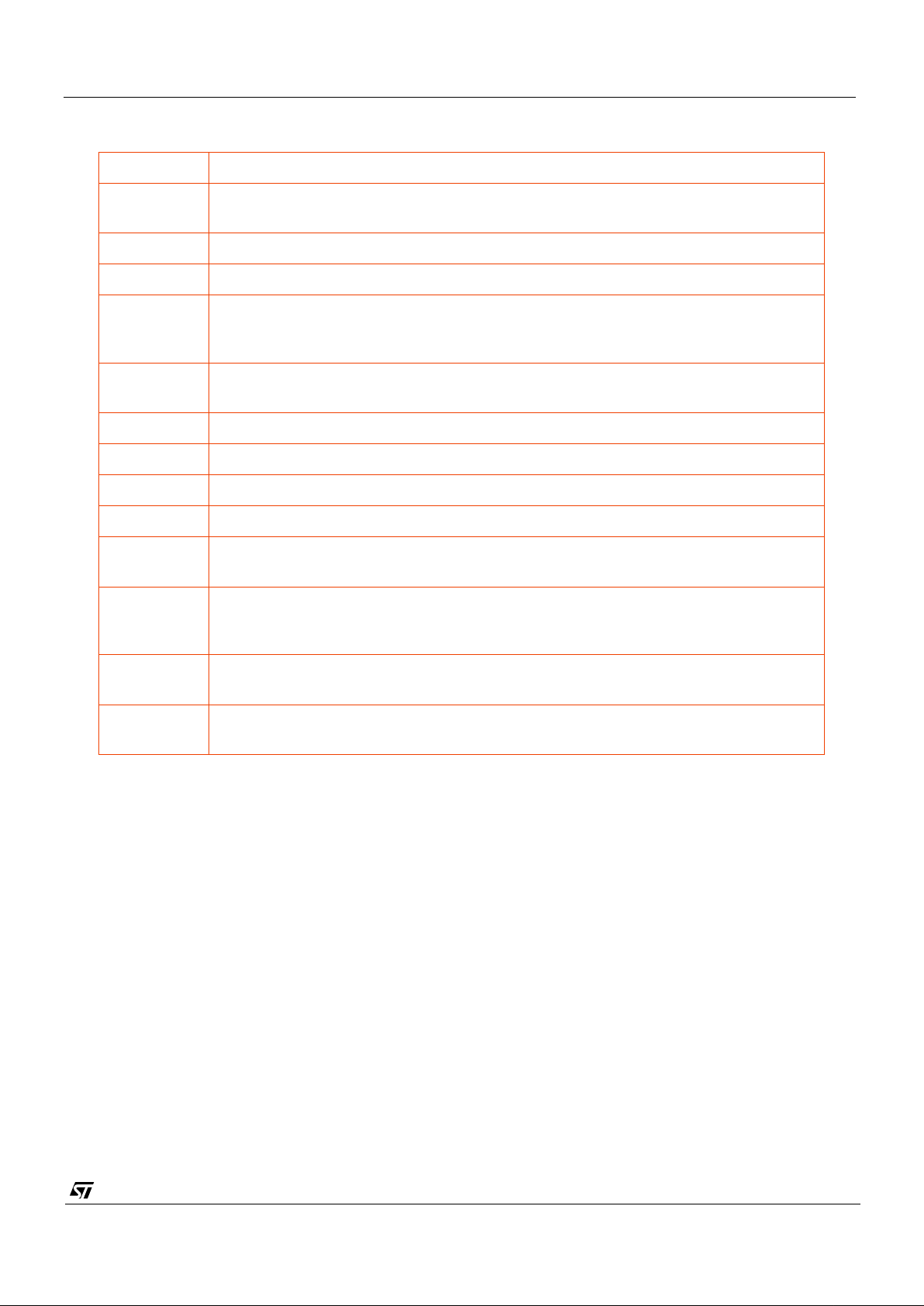

PU0 System Power Up or Sensor Hot Plugged

PU1 Sensor Internal-on Reset Triggers, the sensor enters low power mode and D[3:0] is set

to F

H

.

PU2 Video Processor released from reset.

PU3 Video Processor enables the sensor clock, CLKI.

PU4-PU5 At least 16 CLKI clock periods after CLKI has been enabled the VP sends a “Soft-Reset”

command to the sensor via the serial interface. T his e nsu r es that if a sensor is pre sen t

then it is in low-power mode.

PU6 On detecting 32 consecutive F

H

values on D[3:0], the Video Processor sets the

no_camera low.

PU7-PU8 If present, upload the sensor defect map from E

2

PROM into the Video Process or

PU9 Video Processor disables the sensor clock, CLKI.

PU10 Video Processor generates the VP_Ready interrupt.

PU11 The host software services the VP_Ready interrupt.

PU12 Host issues command to remove sensor from low-power mode. VP enables the sensor

clock, CLKI.

PU13-PU4 At least 16 CLKI clock periods after CLKI has been enabled the VP sends the “Exit Low-

Power Mode” command to the sensor via the serial interface. This initiates the sensors

4 frame start sequence.

PU15-PU16 One frame of alternating 9

H

& 6H data on D[3:0] for the video processor to determine the

best sampling phase for the nibble dat a (D[3:0]).

PU17-PU18 4 Frames after the “Exit Low-Power Mode” serial comms, the sensor starts outputing

valid video data.

Table 7 : System Power-Up or Hot-plugging Device Behaviour

Loading...

Loading...