SST/U401NL Series

New Product

Vishay Siliconix

Monolithic N-Channel JFET Duals

SST404NL

SST406NL

PRODUCT SUMMARY

Part Number V

U401NL -0.5 to -2.5 -40 1 -2 5

SST/U404NL -0.5 to -2.5 -40 1 -2 15

SST/U406NL -0.5 to -2.5 -40 1 -2 40

FEATURES BENEFITS APPLICATIONS

D Anti Latchup Capability

D Monolithic Design

D High Slew Rate

D Low Offset/Drift Voltage

D Low Gate Leakage: 2 pA

D Low Noise

D High CMRR: 102 dB

DESCRIPTION

GS(off)

(V) V

(BR)GSS

Min (V) gfs Min (mS) IG Typ (pA) V

D External Substrate Bias—Avoids Latchup

D Tight Differential Match vs. Current

D Improved Op Amp Speed, Settling Time Accuracy

D Minimum Input Error/Trimming Requirement

D Insignificant Signal Loss/Error Voltage

D High System Sensitivity

D Minimum Error with Large Input Signal

U401NL

U404NL

- V

GS1

D Wideband Differential Amps

D

High-Speed,Temp-Compensated,

Single-Ended Input Amps

D High-Speed Comparators

D Impedance Converters

U406NL

Max (mV)

GS2

The SST/U401NL series of high-performance monolithic dual

JFETs features extremely low noise, tight offset voltage and

low drift over temperature specifications, and is targeted for

use in a wide range of precision instrumentation applications.

This series has a wide selection of offset and drift

specifications with the U401NL featuring a 5-mV offset and

10-mV/_C drift.

Pins 4 and 8 of the SST series, and pin 4 of the U series part

Narrow Body SOIC

S

1

1

D

2

1

G

3

1

SUBSTRATE S

4

Top View

Marking Codes:

SST404NL - 404NL

SST406NL - 406NL

8

7

6

5

SUBSTRATE

G

2

D

2

2

ABSOLUTE MAXIMUM RATINGS

Gate-Drain, Gate-Source Voltage -40 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Gate Current 10 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead Temperature (

Storage Temperature : U Prefix -65 to 200_C. . . . . . . . . . . . . . . . . . . . .

For applications information see AN106.

1

/16” from case for 10 sec.) 300_C. . . . . . . . . . . . . . . . . . .

SST Prefix -55 to 150_C. . . . . . . . . . . . . . . . . . .

numbers enable the substrate to be connected to a positive

polarity, external bias (V

) to avoid latchup.

DD

The U series, hermetically sealed TO-78 package is

available with full military processing. The SS T series SO-8

package provides ease of manufacturing, and the

symmetrical p inout prevents im proper orientation. T he SO-8

package is available with tape-and-reel options for

compatibility with automatic assembly methods.

TO-78

S

1

1

D

1

2

3

G

1

Operating Junction Temperature -55 to 150_C. . . . . . . . . . . . . . . . . . . . . . . . . .

Power Dissipation : Per Side

Notes

a. Derate 2.4 mW/_C above 25_C

b. Derate 4 mW/_C above 25_C

4

CASE, SUBSTRATE

Top View

U401NL

U404NL

U406NL

Total

G

2

7

D

2

6

5

S

2

a

b

300 mW. . . . . . . . . . . . . . . . . . . . . . . .

500 mW. . . . . . . . . . . . . . . . . . . . . . . . . . .

Document Number: 72055

S-22448—Rev. A, 17-Feb-03

www.vishay.com

7-1

SST/U401NL Series

Gate-Source

V

Gate Operating

Gate-Source Voltage

|

|

VDG = 10 V

g

DT

D

m

m

Vishay Siliconix

New Product

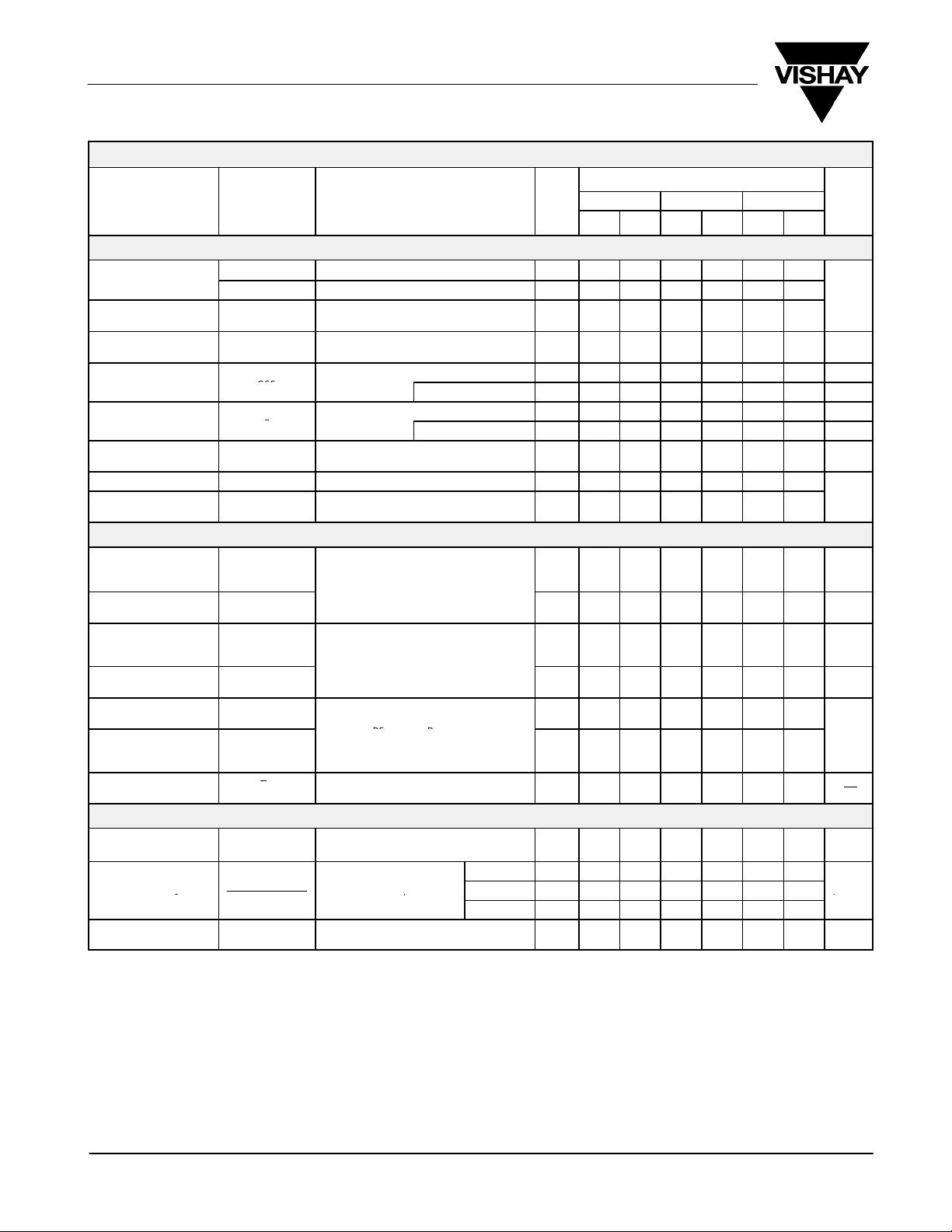

SPECIFICATIONS (TA = 25_C UNLESS OTHERWISE NOTED)

Limits

U401NL SST/U404NL SST/U406NL

Parameter Symbol Test Conditions TypaMin Max Min Max Min Max Unit

Static

Gate-Source

Breakdown Voltage

Gate-Source

Cutoff Voltage

Saturation

Drain Current

Gate Reverse Current I

Gate Operating

Current

Drain-Source

On-Resistance

Gate-Source Voltage V

Gate-Source

Forward Voltage

b

V

V

(BR)G1 - G2

V

r

V

(BR)GSS

GS(off)

I

DSS

GSS

I

G

DS(on)

GS

GS(F)

IG = -1 mA, VDS = 0 V

IG = "1 mA, VDS = 0 V, VGS = 0 V

VDS = 15 V, ID = 1 nA -1.5 -0.5 -2.5 -0.5 -2.5 -0.5 -2.5

VDS = 10 V, VGS = 0 V 3.5 0.5 10 0.5 10 0.5 10 mA

VGS = -30 V, VDS = 0 V -2 -25 -25 -25 pA

TA = 125_C

VDG = 15 V, ID = 200 mA

TA = 125_C

VGS = 0 V, ID = 0.1 mA 250

VDG = 15 V, ID = 200 mA

IG = 1 mA , VDS = 0 V 0.7

Dynamic

Common-Source

Forward

Transconductance

Common-Source

Output Conductance

Common-Source

Forward

Transconductance

Common-Source

Output Conductance

Common-Source

Input Capacitance

Common-Source

Reverse Transfer

Capacitance

Equivalent Input

Noise Voltage

g

fs

g

os

g

fs

g

os

C

iss

C

rss

e

n

VDS = 15 V, ID = 200 mA

f = 1 kHz

VDS = 10 V, VGS = 0 V

f = 1 kHz

VDS = 15 V, ID = 200 mA

f = 1 MHz

VDS = 15 V, ID = 200 mA

f = 10 Hz (U Only)

Matching

Differential

Gate-Source Voltage

Differential Change

with Temperature

Common Mode

Rejection Ratio

Notes

a. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing. NNR

b. Pulse test: PW v300 ms duty cycle v3%.

|

V

GS1–VGS2

D

V

GS1–VGS2

CMRR

|

VDG = 10 V, ID = 200 mA

=

ID = 200 mA

TA = -55 to 125_C

VDG = 10 to 20 V, ID = 200 mA

SST404NL 20

SST406NL 40

All U 10 25 80

-58 -40 -40 -40

"45 "30 "30 "30

-1 nA

-2 -15 -15 -15 pA

-0.8 -10 -10 -10 nA

-1 -2.3 -2.3 -2.3

1.5 1 2 1 2 1 2 mS

1.3 2 2 2

4 2 7 2 7 2 7 mS

5 30 30 30

4 8 8 8

1.5 3 3 3

10 20 20 20

5 15 40 mV

mV/_C

102 95 95 dB

V

W

V

mS

mS

pF

nV⁄

√Hz

www.vishay.com

7-2

Document Number: 72055

S-22448—Rev. A, 17-Feb-03

Loading...

Loading...