查询TFDS6402供应商

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Fast Infrared Transceiver Module Family

(FIR, 4 Mbit/s) for 2.6 V to 5.5 V Operation

Description

The TFDU6102E, TFDS6402, TFDS6502E,

TFDT6502E are a family of low–power infrared

transceiver modules compliant to the IrDA physical

layer standard for fast infrared data communication,

supporting IrDA speeds up to 4.0 Mbit/s (FIR),

HP-SIR, Sharp ASK and carrier based remote control

modes up to 2 MHz. Integrated within the transceiver

modules are a photo PIN diode, an infrared emitter

(IRED), and a low–power CMOS control IC to provide

a total front–end solution in a single package.

Vishay Telefunken’s FIR transceivers are available in

four package options, including our Baby Face

package (TFDU610xE), the standard setting, once

smallest FIR transceiver available on the market. This

wide selection provides flexibility for a variety of

applications and space constraints. The transceivers

are capable of directly interfacing with a wide variety

of I/O devices which perform the modulation/

demodulation function, including National

Semiconductor’s PC87338, PC87108 and PC87109,

SMC’s FDC37C669, FDC37N769 and CAM35C44,

and Hitachi’s SH3. At a minimum, a current–limiting

resistor in series with the infrared emitter and a

VCC bypass capacitor are the only external

components required implementing a complete

solution.

Vishay Semiconductor

Features

Compliant to the IrDA physical layer specification

(Up to 4 Mbit/s),

HP–SIR, Sharp ASK and TV Remote Control

For 3.0 V and 5.0 V Applications

Operates from 2.6 V to 5.5 V within specification,

operational down to 2.4 V

Low Power Consumption (3 mA Supply Current)

Power Shutdown Mode (1 A Shutdown Current)

Four Surface Mount Package Options

– Universal (9.7 × 4.7 × 4.0 mm)

– Side View (13.0 × 5.95 × 5.3 mm)

– Top View (13.0 × 7.6 × 5.95 mm)

– Dracula (11.2 × 5.6 × 2.2 mm)

Push-Pull-Receiver Output, grounded in

shutdown mode

Applications

Notebook Computers, Desktop PCs,

Palmtop Computers (Win CE, Palm PC), PDAs

Digital Still and Video Cameras

Printers, Fax Machines, Photocopiers,

Screen Projectors

High Efficiency Emitter

Baby Face (Universal) Package Capable of

Surface Mount Soldering to Side and Top View

Orientation

Directly Interfaces with Various Super I/O and

Controller Devices

Built–In EMI Protection – No External Shielding

Necessary

Few External Components Required

Backward Pin to Pin Compatible to all Vishay

Telefunken SIR and FIR Infrared Transceivers

Split power supply , transmitter and receiver can be

operated from two power supplies with relaxed

requirements, thus saving costs

Telecommunication Products

(Cellular Phones, Pagers)

Internet TV Boxes, Video Conferencing Systems

External Infrared Adapters (Dongles)

Medical and Industrial Data Collection Devices

Document Number 82526

Rev. B1.6, 02–Nov–00 1

www.vishay.com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

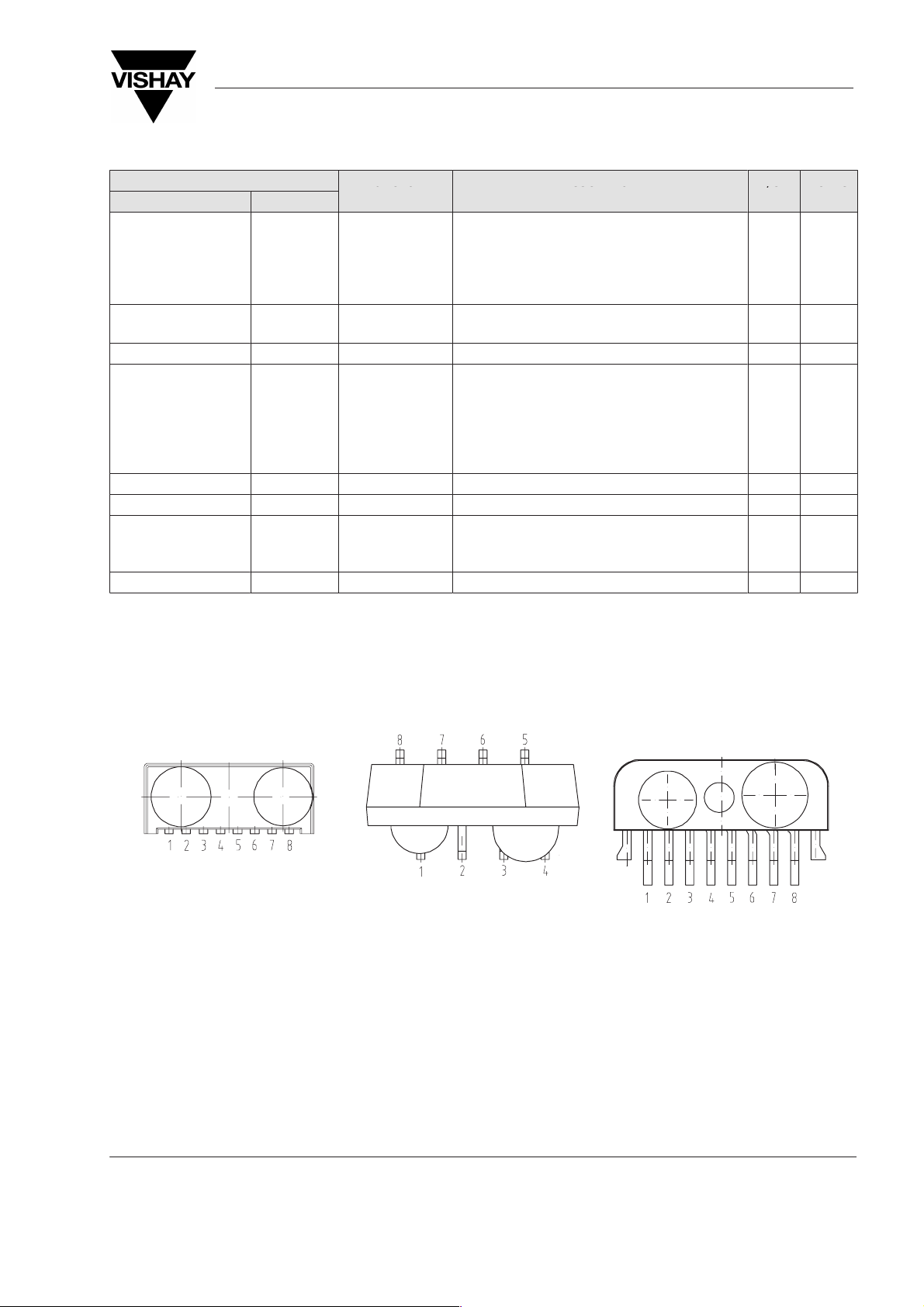

Package Options

TFDU6102E

Baby Face (Universal)

weight 0.20 g

TFDS6402

Dracula Side View

weight 0.30 g

TFDS6502E

Side View

weight 0.39 g

TFDT6502E

Top View

weight 0.39 g

Ordering Information

Part Number Qty / Reel Description

TFDU6102E–TR3 1000 pcs Oriented in carrier tape for side view surface mounting

TFDU6102E–TT3 1000 pcs Oriented in carrier tape for top view surface mounting

TFDS6402–TR3 1000 pcs Side View

TFDS6502E–TR3 750 pcs Side View

TFDT6502E–TR3 750 pcs Top View

Functional Block Diagram

Amplifier

SD/Mode

Txd

AGC

Logic

Open Drain Driver

V

CC

Comparator

GND

Figure 1. Functional Block Diagram

Driver

Rxd

IRED Anode

IRED Cathode

www.vishay.com Document Number 82526

Rev. B1.6, 02–Nov–002

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Function

Descri tion

I/O

Active

Pin Description

Pin Number Function Description I/O Active

“U” and “T” Option “S” Option

1 8 IRED Anode IRED anode, to be externally connected

2 1 IRED Cathode IRED cathode, internally connected to

3 7 Txd Transmit Data Input I HIGH

4 2 Rxd Received Data Output, push-pull CMOS

5 6 SD/Mode Shutdown/ Mode I HIGH

6 3 V

7 5 Mode HIGH: High speed mode;

8 4 GND Ground

CC

Vishay Semiconductor

to V

through a current control resistor.

CC

This pin is allowed to be supplied from

an uncontrolled power supply separated

from the controlled V

driver transistor

driver output capable of driving a standard CMOS or TTL load. No external

pull-up or pull-down resistor is required.

Pin is floating when

device is in shutdown mode

Supply Voltage

LOW: Low speed mode, SIR only

(see chapter “Mode Switching”)

supply

CC

O LOW

I

“U” Option Baby Face (Universal)

and Dracula

IRED Detector

14885

“S” Option Side View “T” Option Top View

IRED Detector

IRED Detector

Figure 2. Pinnings

Document Number 82526

Rev. B1.6, 02–Nov–00 3

www.vishay.com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

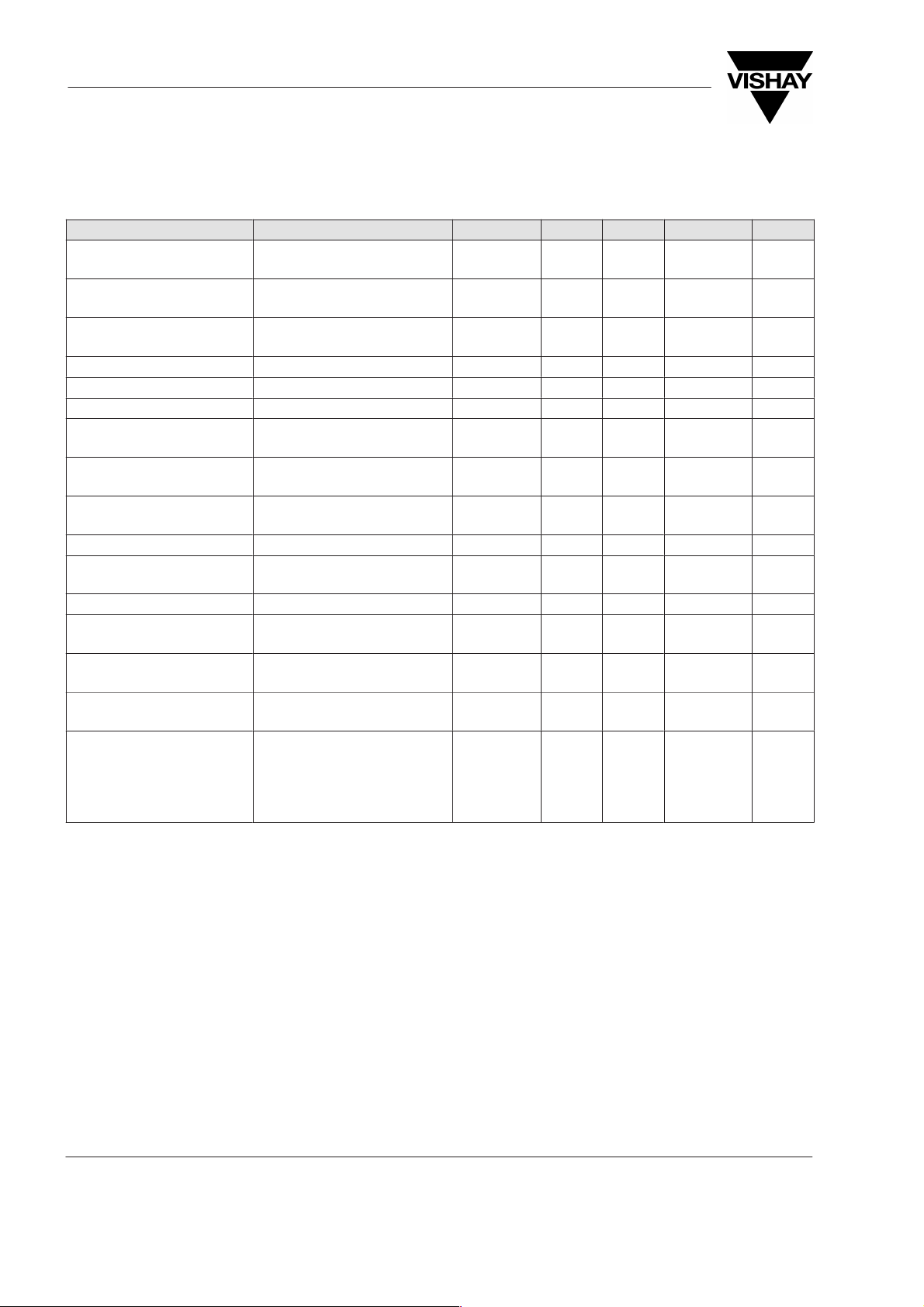

Absolute Maximum Ratings

Reference point Pin: GND unless otherwise noted.

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

Parameters Test Conditions Symbol Min. Typ. Max. Unit

Supply Voltage Range,

Transceiver

Supply Voltage Range,

Transmitter

Input Currents For all Pins, Except IRED

Output Sinking Current 25 mA

Power Dissipation See Derating Curve P

Junction Temperature T

Ambient Temperature

Range (Operating)

Storage Temperature

Range

Soldering Temperature See Recommended Solder

Average Output Current I

Repetitive Pulsed Output

Current

IRED Anode Voltage V

Transmitter Data Input

Voltage

Receiver Data Output

Voltage

Virtual Source Size Method:

Maximum Intensity for

Class 1 Operation of

IEC825–1 or EN60825–1

(worst case IrDA FIR

pulse pattern)

0 V <V

0 V <V

<6 V V

CC2

<6 V V

CC1

Anode Pin

Profile (see Figure 11)

<90 µs, ton <20% I

(1–1/e) encircled energy

EN60825, 1997,

unidirectional operation,

worst case test mode

CC1

CC2

– 0.5 6 V

– 0.5 6 V

10 mA

350 mW

125 °C

T

amb

T

stg

D

J

–25 +85 °C

–25 +85 °C

240 °C

(DC) 130 mA

IRED

(RP) 600 mA

IRED

IREDA

V

Txd

V

Rxd

– 0.5 6 V

– 0.5 V

– 0.5 V

+0.5 V

CC1

+0.5 V

CC1

d 2.5 2.8 mm

320 mW/sr

www.vishay.com Document Number 82526

Rev. B1.6, 02–Nov–004

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Mode Floating,

In ut Voltage High

Vishay Semiconductor

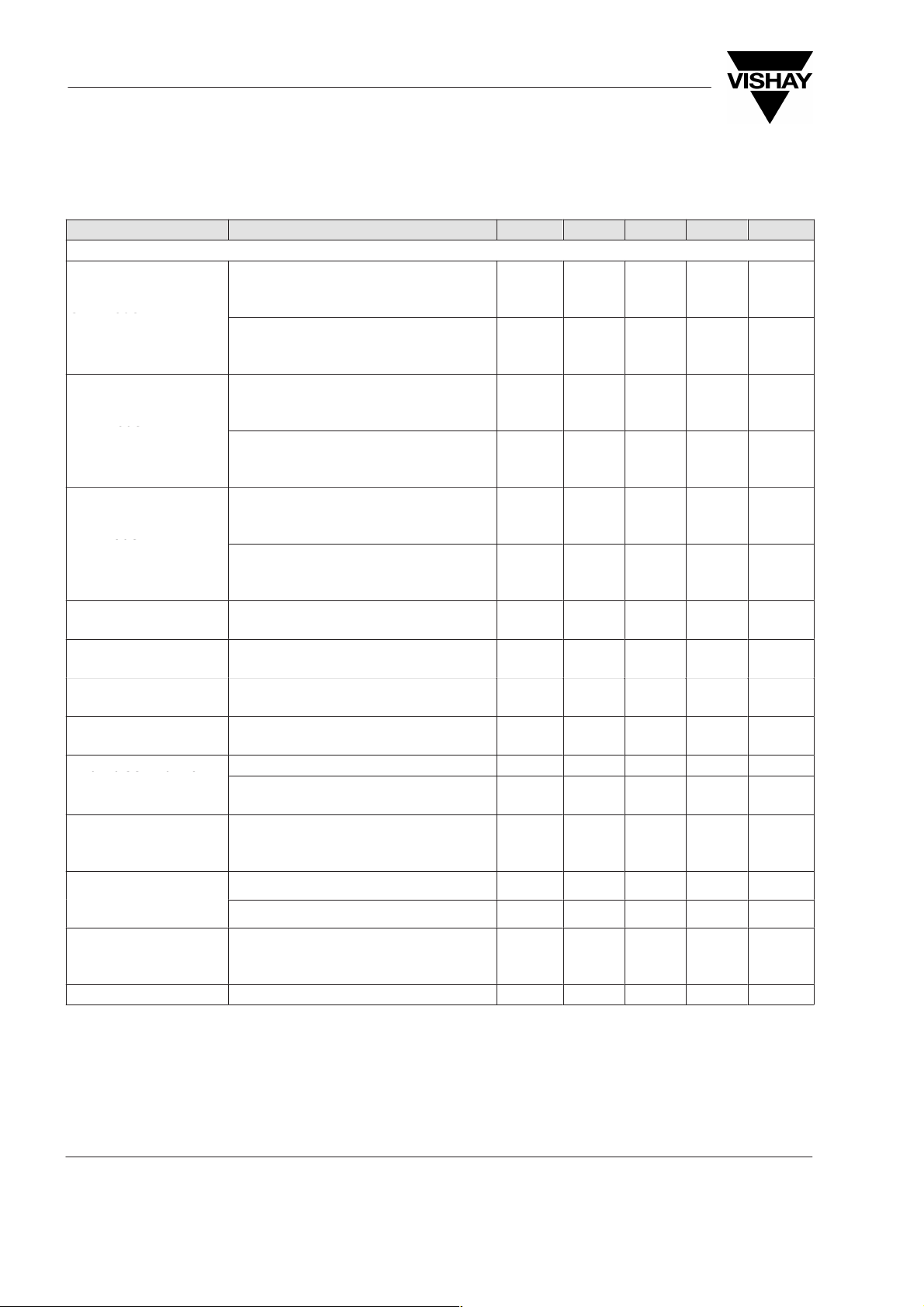

Electrical Characteristics

T

= 25_C, VCC = 2.6V to 5.5 V unless otherwise noted.

amb

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

Parameters Test Conditions / Pins Symbol Min. Typ. Max. Unit

Transceiver

Supply Voltage V

Dynamic Supply Current Receive mode only.

In transmit mode, add additional 85 mA (typ) for IRED current

SD = Low, Ee = 0 klx I

SD = Low, Ee = 1 klx *) I

Standby Supply Current SD = High,

Mode = Floating,

I

T = 25°C, Ee = 0 klx

T = 25°C, Ee = 1 klx *)

SD = High, T = 85°C,

I

Mode = Floating,

Not Ambient Light

Sensitive

Operating Temperature

T

Range

Output Voltage Low R

Output Voltage High R

Input Voltage Low

load

C

load

load

C

load

= 2.2 kW,

= 15 pF

= 2.2 kW,

= 15 pF

V

V

V

(Txd, SD/ Mode, Mode)

Input Voltage High CMOS level **) V

(Txd, SD/ Mode, Mode)

TTL level, VCC ≥ 4.5 V V

Input Leakage Current

(Txd, SD/ Mode)

Input Leakage Current,

Mode

Input Capacitance C

CC

CC

CC

SD

SD

OL

OH

I

I

A

IL

IH

IH

L

L

I

2.6 5.5 V

3 4.5 mA

3 4.5 mA

–25 +85 °C

0.5 0.8 V

VCC–0.5 V

0 0.8 V

0.9 x V

CC

2.4 V

–10 +10 µA

–80 +80 µA

1

1.5

5 µA

5 pF

µA

µA

V

*) Standard Illuminant A

**) The typical threshold level is between 0.5 x V

Document Number 82526

Rev. B1.6, 02–Nov–00 5

(VCC = 3 V) and 0.4 x VCC (VCC = 5.5 V) .

CC/2

It is recommended to use the specified min/ max values to avoid increased operating current.

www.vishay.com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

SIR Mode

MIR Mode

FIR Mode

Rxd Pulse Width of

O

50%

Vishay Semiconductor

Optoelectronic Characteristics

T

= 25_C, VCC = 2.6 V to 5.5 V unless otherwise noted.

amb

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

Parameters Test Conditions Symbol Min. Typ. Max. Unit

Receiver

Minimum Detection

Threshold Irradiance,

SIR Mode

Minimum Detection

Threshold Irradiance,

MIR Mode

Minimum Detection

Threshold Irradiance,

FIR Mode

Maximum Detection

Threshold Irradiance

Logic LOW Receiver

Input Irradiance

Rise Time of Output

Signal––,,,,klll

Fall Time of Output

Signal

Rxd Pulse Width of Input pulse length 20 µs, 9.6 kbit/s t

Output Signal, 50%

SIR Mode

Rxd Pulse Width of

Output Signal, 50%

MIR Mode

Rxd Pulse Width ofpInput pulse length 125 ns, 4.0 Mbit/s t

utput Signal,

FIR Mode

Stochastic Jitter,

Leading Edge,

FIR Mode

Latency t

TFDS6502E/ TFDT6502E

9.6 kbit/s to 115.2 kbit/s

l = 850 nm to 900 nm

TFDU6102E, TFDS6402

9.6 kbit/s to 115.2 kbit/s

l = 850 nm to 900 nm

TFDS6502E/ TFDT6502E

1.152 Mbit/s

l = 850 nm to 900 nm

TFDU6102E, TFDS6402

1.152 Mbit/s

l = 850 nm to 900 nm

TFDS6502E/ TFDT6502E

4.0 Mbit/s

l = 850 nm to 900 nm

TFDU6102E, TFDS6402

4.0 Mbit/s

l = 850 nm to 900 nm

l = 850 nm to 900 nm E

10% to 90%, @2.2 kΩ, 15 pF t

90% to 10%, @2.2 kΩ, 15 pF t

Input pulse length 1.41 ms,

r (Rxd)

f (Rxd)

t

115.2 kbit/s

Input pulse length 217 ns,

t

1.152 Mbit/s

Input pulse length 250 ns, 4.0 Mbit/s t

Input Irradiance = 100 mW/m2,

4.0 Mbit/s

E

E

E

E

E

E

E

PW

PW

PW

PW

PW

e

e

e

e

e

e

e

e

5 10 kW/m

4 mW/m

20 35 mW/m

25 40 mW/m

50 mW/m

65 mW/m

65 100 mW/m

85 100 mW/m

10 40 ns

10 40 ns

1.2 10 20 µs

1.2 1/2 bit

length

110 260 ns

100 160 ns

200 290 ns

±10 ns

L

120 300 µs

2

2

2

2

2

2

2

2

µs

www.vishay.com Document Number 82526

Rev. B1.6, 02–Nov–006

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Duration

Vishay Semiconductor

Optoelectronic Characteristics (continued)

T

= 25_C, VCC = 2.6 V to 5.5 V unless otherwise noted.

amb

Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

Parameters Test Conditions Symbol Min. Typ. Max. Unit

Transmitter

IRED Operating Current R1*) = 7.2 Ω, VCC = 5.0 V I

Output Radiant Intensity

(see Figure 3)

VCC = 5.0 V, α = 0_, 15_

Txd = High, SD = Low, R1 = 7.2 Ω

Output Radiant Intensity VCC = 5.0 V, α = 0_, 15_

D

I

e

I

e

120 170 350 mW/sr

Txd = Low, SD = High,

(Receiver is inactive as long as

SD = High) R1 = 7.2 Ω

Output Radiant Intensity,

a ±24 °

Angle of Half Intensity

Peak – Emission

l

P

880 900 nm

Wavelength

Optical Output Pulse

Duration

Input pulse width 217 ns,

1.152 Mbit/s

Input pulse width 125 ns,

t

opt

t

opt

207 217 227 ns

117 125 133 ns

4 Mbit/s

Input pulse width 250 ns,

t

opt

242 250 258 ns

4 Mbit/s

Input pulse width t < 80 µs

t

opt

Input pulse width t ≥ 80 µs

Optical Rise Time,

Fall Time

t

ropt

t

fopt

,

10 40 ns

Optical Overshoot 10 %

0.4 0.55 A

0.04 mW/sr

t

80

µs

*) R1: control series resistor for current limitation

Document Number 82526

Rev. B1.6, 02–Nov–00 7

www.vishay.com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

Recommended Circuit Diagram

The only required component for designing an

IrDA 1.3 solution using Vishay Telefunken

transceivers is a current limiting resistor, R1, to the

IRED. However, depending on the entire system

design and board layout, additional components may

be required (see figure 3).

V

CC2

V

CC1

Rxd

GND

SD/Mode

Txd

Figure 3. Recommended Application Circuit

R1

R2

IRED

Cathode

Rxd

IRED

Anode

Txd

TFDx6x0xE

C2C1

Note: outlined components are optional depending

on the quality of the power supply

Vcc

GND

SD/Mode

Mode

Vishay Telefunken transceivers integrate a sensitive

receiver and a built-in power driver. The combination

of both needs a careful circuit board layout. The use of

thin, long, resistive and inductive wiring should be

avoided. The inputs (Txd, SD/ Mode) and the output

Rxd should be directly (DC) coupled to the I/O circuit.

R1 is used for controlling the current through the

IR emitter. For increasing the output power of the

IRED, the value of the resistor should be reduced.

Similarly , to reduce the output power of the IRED, the

value of the resistor should be increased. For typical

values of R1 see figure 4. For IrDA compliant

operation, a current control resistor of 7.2 Ω is

recommended. For compensating losses of the cosmetic window, reducing that value to 5.6 Ω is

acceptable. The upper drive current limitation is

dependent on the duty cycle and is given by the

absolute maximum ratings on the data sheet.

R2, C1 and C2 are optional and dependent on the

quality of the supply voltage V

and injected noise.

CC

An unstable power supply with dropping voltage during

transmission may reduce sensitivity (and transmission

range) of the transceiver.

The placement of these parts is critical. It is strongly

recommended to position C2 as near as possible to the

transceiver power supply pins. An electrolytic

capacitor should be used for C1 while a ceramic

capacitor is used for C2.

Table 1. Recommended Application Circuit Components

Component Recommended Value Vishay Part Number

C1 4.7 mF, Tantalum 293D 475X9 016B 2T

C2 0.1 µF, Ceramic VJ 1206 Y 104 J XXMT

R1 5 V supply voltage: 7.2 Ω , 0.25 W

(recommend using

two 3.6 W, 0.125 W resistors in series)

CRCW–1206–3R60–F–RT1

3.3 V supply voltage: 3.6 Ω , 0.25 W

(recommend using

two 1.8 W, 0.125 W resistors in series)

CRCW–1206–1R80–F–RT1

R2 47 Ω , 0.125 W CRCW–1206–47R0–F–RT1

www.vishay.com Document Number 82526

Rev. B1.6, 02–Nov–008

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

500

5.25V

5.0V

400

300

200

Intensity (mW/sr)

100

0

5.0V

Vcc=4.75V

min. intensity in emission cone 15°

0246810121416

Current Control Resistor ( W )14379

max. intensity in

emission cone 15°

min. R

max.R

dson

dson

, min. V

, max.V

F

F

Figure 4. Intensity Ie vs. Current Control Resistor R1,

5 V Applications

700

3.6V

600

500

400

3.3V

300

200

Intensity (mW/sr)

100

0

024681012

3.3V

Vcc=3.0V

Current Control Resistor ( W )15111

max. intensity in

emission cone 15°

min. R

min. intensity in

emission cone 15°

max. R

dson

dson

, min. V

, max. V

F

F

Figure 5. Intensity Ie vs. Current Control Resistor R1,

3 V Applications

In addition, when connecting the described circuit to

the power supply, low impedance wiring should be

used.

I/O and Software

drivers are available from SMSC and Vishay

Semiconductor GmbH. This software is intended to

work with Windows 95, too. Alternatively the

HP/ Sharp settings can be selected. The Microsoft

Operating Systems NT 5.0

Beta 2 and

Windows 2000provide Miniport device drivers.

Mode Switching

The TFDU6102E, TFDS6402, TFDS6502E and

TFDT6502E do not power on with a default mode,

therefore the data transfer rate has to be set by a programming sequence using the Txd and SD/ Mode

inputs as described below or selected by setting the

Mode Pin. The Mode Pin can be used to statically set

the mode (Mode Pin: LOW: SIR, HIGH: 0.576 Mbit/s

to 4.0 Mbit/s). When using the Mode Pin, the standby

current may increase to about 50 to 60 mA when high

or low. If not used or in standby mode, the mode input

should float to minimize standby current. The low

frequency mode covers speeds up to 1 15.2 kbit/s. Signals with higher data rates should be detected in the

high frequency mode. Lower frequency data can also

be received in the high frequency mode but with reduced sensitivity. To switch the transceivers from low

frequency mode to the high frequency mode and vice

versa, the programming sequences described below

are required.

SD/Mode

Txd

50%

Figure 6. Mode Switching Timing Diagram

Setting to the High Bandwidth Mode

(0.576 Mbit/s to 4.0 Mbit/s)

50%

t

t

s

h

High : FIR

50%

Low : SIR

14873

In the description, already different I/Os are

mentioned. Differnt combinations are tested and the

function verified with the special drivers available from

the I/O suppliers. In special cases refer to the I/O

manual, the Vishay application notes, or contact

directly Vishay Sales, Marketing or Application.

Control: Differences to TFDx6000 Series

For applications using I/Os from NSC, Winbond and TI

no software upgrade is necessary . In combination with

the latest SMSC controllers for Microsoft

Windows 98a software upgrade is necessary,

Document Number 82526

Rev. B1.6, 02–Nov–00 9

1. Set SD/MODE input to logic “HIGH”.

2. Set Txd input to logic “HIGH”. Wait ts ≥ 200 ns.

3. Set SD/MODE to logic “LOW” (this negative edge

latches state of Txd, which determines speed

setting).

4. After waiting th ≥ 200 ns Txd can be set to logic

“LOW”. The hold time of Txd is limited by the

maximum allowed pulse length.

Txd is now enabled as normal Txd input for the high

bandwidth mode.

www.vishay.com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

Setting to the Lower Bandwidth Mode

(2.4 kbit/s to 115.2 kbit/s)

1. Set SD/MODE input to logic “HIGH”.

2. Set Txd input to logic “LOW”. Wait ts ≥ 200 ns.

3. Set SD/MODE to logic “LOW” (this negative edge

latches state of Txd, which determines speed

setting).

4. Txd must be held for th ≥ 200 ns.

Txd is now enabled as normal Txd input for the lower

bandwidth mode.

Recommended SMD Pad Layout

The leads of the device should be soldered in the center position of the pads.

7 x 1 = 7

0.6 (≤ 0.7)

2.5 (≥ 2.0)

1

16524

Figure 7. TFDU6102E BabyFace (Universal)

8

1

Figure 8. TFDS6402 (Dracula)

www.vishay .com Document Number 82526

Rev. B1.6, 02–Nov–0010

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

1 1.8

5.08

2.54 2.54

5876

1.8

0.63

1.1

1.0

0.63 1

2.2

4123

2.54 2.54

8.3

15069

Figure 9. TFDS6502E Side View Package

Pad 1 is longer to designate Pin 1 connection to transceiver.

1.27 0.8

18

15068

Figure 10. TFDT6502E Top View Package

Pad 1 is longer to designate Pin 1 connection to transceiver.

Note: Leads of the device should be at least 0.3 mm within the ends of the pads.

Recommended Solder Profile

240

210

180

°

150

120

90

Temperature ( C )

60

30

0

0 50 100 150 200 250 300 350

14874

2 - 4°C/s

2 - 4°C/s

Time ( s )

10 s max.

@ 230°C

90 s max.120 - 180 s

5.08

8.89

1.8

Current Derating Diagram

600

500

400

300

Current derating as a function of

200

the maximum forward current of

IRED. Maximum duty cycle: 25%.

100

Peak Operating Current ( mA )

0

–40 –20 0 20 40 60 80 100 120 140

Temperature ( °C )14875

Figure 1 1. Recommended Solder Profile

Document Number 82526

Rev. B1.6, 02–Nov–00 11

Figure 12. Current Derating Diagram

www.vishay .com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductor

TFDU6102E – Baby Face (Universal) Package

(Mechanical Dimensions)

12249

www.vishay .com Document Number 82526

Rev. B1.6, 02–Nov–0012

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

TFDS6402 Package (Mechanical Dimensions)

Vishay Semiconductor

15971

Document Number 82526

Rev. B1.6, 02–Nov–00 13

www.vishay .com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductors

TFDS6502E – Side V iew Package (Mechanical Dimensions)

14322

www.vishay .com Document Number 82526

Rev. B1.6, 02–Nov–0014

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductors

TFDT6502E – T op View Package (Mechanical Dimensions)

14325

Document Number 82526

Rev. B1.6, 02–Nov–00 15

www.vishay .com

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductors

Revision History:

B1.1, 01/03/1999: New edition for optimized E family. TFDxxx01E – RXD output is grounded when the device

is switched to shutdown mode.

B1.2, 15/03/1999: A clean tri-state version with floating output in shutdown mode was added as 02 version. The

output radiant intensity was increased.

B1.4a, 26/10/1999:TR3 changed to TR4 for 01 types, weight of packages added.

B1.4b, 22/11/1999:Max. operating current changed from 4.0 mA to 4.5 mA, Dracula package version added,

some typos corrected.

B1.5, 13/10/2000: First typos corrected

B1.6, 02/11/2000: SMD pad layout tolerances added

www.vishay .com Document Number 82526

Rev. B1.6, 02–Nov–0016

TFDU6102E/TFDS6402/TFDS6502E/TFDT6502E

Vishay Semiconductors

Ozone Depleting Substances Policy Statement

It is the policy of Vishay Semiconductor GmbH to

1. Meet all present and future national and international statutory requirements.

2. Regularly and continuously improve the performance of our products, processes, distribution and operating

systems with respect to their impact on the health and safety of our employees and the public, as well as

their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as

ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and

forbid their use within the next ten years. V arious national and international initiatives are pressing for an earlier ban

on these substances.

Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of

ODSs listed in the following documents.

1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental

Protection Agency (EPA) in the USA

3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting

substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application

by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the

buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or

indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany

Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423

Document Number 82526

Rev. B1.6, 02–Nov–00 17

www.vishay .com

Loading...

Loading...